Trials@uspto.gov Paper 13

Tel: 571-272-7822 Date: May 31, 2023

### UNITED STATES PATENT AND TRADEMARK OFFICE

\_\_\_\_\_

### BEFORE THE PATENT TRIAL AND APPEAL BOARD

MICROSOFT CORPORATION, Petitioner,

V.

THROUGHPUTER, INC., Patent Owner.

IPR2022-01566 Patent 11,036,556 B1

\_\_\_\_\_

Before MICHAEL R. ZECHER, MATTHEW S. MEYERS, and JULIET MITCHELL DIRBA, *Administrative Patent Judges*.

DIRBA, Administrative Patent Judge.

DECISION

Denying Institution of *Inter Partes* Review 35 U.S.C. § 314

On November 7, 2022, Microsoft Corporation ("Petitioner") filed a Petition requesting *inter partes* review of claims 1–8 of U.S. Patent No. 11,036,556 B1 (Ex. 1001, "the '556 patent"). Paper 2 ("Pet."). ThroughPuter, Inc. ("Patent Owner") timely filed a Preliminary Response. Paper 8 ("Prelim. Resp."). With our authorization (Paper 10), Petitioner filed a Preliminary Reply (Paper 11, "Prelim. Reply"), and Patent Owner filed a Preliminary Sur-Reply (Paper 12, "Prelim. Sur-Reply").

An *inter partes* review may not be instituted unless "the information presented in the petition . . . and any response . . . shows that there is a reasonable likelihood that the petitioner would prevail with respect to at least 1 of the claims challenged in the petition." 35 U.S.C. § 314(a).

For the reasons given below, on this record, Petitioner has not established a reasonable likelihood that it would prevail in showing the unpatentability of at least one challenged claim. Accordingly, we do not institute an *inter partes* review of the '556 patent.

### I. BACKGROUND

### A. Related Matters

The parties indicate that the '556 patent has been asserted in *ThroughPuter, Inc. v. Microsoft Corp.*, No. 2:22-cv-00492-BJR (W.D. Wash.), which was consolidated with *ThroughPuter, Inc. v. Microsoft Corp.*, No. 2:22-cv-00344-BJR (W.D. Wash.). Pet. 76; Paper 4 (Patent Owner's Mandatory Notices), 2. The parties also state that Petitioner has challenged other patents from that litigation in IPR2022-00527, IPR2022-00528, IPR2022-00574, IPR2022-00757, and IPR2022-00758. *Id.*

### B. The Petition's Asserted Grounds

Petitioner asserts the following grounds of unpatentability (Pet. 2):

| Claim(s)<br>Challenged | 35 U.S.C. § | Reference(s)/Basis                              |

|------------------------|-------------|-------------------------------------------------|

| 1, 2, 4–8              | 1031        | Kupferschmidt <sup>2</sup> , Tuan <sup>3</sup>  |

| 1–8                    | 103         | Kupferschmidt, Tuan, Brent <sup>4</sup>         |

| 4                      | 103         | Kupferschmidt, Tuan, Sandstrom-501 <sup>5</sup> |

| 4                      | 103         | Kupferschmidt, Tuan, Brent, Sandstrom-501       |

In support of its contentions, Petitioner relies on the testimony of Jeffrey S. Chase, Ph.D. (Ex. 1003) and June Ann Munford (Ex. 1007).

C. Summary of the '556 Patent

The '556 patent is titled "Concurrent Program Execution Optimization." Ex. 1001, code (54). The application that led to the '556

<sup>&</sup>lt;sup>5</sup> US 2012/0079501 A1, published Mar. 29, 2012 (Ex. 1010).

<sup>&</sup>lt;sup>1</sup> The Leahy-Smith America Invents Act ("AIA"), Pub. L. No. 112-29, 125 Stat. 284, 285–88 (2011), revised 35 U.S.C. § 103 effective March 16, 2013. The challenged patent was filed after March 16, 2013 and claims priority to applications filed after that date. As a consequence, we refer to the current version of the statute. *Accord* Pet. 2.

<sup>&</sup>lt;sup>2</sup> US 2010/0333099 A1, published Dec. 30, 2010 (Ex. 1004).

<sup>&</sup>lt;sup>3</sup> Vu Manh Tuan, "A Study on a Multitasking Environment for Dynamically Reconfigurable Processors," Doctoral Dissertation, School of Science for Open and Environmental Systems Graduate School of Science and Technology, Keio University (2009) (Ex. 1005).

<sup>&</sup>lt;sup>4</sup> US 2010/0131955 A1, published May 27, 2010 (Ex. 1006).

patent was filed on March 8, 2021, claiming priority to applications filed as early as August 23, 2013. *Id.* at (22), (60), (63).

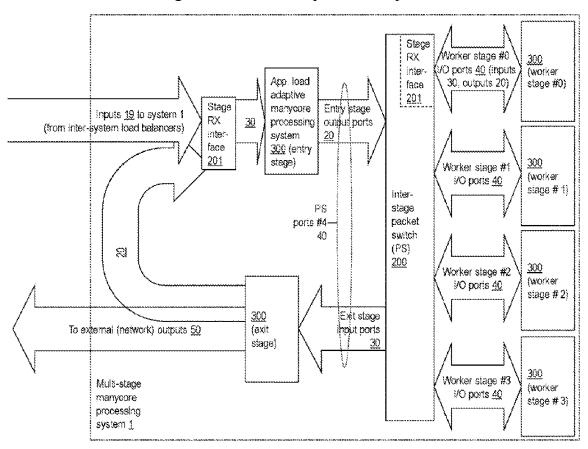

The Specification is directed to "managing execution of multiple concurrent, multi-task software programs on parallel processing hardware." Ex. 1001, 1:45–48. Figure 2 of the '556 patent is reproduced below.

## FIG. 2

Figure 2 is a functional block diagram of multi-stage manycore processing system 1, which is shared dynamically among tasks of multiple application programs (apps) and instances (insts) thereof. *Id.* at 5:18–21, 10:29–32. For each of the apps, each task is located at one of the processing stages 300. *Id.* at 10:32–33. Nevertheless, for any given app-inst, copies of same task

software can be located at more than one of the processing stages 300 of a given system 1, thus supporting any combination of pipelined and/or parallelized processing. *Id.* at 10:34–41. Hardware logic is implemented for scheduling tasks of application program instances and prioritizing inter-task communications (ITC) among tasks of a given app instance. *Id.* at 10:10–13.

### D. Challenged Claims

Petitioner challenges all eight claims of the '556 patent. Of these, only claim 1 is independent. It recites:

1. A method performed in a data processing system, the method comprising:

receiving, by hardware logic and/or software logic, requests to perform different tasks on behalf of instances of a plurality of programs managed by a data processing system;

identifying, by the hardware logic and/or software logic for each of the instances, communication interdependencies between different processing stages of a set of processing stages of the respective instance;

based on conditions in the data processing system, dynamically varying, by the hardware logic and/or software logic, structures of field-programmable gate arrays used to process different tasks of the instances of the plurality of programs, the structures being dynamically varied by

identifying available field-programmable gate arrays of the data processing system that are available to process different processing stages of requesting instances of respective programs,

based at least on the conditions in the data processing system, identifying selected fieldprogrammable gate arrays from the available fieldprogrammable gate arrays to execute the different

# DOCKET

## Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

### **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.