# **EXHIBIT C**

## US006287902B1

# (12) United States Patent Kim

(10) Patent No.:

US 6,287,902 B1

(45) **Date of Patent:** Sep. 11, 2001

# (54) METHODS OF FORMING ETCH INHIBITING STRUCTURES ON FIELD ISOLATION REGIONS

- (75) Inventor: Do-hyung Kim, Seoul (KR)

- (73) Assignee: Samsung Electronics Co., Ltd. (KR)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 09/318,188

- (22) Filed: May 25, 1999

# Related U.S. Application Data

(62) Division of application No. 08/748,148, filed on Nov. 12, 1996, now abandoned.

## (30) Foreign Application Priority Data

| Jun. | 28, 1996              | (KR)   | 96-25227         |

|------|-----------------------|--------|------------------|

| (51) | Int. Cl. <sup>7</sup> |        | H01L 21/338      |

| (52) | U.S. Cl.              | •••••  | 438/183; 438/926 |

| (58) | Field of              | Search | 438/183, 926,    |

| . ,  |                       |        | 438/740 233 439  |

# (56) References Cited

## U.S. PATENT DOCUMENTS

| 5,164,806 |           | Nagatomo et al  |         |

|-----------|-----------|-----------------|---------|

| 5,174,858 |           | Yamamoto et al  |         |

| 5,273,936 | 12/1993   | Ikeda           | 438/453 |

| 5,293,503 |           | Nishigoori      |         |

| 5,306,945 | 4/1994    | Drummond        | 257/620 |

| 5,357,133 | * 10/1994 | Morita          | 257/316 |

| 5,365,111 | 11/1994   | Ramaswami et al | 257/768 |

| 5,436,188 | 7/1995    | Chen            | 438/397 |

| 5,441,916 * 8/1995  | Motonami     | 437/195 |

|---------------------|--------------|---------|

| 5,475,266 * 12/1995 | Rodder       | 257/750 |

| 5,550,076 * 8/1996  | Chen         | 438/253 |

|                     | Ashida       |         |

| 5,698,902 * 12/1997 | Uehara et al | 257/773 |

| 5,706,164 1/1998    | Jeng         | 438/239 |

|                     | Lee          | 438/599 |

| 5,932,920 * 8/1999  | Kim et al    | 257/395 |

## FOREIGN PATENT DOCUMENTS

| 2724165   |   | 12/1977 | (DE).           |

|-----------|---|---------|-----------------|

| 0523856A2 |   | 1/1993  | (EP) H01L/21/90 |

| 53-108391 |   | 9/1978  | (JP) H01L/21/88 |

| 59-76447  | • | 5/1984  | (JP) .          |

| 59-76447  |   | 8/1984  | (JP) H01L/21/88 |

| 60-66444  |   | 4/1985  | (JP) H01L/21/76 |

| 62-177945 |   | 8/1987  | (JP) 257/758    |

| 4-63437   | • | 2/1992  | (JP) .          |

| 8-335701  | • | 2/1992  | (JP) .          |

| 9-64195   | * | 3/1997  | (JP) .          |

<sup>\*</sup> cited by examiner

Primary Examiner—Olik Chaudhuri

Assistant Examiner—Phat X. Cao

(74) Attorney, Agent, or Firm—Myers Bigel Sibley &

# (57) ABSTRACT

A microelectronic structure includes a substrate having adjacent active and field regions. A field isolation layer covers the field region, and an etch inhibiting layer is provided on the field isolation layer adjacent the active region of the substrate. An insulating layer covers the substrate, the field isolation layer, and the etch inhibiting layer, and the insulating layer defines a contact hole therein exposing a portion of the active region adjacent the etch inhibiting layer. Related methods are also discussed.

# 18 Claims, 2 Drawing Sheets

U.S. Patent

Sep. 11, 2001

Sheet 1 of 2

US 6,287,902 B1

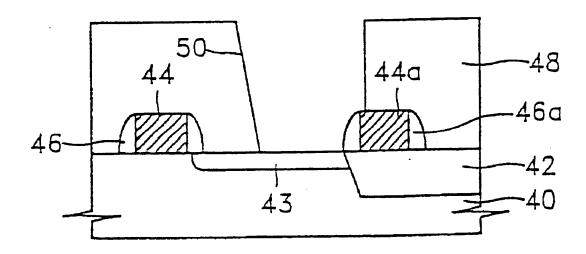

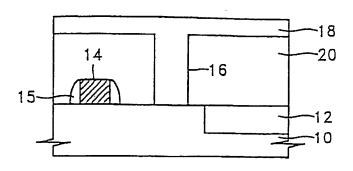

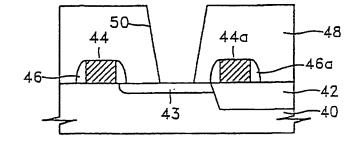

FIG. 1 (PRIOR ART)

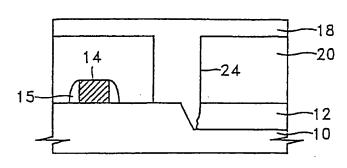

FIG. 2 (PRIOR ART)

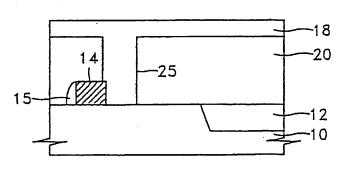

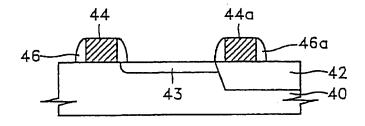

FIG. 3 (PRIOR ART)

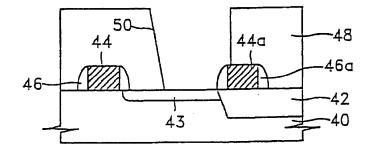

FIG. 4

U.S. Patent

Sep. 11, 2001

Sheet 2 of 2

US 6,287,902 B1

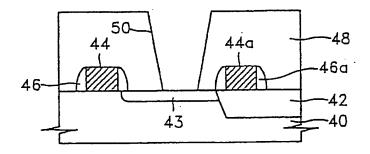

FIG. 5

FIG. 6

FIG. 7

FIG. 8

# US 6,287,902 B1

1

## METHODS OF FORMING ETCH INHIBITING STRUCTURES ON FIELD **ISOLATION REGIONS**

This application is a divisional application of U.S. patent 5 application Ser. No. 08/748,148 filed Nov. 12, 1996, abandoned, and entitled ETCH INHIBITING STRUC-TURES ON FIELD ISOLATION REGIONS AND RELATED METHODS.

#### FIELD OF THE INVENTION

The present invention relates to microelectronic structures and methods and more particularly to microelectronic structures and methods including isolation regions.

## BACKGROUND OF THE INVENTION

As integrated circuit devices become more highly integrated, the space available for individual devices formed thereon is reduced. Accordingly, the sizes of patterns such as gates, bit lines, and metal lines formed on integrated circuits are generally reduced. Furthermore, space between these patterns is also generally reduced.

In particular, integrated circuit memory devices include a plurality of memory cells, and each memory cell is connected to other cells by conductive (metal) lines. The cells and conductive (metal) lines are connected to the substrate or other conductive layers by contact holes or via holes. The contact holes expose active regions of the substrate and the via holes expose the surface of other conductive layers. 30 Patterned layers such as the gate electrodes should be isolated from the holes, and these patterned layers are generally arranged around the holes. Accordingly, the holes must be accurately placed in order to maintain electrical isolation with respect to the patterned layers such as the gate 35 electrodes.

As the space between these patterned layers is reduced, however, the space available for forming the holes may also be reduced. Furthermore, there may be physical limits to the reductions which can be made to the size of the holes. 40 Accordingly, the increased integration reduces the margin available in the placement of the holes. The margin available for the placement of the holes is also influenced by the process limitations of the steps for forming other adjacent patterns. For example, when a LOCOS field oxide layer is 45 improved contact hole structures and methods. formed, the bird's beak phenomenon may reduce the active region. When a trench field oxide layer is formed, the inner wall of the trench may encroach into the active region also reducing the area available to the hole and further decreasing the margin for the formation of the hole.

FIG. 1 is a cross-sectional view of an integrated circuit device having a contact hole 16. The field oxide layer 12 is formed on the semiconductor substrate 10, and the gate electrode 14 is formed on an active region defined by the field oxide layer 12. Spacers 15 are formed along the 55 sidewalls of the gate electrode 14. An insulating layer 20 is then formed on the surface of the substrate including the gate electrode 14 and the field oxide layer 12, and the contact hole 16 is formed therein to expose a portion of the active region of the substrate. The conductive layer 18 is formed on 60 the insulating layer 20 thus filling the contact hole 16. The contact hole 16 is preferably formed over the active region between the gate electrode 14 and the field oxide film 12 so that neither the gate electrode 14 nor the field oxide film 12 is exposed.

While the contact hole 16 is shown centered between the gate electrode 14 and the field oxide layer 12 in FIG. 1, it

2

may become more difficult to form the contact hole between these structures as the device integration increases. As the spaces become smaller, formation of the contact hole 16 may be limited by the physical characteristics of light and the ability to properly align the mask. Accordingly, the margin for error during the formation of the contact hole is reduced. As shown in FIGS. 2 and 3, misalignment of the contact hole photomask may cause the contact hole to expose either the gate electrode 14 or the field oxide layer 12.

As shown in FIG. 2, the misaligned contact hole 24 exposes a portion of the active region as well as a portion of the field region. This misalignment may also result in the formation of a well through the field oxide layer 12 thus exposing a portion of a field region of the substrate when etching the insulating film 20. In other words, a contact hole 24 may partially expose an active region of the substrate and a well in the field region of the substrate. Accordingly, when the contact hole 24 is filled with the conductive layer 18, the conductive layer 18 is brought into contact with the well. Leakage current may thus flow through the conductive layer 18 into the well area. The integrated circuit device may thus overload leading to a delay in the operation of the device or even a malfunction. If a capacitor is formed, the life of the capacitor may also be reduced.

In FIG. 3, a misaligned contact hole exposes a portion of the gate electrode 14. Accordingly, the conductive layer 18 filling the contact hole 25 may contact the gate electrode 14 thus short circuiting the device. The reliability of the integrated circuit device may thus be reduced.

As discussed above, margins for forming contact holes are reduced as device integration increases. For example, the extension of a gate or a field region may reduce the area available for a contact hole, thus reducing the process margins. The reduction of process margins in turn causes a reduction in the alignment margin for the photomask used to form the contact hole. Accordingly, alignment of the photomask may become more difficult. The contact holes for integrated circuit devices may thus be more difficult to form and the alignment thereof may also be more difficult.

Accordingly, there continues to exist a need in the art for improved contact hole structures and related methods.

### SUMMARY OF THE INVENTION

It is therefore an object of the present invention to provide

It is still another object of the present invention to provide increased alignment tolerances for the formation of contact

These and other objects are provided according to the present invention by structures and methods wherein an etch inhibiting layer is provided on a field isolation layer adjacent the active region of the substrate. This etch inhibiting layer allows the misalignment of the contact hole without damaging the field isolation, layer. Accordingly, the yield and reliability of integrated circuit devices formed according to the present invention can be increased at a given level of integration.

In particular, a microelectronic structure includes a substrate having active and field regions and a field isolation layer which covers the field region, and first and second patterned conductive layers. The first patterned conductive layer is on the active region of the substrate spaced apart from the field region, and the second patterned conductive layer is on the field isolation layer adjacent the active region of the substrate. The second patterned conductive layer thus acts as the etch inhibiting layer protecting the field isolation

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

# API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

# **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

# **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

# **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.