## Exhibit F

### Case 6:22-cv-00466-ADA-DTG Document 72-6 Filed 05/09/23 Page 2 of 21

### EXHIBIT F U.S. Patent No. 8,933,945

| Claim 1                                    | Exemplary Accused Product: NXP i.MX 8QuadMax Applications Processor                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A graphics processing circuit, comprising: | To the extent that the preamble is limiting, the NXP processors meet this limitation.                                                                                                                                                                                                                                                                                                                                                                                          |

|                                            | The NXP processors perform graphics processing. To illustrate:                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                            | Graphics processing is handled by two (2x) Graphics Processing Units (GP) some of the latest graphic APIs including OpenVX for computer vision. Vio managed by a dedicated video engine with decoding formats including HEV to 4K60, H.264 up to 4K30 and encoding in H.264 up to 1080p30. The chip various display interfaces that supports up to four displays. In order to feed high demanding blocks, i.MX8QM has two (2) DRAM controllers supporting LPDDR4 memory types. |

|                                            | i.MX 8QuadMax Applications Processor Reference Manual, § 1.1.1, Document No.: I 9/2021 (downloaded from nxp.com).                                                                                                                                                                                                                                                                                                                                                              |

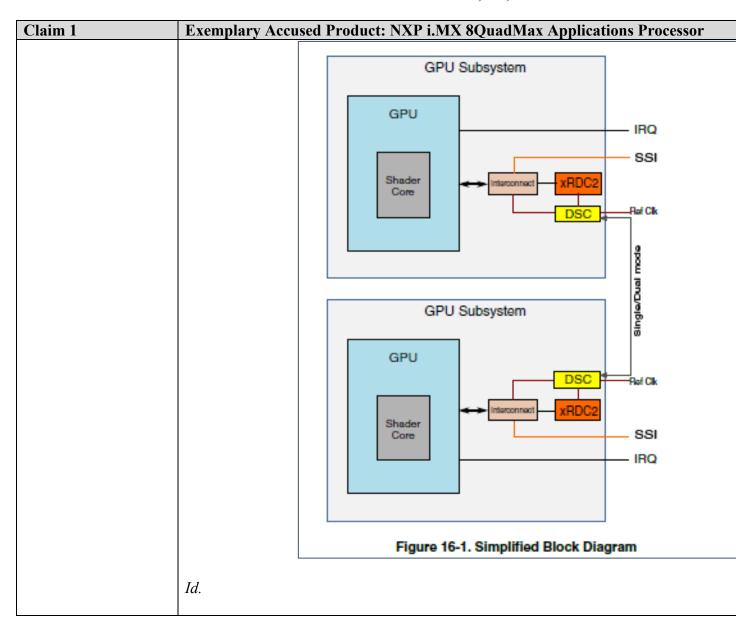

|                                            | The NXP processors include one or more Graphics Processing Unit (GPU) subsystems more GPUs. To illustrate:                                                                                                                                                                                                                                                                                                                                                                     |

|                                            | 16.1.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                            | This section provides a high-level overview of the Graphics Processing U subsystem and the Video Processing Unit (VPU) subsystem on the chip.                                                                                                                                                                                                                                                                                                                                  |

|                                            | 16.1.1.1 GPU  This chip embeds two identical GPU sub-systems.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                            | Id., § 16.1.1. To illustrate further:                                                                                                                                                                                                                                                                                                                                                                                                                                          |

### Case 6:22-cv-00466-ADA-DTG Document 72-6 Filed 05/09/23 Page 3 of 21

EXHIBIT F U.S. Patent No. 8,933,945

### Case 6:22-cv-00466-ADA-DTG Document 72-6 Filed 05/09/23 Page 4 of 21

### EXHIBIT F U.S. Patent No. 8,933,945

### Claim 1

at least two graphics pipelines on a same chip operative to process data in a corresponding set of tiles of a repeating tile pattern corresponding to screen locations,

### Exemplary Accused Product: NXP i.MX 8QuadMax Applications Processor

On information and belief, the NXP processors meet this limitation.

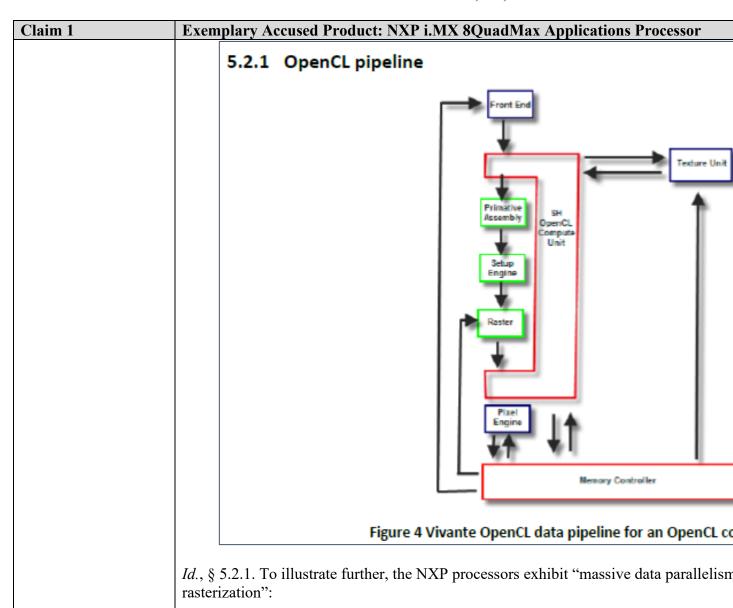

For instance, the NXP processors perform "massively parallel data processing" across engines," and "each compute unit has its own arithmetic logic units (ALUs) . . . that ca computations."

OpenCL uses parallel execution SIMD (single instruction, multiple data) engines found in GPU computational density by performing massively parallel data processing on multiple data iter compute engines. Each compute unit has its own arithmetic logic units (ALUs), including pipe (FP), integer (INT) units and a special function unit (SFU) that can perform computations as w operations. The parallel computations and associated series of operations are called a kernel can execute a kernel on thousands of work-items in parallel at any given time.

i.MX Graphic User's Guide, § 5.1.1, Document No. IMXGRAPHICUG, Rev. 0, 05/20 <a href="https://www.nxp.com/docs/en/user-guide/i.MX\_AA\_Graphics\_User's\_Guide.pdf">https://www.nxp.com/docs/en/user-guide/i.MX\_AA\_Graphics\_User's\_Guide.pdf</a>.

To illustrate further, NXP's user guides show the Vivante OpenCL data pipeline used NXP's public demonstrations of its processors depicts the use of multiple graphics pip

### Case 6:22-cv-00466-ADA-DTG Document 72-6 Filed 05/09/23 Page 5 of 21

### EXHIBIT F U.S. Patent No. 8,933,945

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

### **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

### **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

### **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.