## **EXHIBIT 11**

## Case 6:20-cv-01216-ADA Document 21-11 Fire 10 10 10 10 11 11

US006165695*A*

### **United States Patent** [19]

Yang et al.

[11] Patent Number:

6,165,695

[45] **Date of Patent:**

Dec. 26, 2000

| [54] | THIN RESIST WITH AMORPHOUS SILICON |

|------|------------------------------------|

|      | HARD MASK FOR VIA ETCH APPLICATION |

[75] Inventors: Chih Yuh Yang, San Jose; Christopher F. Lyons, Fremont; Harry J. Levinson, Saratoga; Khanh B. Nguyen, San Mateo; Fei Wang; Scott A. Bell, both

of San Jose, all of Calif.

[73] Assignee: Advanced Micro Devices, Inc.,

Sunnyvale, Calif.

| [21] | Appl. | No.: | 09/203,150 |

|------|-------|------|------------|

|------|-------|------|------------|

| [22] | Filed: | Dec. | 1. | 1998 |

|------|--------|------|----|------|

|      |        |      |    |      |

| [51] <b>Int. Cl.</b> <sup>7</sup> |  | G03C | 5/00 |

|-----------------------------------|--|------|------|

|-----------------------------------|--|------|------|

[52] **U.S. Cl.** ...... **430/314**; 430/316; 430/317; 430/967

216/39, 47, 72

### [56] References Cited

#### U.S. PATENT DOCUMENTS

| 4,299,911     11/1981     Ochi et al.     430/2       5,040,020     8/1991     Rauschenbach et al.     355       5,534,312     7/1996     Hill et al.     427/5       5,580,687     12/1996     Leedy     43       5,757,077     5/1998     Chung et al.     257/7       5,786,262     7/1998     Jang et al.     438/4       5,817,567     10/1998     Jang et al.     438/4 | 5/53<br>533<br>60/5<br>736<br>424 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                               | 424                               |

| 5,989,776 | 11/1999 | Felter et al 430/270.1 |

|-----------|---------|------------------------|

| 6,001,538 | 12/1999 | Chen et al 430/316     |

| 6.025.117 | 2/2000  | Nakano et al. 430/314  |

#### FOREIGN PATENT DOCUMENTS

62-128174 6/1987 Japan .

Primary Examiner—Mark F. Huff

Assistant Examiner—Saleha R. Mohamedulla

Attorney, Agent, or Firm—Amin, Eschweiler & Turocy,

IIP

### [57] ABSTRACT

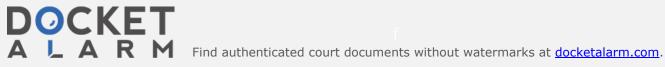

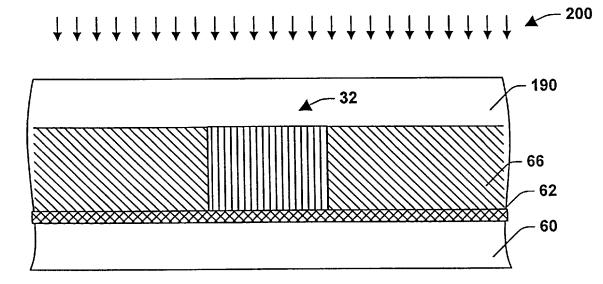

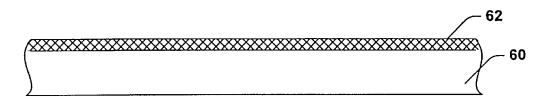

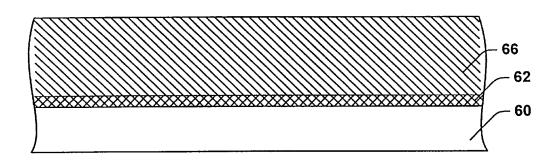

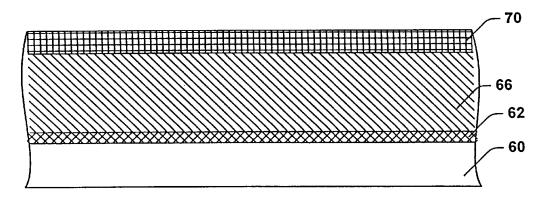

A method of forming a via structure is provided. In the method, a dielectric layer is formed on an anti-reflective coating (ARC) layer covering a first metal layer; and an amorphous silicon layer is formed on the dielectric layer. An ultra-thin photoresist layer is formed on the amorphous silicon layer, and the ultra-thin photoresist layer is patterned with short wavelength radiation to define a pattern for a via. The patterned ultra-thin photoresist layer is used as a mask during a first etch step to transfer the via pattern to the amorphous silicon layer. The first etch step includes an etch chemistry that is selective to the amorphous silicon layer over the ultra-thin photoresist layer and the dielectric layer. The amorphous silicon layer is employed as a hard mask during a second etch step to form a contact hole corresponding to the via pattern by etching portions of the dielectric layer.

### 32 Claims, 9 Drawing Sheets

U.S. Patent

Dec. 26, 2000

Sheet 1 of 9

6,165,695

U.S. Patent

Dec. 26, 2000

Sheet 2 of 9

6,165,695

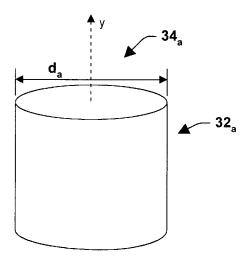

34<sub>b</sub>

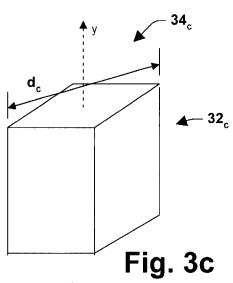

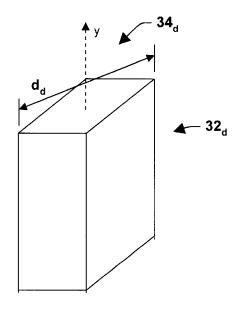

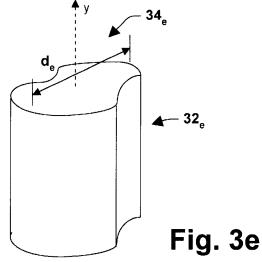

Fig. 3a

Fig. 3b

Fig. 3d

U.S. Patent

Dec. 26, 2000 Sheet 3 of 9

6,165,695

Fig. 4

Fig. 5

Fig. 6

# DOCKET

## Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

### **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.