## Exhibit 4

Volume 6, 15, 4, 2, 2, 0, 0, 8 Caase 6220 covol0008664 ADA Doormeent 19843 Filid do 81/4/2/02 Page 220688

# NANOCHIP TECHNOLOGY JOURNAL

Serving Semiconductor Manufacturers Worldwide With Enabling Process Technology

### In This Issue:

- Aerial Imaging, the Ultimate Defect Classifier

- New Cleaning Technology for Advanced Photomasks

- APC for 32nm Double Patterning

- Gridded Design Rules for Continued CMOS Scaling

## Through-Silicon Via Technology Challenges and Solutions

Find authenticated court documents without watermarks at docketalarm.com.

## NANO CHIP

Publisher: Betty Newboe Email: Betty\_X\_Newboe@amat.com

Chief Editor: Connie Duncan Email: Connie\_Duncan@amat.com

Editor: Richard Lewington Email: Richard\_Lewington@amat.com

Assistant Editor: Priya Gopalakrishnan

Advisory Board: Rudi Hendel, Ph.D., David Kyser, Ph.D., Omkaram Nalamasu, Ph.D., Reza Arghavani, Ph.D.

Nanochip Technology Journal is published by Applied Materials, Inc. in cooperation with United Business Media LLC © Copyright Applied Materials, Inc. 2008, for external use.

#### Cover Art: Elements Group

All trademarks so designated or otherwise indicated as product names or services are trademarks of Applied Materials, Inc. in the U.S. and other countries. All other product and service marks contained herein are trademarks of their respective owners.

**Front Cover:** The industry is moving to 3-D packaging using through-silicon vias. Deep Reactive Ion Etch (DRIE) is the preferred technology for this etch application.

To receive extra copies of the Nanochip Technology Journal or to add colleagues to the mailing list, please email the following information to:

technical\_public\_relations@amat.com

- Name

- Title

- Company

- Business address

www.appliedmaterials.com

DOCKE

### A Message from Ken MacWilliams

Vice President and General Manager of Applied Materials' Maydan Technology Center

One of the most exciting developments taking place in the IC industry is the work being done on through-silicon via (TSV) technology, an emerging solution for interconnecting 3-D chip stacks. This new approach promises better device performance, lower power consumption, reduced costs and the integration of heterogeneous devices. In this issue, we highlight the challenges and progress being made in TSV formation with an exclusive article featuring the viewpoints of some of Applied's leading technologists in this area.

Applied is working on several different TSV approaches at its Maydan Technology Center (MTC), where we are focusing on unit process robustness, cost-effectiveness and integration. This effort leverages Applied's broad range of process technologies and extends to several joint TSV projects with key industry partners and suppliers. Being able to use the MTC to leverage the broad range of Applied's process technologies, platforms and expertise gives us broader insight into overall manufacturability and the capability to deliver optimized and differentiated solutions.

Our research at the MTC on TSV etch processes is featured in an article that reviews both via-first and via-last applications. Since each of these have very different process requirements, the etch reactor must be flexible enough to handle both approaches. We introduce a new hardware and process scheme that provides excellent sidewall roughness without any trade-off in silicon etch rate.

Much of the other research discussed in this issue has also been conducted at the MTC, including the development of a new tantalum barrier process that addresses low k dielectric damage issues in advanced dual damascene interconnect structures and a demonstration of the use of integrated metrology to improve CD control in double patterning wafers.

Representing groundbreaking work in inspection technology, an article from our engineering team in Israel demonstrates that aerial imaging detection technology is the ultimate classifer between printing and non-printing defects, since it allows a very high detection rate without nuisance effects. This property can enable a simple migration from the 65nm node to beyond 32nm by tuning the detection limit.

In addition, we are pleased to present an article from Dr. Michael Smayling – an alum of Applied's MTC and now of Tela Innovations – on one-dimensional gridded design rules (GDR). This approach has been shown to have a number of advantages over two dimensional cells, including smaller area, better gate CD control and the elimination of hotspots. The MTC scientists have also demonstrated 22nm logic cells with Tela by leveraging the emerging Self-Aligned Double Patterning process scheme at this year's SPIE. Dr. Smayling predicts that 1-D GDR cells will enable continued simple scaling of CMOS logic to the 16nm node and beyond.

I hope that you enjoy this issue of the Nanochip Technology Journal and find the articles interesting and informative. Please feel free to contact me or the authors if you have any questions. We appreciate your comments and feedback.

Temath 1. Mail Millan

Find authenticated court documents without watermarks at docketalarm.com.

#### Caaee62200=v+0066664407A Doormeen19843 Fffed0081/40202 Pagge440688

**TECHNOLOGY JOURNAL**

E e

Volume 6, Issue 2, 2008

## **Special Focus: TSV**

- 14 Through-Silicon Via Technologies Challenges and Solutions

- **19** Deep Silicon Etch for TSV Increases Performance and Productivity

- 2 Closed-Loop CD Control for SADP Scheme Integrated metrology improves wafer-to-wafer CD control and minimizes double patterning overlay errors.

- 8 Photomask Cleaning for 45nm and Beyond Photoresist stripping without using haze-promoting sulfuric acid-based chemistries extends mask lifetime.

- 23 Virtual Metrology Improves Thermal Uniformity for Critical Anneals Innovative approach can significantly reduce wafer processing errors, enhance yield and minimize production costs.

- 28 Aerial Imaging the Optimal Classifier of Photomask Defect Printability Breakthrough inspection technique filters out nuisance non-printing defects, allowing "true" defect detection.

- 33 Gridded Design Rules 1-D Design Enables Scaling of CMOS Logic Benefits of 1-D include smaller area requirement, better gate CD control, and elimination of hotspots.

- 38 Innovative Endpoint Technology Optimizes CMP Process Control In situ film thickness monitoring optimizes manufacturing yield and device performance.

- 42 Novel Approach Extends PVD Ta Barrier Technology to 32nm and Below New process preserves delicate low k trench integrity, demonstrates excellent electrical and reliability performance.

- 46 Reducing Low k Damage with CO<sub>2</sub> Plasma Etch CO<sub>2</sub> plasma has the potential to replace O<sub>2</sub> plasma for the ashing process.

##

Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

Caase66200:0xx0006666ADDA DDoomeen19843 Fffded008/40202 Page550688

PVD

## Novel Approach Extends PVD Ta Barrier Technology to 32nm and Below

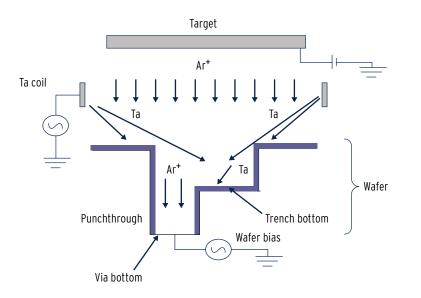

A new PVD tantalum (Ta) barrier process has been developed for 32nm and below copper/ low k dual damascene interconnect structures. The novel process preserves the delicate low k trench integrity, while demonstrating excellent stability, manufacturability, electrical and reliability performance.

#### Keywords: Ta, PVD, Barrier Process

The punch-through process involves the removal of barrier material from the via bottom during the etch/re-sputter step,

intentionally gouging into the underlying copper (Cu) line. This process has been widely used in Cu back-end-ofline (BEOL) 65nm production because it produces high performance devices with superior reliability,<sup>[1-5]</sup> especially compared to non-punch-through processes.<sup>[6]</sup> However, the conventional punch-through process can cause physical damage to porous low k dielectrics, leading to reliability implications such as roughening of the trench bottom in dual damascene structures or microtrenching in the bottom of single trenches.

Figure 1. Diagram represents the new selective re-sputtering reactor and process. Increasing

This article reports on the use of offangular Ta neutral flux during the resputter process to improve the selectivity between the via and trench bottom. This protects the trench bottom and via bevel, while still allowing sufficient gouging into the underlying Cu line. In addition, the plasma density and ion energy are adjusted to further optimize selectivity and avoid micro-trenching. The result is a high deposit/etch selectivity PVD process, validated using TEM and electrical test results. This approach has extended the PVD Ta barrier process to at least the 32nm node.

#### **Experimental Work**

The structures used in this study were etched in a low k dielectric (k≈2.7) film. The structures contained dual damascene via chains and single trench lines with an approximate 2:1 aspect ratio. The structures were deposited with a TaN/Ta bilayer initially, followed by Ar<sup>+</sup> sputtering on the bilayer and a final barrier layer deposition step. The PVD reactor used was able to achieve highionization deposition and in situ Ar<sup>+</sup> sputtering capability. The step coverage performance was evaluated using TEM cross-section images and reliability was evaluated using electrical test wafers.

#### **Results and Discussion**

Selectivity depends on the difference in

## DOCKET A L A R M

## Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

### **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time alerts** and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

### **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

### **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### LAW FIRMS

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### FINANCIAL INSTITUTIONS

Litigation and bankruptcy checks for companies and debtors.

#### E-DISCOVERY AND LEGAL VENDORS

Sync your system to PACER to automate legal marketing.