| BEFORE | THE PATENT TRIAL AND APPEAL BOA | ARD |

|--------|---------------------------------|-----|

|        | AVX CORPORATION                 |     |

|        | Petitioner                      |     |

|        | V.                              |     |

| SAM    | SUNG ELECTRO-MECHANICS CO., LTD |     |

|        | Patent Owner                    |     |

|        | Case No. PGR2017-00010          |     |

|        | Patent No. 9,326,381            |     |

|        |                                 |     |

# **TABLE OF CONTENTS**

| Section |                                                          | Page |

|---------|----------------------------------------------------------|------|

| I.      | INTRODUCTION                                             | 1    |

| II.     | <b>QUALIFICATIONS AND PRIOR TESTIMONY</b>                | 1    |

| III.    | MATERIALS CONSIDERED                                     |      |

| IV.     | BACKGROUND OF THE TECHNOLOGY                             | 5    |

| A.      | Overview                                                 | 5    |

| B.      | <u>U.S. Patent 9,326,381 ('381)</u>                      | 53   |

| C.      | <u>U.S. Patent 7,808,770 (Itamura)</u>                   | 57   |

| D.      | <u>U.S. Patent 5,134,540 (Rutt)</u>                      | 57   |

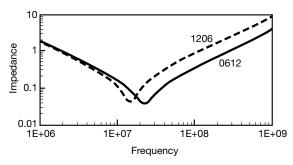

| E.      | U.S. Published Application 2012/0152604 (Ahn)            | 71   |

| V.      | PATENTABILITY OF THE CHALLENGED CLAIMS OF                | 73   |

|         | THE '381 PATENT                                          |      |

| A.      | Applicable Legal Principles                              | 73   |

| B.      | Claim Construction                                       | 76   |

| C.      | Claim 1: Itamura and Rutt                                | 91   |

| D.      | Claims 3, 4, 6 and 7: Itamura and Rutt                   | 97   |

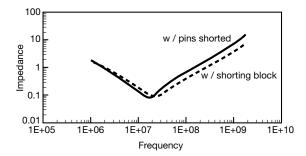

| E.      | Claim 2: Itamura, Rutt and Jeong                         | 97   |

| F.      | Claims 8, 10, 11, 13-15 and 17-19: Itamura, Rutt and Ahn | 97   |

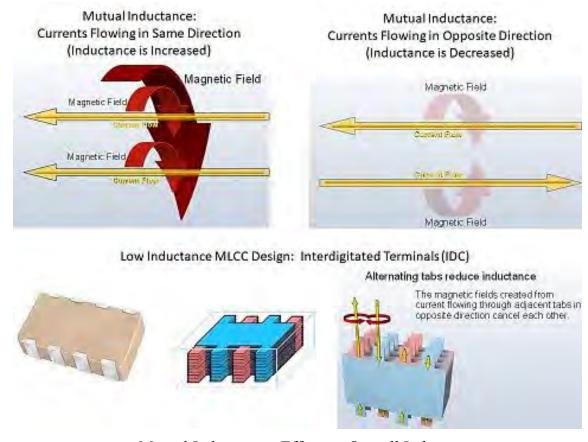

| G.      | Claim 9: Itamura, Rutt, Ahn and Jeong                    | 101  |

| Н.      | Claim 16: Itamura, Jeong, Rutt, Ahn and EIA Standard     | 101  |

| VI.     | CONCLUSION                                               | 102  |

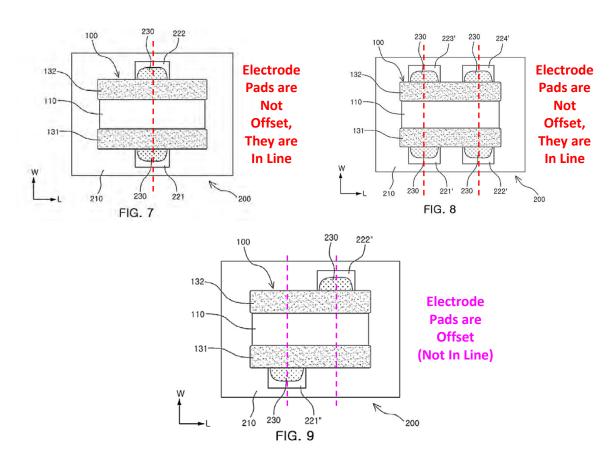

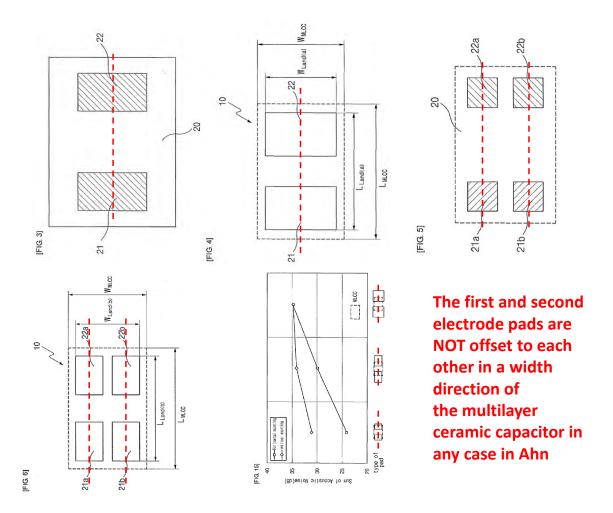

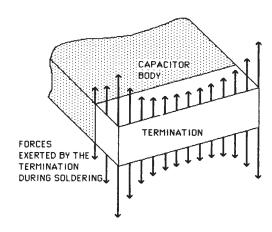

### I. INTRODUCTION

- 1. I am a consultant in electronic materials and processing, ceramic dielectric materials and processes, passive electronic components, and surface mount technology, including with respect to ceramic capacitors.

- 2. I have been retained in this matter by Samsung Electro-Mechanics Co., Ltd. ("SEM") to provide opinions regarding the instituted grounds of review of the Petition for Post-Grant Review (the "Petition") of U.S. Pat. No. 9,326,381 (Ex. 1001, the "381 patent") filed by AVX Corporation ("AVX").

- 3. I am being compensated for my work in this matter. My compensation in no way depends upon the outcome of this proceeding. I have no financial interest in SEM or the '381 patent.

- 4. I am not a patent attorney. My understanding of legal principles regarding patent validity and claim construction is based on information provided to me by SEM's counsel, which I have relied on in forming my opinions set forth in this declaration.

- 5. It is my opinion that challenged claims 1–4, 6–11, and 13–19 of the '381 patent are not rendered obvious based on the instituted grounds.

#### II. OUALIFICATIONS AND PRIOR TESTIMONY

6. A copy of my curriculum vitae is attached as Exhibit A, and it details

my qualifications and experience, as well as listing my publications and prior testimony. I have been involved in the field of Electronic Materials and Processing, Ceramic Dielectric Materials and Processes, Passive Electronic Components, and Surface Mount Technology, for more than 25 years and have experience in the design and manufacture of ceramic capacitors, as detailed in my curriculum vitae (Ex. A). I am an inventor on several patents in these areas.

- 7. I earned a Bachelor of Science degree in ceramic engineering from the NYSCC at Alfred University, Alfred NY in 1985. I earned a Master of Science degree in Materials Science and Engineering from the University of Florida, Gainesville, FL in 1987. I earned a Ph.D. in Materials Science and Engineering from the University of Florida in 1993 as well. I earned a Master of Business Administration from Webster University in 1995.

- **8.** From 1992 to 1997, I was employed by AVX Corporation. My positions at AVX Corporation included Manager of Ceramic Capacitor Research and Development, during which I was responsible for planning and oversight of multi-layered ceramic capacitor and materials development.

- **9.** From 1997 to 1999, I was employed by Ferro Corporation. My positions at Ferro Corporation included Director of Research and Development, during which I was responsible for planning, direction, and oversight of division

level research and development, and new product development, including Low Temperature Cofired Ceramic Systems and Multilayer Materials Systems.

- 10. From 1999 to 2008, I was employed by KEMET Electronics. My positions at KEMET Electronics included Director of Ceramic Technology, during which I was responsible for the direction of teams providing technology solutions for multilayer ceramic capacitor development needs. My positions at KEMET also included Director of Ceramic Technical Marketing and New Business

Development, during which I was responsible for identification and management of ceramic capacitor technical marketing, including multilayer ceramic capacitors, and associated product lines. My positions at KEMET also included Director of Advanced Ceramic Technology, during which I was responsible for new product development for advanced ceramic products, including various capacitor types, and resulting in several inventions.

- 11. Since 2003, I have been an independent consultant with Almegacy LLC in a variety of electronic device and material projects, including electronic component selection and sourcing for capacitors. I have served as an expert witness in the subject area of capacitors, including matters before the United States District Court, including the Central District of California, the Southern District of California, the Eastern District of Texas, and the Eastern District of NY. I have also served as an expert witness in the subject area of capacitors and electronic

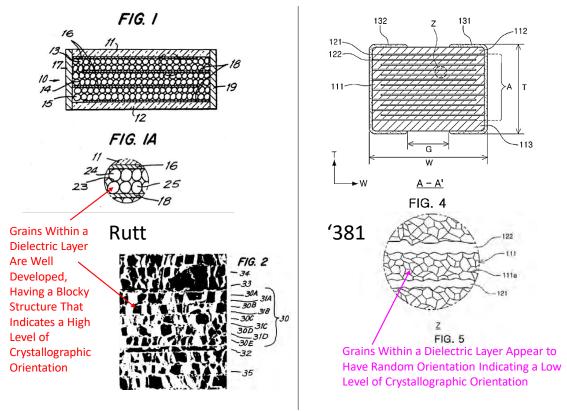

components before the International Trade Commission. And I have served as an expert witness in the subject area of capacitors for matters considered by the United States Patent and Trademark Office regarding nine different patents.

12. This report and my opinions are based upon my own qualifications and experience and my personal knowledge.

#### III. MATERIALS CONSIDERED

13. In forming my opinions, I considered the Petition and its associated exhibits (including the '381 patent (Ex. 1001), its file history (Ex. 1002), the cited prior art, and its attached declarations (see the List of Documents Reviewed, the List of Exhibits, as well as this Report)), as well as SEM's preliminary response and its exhibits (see the List of Documents Reviewed, the List of Exhibits, as well as this Report)), as well as the Patent Trial and Appeals Board ("Board")'s institution decision and any other exhibits or literature cited in this declaration or cited in the associated List of Exhibits or List of Documents Reviewed. My opinions are based upon my education, my related research and experience, as well as my investigation and the study of relevant materials. I may rely upon these materials and/or additional materials to counter arguments raised by the Petitioner. I may also consider additional information and documents, including information and documents that may not yet have been provided to me, in forming any necessary opinions.

14. My analysis of relevant materials produced is ongoing and I will

continue to review any new material as it is provided. This declaration represents

only those opinions I have formed to date. I reserve the right to revise, supplement,

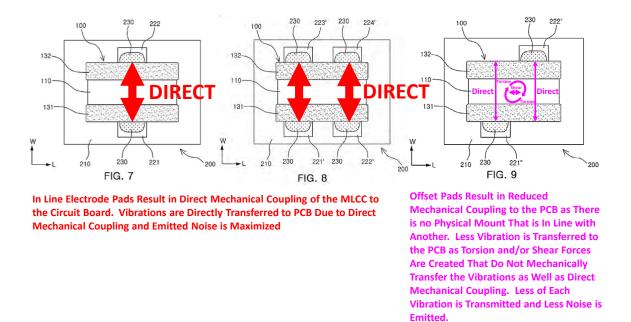

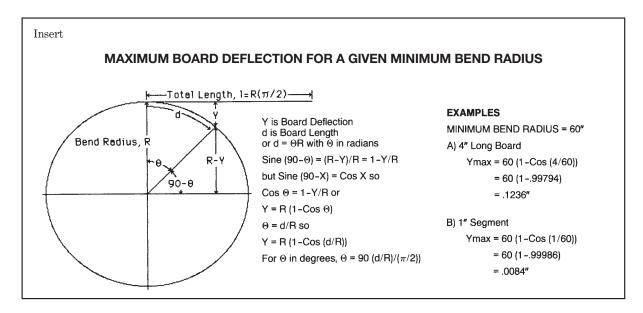

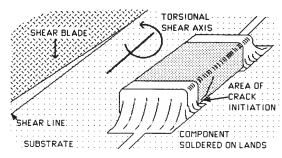

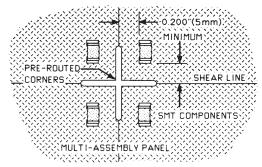

and/or amend my opinions stated herein based on new information and on my

continuing analysis of the materials already provided or on new materials provided.

IV. BACKGROUND OF THE TECHNOLOGY

A. Overview

15. I have been informed by counsel that during a post-grant review, the

Board construes claim terms according to their broadest reasonable construction in

light of the specification of the patent in which they appear. (37 C.F.R. § 42.200(b)).

Taking this into consideration, it is my opinion that the scope of background

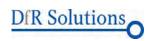

technology of the '381 patent includes certain types of multilayer ceramic capacitors.

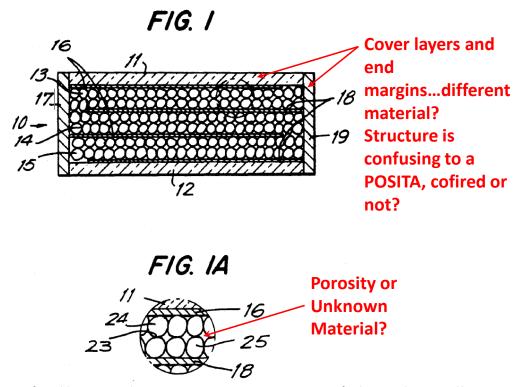

16. The '381 patent relates to a multilayer ceramic capacitor and a board

having the same mounted thereon. ('381 at 1:15-16). The '381 patent does not

mention varistors, or thermistors, such as PTCR (positive temperature coefficient of

resistance) thermistors, and those are outside the scope of the '381 patent.

Additionally, one skilled in the art would have understood that the scope of the

technology related to the '381 patent does not include all capacitors.

17. To explain, there are numerous types of capacitors. The primary major

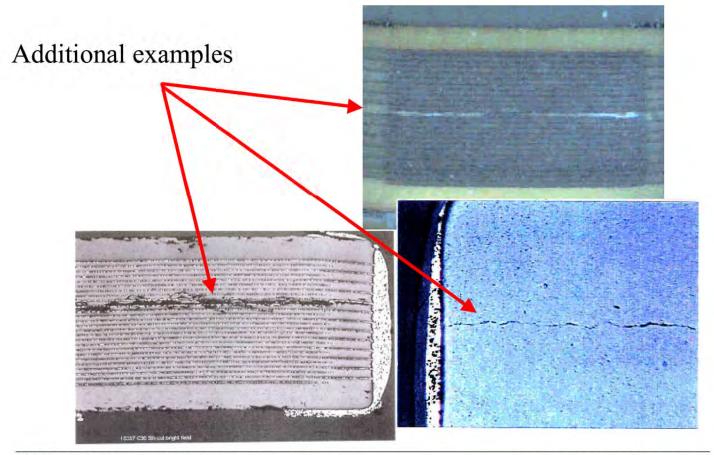

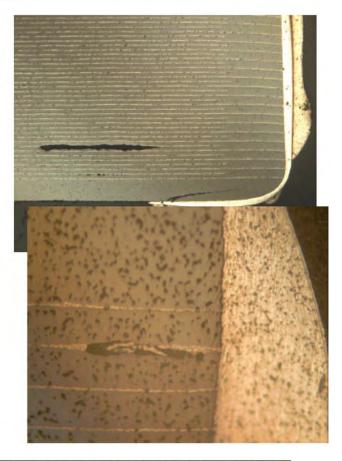

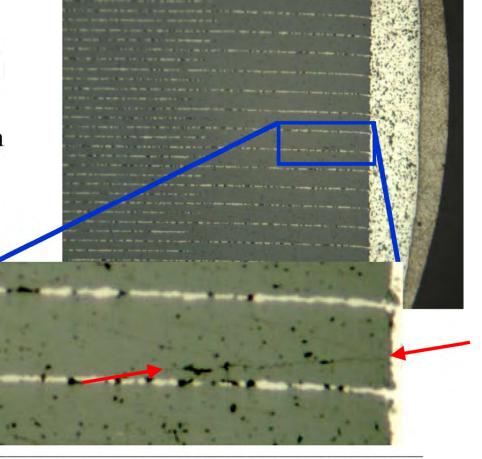

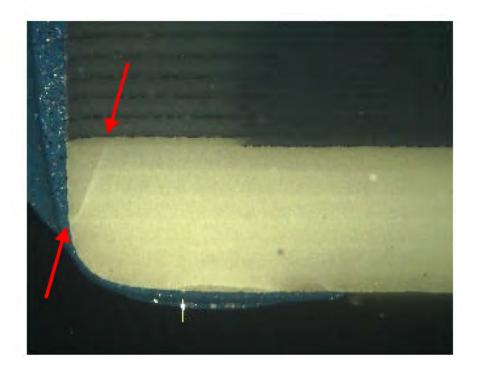

Exhibit 2008 PRG2017-00010 discriminator between capacitors is whether they are electrostatic or electrolytic.

Electrolytic capacitors utilize an electrolyte to facilitate charge transfer and are not

within the scope of the '381 patent. A person of skill in the art (POSITA) would

have understood that the '381 patent does not pertain to electrolytic capacitors. A

POSITA also would have understood that the '381 pertains only to a specific type

of electrostatic capacitors.

18. To explain, electrostatic capacitors utilize solid state conductors (e.g.,

metal electrodes) as a means to facilitate charge (e.g., electron) transfer. A POSITA

further would have understood that a subset of electrostatic capacitors is multilayer

capacitors, and that traditional single layer capacitors are also excluded from the

scope of the subject matter of the '381 patent as they have a different electrode

configuration than multilayer ceramic capacitors.

19. Additionally a POSITA would have understood that the '381 patent

does not pertain to all multilayer capacitors. For example, a POSITA would have

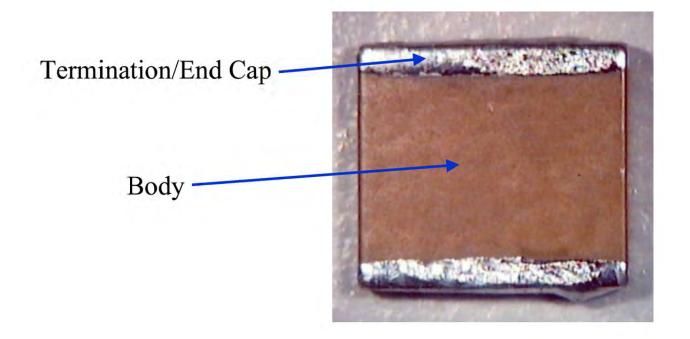

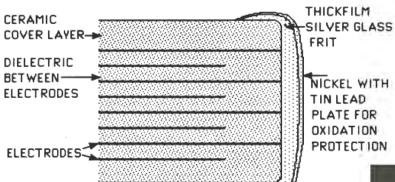

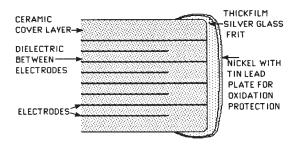

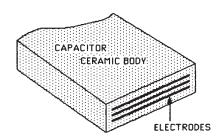

understood that multilayer capacitors that are made from non-ceramic dielectric

materials, such as organic film capacitors, and the like, are outside the scope of the

'381 patent.

20. A POSITA further would have understood that the scope of the art of

the '381 patent includes only certain ceramic dielectric materials, but not all ceramic

dielectric materials, as an objective of the '381 patent is to reduce or minimize

Exhibit 2008 PRG2017-00010 acoustic noise ('381 at 9:9-13:23). Since acoustic noise is insignificant for many types of dielectric ceramics (e.g., non-ferroelectric dielectrics, such as linear dielectrics or Class 1 dielectrics, as well as intergranular barrier layer capacitors (IBLC) materials, which utilize a ceramic material that is comprised of semiconducting grains between insulating barriers at each grain boundary), a POSITA would have understood that the scope of the subject matter of the '381 patent is limited to multilayer ceramic capacitors that are made with ceramic dielectric materials that are ferroelectric or that otherwise exhibit electrostrictive or piezoelectric characteristics or characteristics that cause displacement of the dimensions of the dielectric material when said material is placed under an electric field as discussed below. Thus, a POSITA would have understood that the '381 patent pertains not to multilayer ceramic capacitors comprised of linear ceramic dielectric materials, and not to multilayer ceramic capacitors comprised of intergranular barrier layer materials (IBLC). A POSITA would also have understood that the '381 patent pertains only to multilayer ceramic capacitors comprised of ferroelectric ceramic dielectrics, or other ceramic dielectric materials that exhibit significant mechanical displacement when said material is placed under an electric field as discussed below.

21. A POSITA also would have understood that the '381 patent pertains to "reverse geometry" multilayer ceramic capacitors (MLCC). The term "reverse

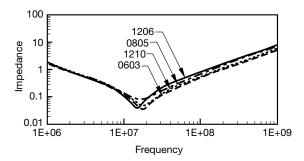

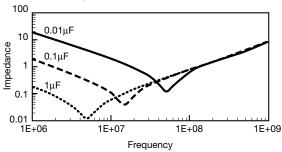

geometry" refers to a reversal in the length (L) and width (W) dimensions of the MLCC (e.g., reversal of length and width dimensions from 1206 (0.126"L x 0.63"W) to 0612 (0.063"L x 0.126"W)) as illustrated below. The reverse geometry of the MLCC device results in internal electrodes that are wider and shorter than the internal electrodes of a traditional MLCC since conductors that have increased cross sectional area, combined with shorter current path length exhibit reduced inductance or ESL. Thus, the reverse geometry configuration exhibits reduced inductance or reduced equivalent series inductance (ESL) compared to a standard MLCC of the same peripheral size. For example, the inductance of a standard MLCC has been measured to be approximately double (1250 pH) that of a reverse geometry MLCC (610 pH) when comparing traditional 1206 MLCCs to reverse geometry 0612 MLCCs.<sup>1</sup>

Standard MLCC vs. Reverse Geometry MLCC<sup>2</sup>

<sup>1</sup> Ex. B: J. Cain, "Parasitic Inductance of Multilayer Ceramic Capacitors," AVX Technical Information, p. 4/4, June 1997. <a href="https://www.avx.com/docs/techinfo/CeramicCapacitors/parasitc.pdf">https://www.avx.com/docs/techinfo/CeramicCapacitors/parasitc.pdf</a>

<sup>&</sup>lt;sup>2</sup> Source: Vishay, Capacitors-Ceramic-Surface Mount: <a href="https://www.vishay.com/capacitors/ceramic/surface-mount/">https://www.vishay.com/capacitors/ceramic/surface-mount/</a>, Source: Digi-Key Electronics, Product Index-Capacitors-Ceramic Capacitors- AVX Corporation 06125C104MAT2A: <a href="https://www.digikey.com/product-detail/en/avx-corporation/06125C104MAT2A/478-2901-1-ND/776677">https://www.digikey.com/product-detail/en/avx-corporation/06125C104MAT2A/478-2901-1-ND/776677</a>

- 22. Reduced inductance in an MLCC is generally preferable for increased frequency applications (e.g., ca. 100 KHz and above) as relatively low inductance reduces device impedance as described below. Simply put, impedance in alternating current (AC) circuits is analogous to resistance for direct current (DC) circuits. Reduced impedance in AC circuits results in less power loss in transmission (generally preferable), which aids in the performance of myriad applications such as high speed decoupling and the like. Realizing this, the inventors on the '381 patent embraced the objective of creating a low inductance MLCC device, having high capacitance density and low acoustic noise emission as explained herein. They also embraced the objective of designing the accompanying circuit board, to which said devices would be mounted, such that the benefits of low inductance and low acoustic noise emission exhibited by the MLCC device(s) are not sacrificed, but remain improved or are further improved.

- 23. The '381 patent mentions inductance or equivalent series inductance (ESL) at least 10 separate times:

- 1. "In the case of a multilayer ceramic capacitor, as equivalent series inductance (hereinafter referred to as "ESL") increases, performance of an electronic product may deteriorate." (*Id.* at 1:22-25).

- 2. "In addition, in a case in which an electronic component is miniaturized and capacitance thereof is increased, the influence of an increase in ESL on deterioration in performance of the electronic product has relatively increased." (*Id.* at 1:25-28).

- 3. "A so-called "low inductance chip capacitor (LICC)" is to decrease inductance by decreasing a distance between external terminals to shorten a current flow path." (*Id.* at 1:29-31).

- 4. "Since the distance between the first and second external electrodes **131** and **132** is shortened, the current path may be shortened, resulting in a reduction in inductance." (*Id.* at 6:1-3).

- 5. "The first and second internal electrodes **121** and **122** are alternately exposed to the first or second side surface S5 or S6, such that a reverse geometry capacitor (RGC) or low inductance chip capacitor (LICC) may be obtained as described below." (*Id.* at 5:17-21).

- 6. "In this case, when an alternative current (AC) voltage is applied to the external electrodes, a current path is relatively long, whereby an intensity of an induced magnetic field may be increased, resulting in an increase in inductance." (*Id.* at 5:25-30).

- 7. "In this case, since a distance between the first and second external electrodes **131** and **132** is relatively short, the current path may be reduced, resulting in a reduction in inductance." (*Id.* at 5:35-40).

- 8. "As described above, the multilayer ceramic capacitor, in which the first and second external electrodes **132** are formed on the first and second side surfaces **5** and **6** of the ceramic body **110**, may be a reverse geometry capacitor (RGC), or low inductance chip capacitor (LICC)." (*Id.* at 6:4-9).

- 9. "Inductance of the multilayer ceramic capacitor may be reduced by controlling the length and the width of the ceramic body to satisfy 0.5L \le W \le L." (*Id.* at 6:54-56).

- 10. "Therefore, low inductance may be implemented in the multilayer ceramic electronic component according to the exemplary embodiment of the present disclosure, whereby electric performance may be improved." (*Id.* at 6:54-56).

24. Thus, a POSITA would have understood that low inductance or ESL is a key objective of the '381 patent. Inductance (L or ESL) of a capacitor device contributes to the impedance (Z) of said device through the relation:

$$Z = \sqrt{ESR^2 + (X_L - X_C)^2}$$

where:

Z is impedance in Ohms ( $\Omega$ ) ESR is equivalent series resistance in Ohms ( $\Omega$ )  $X_L$  is inductive reactance =  $2\pi fL$  in Ohms ( $\Omega$ )  $X_C$  is capacitive reactance =  $(1/(2\pi fC))$  in ohms ( $\Omega$ ) f is frequency in Hertz (H) L is inductance in Henries (H) C is capacitance in Farad (F)

25. Additionally, the self-resonance frequency of a capacitor occurs where the capacitive and inductive reactances are equal, and is determined through the relation:

$$F_r = \frac{1}{2\pi\sqrt{LC}}$$

where:

$F_r$  is self-resonance frequency (SRF) in Hertz (Hz) L is equivalent series inductance (ESL) in Henry (H) C is capacitance in Farads (F)

26. Above the self-resonance frequency  $(F_r)$ , the inductive reactance of the capacitor device  $(2\pi fL)$  dominates the capacitive reactance, and the inductance

or ESL (equivalent series inductance) of the device, becomes the dominant factor in determining impedance (Z).

27. Low ESL (inductance) is important in applications that require low impedance (*Z*), such as decoupling, and the like, as discussed herein. In these applications low inductance results in low impedance, thus reducing "voltage droop" thereby improving signal integrity, etc., such that signals sent to each switching element in, for example, an integrated circuit (IC), are proper and are not significantly compromised by said "voltage droop," or the like. Thus switching errors are avoided as illustrated below.

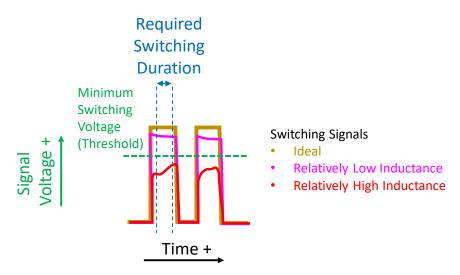

- The Signal Voltage must Exceed The Switching Threshold for The Required Duration in Order for the Switching Element to Properly to Switch

- An Ideal Signal Voltage is Shown, Resulting in No Switching Errors

- Using Low Inductance MLCC, a Good (Usable) Voltage Signal is Achieved and No Switching Errors Occur

- Using MLCC With Too High of an Inductance Results in Switching Errors as Switching Threshold and/or Duration are insufficient

Switching with Low and High Inductance MLCC for Decoupling

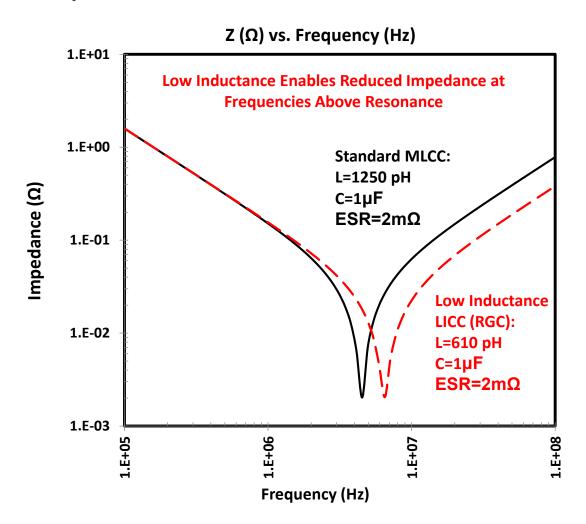

28. An impedance (*Z*) versus frequency (*f*) curve of a low inductance MLCC versus a standard MLCC is shown below in order to illustrate this effect. Therefore, achieving a low inductance MLCC device is an important objective of the '381 patent.

Impedance versus Frequency for Standard MLCC Compared to Low Inductance MLCC (LICC)

29. Further, the inventors of the '381 patent realized that it is necessary but insufficient, when pursuing low inductance circuits, that the MLCC device of interest have low inductance. Since the low ESL device is connected to the circuit in a series configuration (i.e., a first connection to a first polarity and a second connection to a second polarity, which results in at least 3 parasitic inductances as illustrated below), it is important that the connections of the MLCC device to the circuit board or printed circuit board (PCB) also have low inductance, so that the entire configuration has relatively low inductance or ESL.

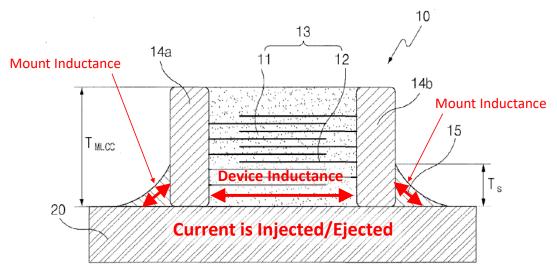

Inductances add together when device is connected in series (always for capacitor as it only works when polarity at each terminal is relatively opposite to the other terminal), in this case:

$$ESL_{Mounted} = ESL_{MLCC} + 2ESL_{MOUNT}$$

Inductance of each of the solder connections (2 or more) depends upon the relative cross-sectional area of the connection in combination with the length of the connection

- Short, wide, high (large cross sectional area) exhibit lower inductance

- Long, narrow, short (small cross-sectional area) exhibit higher inductance

Inductance of a Mounted MLCC (adapted from Ahn)

30. Additionally inductance or ESL has two components:

1. Self-inductance: the inductance of a conductor that is due to the

magnetic field that is generated due to current flowing through

the conductor itself.

2. Mutual inductance: the inductance imposed on a conductor that

is due to the magnetic field that is generated by current flowing

through a neighboring conductor.

These two inductance components combine to provide an overall inductance that a

conductor or component exhibits. Self-inductance is explained above, and is due to

the magnetic field that develops clockwise with respect to the direction of current

flow (i.e., the "Right Hand Rule"). Mutual inductance is the inductance that is

impressed upon a given conductor by the magnetic field(s) of neighboring

conductors. When the current in neighboring conductor(s) flows in the same

direction as the current in the subject conductor, the magnetic fields are also in the

same direction and combine to increase inductance as described and illustrated

herein. When the current in the neighboring conductor(s) flows in the opposite

direction of the conductor of interest, the magnetic fields run in counter directions

and the net magnetic field is reduced, thereby reducing the overall inductance of the

subject conductor.

31. Subsequently, when the current flow in a conductor of interest ceases

or reverses direction, the energy stored in said magnetic field (that is due either to

self-inductance or to the net combination of self and mutual inductances), resists said

change in current flow, which effectively slows down these current changes and results in "voltage droop" in the associated circuit. Thus, in inductive circuits, the current change lags the voltage change. This lag can result in highly undesirable events, such as erroneous switching events in active circuits, such as for example if a switching element in an integrated circuit (IC) does not switch when it is supposed to due to this "voltage droop" (i.e., due to insufficient switching voltage in the signal to the IC, as described above, or the like). These undesirable events occur, for example, when the associated capacitor has unacceptably high inductance (ESL) for the switching speed requirements of the circuit associated with said decoupling application. Thus, in these types of applications, lower inductance (ESL) is required and high inductance (ESL) is not acceptable. Realizing this, the inventors on the '381 patent embraced the objective of creating a low inductance MLCC device, having high capacitance density and low acoustic noise emission as explained herein. They also embraced the objective of designing the accompanying circuit board, to which said devices would be mounted, such that the benefits of low inductance and low acoustic noise emission exhibited by the MLCC device(s) are not sacrificed, but are further improved.

32. In a "nutshell," wide, thick, short conductors exhibit relatively low self-inductance, while narrow, thin, long conductors exhibit relatively high self-inductance. As discussed above, when two closely placed conductors conduct

electrical current in the same direction, the effect of mutual inductance of one conductor upon the other conductor is to increase the inductance of the other conductor. And when two closely placed conductors conduct electrical current in the opposite direction, the effect of mutual inductance of one conductor upon the other conductor is to decrease the inductance of the other conductor; the latter is used by designers and engineers, etc., to reduce inductance of ceramic capacitors by using interdigitated electrode design MLCCs, for example, as illustrated below.

Mutual Inductance: Effect on Overall Inductance

33 These same phenomena work with electrode pads or mounting pads and associated circuitry on circuit boards (PCBs) as well. Thus, placing mounting pads of the same polarity, that conduct current in the same direction into or out of a mounted component such as an MLCC, will increase the mutual component of inductance and thus the overall inductance of the mounted MLCC. A POSITA would have understood that use of this configuration works against the objective of achieving low overall inductance. Further, a POSITA would have understood that use of a plurality of spaced mounting pads and associated solder attach on a circuit board where said pads are much narrower, and/or said solder is thinner in height than a single, full width mounting pad for a terminal of the component will increase the self-inductance of each of the solder mounts between the PCB and the component (MLCC in this case). If this increase in inductance, as well as the increase in mutual inductance as described above, is not overcome by the parallel nature of the mounts, the overall inductance of the mounted component configuration will increase. Again this works against the objective of the '381 patent of achieving low overall inductance of the mounted component.

34. Thus, a POSITA would have understood that prior art that discloses narrower, thinner, multiple electrode pads or circuit traces per terminal mount, and/or that discloses thinner associated solder mount material height, and/or that are closely spaced and flow current in the same direction *all work against* the objectives

of the '381 patent (i.e., a low inductance MLCC device, having high capacitance density and low acoustic noise emission, and an accompanying circuit board, to which said devices mount, that minimizes any additional inductance or noise emission of the overall mounted configuration). Thus, a POSITA would have been dissuaded from using multiple, narrow mounting pads for one MLCC external electrode, as taught by United States Published Patent Application US2012/0152604 (Ahn) for example, as discussed in further detail below. And thus, a POSITA would have also been dissuaded from using relatively thin solder mount material between the mounted MLCC and the electrode mounting pad as is also taught in (Ahn) for example.

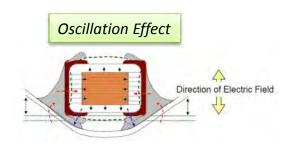

- 35. The inventors of the '381 patent also had the objective of reducing or minimizing acoustic noise emission of the subject MLCCs. To explain, certain dielectric materials physically distort when they are placed within an electric field. This phenomenon is due to the crystal chemistry of the dielectric comprising the MLCC as explained below, and is significant in ferroelectric type or similar type ceramic dielectrics that are used as the dielectric material in high capacitance density MLCCs, such as the subject MLCC devices of the '381 patent.

- 36. To explain, a major driving factor for the design of certain MLCCs (those that pertain to the '381 patent) is the amount of capacitance provided by the device, as well as the amount of capacitance exhibited by a given volume (unit

volume), called "C/V" and also known as the capacitance density of said capacitor device. A POSITA would have understood that, for these applications, it is important to maximize C/V in the subject MLCCs of the '381 patent. In an MLCC, the capacitance is determined by the relation:

$$C = \frac{n\varepsilon_0 \varepsilon' A}{t}$$

where:

*C* is capacitance in Farads (F) *n* is the number of actives within the MLCC device  $\varepsilon_0$  is the dielectric permittivity of free space (8.854 x 10<sup>-12</sup> F/m)  $\varepsilon$ ' is the dielectric constant of the material comprising the actives *t* is the thickness of each dielectric layer comprising the actives (m)

37. In order to simplify the math, the device construction of the MLCC device of interest is often simplified such the MLCC is defined to be marginless, and to have no cover layer volume, and to have no internal or external electrode volume. With these simplifications in place, the volume of the MLCC (i.e., the length x the width x the thickness) may be defined as:

$$V = LWT \propto nAt$$

where:

V is the volume of the MLCC (m) L is the length of the MLCC (m) W is the width of the MLCC (m) L is the thickness of the MLCC (L = L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x L x 38. Using the above simplification, volumetric efficiency or capacitance density is equal to the capacitance divided by the volume (C/V). And using the above simplification leads to the relation:

$$C/V \propto \frac{n\varepsilon_0 \varepsilon' A}{nAt^2} \propto \frac{\varepsilon_0 \varepsilon'}{t^2} \propto \frac{1}{t^2}$$

- 39. Thus, a POSITA would have understood that, in order to maximize capacitance density, it is important to maximize  $\varepsilon$ ' (the dielectric constant) as well as to minimize t (dielectric thickness), which not only increases C, but allows for higher n, thus leading to the effect that C/V increases proportionally to the inverse of the square of the dielectric thickness (t). For example, a POSITA would have understood that if dielectric thickness can be reduced by a factor of 10, capacitance density may be increased by as much as a factor of 100. A POSITA would have understood these factors and would understand that a major driving force in the MLCC industry is (and has been) to maximize C/V by increasing  $\varepsilon$ ' and by decreasing t, thereby enabling increased n as well.

- 40. Subsequently, considerable effort has been devoted to developing dielectric ceramic materials that exhibit increased dielectric constant ( $\varepsilon$ ') and that are capable of enabling very thin dielectric layers in MLCCs. Ferroelectric materials, typically comprised of formulations that include barium titanate (BaTiO<sub>3</sub> or BT) are, by far, the material of choice for these applications since the crystal

structure of BT enables very high values of  $\varepsilon$ '. Said formulations are optimized to provide acceptably and stable  $\varepsilon$ ' over a broad range of temperature. For example, an X5R dielectric is designated as a Class 2 dielectric (ferroelectric or similar) that exhibits a relatively high  $\varepsilon$  over the temperature range from -55C to +85C. In this example  $\varepsilon$ ' cannot deviate more than  $\pm 15\%$  from the room temperature (RT) value of  $\varepsilon$ ' over the temperature range from -55°C to +85°C and still achieve the X5R classification. Using BT, X5Rs exhibiting  $\varepsilon$  values exceeding 3,000-5,000 may be achieved. This enables an increase in C by a factor of  $\sim 30$ X to  $\sim 50$ X when compared to MLCCs made with non-ferroelectric or similar materials (e.g., Class 1 or linear dielectric materials, which typically exhibit  $\varepsilon$  values of ~100 or less). These ferroelectric or similar Class 2 dielectric materials, which exhibit very high dielectric constant values ( $\varepsilon$ ) also are formulated and engineered to enable very thin dielectric layers as discussed below. Since these materials exhibit high dielectric constant  $(\varepsilon')$ , combined with enablement of very thin dielectric thickness (t), and thus high active count (n), these ferroelectric or similar ceramic dielectric materials, are by far, the best capacitance solution for a range of applications requiring small devices of maximized C/V, which are enabled solely by this technology.

41. It is important to note that none of the ferroelectric or similar ceramic dielectric materials as described above are boundary layer-type materials. It is also important to note that, due to the commercial success of the above thin layer (t) Class

2 type ferroelectric or similar dielectric ceramic based MLCCs, there are no commercially successful MLCCs employing boundary layer-type ceramic dielectric materials. Further, due to the success of said materials, there were no commercially successful MLCCs employing boundary layer-type dielectric materials by the time of the invention of the '381 patent either.

As mentioned above, these Class 2 dielectric materials, when properly 42. formulated, engineered and processed, enable very thin dielectric thickness (i.e., to below ~1 µm). This further enables high capacitance density MLCCs as discussed above. For example, an MLCC device utilizing 1 µm thick dielectric layers could have as much as ~640 times the capacitance of an MLCC device utilizing dielectric layers that are 1 mil (25.4 µm) thick. Again, this has enabled the success of ferroelectric or similar MLCC capacitors over the past few decades relative to other types of capacitors such as IBLC dielectric MLCCs. The extent of this success, relative to certain other types of capacitors, has been so large that, for example, multilayer intergranular barrier layer capacitors (IBLCs) are not commercially viable and were not commercially available by the time of the '381 patent. Thus, a POSITA would have understood that the subject materials of the '381 patent are ferroelectric-type or similar ceramic dielectric materials that enable very thin dielectric thickness layers, not IBLC dielectrics.

43. The dramatic increase in dielectric constant ( $\varepsilon$ ') exhibited by

ferroelectric or similar type ceramic dielectric materials comes with certain compromises, however. The crystal chemistry that enables very high  $\varepsilon$ ' in these specialized formulations (i.e., a special type of perovskite exhibiting 4 different crystal structures over a relatively small temperature range, and at relatively low temperatures, and which are typically based upon BT), also exhibit significant electrostriction or piezoelectric response when placed within an electric field. If the field varies (such as in an alternating current (AC) signal or the like), the changing field, results in changing dimensions of the dielectric, which leads to vibration that is similar in frequency to said signal or a multiple thereof, and is also proportional in intensity to the amplitude of the signal or field placed across said dielectric.

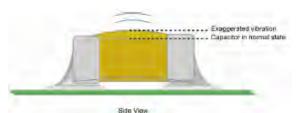

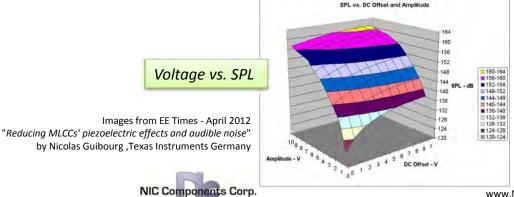

44. If the vibrations explained above are within the audible range (i.e., ~20Hz to ~20KHz), said vibrations may be heard by humans as acoustic emissions or noise. This can be disconcerting to a user of electronic devices (i.e., cellphones, tablets, laptops, computers and the like). The intensity of the acoustic noise may be measured using a sound meter or dB (Decibel) meter or the like, where a dB (Decibel) is a unit of sound intensity and is determined through the relation:

$$I(dB) = 10Log_{10} \left[ \frac{I_i}{I_0} \right]$$

where:

I is the relative sound intensity (noise) in dB  $Log_{I0}$  is the base 10 logarithm operator  $I_i$  is the intensity of the sound of interest  $I_0$  is the intensity of a reference (e.g., ambient, hearing threshold, etc.)

range are more noticeable, and thus more annoying to the device operator, and potentially to others that are in the vicinity of the emitting device. The phenomenon has been referred to as "singing capacitors"<sup>3,4,5</sup> and is generally undesirable. Certain factors, such as one or more of the value(s) of numerous piezoelectric or electrostrictive coefficient(s) as explained herein, the signal field intensity, shape and frequency, the number of "singing" devices "in concert", the type and design of

In general, higher intensities of noise that are in the audible frequency

circuit board that said devices are mounted to, and how mechanically stiff or rigid their associated mounting is to said circuit board are all important factors in

determining the relative intensity (I) of the sound emitted from the "singing

capacitors."

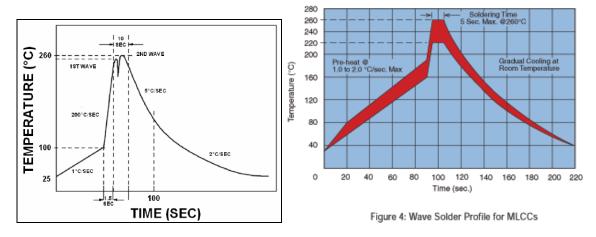

45

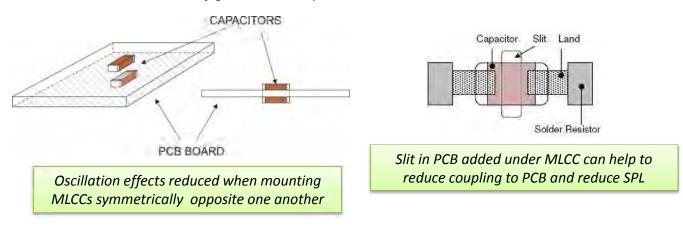

46. When multiple Class 2 (ferroelectric ceramic dielectric or the like) MLCCs are mounted stiffly to a circuit board (PCB) that is compliant and shaped appropriately for amplification (e.g., a large compliant plane), and an appropriate electric signal is applied, the acoustic noise that is emitted from the "singing

capacitors" can be unacceptably annoying. Mitigation of acoustic emission of

<sup>3</sup> Ex. C: TDK, "Frequently Asked Questions Regarding: Singing Capacitors (Piezoelectric Effect)," December, 2006. <a href="https://product.tdk.com/en/contact/faq/31\_singing\_capacitors\_piezoelectric\_effect.pdf">https://product.tdk.com/en/contact/faq/31\_singing\_capacitors\_piezoelectric\_effect.pdf</a>

%20MLC%20Noise.pdf

<sup>&</sup>lt;sup>4</sup> Ex. D: NIC Components Corporation, Piezoelectric Noise: "MLCC Ringing – Singing," REV. May 2015. http://www.niccomp.com/resource/files/ceramic/MLCC-Ringing-Singing-NSPH-SMT-FilmCapacitors-May2015.pdf

<sup>&</sup>lt;sup>5</sup> Ex. E: KEMET Electronics Corporation, "Piezeoelectric Effects Ceramic Chip Capacitors (Singing Capacitors)," Arrow Asian Times, 2006-08, J. Prymak. http://www.kemet.com/Lists/TechnicalArticles/Attachments/88/2006%2007%20ArrowAsiaTimes%20-

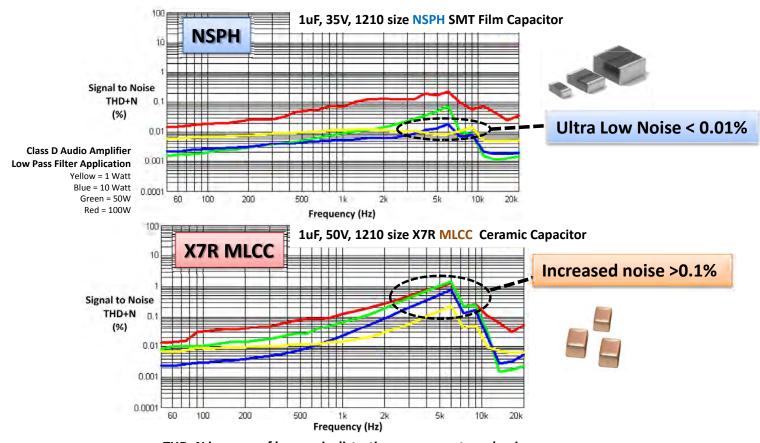

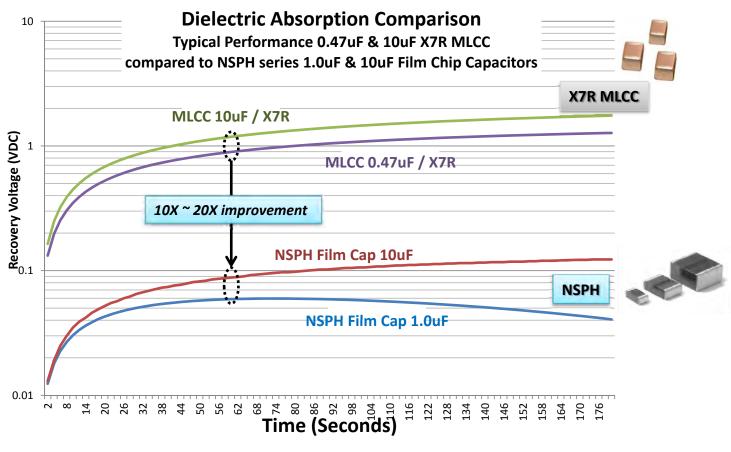

MLCCs due to these factors has received considerable attention in the industry (see e.g., Ex. C, D, E). Thus, an objective of the invention of the '381 patent is an MLCC device exhibiting low inductance (ESL) that is achieved via reverse device geometry, that also emits low acoustic noise, has a high C/V, and that is reliable. Further, the '381 patent teaches how said device should be mounted so as to further mitigate undesirable acoustic noise.

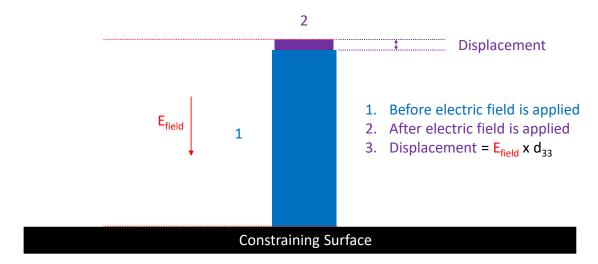

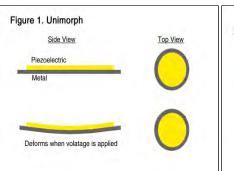

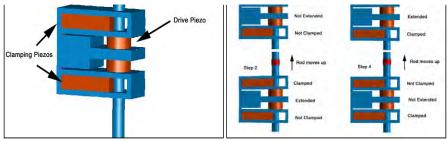

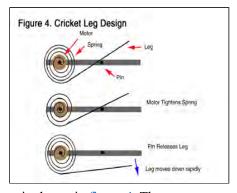

47. The intensity of the acoustic noise that a single MLCC emits depends upon one or more of numerous piezoelectric coefficient(s) or electrostrictive coefficient(s) of the ceramic dielectric material used between internal electrodes of opposite polarity. For example, with regard to piezoelectric effect, in its simplest form, the piezoelectric coefficient (d) is the amount of displacement that results from the application of a given amount of electric field across the dielectric as illustrated below. Prior to the application of electric field, a piezoelectric material (shown below in blue) has a given set of dimensions. After application of an electric field (shown in purple), the piezoelectric material increases in length and is reduced in width, for example as illustrated below. The amount of displacement in length depends upon the amount of electric field applied as well as the piezoelectric coefficient (d). The coefficient (d) generally scales with the amount of polarization per unit volume that the material of interest exhibits, as does the dielectric constant  $\varepsilon$ ' of said material, and materials that exhibit higher  $\varepsilon$ ' also tend to exhibit higher d.

- 1. Before electric field is applied

- 2. After electric field is applied

- 3. Displacement = E<sub>field</sub> x d (Piezoelectric Coefficient)

Basic, Simplified Piezoelectric Displacement

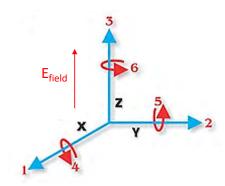

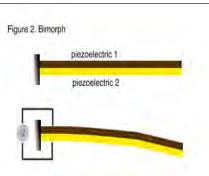

48. More realistically, because d depends upon a complex combination of crystal chemistry, crystallographic alignment, and crystal morphology (e.g., whether the material is single crystal or polycrystalline) of the material of interest, the piezoelectric coefficient has directionality and the d coefficient generally is specified in several directional displacements with respect to displacement as well as to the direction of the application of electric field. This results in a nomenclature for piezoelectric displacement that is generally in the form of d<sub>AB</sub>, where A denotes the direction of applied electric field and B denotes the direction of induced strain by said applied field per the illustration below. For example, d<sub>33</sub>, d<sub>31</sub>, and d<sub>15</sub> are defined

as illustrated below. Other piezoelectric coefficients are also defined in a directional manner, similar to those illustrated below.

## **Examples**

- d<sub>33</sub> is induced strain in direction 3 per unit electric field applied in direction 3

- d<sub>31</sub> is induced strain in direction 1 per unit electric field applied in direction 3

- **d**<sub>15</sub> is induced shear strain about direction 2 per unit electric field applied in direction 1

## Dimensionality of the Piezoelectric Effect<sup>6</sup>

49. The d<sub>33</sub> coefficient is usually the largest of the piezoelectric coefficients, and the piezoelectric effect (and thus emission of acoustic noise) is increased as d<sub>33</sub> increases. Generally, d<sub>33</sub> increases as all of the crystals within the grains of the polycrystalline ceramic dielectric align in the Z-direction (i.e.,

<sup>&</sup>lt;sup>6</sup> Adapted with: APC International, Ltd., Knowledge Center-Piezo Theory-Piezoelectric Constants: https://www.americanpiezo.com/knowledge-center/piezo-theory/piezoelectric-constants.html

orthogonal to the applied field) within the MLCC. Thus, dielectric materials having well developed, consistent grains that are aligned in a consistent direction are generally not preferred when reduction of acoustic noise is a goal, as they tend to exhibit maximized d<sub>AB</sub> (d<sub>33</sub> in this case). Thus, a POSITA would have understood that, from the standpoint of piezoelectric effect, it is generally best that the ceramic dielectric within the MLCC be polycrystalline, with little or no crystallographic orientation when reduction or minimization of acoustic noise is a goal.

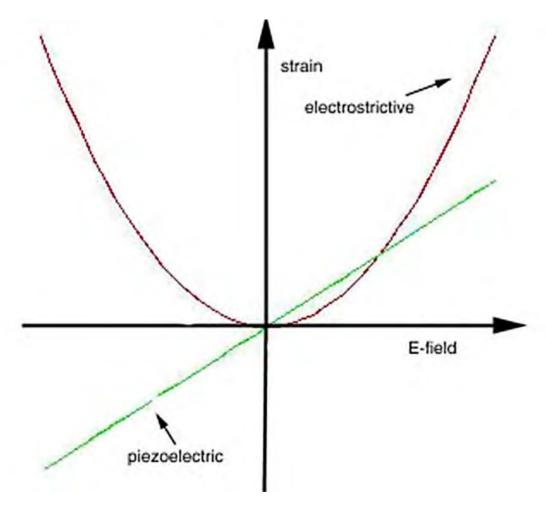

50. Electrostriction is somewhat analogous to piezoelectric effect in that application of electric field leads to displacement of the crystal structure in a manner that is somewhat similar to the description of the piezoelectric effect above. This again results in strain exhibited by the ceramic dielectric material. In the case of electrostriction, however, the displacement is proportional to the square of the applied electric field, as opposed to being directly proportional to the applied electric field as is characteristic of the piezoelectric effect. Also, electrostrictive effect is different from piezoelectric effect as the displacement (d or d<sub>AB</sub>) coefficients for electrostrictive effect tend to be somewhat smaller than the displacement (d or d<sub>AB</sub>) coefficients for the piezoelectric effect. Additionally electrostriction does not result in negative displacement, but only in positive displacement, contrary to the piezoelectric effect. Further, the displacement of electrostrictive materials occurs at twice the frequency of the applied electric signal for the electrostrictive effect, while

the piezoelectric effect occurs at the same frequency as the applied electric signal.

A generic comparison of the basic longitudinal displacement of a piezoelectric material vs. an electrostrictive material as a function of applied electric field (polarization) is illustrated below.

Comparison of Electrostrictive Effect and Piezoelectric Effect: Mechanical Strain vs. Applied Electric Field<sup>7</sup>

<sup>7</sup> Ex. F: J.C. Tucker, "Actuation for Mobile Micro-Robotics," North Carolina State University, <a href="https://www.ece.ncsu.edu/erl/microrobotics/actuation/actuation.html">https://www.ece.ncsu.edu/erl/microrobotics/actuation/actuation.html</a>

- As with the piezoelectric effect, emitted noise increases as 51. electrostriction increases, and the electrostrictive effect also tends to increase as  $\varepsilon$ ' increases. Additionally, electrostrictive displacement tends also to be largest in the "33" direction as explained above, and thus generated acoustic noise is generally greatest in the direction parallel to the applied electric field (i.e., orthogonal to the electrode plates). And as with piezoelectric dielectric ceramics, materials having well developed, consistent grains are generally not preferred when reduction of electrostrictive effect and thus acoustic noise emission is a goal. And although electrostriction is a phenomenon different from piezoelectricity, it is also generally favorable, from the standpoint of electrostriction, that the ceramic dielectric within the MLCC be polycrystalline, with little or no crystallographic orientation, when reduction or minimization of acoustic noise is a goal. Thus, as with piezoelectric effect, a POSITA would have understood that, from the standpoint of electrostrictive effect, it is generally best that the ceramic dielectric within the MLCC be polycrystalline, with little or no crystallographic orientation when reduction or minimization of acoustic noise emission is a goal.

- 52. Thus, use of ferroelectric effect or similar dielectric materials in MLCCs leads to tradeoffs. While the very high  $\varepsilon$ ' associated with the ferroelectric effect or similar materials enables very high capacitance per unit volume (C/V), and while these materials are formulated and engineered specifically for very thin (t)

dielectric layers, further enabling very high active count (n) and further enabling high C/V, these materials also exhibit significant piezoelectric or electrostrictive effect which can lead to unacceptable emission of acoustic noise in certain applications. The invention of the '381 patent is directed toward minimization of that noise emission while maintaining high C/V in a low inductance MLCC design and associated circuit board for mounting of said device(s).

electrostrictive effect are significant in electrolytic capacitors, or in general film electrostatic capacitors, or in Class 1 dielectric MLCCs, or in boundary layer devices such as intergranular barrier layer capacitors (IBLCs). Additionally, it should be noted that boundary layer-type capacitor devices, such as IBLCs, are generally only single layer type capacitors, as the benefit from these devices occurs only when the grain size of the material within the device is prohibitively large in comparison to the dielectric thickness (t) range that is relevant to high C/V MLCC as discussed herein. It is further important to note that boundary layer devices, such as IBLCs, do not rely upon the ferroelectric effect or similar mechanisms, but upon the space charge effect to create high  $\varepsilon$  and thus capacitance, so they do not exhibit significant piezoelectric or electrostrictive effect, and thus do not emit significant levels of acoustic noise and thus are not relevant to the subject matter of the '381 patent. It should also be noted that, piezoelectric and electrostrictive effects that result in

significant levels of emission of acoustic noise as described above, are generally only significant in high  $\varepsilon$ ' ceramic dielectric MLCCs that rely upon the ferroelectric effect or similar effect to produce the combination of high  $\varepsilon$ ' while enabling small t,

high n, and thus high C/V. (see e.g., Exs. C, D, E). Again, this combination is not

demonstrated by boundary layer devices as discussed herein, and thus, these devices

are not relevant to the subject matter of the '381 patent.

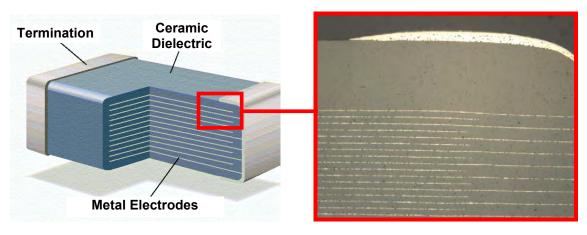

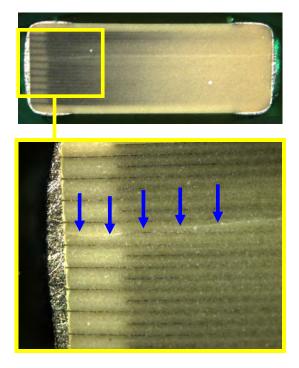

54. Other factors affecting the emission level of acoustic noise from high

C/V MLCCs are design factors, such as those with regard to cover layer thickness.

For example, MLCCs of the type described above, having thinner cover layers that

are oriented toward the circuit board during mounting exhibit lower acoustic noise

emission than those having thicker cover layers oriented toward the circuit board

during mounting. Again, this is a tradeoff as use of too thin of a cover layer may

adversely affect device reliability as disclosed in '381.

55. Additionally, the gap between device terminations may affect the level

of emission of acoustic noise from a device. Smaller gaps tend to result in lower

emitted noise. However, as the gap is reduced to relatively very small levels, the

incidence of shorts may increase, indicating another tradeoff as disclosed in '381.

56. As described above, piezoelectric and/or electrostrictive effect(s) that

result in vibration leading to emission of acoustic noise may be amplified by

mounting one or more ferroelectric effect or similar high  $\varepsilon$ ', high C/V capacitors to

Exhibit 2008 PRG2017-00010 a circuit board. The amount of amplification from mounting to the circuit board depends upon several factors, such as the number of devices mounted that experience the same signal, the location of the mounted parts with respect to the center of the circuit board, the orientation of the parts with respect to where the terminations of the device are located (i.e., on the long or short side of the MLCC device), the extent of mechanical coupling of the mounted device(s) to the circuit board (based upon the mounting conductor material and the amount or thickness of said material used, as well as upon the relative size, number and alignment of the mounting pads per mounted device). Further, the amount of acoustic noise emission may depend upon the shape and material of the circuit board to which the device(s) are mounted.

- 57. Realizing the factors discussed above and herein, the inventors of the '381 patent had the objective of creating a low inductance MLCC device, having high capacitance density (*C/V*) and with low acoustic noise emission. They also embraced the objective of designing the accompanying circuit board, to which said devices would be mounted, such that the benefits of low inductance and low acoustic noise emission exhibited by the MLCC device(s) are not sacrificed, but are held in check or even further improved upon.

- 58. Boundary layer devices that have been argued in this matter include IBLC capacitors, varistors, and positive temperature coefficient of resistance

(PTCR) thermistors. IBLCs are discussed above and are quite different from the MLCCs that are the subject matter of the '381 patent. Varistors, or variable resistors, or voltage dependent resistors, are electronic devices that are used to prevent circuit overvoltage. Varistors are typically used in a shunt configuration, connecting a voltage to ground. At normal voltages, the varistor acts as a low capacitance (*C*) value decoupling capacitor, and charges to the supply voltage of the device, providing somewhat of a voltage smoothing function. However, when a certain voltage (typically a few multiples of the design supply voltage) are experienced, the varistor begins to conduct at a much higher rate as voltage is increased (e.g., as in the case of a voltage transient or spike, or the like). This is typically known as the onset voltage or the "turn on" voltage.

59. A varistor typically conducts current as a function of voltage according to the relation:

$$I \propto KV^{\alpha}$$

where:

*I* is current in Amperes (A)

K is a constant based upon the ceramic type used for the varistor  $\alpha$  is the non-linearity coefficient (alpha value)

60. In the case of the varistor, K helps to establish the onset voltage, above which the varistor begins to conduct significantly. The  $\alpha$  (alpha) value is always greater than 1 and is a figure of merit for the varistor. The higher the value of  $\alpha$ , the

more current the varistor will conduct to ground as the supply voltage is increased, once past the onset voltage, and consequently the better the level of circuit protection.

- 61. When the varistor functions as a capacitor (i.e., below the onset voltage), the varistor acts as an intergranular boundary layer capacitor (IBLC). IBLCs are different from normal capacitors in that they utilize a dielectric that is characterized by semiconducting grains combined with insulating grain boundaries. This enables a relatively high dielectric constant ( $\varepsilon$ ') combined with low piezoelectric and electrostrictive effect, resulting in negligible acoustic noise emission. However, these are very large grained devices, with relatively large dielectric thicknesses (t), and due to economic as well as technical limitations such as limited C/V, they are not used in place of low cost, high C/V MLCCs, such as those that are the subject matter of the '381 patent. They are also not used in place of low inductance MLCCs such as those that are the subject matter of the '381 patent. They also do not exhibit appreciable piezoelectric or electrostrictive effect, and thus are not of concern with regard to acoustic noise emission as are the MLCCs of the '381 patent.

- 62. Thus, a POSITA would have understood that boundary layer devices such as varistors and IBLCs are very different from standard ferroelectric or similar mechanism dielectric based MLCCs. For example, as mentioned above and herein,

neither the varistor nor the IBLC capacitor exhibit significant piezoelectric or electrostrictive effect during operation and thus these devices do not exhibit significant emissions of acoustic noise, and thus are not relevant with respect to the '381 patent.

- 63. PTCR thermistors are also boundary layer devices. They are important in that they may be used to provide over-temperature protection to electrical devices such as electric motors and the like. They function basically as a temperature sensitive switch and are placed in series with the device to be protected. When the temperature exceeds a certain level, the resistivity (or resistance) of the PTCR thermistor device increases dramatically (orders of magnitude), thereby limiting current to the electrical device that is overheating to the extent that the device shuts off and can no longer overheat. As the device cools back down, the resistance is reduced such that the device can turn back on. Thus, a PTCR can function as a self-resetting fuse or the like.

- 64. The material that is typically utilized to make PTCR thermistors is comprised of semiconducting grains and boundary layers at each grain, similar to a varistor. In the case of a PTCR the material used is heavily doped polycrystalline barium titanate (BaTiO<sub>3</sub> or BT) and the boundary layers are Schottky barriers which are sensitive to the dielectric constant ( $\varepsilon$ ') of the semiconducting grains. Thus, this boundary layer material has the property that its resistivity begins to rise suddenly

at a certain critical temperature, which is the curie temperature of the boundary layer material. This is quite different from the insulating grains and grain boundaries that are used in high C/V MLCCs as disclosed in the '381 patent.

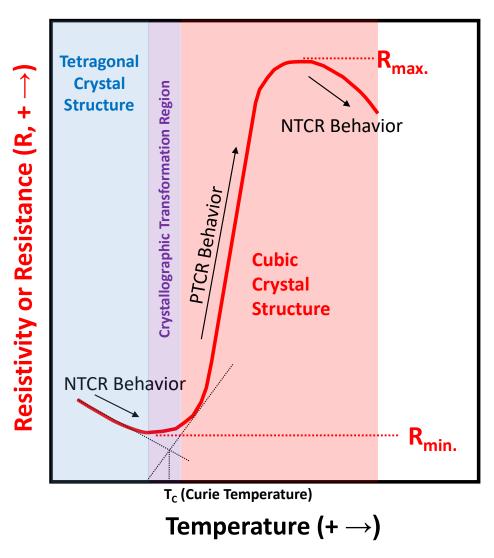

- 65. The Curie temperature ( $T_C$ ) is the temperature at which the heavily doped BT grains, having a tetragonal crystal structure below  $T_C$ , begin to transform to a cubic crystal structure. While in its low resistivity state (i.e., at temperatures below  $T_C$ ), the material comprising the device has a low resistivity (resistance). This is because the material is in its tetragonal crystal state, and the BT grains are ferroelectric, having a relatively high dielectric constant ( $\varepsilon$ '). The high dielectric constant of the BT when below  $T_C$  prevents the formation of relatively high potential barriers (Schottky barriers) between the crystal grains at the boundary layers of each of the grains. Thus, the material is in a low resistivity state below the Curie temperature ( $T_C$ ). In fact, in the region below the Curie temperature the device has a small and negative temperature coefficient (NTC) or resistivity that is typical of a semiconductor material, as illustrated below.

- 66. At and above  $T_C$ , the crystal structure of the heavily doped BT begins to change from tetragonal to cubic and the dielectric constant ( $\varepsilon$ ') drops significantly, thus resulting in the formation of a high level of potential barriers (Schottky barriers) at the boundary layers on the periphery of each grain. Subsequently, the resistivity (or resistance) increases sharply with increasing temperature (e.g., several orders of

magnitude per  $10^{\circ}$ C temperature increase) after the Curie temperature ( $T_{C}$ ) is exceeded. At temperatures that are well beyond the Curie temperature, the material reverts back to NTC-like behavior typical of a semiconductor, albeit at a higher base resistivity.

PTCR Resistance vs. Temperature<sup>8</sup>

<sup>&</sup>lt;sup>8</sup> Adapted from: Sensors and Transducers, All About It, Thermistors: <a href="https://sensorsandtransducers.wordpress.com/2012/02/07/thermistors/">https://sensorsandtransducers.wordpress.com/2012/02/07/thermistors/</a>

As is evident from the discussion above, PTCR devices are boundary layer devices that are not capacitors and thus are not relevant to the '381 patent as they are not relevant to the objective of the '381 patent (i.e., a low inductance MLCC device, having high capacitance density and low acoustic noise emission, and an accompanying circuit board, to which said devices can be mounted, that maintains or furthers the benefits of low inductance and low acoustic noise emission exhibited by said MLCC device(s)).

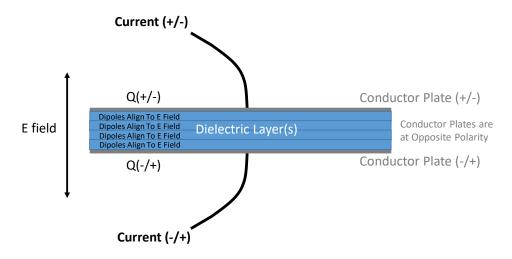

67. With regard to an electrostatic capacitor, a dielectric layer is one or more layers of dielectric material that is placed between two conductor plates that are capable of opposite polarities. The electric field that is generated between the conductor plates of opposite polarity is used to store energy in the form of charge as illustrated below. The illustration shows that the relative amount of charge that may be stored per unit of electrical potential between the conductor plates (V) increases as the capacitance of the device increases. As discussed in detail above, the capacitance increases as the dielectric constant ( $\varepsilon$ ') of the material that comprises the dielectric layer, or as the dielectric constant(s) ( $\varepsilon$ ') of the material(s) that comprise each of the multiple single dielectric layers that combine to achieve said dielectric layer between the conductor plates is/are increased.

- When conductor plates are at opposite polarity, an electric field (E field) forms

- Dipoles within the dielectric layer(s) align with the E field, binding charge to the conductor plates

- Electrical energy (E) is stored in the form of charge (Q): Q=CV, E=1/2(CV)<sup>2</sup>=1/2Q<sup>2</sup>

- Q=Stored Charge (Coulombs)

- C=Device Capacitance (Farads), increases as the number of operant dipoles per unit volume increases, increases as dielectric constant ( $\varepsilon$ ') increases

- V=Voltage (Volts)

- The stored energy is released as the E field is reversed

## Electrostatic Capacitor

- 68. As shown above, the dielectric material between the conductor plates may be comprised of more than one layer or stratum. A POSITA would have understood that multiple single dielectric layers (i.e., strata) are sometimes used between conductor plates for numerous purposes, such as to increase the dielectric breakdown voltage of the device, or to reduce the incidence of shorting between the conductive plates or the like.

- 69. In an electrostatic capacitor, the placement or deposition of multiple single dielectric layers between conductor plates is enabled using standard MLCC

fabrication technology. Said technology is usually accomplished either by way of a dry (green tape) process, or by a wet build up process. Either method enables multiple single dielectric layers (i.e., several stratum) within a dielectric layer or strata as detailed below.

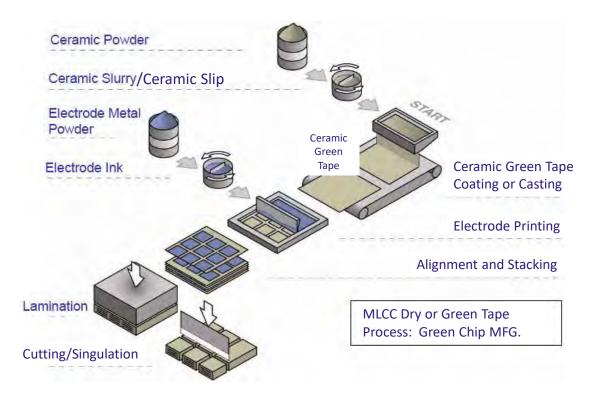

70. The green chip processing portion of the green tape process is illustrated below and involves first batching of ceramic powders, then mixing said powders with additives and dispersing the powders and additives in a liquid medium to form a suspension. The suspension of ceramic powders and additives is then milled in order to further disperse the powder particles as well as to comminute said powders to the appropriate particle size. Once a satisfactory dispersion is achieved having the appropriate particle size, the dispersion or slurry is transformed into a material called slip by adding binder and other additives to said dispersion or slurry so as to achieve the appropriate rheology, surface tension and materials properties for coating the slip onto a carrier. The slip is then further processed and then cast or coated onto a carrier, then dried to achieve green tape. In the case of thicker green tape (i.e., green tape thickness of greater than ~0.5mils or ~12.5µm), the ceramic green tape may be removed from the carrier for further processing, and is thus called free standing tape. In the case of thinner green tape (i.e., green tape thickness less than ~0.5 mils or ~12.5 µm), the ceramic green tape is coated onto a disposable carrier and stays on the carrier until removed later in the process as it is not mechanically

strong enough to be processed further without said carrier in contrast to free standing tape. After the green ceramic tape is produced, it is a thin, continuous, supple film.

Dry (Ceramic Green Tape) Green Chip MLCC Manufacturing Process<sup>9</sup>

71. Next the green tape is printed with an electrode ink in a precisely patterned and metered fashion, typically by a screen printing process. The electrode ink is comprised of metallic powder particles that are dispersed in a solvent with organic binders and other materials. The solvent is carefully selected in order to not dissolve the binder in the ceramic green tape or otherwise damage said tape. After

<sup>&</sup>lt;sup>9</sup> Adapted from: Johanson Dielectrics, Basics of Ceramic Chip Capacitors, J. Maxwell, 12/2007. http://www.johansondielectrics.com/basics-of-ceramic-chip-capacitors

printing, the electrode ink is dried.

device reliability as discussed below.

72. After the electrode ink printing process, the printed ceramic green sheets are then aligned, stacked and laminated under high pressure as well as moderately increased temperature in order to create a laminated green pad. During this process, unprinted ceramic green tape layers may be placed between printed ceramic green tape layers to achieve multiple single dielectric layers between each set of electrodes. These layers may be coated with one or more additional binder layers in order to promote adhesion, or to impede or prevent grain growth, etc., between single dielectric layers (stratum). However, this practice is typically avoided as it leads to further cost and complication of the process, and also may lead to cracking in the resulting device, leading to device failure or other compromises in

73. Also during the alignment, stacking and lamination process, multiple single layers (stratum) of ceramic green sheet are added to the top and bottom of the laminated pad in order to fabricate the top and bottom cover layers (strata). Again, these layers may be coated with one or more additional binder layers in order to promote adhesion, or to impede or prevent grain growth, etc., between single dielectric layers (stratum). Again, this practice is typically avoided as it leads to further cost and complication of the process, and also may lead to knit lines between each of the single dielectric layers that are placed between each electrode pair which

may lead to cracking, thereby compromising device reliability.

74. As a result of the lamination process, each ceramic green tape layer,

and each printed ceramic green tape layer in the "build up" is compressed in the Z-

axis or thickness direction. The amount of compression for thin dielectric layer

applications is generally ca. 25% - 45% in the thickness or Z-axis direction.

75. The resulting output of this portion of the green chip process is a pad or

bar of precisely aligned stacked and laminated green ceramic sheets (some printed,

some not printed), that is typically on the order of about 8" x 8" in size. The pad or

bar is also affixed to a carrier plate that is typically made of metal or glass.

76. The laminated pad or bar on carrier plate, is then singulated into

multilayer ceramic green chips using a precisely aligned dicing blade. The dicing

blade may be a saw blade, or a guillotine type blade or other suitable singulation

method. From the laminated pad or bar, tens of thousands of individual ceramic

green chips may be created, depending upon the size of each individual green

ceramic chip. The singulated chips are then released from the carrier plate and the

individual ceramic green chips are sent to thermal processing.

77. After green chip processing is complete, the singulated ceramic green

chips are then thermal processed. The first step of thermal processing is to "burn

out" or remove the organic materials present in each green chip. This is done at

relatively low temperatures for relatively long times.

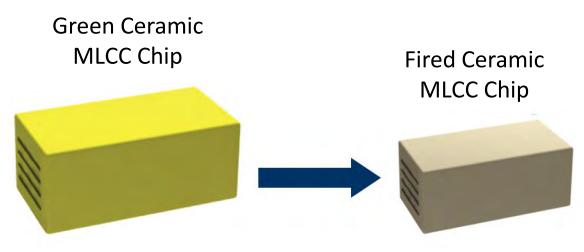

- 78. The burned out MLCC chips are then fired at higher temperature in order to sinter the particles together, thereby densifying the packed particles within each burned out chip into a dense structure, having ceramic grains of the appropriate chemistry, crystal chemistry, and size.

- 79. The effect of the firing or sintering process is to shrink the exterior dimensions of the MLCC chip as illustrated below. During this process, the metallic particles in the electrode ink also densify into a continuous, patterned conductor to form the internal electrodes of each MLCC device.

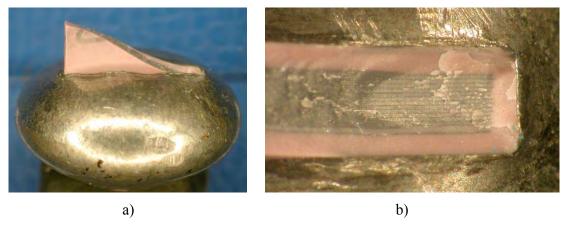

Green vs. Fired MLCC Chips

80. Additional heat treatment may be used to grow the densified ceramic grains in order to achieve preferred properties, such as increased dielectric constant  $(\varepsilon)$  and commensurate crystallographic orientation, but this is generally avoided as

it is generally preferable to keep grain size small in very thin dielectric layer MLCCs so as to enable thin (ca. 1  $\mu$ m) dielectric layers (t), which enable high active counts (t) and high tC/tV as described above and as disclosed in the '381 patent.

- 81. As mentioned above, during the firing stage of thermal processing, each green MLCC chip shrinks as the powder particles that comprise said chip sinter together. The firing stage may be separated into several sub-stages, known as the stages of sintering. During these stages, the heat from the atmosphere of the furnace imparts thermal energy to the packed particles.

- 82. In the initial stage of sintering the packed particles first react to "neck" together without densification. In the intermediate stages of sintering, densification begins as the mass transport mechanisms from the interior of each particle begin to dominate the process, so as to further reduce surface energy, transforming the green structure to a densified structure. Additionally, the pores existing within the material start to take a more circular shape and begin to close off, isolating each pore, one from another.

- 83. At the end of the final stage of sintering, the material has fully densified and pores have completely closed off and have been mostly, if not completely, removed. At this point, the sintering (densification) process is complete and the device has been reduced in dimension approximately 15%-25% in each linear dimension, compared to the green chip state (i.e., a volume % reduction of ca. 39V%

- 58V% from green MLCC to fired MLCC).

84. Combining the shrinkage of the green ceramic tape in the thickness or Z-axis direction with the shrinkage of the ceramic in all dimensions during thermal processing, the green ceramic tape shrinks ca. 35% - 60% in the thickness or Z-axis direction throughout the entire process (i.e., from green ceramic tape fabrication, through lamination and through thermal processing) during the manufacture of thin dielectric layer MLCCs such as those disclosed in the '381 patent. Thus, a POSITA would have understood that an MLCC, made with ca. 2 μm ceramic green tape, and

85. After firing, the densified MLCC chips may be subjected to a reoxidation heat treatment at significantly lower temperature than the firing temperature in order to increase the insulation resistance of the ceramic dielectric comprising the MLCC. This is typically reserved for MLCCs having base metal

having a single ceramic green tape layer (stratum) between each set of opposing

internal electrodes, would result in a final dielectric thickness (t) of ca. 1 µm.

internal electrodes (BME MLCC) as they are typically fired in a reducing

atmosphere in order to prevent oxidation of the base metal internal electrodes during

thermal processing.

86. After firing, the densified ceramic chips are corner rounded, then finished, typically by standard termination and plating processes. The termination process typically involves precisely dipping of each of the edges of the MLCC

having exposed internal electrodes, into a precisely metered thick film or termination paste.

87. The termination paste is typically comprised of a relatively large amount of metal conductor particles (such as Silver or Copper) in sphere and/or flake particulate form. The termination paste also includes a small amount of glass and/or other bonding agent, as well as other inorganic additives, as well as select organic materials; such as binder, film former, resin, solvent, and the like.

88. The MLCC chip is precisely aligned in a fixture, and is then dipped into the metered termination paste. The paste is then dried onto the chip, and the chip is realigned and the termination is deposited onto the second edge of the chip having exposed internal electrodes, in the same manner as above. The chips are then termination fired in a termination kiln, typically at temperature and time that are significantly lower than the firing temperature and time for the MLCC chips.

89. The terminated MLCCs are then finished. This is typically done by applying two conductive metal coatings; one to provide a barrier layer against dissolution by molten solder during the surface mount solder reflow and/or wave solder or similar processes, and the second layer is typically a highly solderable layer, that is also relatively unreactive to the atmosphere. The purpose of the second layer is to impart solderability to the outside surface of the termination of the finished MLCC for a relatively long duration (e.g., typically 18 months or more), thereby

imparting an acceptable shelf life to the finished MLCC.

90. Chip finishing is typically accomplished using barrel plating, medialess

plating or a combination or the like. One or more of these methods are generally

used to deposit the plated finish layers onto the fired termination in order to finish

the MLCC. As discussed above, typically (but not always) two plated layers are

used. As discussed above, the interior finish layer (typically a Nickel-based layer)

is usually used as a barrier layer that prevents molten solder from dissolving the

termination during the solder attach process that is typically used to attach the

MLCC to the circuit board or PCB. The exterior finish layer (typically Tin-based or

Lead/Tin-based) is usually used so as to be a relatively stable finish, with respect to

storage environment, that promotes and preserves solderability of the finished

MLCC part over an acceptably long period of time (e.g., ca. 18+ months shelf life).

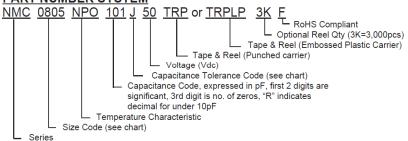

91. The finished chips are typically then inspected and tested, then

packaged, typically in tape and reel type packaging, and are then ready for shipment

to the customer.

92. The wet green ceramic chip build up process is similar to the dry

process, described above, with the exception that green tape is not utilized in the wet

process. During the wet build up process, the ceramic slip is wet deposited onto a

previously deposited and dried layer using a doctor blade, or similar method. This

method is advantageous since no carrier film is used.

93. Depending upon the design, each wet deposited, then dried ceramic green layer may then be printed with an internal electrode ink. The cover layer portions of the build are typically are not printed with electrode ink between layers, while the active portion is generally printed with internal electrode ink between each deposited and dried ceramic green layer or a multiple thereof. Each printed internal electrode ink layer is also dried prior to deposition of the next layer (ceramic green layer) upon the green "build up."

94. As with the ceramic green tape or dry process, multiple green ceramic layers (strata) may be deposited, then dried between each electrode print in order to form a multi-stratum dielectric layer.

95. However, the wet green chip build up method is disadvantaged in that it is typically not used for fired dielectric thickness (*t*) less than ca. 4 µm. This is because the incidence of shorting between internal electrodes, and poor device reliability increases when fired dielectric thickness (*t*) is less than ca. 4 µm. Thus, yield and reliability issues become prohibitive at these thicknesses and below. The reason for this is that it is not possible to pre-inspect prints or dielectric layers prior to the green chip build up process using the wet process. Therefore, defective layers are not removed from the build. Additionally, degradation of the base substrate (i.e., the previous layer of dried green ceramic and/or dried printed internal electrode ink) may occur throughout the build, resulting in fatal flaws (e.g., shorts, etc.) to the

resulting MLCCs at an unacceptably high level when thin dielectric layer designs are pursued.

96. The wet build up method is further disadvantaged in that the drying process is incorporated into the green chip build up process, thereby increasing build up time. For these reasons, the wet build up process is generally not used for manufacture of MLCCs having very thin (i.e., ca. 1  $\mu$ m) fired dielectric thickness (t) or for the manufacture of MLCCs having very high (i.e., ca. 200++) active counts (n), both of which are disclosed as key elements of the high C/V MLCCs of the '381 patent.

97. As with the dry ceramic green tape process, the wet build-up process enables the use of multiple single layers (stratum) between each set of electrode layers. To do this, multiple wet dielectric passes (i.e., deposit, then dry, then deposit, then dry...) are made between each electrode print and dry. As with the ceramic green tape process, these additional individual ceramic dielectric layers may also be coated with one or more additional binder layers in order to promote adhesion, or to impede or prevent grain growth, etc., between each single dielectric layer (stratum). However, as with the dry green tape process, this practice is typically avoided as it leads to further cost and complication of the process, and also may lead to knit lines between each of the single dielectric layers that are placed between each electrode pair, and which may become cracks, thereby compromising device reliability.

98. Further, during the wet build up process, multiple single layers (stratum) of green ceramic dielectric are also added to the top and bottom of the wet build up or pad in order to fabricate the top and bottom cover layers (strata). Again, each of these single dielectric layers (stratum) may be coated with one or more additional binder layers in order to promote adhesion, or to impede or prevent grain growth, etc., between single dielectric layers (stratum). Again, this practice is typically avoided, as it leads to further cost and complication of the process, and also may lead to knit lines between each of the single dielectric layers which may become cracks, thereby compromising device reliability.

99. Once the wet build-up pad is fabricated, the multiple green chip containing pad is then singulated into green ceramic MLCC chips, then subjected to thermal processing (i.e., burnout, firing and possibly re-oxidation), then corner rounding, termination and chip finishing, in a manner similar to that described above for ceramic dielectric MLCC chips manufactured via the dry tape process.

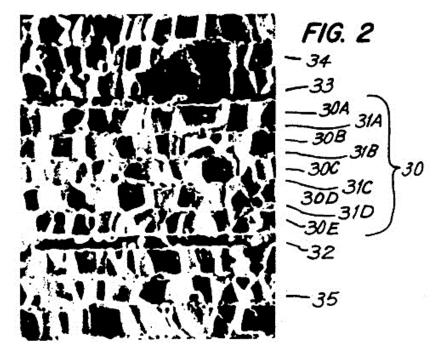

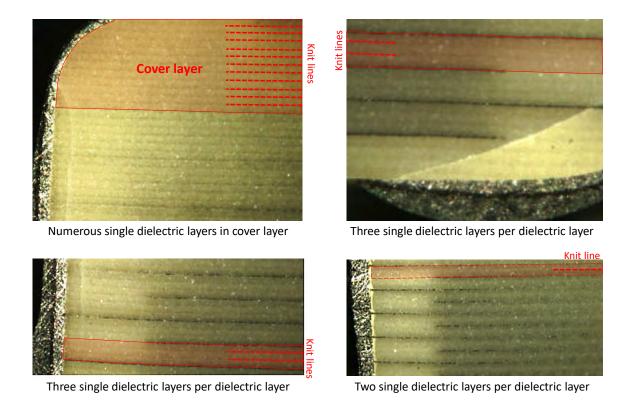

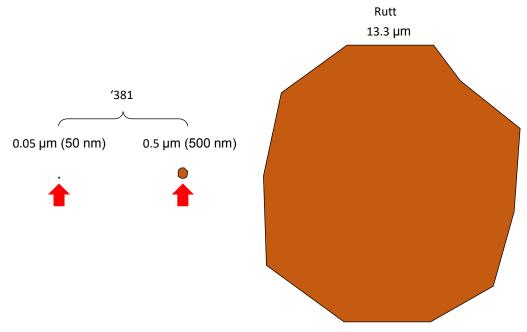

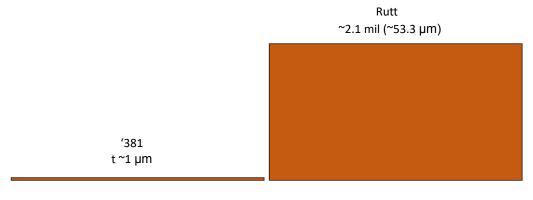

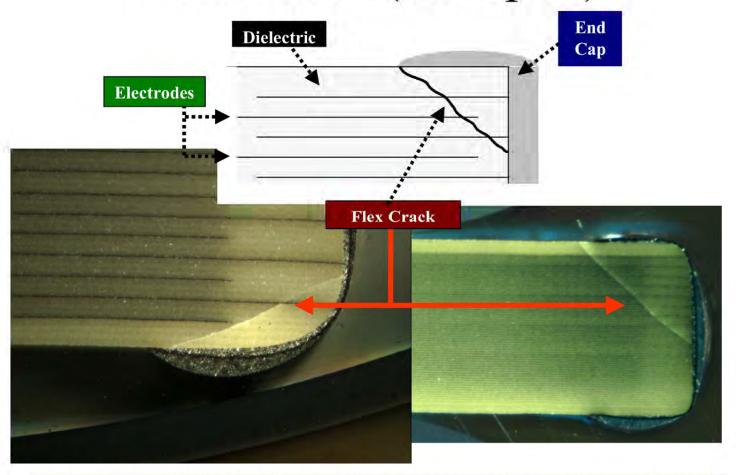

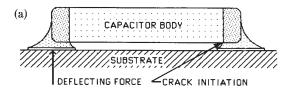

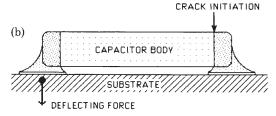

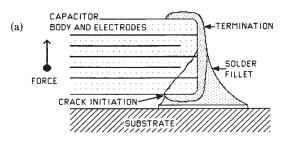

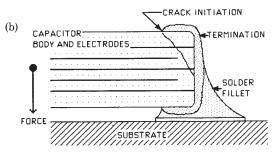

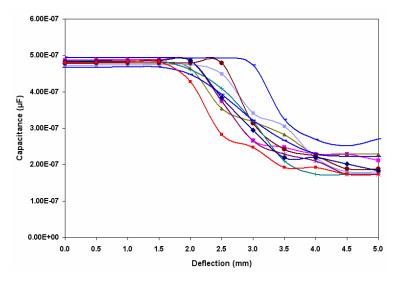

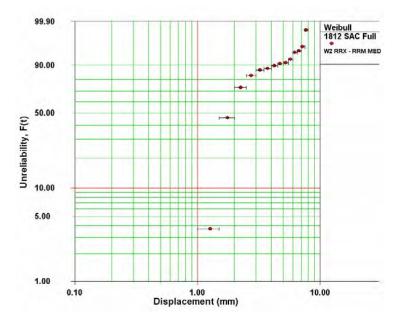

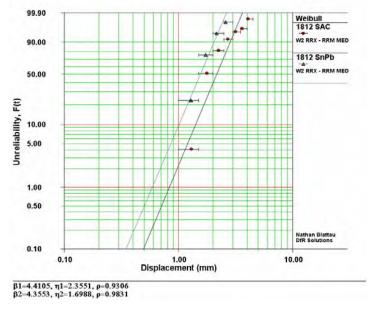

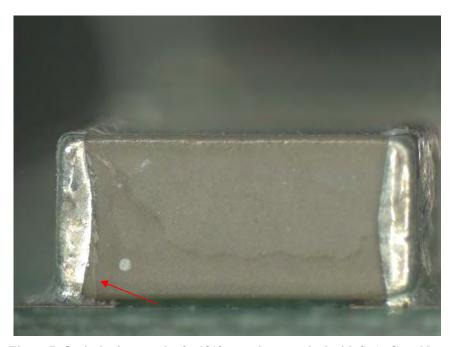

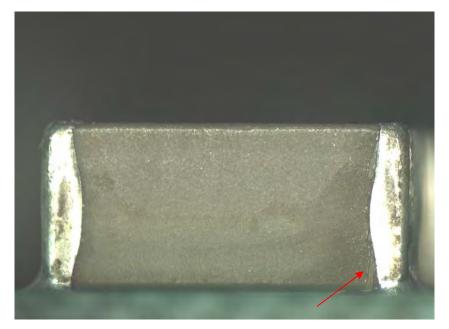

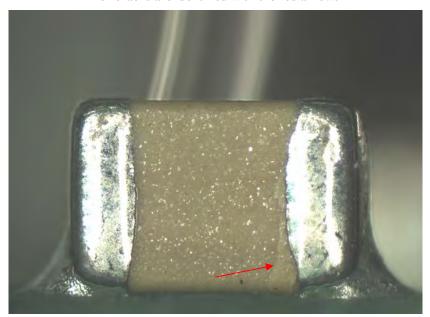

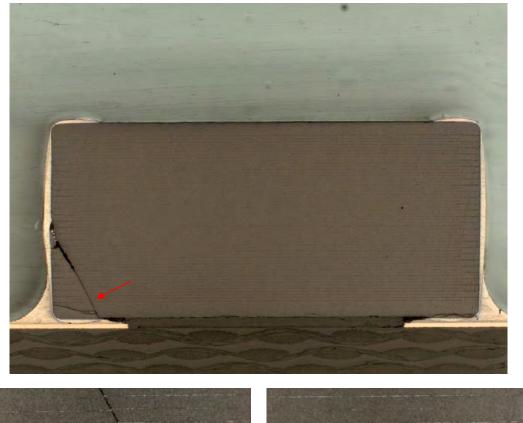

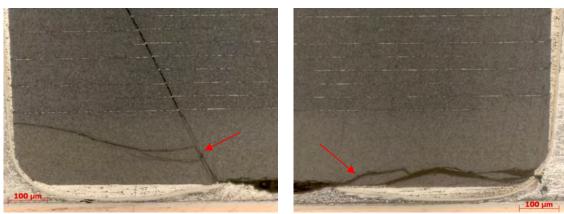

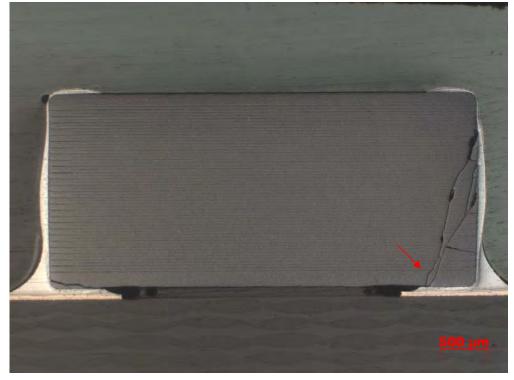

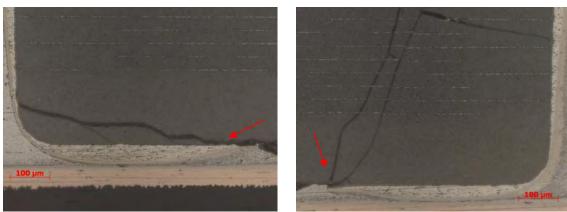

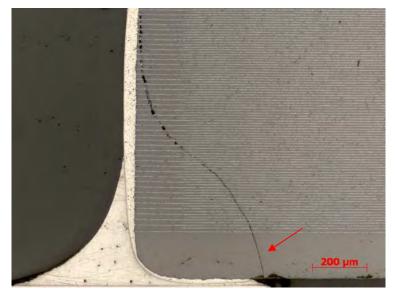

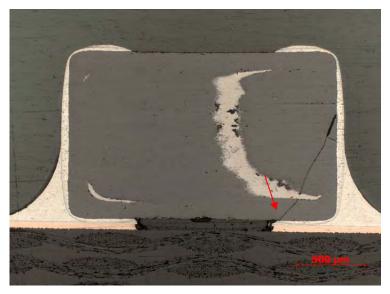

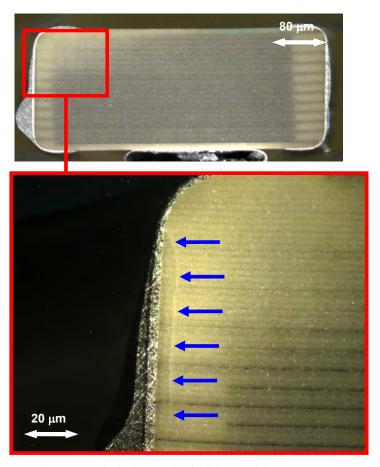

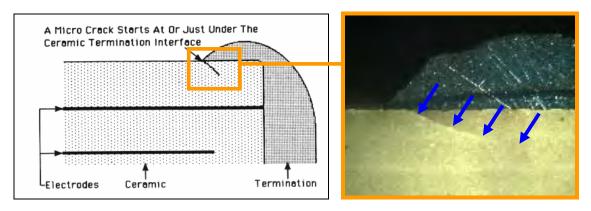

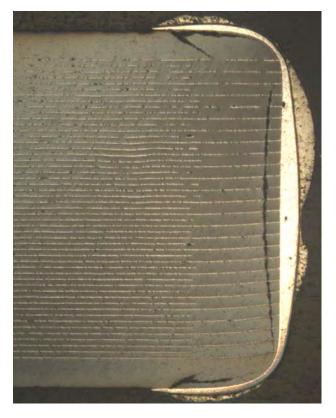

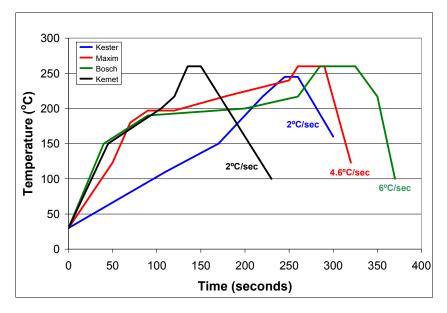

## B. U.S. Patent 9,326,381 ('381)