# (12) United States Patent

Tremblay et al.

(10) Patent No.: US 6,615,338 B1

(45) **Date of Patent:** Sep. 2, 2003

# (54) CLUSTERED ARCHITECTURE IN A VLIW PROCESSOR

(75) Inventors: Marc Tremblay, Menlo Park, CA (US); William Joy, Aspen, CO (US)

(73) Assignee: Sun Microsystems, Inc., Palo Alto, CA

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 09/204,584

(22) Filed: Dec. 3, 1998

## (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,228,497 | Α          |   | 10/1980 | Gupta et al 364/200       |

|-----------|------------|---|---------|---------------------------|

| 5,268,995 | Α          | * | 12/1993 | Diefendorff et al 395/122 |

| 5,301,340 | Α          | * | 4/1994  | Cook 395/800              |

| 5,467,476 | Α          |   | 11/1995 | Kawasaki 395/800          |

| 5,530,817 | Α          |   | 6/1996  | Masubuchi 395/375         |

| 5,542,059 | Α          |   | 7/1996  | Blomgren 395/375          |

| 5,657,291 | Α          |   | 8/1997  | Podlesny et al.           |

| 5,721,868 | Α          |   | 2/1998  | Yung et al 395/476        |

| 5,761,475 | Α          |   | 6/1998  | Yung et al 395/394        |

| 5,764,943 | Α          |   | 6/1998  | Wechsler 395/394          |

| 5,778,248 | Α          |   | 7/1998  | Leung 395/800.23          |

| 5,790,827 | Α          | * | 8/1998  | Leung                     |

| 5,901,301 | Α          | * | 5/1999  | Matsuo et al              |

| 6,076,159 | Α          | * | 6/2000  | Fleck et al 712/241       |

| 6,170,051 | <b>B</b> 1 | * | 1/2001  | Dowling 712/225           |

## FOREIGN PATENT DOCUMENTS

| EP | 0 730 223 | 9/1994 | G06F/9/38 |

|----|-----------|--------|-----------|

| EP | 0 653 703 | 5/1995 | G06F/9/38 |

#### OTHER PUBLICATIONS

Findlay et al., "HARP: A VLIW RISC Processor", IEEE, pp. 368–372, 1991.\*

Keckler et al.: "Processor Coupling: Integrating Compile Time and Runtime Scheduling for Parallelism" Proceedings of the Annual International Symposium on Computer Architecture, US, New York, IEEE, vol. Symp. 19, 1992, pp. 202–213, XP000325804, ISBN: 0–89791–510–6.

Steven et al.: "iHARP: a multiple instruction issue processor" IEE Proceedings E. Computers & Digital Techniques., vol. 139, No. 5, Sep. 1992, pp. 439–449, XP000319892, Institution of Electrical Engineers. Stevenage., GB, ISSN: 1350–2387.

Primary Examiner—Emanuel Todd Voeltz (74) Attorney, Agent, or Firm—Zagorin, O'Brien & Graham, LLP

## (57) ABSTRACT

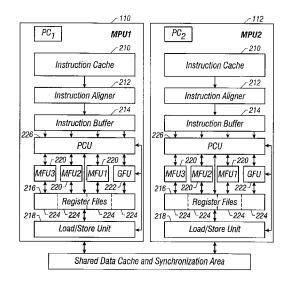

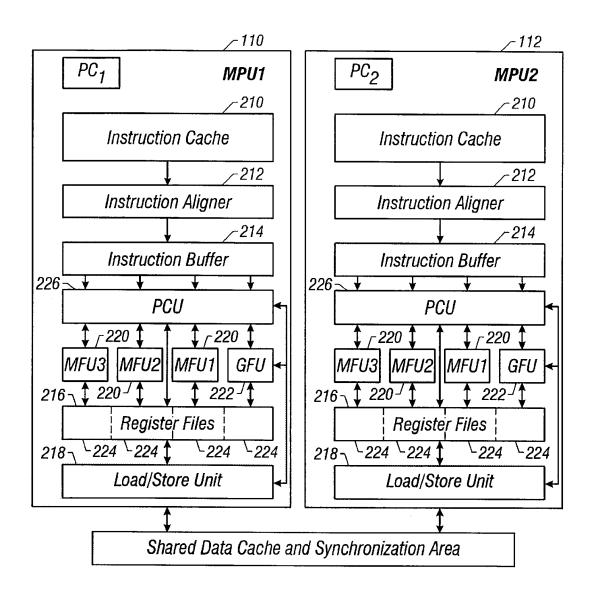

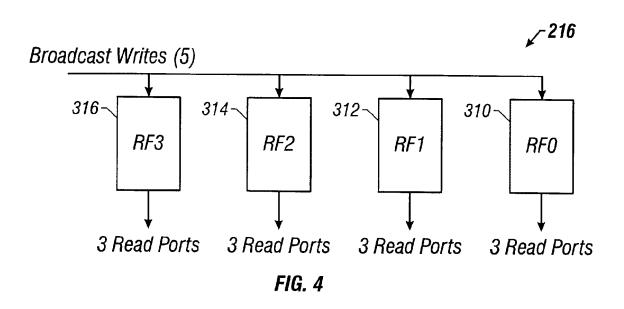

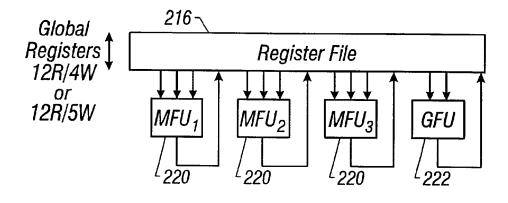

A Very Long Instruction Word (VLIW) processor has a clustered architecture including a plurality of independent functional units and a multi-ported register file that is divided into a plurality of separate register file segments, the register file segments being individually associated with the plurality of independent functional units. The functional units access the respective associated register file segments using read operations that are local to the functional unit/ register file segment pairs. In contrast, the functional units access the register file segments using write operations that are broadcast to a plurality of register file segments. Independence between clusters is attained since the separate clustered functional unit/ register file segment pairs have local (internal) bypassing that allows internal computations to proceed, but have only limited bypassing between different functional unit/ register file segment pair clusters. Thus a particular functional unit/ register segment pair does not bypass to all other functional unit/ register segment pairs.

## 25 Claims, 18 Drawing Sheets

<sup>\*</sup> cited by examiner

Sep. 2, 2003

FIG. 3

FIG. 5

# DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

## **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

## **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

# **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.