US006891397B1

# (12) United States Patent

**Brebner**

## (10) Patent No.: US 6,891,397 B1

(45) **Date of Patent:** May 10, 2005

# (54) GIGABIT ROUTER ON A SINGLE PROGRAMMABLE LOGIC DEVICE

(75) Inventor: Gordon J. Brebner, Monte Sereno, CA

(US)

(73) Assignee: Xilinx, Inc., San Jose, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 10/420,224

(22) Filed: Apr. 21, 2003

(51) Int. Cl.<sup>7</sup> ...... H03K 19/177

(56) References Cited

#### U.S. PATENT DOCUMENTS

6,275,491 B1 \* 8/2001 Prasad et al. ...................... 370/389 6,279,045 B1 \* 8/2001 Muthujumaraswathy et al. 710/

### OTHER PUBLICATIONS

http://www-cad.eecs.berkeley.edu/Respep/Research/hsc/; downloaded Apr. 18, 2003; pp. 1–6.

N. Bergmann et al.; "Reconfigurable Computing and Reactive Systems"; Proceedings of the 7th Australasian Conference on Parallel and Real–Time Systems; Springer; Nov. 29–30, 2000; pp. 171–180.

F. Braun et al.; "Reconfigurable Router Modules Using Network Protocol Wrappers"; 11th International Conference on Field Programmable Logic and Applications; Springer LNCS 2147; Aug. 27–29, 2001; pp. 254–263.

G. Brebner; "A Virtual Hardware Operating System for the Xilinx XC6200"; 6th International Workshop on Field Programmable Logic and Applications; Springer LNCS 1142; Sep. 23–25, 1996; pp. 327–336.

G. Brebner et al.; "Chip-Based Reconfigurable Task Management"; 11th International Conference on Field Programmable Logic and Applications; Springer LNCS 2147; Aug. 27–29, 2001; pp. 182–191.

- G. Brebner; "Single-Chip Gigabit Mixed-Version IP Router on Virtex-II Pro"; IEEE Symposium on FPGAs Custom Computing Machines; IEEE Computer Society Press; Apr. 22–24, 2002; pp. 35–44.

- J. Burns et al.; "A Dynamic Reconfiguration Run-Time System"; Proc. 5th Annual IEEE Symposium on FPGAs Custom Computing Machines; IEEE; Apr. 16–18, 1997; pp. 66–75.

- O. Diessel et al.; "Run-Time Compaction of FPGA Designs";7th International Workshop on Field Programmable Logic and Applications; Springer LNCS 1304; Sep. 1–3, 1997; pp. 131–140.

- H. ElGindy et al.; "Task Rearrangement on Partially Reconfigurable FPGAs with Restricted Buffer"; 10th International Workshop on Field Programmable Logic and Applications; Springer LNCS 1896; Aug. 27–28, 2000; pp. 379–388.

- H. Fallside et al.; "Internet Connected FPL"; 10th International Workshop on Field Programmable Logic and Applications; Springer LNCS 1896; Aug. 27–30, 2000; pp. 48–57.

- D. Harel; "Statecharts: A Visual Formalism for Complex Systems"; p Science of Computer Programming; 8; Jun. 1987; pp. 231–274; downloaded from: http://www.wisdom.weizmann.ac.iL/~dharel/Scanned.Papers/Statecharts.pdf.

- A. Silberschattz et al., "Applied Operating System Concepts", 1st Edition; New York; published by John Wiley & Sons; Copyright 2000; Chapter 5: Threads; pp. 116–117.

(Continued)

Primary Examiner—Anh Q. Tran (74) Attorney, Agent, or Firm—W. Eric Webostad

### (57) ABSTRACT

Apparatus for network and system on a single programmable logic device is described. The programmable logic includes port modules. The port modules have configurable logic configured to process communications for routing communications. The port modules are configured to the process communications for at least one of a plurality of protocols.

## 45 Claims, 16 Drawing Sheets

#### OTHER PUBLICATIONS

- G. Brebner; "Multithreading for Logic-Centric Systems"; 12th International Conference on Field Programmable Logic and Applications; Montepellier, France; Sep. 2–4, 2002; Springer LNCS 2438; pp. 5–14.

- R. Gilligan et al.; Internet Requests for Comments (RFC); RFC 2893 "Transition Mechanisms for IPv6 Hosts and Routers"; Aug. 2000; Accessible at http://www.rfc-editor.org/rfc.html.

- A. Conta; Internet Requests for Comments (RFC); RFC 2473 "Generic Packet Tunneling in IPv6 Specification"; Dec. 19981 Accessible at http://www.rfc-editor.org/rfc.html.

- G. Tsirtsis; Internet Requests for Comments (RFC); RFC 2766 "Network Address Translation—Protocol Translation (NAT-PT)"; Feb. 2000; Accessible at http://www.rfc-editor.org/rfc.html.

- E. Nordmark; Internet Requests for Comments (RFC); RFC 2765 "Stateless IP/ICMP Translation Algorithm (SIIT)"; Feb. 2000; Accessible at http://www.rfc-editor.org/rfc.html.

- R. Hinden et al.; Internet Requests for Comments (RFC); RFC 2374 "An Aggregatable Global Unicast Address Format"; Jul. 1998; Accessible at http://www.rfc-editor.org/rfc.html.

- G. Brebner; "Highly Reconfigurable Communication Protocol Multiplexing Element for SCOPH"; Reconfigurable Technology, Proceedings of SPIE, 4525; Aug. 21–22, 2001; pp. 99–106.

- J. Lockwood et al.; "Reprogrammable Network Packet Processing on the Field Programmable Extender (FPX)"; 9th International Symposium on Field Programmable Gate Arrays; ACM Press 2001; pp. 87–93.

- J. Ditmar et al.; "A Dynamically Reconfigurable FPGA—Based Content Addressable Memory for Internet Protocol Characterization"; Proc. 10th International Conference on Field Programmable Logic and Applications; Springer LNCS 1896; Aug. 27–30, 2000; pp. 19–28.

- S. Guccione et al.; "A Reconfigurable Content Addressable Memory"; Parallel and Distributed Processing; 15 IPDPS 2000 Workshop; Springer LNCS 1800; May 1–5, 2000; pp. 882–889.

- G. Brebner et al.; "Runtime Reconfigurable Routing"; Proc. 12th International Parallel Processing Symposium and 9th Symposium Parallel and Distributed Process; Springer LNCS 1388; Mar. 30–Apr. 3, 1998; pp. 25–30.

- D. Comer; Chapter 22 The Future IP (IPv6) of *Computer Networks and Internets*; (3rd Edition); Prentice–Hall; 2001; pp. 338–349.

- A. Dollas et al.; "Architecture and Applications of PLATO: . . ."; Proc. 9th IEEE Symposium on Field Programmable Custom Computing Machines; IEEE Press; Apr. 30–May 2, 2001; pp. [Preliminary Proceeding].

- U.S. Appl. No. 10/420,603, filed Apr. 21, 2003, inventor Brebner.

- U.S. Appl. No. 10/420,652, filed Aprl 21, 2003, inventor Brebner.

- U.S. Appl. No. 10/421,013, filed Apr. 21, 2003, inventor Brebner.

- \* cited by examiner

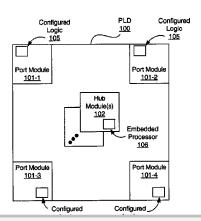

FIG. 1

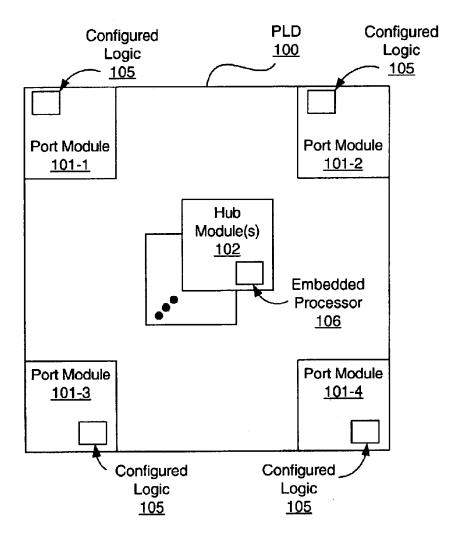

FIG. 2A

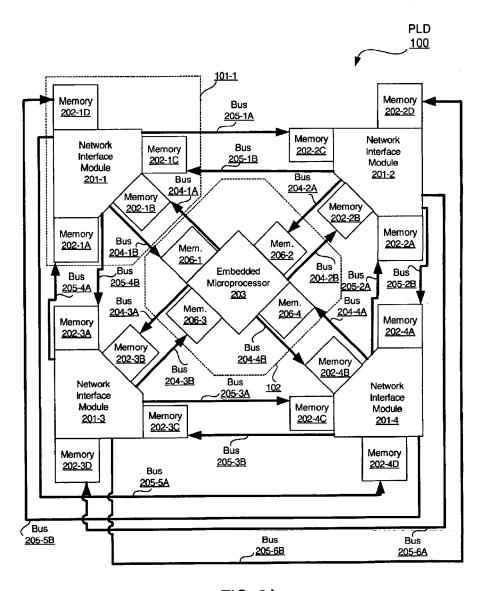

FIG. 2B

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

## **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.