RM

Δ

Α

Find authenticated court documents without watermarks at docketalarm.com.

## INTRODUCTION TO MULTICHIP MODULES

NAVEED SHERWANI Intel Corporation

QIONG YU Cadence Design Systems

SANDEEP BADIDA Advanced Micro Devices

##

Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

This text is printed on acid-free paper.

DOCKF

Α

Copyright © 1995 by John Wiley & Sons, Inc.

All rights reserved. Published simultaneously in Canada.

Reproduction or translation of any part of this work beyond that permitted by Section 107 or 108 of the 1976 United States Copyright Act without the permission of the copyright owner is unlawful. Request for permission or further information should be addressed to the Permissions Department, John Wiley & Sons, Inc., 605 Third Avenue, New York, NY 10158-0012.

Library of Congress Cataloging in Publication Data: Sherwani, N. A. (Naveed A.) Introduction to multichip modules / Naveed Sherwani, Qiong Yu, Sandeep Badida. p. cm.

Sandeep Banda, p. cm. "A Wiley-Interscience publication." Includes bibliographical references (p. ). ISBN 0-471-11438-3 (alk. paper) 1. Multichip modules (Microelectronics) I. Yu, Qiong. II. Sandeep, Badida, 1965 III. Title.

Find authenticated court documents without watermarks at docketalarm.com.

microprocessor, which is capable of over 400 MIPS. In the years to come, it is expected that the MIPS rating will give way to BIPS, that is, billions of instructions per second.

The performance of an electronic system is mainly determined by the number of instructions executed in each cycle and the clock frequency (see Fig. 1.4). As shown in Figure 1.4, the number of instructions executed per cycle depends on the system design, whereas the clock frequency depends on the IC and electronic packaging technologies. It should be further noted that, while the performance is a fundamental parameter, it is affected by the architecture and instruction set. Thus a reduced instruction set computer (RISC) system cannot be compared easily with a complex instruction set computer (CISC) system. Accordingly, performance comparisons are only valid within a given system design.

Δ

Δ

R

Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

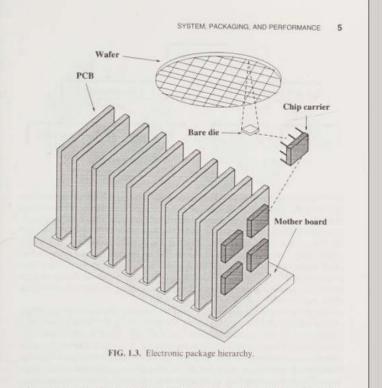

Far from being passive carriers for microelectronic devices, the packages in today's high performance computers pose at least as many engineering challenges as the semiconductor chips that they interconnect, power, cool, and protect. While the semiconductor circuit performance as measured in picoseconds continues to be improved upon relentlessly, the computer performance is expected to be in nanoseconds for the rest of this century. The factor of 1,000 is attributable to the packaging. Thus the packaging, which interconnects all the chips to form a particular function, such as a central processor, is likely to set the limits on how far computers can evolve. Multichip packaging, which minimizes these limits drastically, is expected to be the basis of all advanced computers in the future. In addition, since this technology allows chips to be placed closer and to occupy less space, it has the added advantages of being used in portable consumer electronics and medical, aerospace, automotive, and telecommunication applications.

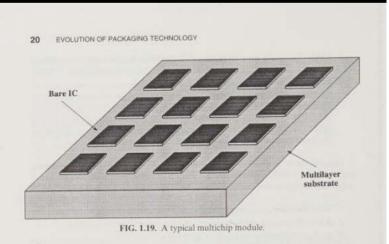

Multichip modules have been developing rapidly. As a result, different types of MCMs have been developed. In the following section, we discuss the different types of MCMs.

## 1.3.1 Substrate Technologies

MCMs are generally categorized on the basis of the substrate technology. While some MCMs are based on older PCB technology, others use state-of-the-art VLSI technology. In this section, we briefly review MCM substrate technologies

Find authenticated court documents without watermarks at docketalarm.com.