US007921323B2

# (12) United States Patent

## Yancey et al.

## (10) **Patent No.:**

US 7,921,323 B2

### (45) **Date of Patent:**

Apr. 5, 2011

#### (54) RECONFIGURABLE COMMUNICATIONS INFRASTRUCTURE FOR ASIC NETWORKS

- (75) Inventors: **Jerry W. Yancey**, Rockwall, TX (US);

- Yea Zong Kuo, Rockwall, TX (US)

- (73) Assignee: L-3 Communications Integrated

Systems, L.P., Greenville, TX (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35 U.S.C. 154(b) by 1104 days.

(21) Appl. No.: 11/600,934

(22) Filed: **Nov. 16, 2006**

(65) **Prior Publication Data**

US 2007/0101242 A1 May 3, 2007

#### Related U.S. Application Data

- (63) Continuation-in-part of application No. 10/843,226, filed on May 11, 2004, now Pat. No. 7,444,454.

- (51) **Int. Cl. G06F 13/00**

(2006.01)

- (52) U.S. Cl. ...... 714/4

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,528,658 | Α |   | 7/1985  | Israel            |

|-----------|---|---|---------|-------------------|

| 5,737,235 | Α |   | 4/1998  | Kean et al.       |

| 5,802,290 | Α | * | 9/1998  | Casselman 709/201 |

| 5,838,167 | Α |   | 11/1998 | Erickson et al.   |

| 5,931,959 | Α | * | 8/1999  | Kwiat 714/48      |

| 5,941,988 | Α |   | 8/1999  | Bhagwat et al.    |

| 5,953,372 | Α |   | 9/1999  | Virzi             |

| 6,020,755 | Α |   | 2/2000  | Andrews et al.    |

|           |   |   |         |                   |

| 6,075,380   | Α   | 6/2000  | Lane                    |  |  |  |

|-------------|-----|---------|-------------------------|--|--|--|

| 6,172,927   | B1  | 1/2001  | Taylor                  |  |  |  |

| 6,201,829   | B1  | 3/2001  | Schneider               |  |  |  |

| 6,233,704   | B1  | 5/2001  | Scott et al.            |  |  |  |

| 6,259,693   | B1  | 7/2001  | Ganmukhi et al.         |  |  |  |

| 6,292,923   | B1  | 9/2001  | Genrich et al.          |  |  |  |

| 6,333,641   | B1  | 12/2001 | Wasson                  |  |  |  |

| 6,339,819   | B1* | 1/2002  | Huppenthal et al 712/16 |  |  |  |

| 6,381,238   | B1  | 4/2002  | Hluchyj                 |  |  |  |

| 6,385,236   | B1  | 5/2002  | Chen                    |  |  |  |

| 6,389,379   | B1  | 5/2002  | Lin et al.              |  |  |  |

| 6,421,251   | B1  | 7/2002  | Lin                     |  |  |  |

| 6,496,291   | В1  | 12/2002 | Raj et al.              |  |  |  |

| (Continued) |     |         |                         |  |  |  |

#### FOREIGN PATENT DOCUMENTS

GB 2377138 A 12/2002

#### OTHER PUBLICATIONS

Search Report, PCT/US07/23700; Apr. 18, 2008; 2 pgs.

(Continued)

Primary Examiner — Stephen M Baker (74) Attorney, Agent, or Firm — O'Keefe, Egan, Peterman & Enders LLP

#### (57) ABSTRACT

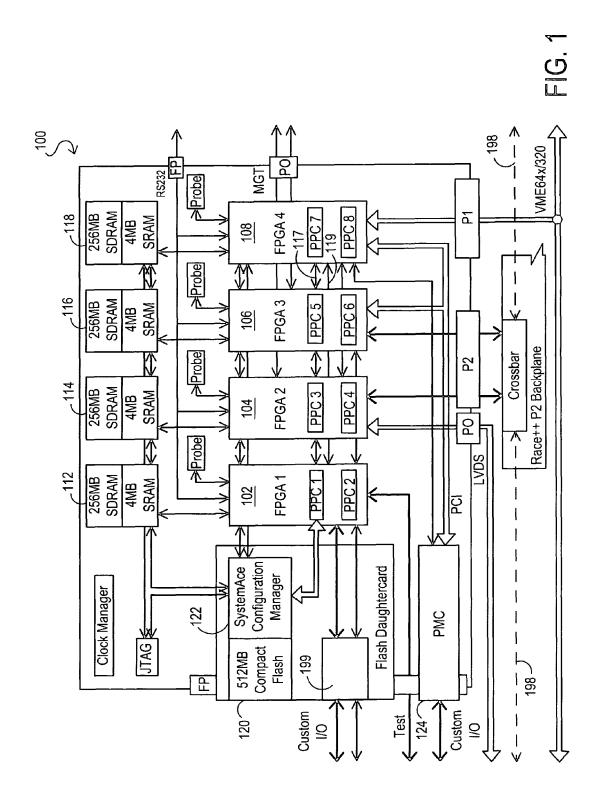

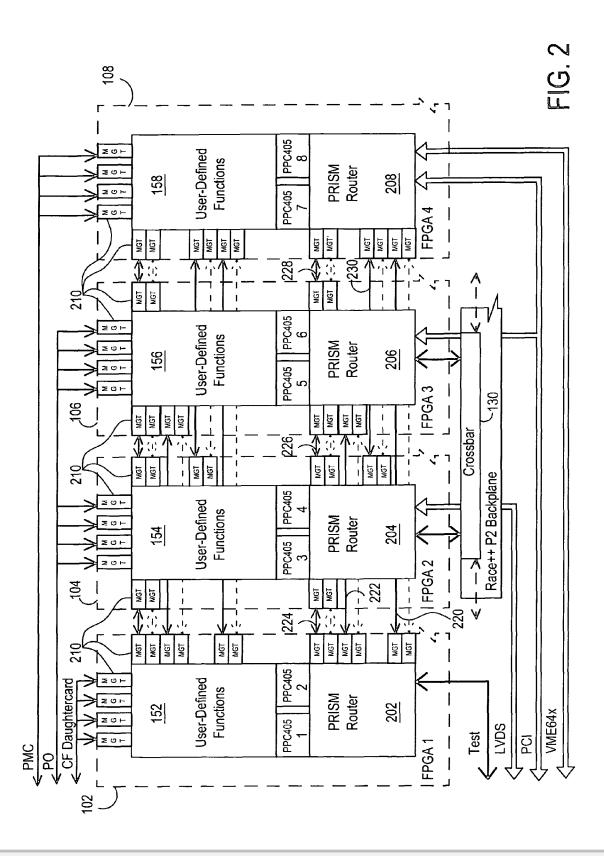

Reconfigurable communications infrastructures may be implemented to interconnect ASIC devices (e.g., FPGAs) and other computing and input/output devices using high bandwidth interconnection mediums. The computing and input/output devices may be positioned in locations that are physically segregated from each other, and/or may be provided to project a reconfigurable network across a wide area. The reconfigurable communications infrastructures may be implemented to allow such computing and input/output devices to be used in different arrangements and applications, e.g., for use in any application where a large array of ASIC devices may be usefully employed such as supercomputing, etc.

### 34 Claims, 18 Drawing Sheets

#### U.S. PATENT DOCUMENTS

| 6,496,505    | B2   | 12/2002 | La Porta et al.             |

|--------------|------|---------|-----------------------------|

| 6,614,267    | B2 * | 9/2003  | Taguchi 326/101             |

| 6,617,877    | В1   | 9/2003  | Cory et al.                 |

| 6,651,225    | B1   | 11/2003 | Lin et al.                  |

|              | B2 * | 12/2003 | Bailis et al 716/4          |

|              | B1   | 4/2004  | Van Duyne                   |

|              | B2 * | 6/2004  | Kuhlmann et al 716/16       |

| 6,873,180    | B2   | 3/2005  | Bentz                       |

| 6,888,376    | В1   | 5/2005  | Venkata et al.              |

|              | B1   | 5/2005  | Wong                        |

|              | B2   | 8/2005  | Kubota et al.               |

|              | B2   | 11/2005 | Webber                      |

|              | B1   | 1/2006  | Dammann et al.              |

|              | B2   | 2/2006  | Phong et al.                |

|              | В1   | 3/2006  | Amadon et al.               |

|              | B2   | 4/2006  | Baumer                      |

|              | В1   | 9/2006  | Pedersen                    |

| , ,          | B2   | 11/2006 | Zerbe et al.                |

|              | B1   | 3/2007  | Shafer et al.               |

| , ,          | Bī   | 5/2007  | Levi et al.                 |

| , ,          | В1   | 8/2007  | Lueckenhoff                 |

|              | B1*  | 6/2008  | Chan et al 716/17           |

| , ,          | B2 * | 7/2008  | Schott et al 716/16         |

|              | B2 * | 8/2008  | Dapp et al 701/25           |

|              | B1 * | 10/2008 | Kavipurapu et al 326/38     |

|              | B1*  | 11/2008 | Vaida et al                 |

|              | B2 * | 3/2009  | Mukherjee et al 716/18      |

|              | BI   | 4/2009  | Kondapalli et al.           |

| 2002/0021680 | Al   | 2/2002  | Chen                        |

| 2002/0057657 | Al   | 5/2002  | La Porta et al.             |

| 2002/0059274 | Al   | 5/2002  | Hartsell et al.             |

| 2002/0095400 | Al   | 7/2002  | Johnson et al.              |

| 2003/0009585 | Al   | 1/2003  | Antoine et al.              |

| 2003/0026260 | Al   | 2/2003  | Ogasawara et al.            |

| 2003/0167340 | Al   | 9/2003  | Jonsson                     |

| 2004/0085902 | Al   | 5/2004  | Miller et al.               |

| 2004/0131072 | Al   | 7/2004  | Khan et al.                 |

| 2004/0156368 | Al   | 8/2004  | Barri et al.                |

| 2004/0158784 | Al   | 8/2004  | Abuhamdeh et al.            |

| 2004/0240468 | A1   | 12/2004 | Chin et al.                 |

| 2004/0249964 | A1   | 12/2004 | Mougel                      |

| 2005/0044439 | Al   | 2/2005  | Shatas et al.               |

| 2005/0169311 | A1   | 8/2005  | Millet et al.               |

| 2005/0175018 | A1   | 8/2005  | Wong                        |

| 2005/01/3018 | Al   | 8/2005  | Vogel et al.                |

| 2005/0183042 | A1   | 11/2005 | Vadi et al.                 |

|              | A1   | 11/2005 | Vadi et al.                 |

| 2005/0248304 | A1   | 11/2005 |                             |

|              | A1   | 1/2005  | Yancey et al.<br>Yik et al. |

| 2000/0002380 | A1   | 1/2000  | TIK CLAI.                   |

#### OTHER PUBLICATIONS

Copending U.S. Appl. No. 11/600,935; entitled "Methods and Systems for Relaying Data Packets", filed Nov. 16, 2006; 101 pgs. Laxdal, "ELEC 563 Project Reconfigurable Computers", http://www.ece.uvic.ca/~elaxdal/Elec563/reconfigurable\_computers. html; printed from the Internet Dec. 19, 2003, Dec. 2, 1999, 10 pgs. "PCI/DSP-4 Four Complete Channels Of Digital Acoustic Emission Data Acquisition On A Single Board", http://www.pacndt.com/products/Multichannel/pcidsp.html, printed from the Internet Dec. 19,

Zaiq Technologies, "Innovation: Methodology Briefs", http://www.zaiqtech.com/innovation/m\_fpga.html, printed from the Internet Jan. 15, 2004, 12 pgs.

Hardt et al, "Flysig: Dataflow Oriented Delay-Insensitive Processor for Rapid Prototyping of Signal Processing", (obtained from Internet Dec. 2003), 6 pgs.

Chang et al., "Evaluation of Large Matrix Operations on a Reconfigurable Computing Platform for High Performance Scientific Computations," (obtained from Internet Dec. 2003), 10 pgs. Alfke, "FPGA Configuration Guidelines," XAPP, 090 Nov. 24, 1997, Version 1.1, pp. 31-38.

"XC18V00 Series of In-System Programmable Configuration

Thacker, "System ACE Technology: Configuration Manager Breakthrough", New Technology, FPGA Configuration, Xcell Journal, Summer 2001, pp. 52-55.

"System ACE MPM Solution", Xilinx Product Specification, DS087 (v1.0) Sep. 25, 2001, 29 pgs.

"RapidIO™: An Embedded System Component Network Architecture", Architecture and Systems Platforms, Feb. 22, 2000, 25 pgs. "Raceway Internlink Functional Specification", Mercury Computer Systems, Inc., Nov. 8, 2000, 118 pgs.

"[XMC-3310] High Speed Transceiver ePMC Module", Spectrum Signal Processing, http://www.spectrumsignal.com/Products/\_Datasheets/XMC-3310\_datasheet.asp, (© 2002-2004), 5 pgs. (this reference describes a product available prior to the May 11, 2004 filing date of the present application).

"XMC-3310 High Speed Transceiver ePMC Module", Spectrum Signal Processing, Rev. May 2004, 4 pgs. (this reference describes a product available prior to the May 11, 2004 filing date of the present application).

RocketIO<sup>TM</sup> Transceiver User Guide, Xilinx, UG024 (v2.3) Feb. 24, 2004, 152 pgs.

"The FPGA Systems Connectivity Tool", Product Brief, Nallatech, DIMEtalk 2.1, Feb. 2004, pp. 1-8.

B. Hall, "BTeV Front End Readout & Links", BTEV Co., Aug. 17, 2000, 11 pgs.

Irwin, "Usage Models for Multi-Gigabit Serial Transceivers", Xilinx, xilinix.com, White Paper, WP157 (v1.0), Mar. 15, 2002, 10 pgs.

Campenhout, "Computing Structures and Optical Interconnect: Friends or Foes?", Department of Electronics and Information Systems, Ghent University, Obtained from Internet Oct. 8, 2006, 11 pgs. E. Hazen, "HCAL HO Trigger Link", Optical SLB-HTR Interface Specification, May 24, 2006, 4 pgs.

G. Russell, "Analysis and Modelling of Optically Interconnected Computing Systems", School of Engineering and Physical Sciences, Heriot-Watt University, May 2004, 170 pgs.

Copending U.S. Appl. No. 11/529,712; entitled "Systems and Methods for Interconnection of Multiple FPGA Devices", filed Sep. 28, 2006; 42 pgs.

Copending U.S. Appl. No. 11/529,713; entitled "Systems and Methods for Interconnection of Multiple FPGA Devices", filed Sep. 28, 2006; 42 pgs.

Yancey et al, "Systems and Methods for Data Transfer", U.S. Appl. No. 11/529,713, filed Sep. 28, 2006, Preliminary Amendment; Dec. 22, 2006, 11 pgs.

Yancey et al, "Systems and Methods for Data Transfer", U.S. Appl. No. 11/529,713, filed Sep. 28, 2006, Office Action, Feb. 19, 2009, 12 pgs.

Yancey et al, "Systems and Methods for Data Transfer", U.S. Appl. No. 11/529,713, filed Sep. 28, 2006, Amendment; Response to Office Action, May 19, 2009, 17 pgs.

Yancey et al, "Systems and Methods for Data Transfer", U.S. Appl. No. 11/529,713, filed Sep. 28, 2006, Office Action, Aug. 19, 2009, 5 pgs.

Yancey et al, "Systems and Methods for Data Transfer", U.S. Appl. No. 11/529,713, filed Sep. 28, 2006, Response to Office Action, Aug. 25, 2009, 4 pgs.

Yancey et al, "Systems and Methods for Data Transfer", U.S. Appl. No. 11/529,713, filed Sep. 28, 2006, Office Action, Oct. 2, 2009, 3 pgs.

Yancey et al, "Systems and Methods for Data Transfer", U.S. Appl. No. 11/529,713, filed Sep. 28, 2006, Response to Advisory Action, Oct. 14, 2009, 4 pgs.

Yancey et al, "Systems and Methods for Data Transfer", U.S. Appl. No. 11/529,713, filed Sep. 28, 2006, Notice of Allowance and Fees Due, Dec. 4, 2009, 4 pgs.

Yancey et al, "Systems and Methods for Interconnection of Multiple FPGA Devices", U.S. Appl. No. 10/843,226, filed May 11, 2004, Preliminary Amendment, Nov. 14, 2006, 19 pgs.

Yancey et al, "Systems and Methods for Interconnection of Multiple FPGA Devices", U.S. Appl. No. 10/843,226, filed May 11, 2004, Second Preliminary Amendment, Nov. 29, 2006, 3 pgs.

Yancey et al, "Systems and Methods for Interconnection of Multiple

2003, 3 pgs

Yancey et al, "Systems and Methods for Interconnection of Multiple FPGA Devices", U.S. Appl. No. 10/843,226, filed May 11, 2004, Amendment and response to Office Action, May 4, 2007, 32 pgs. Yancey et al, "Systems and Methods for Interconnection of Multiple FPGA Devices", U.S. Appl. No. 10/843,226, filed May 11, 2004, Office Action, Jul. 27, 2007, 29 pgs.

Yancey et al, "Systems and Methods for Interconnection of Multiple FPGA Devices", U.S. Appl. No. 10/843,226, filed May 11, 2004, Amendment and Response to Office Action, Sep. 27, 2007, 37 pgs. Yancey et al, "Systems and Methods for Interconnection of Multiple FPGA Devices", U.S. Appl. No. 10/843,226, filed May 11, 2004, Office Action, Nov. 6, 2007, 26 pgs.

Yancey et al, "Systems and Methods for Interconnection of Multiple FPGA Devices", U.S. Appl. No. 10/843,226, filed May 11, 2004, Amendment and Response to Office Action, Apr. 16, 2008, 46 pgs. Yancey et al, "Systems and Methods for Interconnection of Multiple FPGA Devices", U.S. Appl. No. 10/843,226, filed May 11, 2004, Notice of Allowance and Fees Due, Jul. 23, 2008, 11 pgs.

Yancey et al, "Systems and Methods for Writing Data With a Fifo Interface", U.S. Appl. No. 11/529,712, filed Sep. 28, 2006, Preliminary Amendment, Dec. 7, 2006, 13 pgs.

Yancey et al, "Systems and Methods for Writing Data With a Fifo Interface", U.S. Appl. No. 11/529,712, filed Sep. 28, 2006, Office Action, Apr. 27, 2007, 17 pgs.

Yancey et al, "Systems and Methods for Writing Data With a Fifo Interface", U.S. Appl. No. 11/529,712, filed Sep. 28, 2006, Amendment and Response to Office Action, Jul. 25, 2007, 19 pgs.

Yancey et al, "Systems and Methods for Writing Data With a Fifo Interface", U.S. Appl. No. 11/529,712, filed Sep. 28, 2006, Office Action, Oct. 22, 2007, 17 pgs.

Yancey et al, "Systems and Methods for Writing Data With a Fifo Interface", U.S. Appl. No. 11/529,712, filed Sep. 28, 2006, RCE and Amendment, Mar. 19, 2008, 26 pgs.

Yancey et al, "Systems and Methods for Writing Data With a Fifo Interface", U.S. Appl. No. 11/529,712, filed Sep. 28, 2006, Notice of Allowance and Fees Due, May 30, 2008, 7 pgs.

\* cited by examiner

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

## **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.