|                 | ORIGINATE DATE                                               | EDIT DATE                                 | DOCUMENT-REV. NUM.                                                         | PAGE          |

|-----------------|--------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------|---------------|

|                 | 24 September, 2001                                           | 4 September, 201544                       | GEN-CXXXXX-REVA                                                            | 1 of 51       |

| Author:         | Laurent Lefebvre                                             |                                           |                                                                            |               |

|                 |                                                              |                                           |                                                                            |               |

| Issue To:       |                                                              | Copy No:                                  |                                                                            |               |

|                 |                                                              |                                           |                                                                            |               |

|                 | R400 S                                                       | equencer Spe                              | cification                                                                 |               |

|                 | א איז איז איז איז איז איז איז איז איז אי                     | ายา เอรี เอม เอะ ห ห เอา เอะ ห เอะ โอะ เอ | מיזעטר איזאי אעטר פטאיאישטר איז                                            |               |

|                 |                                                              | SQ                                        |                                                                            |               |

|                 |                                                              | 20                                        |                                                                            |               |

|                 |                                                              | Version 2.07                              |                                                                            |               |

|                 |                                                              | Version 2.07                              |                                                                            |               |

| Overview: Thi   | s is an architectural specific                               | cation for the R400 Sequen                | cer block (SEQ). It provides an ov                                         | erview of the |

|                 | uired capabilities and expe<br>cks, and provides internal st |                                           | Iso describes the block interfaces,                                        | internal sub- |

|                 |                                                              |                                           |                                                                            |               |

|                 |                                                              |                                           |                                                                            |               |

|                 |                                                              |                                           |                                                                            |               |

| Δυτομάτις       | ALLY UPDATED FIELDS:                                         |                                           |                                                                            |               |

| Document L      | ocation: C:\pe                                               |                                           | locks\sq\R400_Sequencer.doc                                                |               |

|                 | anet Search Title: R400                                      | 0 Sequencer Specification<br>APPROVALS    |                                                                            |               |

|                 | Name/Dept                                                    |                                           | Signature/Date                                                             |               |

|                 |                                                              |                                           |                                                                            |               |

|                 |                                                              |                                           |                                                                            |               |

|                 |                                                              |                                           |                                                                            |               |

| Remarks:        |                                                              |                                           |                                                                            |               |

|                 |                                                              |                                           |                                                                            |               |

| THIS DO         | CUMENT CONTAIN                                               | IS CONFIDENTIAL I                         | NFORMATION THAT CO                                                         | ULD BE        |

|                 | NTIALLY DETRIME                                              | INTAL TO THE INTE                         | REST OF ATI TECHNOL                                                        |               |

|                 | INC. THROUGH L                                               | JNAUTHORIZED US                           | SE OR DISCLOSURE.                                                          |               |

|                 |                                                              |                                           |                                                                            |               |

|                 |                                                              |                                           |                                                                            |               |

|                 |                                                              |                                           | rial in this document constitutes an<br>provide notice that ATI owns a cop |               |

| unpublished w   | ork. The copyright notice                                    | is not an admission that                  | publication has occurred. This w<br>of this document may be used, re       | ork contains  |

|                 |                                                              |                                           | sion of ATI Technologies Inc."                                             | produced, or  |

|                 |                                                              |                                           |                                                                            |               |

|                 |                                                              |                                           |                                                                            | _             |

| Exhibit 2035.do | cR400_Sequencer.doc 73569 Bytes*** 🤅                         | ATI Confidential. Referer                 | nce Copyright Notice on Cover Pa                                           | ge © ***      |

|                 |                                                              |                                           |                                                                            |               |

ATI 2035 LG v. ATI IPR2015-00325

AMD1044\_0257711

ATI Ex. 2109 IPR2023-00922 Page 1 of 326

|                         | 2                     | ORIGINATE DATE         | EDIT DATE                  | R400 Sequencer Specification       | PAGE    |

|-------------------------|-----------------------|------------------------|----------------------------|------------------------------------|---------|

|                         | <u>u</u>              | 24 September, 2001     | <u>4 September, 201544</u> |                                    | 2 of 51 |

| Tab<br>1.<br>1.1<br>1.2 | <b>OVER</b><br>Top Le | evel Block Diagram     |                            |                                    | 9       |

| 1.2                     |                       |                        |                            |                                    |         |

| 2.                      | INTER                 | RPOLATED DATA BU       | JS                         |                                    | 11      |

| 3.                      |                       |                        |                            |                                    |         |

| 4.<br>5.                |                       |                        |                            | *****                              |         |

| 5.1                     | Memo                  | ry organizations       |                            |                                    | 14      |

| 5.2                     |                       |                        |                            |                                    |         |

| 5.3                     |                       |                        |                            |                                    |         |

|                         |                       |                        |                            |                                    |         |

|                         |                       |                        | -                          | t                                  |         |

|                         |                       | ,                      |                            |                                    |         |

|                         |                       |                        |                            |                                    |         |

|                         |                       |                        |                            |                                    |         |

|                         |                       |                        |                            |                                    |         |

| 5.4<br>5.5              |                       | -                      |                            |                                    |         |

| 5.6                     |                       |                        |                            |                                    |         |

| 6.                      |                       |                        |                            |                                    |         |

| 6.1<br>6.2              |                       | •                      |                            |                                    |         |

|                         |                       |                        |                            |                                    |         |

| 6.3                     |                       |                        |                            |                                    |         |

| 6.4<br>6.5              | Data c                | lependant predicate i  | nstructions                |                                    | 24      |

| 6.6<br>6.7              |                       |                        |                            |                                    |         |

| 6.                      | 7.1 r                 | Method 1: Debugging    | registers                  |                                    |         |

| 6.                      | 7.2 r                 | Method 2: Exporting tl | ne values in the GPR       | \$                                 |         |

| 7.                      |                       |                        |                            |                                    |         |

| 8.<br>9.                |                       |                        |                            |                                    |         |

| 10.                     |                       | H ARBITRATION          |                            |                                    |         |

| 11.                     | ALU A                 | ARBITRATION            | *****                      |                                    |         |

| 12.                     |                       |                        |                            |                                    |         |

| 13.<br>14.              |                       |                        |                            | IFOS                               |         |

| 15.                     |                       |                        |                            |                                    |         |

| 15.1<br>16.             |                       |                        |                            |                                    |         |

|                         |                       |                        |                            | erence Copyright Notice on Cover F |         |

ATI Ex. 2109 IPR2023-00922 Page 2 of 326

|           | ORIGINATE DATE           | EDIT DATE              | DOCUMENT-REV. NUM.                      | PAGE    |

|-----------|--------------------------|------------------------|-----------------------------------------|---------|

|           | 24 September, 2001       |                        | GEN-CXXXXX-REVA                         | 3 of 51 |

| 17. THE F | • • •                    | 4 September, 201514    |                                         |         |

|           |                          |                        | *************************************** |         |

| 17.1.1    |                          |                        |                                         |         |

| 17.1.2    |                          |                        |                                         |         |

| 17.1.3    |                          |                        |                                         |         |

|           | tration restrictions     |                        |                                         | 32      |

|           |                          |                        | *****                                   |         |

|           |                          |                        |                                         |         |

|           |                          |                        | ****                                    |         |

|           |                          |                        |                                         |         |

|           |                          |                        |                                         |         |

|           | •                        |                        |                                         |         |

| 19.3.2    |                          |                        |                                         |         |

|           |                          |                        | ****                                    |         |

|           |                          |                        |                                         |         |

|           |                          |                        |                                         |         |

|           |                          |                        | *****                                   |         |

|           |                          |                        |                                         |         |

|           |                          |                        |                                         |         |

|           |                          |                        |                                         |         |

| 23.2.1    | SC_SP#                   |                        |                                         |         |

| 23.2.2    | SC_SQ                    |                        |                                         |         |

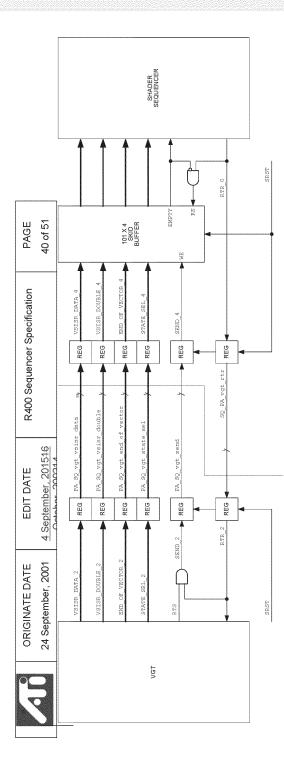

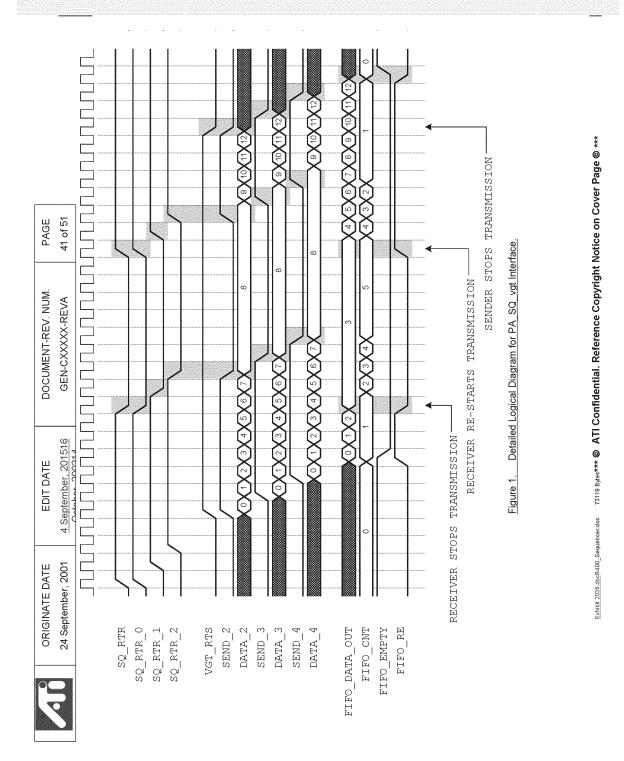

| 23.2.3    | SQ to SX(SP): Interpo    | olator bus             |                                         | 39      |

| 23.2.4    |                          |                        |                                         |         |

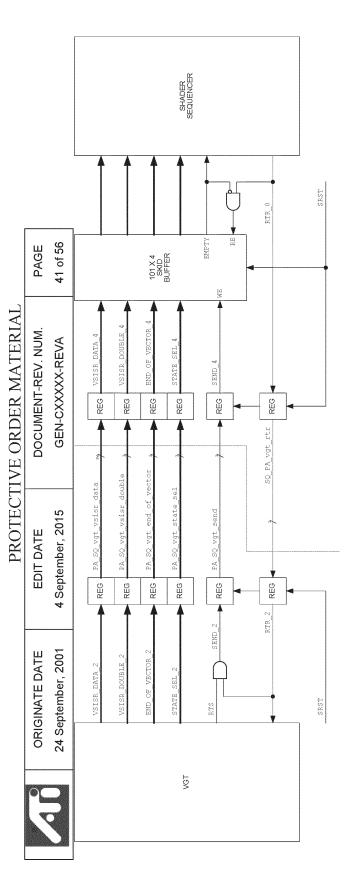

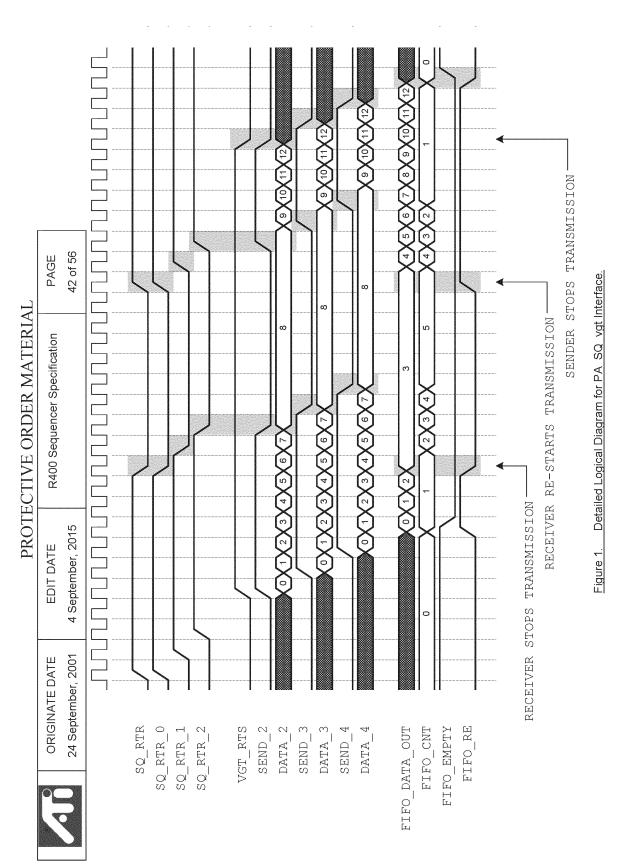

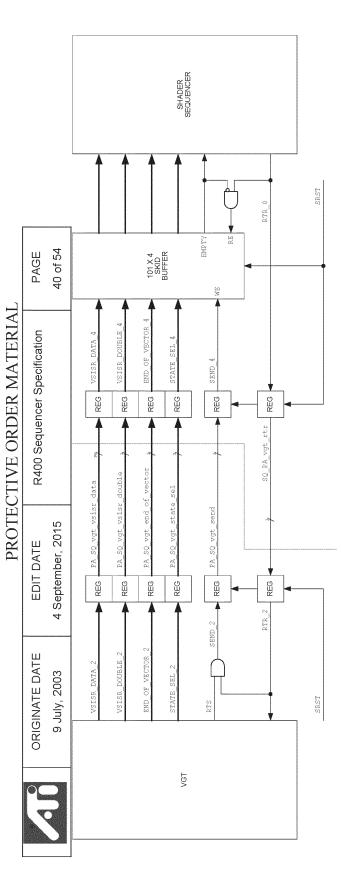

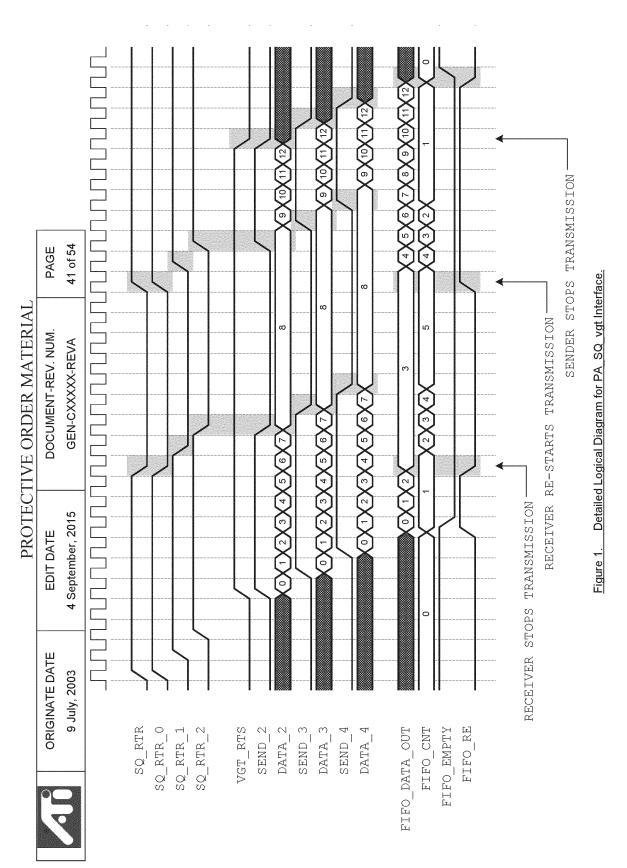

| 23.2.5    | VGT to SQ : Vertex in    | terface                |                                         | 39      |

| 23.2.6    | SQ to SX: Control bus    | S                      |                                         |         |

| 23.2.7    | SX to SQ : Output file   | control                |                                         |         |

| 23.2.8    | SQ to TP: Control bus    | \$                     |                                         |         |

| 23.2.9    | TP to SQ: Texture sta    |                        |                                         | 43      |

| 23.2.10   | SQ to SP: Texture sta    | all                    |                                         |         |

| 23.2.11   | SQ to SP: GPR and a      | uto counter            |                                         | 44      |

|           |                          |                        |                                         |         |

| 23.2.13   | SP to SQ: Constant a     | ddress load/ Predicate | Set/Kill set                            |         |

| 23.2.14   | SQ to SPx: constant I    | proadcast              |                                         |         |

| 23.2.15   | SQ to CP: RBBM bus       | i                      |                                         |         |

| 23.2.16   | CP to SQ: RBBM bus       | i                      |                                         |         |

|           |                          |                        |                                         |         |

| 23.3 Exa  | mple of control flow pro | gram execution         |                                         |         |

|           |                          | •                      | ce Copyright Notice on Cover Pa         |         |

ATI Ex. 2109 IPR2023-00922 Page 3 of 326

|          | ORIGINATE DATE     | EDIT DATE           | R400 Sequencer Specification | PAGE    |

|----------|--------------------|---------------------|------------------------------|---------|

|          | 24 September, 2001 | 4 September, 201514 |                              | 4 of 51 |

| 24. OPEN | I ISSUES           |                     |                              |         |

Exhibit 2035.docR400\_Sequencer.doc 73569 Bytes\*\*\* © ATI Confidential. Reference Copyright Notice on Cover Page © \*\*\*

AMD1044\_0257714

ATI Ex. 2109 IPR2023-00922 Page 4 of 326

|                                                                                                                                                                                                                                      | ORIGINATI                                                                                                                                                                                        | E DATE           | EDIT DATE                                                                                                            | DOCUMENT-RE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | /. NUM.                                      | PAGE                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------|

| CAU                                                                                                                                                                                                                                  | 24 Septemb                                                                                                                                                                                       | er, 2001         | 4 September, 201514                                                                                                  | GEN-CXXXXX-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | REVA                                         | 5 of 51                      |

| Revision                                                                                                                                                                                                                             | Changes                                                                                                                                                                                          | S<br>S<br>Soom   |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                              |                              |

| <b>Rev 0.1 (Laur</b><br>Date: May 7, 2                                                                                                                                                                                               | r <b>ent Lefebvre)</b><br>2001                                                                                                                                                                   |                  | First o                                                                                                              | raft.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                              |                              |

| Rev 0.2 (Laure<br>Date : July 9, 2<br>Rev 0.3 (Laure<br>Date : August<br>Rev 0.4 (Laure<br>Date : August<br>Rev 0.5 (Laure<br>Date : Septem<br>Rev 0.6 (Laure<br>Date : Septem<br>Rev 0.7 (Laure<br>Date : Octobel<br>Rev 0.8 (Laure | 2001<br>ent Lefebvre)<br>6, 2001<br>ent Lefebvre)<br>24, 2001<br>ent Lefebvre)<br>nber 7, 2001<br>ent Lefebvre)<br>nber 24, 2001<br>ent Lefebvre)<br>r 5, 2001<br>ent Lefebvre)<br>ent Lefebvre) |                  | SP. A<br>Revie<br>Augue<br>Addee<br>file ar<br>flow o<br>Addee<br>Chan<br>archit<br>Addee<br>store<br>data o<br>Chan | Changed the interfaces to reflect the changes in the<br>SP. Added some details in the arbitration section.<br>Reviewed the Sequencer spec after the meeting on<br>August 3, 2001.<br>Added the dynamic allocation method for register<br>file and an example (written in part by Vic) of the<br>flow of pixels/vertices in the sequencer.<br>Added timing diagrams (Vic)<br>Changed the spec to reflect the new R400<br>architecture. Added interfaces.<br>Added constant store management, instruction<br>store management, control flow management and<br>data dependant predication.<br>Changed the control flow method to be more |                                              |                              |

| Date : Octobe<br>Rev 0.9 (Laure<br>Date : Octobe                                                                                                                                                                                     | ent Lefebvre)<br>r 17, 2001                                                                                                                                                                      |                  | Incorp<br>flow r<br>the o<br>regist                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | the 10/18/01<br>instruction, re<br>mp. Added | moved<br>debug               |

| Rev 1.0 (Laure<br>Date : Octobel<br>Rev 1.1 (Laure<br>Date : Octobel                                                                                                                                                                 | r 19, 2001<br>ent Lefebvre)<br>r 26, 2001                                                                                                                                                        |                  | Addeo<br>precis<br>Metho                                                                                             | ed interfaces to RB. Adde<br>I SEQ→SP0 interface<br>ion. Changed VGT→SF<br>ds added.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | s. Changed<br>0 interface.                   | delta<br>Debug               |

| Rev 1.2 (Laure<br>Date : Novemi<br>Rev 1.3 (Laure<br>Date : Novemi                                                                                                                                                                   | ber 16, 2001<br>ent Lefebvre)                                                                                                                                                                    |                  |                                                                                                                      | ces greatly refined. Clear<br>I the different interpolation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              | C.                           |

| Rev 1.4 (Laure<br>Date : Decemi<br>Rev 1.5 (Laure                                                                                                                                                                                    | ent Lefebvre)<br>ber 6, 2001                                                                                                                                                                     |                  | the Vi<br>mana                                                                                                       | I the auto incrementing<br>GT→SQ interface. Added<br>gement. Updated GPRs.<br>ved from the spec all in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | content on co                                | onstant                      |

| Date : Decemi                                                                                                                                                                                                                        | ber 11, 2001                                                                                                                                                                                     |                  | direct<br>const<br>synch                                                                                             | y tied to the SQ. Add<br>int management.<br>ronization fields and expla                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ed explanatio<br>Added P.<br>anation.        | ons on<br>A→SQ               |

| Rev 1.6 (Laure<br>Date : January                                                                                                                                                                                                     | y 7, 2002                                                                                                                                                                                        |                  | detail<br>call ii<br>Addeo<br>updat                                                                                  | I more details on the sta<br>about the parameter ca<br>istruction to a Condition<br>I details on constant<br>ed the diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ches. Chang<br>nnal_call instr<br>managemen  | ed the<br>ruction.<br>it and |

| Rev 1.7 (Laure<br>Date : Februar<br>Rev 1.8 (Laure<br>Date : March 4                                                                                                                                                                 | ry 4, 2002<br>ent Lefebvre)                                                                                                                                                                      |                  | interfa<br>New i                                                                                                     | I Real Time parameter<br>ce. Updated the control fl<br>nterfaces to the SX bloc<br>e modifier, removed t<br>stions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ow section.<br>k. Added the                  | end of                       |

| Date : March 2                                                                                                                                                                                                                       | 18, 2002<br>irrent Lefebvre)<br>25, 2002<br>irrent Lefebvre)<br>0, 2002<br>ent Lefebvre)                                                                                                         |                  | Reara<br>ensur<br>Updat<br>expor<br>Addeo<br>spec v                                                                  | ngement of the CF instru-<br>byte alignement.<br>ed the interfaces and a<br>ing rules.<br>I CP state report interfact<br>vith the old control flow so<br>ontrol flow scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                           | added a sect<br>e. Last versior              | ion on                       |

| Exhibit 2035.docR                                                                                                                                                                                                                    | 1400_Sequencer.doc 7                                                                                                                                                                             | 73569 Bytes*** C | ATI Confidential. Refe                                                                                               | ence Copyright Notice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | on Cover Pag                                 | e © ***                      |

ATI Ex. 2109 IPR2023-00922 Page 5 of 326

|                                         | ORIGINATE DATE     | EDIT DATE           | R400 Sequencer Specification           | PAGE            |

|-----------------------------------------|--------------------|---------------------|----------------------------------------|-----------------|

|                                         | 24 September, 2001 | 4 September, 201514 |                                        | 6 of 51         |

| Rev 2.01 (Lau                           | rent Lefebvre)     | Cha                 | nged slightly the control flow instru  | uctions to      |

| Date : May 2,                           | 2002               | allov               | v force jumps and calls.               |                 |

| Rev 2.02 (Lau                           | rent Lefebvre)     | Upd                 | ated the Opcodes. Added type fie       | ld to the       |

| Date : May 13                           | , 2002             | cons                | stant/pred interface. Added Last fie   | ld to the       |

|                                         |                    | SQ-                 | →SP instruction load interface.        |                 |

| Rev 2.03 (Lau                           | rent Lefebvre)     | SP                  | interface updated to include p         | redication      |

| Date : July 15                          | , 2002             | •                   | nizations. Added the predicate         | no stall        |

|                                         |                    |                     | uctions,                               |                 |

| (                                       | rent Lefebvre)     |                     | umented the new parameter generatio    | n scheme        |

| Date :August 2                          |                    |                     | Y coordinates points and lines STs.    |                 |

|                                         | rent Lefebvre)     |                     | e interface changes and an ar          | chitectural     |

| Date : Septem                           |                    |                     | nge to the auto-counter scheme.        |                 |

|                                         | rent Lefebvre)     |                     | ened the event interface to 5 bits. So | ome other       |

| Date : Octobe                           | ,                  |                     | typos corrected.                       |                 |

| *************************************** | rent Lefebvre)     |                     | os, jumps and calls are now using      |                 |

| Date : Octobe                           | <u>r 14, 2002</u>  |                     | ress which allows to jump and call     |                 |

|                                         |                    |                     | nd any control flow addresses (        | <u>does not</u> |

|                                         |                    | requ                | iires to be even anymore).             |                 |

|                                         |                    |                     |                                        |                 |

|                                         |                    |                     |                                        |                 |

|                                         |                    |                     |                                        |                 |

Exhibit 2035.doc.R400\_Sequences.doc 73569 Bytes\*\*\* C ATI Confidential. Reference Copyright Notice on Cover Page C \*\*\*

AMD1044\_0257716

ATI Ex. 2109 IPR2023-00922 Page 6 of 326

|  | ORIGINATE DATE     | EDIT DATE           | DOCUMENT-REV. NUM. | PAGE    |  |

|--|--------------------|---------------------|--------------------|---------|--|

|  | 24 September, 2001 | 4 September, 201514 | GEN-CXXXXX-REVA    | 7 of 51 |  |

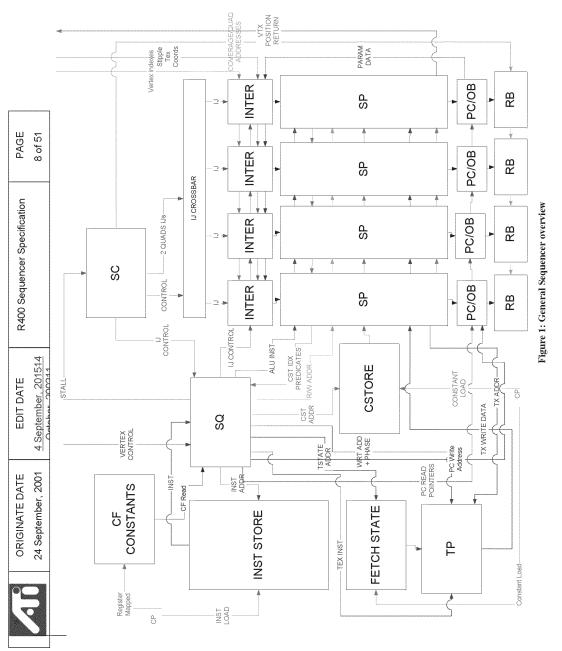

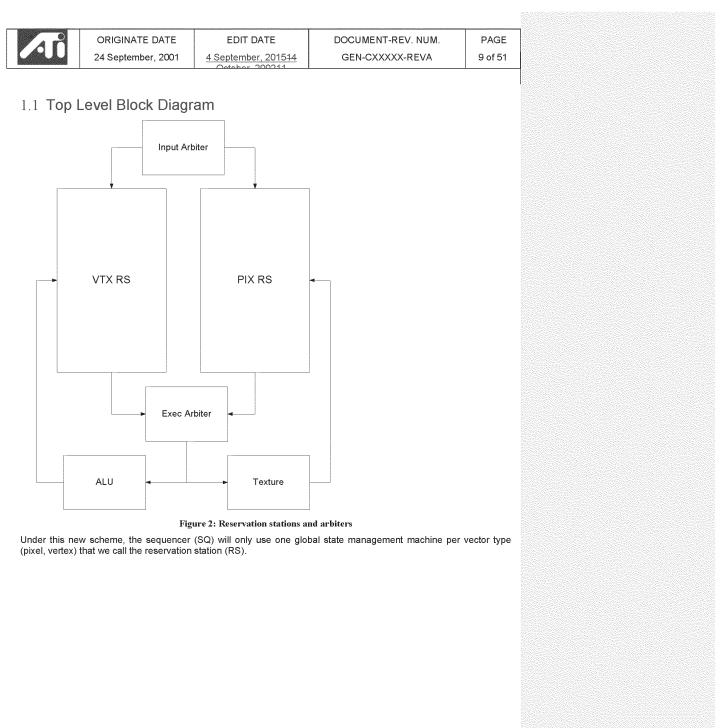

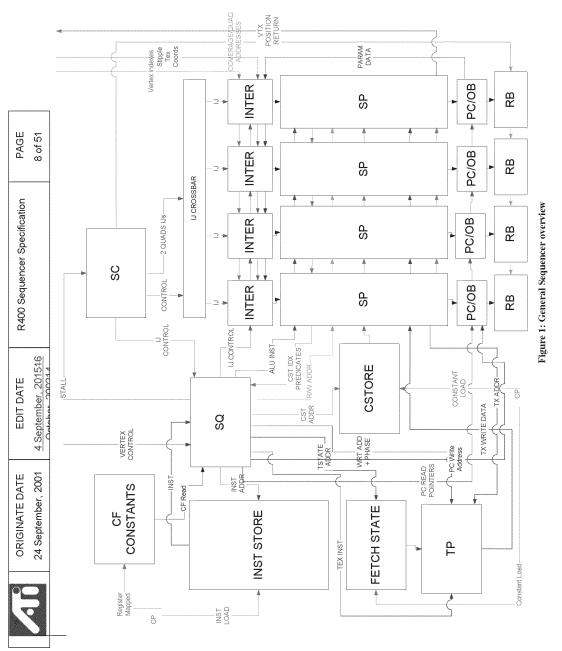

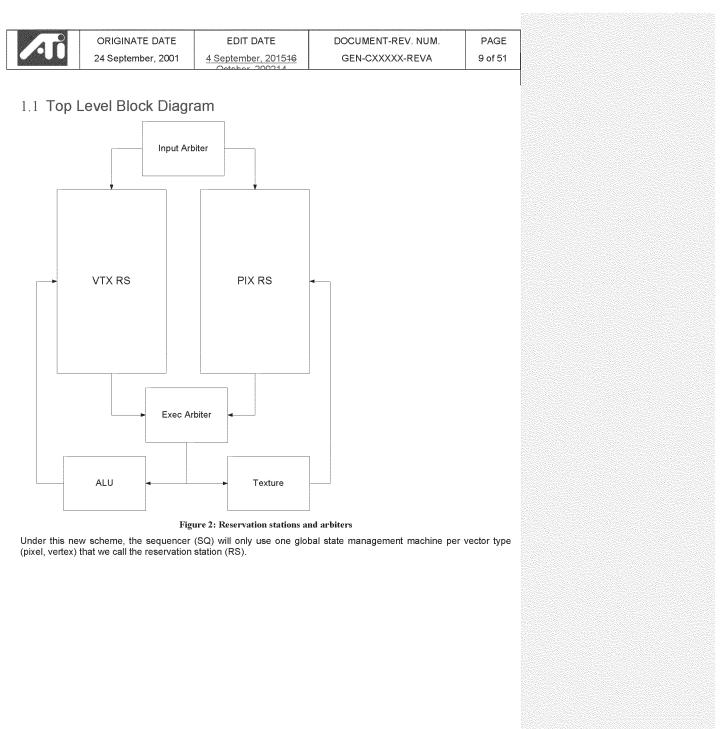

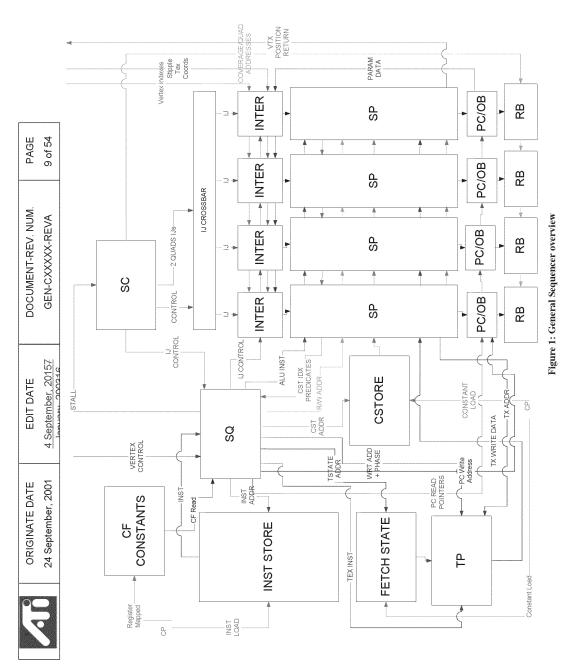

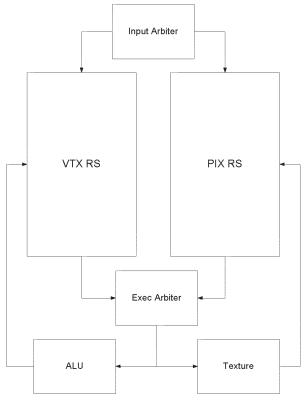

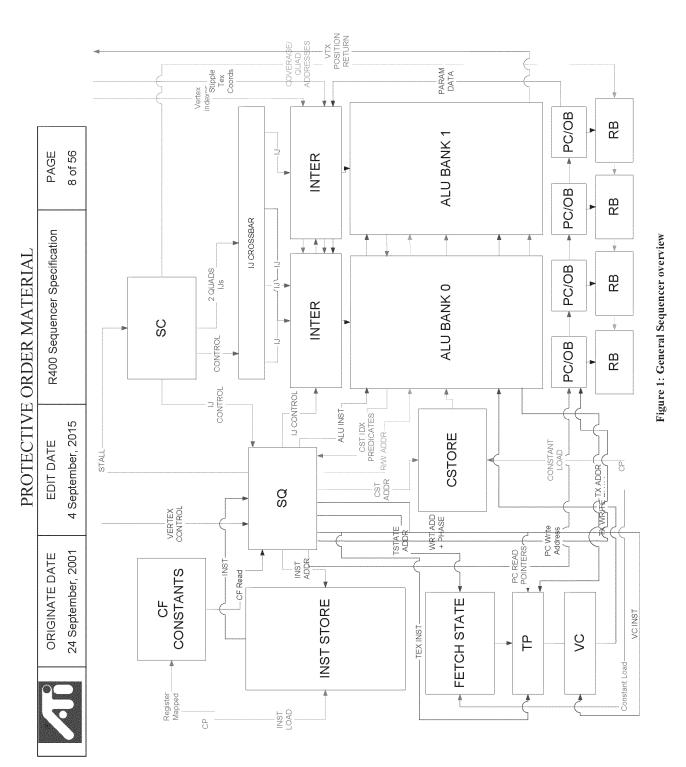

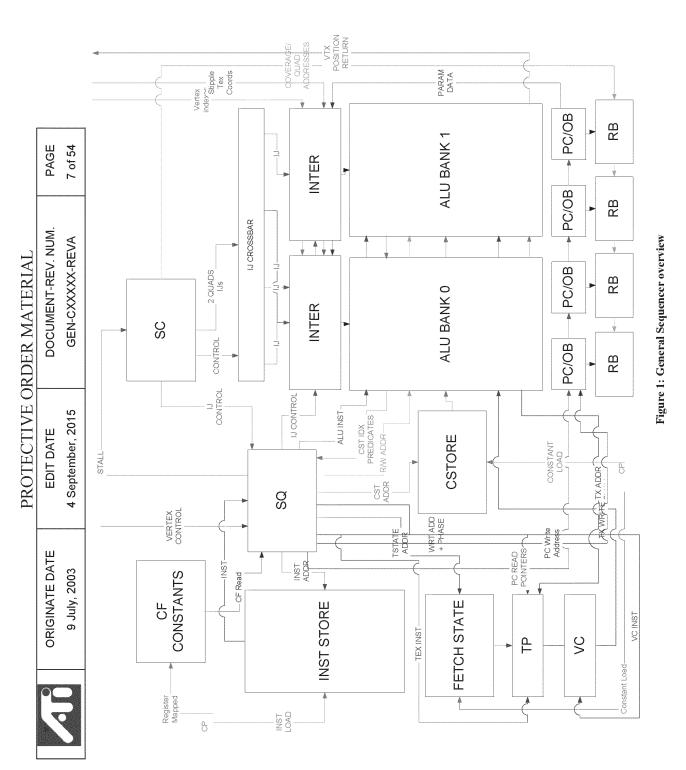

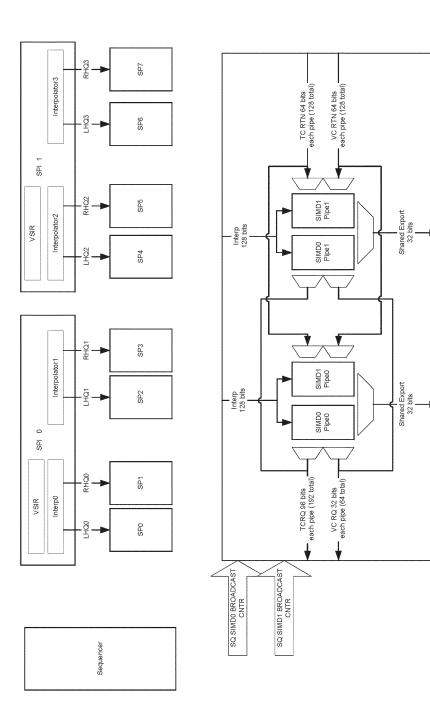

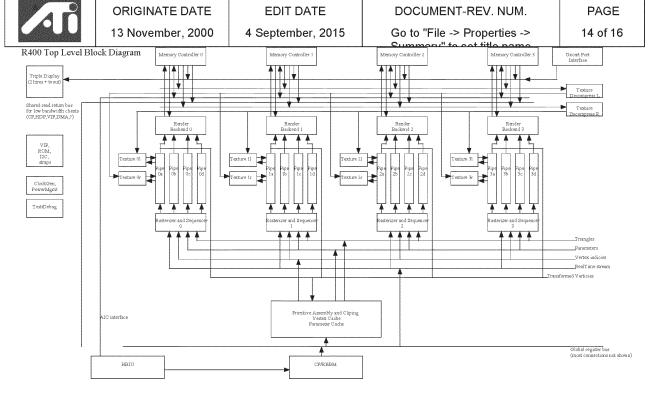

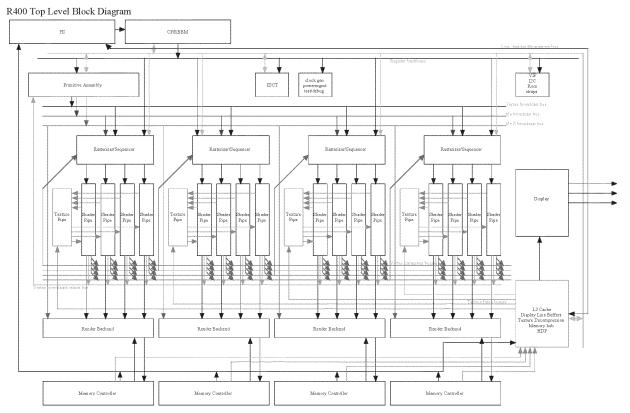

## 1. Overview

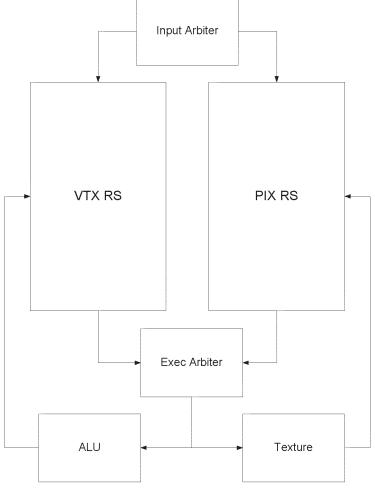

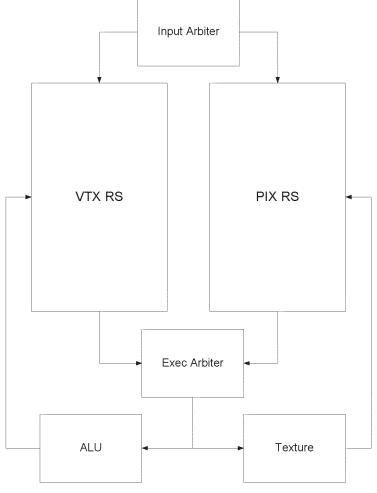

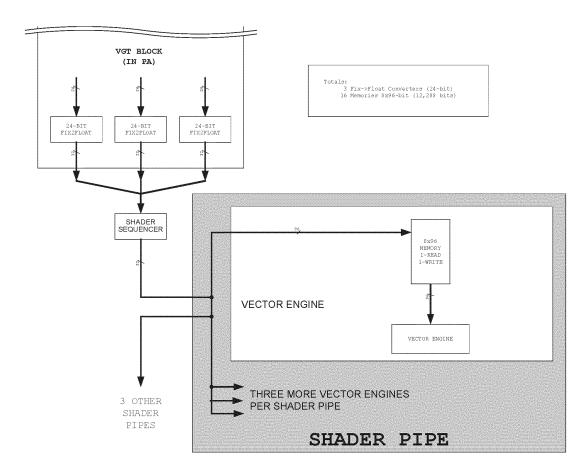

The sequencer chooses two ALU threads and a fetch hread to execute, and executes all of the instructions in a block before looking for a new clause of the same type. Two ALU threads are executed interleaved to hide the ALU latency. The arbitrator will give priority to older threads. There are two separate reservation stations, one for pixel vectors and one for vertices vectors. This way a pixel can pass a vertex and a vertex can pass a pixel.

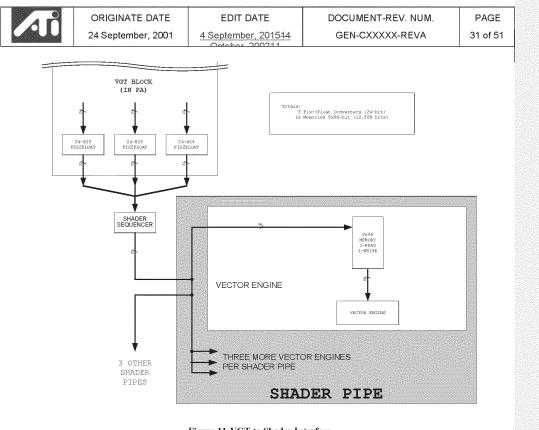

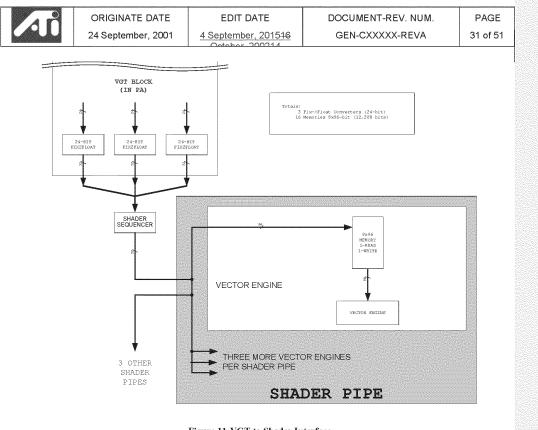

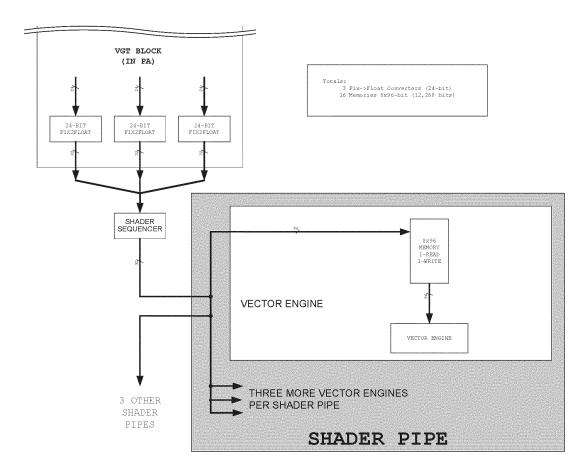

To support the shader pipe the sequencer also contains the shader instruction cache, constant store, control flow constants and texture state. The four shader pipes also execute the same instruction thus there is only one sequencer for the whole chip.

The sequencer first arbitrates between vectors of 64 vertices that arrive directly from primitive assembly and vectors of 16 quads (64 pixels) that are generated in the scan converter.

The vertex or pixel program specifies how many GPRs it needs to execute. The sequencer will not start the next vector until the needed space is available in the GPRs.

Exhibit 2035. doc R400\_Sequencer.doc 73569 Bytes\*\*\*\* © ATI Confidential. Reference Copyright Notice on Cover Page © \*\*\*

AMD1044\_0257717

ATI Ex. 2109 IPR2023-00922 Page 7 of 326

# PROTECTIVE ORDER MATERIAL

Exhibit 2035 doc/8400\_Sequencer.doo 73569 Bytes\*\*\* © ATI Confidential. Reference Copyright Notice on Cover Page © \*\*\*

AMD1044\_0257718

ATI Ex. 2109 IPR2023-00922 Page 8 of 326

Exhibit 2035.docR400\_Sequencer.doc 73569 Bytes\*\*\* © ATI Confidential. Reference Copyright Notice on Cover Page © \*\*\*

AMD1044\_0257719

ATI Ex. 2109 IPR2023-00922 Page 9 of 326

ATI Ex. 2109 IPR2023-00922 Page 10 of 326

| ORIGINATE DATE     | EDIT DATE           | DOCUMENT-REV. NUM. | PAGE     |

|--------------------|---------------------|--------------------|----------|

| 24 September, 2001 | 4 September, 201544 | GEN-CXXXXX-REVA    | 11 of 51 |

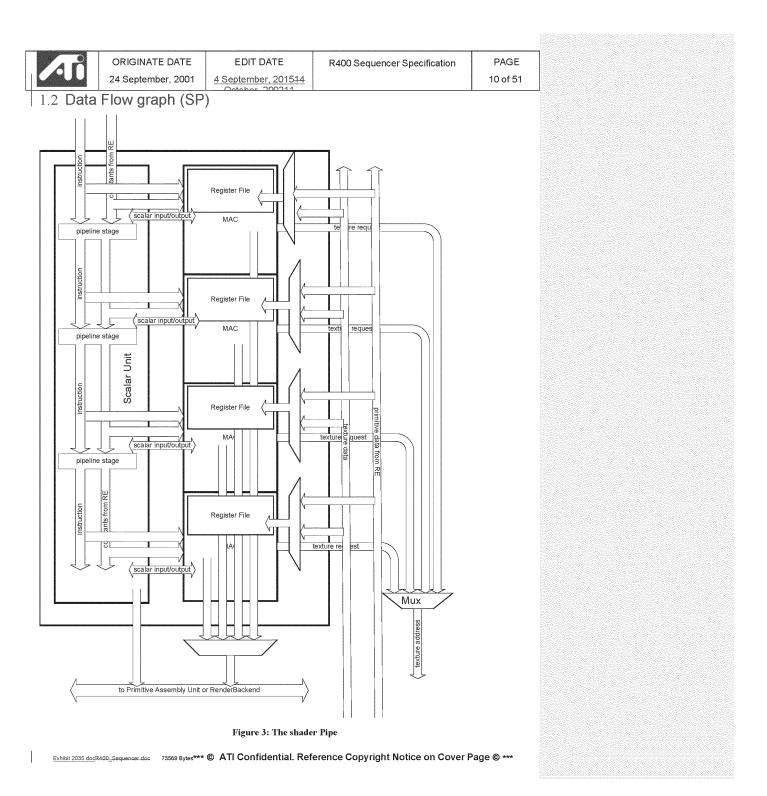

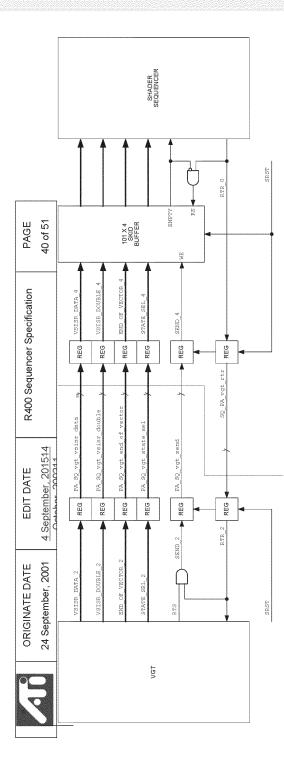

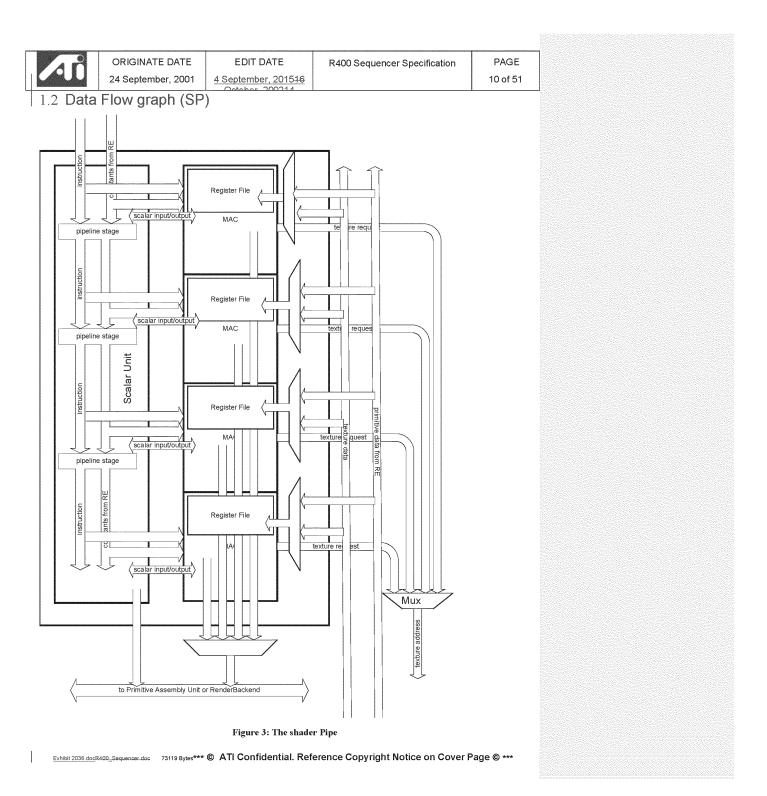

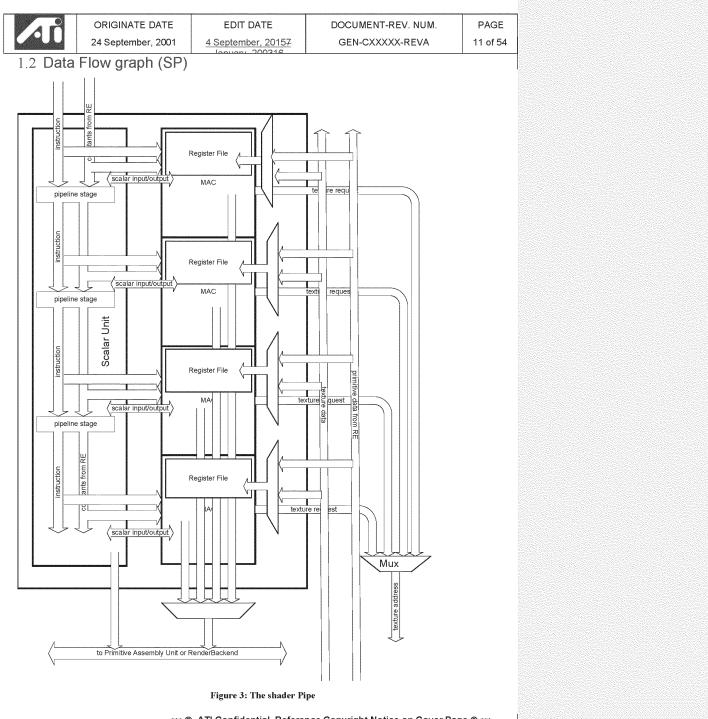

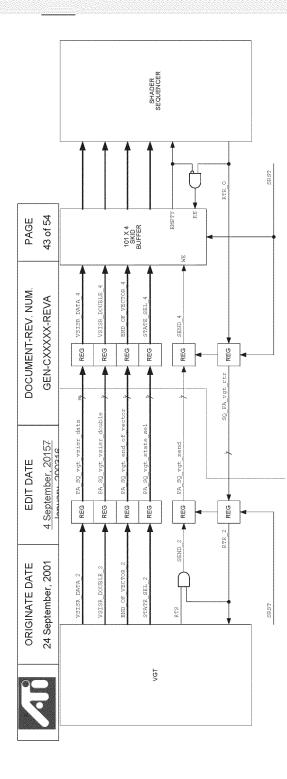

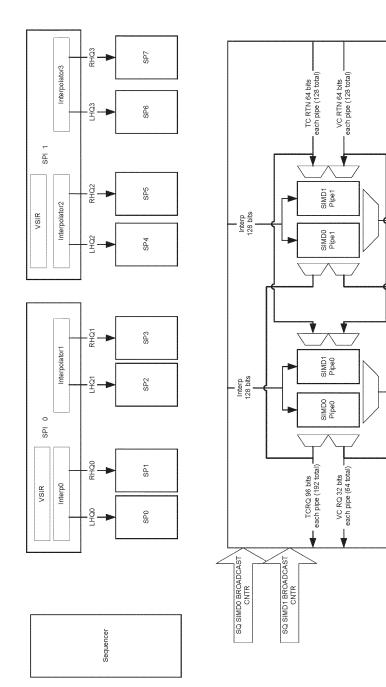

The gray area represents blocks that are replicated 4 times per shader pipe (16 times on the overall chip).

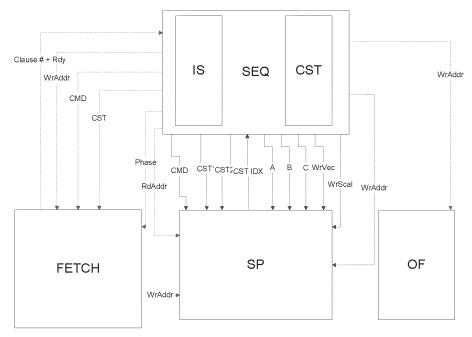

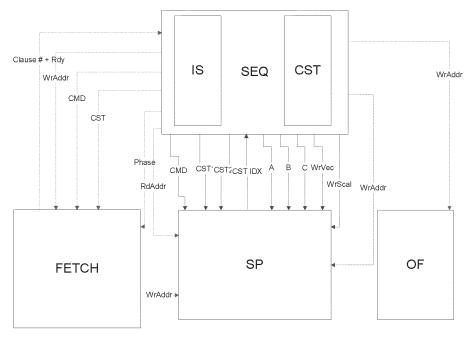

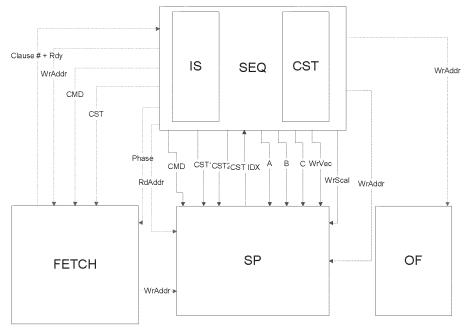

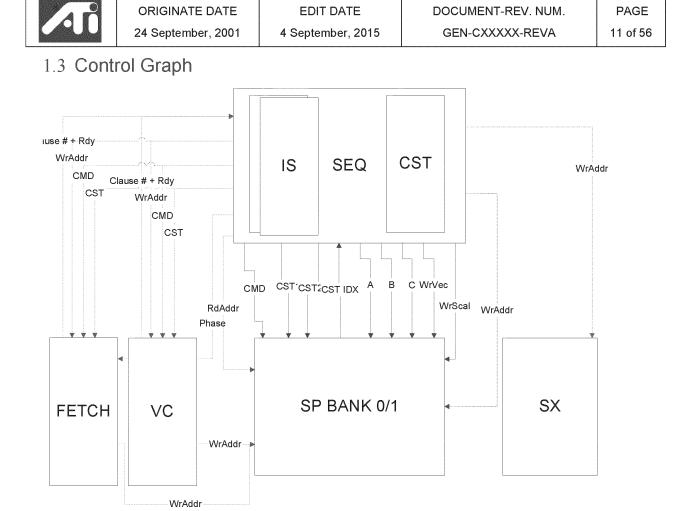

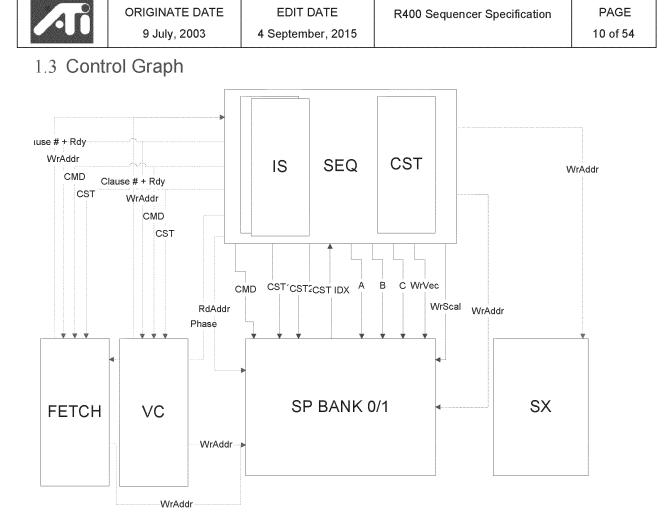

# 1.3 Control Graph

Figure 4: Sequencer Control interfaces

In green is represented the Fetch control interface, in red the ALU control interface, in blue the Interpolated/Vector control interface and in purple is the output file control interface.

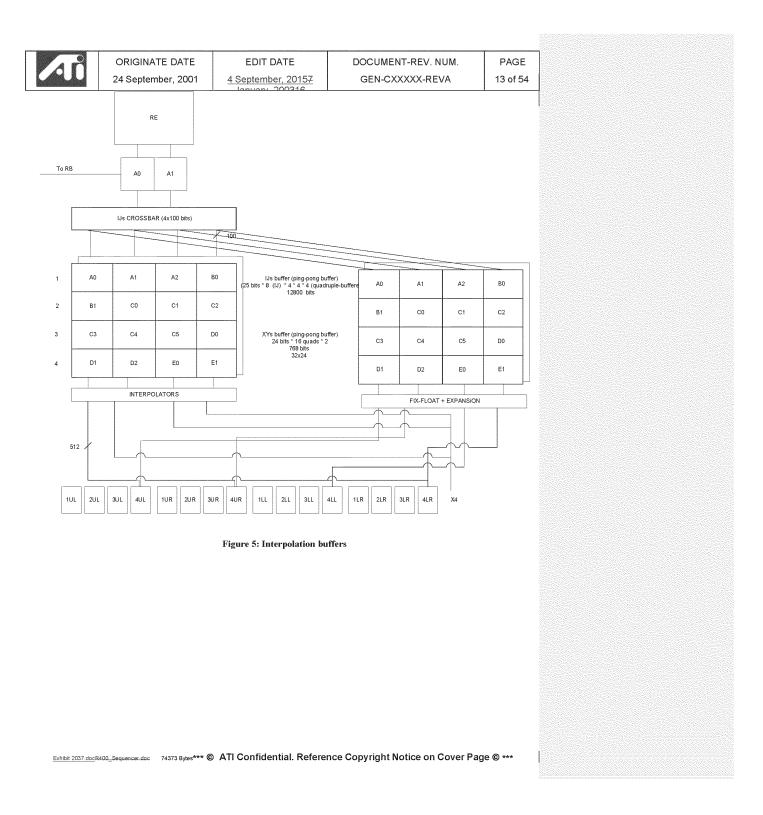

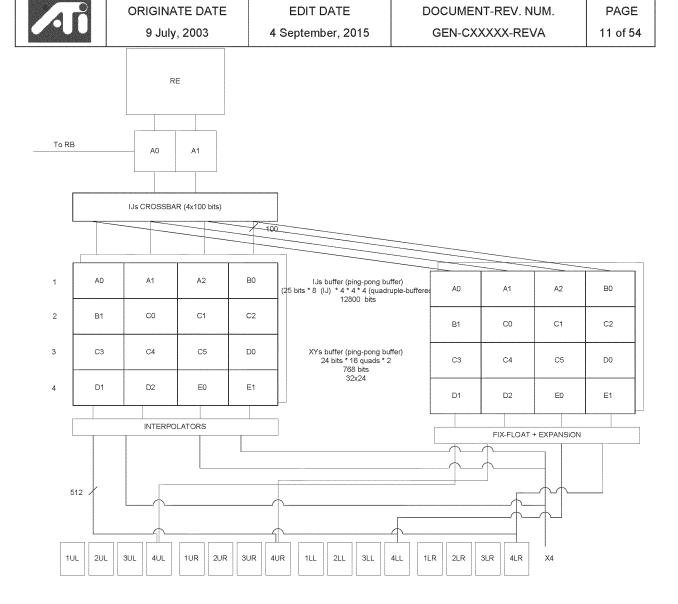

# 2. Interpolated data bus

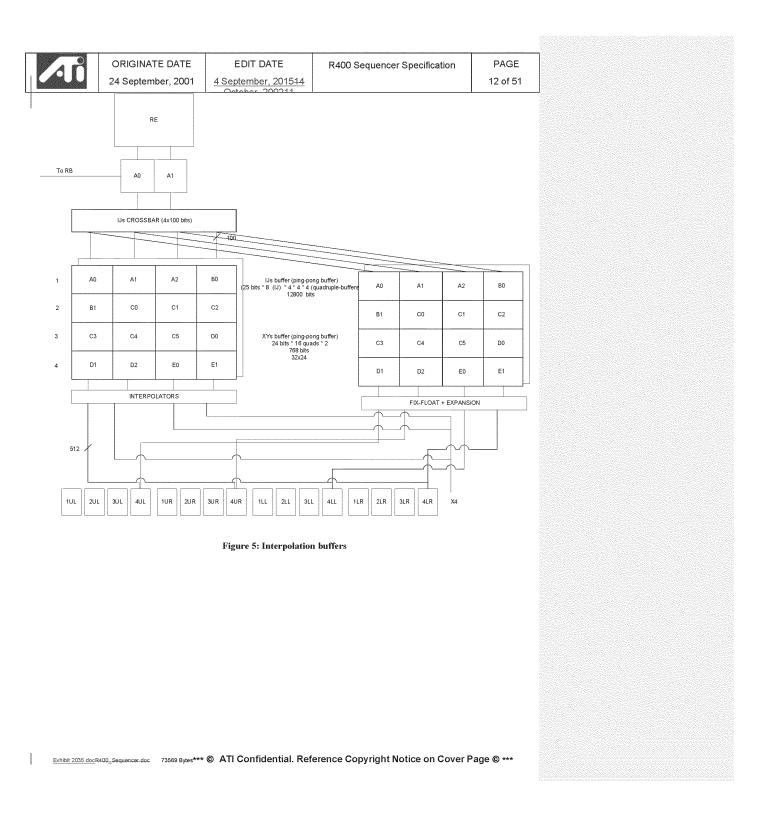

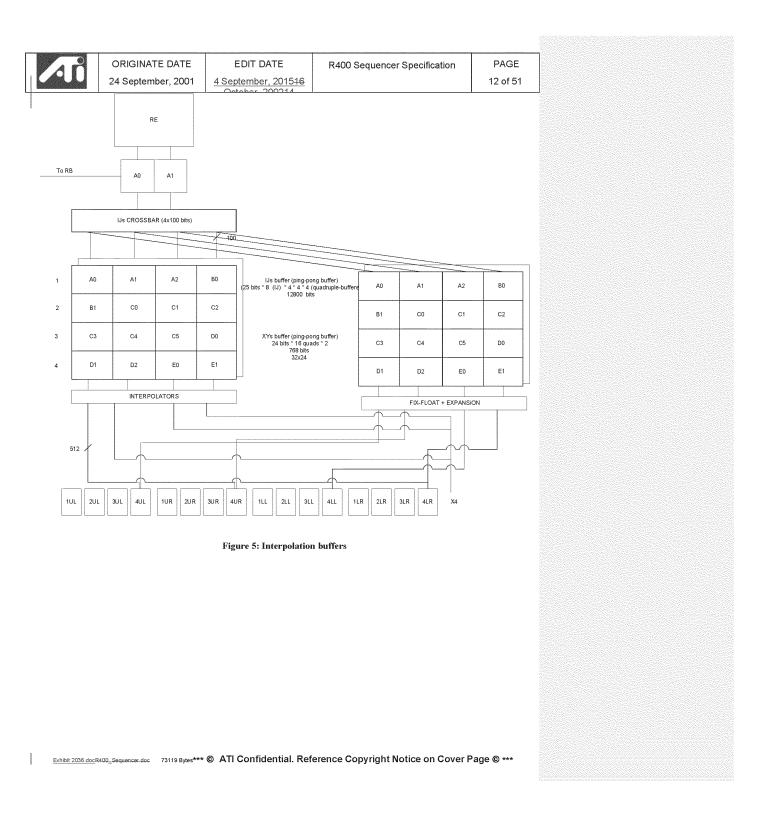

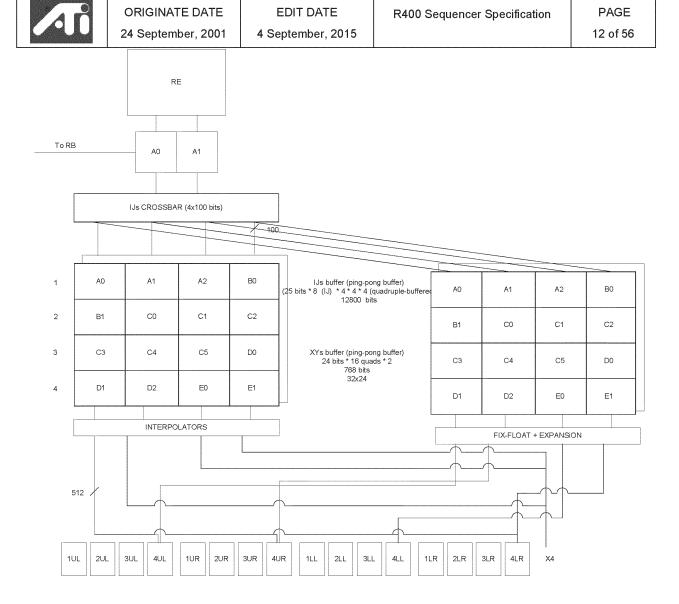

The interpolators contain an IJ buffer to pack the information as much as possible before writing it to the register file.

Exhibit 2035. docR400\_Sequences.doc 73569 Bytes\*\*\* © ATI Confidential. Reference Copyright Notice on Cover Page © \*\*\*

AMD1044\_0257721

ATI Ex. 2109 IPR2023-00922 Page 11 of 326

ATI Ex. 2109 IPR2023-00922 Page 12 of 326

# PROTECTIVE ORDER MATERIAL

|                    |                     | T23                 |                  |                |      |        | 51 - 48 <              | 52-<br>55           | 56-<br>59              | ≥ ° 8                     |                    |

|--------------------|---------------------|---------------------|------------------|----------------|------|--------|------------------------|---------------------|------------------------|---------------------------|--------------------|

|                    |                     | T22                 |                  |                |      |        | V V<br>32-48-<br>35 51 | အ အွဲ <             | V V<br>40-56-<br>43 59 | V V<br>44-60-<br>47 63    | X                  |

|                    |                     | T21                 |                  |                |      |        | > 16-<br>19            | 23 <sup>2</sup> 0 < | 24-<br>27              | 31 -28 <                  | ×<br>15            |

|                    |                     | T19 T20 T21 T22 T23 |                  |                |      |        | > 0-3                  | > 4-7               | , ⇒ ⇔ <del>,</del>     | →<br>15<br>15 <           |                    |

|                    |                     | T19                 |                  |                |      |        |                        |                     | ΕO                     | Ш                         |                    |

|                    |                     | T18                 |                  |                |      |        |                        |                     |                        | 8                         |                    |

| щ                  | 51                  | T17                 |                  |                | ≳ ଘ  | ×Π     |                        | 8                   | 5                      | ß                         |                    |

| PAGE               | 13 of 51            | T16                 |                  |                | В    | ш      |                        |                     |                        | BO                        | P2                 |

|                    |                     | T15                 |                  |                | ШO   | Ш<br>Т | 5                      | D2                  |                        |                           | ۵                  |

| NUM.               | VA                  | T14                 | ₹₽               | ≳8             |      | ×۵     | ប៊                     | C4                  | C5                     |                           |                    |

| DOCUMENT-REV. NUM. | GEN-CXXXX-REVA      | T13                 | δ                | D2             |      | ß      | B1                     |                     |                        |                           |                    |

| IENT-F             | (XXX)               | T12                 | Б                | 6              |      | ß      | AO                     | A1                  | A2                     |                           |                    |

| ocuN               | GEN-(               | T10 T11 T12         |                  | ≿ 2            | ≿ ນິ |        |                        |                     | о<br>Ш                 | Ш                         | ****************** |

| ă                  |                     | T10                 | É                | 5              | C5   | 0      | ¥                      |                     |                        | 8                         |                    |

|                    | 4                   | T9                  |                  | 5              | C5   |        |                        | 8                   | 5                      | ß                         |                    |

| ΞĽ                 | 2015                | Т8                  | ≿ ເິ             | ≳ 8            | ≿ ວ  | ≿ 8    |                        |                     |                        | BO                        | demaana            |

| EDIT DATE          | mber,               | 11                  | ខ                | 8              | δ    | 3      | 5                      | D2                  |                        |                           | À                  |

|                    | 4 September, 201514 | T6                  | ទ                | 8              | ъ    | 3      | ប៊                     | 5<br>2              | C5                     |                           |                    |

|                    | ~                   | Т5                  | ×₽               |                |      | ×₿     | B1                     |                     |                        |                           |                    |

| ATE                | 2001                | Т4                  | Bi               |                |      | BO     | AO                     | A1                  | A2                     |                           |                    |

| ATE D              | mber,               | T3                  | Ð                |                |      | BO     | X<br>48-<br>51         | XY<br>52-<br>55     | 56 -<br>56 -           | 3°X                       |                    |

| RIGINATE DATE      | September, 2001     | Т2                  | ¥ 8              | ≿₽             | Σ₹   |        | 35 23 ₹                | အ အွ X              | ∑ \$ £                 | XY XY<br>44- 60-<br>47 63 | $\geq$             |

| ō                  | 24                  | 11                  | Ao               | A1             | A2   |        | , †<br>19<br>19        | 3 \$ X              | 24-27                  | 3 % X                     | ×                  |

| 9                  |                     | D<br>10             | Ao               | A1             | A2   |        | 53 X                   | × × -4              | ≿ ∾ ≿                  | 15 ¦2 ≷                   |                    |

| K                  | 3                   |                     | Ч <sup>S</sup> о | <del>с</del> – | dS ∽ | ი წ    | с о                    | с<br>С              | р<br>С<br>С            | ი ი                       |                    |

Figure 6: Interpolation timing diagram

Exhibit 2035 doe R400\_Sequences 73589 Bytes\*\*\*\* © ATI Confidential. Reference Copyright Notice on Cover Page © \*\*\*

AMD1044\_0257723

ATI Ex. 2109 IPR2023-00922 Page 13 of 326

| 2  | ORIGINATE DATE     | EDIT DATE           | R400 Sequencer Specification | PAGE     |

|----|--------------------|---------------------|------------------------------|----------|

| JU | 24 September, 2001 | 4 September, 201514 |                              | 14 of 51 |

Above is an example of a tile the sequencer might receive from the SC. The write side is how the data get stacked into the XY and IJ buffers, the read side is how the data is passed to the GPRs. The IJ information is packed in the IJ buffer 4 quads at a time or two clocks. The sequencer allows at any given time as many as four quads to interpolate a parameter. They all have to come from the same primitive. Then the sequencer controls the write mask to the GPRs to write the valid data in.

# 3. Instruction Store

There is going to be only one instruction store for the whole chip. It will contain 4096 instructions of 96 bits each.

It is likely to be a 1 port memory; we use 1 clock to load the ALU instruction, 1 clocks to load the Fetch instruction, 1 clock to load 2 control flow instructions and 1 clock to write instructions.

The instruction store is loaded by the CP thru the register mapped registers.

The VS\_BASE and PS\_BASE context registers are used to specify for each context where its shader is in the instruction memory.

For the Real time commands the story is quite the same but for some small differences. There are no wrap-around points for real time so the driver must be careful not to overwrite regular shader data. The shared code (shared subroutines) uses the same path as real time.

#### 4. Sequencer Instructions

All control flow instructions and move instructions are handled by the sequencer only. The ALUs will perform NOPs during this time (MOV PV,PV, PS,PS) if they have nothing else to do.

# 5. Constant Stores

#### 5.1 Memory organizations

A likely size for the ALU constant store is 1024x128 bits. The read BW from the ALU constant store is 128 bits/clock and the write bandwidth is 32 bits/clock (directed by the CP bus size not by memory ports).

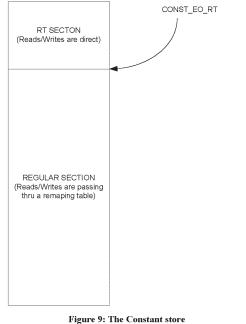

The maximum logical size of the constant store for a given shader is 256 constants. Or 512 for the pixel/vertex shader pair. The size of the re-mapping table is 128 lines (each line addresses 4 constants). The write granularity is 4 constants or 512 bits. It takes 16 clocks to write the four constants. Real time requires 256 lines in the physical memory (this is physically register mapped).

The texture state is also kept in a similar memory. The size of this memory is 320x96 bits (128 texture states for regular mode, 32 states for RT). The memory thus holds 128 texture states (192 bits per state). The logical size exposes 32 different states total, which are going to be shared between the pixel and the vertex shader. The size of the re-mapping table to for the texture state memory is 32 lines (each line addresses 1 texture state lines in the real memory). The CP write granularity is 1 texture state lines (or 192 bits). The driver sends 512 bits but the CP ignores the top 320 bits. It thus takes 6 clocks to write the texture state. Real time requires 32 lines in the physical memory (this is physically register mapped).

The control flow constant memory doesn't sit behind a renaming table. It is register mapped and thus the driver must reload its content each time there is a change in the control flow constants. Its size is 320\*32 because it must hold 8 copies of the 32 dwords of control flow constants and the loop construct constants must be aligned.

The constant re-mapping tables for texture state and ALU constants are logically register mapped for regular mode and physically register mapped for RT operation.

Exhibit 2035.docR400\_Sequencer.doc 73669 Bytes\*\*\* © ATI Confidential. Reference Copyright Notice on Cover Page © \*\*\*

AMD1044\_0257724

ATI Ex. 2109 IPR2023-00922 Page 14 of 326

| ORIGINATE DATE     | EDIT DATE           | DOCUMENT-REV. NUM. | PAGE     |

|--------------------|---------------------|--------------------|----------|

| 24 September, 2001 | 4 September, 201514 | GEN-CXXXXX-REVA    | 15 of 51 |

# 5.2 Management of the Control Flow Constants

The control flow constants are register mapped, thus the CP writes to the according register to set the constant, the SQ decodes the address and writes to the block pointed by its current base pointer (CF\_WR\_BASE). On the read side, one level of indirection is used. A register (SQ\_CONTEXT\_MISC.CF\_RD\_BASE) keeps the current base pointer to the control flow block. This register is copied whenever there is a state change. Should the CP write to CF after the state change, the base register is updated with the (current pointer number +1)% number of states. This way, if the CP doesn't write to CF the state is going to use the previous CF constants.

# 5.3 Management of the re-mapping tables

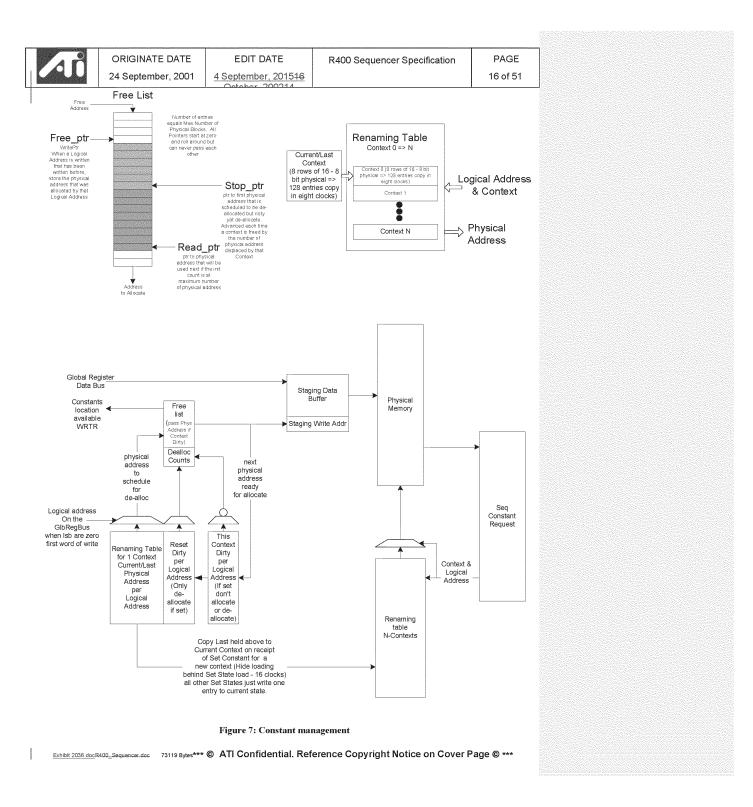

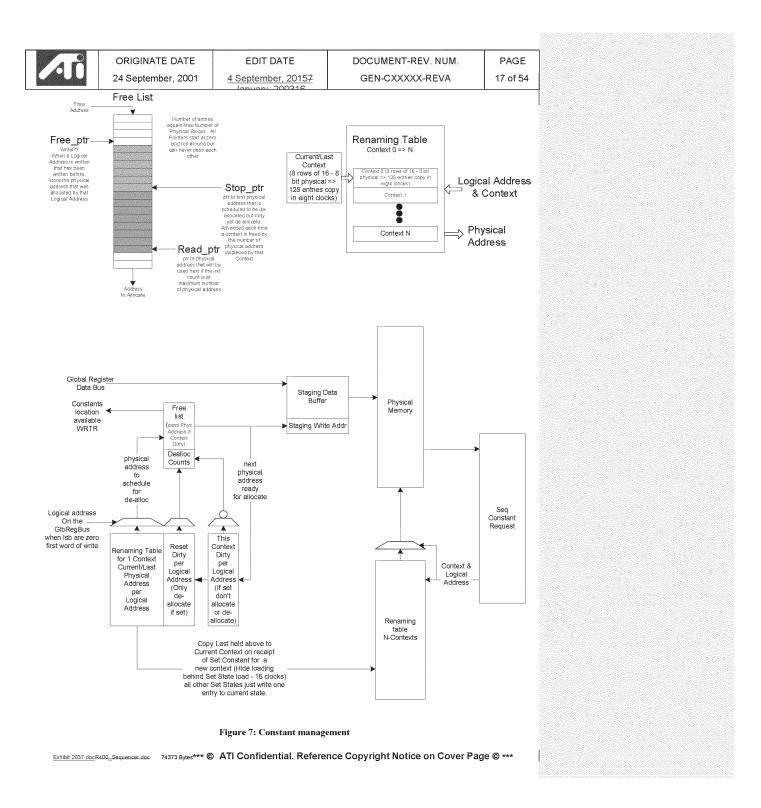

#### 5.3.1 R400 Constant management

The sequencer is responsible to manage two re-mapping tables (one for the constant store and one for the texture state). On a state change (by the driver), the sequencer will broadside copy the contents of its re-mapping tables to a new one. We have 8 different re-mapping tables we can use concurrently.

The constant memory update will be incremental, the driver only need to update the constants that actually changed between the two state changes.

For this model to work in its simplest form, the requirement is that the physical memory MUST be at least twice as large as the logical address space + the space allocated for Real Time. In our case, since the logical address space is 512 and the reserved RT space can be up to 256 entries, the memory must be of sizes 1280 and above. Similarly the size of the texture store must be of 32\*2+32 = 96 entries and above.

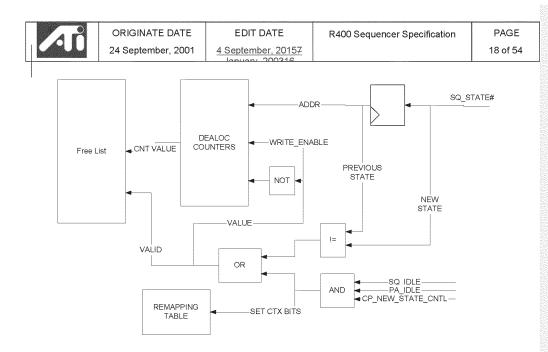

#### 5.3.2 Proposal for R400LE constant management

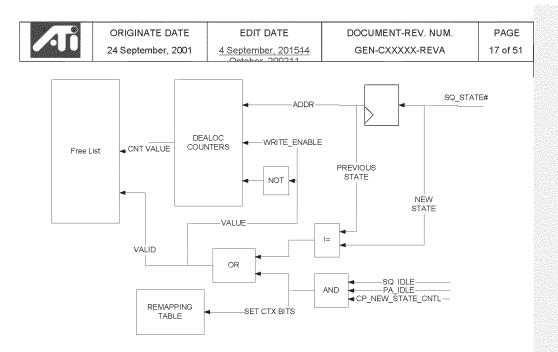

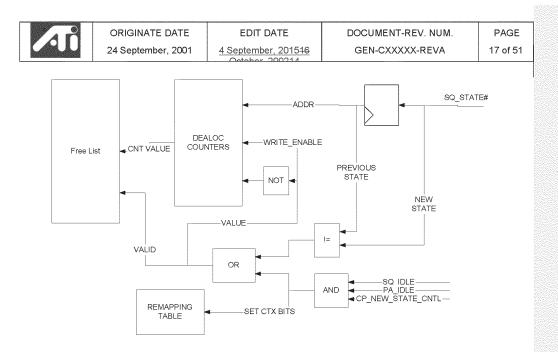

To make this scheme work with only 512+256 = 768 entries, upon reception of a CONTROL packet of state + 1, the sequencer would check for SQ\_IDLE and PA\_IDLE and if both are idle will erase the content of state to replace it with the new state (this is depicted in <u>Figure 8: De-allocation mechanismFigure 8: De-allocation mechanismFigure 8: De-allocation mechanismFigure 8: De-allocation mechanismFigure 8: De-allocation content of 0 is written to the corresponding de-allocation counter location so that when the SQ is going to report a state change, nothing will be de-allocated upon the first report.</u>

The second path sets all context dirty bits that were used in the current state to 1 (thus allowing the new state to reuse these physical addresses if needed).

Exhibit 2035. docR400\_Sequencer.doc 73569 Bytes\*\*\* © ATI Confidential. Reference Copyright Notice on Cover Page © \*\*\*

AMD1044\_0257725

ATI Ex. 2109 IPR2023-00922 Page 15 of 326

ATI Ex. 2109 IPR2023-00922 Page 16 of 326

Figure 8: De-allocation mechanism for R400LE

#### 5.3.3 Dirty bits

Two sets of dirty bits will be maintained per logical address. The first one will be set to zero on reset and set when the logical address is addressed. The second one will be set to zero whenever a new context is written and set for each address written while in this context. The reset dirty is not set, then writing to that logical address will not require de-allocation of whatever address stored in the renaming table. If it is set and the context dirty is not set, then the physical address is necessary to store the incoming data. If they are both set, then the data will be written into the physical address held in the renaming for the current logical address. No de-allocation or allocation takes place. This will happen when the driver does a set constant twice to the same logical address between context changes. NOTE: It is important to detect and prevent this, failure to do it will allow multiple writes to allocate all physical memory and thus hang because a context will not fit for rendering to start and thus free up space.

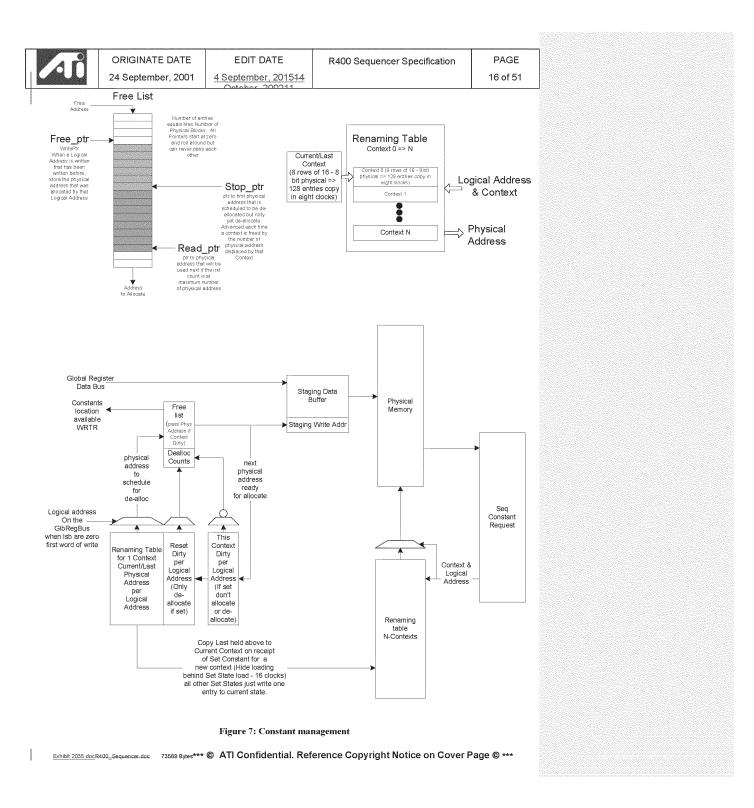

#### 5.3.4 Free List Block

A free list block that would consist of a counter (called the IFC or Initial Free Counter) that would reset to zero and incremented every time a chunk of physical memory is used until they have all been used once. This counter would be checked each time a physical block is needed, and if the original ones have not been used up, us a new one, else check the free list for an available physical block address. The count is the physical address for when getting a chunk from the counter.

Storage of a free list big enough to store all physical block addresses.

Maintain three pointers for the free list that are reset to zero. The first one we will call write\_ptr. This pointer will identify the next location to write the physical address of a block to be de-allocated. Note: we can never free more physical memory locations than we have. Once recording address the pointer will be incremented to walk the free list like a ring.

The second pointer will be called stop\_ptr. The stop\_ptr pointer will be advanced by the number of address chunks de-allocates when a context finishes. The address between the stop\_ptr and write\_ptr cannot be reused because they are still in use. But as soon as the context using then is dismissed the stop\_ptr will be advanced.

The third pointer will be called read\_ptr. This pointer will point will point to the next address that can be used for allocation as long as the read\_ptr does not equal the stop\_ptr and the IFC is at its maximum count.

Exhibit 2035.docR400\_Sequencer.doc 73699 Bytes\*\*\* © ATI Confidential. Reference Copyright Notice on Cover Page © \*\*\*

AMD1044\_0257727

ATI Ex. 2109 IPR2023-00922 Page 17 of 326

| ORIGINATE DATE     | EDIT DATE           | R400 Sequencer Specification | PAGE     |

|--------------------|---------------------|------------------------------|----------|

| 24 September, 2001 | 4 September, 201514 |                              | 18 of 51 |

#### 5.3.5 De-allocate Block

This block will maintain a free physical address block count for each context. While in current context, a count shall be maintained specifying how many blocks were written into the free list at the write\_ptr pointer. This count will be reset upon reset or when this context is active on the back and different than the previous context. It is actually a count of blocks in the previous context that will no longer be used. This count will be used to advance the write\_ptr pointer to make available the set of physical blocks in one clock.

#### 5.3.6 Operation of Incremental model

The basic operation of the model would start with the write\_ptr, stop\_ptr, read\_ptr pointers in the free list set to zero and the free list counter is set to zero. Also all the dirty bits and the previous context will be initialized to zero. When the first set constants happen, the reset dirty bit will not be set, so we will allocate a physical location from the free list counter is not at the max value. The data will be written into physical address zero. Both the additional copy of the renaming table and the context zeros of the big renaming table will be updated for the logical address that was written by set start with physical address of 0. This process will be repeated for any logical address that are not dirty until the context changes. If a logical address is hit that has its dirty bits set while in the same context, both dirty bits would be set, so the new data will be over-written to the last physical address assigned for this logical address. When the first draw command of the context is detected, the previous context stored in the additional renaming table will be copied to the larger renaming table in the current (new) context location. Then the set constant logical address it replaced in the renaming table would be entered at the write\_ptr pointer location on the free list and the write\_ptr will be incremented. The de-allocation counter for the previous context (eight) will be incremented. This as set states come in for this context one of the following will happen:

- 1.) No dirty bits are set for the logical address being updated. A line will be allocated of the free-list counter or the free list at read\_ptr pointer if read\_ptr != to stop\_ptr .

- 2.) Reset dirty set and Context dirty not set. A new physical address is allocated, the physical address in the renaming table is put on the free list at write\_ptr and it is incremented along with the de-allocate counter for the last context.

- 3.) Context dirty is set then the data will be written into the physical address specified by the logical address.

This process will continue as long as set states arrive. This block will provide backpressure to the CP whenever he has not free list entries available (counter at max and stop\_ptr == read\_ptr). The command stream will keep a count of contexts of constants in use and prevent more than max constants contexts from being sent.

Whenever a draw packet arrives, the content of the re-mapping table is written to the correct re-mapping table for the context number. Also if the next context uses less constants than the current one all exceeding lines are moved to the free list to be de-allocated later. This happens in parallel with the writing of the re-mapping table to the correct memory.

Now preferable when the constant context leaves the last ALU clause it will be sent to this block and compared with the previous context that left. (Init to zero) If they differ than the older context will no longer be referenced and thus can be de-allocated in the physical memory. This is accomplished by adding the number of blocks freed this context to the stop\_ptr pointer. This will make all the physical addresses used by this context available to the read\_ptr allocate pointer for future allocation.

This device allows representation of multiple contexts of constants data with N copies of the logical address space. It also allows the second context to be represented as the first set plus some new additional data by just storing the delta's. It allows memory to be efficiently used and when the constants updates are small it can store multiple context. However, if the updates are large, less contexts will be stored and potentially performance will be degraded. Although it will still perform as well as a ring could in this case.

# 5.4 Constant Store Indexing

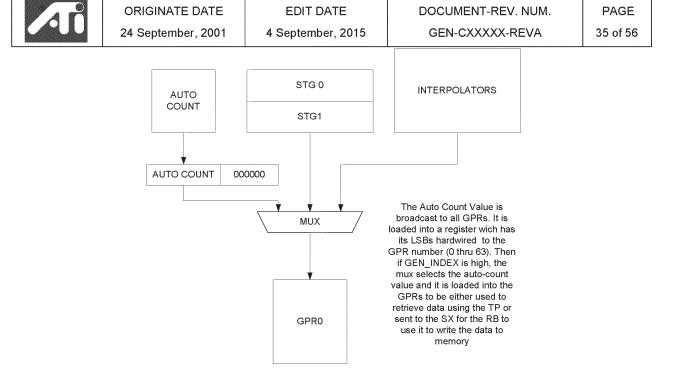

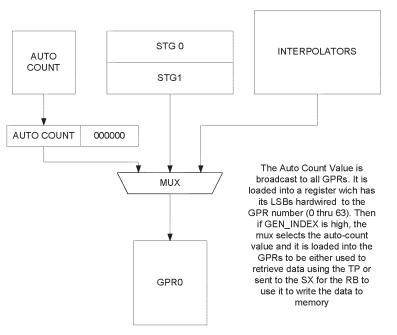

In order to do constant store indexing, the sequencer must be loaded first with the indexes (that come from the GPRs). There are 144 wires from the exit of the SP to the sequencer (9 bits pointers x 16 vertexes/clock). Since the data must pass thru the Shader pipe for the float to fixed conversion, there is a latency of 4 clocks (1 instruction)

Exhibit 2035.docR400\_Sequencer.doc 73569 Bytes\*\*\* © ATI Confidential. Reference Copyright Notice on Cover Page © \*\*\*

AMD1044\_0257728

ATI Ex. 2109 IPR2023-00922 Page 18 of 326

| ORIGINATE DATE     | EDIT DATE           | DOCUMENT-REV. NUM. | PAGE     |

|--------------------|---------------------|--------------------|----------|

| 24 September, 2001 | 4 September, 201514 | GEN-CXXXXX-REVA    | 19 of 51 |

between the time the sequencer is loaded and the time one can index into the constant store. The assembly will look like this

MOVA R1.X,R2.X // Loads the sequencer with the content of R2.X, also copies the content of R2.X into R1.X NOP // latency of the float to fixed conversion ADD R3,R4,C0[R2.X]// Uses the state from the sequencer to add R4 to C0[R2.X] into R3

Note that we don't really care about what is in the brackets because we use the state from the MOVA instruction. R2.X is just written again for the sake of simplicity and coherency.

The storage needed in the sequencer in order to support this feature is 2\*64\*9 bits = 1152 bits.

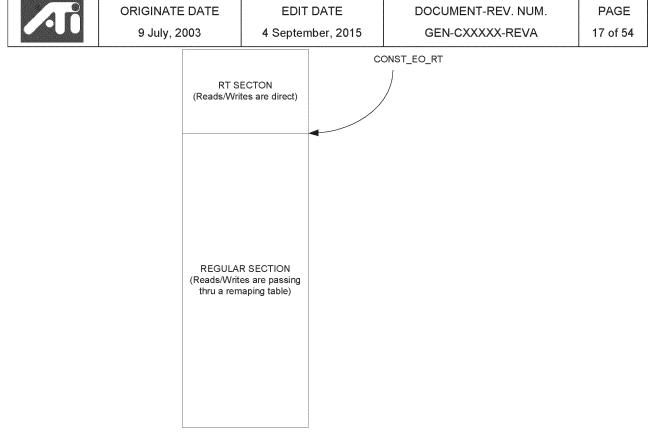

# 5.5 Real Time Commands

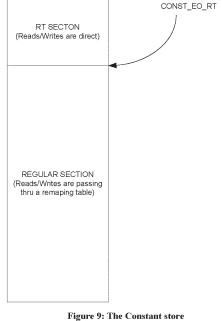

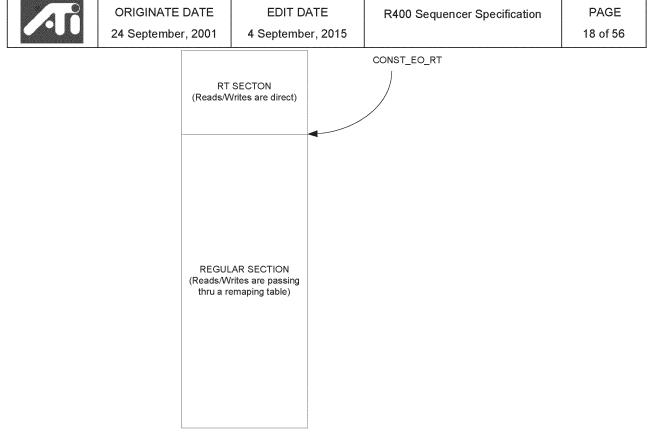

The real time commands constants are written by the CP using the register mapped registers allocated for RT. It works is the same way than when dealing with regular constant loads BUT in this case the CP is not sending a logical address but rather a physical address and the reads are not passing thru the re-mapping table but are directly read from the memory. The boundary between the two zones is defined by the CONST\_EO\_RT control register. Similarly, for the fetch state, the boundary between the two zones is defined by the TSTATE\_EO\_RT control register.

# 5.6 Constant Waterfalling

In order to have a reasonable performance in the case of constant store indexing using the address register, we are going to have the possibility of using the physical memory port for read only. This way we can read 1 constant per clock and thus have a worst-case waterfall mode of 1 vertex per clock. There is a small synchronization issue related with this as we need for the SQ to make sure that the constants where actually written to memory (not only sent to the sequencer) before it can allow the first vector of pixels or vertices of the state to go thru the ALUs. To do so, the sequencer keeps 8 bits (one per render state) and sets the bits whenever the last render state is written to memory and clears the bit whenever a state is freed.

Exhibit 2035.docR400\_Sequencer.doc 73569 Bytes\*\*\* © ATI Confidential. Reference Copyright Notice on Cover Page © \*\*\*

AMD1044 0257729

ATI Ex. 2109 IPR2023-00922 Page 19 of 326

| ORIGINATE DATE     | EDIT DATE           | R400 Sequencer Specification | PAGE     |

|--------------------|---------------------|------------------------------|----------|

| 24 September, 2001 | 4 September, 201514 |                              | 20 of 51 |

6. Looping and Branches

Loops and branches are planned to be supported and will have to be dealt with at the sequencer level. We plan on supporting constant loops and branches using a control program.

# 6.1 The controlling state.

The R400 controling state consists of:

Boolean[256:0] Loop\_count[7:0][31:0] Loop\_Start[7:0][31:0] Loop\_Step[7:0][31:0]

That is 256 Booleans and 32 loops.

We have a stack of 4 elements for nested calls of subroutines and 4 loop counters to allow for nested loops.

This state is available on a per shader program basis.

#### 6.2 The Control Flow Program

We'd like to be able to code up a program of the form:

| 1: | Loop   |          |

|----|--------|----------|

| 2: | Exec   | TexFetch |

| 3: |        | TexFetch |

| 4: |        | ALU      |

| 5: |        | ALU      |

| 6: |        | TexFetch |

| 7: | End Lo | ор       |

| 8: | ALU Ex | port     |

But realize that 3: may be dependent on 2: and 4: is almost certainly dependent on 2: and 3:. Without clausing, these dependencies need to be expressed in the Control Flow instructions. Additionally, without separate 'texture clauses' and 'ALU clauses' we need to know which instructions to dispatch to the Texture Unit and which to the ALU unit. This information will be encapsulated in the flow control instructions.

Each control flow instruction will contain 2 bits of information for each (non-control flow) instruction: a) ALU or Texture

b) Serialize Execution

(b) would force the thread to stop execution at this point (before the instruction is executed) and wait until all textures have been fetched. Given the allocation of reserved bits, this would mean that the count of an 'Exec' instruction would be limited to about 8 (non-control-flow) instructions. If more than this were needed, a second Exec (with the same conditions) would be issued.

Another function that relies upon 'clauses' is allocation and order of execution. We need to assure that pixels and vertices are exported in the correct order (even if not all execution is ordered) and that space in the output buffers are allocated in order. Additionally data can't be exported until space is allocated. A new control flow instruction:

#### Alloc <buffer select -- position, parameter, pixel or vertex memory. And the size required>.

would be created to mark where such allocation needs to be done. To assure allocation is done in order, the actual allocation for a given thread can not be performed unless the equivalent allocation for all previous threads is already completed. The implementation would also assure that execution of instruction(s) following the serialization due to the Alloc will occur in order -- at least until the next serialization or change from ALU to Texture. In most cases this will allow the exports to occur without any further synchronization. Only 'final' allocations or position allocations are

Exhibit 2035.docR400\_Sequencer.doc 73569 Bytes\*\*\* C ATI Confidential. Reference Copyright Notice on Cover Page C \*\*\*

AMD1044\_0257730

ATI Ex. 2109 IPR2023-00922 Page 20 of 326

|         | ORIGINATE DATE     | EDIT DATE           | DOCUMENT-REV. NUM. | PAGE     | The Association of the Associati |

|---------|--------------------|---------------------|--------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u></u> | 24 September, 2001 | 4 September, 201514 | GEN-CXXXXX-REVA    | 21 of 51 | Contraction of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

guaranteed to be ordered. Because strict ordering is required for pixels, parameters and positions, this implies only a single alloc for these structures. Vertex exports to memory do not require ordering during allocation and so multiple 'allocs' may be done.

#### 6.2.1 Control flow instructions table

Here is the revised control flow instruction set.

Note that whenever a field is marked as RESERVED, it is assumed that all the bits of the field are cleared (0).

| NOP   |            |          |       |  |  |  |  |

|-------|------------|----------|-------|--|--|--|--|

| 47 44 | 43         | 42 0     | 20000 |  |  |  |  |

| 0000  | Addressing | RESERVED | 10000 |  |  |  |  |

This is a regular NOP.

|       | Execute    |          |                                                   |       |              |  |  |  |  |  |  |

|-------|------------|----------|---------------------------------------------------|-------|--------------|--|--|--|--|--|--|

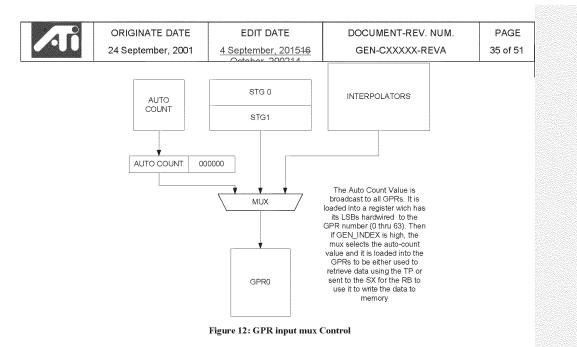

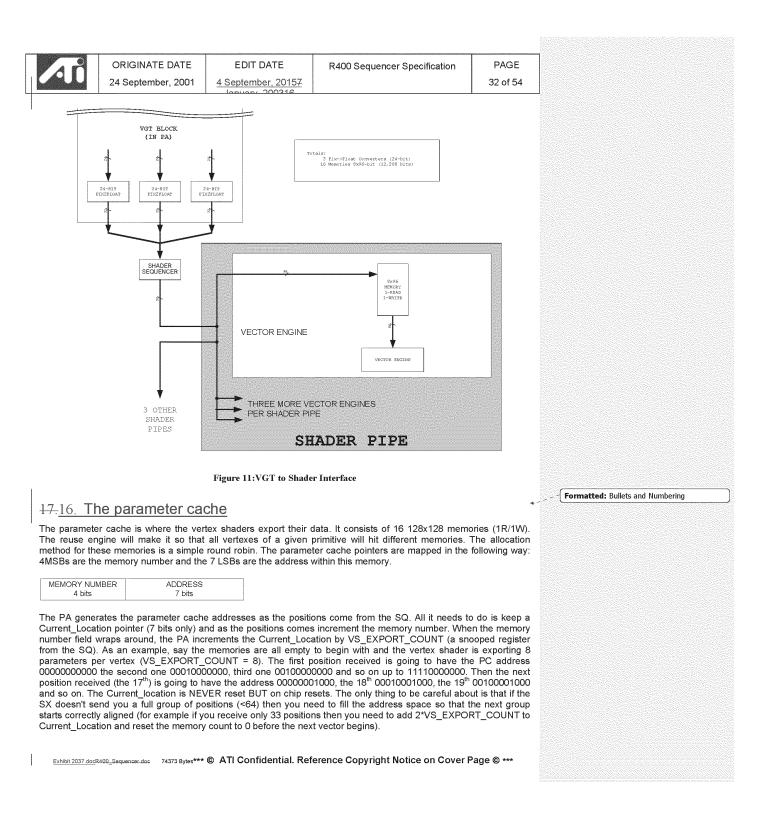

| 47 44 | 43         | 40 34    | 33 16                                             | 1512  | 11 0         |  |  |  |  |  |  |