| J. A |   |

|------|---|

|      | L |

|      |   |

EDIT DATE

4 September, 20152

DOCUMENT-REV. NUM. GEN-CXXXXX-REVA

PAGE 1 of 54

Author:

Laurent Lefebvre

| issue to: | Copy No |

|-----------|---------|

|           | 1       |

# **R400 Sequencer Specification**

# SQ

### Version 2.010

Overview: This is an architectural specification for the R400 Sequencer block (SEQ). It provides an overview of the required capabilities and expected uses of the block. It also describes the block interfaces, internal subblocks, and provides internal state diagrams.

**AUTOMATICALLY UPDATED FIELDS:**

Document Location: C:\perforce\r400\doc\_lib\design\blocks\sq\R400\_Sequencer.doc

Current Intranet Search Title: R400 Sequencer Specification

|           | APPROVALS      |  |  |  |  |  |  |

|-----------|----------------|--|--|--|--|--|--|

| Name/Dept | Signature/Date |  |  |  |  |  |  |

|           |                |  |  |  |  |  |  |

|           |                |  |  |  |  |  |  |

|           |                |  |  |  |  |  |  |

|           |                |  |  |  |  |  |  |

|           |                |  |  |  |  |  |  |

#### Remarks:

THIS DOCUMENT CONTAINS CONFIDENTIAL INFORMATION THAT COULD BE SUBSTANTIALLY DETRIMENTAL TO THE INTEREST OF ATI TECHNOLOGIES INC. THROUGH UNAUTHORIZED USE OR DISCLOSURE.

"Copyright 2001, ATI Technologies Inc. All rights reserved. The material in this document constitutes an unpublished work created in 2001. The use of this copyright notice is intended to provide notice that ATI owns a copyright in this unpublished work. The copyright notice is not an admission that publication has occurred. This work contains confidential, proprietary information and trade secrets of ATI. No part of this document may be used, reproduced, or transmitted in any form or by any means without the prior written permission of ATI Technologies Inc."

Exhibit 2029.docR400\_Sequencer.doc 73711 Bytes\*\*\* © ATI Confidential. Reference Copyright Notice on Cover Page © \*\*\*

ATI 2029 LG v. ATI IPR2015-00325

AMD1044\_0257395

EDIT DATE

4 September, 20152

R400 Sequencer Specification

PAGE 2 of 54

# Table Of Contents

| 1.                                      | OVERVIEW                                       | 97                       |

|-----------------------------------------|------------------------------------------------|--------------------------|

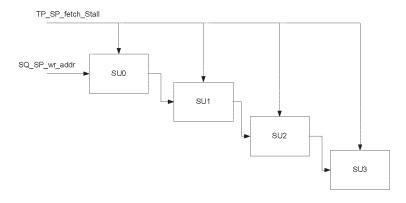

| 1.1                                     | Top Level Block Diagram                        | 119                      |

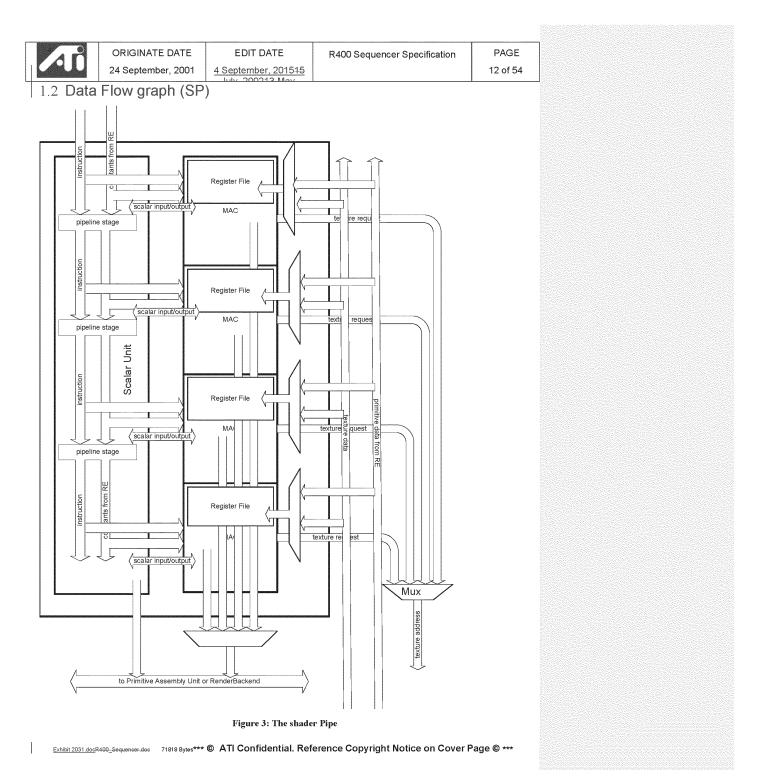

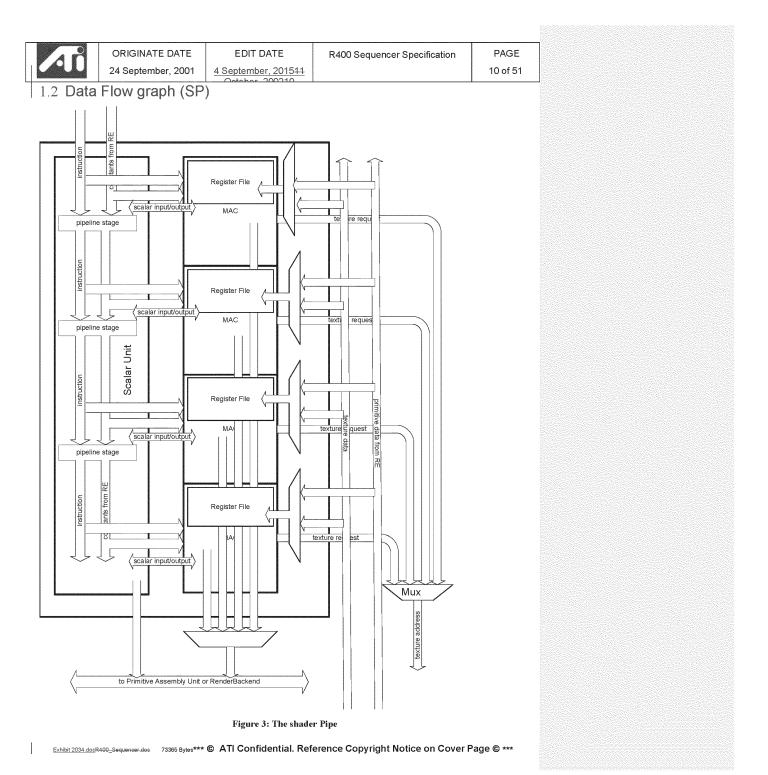

| 1.2                                     | Data Flow graph (SP)                           | . 1240                   |

| 1.3                                     | Control Graph                                  | 1311                     |

| 2.                                      | INTERPOLATED DATA BUS                          |                          |

| 3.                                      | INSTRUCTION STORE                              | <u>.1614</u>             |

| 4.                                      | SEQUENCER INSTRUCTIONS                         | .1614                    |

| 5                                       | CONSTANT STORES                                | <u>. 1614</u>            |

| 5.1                                     | Memory organizations.                          | <u>. 1614</u>            |

| 5.2                                     | Management of the Control Flow Constants       | <u>. 17<del>15</del></u> |

| 5.3                                     | Management of the re-mapping tables            | 1745                     |

| *************************************** | 3.1 R400 Constant management                   |                          |

| 5.3                                     | 3.2 Proposal for R400LE constant management    | 1745                     |

| 5.3                                     | 3.3 Dirty bits                                 | . 1947                   |

| 5.3                                     | 3.4 Free List Block                            | 1917                     |

| <u>5.3</u>                              | 3.5 De-allocate Block                          | .2048                    |

| 5.3                                     | 3.6 Operation of Incremental model             |                          |

| 5.4                                     | Constant Store Indexing.                       |                          |

| 5.5                                     | Real Time Commands.                            | .2149                    |

| 5.6                                     | Constant Waterfalling                          | 2119                     |

| <u>6.</u>                               | LOOPING AND BRANCHES                           | . 2220                   |

| 6.1                                     | The controlling state.                         | .2220                    |

| 6.2                                     | The Control Flow Program                       | <u>. 2220</u>            |

|                                         | 2.1 Control flow instructions table            |                          |

| 6.3                                     | Implementation                                 | 2422                     |

| 6.4                                     | Data dependant predicate instructions          | 2624                     |

| 6.5                                     | HW Detection of PV,PS                          | .2724                    |

| 6.6                                     | Register file indexing.                        |                          |

| 6.7                                     | Debugging the Shaders                          |                          |

| <u>6.</u>                               | 7.1 Method 1: Debugging registers              |                          |

|                                         | 7.2 Method 2: Exporting the values in the GPRs |                          |

| <u>7.</u>                               | PIXEL KILL MASK                                | <u>. 2826</u>            |

| 8.                                      | MULTIPASS VERTEX SHADERS (HOS)                 |                          |

| 9.                                      | REGISTER FILE ALLOCATION.                      |                          |

| <u>10.</u>                              | FETCH ARBITRATION                              |                          |

| 11.                                     | ALU ARBITRATION                                | .2927                    |

| <u>12.</u>                              | HANDLING STALLS                                | .3028                    |

| 13.                                     | CONTENT OF THE RESERVATION STATION FIFOS       | 3028                     |

| <u>14.</u>                              | THE OUTPUT FILE                                |                          |

| 15.                                     | IJ FORMAT                                      | 3028                     |

| 15.1                                    | Interpolation of constant attributes           |                          |

| 16.                                     | STAGING REGISTERS                              | .3129                    |

|                                         | ORIGINATE DATE                          | EDIT DATE                                    | DOCUMENT-REV. NUM.                      | PAGE                                    |

|-----------------------------------------|-----------------------------------------|----------------------------------------------|-----------------------------------------|-----------------------------------------|

| <i>-</i>                                | 24 September, 2001                      | 4 September, 20152                           | GEN-CXXXXX-REVA                         | 3 of 54                                 |

| 17. THE P                               | ARAMETER CACHE.                         | May 700710 April 7007                        | *************************************** | 3330                                    |

| 17.1 Expo                               | ort restrictions                        |                                              |                                         | 3430                                    |

| 17.1.1                                  | Pixel exports:                          |                                              | *************************************** | 34 <u>30</u>                            |

| 17.1.2                                  | Vertex exports:                         |                                              |                                         | 3430                                    |

| 17.1.3                                  | Pass thru exports:                      |                                              |                                         | 3430                                    |

|                                         |                                         |                                              |                                         |                                         |

|                                         |                                         |                                              |                                         |                                         |

|                                         |                                         |                                              |                                         |                                         |

| 19. SPEC                                | IAL INTERPOLATION                       | MODES                                        | *************                           | 3534                                    |

| 19.1 Rea                                | time commands                           |                                              | *************************************** | 3531                                    |

|                                         |                                         |                                              |                                         |                                         |

|                                         |                                         |                                              |                                         |                                         |

|                                         |                                         |                                              |                                         | 1                                       |

| 19.3.2                                  |                                         |                                              |                                         |                                         |

| 20. STATI                               | E MANAGEMENT                            | * * * * * * * * * * * * * * * * * * * *      |                                         | 3633                                    |

|                                         |                                         |                                              | *************************************** |                                         |

| 21.1 Vert                               | ex indexes imports                      | *********************                        |                                         | 3733                                    |

|                                         |                                         |                                              | *************************************** |                                         |

| 22.1 Conf                               | trol                                    |                                              |                                         | 3734                                    |

|                                         |                                         |                                              | *************************************** |                                         |

|                                         |                                         |                                              |                                         |                                         |

|                                         |                                         |                                              |                                         |                                         |

| *************************************** |                                         |                                              |                                         |                                         |

|                                         |                                         |                                              |                                         |                                         |

|                                         |                                         |                                              |                                         |                                         |

| 24.2.1                                  |                                         | ***************************************      |                                         |                                         |

| 24.2.2                                  |                                         |                                              |                                         |                                         |

| 24.2.3                                  | *************************************** | ***************************************      |                                         |                                         |

| 24.2.4                                  |                                         |                                              |                                         |                                         |

|                                         |                                         |                                              |                                         |                                         |

| 24.2.5                                  |                                         |                                              |                                         |                                         |

| 24.2.6                                  |                                         |                                              |                                         |                                         |

| 24.2.7                                  | **************************************  |                                              |                                         | *************************************** |

| 24.2.8                                  |                                         |                                              |                                         |                                         |

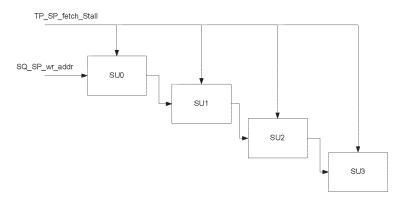

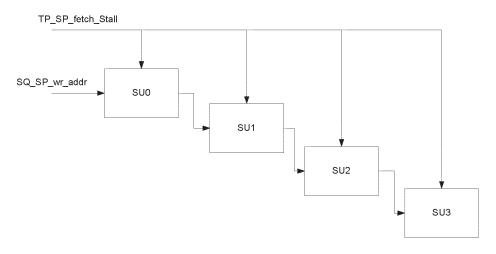

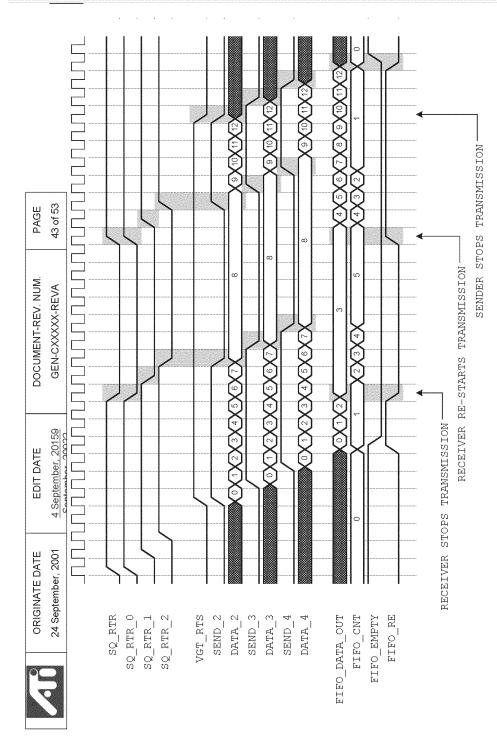

| 24.2.9                                  | TP to SQ: Texture sta                   | all                                          |                                         | 4642                                    |

| 24.2.10                                 | SQ to SP: Texture sta                   | <u> </u>                                     |                                         | 4742                                    |

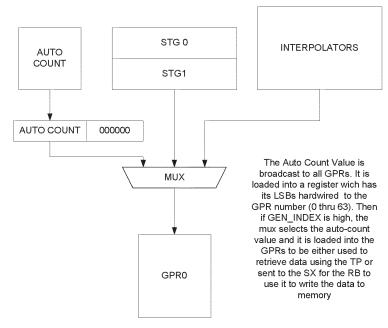

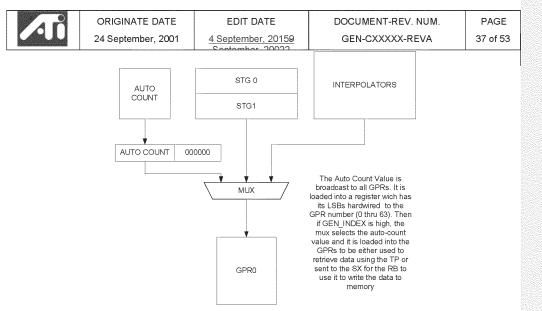

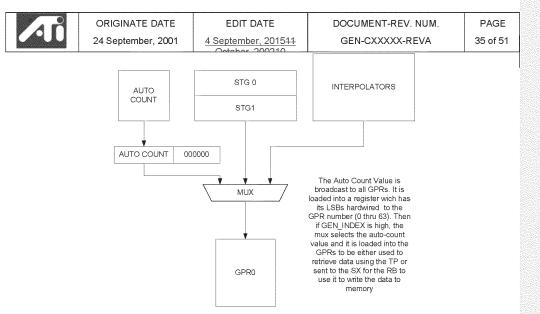

| 24.2.11                                 | SQ to SP: GPR and a                     | uto counter                                  |                                         | 4743                                    |

| 24.2.12                                 |                                         |                                              |                                         | 1                                       |

| 24.2.13                                 |                                         |                                              | Set                                     |                                         |

| 24.2.14                                 |                                         |                                              |                                         |                                         |

| hand 3 , hand , 2, "V                   | OG TO OF A. CONSTAINT                   | J. J. G. |                                         |                                         |

| A PA     | ORIGINATE DATE         | EDIT DATE             | R400 Sequencer Specification | PAGE    |

|----------|------------------------|-----------------------|------------------------------|---------|

| 6,000    | 24 September, 2001     | 4 September, 20152    |                              | 6 of 54 |

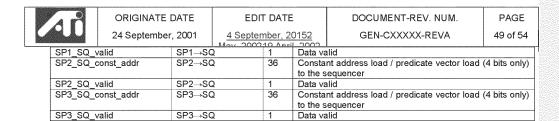

| 27.2.13  | SP to SQ: Constant     | address load/ Predica | ate Set                      | 44      |

| 27.2.14  | SQ to SPx: constant    | : broadcast           |                              | 45      |

| 27.2.15  | SP0 to SQ: Kill vector | or load               |                              | 45      |

| 27.2.16  | SQ to CP: RBBM bu      | ls                    |                              | 45      |

| 27.2.17  | CP to SQ: RBBM bu      | IS                    |                              | 45      |

| 27.2.18  | SQ to CP: State rep    | ort                   |                              | 45      |

| 28.—OPEN | HSSUES                 | ******************    |                              | 50      |

**EDIT DATE** 4 September, 20152 DOCUMENT-REV. NUM. GEN-CXXXXX-REVA

PAGE 7 of 54

# Revision Changes:

Rev 0.1 (Laurent Lefebvre) Date: May 7, 2001

Rev 0.2 (Laurent Lefebvre) Date: July 9, 2001 Rev 0.3 (Laurent Lefebvre) Date: August 6, 2001 Rev 0.4 (Laurent Lefebvre) Date: August 24, 2001

Rev 0.5 (Laurent Lefebvre) Date: September 7, 2001 Rev 0.6 (Laurent Lefebvre) Date: September 24, 2001 Rev 0.7 (Laurent Lefebvre) Date: October 5, 2001

Rev 0.8 (Laurent Lefebvre) Date: October 8, 2001 Rev 0.9 (Laurent Lefebvre) Date: October 17, 2001

Rev 1.0 (Laurent Lefebvre) Date: October 19, 2001 Rev 1.1 (Laurent Lefebyre) Date: October 26, 2001

Rev 1.2 (Laurent Lefebvre) Date: November 16, 2001 Rev 1.3 (Laurent Lefebvre) Date: November 26, 2001 Rev 1.4 (Laurent Lefebvre) Date: December 6, 2001

Rev 1.5 (Laurent Lefebvre) Date: December 11, 2001

Rev 16 (Laurent Lefebyre) Date: January 7, 2002

Rev 1.7 (Laurent Lefebvre) Date: February 4, 2002 Rev 1.8 (Laurent Lefebvre) Date: March 4, 2002

Rev 1.9 (Laurent Lefebvre) Date: March 18, 2002 Rev 1.10 (Laurent Lefebvre) Date: March 25, 2002 Rev 1.11 (Laurent Lefebvre) Date: April 19, 2002 Rev 2.0 (Laurent Lefebvre) Date: April 19, 2002

First draft.

Changed the interfaces to reflect the changes in the SP. Added some details in the arbitration section. Reviewed the Sequencer spec after the meeting on August 3, 2001.

Added the dynamic allocation method for register file and an example (written in part by Vic) of the flow of pixels/vertices in the sequencer. Added timing diagrams (Vic)

Changed the spec to reflect the new R400 architecture. Added interfaces.

Added constant store management, instruction store management, control flow management and data dependant predication.

Changed the control flow method to be more flexible. Also updated the external interfaces.

Incorporated changes made in the 10/18/01 control flow meeting. Added a NOP instruction, removed the conditional\_execute\_or\_jump. Added debug registers.

Refined interfaces to RB. Added state registers.

Added SEQ-SP0 interfaces. Changed delta precision. Changed VGT→SP0 interface. Debug Methods added.

Interfaces greatly refined. Cleaned up the spec.

Added the different interpolation modes.

Added the auto incrementing counters. Changed the VGT-SQ interface. Added content on constant management. Updated GPRs.

Removed from the spec all interfaces that weren't directly tied to the SQ. Added explanations on constant management. Added synchronization fields and explanation.

Added more details on the staging register. Added detail about the parameter caches. Changed the call instruction to a Conditionnal\_call instruction. Added details on constant management and updated the diagram.

Added Real Time parameter control in the SX interface. Updated the control flow section.

New interfaces to the SX block. Added the end of clause modifier, removed the end of clause instructions.

Rearangement of the CF instruction bits in order to ensure byte alignement.

Updated the interfaces and added a section on exporting rules.

Added CP state report interface. Last version of the spec with the old control flow scheme

New control flow scheme

EDIT DATE

4 September, 20152

R400 Sequencer Specification

PAGE 8 of 54

Rev 2.01 (Laurent Lefebvre) Date: May 2, 2002 Changed slightly the control flow instructions to allow force jumps and calls.

EDIT DATE

4 September, 20152

DOCUMENT-REV. NUM. GEN-CXXXXX-REVA PAGE 9 of 54

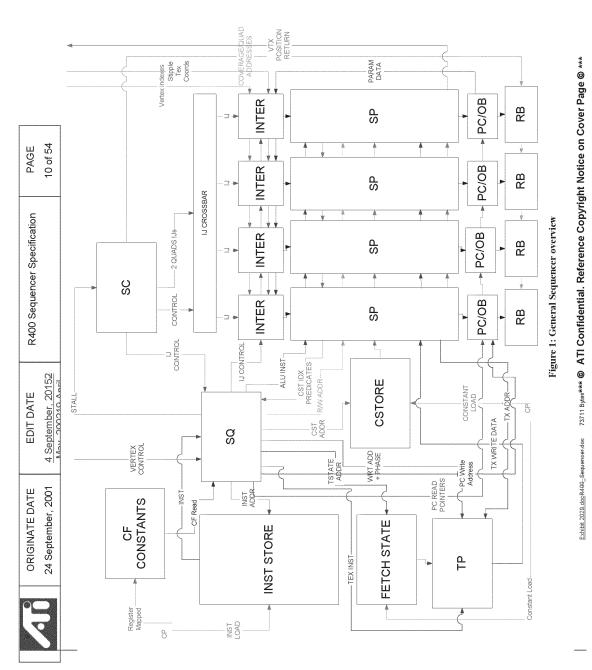

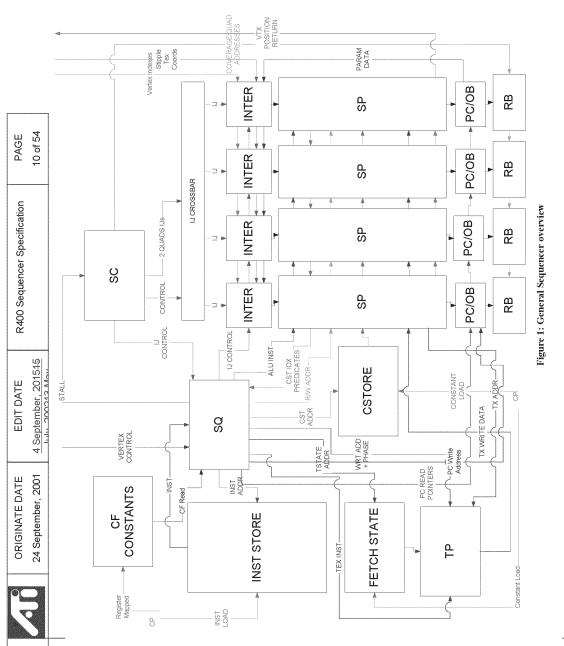

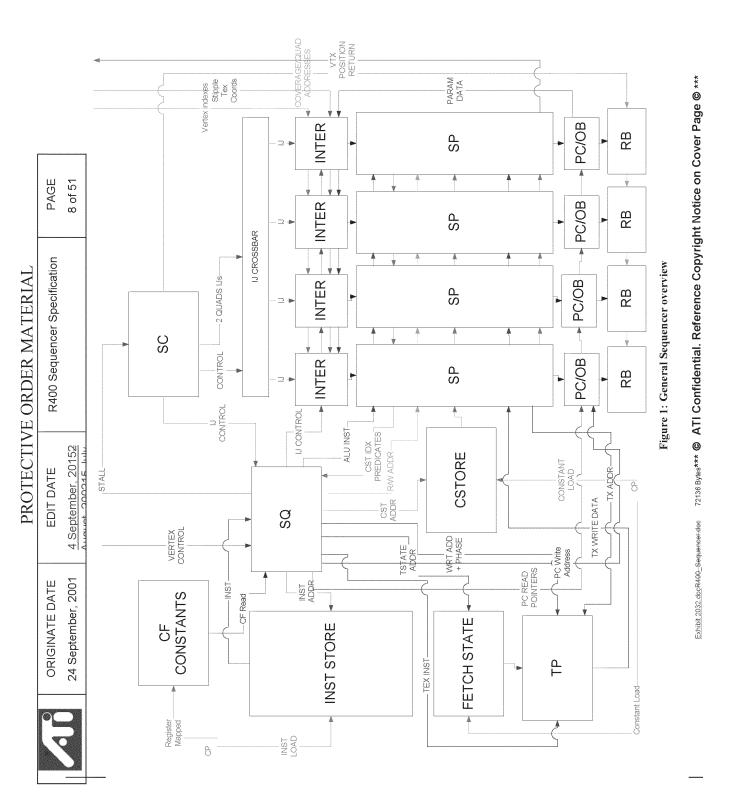

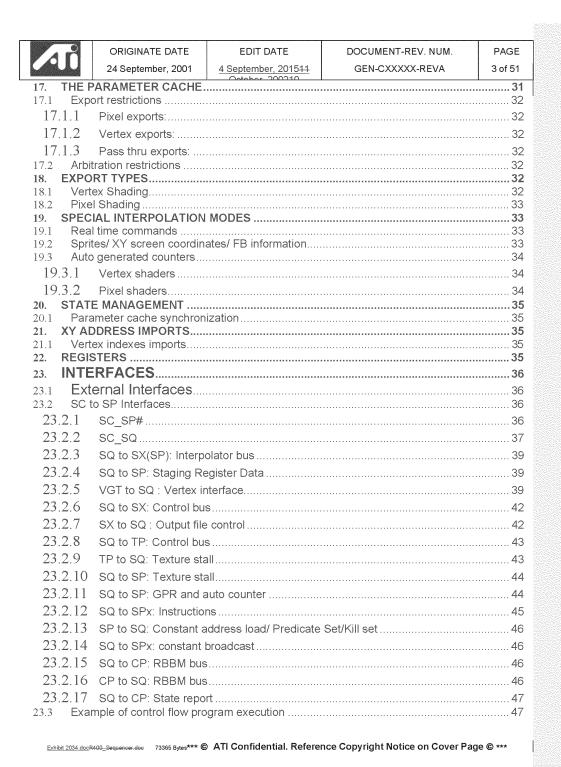

### 1. Overview

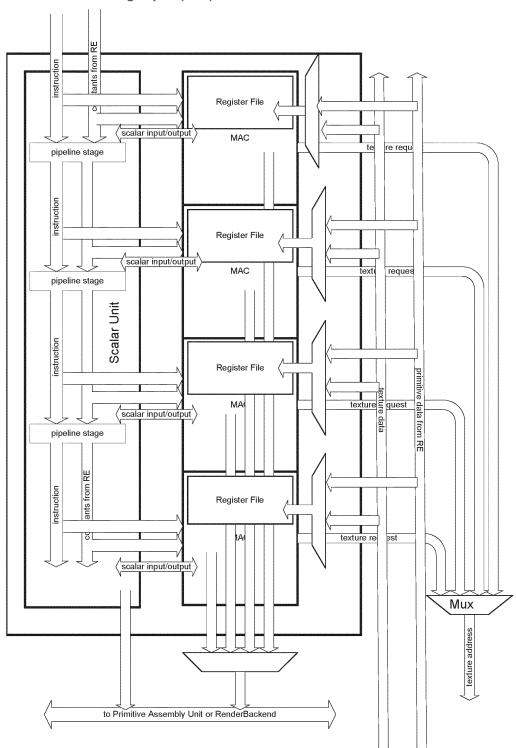

The sequencer chooses two ALU threads and a fetch hread to execute, and executes all of the instructions in a block before looking for a new clause of the same type. Two ALU threads are executed interleaved to hide the ALU latency. The arbitrator will give priority to older threads. There are two separate reservation stations, one for pixel vectors and one for vertices vectors. This way a pixel can pass a vertex and a vertex can pass a pixel.

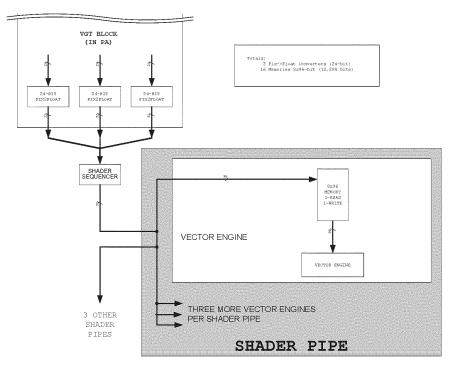

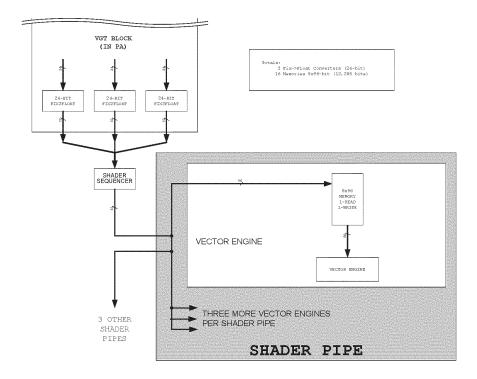

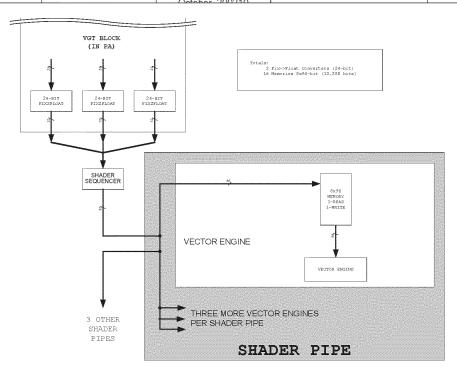

To support the shader pipe the sequencer also contains the shader instruction cache, constant store, control flow constants and texture state. The four shader pipes also execute the same instruction thus there is only one sequencer for the whole chip.

The sequencer first arbitrates between vectors of 64 vertices that arrive directly from primitive assembly and vectors of 16 quads (64 pixels) that are generated in the scan converter.

The vertex or pixel program specifies how many GPRs it needs to execute. The sequencer will not start the next vector until the needed space is available in the GPRs.

AMD1044\_0257404

# September, 20152

DOCUMENT-REV. NUM.

GEN-CXXXXX-REVA

PAGE 11 of 54

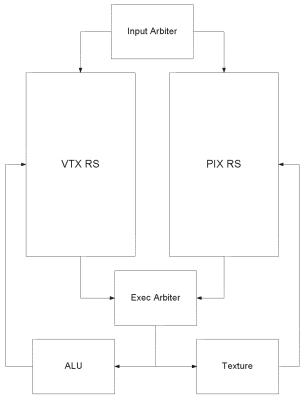

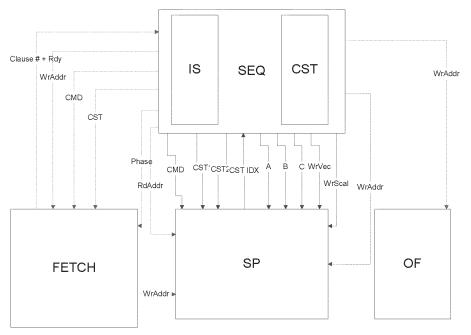

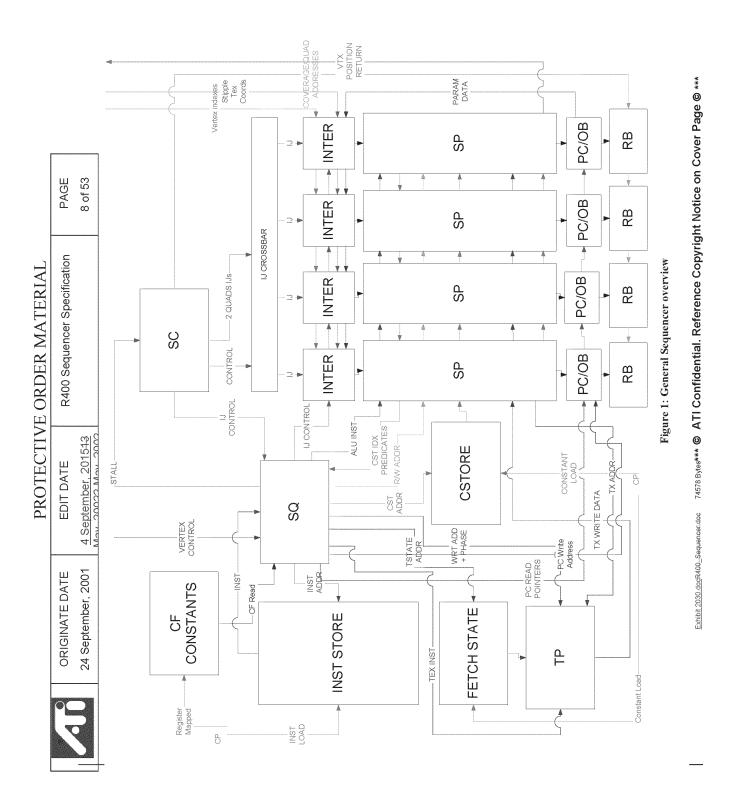

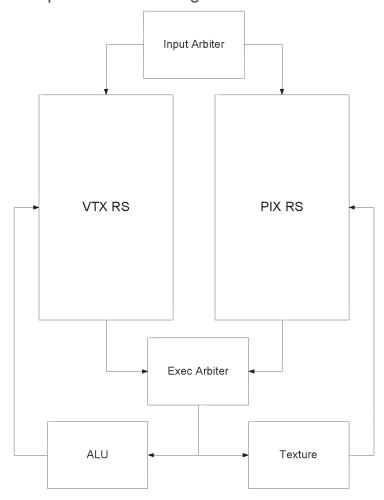

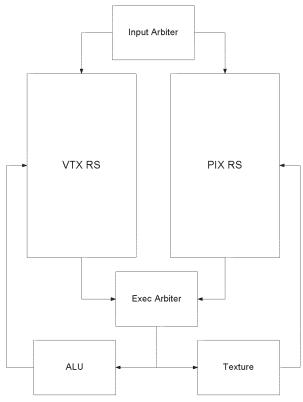

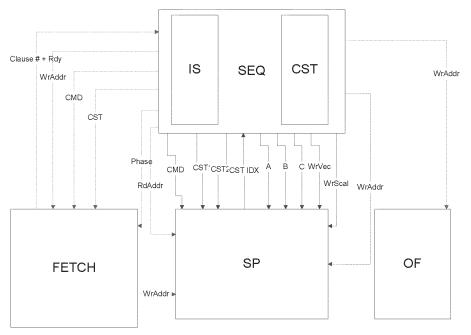

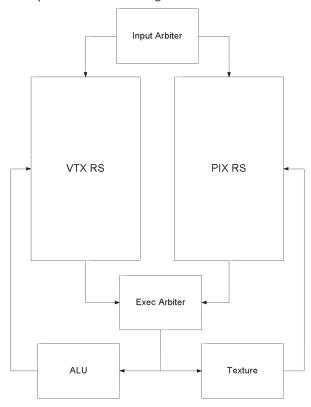

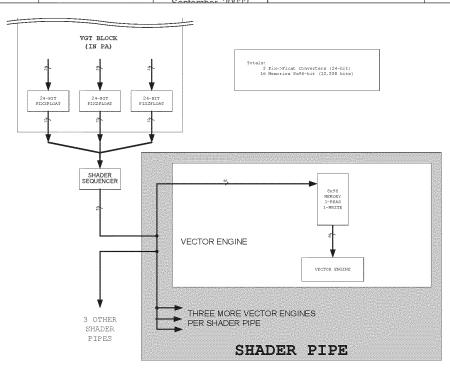

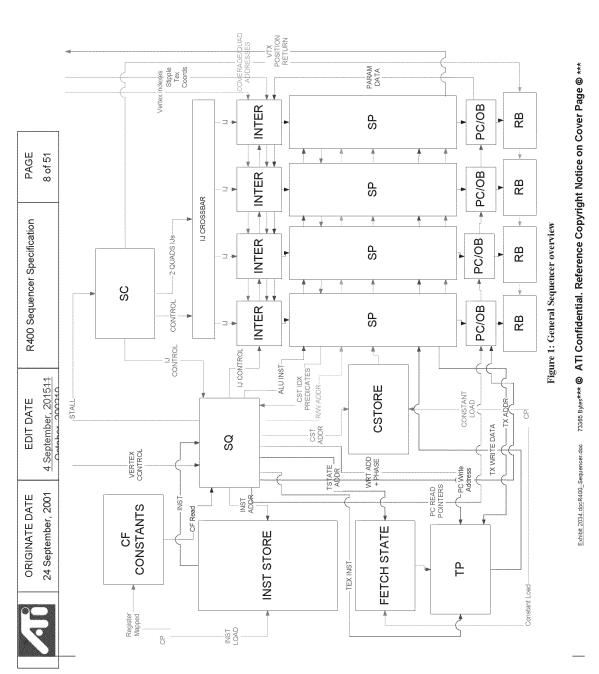

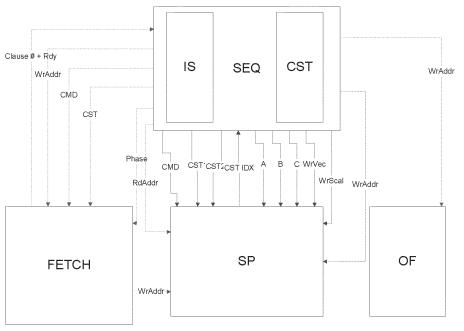

# 1.1 Top Level Block Diagram

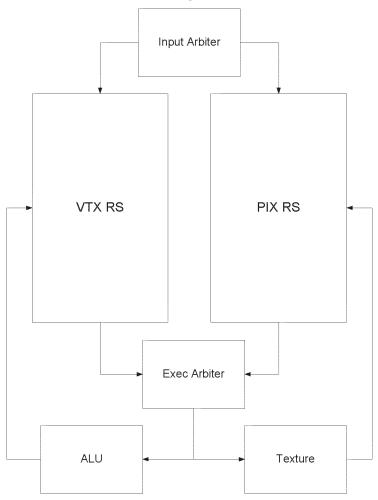

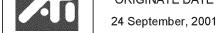

Figure 2: Reservation stations and arbiters

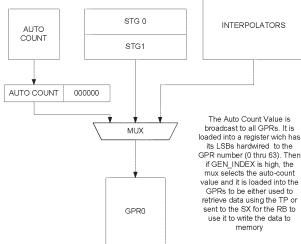

Under this new scheme, the sequencer (SQ) will only use one global state management machine per vector type (pixel, vertex) that we call the reservation station (RS).

EDIT DATE

4 September, 20152

DOCUMENT-REV. NUM. GEN-CXXXXX-REVA PAGE 13 of 54

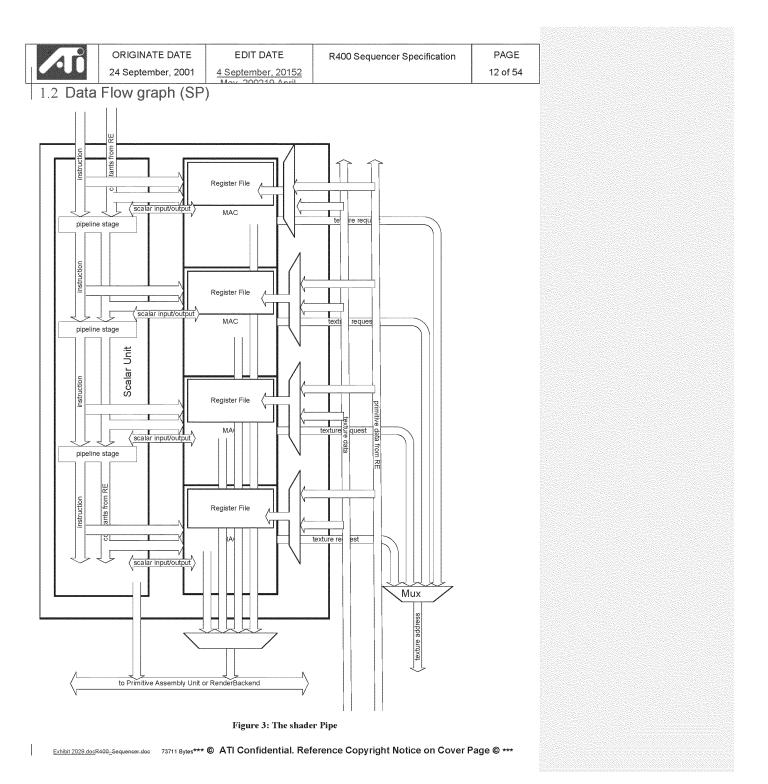

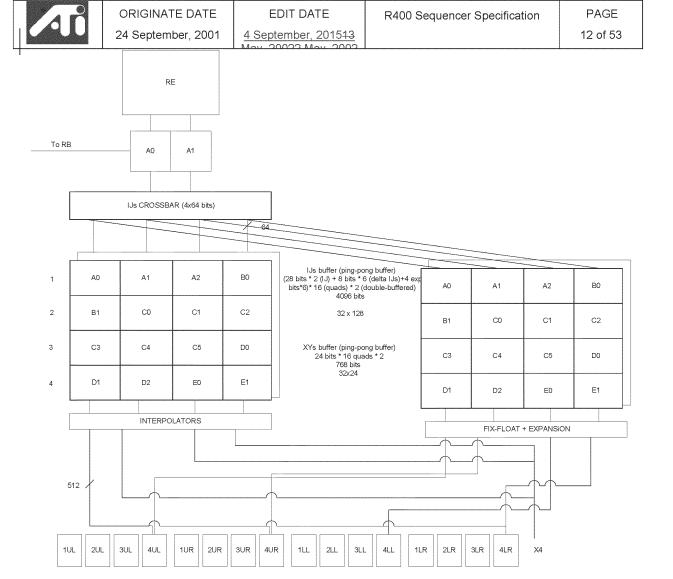

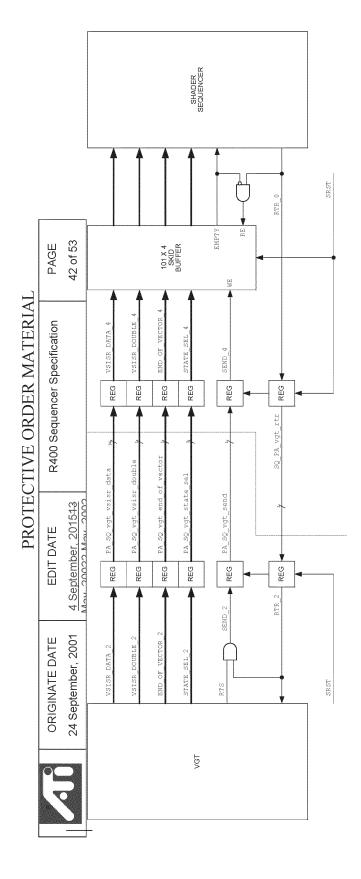

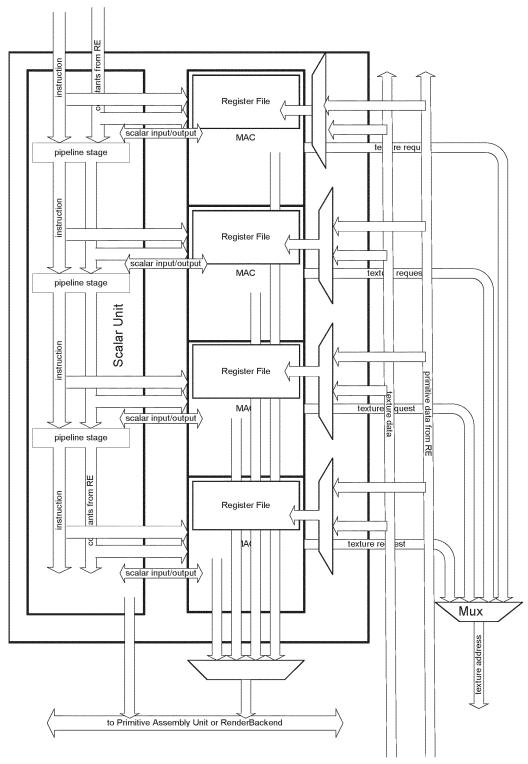

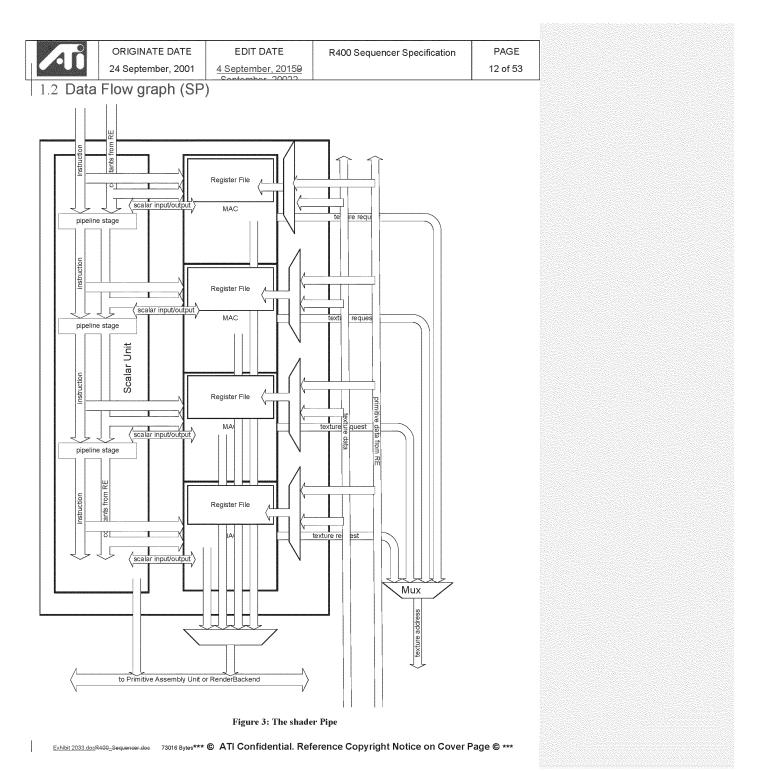

The gray area represents blocks that are replicated 4 times per shader pipe (16 times on the overall chip).

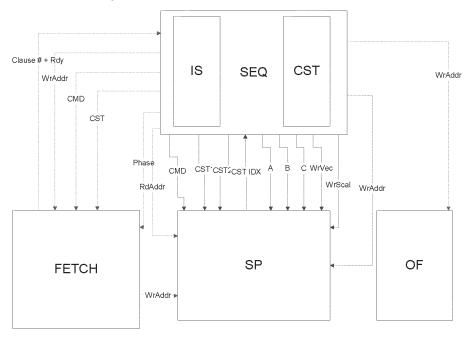

# 1.3 Control Graph

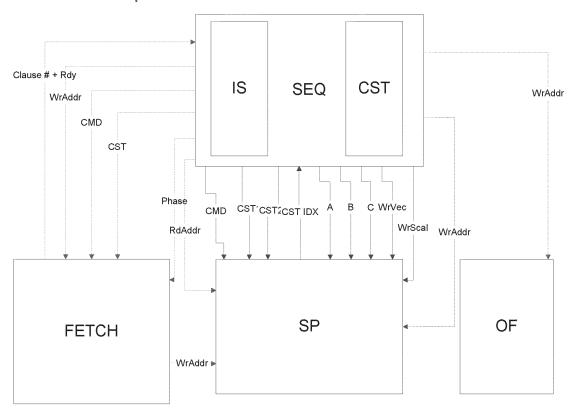

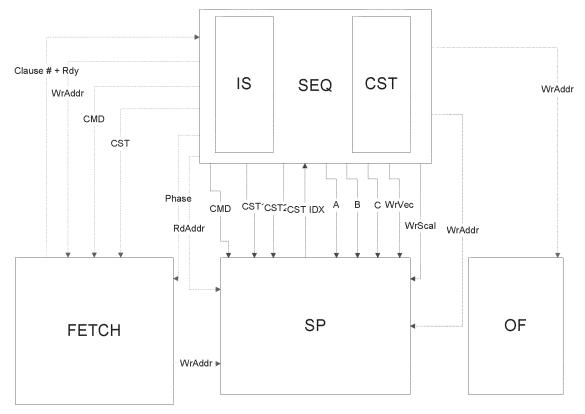

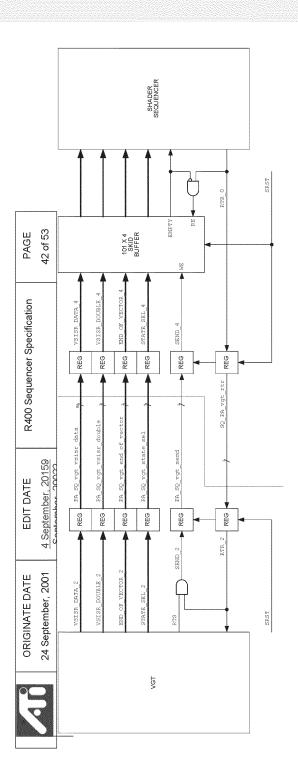

Figure 4: Sequencer Control interfaces

In green is represented the Fetch control interface, in red the ALU control interface, in blue the Interpolated/Vector control interface and in purple is the output file control interface.

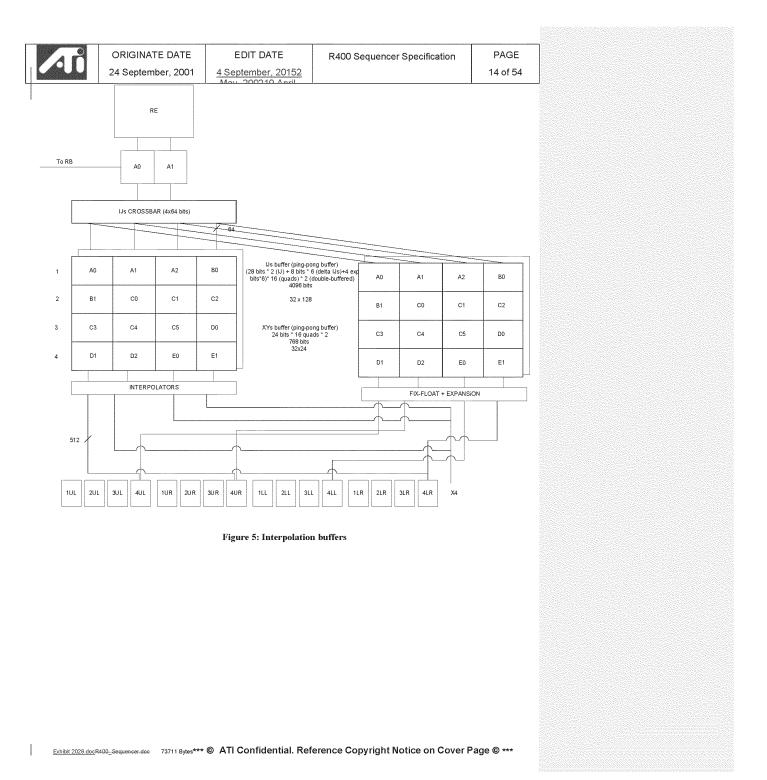

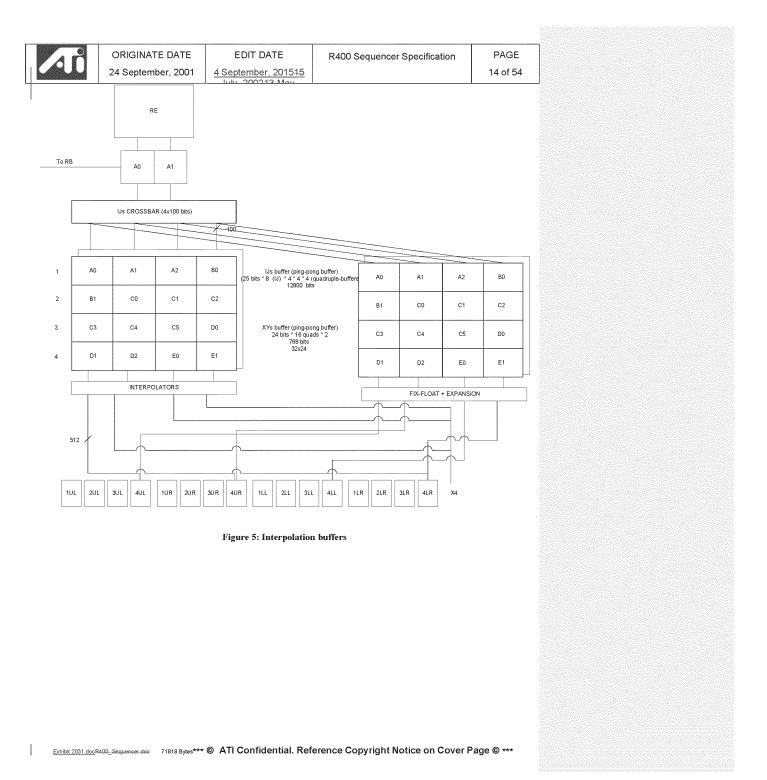

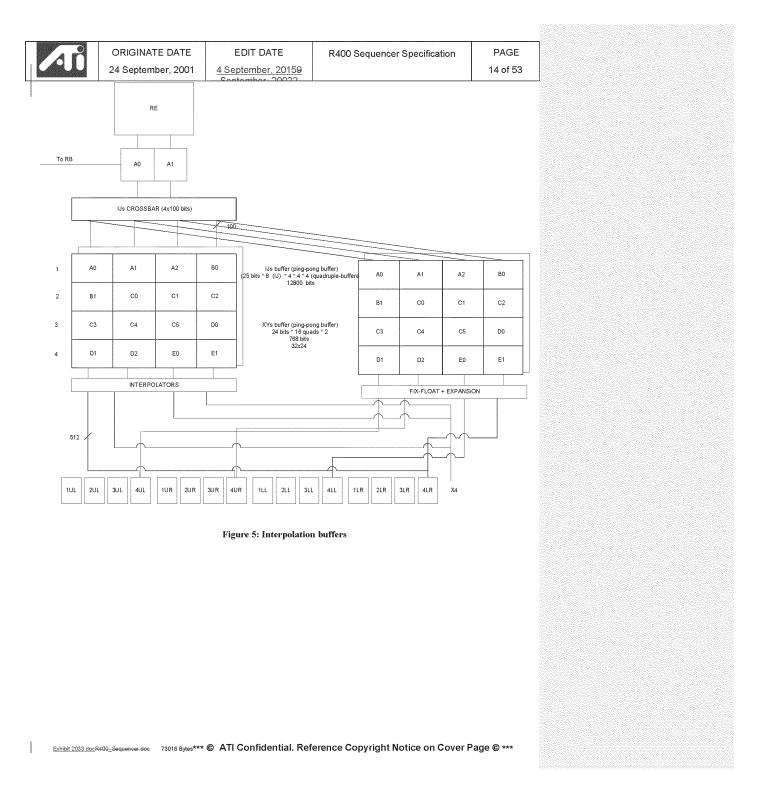

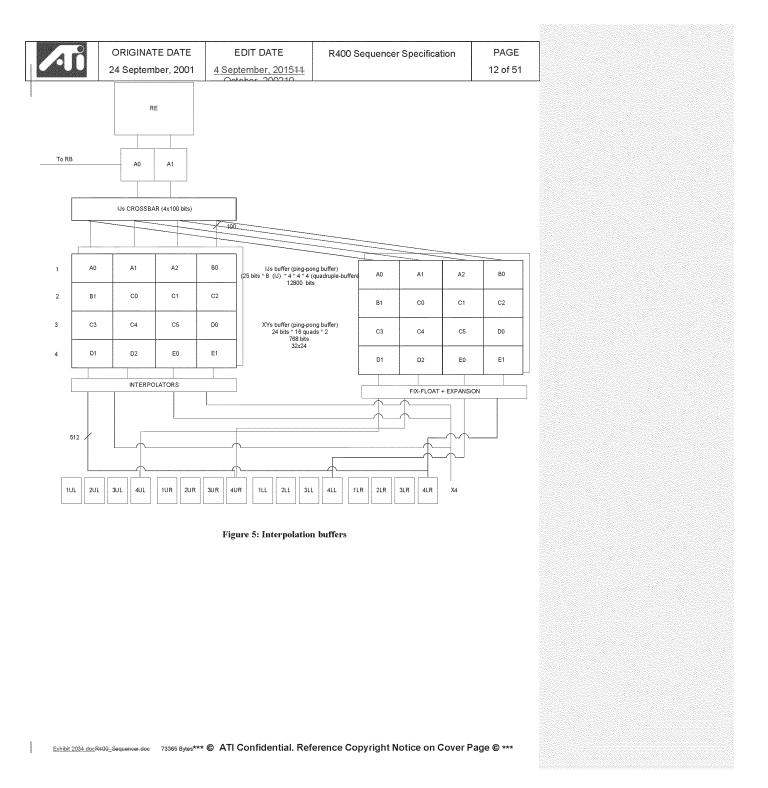

# 2. Interpolated data bus

The interpolators contain an IJ buffer to pack the information as much as possible before writing it to the register file.

≿ ?

S o

× √-4

<u>გ</u> ←

**≯** % <del>≠</del>

SP 2

**Y**5

Ą

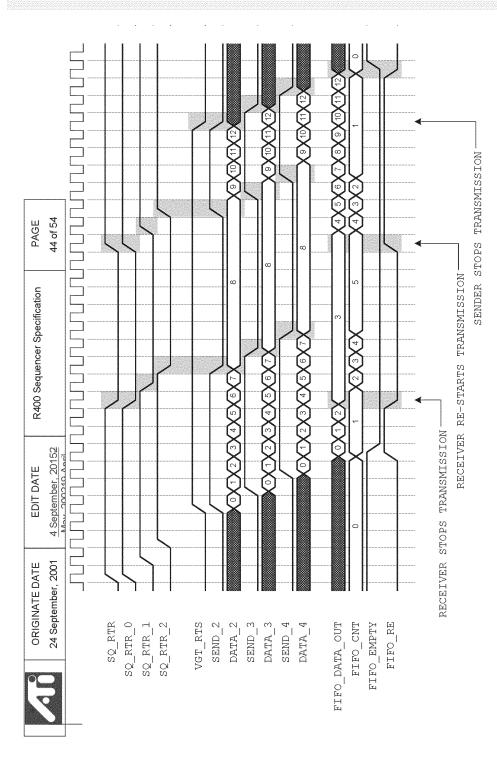

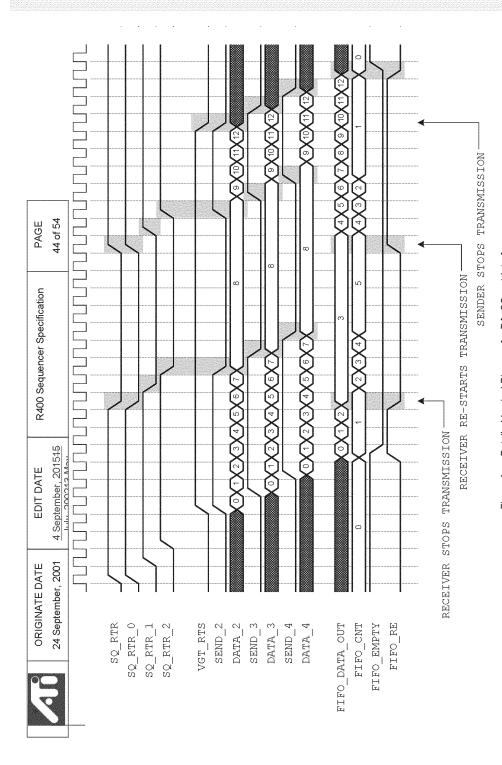

Figure 6: Interpolation timing diagram

V V 44-60-47 63

3 % <

> 4 4

ω

8

8

8

Щ

8

$^{\circ}$

8

XY XY 44- 60-47 63

3 % ₹

\$ 42 €

S S

2

73711 Bytes\*\*\* @ ATI Confidential. Reference Copyright Notice on Cover Page @ \*\*\*

**EDIT DATE**

R400 Sequencer Specification

PAGE

24 September, 2001

4 September, 20152

16 of 54

Above is an example of a tile the sequencer might receive from the SC. The write side is how the data get stacked into the XY and IJ buffers, the read side is how the data is passed to the GPRs. The IJ information is packed in the IJ buffer 4 quads at a time or two clocks. The sequencer allows at any given time as many as four quads to interpolate a parameter. They all have to come from the same primitive. Then the sequencer controls the write mask to the GPRs to write the valid data in.

# 3. Instruction Store

There is going to be only one instruction store for the whole chip. It will contain 4096 instructions of 96 bits each.

It is likely to be a 1 port memory; we use 1 clock to load the ALU instruction, 1 clocks to load the Fetch instruction, 1 clock to load 2 control flow instructions and 1 clock to write instructions.

The instruction store is loaded by the CP thru the register mapped registers.

The VS\_BASE and PS\_BASE context registers are used to specify for each context where its shader is in the instruction memory.

For the Real time commands the story is quite the same but for some small differences. There are no wrap-around points for real time so the driver must be careful not to overwrite regular shader data. The shared code (shared subroutines) uses the same path as real time.

#### 4. Sequencer Instructions

All control flow instructions and move instructions are handled by the sequencer only. The ALUs will perform NOPs during this time (MOV PV,PV, PS,PS) if they have nothing else to do.

# 5. Constant Stores

# 5.1 Memory organizations

A likely size for the ALU constant store is 1024x128 bits. The read BW from the ALU constant store is 128 bits/clock and the write bandwidth is 32 bits/clock (directed by the CP bus size not by memory ports).

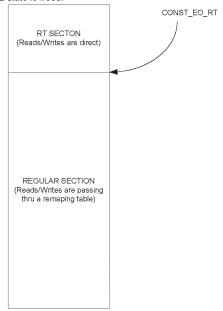

The maximum logical size of the constant store for a given shader is 256 constants. Or 512 for the pixel/vertex shader pair. The size of the re-mapping table is 128 lines (each line addresses 4 constants). The write granularity is 4 constants or 512 bits. It takes 16 clocks to write the four constants. Real time requires 256 lines in the physical memory (this is physically register mapped).

The texture state is also kept in a similar memory. The size of this memory is 320x96 bits (128 texture states for regular mode, 32 states for RT). The memory thus holds 128 texture states (192 bits per state). The logical size exposes 32 different states total, which are going to be shared between the pixel and the vertex shader. The size of the re-mapping table to for the texture state memory is 32 lines (each line addresses 1 texture state lines in the real memory). The CP write granularity is 1 texture state lines (or 192 bits). The driver sends 512 bits but the CP ignores the top 320 bits. It thus takes 6 clocks to write the texture state. Real time requires 32 lines in the physical memory (this is physically register mapped).

The control flow constant memory doesn't sit behind a renaming table. It is register mapped and thus the driver must reload its content each time there is a change in the control flow constants. Its size is 320\*32 because it must hold 8 copies of the 32 dwords of control flow constants and the loop construct constants must be aligned.

The constant re-mapping tables for texture state and ALU constants are logically register mapped for regular mode and physically register mapped for RT operation.

EDIT DATE

4 September, 20152

DOCUMENT-REV. NUM. GEN-CXXXXX-REVA PAGE 17 of 54

# 5.2 Management of the Control Flow Constants

The control flow constants are register mapped, thus the CP writes to the according register to set the constant, the SQ decodes the address and writes to the block pointed by its current base pointer (CF\_WR\_BASE). On the read side, one level of indirection is used. A register (SQ\_CONTEXT\_MISC.CF\_RD\_BASE) keeps the current base pointer to the control flow block. This register is copied whenever there is a state change. Should the CP write to CF after the state change, the base register is updated with the (current pointer number +1)% number of states. This way, if the CP doesn't write to CF the state is going to use the previous CF constants.

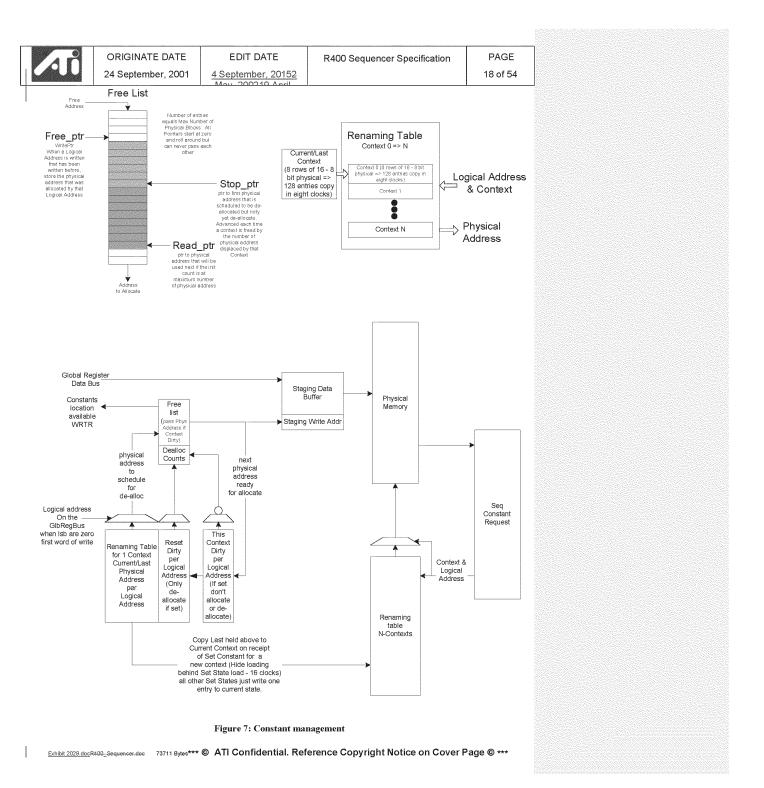

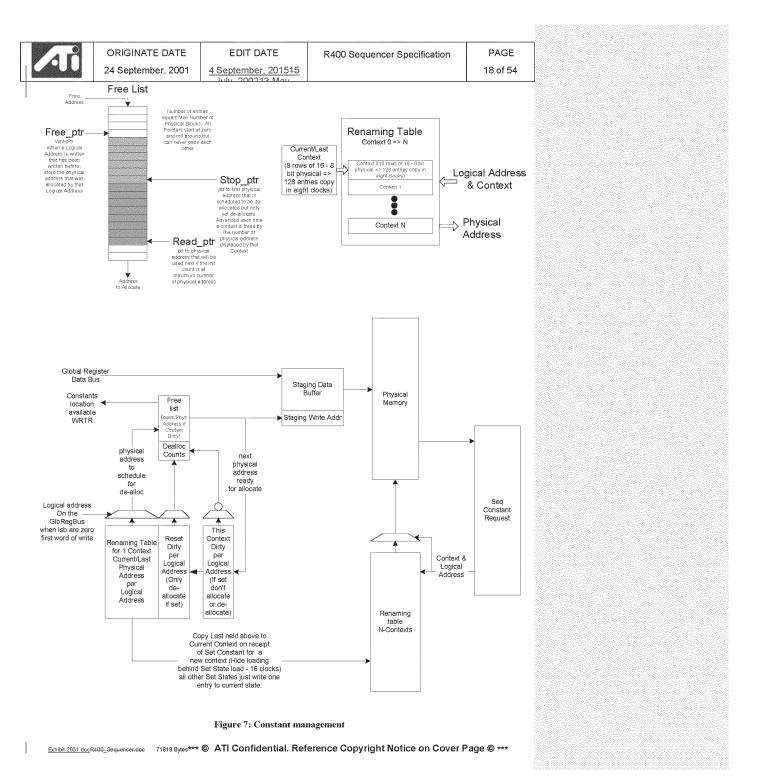

### 5.3 Management of the re-mapping tables

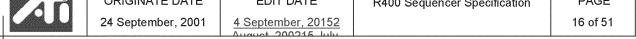

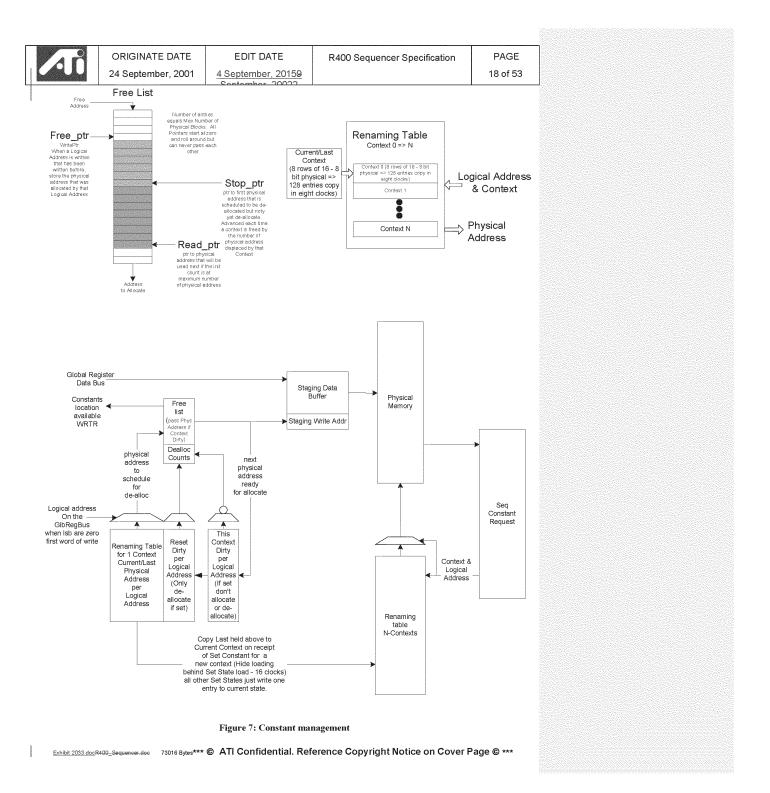

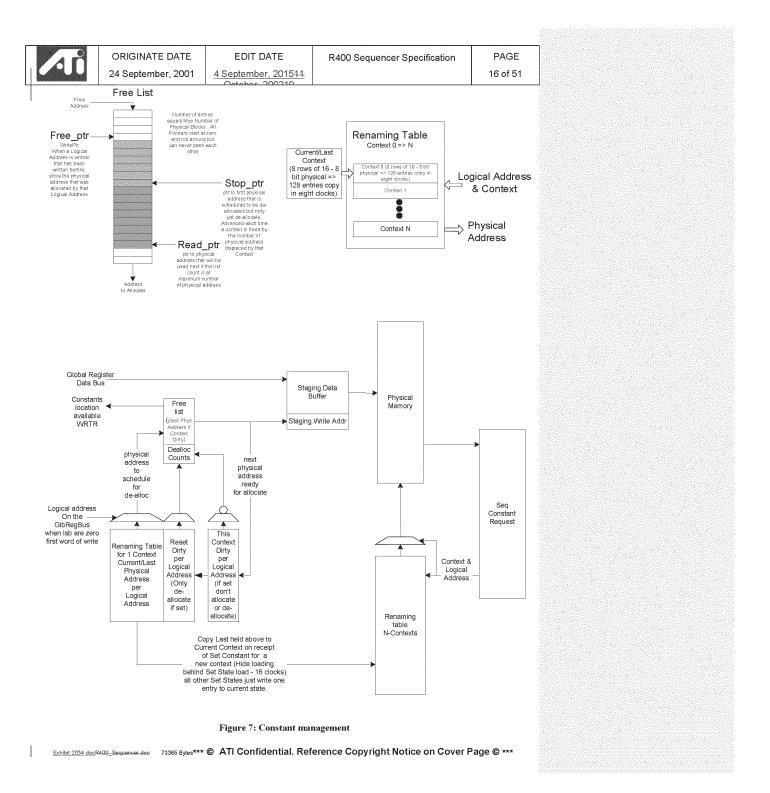

#### 5.3.1 R400 Constant management

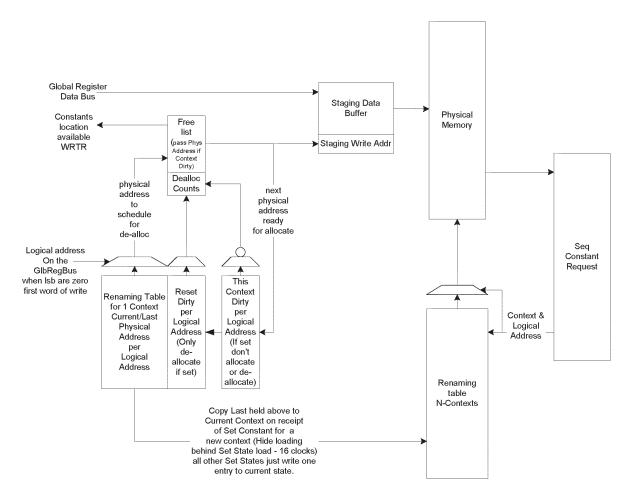

The sequencer is responsible to manage two re-mapping tables (one for the constant store and one for the texture state). On a state change (by the driver), the sequencer will broadside copy the contents of its re-mapping tables to a new one. We have 8 different re-mapping tables we can use concurrently.

The constant memory update will be incremental, the driver only need to update the constants that actually changed between the two state changes.

For this model to work in its simplest form, the requirement is that the physical memory MUST be at least twice as large as the logical address space + the space allocated for Real Time. In our case, since the logical address space is 512 and the reserved RT space can be up to 256 entries, the memory must be of sizes 1280 and above. Similarly the size of the texture store must be of 32\*2+32 = 96 entries and above.

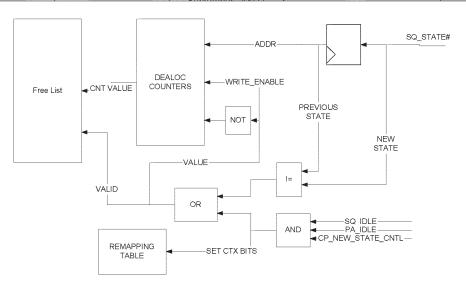

#### 5.3.2 Proposal for R400LE constant management

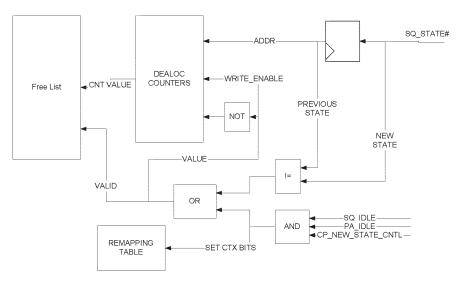

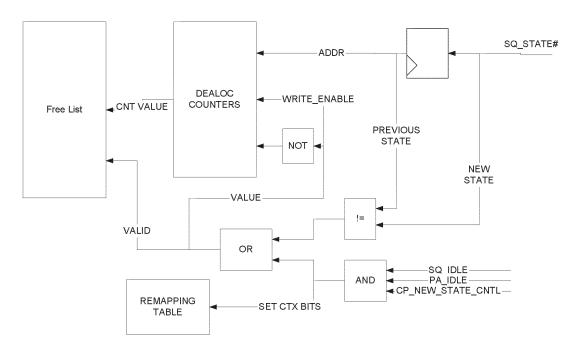

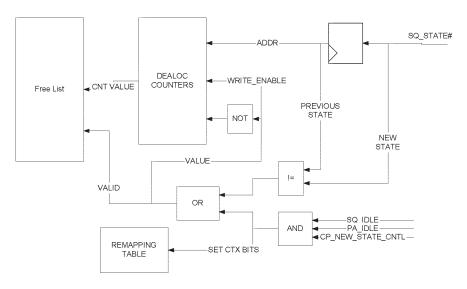

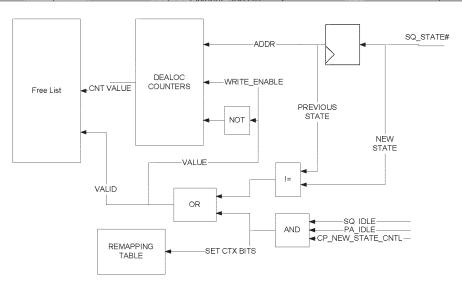

To make this scheme work with only 512+256 = 768 entries, upon reception of a CONTROL packet of state + 1, the sequencer would check for SQ\_IDLE and PA\_IDLE and if both are idle will erase the content of state to replace it with the new state (this is depicted in Figure 8: De-allocation mechanismFigure 8: De-allocation mechanismFigure 8: De-allocation mechanism). Note that in the case a state is cleared a value of 0 is written to the corresponding de-allocation counter location so that when the SQ is going to report a state change, nothing will be de-allocated upon the first report.

The second path sets all context dirty bits that were used in the current state to 1 (thus allowing the new state to reuse these physical addresses if needed).

EDIT DATE

4 September, 20152

DOCUMENT-REV. NUM.

GEN-CXXXXX-REVA

PAGE 19 of 54

Figure 8: De-allocation mechanism for R400LE

### 5.3.3 Dirty bits

Two sets of dirty bits will be maintained per logical address. The first one will be set to zero on reset and set when the logical address is addressed. The second one will be set to zero whenever a new context is written and set for each address written while in this context. The reset dirty is not set, then writing to that logical address will not require de-allocation of whatever address stored in the renaming table. If it is set and the context dirty is not set, then the physical address store needs to be de-allocated and a new physical address is necessary to store the incoming data. If they are both set, then the data will be written into the physical address held in the renaming for the current logical address. No de-allocation or allocation takes place. This will happen when the driver does a set constant twice to the same logical address between context changes. NOTE: It is important to detect and prevent this, failure to do it will allow multiple writes to allocate all physical memory and thus hang because a context will not fit for rendering to start and thus free up space.

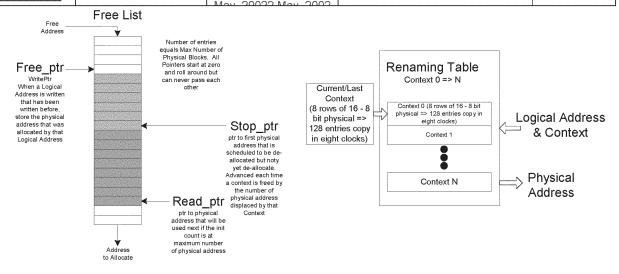

### 5.3.4 Free List Block

A free list block that would consist of a counter (called the IFC or Initial Free Counter) that would reset to zero and incremented every time a chunk of physical memory is used until they have all been used once. This counter would be checked each time a physical block is needed, and if the original ones have not been used up, us a new one, else check the free list for an available physical block address. The count is the physical address for when getting a chunk from the counter.

Storage of a free list big enough to store all physical block addresses.

Maintain three pointers for the free list that are reset to zero. The first one we will call write\_ptr. This pointer will identify the next location to write the physical address of a block to be de-allocated. Note: we can never free more physical memory locations than we have. Once recording address the pointer will be incremented to walk the free list like a ring.

The second pointer will be called stop\_ptr. The stop\_ptr pointer will be advanced by the number of address chunks de-allocates when a context finishes. The address between the stop\_ptr and write\_ptr cannot be reused because they are still in use. But as soon as the context using then is dismissed the stop\_ptr will be advanced.

The third pointer will be called read\_ptr. This pointer will point will point to the next address that can be used for allocation as long as the read\_ptr does not equal the stop\_ptr and the IFC is at its maximum count.

24 September, 2001 4 September, 20152

EDIT DATE R400 Sequencer Specification

PAGE 20 of 54

### 5.3.5 De-allocate Block

This block will maintain a free physical address block count for each context. While in current context, a count shall be maintained specifying how many blocks were written into the free list at the write\_ptr pointer. This count will be reset upon reset or when this context is active on the back and different than the previous context. It is actually a count of blocks in the previous context that will no longer be used. This count will be used to advance the write\_ptr pointer to make available the set of physical blocks freed when the previous context was done. This allows the discard or de-allocation of any number of blocks in one clock.

#### 5.3.6 Operation of Incremental model

The basic operation of the model would start with the write\_ptr, stop\_ptr, read\_ptr pointers in the free list set to zero and the free list counter is set to zero. Also all the dirty bits and the previous context will be initialized to zero. When the first set constants happen, the reset dirty bit will not be set, so we will allocate a physical location from the free list counter because its not at the max value. The data will be written into physical address zero. Both the additional copy of the renaming table and the context zeros of the big renaming table will be updated for the logical address that was written by set start with physical address of 0. This process will be repeated for any logical address that are not dirty until the context changes. If a logical address is hit that has its dirty bits set while in the same context, both dirty bits would be set, so the new data will be over-written to the last physical address assigned for this logical address. When the first draw command of the context is detected, the previous context stored in the additional renaming table will be copied to the larger renaming table in the current (new) context location. Then the set constant logical address with be loaded with a new physical address during the copy and if the reset dirty was set, the physical address it replaced in the renaming table would be entered at the write ptr pointer location on the free list and the write ptr will be incremented. The de-allocation counter for the previous context (eight) will be incremented. This as set states come in for this context one of the following will happen:

- 1.) No dirty bits are set for the logical address being updated. A line will be allocated of the free-list counter or the free list at read\_ptr pointer if read\_ptr != to stop\_ptr .

- 2.) Reset dirty set and Context dirty not set. A new physical address is allocated, the physical address in the renaming table is put on the free list at write\_ptr and it is incremented along with the de-allocate counter for

- 3.) Context dirty is set then the data will be written into the physical address specified by the logical address.

This process will continue as long as set states arrive. This block will provide backpressure to the CP whenever he has not free list entries available (counter at max and stop\_ptr == read\_ptr). The command stream will keep a count of contexts of constants in use and prevent more than max constants contexts from being sent.

Whenever a draw packet arrives, the content of the re-mapping table is written to the correct re-mapping table for the context number. Also if the next context uses less constants than the current one all exceeding lines are moved to the free list to be de-allocated later. This happens in parallel with the writing of the re-mapping table to the correct memory.

Now preferable when the constant context leaves the last ALU clause it will be sent to this block and compared with the previous context that left. (Init to zero) If they differ than the older context will no longer be referenced and thus can be de-allocated in the physical memory. This is accomplished by adding the number of blocks freed this context to the stop\_ptr pointer. This will make all the physical addresses used by this context available to the read\_ptr allocate pointer for future allocation.

This device allows representation of multiple contexts of constants data with N copies of the logical address space. It also allows the second context to be represented as the first set plus some new additional data by just storing the delta's. It allows memory to be efficiently used and when the constants updates are small it can store multiple context. However, if the updates are large, less contexts will be stored and potentially performance will be degraded. Although it will still perform as well as a ring could in this case.

# 5.4 Constant Store Indexing

In order to do constant store indexing, the sequencer must be loaded first with the indexes (that come from the GPRs). There are 144 wires from the exit of the SP to the sequencer (9 bits pointers x 16 vertexes/clock). Since the data must pass thru the Shader pipe for the float to fixed conversion, there is a latency of 4 clocks (1 instruction)

EDIT DATE

DOCUMENT-REV. NUM. GEN-CXXXXX-REVA PAGE 21 of 54

between the time the sequencer is loaded and the time one can index into the constant store. The assembly will look like this

MOVA R1.X,R2.X // Loads the sequencer with the content of R2.X, also copies the content of R2.X into R1.X NOP // latency of the float to fixed conversion

ADD R3,R4,C0[R2.X]// Uses the state from the sequencer to add R4 to C0[R2.X] into R3

Note that we don't really care about what is in the brackets because we use the state from the MOVA instruction. R2.X is just written again for the sake of simplicity and coherency.

The storage needed in the sequencer in order to support this feature is 2\*64\*9 bits = 1152 bits.

### 5.5 Real Time Commands

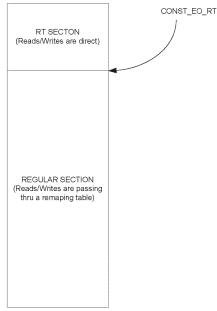

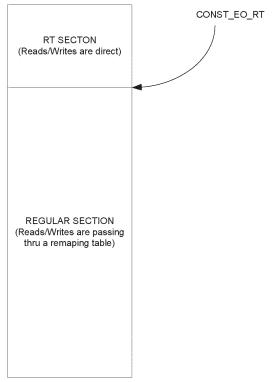

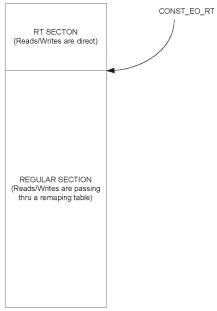

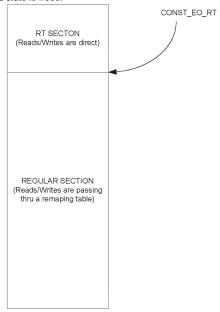

The real time commands constants are written by the CP using the register mapped registers allocated for RT. It works is the same way than when dealing with regular constant loads BUT in this case the CP is not sending a logical address but rather a physical address and the reads are not passing thru the re-mapping table but are directly read from the memory. The boundary between the two zones is defined by the CONST\_EO\_RT control register. Similarly, for the fetch state, the boundary between the two zones is defined by the TSTATE\_EO\_RT control register.

### 5.6 Constant Waterfalling

In order to have a reasonable performance in the case of constant store indexing using the address register, we are going to have the possibility of using the physical memory port for read only. This way we can read 1 constant per clock and thus have a worst-case waterfall mode of 1 vertex per clock. There is a small synchronization issue related with this as we need for the SQ to make sure that the constants where actually written to memory (not only sent to the sequencer) before it can allow the first vector of pixels or vertices of the state to go thru the ALUs. To do so, the sequencer keeps 8 bits (one per render state) and sets the bits whenever the last render state is written to memory and clears the bit whenever a state is freed.

Figure 9: The instruction store

EDIT DATE

R400 Sequencer Specification

PAGE 22 of 54

24 September, 2001 4 September, 20152

# 6. Looping and Branches

Loops and branches are planned to be supported and will have to be dealt with at the sequencer level. We plan on supporting constant loops and branches using a control program.

# 6.1 The controlling state.

The R400 controling state consists of:

Boolean[256:0] Loop\_count[7:0][31:0] Loop\_Start[7:0][31:0] Loop\_Step[7:0][31:0]

That is 256 Booleans and 32 loops.

We have a stack of 4 elements for nested calls of subroutines and 4 loop counters to allow for nested loops.

This state is available on a per shader program basis.

# 6.2 The Control Flow Program

We'd like to be able to code up a program of the form:

1: Loop

2: Exec TexFetch

3: TexFetch

4: ALU

5: ALU

6: TexFetch

7: End Loop

8: ALU Export

But realize that 3: may be dependent on 2: and 4: is almost certainly dependent on 2: and 3:. Without clausing, these dependencies need to be expressed in the Control Flow instructions. Additionally, without separate 'texture clauses' and 'ALU clauses' we need to know which instructions to dispatch to the Texture Unit and which to the ALU unit. This information will be encapsulated in the flow control instructions.

Each control flow instruction will contain 2 bits of information for each (non-control flow) instruction:

- a) ALU or Texture

- b) Serialize Execution

(b) would force the thread to stop execution at this point (before the instruction is executed) and wait until all textures have been fetched. Given the allocation of reserved bits, this would mean that the count of an 'Exec' instruction would be limited to about 8 (non-control-flow) instructions. If more than this were needed, a second Exec (with the same conditions) would be issued.

Another function that relies upon 'clauses' is allocation and order of execution. We need to assure that pixels and vertices are exported in the correct order (even if not all execution is ordered) and that space in the output buffers are allocated in order. Additionally data can't be exported until space is allocated. A new control flow instruction:

Alloc <buf>fer select -- position,parameter, pixel or vertex memory. And the size required>.

would be created to mark where such allocation needs to be done. To assure allocation is done in order, the actual allocation for a given thread can not be performed unless the equivalent allocation for all previous threads is already completed. The implementation would also assure that execution of instruction(s) following the serialization due to the Alloc will occur in order -- at least until the next serialization or change from ALU to Texture. In most cases this will allow the exports to occur without any further synchronization. Only 'final' allocations or position allocations are

EDIT DATE

4 September, 20152

DOCUMENT-REV. NUM. GEN-CXXXXX-REVA PAGE 23 of 54

guaranteed to be ordered. Because strict ordering is required for pixels, parameters and positions, this implies only a single alloc for these structures. Vertex exports to memory do not require ordering during allocation and so multiple 'allocs' may be done.

#### 6.2.1 Control flow instructions table

Here is the revised control flow instruction set.

Note that whenever a field is marked as RESERVED, it is assumed that all the bits of the field are cleared (0).

|            | Execute                         |          |                                  |       |              |  |  |  |

|------------|---------------------------------|----------|----------------------------------|-------|--------------|--|--|--|

| 47         | 47 46 43 40 34 33 16 15 12 11 0 |          |                                  |       |              |  |  |  |

| Addressing | 0001                            | RESERVED | Instructions type + serialize (9 | Count | Exec Address |  |  |  |

|            |                                 |          | instructions)                    |       |              |  |  |  |

Execute up to 9 instructions at the specified address in the instruction memory. The Instruction type field tells the sequencer the type of the instruction (LSB) (1 = Texture, 0 = ALU and whether to serialize or not the execution (MSB) (1 = Serialize, 0 = Non-Serialized).

|            | NOP               |          |   |  |  |  |

|------------|-------------------|----------|---|--|--|--|

| 47         | 47   46 43   42 0 |          |   |  |  |  |

| Addressing | 0010              | RESERVED | 1 |  |  |  |

This is a regular NOP.

| Conditional_Execute                           |  |  |                                                                |  |       |              |

|-----------------------------------------------|--|--|----------------------------------------------------------------|--|-------|--------------|

| 47   46 43   42   41 34   3316   15 12   11 0 |  |  |                                                                |  |       |              |

| Addressing                                    |  |  | Boolean Instructions type + serialize (9 address instructions) |  | Count | Exec Address |

If the specified Boolean (8 bits can address 256 Booleans) meets the specified condition then execute the specified instructions (up to 9 instructions). If the condition is not met, we go on to the next control flow instruction.

| Conditional_Execute_Predicates                       |      |           |          |                     |                                                      |       |              |  |

|------------------------------------------------------|------|-----------|----------|---------------------|------------------------------------------------------|-------|--------------|--|

| 47   46 43   42   41 36   35 34   3316   1512   11 0 |      |           |          |                     |                                                      |       |              |  |

| Addressing                                           | 0010 | Condition | RESERVED | Predicate<br>vector | Instructions<br>type + serialize<br>(9 instructions) | Count | Exec Address |  |

Check the AND/OR of all current predicate bits. If AND/OR matches the condition execute the specified number of instructions. We need to AND/OR this with the kill mask in order not to consider the pixels that aren't valid. If the condition is not met, we go on to the next control flow instruction.

|            | Loop_Start |          |         |                                     |              |  |  |  |

|------------|------------|----------|---------|-------------------------------------|--------------|--|--|--|

| 47         | 46 43      | 42 17    | 20 16   | 1512 <del>16</del><br><del>12</del> | 11 0         |  |  |  |

| Addressing | 0101       | RESERVED | loop ID | RESERVEDIO                          | Jump address |  |  |  |

Loop Start. Compares the loop iterator with the end value. If loop condition not met jump to the address. Forward jump only. Also computes the index value. The loop id must match between the start to end, and also indicates which control flow constants should be used with the loop.

EDIT DATE

4 September, 20152

May 200319 April

R400 Sequencer Specification

PAGE 24 of 54

| Loop_End   |       |                |                 |                            |                     |               |  |

|------------|-------|----------------|-----------------|----------------------------|---------------------|---------------|--|

| 47         | 46 43 | 42 20 <u>4</u> | <u>23 21</u>    | <u>20 16</u> 19 17         | 151216<br>12        | 11 0          |  |

| Addressing | 0011  | RESERVED       | Predicate break | loop ID<br>Predicate-break | RESERVED<br>loop-ID | start address |  |

Loop end. Increments the counter by one, compares the loop count with the end value. If loop condition met, continue, else, jump BACK to the start of the loop. If predicate break != 0, then compares predicate vector n (specified by predicate break number). If all bits cleared then break the loop.

The way this is described does not prevent nested loops, and the inclusion of the loop id make this easy to do.

| Conditionnal_Call |                                                     |           |                                 |          |            |              |

|-------------------|-----------------------------------------------------|-----------|---------------------------------|----------|------------|--------------|

| 47                | 47 46 43 42 35-41 34 33 1 <u>3</u> 2 <u>12</u> 11 0 |           |                                 |          |            |              |

| Addressing        | 0111                                                | Condition | Predicate vectorBoolean address | RESERVED | Force Call | Jump address |

If the condition is met, jumps to the specified address and pushes the control flow program counter on the stack. If force call is set the condition is ignored and the call is made always.

| Return     |       |          |   |  |  |

|------------|-------|----------|---|--|--|

| 47         | 46 43 | 42 0     |   |  |  |

| Addressing | 1000  | RESERVED | 8 |  |  |

Pops the topmost address from the stack and jumps to that address. If nothing is on the stack, the program will just continue to the next instruction.

|   | Conditionnal_Jump |       |           |         |         |          |            |              |

|---|-------------------|-------|-----------|---------|---------|----------|------------|--------------|

|   | 47                | 46 43 | 42        | 41 34   | 33      | 32 132   | <u>12</u>  | 11 0         |

| - | Addressing        | 1001  | Condition | Boolean | FW only | RESERVED | Force Jump | Jump address |

|   |                   |       |           | address |         |          |            |              |

If force jump is set the condition is ignored and the jump is made always. If FW only is set then only forward jumps are allowed.

| Allocate |       |               |          |                 |  |

|----------|-------|---------------|----------|-----------------|--|

| 47       | 46 43 | 4241          | 40 4     | 30              |  |

| Debug    | 1010  | Buffer Select | RESERVED | Allocation size |  |

Buffer Select takes a value of the following:

01 - position export (ordered export)

10 - parameter cache or pixel export (ordered export)

11 - pass thru (out of order exports).

If debug is set this is a debug alloc (ignore if debug DB\_ON register is set to off).

| End Of Program         |  |  |  |  |

|------------------------|--|--|--|--|

| 47 46 43 42 0          |  |  |  |  |

| RESERVED 1011 RESERVED |  |  |  |  |

Marks the end of the program.

# 6.3 Implementation

EDIT DATE

4 September, 20152

DOCUMENT-REV. NUM. GEN-CXXXXX-REVA PAGE 25 of 54

The envisioned implementation has a buffer that maintains the state of each thread. A thread lives in a given location in the buffer during its entire life, but the buffer has FIFO qualities in that threads leave in the order that they enter. Actually two buffers are maintained — one for Vertices and one for Pixels. The intended implementation would allow for:

16 entries for vertices 48 entries for pixels.

From each buffer, arbitration logic attempts to select 1 thread for the texture unit and 1 (interleaved) thread for the ALU unit. Once a thread is selected it is read out of the buffer, marked as invalid, and submitted to appropriate execution unit. It is returned to the buffer (at the same place) with its status updated once all possible sequential instructions have been executed. A switch from ALU to TEX or visa-versa or a Serialize\_Execution modifier forces the thread to be returned to the buffer.

Each entry in the buffer will be stored across two physical pieces of memory - most bits will be stored in a 1 read port device. Only bits needed for thread arbitration will be stored in a highly multi-ported structure. The bits kept in the 1 read port device will be termed 'state'. The bits kept in the multi-read ported device will be termed 'status'.

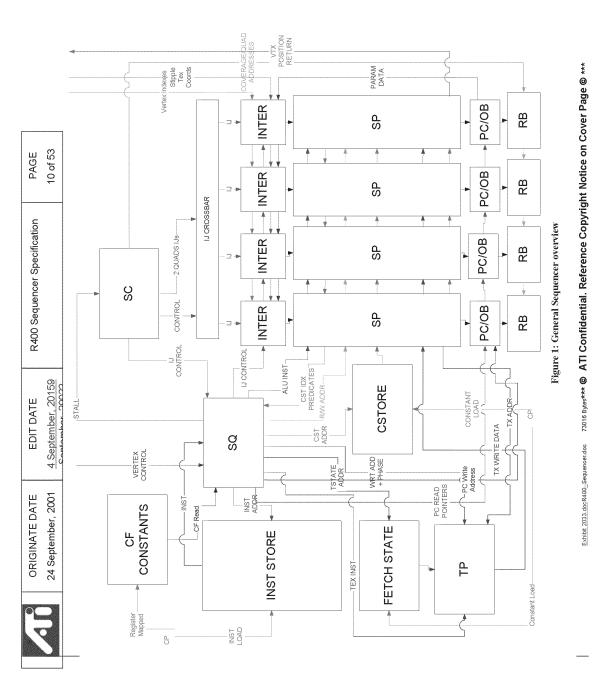

#### 'State Bits' needed include:

- 1. Control Flow Instruction Pointer (12\_13 bits),

- 2. Execution Count Marker 4 bits),

- 3. Loop Iterators (4x9 bits),

- 4. Call return pointers (4x12 bits),

- 5. Predicate Bits (4x64 bits),

- 6. Export ID (1 bit),

- 7. Parameter Cache base Ptr (7 bits),

- 8. GPR Base Ptr (8 bits),

- 9. Context Ptr (3 bits).

- 10. LOD corrections (6x16 bits)

- 11. Valid bits (64 bits)

Absent from this list are 'Index' pointers. These are costly enough that I'm presuming that they are instead stored in the GPRs. The first seven fields above (Control Flow Ptr, Execution Count, Loop Counts, call return ptrs, Predicate bits, PC base ptr and export ID) are updated every time the thread is returned to the buffer based on how much progress has been mode on thread execution. GPR Base Ptr, Context Ptr and LOD corrections are unchanged throughout execution of the thread.

#### 'Status Bits' needed include:

- Valid Thread

- Texture/ALU engine needed

- Texture Reads are outstanding

- · Waiting on Texture Read to Complete

- Allocation Wait (2 bits)

- 00 No allocation needed

- 01 Position export allocation needed (ordered export)

- 10 Parameter or pixel export needed (ordered export)

- 11 pass thru (out of order export)

- · Allocation Size (4 bits)

- Position Allocated

- First thread of a new context

- · Event thread (NULL thread that needs to trickle down the pipe)

- Last (1 bit)

- Pulse SX (1 bit)

Formatted: Bullets and Numbering

Formatted: Bullets and Numbering

EDIT DATE

R400 Sequencer Specification

PAGE 26 of 54

24 September, 2001

4 September, 20152

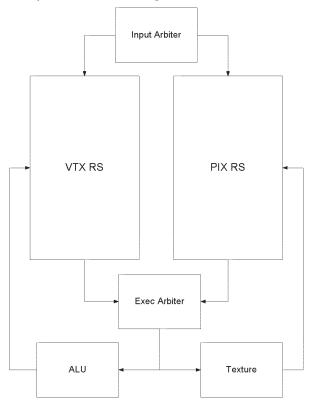

All of the above fields from all of the entries go into the arbitration circuitry. The arbitration circuitry will select a winner for both the Texture Engine and for the ALU engine. There are actually two sets of arbitration -- one for pixels and one for vertices. A final selection is then done between the two. But the rest of this implementation summary only considers the 'first' level selection which is similar for both pixels and vertices.

Texture arbitration requires no allocation or ordering so it is purely based on selecting the 'oldest' thread that requires the Texture Engine.

ALU arbitration is a little more complicated. First, only threads where either of Texture\_Reads\_outstanding or Waiting\_on\_Texture\_Read\_to\_Complete are '0' are considered. Then if Allocation\_Wait is active, these threads are further filtered based on whether space is available. If the allocation is position allocation, then the thread is only considered if all 'older' threads have already done their position allocation (position allocated bits set). If the allocation is parameter or pixel allocation, then the thread is only considered if it is the oldest thread. Also a thread is not considered if it is a parameter or pixel or position allocation, has its First\_thread\_of\_a\_new\_context bit set and would cause ALU interleaving with another thread performing the same parameter or pixel or position allocation. Finally the 'oldest' of the threads that pass through the above filters is selected. If the thread needed to allocate, then at this time the allocation is done, based on Allocation\_Size. If a thread has its "last" bit set, then it is also removed from the buffer, never to return.

If I now redefine 'clauses' to mean 'how many times the thread is removed from the thread buffer for the purpose of exection by either the ALU or Texture engine', then the minimum number of clauses needed is 2 -- one to perform the allocation for exports (execution automatically halts after an 'Alloc' instruction) (but doesn't performs the actual allocation) and one for the actual ALU/export instructions. As the 'Alloc' instruction could be part of a texture clause (presumably the final instruction in such a clause), a thread could still execute in this minimal number of 2 clauses, even if it involved texture fetching.

The Texture\_Reads\_Outstanding bit must be updated by the sequencer, based on keeping track of how many Texture Clauses have been executed by a given thread that have not yet had there data returned. Any number above 0 results in this bit being set. We could consider forcing synchronization such that two texture clauses for a given thread may not be outstanding at any time (that would be my preference for simplicity reasons and because it would require only very little change in the texture pipe interface). This would allow the sequencer to set the bit on execution of the texture clause, and allow the texture unit to return a pointer to the thread buffer on completion that clears the bit

# 6.4 Data dependant predicate instructions

Data dependant conditionals will be supported in the R400. The only way we plan to support those is by supporting three vector/scalar predicate operations of the form:

PRED\_SETE\_# - similar to SETE except that the result is 'exported' to the sequencer.

PRED\_SETNE\_# - similar to SETNE except that the result is 'exported' to the sequencer.

PRED\_SETGT\_# - similar to SETGT except that the result is 'exported' to the sequencer

PRED\_SETGTE\_# - similar to SETGTE except that the result is 'exported' to the sequencer

For the scalar operations only we will also support the two following instructions:

PRED\_SETÉ0\_# - SETE0 PRED\_SETE1\_# - SETE1

The export is a single bit - 1 or 0 that is sent using the same data path as the MOVA instruction. The sequencer will maintain 4 sets of 64 bit predicate vectors (in fact 8 sets because we interleave two programs but only 4 will be exposed) and use it to control the write masking. This predicate is not maintained across clause boundaries. The # sign is used to specify which predicate set you want to use 0 thru 3.

Then we have two conditional execute bits. The first bit is a conditional execute "on" bit and the second bit tells us if we execute on 1 or 0. For example, the instruction:

P0\_ADD\_# R0,R1,R2

Exhibit 2029.docR490\_Sequencer.doc 73711 Bytes\*\*\* © ATI Confidential. Reference Copyright Notice on Cover Page © \*\*\*

AMD1044 0257420

EDIT DATE

4 September, 20152

DOCUMENT-REV. NUM. GEN-CXXXXX-REVA PAGE 27 of 54

Is only going to write the result of the ADD into those GPRs whose predicate bit is 0. Alternatively, P1\_ADD\_# would only write the results to the GPRs whose predicate bit is set. The use of the P0 or P1 without precharging the sequencer with a PRED instruction is undefined.

{Issue: do we have to have a NOP between PRED and the first instruction that uses a predicate?}

# 6.5 HW Detection of PV,PS

Because of the control program, the compiler cannot detect statically dependant instructions. In the case of nonmasked writes and subsequent reads the sequencer will insert uses of PV,PS as needed. This will be done by comparing the read address and the write address of consecutive instructions. For masked writes, the sequencer will insert NOPs wherever there is a dependant read/write.

The sequencer will also have to insert NOPs between PRED\_SET and MOVA instructions and their uses.

### 6.6 Register file indexing

Because we can have loops in fetch clause, we need to be able to index into the register file in order to retrieve the data created in a fetch clause loop and use it into an ALU clause. The instruction will include the base address for register indexing and the instruction will contain these controls:

| Bit7 | Bit 6 |                     |

|------|-------|---------------------|

| 0    | 0     | 'absolute register  |

| 0    | 1     | 'relative register' |

| 1    | 0     | 'previous vector'   |

| 1    | 1     | 'previous scalar'   |

In the case of an absolute register we just take the address as is. In the case of a relative register read we take the base address and we add to it the loop\_index and this becomes our new address that we give to the shader pipe.

The sequencer is going to keep a loop index computed as such:

Index = Loop\_iterator\*Loop\_step + Loop\_start.

We loop until loop\_iterator = loop\_count. Loop\_step is a signed value [-128...127]. The computed index value is a 10 bit counter that is also signed. Its real range is [-256,256]. The tenth bit is only there so that we can provide an out of range value to the "indexing logic" so that it knows when the provided index is out of range and thus can make the necessary arrangements.

# 6.7 Debugging the Shaders

In order to be able to debug the pixel/vertex shaders efficiently, we provide 2 methods.

### 6.7.1 Method 1: Debugging registers

Current plans are to expose 2 debugging, or error notification, registers:

- 1. address register where the first error occurred

- 2. count of the number of errors

The sequencer will detect the following groups of errors:

- count overflow

- constant indexing overflow

- register indexing overflow

Compiler recognizable errors:

- jump errors

- relative jump address > size of the control flow program

- call stack

call with stack full return with stack empty

EDIT DATE

R400 Sequencer Specification

PAGE 28 of 54

24 September, 2001

4 September, 20152

nber, 20152

A jump error will always cause the program to break. In this case, a break means that a clause will halt execution, but allowing further clauses to be executed.

With all the other errors, program can continue to run, potentially to worst-case limits. The program will only break if the DB\_PROB\_BREAK register is set.

If indexing outside of the constant or the register range, causing an overflow error, the hardware is specified to return the value with an index of 0. This could be exploited to generate error tokens, by reserving and initializing the 0th register (or constant) for errors.

{ISSUE : Interrupt to the driver or not?}

### 6.7.2 Method 2: Exporting the values in the GPRs

1) The sequencer will have a debug active, count register and an address register for this mode.

Under the normal mode execution follows the normal course.

Under the debug mode it is assumed that the program is always exporting n debug vectors and that all other exports to the SX block (position, color, z, ect) will been turned off (changed into NOPs) by the sequencer (even if they occur before the address stated by the ADDR debug register).

### 7. Pixel Kill Mask

A vector of 64 bits is kept by the sequencer per group of pixels/vertices. Its purpose is to optimize the texture fetch requests and allow the shader pipe to kill pixels using the following instructions:

MASK\_SETE MASK\_SETNE MASK\_SETGT MASK\_SETGTE

# 8. Multipass vertex shaders (HOS)

Multipass vertex shaders are able to export from the 6 last clauses but to memory ONLY.

### 9. Register file allocation

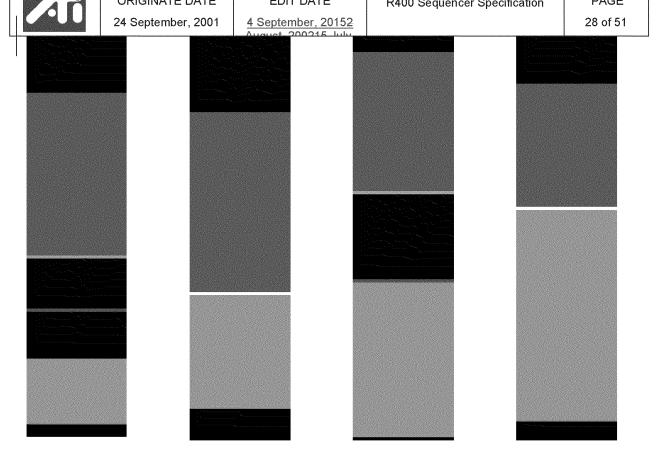

The register file allocation for vertices and pixels can either be static or dynamic. In both cases, the register file in managed using two round robins (one for pixels and one for vertices). In the dynamic case the boundary between pixels and vertices is allowed to move, in the static case it is fixed to 128-VERTEX\_REG\_SIZE for vertices and PIXEL REG\_SIZE for pixels.

Above is an example of how the algorithm works. Vertices come in from top to bottom; pixels come in from bottom to top. Vertices are in orange and pixels in green. The blue line is the tail of the vertices and the green line is the tail of the pixels. Thus anything between the two lines is shared. When pixels meets vertices the line turns white and the boundary is static until both vertices and pixels share the same "unallocated bubble". Then the boundary is allowed to move again. The numbering of the GPRs starts from the bottom of the picture at index 0 and goes up to the top at index 127.

# 10. Fetch Arbitration

The fetch arbitration logic chooses one of the 8 potentially pending fetch clauses to be executed. The choice is made by looking at the fifos from 7 to 0 and picking the first one ready to execute. Once chosen, the clause state machine will send one 2x2 fetch per clock (or 4 fetches in one clock every 4 clocks) until all the fetch instructions of the clause are sent. This means that there cannot be any dependencies between two fetches of the same clause.

The arbitrator will not wait for the fetches to return prior to selecting another clause for execution. The fetch pipe will be able to handle up to X(?) in flight fetches and thus there can be a fair number of active clauses waiting for their fetch return data.

# 11. ALU Arbitration

ALU arbitration proceeds in almost the same way than fetch arbitration. The ALU arbitration logic chooses one of the 8 potentially pending ALU clauses to be executed. The choice is made by looking at the fifos from 7 to 0 and picking the first one ready to execute. There are two ALU arbiters, one for the even clocks and one for the odd clocks. For example, here is the sequencing of two interleaved ALU clauses (E and O stands for Even and Odd sets of 4 clocks):

Einst0 Oinst0 Einst1 Oinst1 Einst2 Oinst2 Einst0 Oinst3 Einst1 Oinst4 Einst2 Oinst0...

Proceeding this way hides the latency of 8 clocks of the ALUs. Also note that the interleaving also occurs across clause boundaries.

4 September, 20152

**EDIT DATE**

R400 Sequencer Specification

PAGE 30 of 54

24 September, 2001

# 12. Handling Stalls

When the output file is full, the sequencer prevents the ALU arbitration logic from selecting the last clause (this way nothing can exit the shader pipe until there is place in the output file. If the packet is a vertex packet and the position buffer is full (POS FULL) then the sequencer also prevents a thread from entering the exporting clause (3?). The sequencer will set the OUT FILE FULL signal n clocks before the output file is actually full and thus the ALU arbiter will be able read this signal and act accordingly by not preventing exporting clauses to proceed.

# 13. Content of the reservation station FIFOs

The reservation FIFOs contain the state of the vector of pixels and vertices. We have two sets of those: one for pixels, and one for vertices. They contain 3 bits of Render State 7 bits for the base address of the GPRs, some bits for LOD correction and coverage mask information in order to fetch fetch for only valid pixels, the quad address.

### 14. The Output File

The output file is where pixels are put before they go to the RBs. The write BW to this store is 256 bits/clock. Just before this output file are staging registers with write BW 512 bits/clock and read BW 256 bits/clock. The staging registers are 4x128 (and there are 16 of those on the whole chip).

#### 15. IJ Format

The IJ information sent by the PA is of this format on a per quad basis:

We have a vector of IJ's (one IJ per pixel at the centroid of the fragment or at the center of the pixel depending on the mode bit). The interpolation is done at a different precision across the 2x2. The upper left pixel's parameters are always interpolated at full 20x24 mantissa precision. Then the result of the interpolation along with the difference in IJ in reduced precision is used to interpolate the parameter for the other three pixels of the 2x2. Here is how we do it:

Assuming P0 is the interpolated parameter at Pixel 0 having the barycentric coordinates I(0), J(0) and so on for P1,P2 and P3. Also assuming that A is the parameter value at V0 (interpolated with I), B is the parameter value at V1 (interpolated with J) and C is the parameter value at V2 (interpolated with (1-I-J).

$$\Delta 01I = I(1) - I(0)$$

$$\Delta 01J = J(1) - J(0)$$

$$\Delta 02I = I(2) - I(0)$$

$$\Delta 02J = J(2) - J(0)$$

$$\Delta 03I = I(3) - I(0)$$

$$\Delta 03J = J(3) - J(0)$$

$$P0 = C + I(0)*(A-C) + J(0)*(B-C)$$

$$P1 = P0 + \Delta 01I * (A - C) + \Delta 01J * (B - C)$$

$$P2 = P0 + \Delta 02I * (A - C) + \Delta 02J * (B - C)$$

$$P3 = P0 + \Delta 03I * (A - C) + \Delta 03J * (B - C)$$

P0 is computed at 20x24 mantissa precision and P1 to P3 are computed at 8X24 mantissa precision. So far no visual degradation of the image was seen using this scheme.

Multiplies (Full Precision): 2 Multiplies (Reduced precision): 6 Subtracts 19x24 (Parameters): 2

EDIT DATE

4 September, 20152

DOCUMENT-REV. NUM.

GEN-CXXXXX-REVA

PAGE 31 of 54

Adds: 8

FORMAT OF P0's IJ: Mantissa 20 Exp 4 for I + Sign

Mantissa 20 Exp 4 for J + Sign

FORMAT of Deltas (x3): Mantissa 8 Exp 4 for I + Sign Mantissa 8 Exp 4 for J + Sign

Total number of bits:  $20^2 + 8^6 + 4^8 + 4^2 = 128$

All numbers are kept using the un-normalized floating point convention: if exponent is different than 0 the number is normalized if not, then the number is un-normalized. The maximum range for the IJs (Full precision) is +/- 63 and the range for the Deltas is +/- 127.

# 15.1 Interpolation of constant attributes

Because of the floating point imprecision, we need to take special provisions if all the interpolated terms are the same or if two of the barycentric coordinates are the same.

We start with the premise that if A = B and B = C and C = A, then P0,1,2,3 = A. Since one or more of the IJ terms may be zero, so we extend this to:

```

if (A=B and B=C and C=A)

P0,1,2,3 = A;

else if ((I = 0) \text{ or } (J = 0)) and

((J = 0) \text{ or } (1-I-J = 0)) \text{ and }

((1-J-I=0) \text{ or } (I=0))) {

if(I != 0) {

P0 = A

} else if(J != 0) {

P0 = B;

} else {

P0 = C:

//rest of the quad interpolated normally

}

else

{

normal interpolation

}

```

# 16. Staging Registers

In order for the reuse of the vertices to be 14, the sequencer will have to re-order the data sent IN ORDER by the VGT for it to be aligned with the parameter cache memory arrangement. Given the following group of vertices sent by the VGT:

$0\ 1\ 2\ 3\ 4\ 5\ 6\ 7\ 8\ 9\ 10\ 11\ 12\ 13\ 14\ 15\ ||\ 16\ 17\ 18\ 19\ 20\ 21\ 22\ 23\ 24\ 25\ 26\ 27\ 28\ 29\ 30\ 31\ ||\ 32\ 33\ 34\ 35\ 36\ 37\ 38\ 39\ 40\ 41\ 42\ 43\ 44\ 45\ 46\ 47\ ||\ 48\ 49\ 50\ 51\ 52\ 53\ 54\ 55\ 56\ 57\ 58\ 59\ 60\ 61\ 62\ 63$

The sequencer will re-arrange them in this fashion:

0 1 2 3 16 17 18 19 32 33 34 35 48 49 50 51  $\parallel$  4 5 6 7 20 21 22 23 36 37 38 39 52 53 54 55  $\parallel$  8 9 10 11 24 25 26 27 40 41 42 43 56 57 58 59  $\parallel$  12 13 14 15 28 29 30 31 44 45 46 47 60 61 62 63

The || markers show the SP divisions. In the event a shader pipe is broken, the VGT will send padding to account for the missing pipe. For example, if SP1 is broken, vertices 4 5 6 7 20 21 22 23 36 37 38 39 52 53 54 55 will still be sent by the VGT to the SQ **BUT** will not be processed by the SP and thus should be considered invalid (by the SU and VGT).

EDIT DATE

4 September, 20152

R400 Sequencer Specification

PAGE 32 of 54

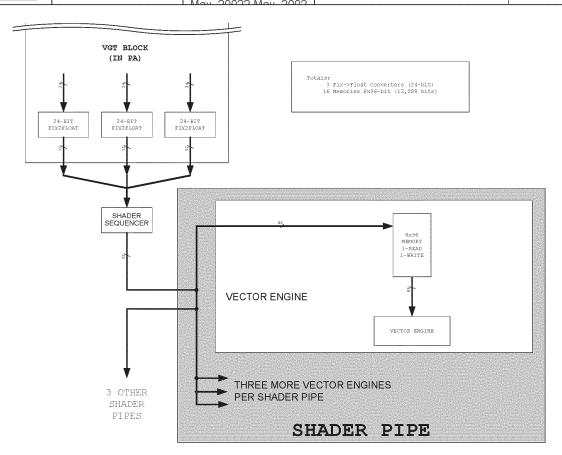

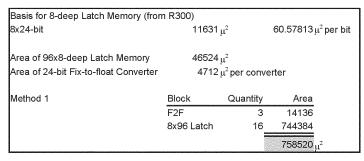

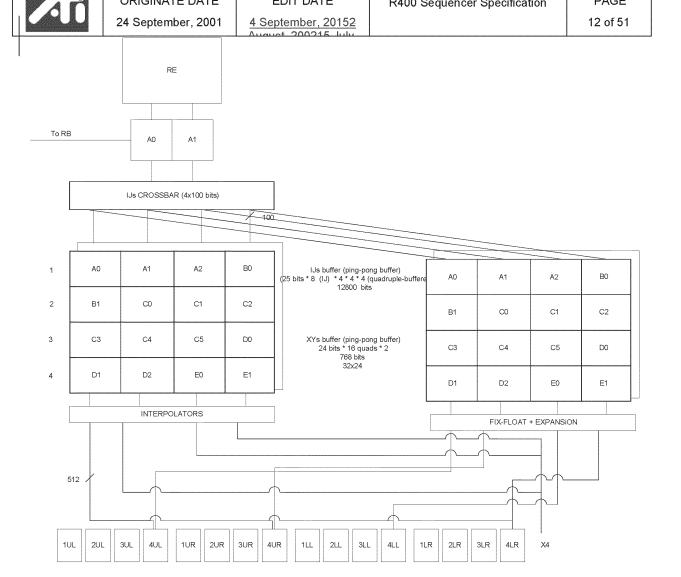

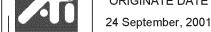

The most straightforward, *non-compressed* interface method would be to convert, in the VGT, the data to 32-bit floating point prior to transmission to the VSISRs. In this scenario, the data would be transmitted to (and stored in) the VSISRs in full 32-bit floating point. This method requires three 24-bit fixed-to-float converters in the VGT. Unfortunately, it also requires and additional 3,072 bits of storage across the VSISRs. This interface is illustrated in <u>Figure 11Figure 11Figure 11</u>. The area of the fixed-to-float converters and the VSISRs for this method is roughly estimated as 0.759sqmm using the R300 process. The gate count estimate is shown in <u>Figure 10Figure 10Figure 10</u>.

| Basis for 8-deep Latch Memory (fron   | n R300)    |                          |                               |  |

|---------------------------------------|------------|--------------------------|-------------------------------|--|

| 8x24-bit                              | 11631      | $\mu^2$                  | $60.57813\mu^2\text{per bit}$ |  |

| Area of 96x8-deep Latch Memory        | 46524      | $\mu^2$                  |                               |  |

| Area of 24-bit Fix-to-float Converter | 4712       | μ <sup>2</sup> per conve | erter                         |  |

| Method 1                              | Block      | Quantity                 | Area                          |  |

|                                       | F2F        | 3                        | 14136                         |  |

|                                       | 8x96 Latch | 16_                      | 744384                        |  |

|                                       |            |                          | 758520 µ²                     |  |

Figure 10:Area Estimate for VGT to Shader Interface

EDIT DATE

4 September, 20152

DOCUMENT-REV. NUM.

GEN-CXXXXX-REVA

PAGE 33 of 54

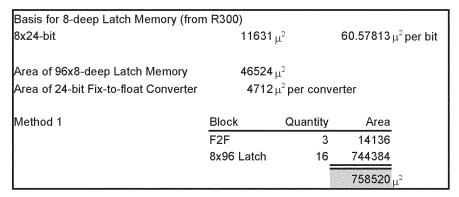

Figure 11:VGT to Shader Interface

# 17. The parameter cache

The parameter cache is where the vertex shaders export their data. It consists of 16 128x128 memories (1R/1W). The reuse engine will make it so that all vertexes of a given primitive will hit different memories. The allocation method for these memories is a simple round robin. The parameter cache pointers are mapped in the following way: 4MSBs are the memory number and the 7 LSBs are the address within this memory.

| MEMORY NUMBER | ADDRESS |

|---------------|---------|

| 4 bits        | 7 bits  |

The PA generates the parameter cache addresses as the positions come from the SQ. All it needs to do is keep a Current\_Location pointer (7 bits only) and as the positions comes increment the memory number. When the memory number field wraps around, the PA increments the Current\_Location by VS\_EXPORT\_COUNT (a snooped register from the SQ). As an example, say the memories are all empty to begin with and the vertex shader is exporting 8 parameters per vertex (VS\_EXPORT\_COUNT = 8). The first position received is going to have the PC address 00000000000 the second one 00010000000, third one 00100000000 and so on up to 11110000000. Then the next position received (the 17<sup>th</sup>) is going to have the address 0000001000, the 18<sup>th</sup> 00010001000, the 19<sup>th</sup> 00100001000 and so on. The Current\_location is NEVER reset BUT on chip resets. The only thing to be careful about is that if the SX doesn't send you a full group of positions (<64) then you need to fill the address space so that the next group starts correctly aligned (for example if you receive only 33 positions then you need to add 2\*VS\_EXPORT\_COUNT to Current\_Location and reset the memory count to 0 before the next vector begins).

EDIT DATE

R400 Sequencer Specification

PAGE 34 of 54

24 September, 2001 4 September, 20152

# 17.1 Export restrictions

#### 17.1.1 Pixel exports:

Pixels can export 1,2,3 or 4 color buffers to the SX( +z). The exports will be done in order. The PRED\_OPTIMIZE function has to be turned of if the exports are done using interleaved predicated instructions. The exports will always be ordered to the SX.

#### 17.1.2 Vertex exports:

Position or parameter caches can be exported in any order in the shader program. It is always better to export posistion as soon as possible. Position has to be exported in a single export block (no texture instructions can be placed between the exports). Parameter cache exports can be done in any order with texture instructions interleaved. The PRED\_OPTIMIZE function has to be turned of if the exports are done using interleaved predicated instructions to the Parameter cache (see Arbitration restrictions for details). The exports will always be allocated in order to the SX.

#### 17.1.3 Pass thru exports:

Pass thru exports have to be done in groups of the form:

Alloc 4 (8 or 12)

Execute ALU(ADDR) ALU(DATA) ALU(DATA) ALU(DATA)...

They cannot have texture instructions interleaved in the export block. These exports are not guaranteed to be ordered.

Also, when doing a pass thru export, Position MUST be exported AFTER all pass thru exports. This position export is used to synchronize the chip when doing a transition from pass thru shader to regular shader and vice versa.

#### 17.2 Arbitration restrictions

Here are the Sequencer arbitration restrictions:

- 1) Cannot execute a serialized thread if the corresponding texture pending bit is set

- 2) Cannot allocate position if any older thread has not allocated position

- 3) If last thread is marked as not valid AND marked as last and we are about to execute the second to oldest thread also marked last then:

- a. Both threads must be from the same context (cannot allow a first thread)

- b. Must turn off the predicate optimization for the second thread

- 4) Cannot execute a texture clause if texture reads are pending

- 5) Cannot execute last if texture pending (even if not serial)

# 18. Export Types

The export type (or the location where the data should be put) is specified using the destination address field in the ALU instruction. Here is a list of all possible export modes:

# 18.1 Vertex Shading

0:15 - 16 parameter cache 16:31 - Empty (Reserved?)

32 - Export Address