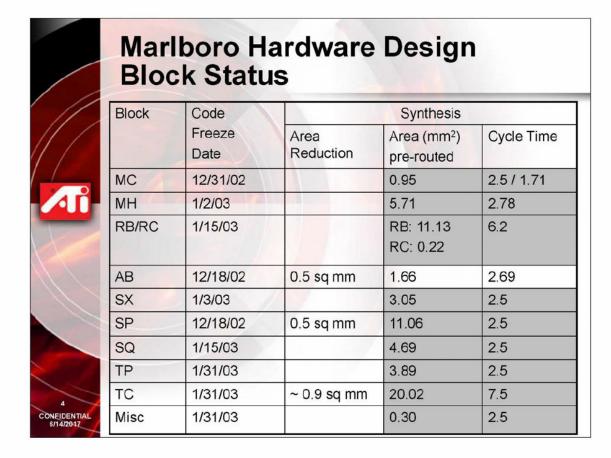

## Marlboro Hardware Design Block Status

- · SQ

- Star memories & supporting logic implemented

- Power management defined control logic to be implemented

- Hardware support for shader debug & Performance counters yet to be added

- Main focus has been on debug to support the SP

- · SP

- Area optimizations implemented

- Working to freeze the block with known precision issue fixes will have little area and no timing impact

- Clock gating done

- · SX

- Memory export function has yet to be verified

- Alpha to mask optimization yet to be implemented

- Performance counters defined yet to be implemented

- Clock gating done

## Marlboro Hardware Design Block Status

- · TP/TC

- Critical path block with slow progress

- Added design resources

- Re-written some sections to reduce area and aid debug

- · RB/RC/AB

- Broken out Blend logic to a new top level block (AB)

- Area optimizations:

- · reduced precision in AB from 16 to 12 bits

- · changed flop based queues to RAM based not yet implemented

- · reduced number of CAM units

- Performance counters have yet to be added

- Support for 64 & 128 bit endian modes

- Power management logic is complete

## Marlboro Hardware Design **Block Status**

- · MC

- Pad Interface definition is complete and being implemented

- Performance counters have been implemented

- MH

- Adding newly defined support

- 3D Array access through HDP64 & 128 bit endian modes

- Performance counters have been added

- Power management is being added now

- ROM

- fully validated

- · CG/CGM

- in final validation

- TST / ID / DEBUG

- implemented and reviewed