|                                                                   | ORIGINATE                  | EDIT DATE                 | DOCUMENT-VER. NUM.                                                                       | PAGE                      |

|-------------------------------------------------------------------|----------------------------|---------------------------|------------------------------------------------------------------------------------------|---------------------------|

|                                                                   | 10-Feb-15                  | 3-Nov-16                  | 1.0                                                                                      | 1 of 62                   |

| d Author: Randy Ramsey                                            |                            |                           |                                                                                          |                           |

| ISS                                                               | UED TO:                    |                           | COPY NO.                                                                                 |                           |

|                                                                   |                            |                           | cification                                                                               |                           |

|                                                                   | Rev                        | 1.0 – Last Edit:          | 3-Nov-16                                                                                 |                           |

|                                                                   | ALLY DETRIME               | NTAL TO THE               | INFORMATION THA<br>E INTEREST OF AMD T<br>IORIZED DISCLOSURE.                            | HROUGH                    |

| . Preserve this docume                                            | nt's integrity:            |                           |                                                                                          |                           |

| ⇒ Do not reproduce                                                | any portions of it.        |                           |                                                                                          |                           |

| ⇒ Do not separate a                                               | ny pages from this o       | over.                     |                                                                                          |                           |

| <ol> <li>This document is issue<br/>organization.</li> </ol>      | ed to you alone. Do        | not transfer it to o      | r share it with another person,                                                          | even within your          |

| . Store this document in                                          | n a locked cabinet a       | ccessible only by a       | uthorized users. Do not leave it                                                         | unattended.               |

| . When you no longer n                                            | eed this document,         | return it to AMD.         | Please do not discard it.                                                                |                           |

|                                                                   |                            |                           | contains confidential, proprietary to the r<br>form or by any means without the prior wr |                           |

| MD, the AMD Arrow Logo and co<br>rademark of HDMI Licensing, LLC. | mbinations thereof are tra | demarks of Advanced Mi    | cro Devices, Inc. PCIe is a registered trade                                             | emark of PCI-SIG. HDMI is |

|                                                                   | hics and computing techno  | logies power a variety of | digital experiences with its ground-break<br>devices including PCs, game consoles and    |                           |

| ORIGINATE | EDIT DATE | DOCUMENT-VER. NUM. | PAGE    |  |

|-----------|-----------|--------------------|---------|--|

| 10-Feb-15 | 3-Nov-16  | 1.0                | 2 of 62 |  |

# **Revision History**

| Date | Revision | Description |  |

|------|----------|-------------|--|

|      |          |             |  |

|      |          |             |  |

|      |          |             |  |

| -    |          |             |  |

| -    |          |             |  |

| -    |          |             |  |

| -    |          |             |  |

|      | -        |             |  |

|      |          |             |  |

| AMD                                     | ORIGINATE                                                                                                                                                                                                                                                                                                                                             | EDIT DATE<br>3-Nov-16  | DOCUMENT-VER. NUM. | PAGE    |  |  |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------|---------|--|--|

|                                         | 10-Feb-15                                                                                                                                                                                                                                                                                                                                             | 3-NOV-10               | 1.0                | 3 of 62 |  |  |

| Table of Conter                         | nts                                                                                                                                                                                                                                                                                                                                                   |                        |                    |         |  |  |

| 1 INTRODUC                              | TION                                                                                                                                                                                                                                                                                                                                                  |                        |                    |         |  |  |

| 1.1 OPEN ISSU                           | IFS.                                                                                                                                                                                                                                                                                                                                                  |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

| 200000 XXXX                             | CONTRACTOR CONTRACTOR CONTRACTOR                                                                                                                                                                                                                                                                                                                      |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         | 2. 요즘이 많은 것은 것은 것은 것은 것이 있어요.                                                                                                                                                                                                                                                                                                                         |                        |                    |         |  |  |

| 1022120 1223                            |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         | , 2019년 1월 17일 - 1998년 1998<br>1998년 1999년 1998년 199<br>1998년 1998년 199 |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

| 10000000 00000                          |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

| 200000 000                              |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

| 1022730-10 D-1027                       |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

| 000000 0000                             | 승규는 그는 것이 안 못했는 것을 다 가지 않는 것이 없다.                                                                                                                                                                                                                                                                                                                     | prwarding to SQG       |                    |         |  |  |

| - 1717533 S.C.S.                        | Nave of Dispatch                                                                                                                                                                                                                                                                                                                                      |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

| 100000000000000000000000000000000000000 | 전신 것이 많은 것이 아직 것 같은 바람이 많이 많다.                                                                                                                                                                                                                                                                                                                        |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

| 10022-071 12220                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         | 그는 그 그 같아? 아이는 것 같은 아이는 것 같아? 아이는 것 같아?                                                                                                                                                                                                                                                                                                               |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

| 2.4.1.2 P                               | ull Model                                                                                                                                                                                                                                                                                                                                             |                        |                    |         |  |  |

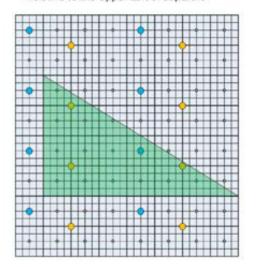

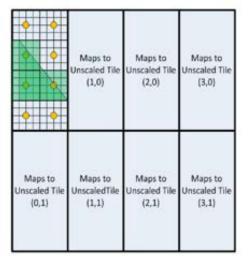

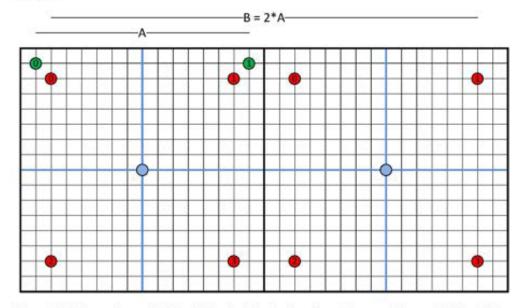

| 2.4.2 Sca                               | le Resolution Based on S                                                                                                                                                                                                                                                                                                                              | Screen Location (9.12) | 5)                 |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

| 2.4.2.2 1                               | mpacts to BCI Equations                                                                                                                                                                                                                                                                                                                               |                        |                    |         |  |  |

|                                         | -                                                                                                                                                                                                                                                                                                                                                     |                        | Y BE OUT OF DATE   |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         | 10 M                                                                                                                                                                                                                                                                                                                                                  |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

|                                         | Contraction of the second second second                                                                                                                                                                                                                                                                                                               |                        | licate Data        |         |  |  |

|                                         |                                                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

| 3.3 PIXEL SHA                           | man 147 DD country a strain man                                                                                                                                                                                                                                                                                                                       |                        |                    |         |  |  |

ATI Ex. 2027 IPR2023-00922 Page 3 of 62

| AMD           | ORIGINATE<br>10-Feb-15     | EDIT DATE<br>3-Nov-16                                                                                           | DOCUMENT-VER. NUM.<br>1.0 | PAGE<br>4 of 62 |

|---------------|----------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------|-----------------|

| 2.5           |                            |                                                                                                                 |                           | 000000000       |

|               |                            |                                                                                                                 |                           |                 |

|               |                            |                                                                                                                 |                           |                 |

|               |                            |                                                                                                                 | Bandwidth                 |                 |

|               |                            | Contraction of the second s | panowioun                 |                 |

|               |                            |                                                                                                                 |                           |                 |

|               |                            |                                                                                                                 |                           |                 |

|               |                            |                                                                                                                 |                           |                 |

|               |                            |                                                                                                                 |                           |                 |

|               |                            |                                                                                                                 |                           |                 |

|               |                            |                                                                                                                 |                           |                 |

|               |                            |                                                                                                                 |                           |                 |

| 3.6.9 Allo    | cation Priority            |                                                                                                                 |                           |                 |

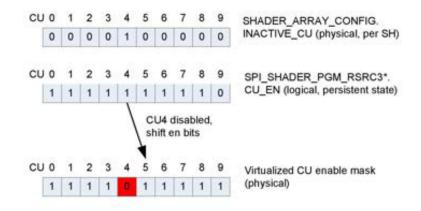

| 3.6.10 Virt   | ualization of Compute L    | Init Masks                                                                                                      |                           |                 |

| 3.6.11 Res    | ource Reservations         |                                                                                                                 |                           |                 |

| 3.6.12 Mu     | tiplier for Resource Lim   | its                                                                                                             |                           |                 |

| 3.7 EXPORT A  | RBITRATION                 |                                                                                                                 |                           |                 |

| 3.7.1 Ma      | intaining GDS order        |                                                                                                                 |                           |                 |

| 3.7.2 Exp     | ort Granting               |                                                                                                                 |                           |                 |

| 3.8 PERSISTEN | T STATE                    |                                                                                                                 |                           |                 |

| 3.9 PARTIAL F | LUSH EVENTS                |                                                                                                                 |                           |                 |

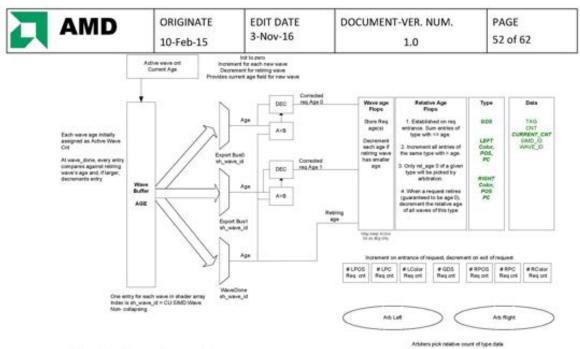

| 3.10 WAVE/EV  | ENT ORDERING               |                                                                                                                 |                           |                 |

|               |                            |                                                                                                                 |                           |                 |

| 3.12 H/V (HOR | IZONTAL/VERTICAL) PIXEL PI | ICKER (FOR DEBUG AND F                                                                                          | ERFORMANCE ANALYSIS)      |                 |

| 3.13 WAVEFRO  | NT LIFETIME STATUS COUNT   | ERS                                                                                                             |                           |                 |

| 4 PERFORM     | NCE                        |                                                                                                                 |                           |                 |

| 4.1 BARYCENT  | RIC CALCULATION            |                                                                                                                 |                           |                 |

| 4.2 PARAMET   | ER CACHE READ              |                                                                                                                 |                           |                 |

| 4.3 GPR LOA   | XING                       |                                                                                                                 |                           |                 |

| 4.4 POCEL     |                            |                                                                                                                 |                           |                 |

| 4.5 GRAPHICS  | BALANCED THROUGHPUT C      | ASES                                                                                                            |                           |                 |

| 4.6 PERFORM   | ANCE COUNTERS              |                                                                                                                 |                           |                 |

| 4.6.1 Per     | formance Counter Binni     | ng                                                                                                              |                           |                 |

| 5 CLOCK GAT   |                            |                                                                                                                 |                           |                 |

Г

| AMD | ORIGINATE | EDIT DATE | DOCUMENT-VER. NUM. | PAGE    |

|-----|-----------|-----------|--------------------|---------|

|     | 10-Feb-15 | 3-Nov-16  | 1.0                | 5 of 62 |

#### Table of Figures

| Figure 1 - SPI Chip Level Data Flow Diagram                          |   |

|----------------------------------------------------------------------|---|

| Figure 2 – Chip Level Diagram                                        | 9 |

| Figure 3 - Top Level Connectivity Block Diagram                      |   |

| Figure 4 – Block Diagram                                             |   |

| Figure 5 - CS Data Flow                                              |   |

| Figure 6 - Async Compute Block Diagram                               |   |

| Figure 7 - CS Threadgroup Ordering                                   |   |

| Figure 8 - CS Thread Count Increment Example                         |   |

| Figure 9 - "Vertex" Data Flow VGT-SPI                                |   |

| Figure 10 - VGT ES, GS, VS Vertex Input                              |   |

| Figure 11 - LS,HS,ES,GS,VS Vertex Input                              |   |

| Figure 12 - Pixel Input Data                                         |   |

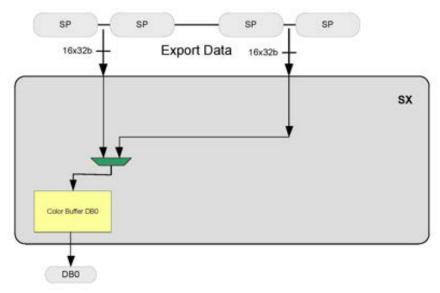

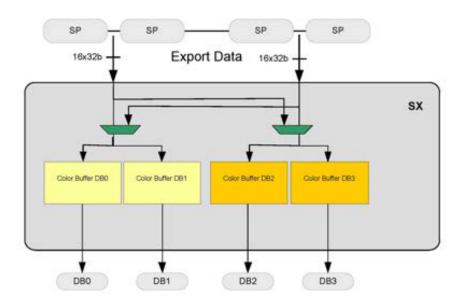

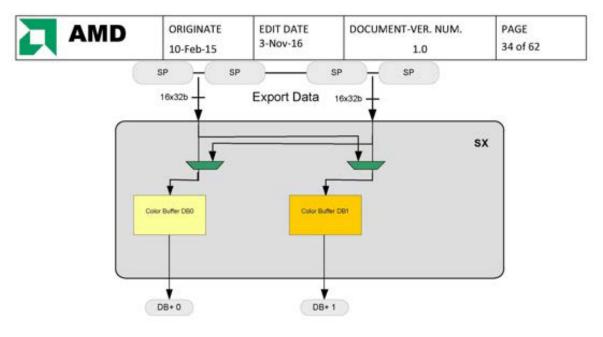

| Figure 13 - Color Export Bus Arbitration, 1RB                        |   |

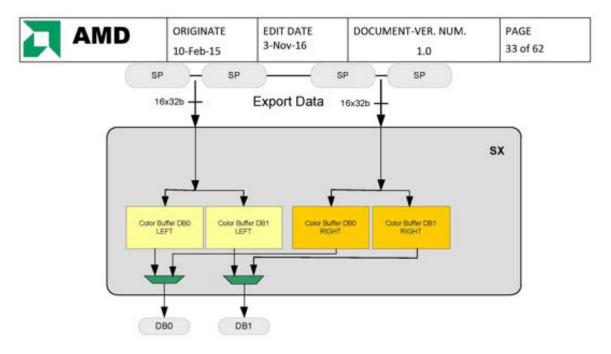

| Figure 14 - Color Export Bus Arbitration, 2RB                        |   |

| Figure 15 - Color Export Bus Arbitration, 4RB                        |   |

| Figure 16 - Color Export Bus Arbitration, 2RB+                       |   |

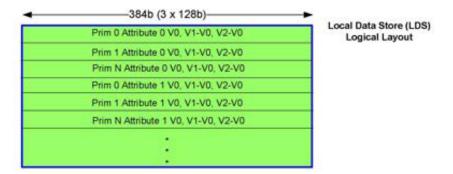

| Figure 17 – LDS Logical Layout                                       |   |

| Figure 18 – Parameter Cache Data Organization                        |   |

| Figure 19 - Combined Data Flow                                       |   |

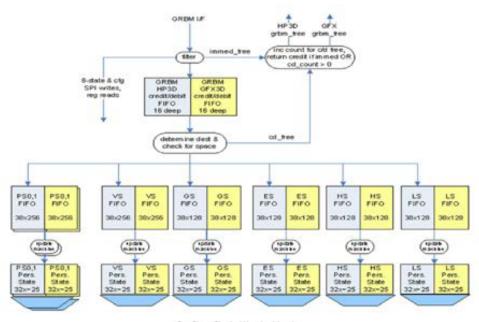

| Figure 20 – Persistent State Update FIFOs                            |   |

| Figure 21 - Persistent State Update FIFOs                            |   |

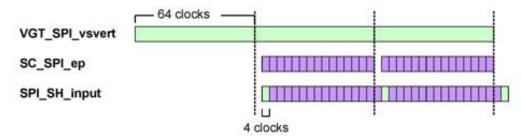

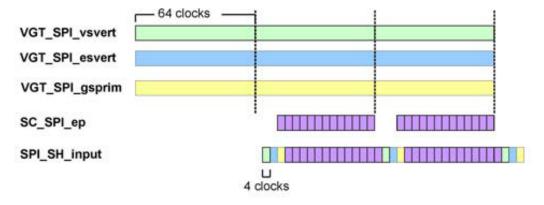

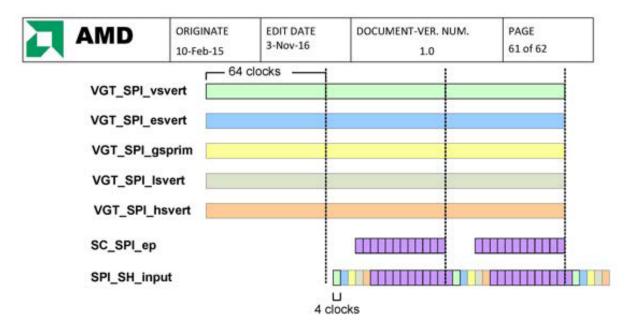

| Figure 22 - Performance, Balanced Throughput Case, VS-PS             |   |

| Figure 23 - Performance, Balanced Throughput Case, ES-GS-VS-PS.      |   |

| Figure 24 - Performance, Balanced Throughput Case, LS-HS-ES-GS-VS-PS |   |

| ORIGINATE | EDIT DATE | DOCUMENT-VER. NUM. | PAGE    |  |

|-----------|-----------|--------------------|---------|--|

| 10-Feb-15 | 3-Nov-16  | 1.0                | 6 of 62 |  |

#### 1 Introduction

This document describes the requirements, functionality, and target performance of the Shader Processor Input (SPI) block.

#### 1.1 Open Issues

#### 1.2 Definitions

#### 1.2.1 Acronyms

SPI - Shader Processor Input

SC - Scan Converter

SQ - Sequencer

SQC – Sequencer Cache SQG – SQ Global Block, instanced in SPI

SX - Shader Export

SP - Shader Processor

CP - Command Processor

CPG – Command Processor, Graphics

CPC – Command Processor, Compute

SE - Shader Engine

SH - Shader Array

CU - Compute Unit

SIMD - Single Instruction Multiple Data unit in the shader processor (SP).

UL - Upper Left

UR - Upper Right

LL - Lower Left

LR - Lower Right

VGPR - Vector General Purpose Register in the SP

SGPR - Scalar General Purpose Register in the SQ

CS - Compute shader

LS - API Vertex shader stage when doing tessellation, writes to LDS

HS - Hull shader stage of tessellation

VS- Vertex shader, could be normal vertices, final pass of a Geometry Shader, or domain shader.

GS - Geometry Shader, processes primitives.

ES - Export Shader, first vertex pass of a Geometry Shader that processes vertices.

PS - Pixel Shader, processes pixels.

VSR -Vertex Input Staging Register, holds input data for vertex threads.

PSR -Pixel Input Staging Register, holds input data for pixel threads.

LDS - Local Data Store

se\_id - Shader Engine Identification Number

sh\_id - Shader Array Identification Number

MSAA - Multi-sample Anti-Aliasing

EQAA - Enhance Quality Anti-Aliasing

| ORIGINATE | EDIT DATE | DOCUMENT-VER. NUM. | PAGE    |

|-----------|-----------|--------------------|---------|

| 10-Feb-15 | 3-Nov-16  | 1.0                | 7 of 62 |

## 1.2.2 Terminology

Event – an event is a special token sent through the graphics pipeline which can be used to enforce synchronization, flush caches, and report status back to the CP. All blocks pipeline these tokens and keep them ordered with other graphics data.

Thread: one instance of a shader program being executed on a wavefront. Each thread has its own data which is unique from any other thread.

Wavefront: This is the basic unit of work. There are 64 threads per wavefront. It is a group of threads that can be executed simultaneously on a SIMD.

Threadgroup, Subgroup: Group of threads that may span several wavefronts. All threads are guaranteed to run on the same CU. This allows for shared CU resources such as the Local Data Store (LDS) and synchronization resources across all threads.

Tessellation Engine: A VGT module that implements DX11 tessellation functionality.

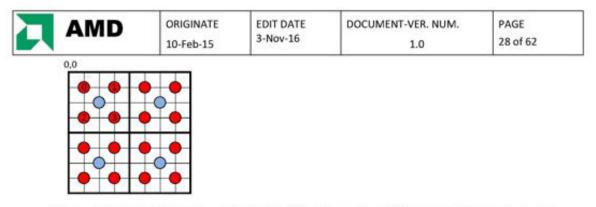

Pixel Quad: A 2x2 pixel region.

Pixel Center: Current pixel's screen coordinates, given as PIX\_X.5, PIX\_Y.5.

Pixel Centroid: Current pixel's centroid in screen coordinates, defined as the covered sample location closest to pixel center. If all samples of a pixel are hit, center will be used for centroid even if center is not one of the current sample locations.

Pixel Sample: Location of the sample ID of the current iteration when running at sample frequency.

Facedness: The PA determined face flag indicating front or back facing.

Param\_gen: Automatically generated ST texture coordinates, typically used with points.

SIMD: Single Instruction Multiple Data unit in the shader processor (SP).

Shader Array: A combination of blocks separate and unique for shader processing, including a shader core consisting of Compute Units.

new\_vector aka fpos, first\_prim\_of\_slot: Parameter cache sync token received from the SC for pixels and used to make sure the SPI waits for VS to finish exporting parameter data before pixels start trying to read it. Helper pixel: Any non-hit pixel being processed as a part of a quad with other hit pixels.

#### 1.3 Top Level Description

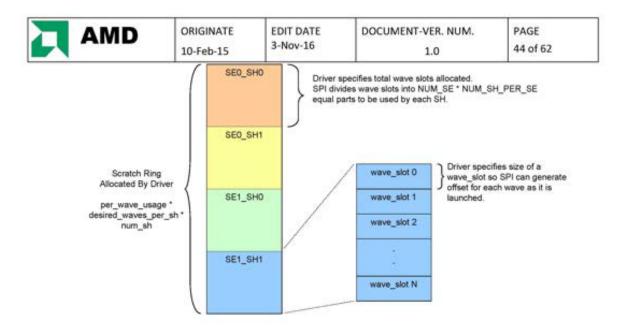

The main purpose of the SPI is to manage shader resources and provide shader input data to the GPRs and wavefronts to the SQ. It accumulates "vertex" type shader input data from the VGT (VS, GS, ES, HS, LS) into wavefronts. It receives compute shader (CS) data and state from the CPG and CPC on esdata interfaces. Resources required to process wavefronts and CU/SIMD assignment in the shader array (SH) are managed by the SPI in terms of allocation and de-allocation. SPI passes data through for the VGT verts and prims. For HS and GS, SPI unrolls threadgroups and subgroups into wavefronts. For CS, SPI unrolls threadgroups into wavefronts and generates an index per thread based on the threadgroup size. Pixel quad data delivered from the SC is accumulated into wavefronts. The SPI processes this data, per pixel, to interpolate and produce barycentric gradient data (IJ) or screen X, Y, and/or primitive faceness data. The SPI loads IJ data into VGPRs and coordinates moving primitive attribute data from the parameter caches into a CU Local Data Store (LDS) for the pixel shader to use for attributes, guaranteeing that attribute data has been written to the parameter cache before allowing PS to read.

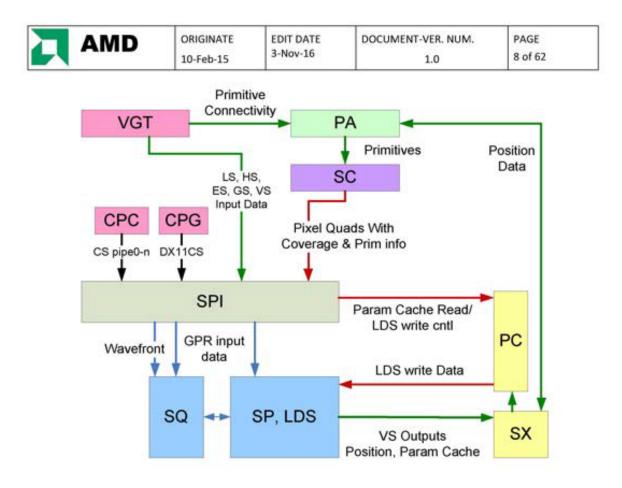

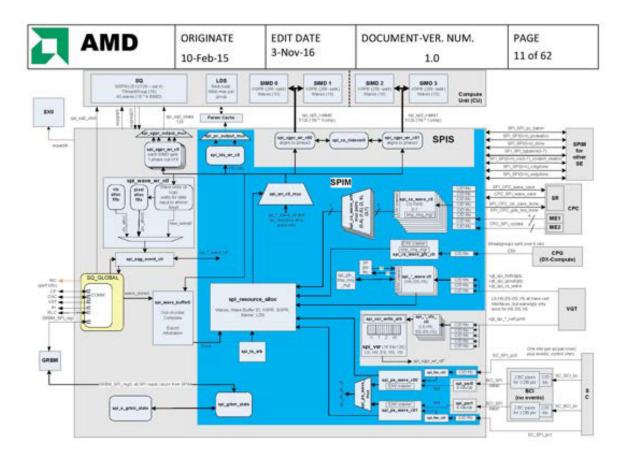

#### 1.3.1 SPI Chip Level Data Flow Diagram

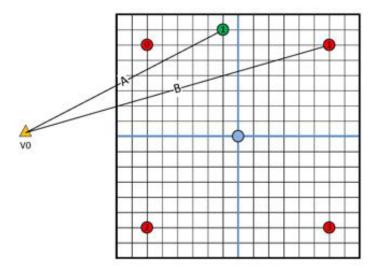

Figure 1 shows the blocks and major data paths directly and functionally associated with the SPI.

Inputs from the VGT: subgroups, waves, events, and vertex input data for the data types VS, GS, ES, HS, LS. Inputs from the SC: pixel data including coverage, primitive information and events. From the CPG: compute state, events, threadgroups for GFX. From the CPC: compute state, events, threadgroups for async compute. Shader input data into the S/VGPRs and wavefront input to the SQ. VS position and parameter cache data writes to the SX and PC. Parameter cache read and LDS write controls.

> ATI Ex. 2027 IPR2023-00922 Page 7 of 62

Referencing Figure 1, for doing just vertex and pixel shading, vertex and primitive type processing are associated with the green colored lines. The VGT initially starts off sending vertex indices in the form of vsverts to the SPI and at the same time sending the primitive connectivity to the PA identifying how those vertices will get built back into primitives. The SPI buffers up the vsverts into a wavefront and once it has received a full wavefront of data, the wave transfer from the VGT will trigger the SPI to release the data to the SQ and feed associated data into the GPRs. When the vertex shader starts processing position data, typically it will send out position early to the position buffers in the SX which then allows the PA to read that position data and start building the primitives and producing those primitives which go through the Scan Converter (SC) to produce pixels. Once the SC has primitives, it will start producing pixels which are fed to the SPI. Once the SPI has a full wavefront of pixels, it will try and send associated data into the GPRs with the wavefront to the SQ. Reads are made to copy parameter data out of the parameter cache and write it into an SPI determined range of LDS in a particular CU.

> ATI Ex. 2027 IPR2023-00922 Page 8 of 62

| ORIGINATE | EDIT DATE | DOCUMENT-VER. NUM. | PAGE    |

|-----------|-----------|--------------------|---------|

| 10-Feb-15 | 3-Nov-16  | 1.0                | 9 of 62 |

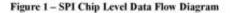

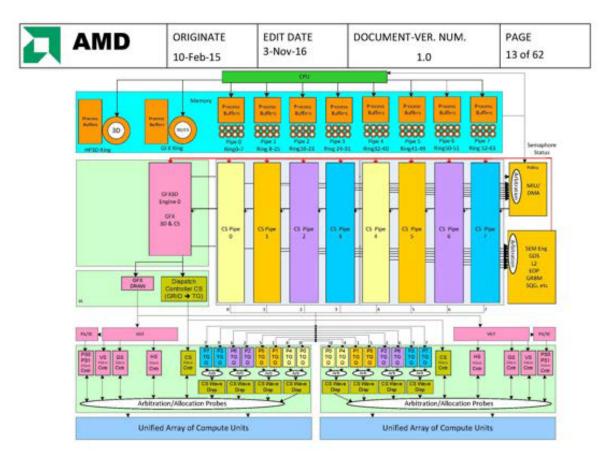

# 1.3.2 Chip Level Diagram

Figure 2 shows the SPI block and its associated relationship to chip level inter-connections. Here, the physical partitioning of baryc logic is shown by the BCI blocks. For the purpose of this document, the BCI logic will be considered as part of the logical SPI design.

Figure 2 - Chip Level Diagram

ATI Ex. 2027 IPR2023-00922 Page 9 of 62

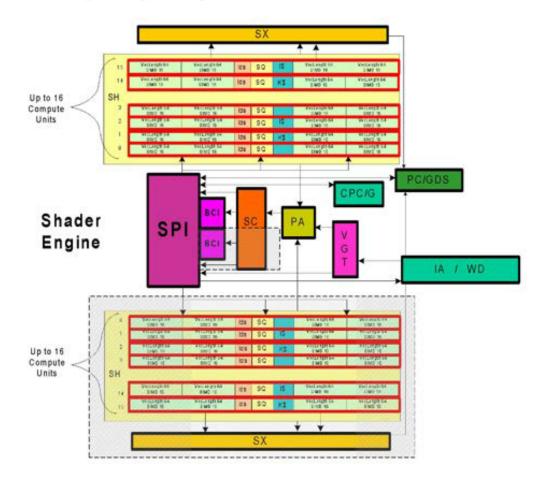

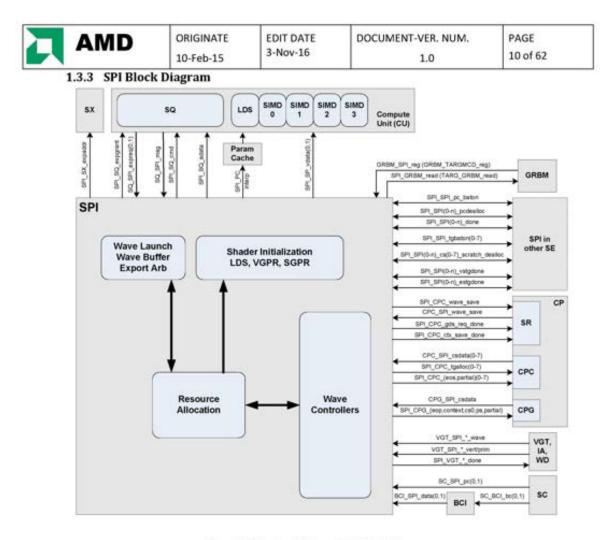

Figure 3 - Top Level Connectivity Block Diagram

Figure 4 - Block Diagram

Diagram copied from //gfxip/gfx9/doc/design/blocks/spi/gfx9\_SPI\_Block\_Diagram.vsd

#### 2 Features / Functionality

#### 2.1 Stage And Organize Data for Shader Launch

The SPI logical block stages and organizes efficient loading of shader input data to the Vector/Scalar General Purpose Registers (VGPR/SGPR) and Local Data Store (LDS) in the Shader Array and manages resources required to run those shader programs. The VGT will have several types of inputs to the SPI: normal vertices that will create positions and parameters for rasterization and pixel processing (VS, which could be normal vertices or the final pass of a Geometry Shader), Geometry Shader (GS) primitives, vertices that only export to memory (ES, which is the first vertex pass of a Geometry Shader), vertices acting as the first stage of tessellation processing (LS), and patch data associated with the Hull Shader (HS). The VS, GS, ES, HS, and LS are often generalized into the category of "verts" when discussing data moving through the SPI. The Scan Converter (SC) delivers pixel quads to the SPI for pixel shading. The CPG block delivers DX11 Compute threadgroups to the SPI for launching compute shaders. The CPC delivers Async Compute threadgroups to the SPI for launching compute shaders.

#### 2.2 Compute Shader (CS)

As shown in Figure 1, Compute Shader input data can come from either the CPG (GFX-CS) or the CPC (Async CS). CS waves go through the same resource arbitration and allocation as all other supported SPI wavefront types.

ATI Ex. 2027 IPR2023-00922 Page 11 of 62

| ORIGINATE | EDIT DATE | DOCUMENT-VER. NUM. | PAGE     |

|-----------|-----------|--------------------|----------|

| 10-Feb-15 | 3-Nov-16  | 1.0                | 12 of 62 |

DX11 requires support for compute shaders, and the SPI plays a role in getting compute shaders into the shader array. Both the CPG and CPC deliver threadgroups to the SPI along with persistent state data that tells the SPI how to process those threadgroups. The SPI is responsible for unrolling each threadgroup into the number of wavefronts required to process all of the threads for the threadgroup.

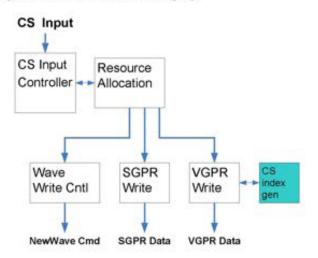

Figure 5 - CS Data Flow

ATI Ex. 2027 IPR2023-00922 Page 12 of 62

Figure 6 - Async Compute Block Diagram

#### 2.2.1 Resource Probing

If there are more than 4 Async Compute Pipes present in a configuration (more than 1 compute ME) then pairs of compute wave controllers will share a single probe to Resource Alloc (RA) for allocating resources. Each of the pair takes alternating turns using the probe to request resources. This probing opportunity will alternate between the two pipelines once every four clocks until a probing pipeline has a work group that fits and is selected by RA. Once a pipeline is selected, it will allocate resources for all waves in its threadgroup before releasing the probe. If only one pipe of a pair has a threadgroup ready to allocate, it will have exclusive use of the probe for requesting resources and can continue requesting on every four clock cycle.

Each CS controller should check its tg\_per\_cu limit, wave\_per\_sh limit, scratch limit, and crawler space before requesting resources so it doesn't take cycles away from the other cs\_ctl sharing a common probe.

#### 2.2.2 Threadgroup Ordering

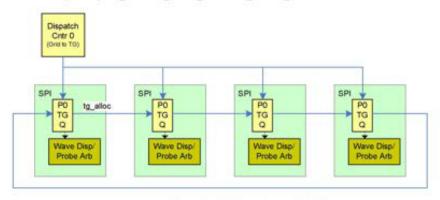

Ordering of threadgroups for a given async compute pipe needs to be maintained across all SE. The Dispatch Controller (DC) assigns threadgroups round-robin to all SE in the chip, and the SPIs from each of those SE must cooperate to ensure that a threadgroup from a given SE is not allowed to probe until the threadgroup before it has won allocation. The SPI needs to wait until the first wave of the previous group allocates, but does not need to wait for all waves of the previous threadgroup.

The Dispatch Controller will send two signals with each threadgroup, first\_group and last\_group to tell the SPI when each dispatch starts and finishes. If a group is marked as first\_group, the CS controller can start requesting immediately without waiting on any previous group. If a task is pre-empted and restarted, the first threadgroup of

> ATI Ex. 2027 IPR2023-00922 Page 13 of 62

| ORIGINATE | EDIT DATE | DOCUMENT-VER. NUM. | PAGE     |  |

|-----------|-----------|--------------------|----------|--|

| 10-Feb-15 | 3-Nov-16  | 1.0                | 14 of 62 |  |

the restart should be marked as first\_group even if it is not the first of the dispatch. Once that first\_group allocates, the allocating controller sends a tg\_alloc pulse to the next SPI in the dispatch sequence so that it can start requesting for its group. For allocating groups marked as last\_group, no tg\_alloc pulse is sent. This scheme avoids any problems that can arise from an implicit ordering scheme where the DC and the SPI both independently manage threadgroup ordering. First\_groups can be sent to any SPI, regardless of where the previous group was sent, and last\_groups won't create any left-over status in the SPI. Power gating and soft\_reset issues are also avoided since no duplicate status needs to be kept in sync between DC and SPI, which are physically in separate tiles.

SPI also supports a mode where a DISPATCH\_INITIATOR write clears the baton for that async compute pipe such that the last\_tg from the dispatch controller is not necessary. This is the default behavior for SPI, but it can be disabled by setting SPI\_CONFIG\_CNTL\_1.BATON\_RESET\_DISABLE to 1.

Figure 7 - CS Threadgroup Ordering

The compute controllers also support disabling of entire SH for a given pipe using the

COMPUTE\_STATIC\_THREAD\_MGMT register. This feature is also known as "steering", and allows a dispatch to be sent only to a subset of the possible SH in a given config. The DC will shadow CU\_EN settings and only send threadgroups to SPI with at least one CU enabled for the dispatch. When passing/receiving tg\_alloc, each SPI needs to check its own CU\_EN settings. If the receiving SPI has a CU\_EN of 0 then it should pass the token along to the next SPI. This passing of the token through disabled SPI adds extra time between threadgroups starting. The ADC will optimize for the case where only a single SH is enabled for a dispatch by marking every threadgroup sent to that single SH as both first and last of group. This way no ordering tokens are passed by the SPI and the single enabled SH is allowed to launch threadgroups as fast as possible.

# 2.2.3 Threadgroup Halting and Discarding

The CS controller will also respond to halt signaling to accomplish precise launch pre-emption. Upon being commanded to halt by the CPC, the controller will finish out any wavefronts from partially started work groups and then stall any subsequent traffic from that pipe.

| Name:                  | Bits: | Description:                                                                                                                                                            |

|------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLIENT_TARGET_halt_req | 1     | If asserted the receiving block must halt the production of<br>compute work at a well-defined pipeline location. After halting,<br>the receiver must return a halt ack. |

If a discard is then requested, any other entries in the input fifo will be popped and discarded before signaling back to the grid dispatcher the SPI has prepared to switch. A discard\_req will always happen within a halt\_req/halt\_ack window. The SPI must be halted before it can be told to discard.

|                       | ORIGINATE<br>10-Feb-15 | EDIT DA<br>3-Nov-1 | 81.57                    | DOCUMENT-VER. NUM.<br>1.0                                                                                                                              | PAGE<br>15 of 62 |

|-----------------------|------------------------|--------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Names<br>CLIENT_TARGE | f_discard_req          | Bits:<br>1         | that has n<br>A client s | I the receiving block discard any pendi<br>ot yet been allocated shader resources<br>hould only assert this when both<br>TARGET_halt_req and TARGET_CL |                  |

The CS controller will drive a tg\_allocated signal to the CP notifying the DC when a threadgroup allocates. This is needed so the DC can track the exact number of groups that launch versus those that are discarded after a halt.

# 2.2.4 Queue Status

Each CS controller maintains a count of active waves for all 8 queues that can drive that pipe. SPI provides that status through GRBM reads using several register decodes. One register, SPI\_CSQ\_WF\_ACTIVE\_STATUS, contains a single ACTIVE bit for each queue of each pipe of a given ME. SPI\_CSQ\_WF\_ACTIVE\_STATUS is indexed by GRBM.ME\_ID. SPI\_CSQ\_WF\_ACTIVE\_COUNT\_{0-7}.COUNT provides the actual number of wavefronts that are in flight for a specific queue. SPI\_CSQ\_WF\_ACTIVE\_COUNT\_{0-7}.EVENTS provides the actual number of events that are in flight for a specific queue. SPI\_CSQ\_WF\_ACTIVE\_COUNT\_{0-7}.EVENTS provides the gRBM.ME\_ID and GRBM.PIPE\_ID.

#### 2.2.5 Unordered Dispatches

DC and SPI also support an Unordered Dispatch mode using the ORDER\_MODE field of the DISPATCH\_INITIATOR. When launching an Unordered dispatch, the Dispatch Controller will send every threadgroup marked with both first/last\_group. This allows the SPI in each SH to launch threadgroups independently without passing or expecting the order baton.

Unordered mode also changes the way SPI responds to halt requests. In the ordered mode, SPI can halt on any threadgroup boundary and return halt\_ack with threadgroups still pending in its input fifo. In the unordered mode, SPI will allocate all threadgroups that have been sent from the DC before returning halt\_ack.

#### 2.2.6 State Forwarding to SQG

All state traffic to each compute pipe needs to be passed to the SQG for logging. State writes are sent from the outputs of credit/debit fifos with arbitration and backpressure to ensure that only 1 controller sends per clock.

#### 2.2.7 First Wave of Dispatch

SPI supports SQ/SQC volatile cache deallocation control by marking the first threadgroup of a dispatch that is sent to each CU and SQC (group of CU). The scoreboard logic used to track when threadgroups are sent to CU/SQC needs to be reset at the start of each dispatch, so each CS wave controller needs to provide this information. The CS wave controller will signal "first wave of dispatch" to RA for the first\_wave request of the first threadgroup after each DISPATCH\_INITIATOR.

SPI is aware of SQ to SQC mapping, both for this invalidate volatile feature as well as CU busy signaling for clkgate control. The SPI is ifdef'ed to handle both different numbers of CU (GPU\_GC\_NUM\_CU\_PER\_SH) and different numbers of CU-per-SQC (GPU\_GC\_MAX\_3\_CU\_PER\_SQC).

#### 2.2.8 Compute Shader Index Terms

For CS, the SPI can load up to 3 index terms as input into the VGPR. This is a 1 to 3-Dimensional incrementing index that represents the relative ID of the thread within its threadgroup known as ThreadIDInGroup. COMPUTE\_PGM\_RSRC2.TIDIG\_COMP\_CNT is used to control the number of components written by the SPI. Here is a simple example of how the SPI would generate the ThreadIDInGroup across the wavefronts with incrementing 3d indices.

For a threadgroup with dimension X=3, Y=16, Z=2, the SPI would create 2 wavefronts to process the 96 valid threads (3\*16\*2). Sequentially, the thread input values would look like this where the X increments first and wraps back to zero. At each wrap point, the Y term would increment all the way up to the Z term incrementing.

ATI Ex. 2027 IPR2023-00922 Page 15 of 62

| ORIGINATE | EDIT DATE | DOCUMENT-VER. NUM. | PAGE     |  |

|-----------|-----------|--------------------|----------|--|

| 10-Feb-15 | 3-Nov-16  | 1.0                | 16 of 62 |  |

Thread0 (X, Y, Z) = 0.0.0Thread1 = 1.0.0 Thread2 = 2.0.0 Thread3 = 0.1.0 Thread95 = 2.15.1

16 threads wide and 4 clocks deep counts demonstrated in Figure 8.

| 0,0,0  | 1,0,0  | 2,0,0  | 0,1,0  | 1,1,0  | 2,1,0  | 0,2,0  | 1,2,0  | 2.2.0   | 0,3,0  | 1,3,0  | 2,3,0  | 0,4,0  | 1,4,0  | 2,4,0  | 0,5,0  |

|--------|--------|--------|--------|--------|--------|--------|--------|---------|--------|--------|--------|--------|--------|--------|--------|

| 1,5,0  | 2,5,0  | 0,6,0  | 1,6,0  | 2,6,0  | 0,7,0  | 1,7,0  | 2,7,0  | 0,8,0   | 1,8,0  | 2,8,0  | 0,9,0  | 1,9,0  | 2,9,0  | 0,10,0 | 1,10,0 |

| 2,10,0 | 0,11,0 | 1.11.0 | 2,11,0 | 0,12,0 | 1,12,0 | 2,12,0 | 0,13,0 | 1,13,0  | 2,13,0 | 0,14,0 | 1,14,0 | 2,14,0 | 0,15,0 | 1,15,0 | 2,15,0 |

| 0,0,1  | 1,0,1  | 2,0,1  | 0,1,1  | 1,1,1  | 2,1,1  | 0,2,1  | 1,2,1  | 2,2,1   | 0,3,1  | 1,3,1  | 2,3,1  | 0,4,1  | 1,4,1  | 2,4,1  | 0,5,1  |

| 1.5.1  | 2.5,1  | 0,6,1  | 1,6,1  | 2,6,1  | 0,7,1  | 1.7.1  | 2.7.1  | 0.8.1   | 1.8.1  | 2.8,1  | 0,9,1  | 1,9,1  | 2,9,1  | 0,10,1 | 1,10,1 |

| 2,10,1 | 0,11,1 | 1,11,1 | 2,11,1 | 0,12,1 | 1,12,1 | 2,12,1 | 0,13,1 | 1.13.1  | 2,13,1 | 0,14,1 | 1,14,1 | 2,14,1 | 0,15,1 | 1,15,1 | 2,15,1 |

| X,XX,X | X,XX,X | X,XX,X | X.XX,X | XXXX   | X,XX,X | X,XX,X | X,XX,X | X,XX,X  | xxxx   | XXXX   | XXXX   | X,XX,X | 3,33,3 | 3,33,3 | XXXX   |

| X,XX,X | x,xx,x | X,XX,X | XXXX   | XXXX   | X,XX,X | X,XX,X | X,XX,X | X.XXX.X | XXXX   | XXXX   | XXXX   | X.XX,X | X,XX,X | XXXX   | XXXX   |

#### Figure 8 - CS Thread Count Increment Example

# 2.3 VGT-SPI "Vert" Shaders

The SPI can receive one thread per clock from the VGT for each of LS, HS, ES, GS, and VS. The LS, ES, and VS interfaces are all 128 bits wide, GS is 87 bits wide, and HS is 45 bits. The SPI takes a serial stream of up to 64 threads from the VGT (one wavefront) and accumulates it into four parallel lines in the Vertex Staging Register (VSR), matching the VGPR write format and allowing the SPI to minimize the VGPR input cycles for vertex data. The interface between the SPI and the VGPRs is 16 verts \* 1 component wide and the SPI is always trying to write 16 threads per cycle into the GPRs. The SPI arbitrates on 4 clock cycles so every time a particular type gets to write into the VGPRs ir really wants to write 64 threads, 16 at a time, over 4 cycles. If the SPI tried to write immediately to the VGPRs every time the VGT came in with 1 serial thread, the other 63 threads of the 4 clock cycle would be wasted.

Figure 9 shows the serial stream from the VGT being packed into this 16 wide over 4 clock wavefront.

Figure 9 - "Vertex" Data Flow VGT-SPI

| ORIGINATE | EDIT DATE | DOCUMENT-VER. NUM. | PAGE     |  |

|-----------|-----------|--------------------|----------|--|

| 10-Feb-15 | 3-Nov-16  | 1.0                | 17 of 62 |  |

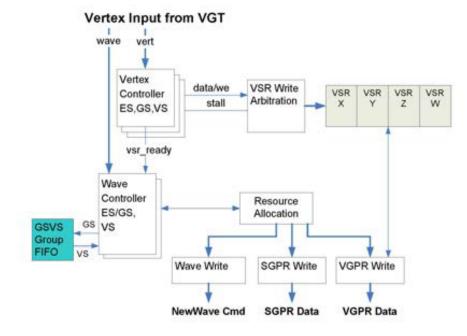

# 2.3.1 ES, GS, VS Processing

In GFX9 the change was made to combine ES and GS processing into a single shader stage so there is no need to synchronize ES-done to GS-start. There is also no need for SPI to pass parent CU information from ES to GS groups like was necessary for onchip-GS processing in previous families. The synchronization of GS to VS processing is handled outside of the SPI (VGT waits on gscount\_done from GS shader before generating VS). If GS is passing data to VS using onchip LDS (onchip-GS) then SPI must pass subgroup information from the producing GS to the consuming VS subgroup.

Each vertex controller runs independently, with the only interaction being the arbitration for writes to a particular VSR, until wavefronts request for resource allocation. There is only one copy of VSR memory composed of multiple banks which hold the different components. There is a simple priority arbitration here to make sure there are no data collisions when multiple controllers need to write to the same memory banks. The priority order is a fixed lowest-to-highest of LS, HS, ES, GS, VS. Space for multiple wavefronts exists for each type in the SPI which allows the SPI to start copying one wavefront while the VGT starts sending the next wavefront.

Once a full wavefront of vertex indices are written into the VSR and the associated wave transfer from the VGT has occurred to let the SPI know it is ok to issue that wavefront, the Vertex Wave Controllers will try to allocate the resources that the shader needs to execute in the shader complex. In the case of LS/HS and ES/GS groups, SPI waits until all transfers of all waves of the group (LS-vert/HS-vert or ES-vert/GS-prim) have been received before trying to launch the group. This means the VSR must be able to hold an entire group's worth of data, up to a max of 4 wavefronts, for each of these group types. If the wave/group wins resources allocation, the wave control information (resource bases/sizes, state\_id, pipe\_id, etc) is sent to the shader input write controllers to load the wavefront to the Shader Array.

Figure 10 - VGT ES, GS, VS Vertex Input

| ORIGINATE | EDIT DATE | DOCUMENT-VER. NUM. | PAGE     |  |

|-----------|-----------|--------------------|----------|--|

| 10-Feb-15 | 3-Nov-16  | 1.0                | 18 of 62 |  |

# 2.3.2 On-chip GS

Onchip GS mode allows the use of onchip LDS space to store the ESGS and GSVS ring buffers, eliminating the traffic to offchip memory that is necessary for offchip modes. Typically scenarios with small amplification will benefit the most from this approach. Prior offchip ES/GS modes used two offchip ring buffers that wrapped individually, and were of a fixed size and base for the entire application. In the new combined ES/GS shader the passing of data from ES to GS is always done using onchip LDS space. Onchip versus offchip GS now refers to how data is being passed from the GS stage to the VS stage.

The VGT partitions the ES/GS work into smaller chunks called subgroups. Each ES/GS subgroup gets allocated to a Compute Unit (CU) by the SPI and for onchip GS that subgroup stays on the same CU for the duration of its lifetime (which is ES/GS/VS). Onchip GS mode requires the SPI to maintain a task grouping for ES/GS/VS processing. ES/GS waves in a subgroup (waves between first/last of subgroup) must all go to the same CU and need to share a common LDS base and size. The subsequent VS subgroup must also go to the same CU and launch with the same LDS base and size and this information is communicated through the GS-to-VS group fifo.

SPI offers a means of controlling "subgroups between GS output and VS consumption". SPI\_SHADER\_PGM\_RSRC4\_GS.GROUP\_FIFO\_DEPTH will set a limit on the number of groups between GS launch and VS launch. This limit will also support scaling through the SPI\_WCL\_PIPE\_PERCENT\_GFX.GS\_GRP\_VALUE register field.

The SPI also has to know when all waves of a VS subgroup have completed so that the onchip-GS LDS can be freed.

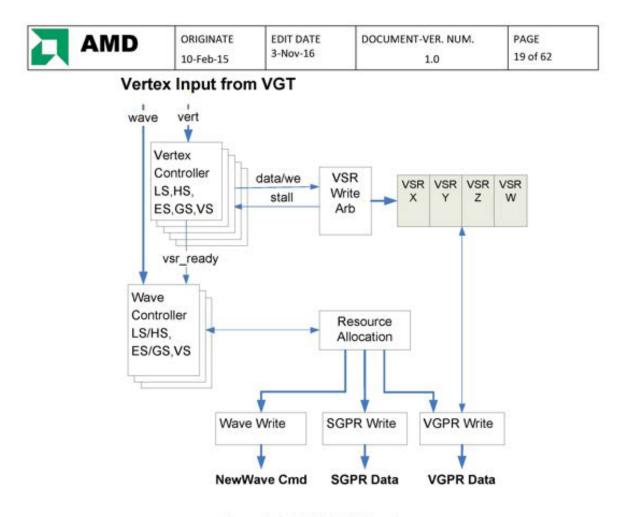

# 2.3.3 Tessellation

DX11 Tessellation requires two vertex types through the SPI: LS and HS. LS is the API vertex shader which writes to the LDS, and HS is the hardware stage that creates tessellation factors for the tessellation engine and output data for the Domain Shader. The hardware shader stage flow is LS/HS->DS(ES/GS,VS), depending on whether geometry shading is enabled (ES/GS) or not (VS). The passing of computed results from LS to HS is always done using the onchip LDS of the executing CU. LDS is a per-CU resource and only waves sent to that CU can access it, so all waves of a tessellation threadgroup must be sent to the same CU. The onchip LDS space associated with an LS/HS threadgroup is freed when the final HS of the group completes

HS-to-DS data is always passed using offchip buffering and SPI is responsible for managing this offchip LDS space. SPI allocates a buffer with each LS/HS threadgroup and then frees the buffer once all DS that source the data are complete.

Figure 11 - LS, HS, ES, GS, VS Vertex Input

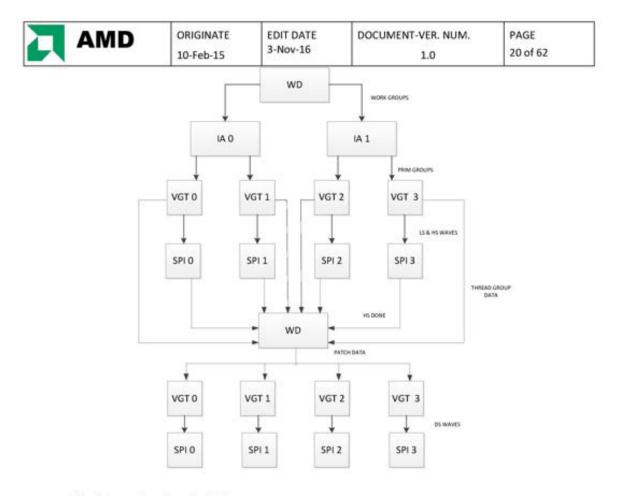

# 2.3.4 Distributed Tessellation

The intention of distributed tessellation is to rebalance the DS work after the HS stage in order to generate new primgroups with post tessellation primitives. This enables the workload to be distributed more uniformly amongst the available VGT and SH units for an overall higher performance.

> ATI Ex. 2027 IPR2023-00922 Page 19 of 62

The diagram above shows the data flow.

Note that commonly named blocks such as VGT 0, WD etc are the same physical block (not duplicated) just redrawn for clarity.

Note that all variants have this architecture, the legacy patch distribution method of all DS sent to parent SH is still supported but the infrastructure is changed to the above.

#### 2.3.4.1 Work Creation Description

The unit of work that the VGT creates is a threadgroup. There could be multiple threadgroups present in the primgroup each VGT receives. LS/HS verts are created for the entire threadgroup and then the HS threadgroup transfer is sent to the SPI. A FLUSH\_HS\_OUTPUT event is inserted after all each threadgroup transfer. The SPI allocates onchip LDS space and an offchip LDS buffer for each LS/HS threadgroup. The SPI sends the VGT an HS\_done signal per threadgroup when the entire threadgroup completes.

The WD needs to process threadgroups in the order they were issued originally by the WD/IA/VGT when producing DS threadgroups. There is a HS threadgroup done counter per VGT which is incremented when the respective HS\_done is received from the SPI. At the beginning of the packet, the VGT fifo with a threadgroup tagged first\_primgroup will be processed first. This will ensure the launch order of the LS/HS is maintained. After this threadgroup is popped off, its next\_fe\_id field will be used to determine which fifo to read from next. All the

> ATI Ex. 2027 IPR2023-00922 Page 20 of 62

| ORIGINATE | EDIT DATE | DOCUMENT-VER. NUM. | PAGE     |  |

|-----------|-----------|--------------------|----------|--|

| 10-Feb-15 | 3-Nov-16  | 1.0                | 21 of 62 |  |

tessellation factors for the patches in an entire threadgroup are fetched from memory and the patches are then sent to the distribution logic.

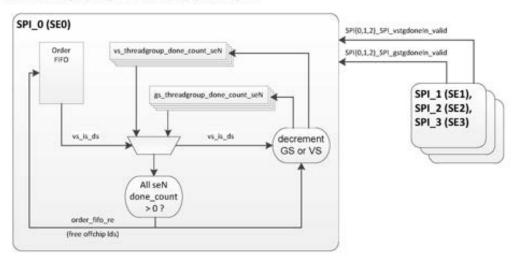

Each VGT will receive patches that will potentially be tagged with start/stop points. Each VGT will only tessellate the portion of the patch that is active and will issue the respective DS waves to the SPI. The WD will create and insert the OFFCHIP\_HS\_DEALLOC event at the end of each DS threadgroup and broadcast it to all VGT, attaching the appropriate VGT\_ID to the event so the SPI knows which frontend allocated the offchip space for the threadgroup. The VGT\_ID of the original threadgroup will be sent on the new parent\_se[1:0] field of the VS\_wave or GS\_subgrp interfaces. The SPI will launch the DS waves on any available CU and the HS output data will be fetched from offchip memory. Once all DS of the threadgroup complete the SPI will handle the OFFCHIP\_HS\_DEALLOC event by incrementing either gs\_offchip\_done\_count or vs\_offchip\_done\_count in the appropriate SPI as identified by parent\_se. If an SPI sees an event with a parent\_se that does not match its own SE\_ID, a done signal will be forwarded to the appropriate SPI. Offchip LDS will always be deallocated by the OFFCHIP\_HS\_DEALLOC event, occurring when the event pops off the SPI's event/wave crawler.

#### 2.3.4.2 Offchip LDS ID Changes

With distributed tessellation the DS from a given LS/HS can be sent to other SE and those other SE do not have access to the parent SPI's group information. Because of that, the distributed DS need another way to get the offchip\_lds\_id allocated to their parent LS/HS. The WD will add a per-SE offchip\_lds\_id counter that increments for each tessellation threadgroup that is issued to that SE. This offchip\_lds\_id will be stored through the WD and VGT for each outstanding threadgroup and patch and then sent to the SPI with every DS wave on the GS or VS wave interface. The event\_id field on these interfaces is increased to 7 bits and is used to send offchip\_lds\_id for wave or subgroup transfers.

SPI still allocates offchip space with LS/HS and makes sure that the next buffer is available, but the ID is assigned by and delivered from the WD. VGT\_HS\_OFFCHIP\_PARAM.OFFCHIP\_BUFFERING specifies the current number of offchip buffers and offchip\_lds\_id should reset to 0 for each SE whenever that register value changes (SPI does not reset if the register is rewritten with the same value). OFFCHIP\_BUFFERING is divided between the number of SE in the config, regardless of front-end harvesting, and each SE's ID should count from 0 to ((BUFFERING/NUM\_SE) – 1).

The OFFCHIP\_BUFFERING field will range 0-511 representing 1-512 buffers. A setting of 0 is not useful for this register and being able to represent 512 allocated buffers allows support for 128 buffers \* 4 SE in larger configurations.

The offchip\_lds\_id sent to SPI will be a total of nine bits, two bits of parent\_se and the seven bit event\_id carrying offchip\_lds\_id count from the parent LS/HS.

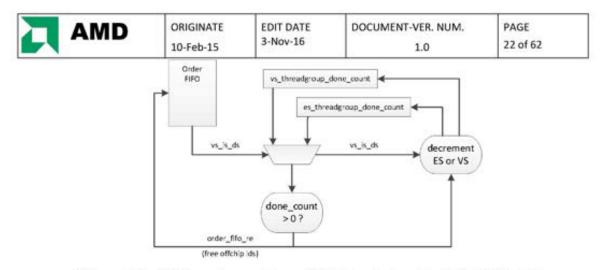

#### 2.3.4.3 Offchip LDS Deallocation Changes

In previous projects the work associated with a given SE's offchip LDS allocation was only ever sent to that same SE. This meant that all LS/HS/DS for a threadgroup went to the same SE and a given SE's offchip space could be deallocated based solely on work completing in that SE. ES and VS executing as DS could also potentially complete out of order with respect to each other, and offchip LDS manager dealt with that by keeping a FIFO history of allocation order (ES/VS is DS) along with group done counts for each of GS and DS.

> ATI Ex. 2027 IPR2023-00922 Page 21 of 62

SPI incremented the ES/VS group done count when an ES/VS lastwave that launched with offchip LDS enabled popped from a wave controller's crawler, maintaining order within a shader stage. Once the done count corresponding to the order FIFO output was greater than 0, SPI would deallocate the offchip space, pop the order FIFO, and decrement the appropriate done\_count.

Distributed Tessellation means that tessellation work originating on a given SE (and therefore associated with that SE's managed offchip space) can also be sent to other SE. This means that a given SE has to ensure that all other SE are done using an offchip allocation before deallocating and reusing that space. In order to handle this, the SPI will use a scheme similar to the one used for parameter cache deallocation across multiple Shader Engines where the SPI signal to each other when they see a dealloc they do not own. For instance, if SPI2 pops an OFFCHIP\_HS\_DEALLOC event with a VGT\_ID of 0 from a VS or GS crawler then it will send a signal to SPI0 rather than doing anything with its own offchip LDS mgmt.

Each SPI has to keep a done count for every SE and check that all done counts are greater than zero before freeing an offchip LDS buffer. When offchip LDS is freed, all SE done counts for the freeing shader stage (GS or VS)

> ATI Ex. 2027 IPR2023-00922 Page 22 of 62

| ORIGINATE | EDIT DATE | DOCUMENT-VER. NUM. | PAGE     |  |

|-----------|-----------|--------------------|----------|--|

| 10-Feb-15 | 3-Nov-16  | 1.0                | 23 of 62 |  |

decrement together. If a frontend is disabled (as specified by CC\_GC/GC\_USER\_PRIM\_CONFIG regs) then the SPI attached to that frontend will not receive an OFFCHIP\_HS\_DEALLOC event. The SPI's offchip LDS deallocation logic should not wait for pulses from other SPI that are connected to disabled frontends, and also should not decrement the done count associated with those SPI. All counts associated with a disabled frontend SPI should be held at 0 as long as the frontend is disabled so that the counts will be in a known good state if the frontend is enabled at a later time.

The move to only supporting offchip tessellation (HS-DS only through offchip LDS) means that SPI no longer needs an HS-DS group fifo to pass information to the DS stage. However, SPI does still offer a means of controlling "groups between HS output and DS consumption" similar to what the programmable depth group fifo offered previously. SPI\_SHADER\_PGM\_RSRC3\_HS.GROUP\_FIFO\_DEPTH will set a limit on the number of groups between LS/HS offchip allocation and DS consumption. This limit will also support scaling through the SPI\_WCL\_PIPE\_PERCENT\_GFX.HS\_GRP\_VALUE register field.

#### 2.4 Pixel Shader (PS)

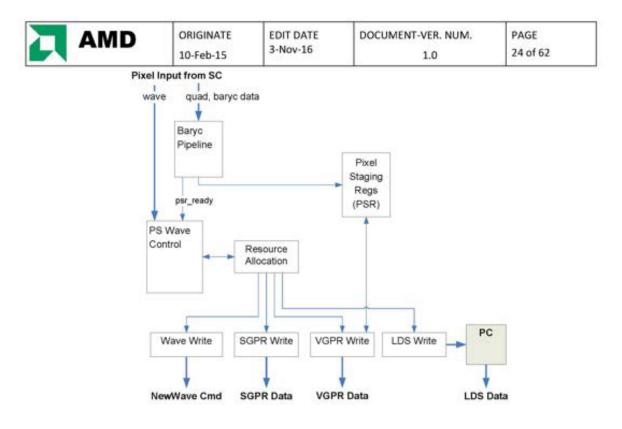

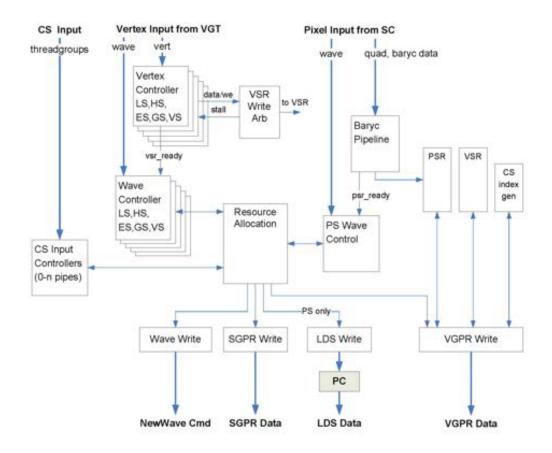

Figure 12 shows the flow of pixel data through the SPI. The SPI gets input data for pixels from the Scan Converter (SC). Wave control information tells the SPI which quads are hit, parameter cache sync and deallocation tokens, and if the transfer is an event. The SC also delivers quad and per primitive barycentric information to the Baryc interpolation math. As quads are being received from the SC, the Pixel Input Controller will buffer the control information until a full wavefront is received. The quad information is also flowing down the barycentric math pipe where the SPI calculates the per pixel IJ and W terms and can also store off screen X/Y, primitive facedness, and other ancillary terms. That data gets delivered to the Pixel Staging Registers for storage until the wavefront is ready to launch. Once a full wavefront is accumulated, the SPI requests to allocate resources and, once granted, the wavefront is sent to the various Write Controllers which coordinate the loading of PS data to the SH.

PSR data is read and sent into VGPRs, attribute data is copied from the PC into the LDS of the appropriate CU, and other various terms are written into SGPRs. Once the full wavefront of pixel data is sent to VGPRs, SGPRs, and the LDS, the Wave Write Controller sends the wave to the SQ to initiate pixel shader execution.

> ATI Ex. 2027 IPR2023-00922 Page 23 of 62

Figure 12 - Pixel Input Data

# 2.4.1 Pixel Data Flow

SPI accepts pixel quad rows from the SC at the peak rate of 2 quads (8 pixels) per clock per packer containing:

- Primitive control data:

- parameter cache base pointers where attributes of the vertices that created the primitives that created those pixels are located in the parameter cache

- first\_prim\_of\_slot aka new\_vector this is how the SPI makes sure the attribute data for the primitives that created these pixels is actually in the parameter cache before a read is attempted

- dealloc tokens lets the SPI know that this is the last prim from the last vertex of a VS wavefront so it is ok to free up all of the associated attribute data

- end\_of\_vector flag Informs the SPI this is the last row of a pixel wavefront, and can happen early prior to getting all 16 quads

- first\_quad\_of\_prim Attached to the first quad created by each primitive

- prim\_type associated with each quad

Quad Data:

screen (X,Y) - where the quad is located in screen space

centermost sample id - The centroid of each pixel in each quad

iterated sample number - which sample is running during sample frequency pixel shading

per pixel coverage - mask identifying all hit pixel samples as determined by the SC

Primitive Data:

perspective/linear barycentric gradients, depth (Z) information

ATI Ex. 2027 IPR2023-00922 Page 24 of 62

| ORIGINATE | EDIT DATE | DOCUMENT-VER. NUM. | PAGE     |  |

|-----------|-----------|--------------------|----------|--|

| 10-Feb-15 | 3-Nov-16  | 1.0                | 25 of 62 |  |

#### 2.4.1.1 Calculate Per-Pixel IJ Barycentric Coordinates

The SPI receives IJ gradient information from the SC on a per quad basis (all values are 32-bit IEEE).

InvW0 – value of 1/W at ref vtx (value of line\_stipple\_tex\_coord at ref vtx with linear gradient) InvWdx – 1/W rate of change in x (line\_stipple\_tex\_coord rate of change with linear gradient) InvWdy – 1/W rate of change in y (line\_stipple\_tex\_coord rate of change with linear gradient) IW0 – value of I/W at ref vtx IWdx – I/W rate of change in x IWdy – 1/W rate of change in y JW0 – value of J/W at ref vtx JWdx – J/W rate of change in x JWdx – J/W rate of change in x

The SPI uses the following equations to calculate per-pixel I,J,W. One barycentric triplet (I,J,W) is computed per cycle per quad, so all of the math below is instanced per quad in each SPI.

The SPI calculates the distance of the current quad's upper left pixel to the reference vertex and uses that distance to calculate the terms IWref, JWref, and InvWref which are the values at the upper left pixel of the quad and known as the "reference pixel".

```

Reference Pixel (1 per quad):

(delta_x and delta_y are 16.8 2's comp convert to flt pt distance of quad UL pixel from vertex 0)

IWref = IWo + (delta_x * Iwdx) + (delta_y * Iwdy)

JWref = JWo + (delta_x * Jwdx) + (delta_y * Jwdy)

InvWref = InvWo + (delta_x * InvWdx) + (delta_y * InvWdy)

```

IJ and per pixel W values are stored in 32-bit IEEE float.

#### Delta Pixels (3 per quad):