|                         | ORIGINATE DATE                       | EDIT DATE                               | DOCUMENT-REV. NUM.                                                          | PAGE           |

|-------------------------|--------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------|----------------|

|                         | 24 September, 2001                   | 4 September, 201519                     | GEN-CXXXXX-REVA                                                             | 1 of 58        |

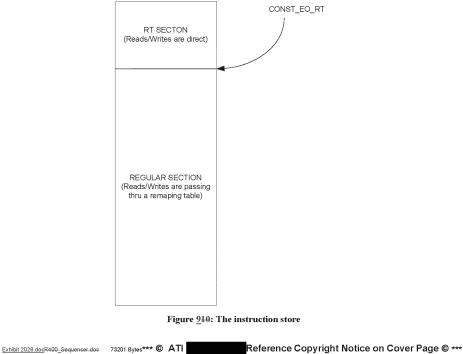

| Author:                 | Laurent Lefebvre                     | L                                       |                                                                             | 1              |

|                         |                                      |                                         |                                                                             |                |

| Issue To:               |                                      | Copy No:                                |                                                                             |                |

|                         |                                      |                                         |                                                                             |                |

|                         | R400 S                               | equencer Spe                            | ecification                                                                 |                |

|                         |                                      | 8 8                                     |                                                                             |                |

|                         |                                      | SQ                                      |                                                                             |                |

|                         |                                      |                                         |                                                                             |                |

|                         |                                      | Version <del>1.11</del> 2.0             |                                                                             |                |

|                         |                                      |                                         | e                                                                           |                |

|                         |                                      |                                         | cer block (SEQ). It provides an over<br>lso describes the block interfaces, |                |

|                         | ocks, and provides internal st       |                                         | iso describes the block interfaces,                                         | intenial sub-  |

|                         |                                      |                                         |                                                                             |                |

|                         |                                      |                                         |                                                                             |                |

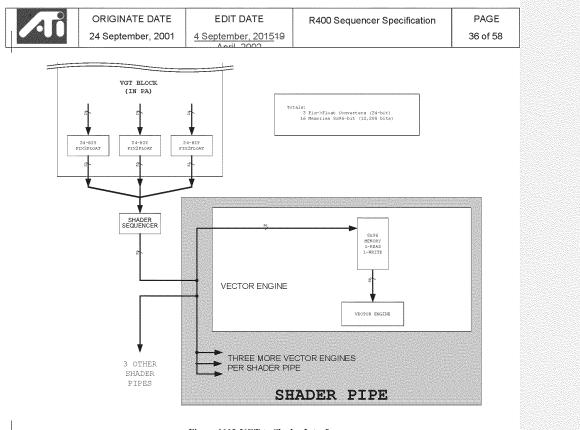

|                         |                                      |                                         |                                                                             |                |

| AUTOMATIC<br>Document L | ALLY UPDATED FIELDS:                 | arfarca\r400\dag_lib\dagian\b           | Nocks/sa/P400_Sogueneer.doe                                                 |                |

|                         |                                      | Control Sequencer Specification         | olocks\sq\R400_Sequencer.doc                                                |                |

|                         | Name/Dept                            | APPROVALS                               | Signature/Date                                                              |                |

|                         |                                      | 20.000000000000000000000000000000000000 | olghatalo, Sato                                                             |                |

|                         |                                      |                                         |                                                                             |                |

|                         |                                      |                                         |                                                                             |                |

| Remarks:                |                                      |                                         |                                                                             |                |

| . comanto.              |                                      |                                         |                                                                             |                |

| THIS DO                 | CUMENT CONTAIN                       | S                                       | NFORMATION THAT CO                                                          | ULD BE         |

| SUBSTA                  | ANTIALLY DETRIME                     | NTAL TO THE INTE                        | REST OF ATI TECHNOL                                                         | OGIES          |

|                         | INC. THROUGH L                       | JNAUTHORIZED US                         | SE OR DISCLOSURE.                                                           |                |

|                         |                                      |                                         |                                                                             |                |

| *O                      |                                      | 1                                       |                                                                             |                |

| work created i          | n 2001. The use of this cop          | pyright notice is intended to           | rial in this document constitutes an<br>provide notice that ATI owns a cor  | yright in this |

| pr                      | roprietary information and tra       | ade secrets of ATI. No part             | publication has occurred. This w<br>of this document may be used, re        |                |

| transmitted in a        | any form or by any means wit         | thout the prior written permis          | sion of ATI Technologies Inc."                                              |                |

|                         |                                      |                                         |                                                                             |                |

| Exhibit 2028.do         | ©R400_Sequencer.doc 73201 Bytes*** @ | ATI                                     | nce Copyright Notice on Cover Pa                                            | ge © ***       |

|                         |                                      |                                         |                                                                             | -              |

ATI 2028 LG v. ATI IPR2015-00325

AMD1044\_0017308

ATI Ex. 2011 IPR2023-00922 Page 1 of 58

|                                                                                                                                                                                                                                                                                                                                                   | ORIGINATE DATE                                                                                                                                                                                                                                                          | EDIT DATE                                                 | R400 Sequencer Specification | PAGE                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                   | 24 September, 2001                                                                                                                                                                                                                                                      | <u>4 September, 2015</u> 19                               |                              | 2 of 58                                                                                                                                                                                                                       |

| <ol> <li>1.1 Top Lo</li> <li>1.2 Data F</li> <li>1.3 Contro</li> <li>2. INTEF</li> <li>3. INSTF</li> </ol>                                                                                                                                                                                                                                        | VIEW<br>evel Block Diagram<br>Flow graph (SP)<br>Graph<br>RPOLATED DATA BU<br>RUCTION STORE                                                                                                                                                                             | JS                                                        |                              | <u>98</u><br><u>13</u> 10<br><u>14</u> 11<br><u>14</u> 11<br><u>17</u> 14                                                                                                                                                     |

| 5.         CONS           5.1         Memo           5.2         Manag           5.3         Manag                                                                                                                                                                                                                                                | TANT STORES<br>ry organizations<br>gement of the Control<br>gement of the re-map                                                                                                                                                                                        | Flow Constants<br>ping tables                             |                              |                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                         |                                                           | <br>t                        |                                                                                                                                                                                                                               |

| 5.3.3 (                                                                                                                                                                                                                                                                                                                                           | Dirty bits                                                                                                                                                                                                                                                              |                                                           | t                            | <u>20</u> 17                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                         |                                                           |                              |                                                                                                                                                                                                                               |

| 5.4         Const.           5.5         Real T           5.6         Const.           6.         LOOP           6.1         The const.           6.2         The C           6.3         Data const.           6.4         HW D           6.5         Regist           6.6         Predict           6.7         Debug           6.7.1         1 | ant Store Indexing<br>Time Commands<br>ant Waterfalling<br><b>ING AND BRANCHE</b><br>pontrolling state<br>ontrol Flow Program.<br>dependant predicate in<br>etection of PV,PS<br>ter file indexing<br>ated Instruction supp<br>gging the Shaders<br>Method 1: Debugging | S<br>Instructions<br>ort for Texture clauses<br>registers | ss. (12)                     | 2118<br>2219<br>2219<br>2320<br>2320<br>2320<br>2922<br>2923<br>2923<br>2923<br>3023<br>30                                                                                                                                    |

| 7.         PIXEL           8.         MULT           9.         REGIS           10.         FETC           11.         ALU #           12.         HAND           13.         CONT           14.         THE C           15.         IJ FOI           15.1         Inter           16.         STAG           17.         THE F                   | KILL MASK<br>IPASS VERTEX SHA<br>STER FILE ALLOCAT<br>H ARBITRATION<br>ARBITRATION<br>ING STALLS<br>ENT OF THE RESER<br>DUTPUT FILE<br>POLATION OF CONSTANT A<br>ING REGISTERS<br>PARAMETER CACHE                                                                       | ADERS (HOS)<br>FION.<br>RVATION STATION F                 | IFOS                         | <u>3124</u><br><u>3124</u><br><u>3124</u><br><u>3226</u><br><u>3226</u><br><u>3327</u><br><u>3327</u><br><u>3327</u><br><u>3327</u><br><u>3327</u><br><u>3327</u><br><u>3428</u><br><u>3428</u><br><u>3428</u><br><u>3630</u> |

Exhibit 2028.docR400\_Sequencer.doc 73201 Bytes\*\*\* © ATI

Reference Copyright Notice on Cover Page © \*\*\*

AMD1044\_0017309

ATI Ex. 2011 IPR2023-00922 Page 2 of 58

|         | ORIGINATE DATE         | EDIT DATE           | DOCUMENT-REV. NUM. | PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|------------------------|---------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 24 September, 2001     | 4 September, 201519 | GEN-CXXXXX-REVA    | 3 of 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         |                        |                     |                    | SWARADOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         |                        |                     |                    | serverseers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         |                        |                     |                    | and the second se |

|         |                        |                     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                        |                     |                    | SANDADORA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         |                        |                     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                        |                     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.1 Rea | I time commands        | ****                |                    | <u>39</u> 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         |                        |                     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                        |                     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 22.3.1  |                        |                     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 22.3.2  |                        |                     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                        |                     |                    | BOLING BOLING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | ,                      |                     | *****              | ARRONAL ARRONAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                        |                     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                        |                     | ****               | boutowitable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         |                        |                     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                        |                     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                        |                     |                    | BOUNDARY .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |                        |                     |                    | accounts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         |                        |                     | ****               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                        |                     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                        |                     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 27.2.1  |                        |                     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 27.2.2  | SC_SQ                  |                     |                    | <u>43</u> 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 27.2.3  | SQ to SX: Interpolato  | r bus               |                    | <u>45</u> 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 27.2.4  | SQ to SP: Staging Re   | gister Data         |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

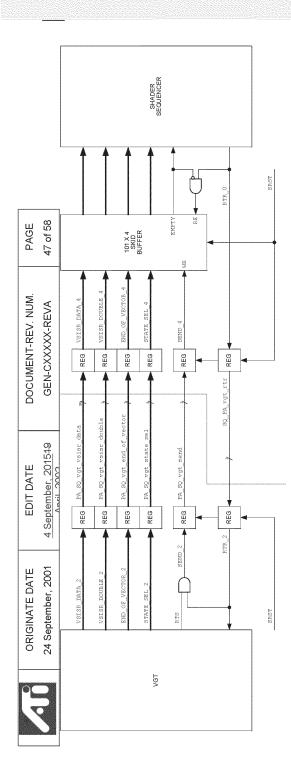

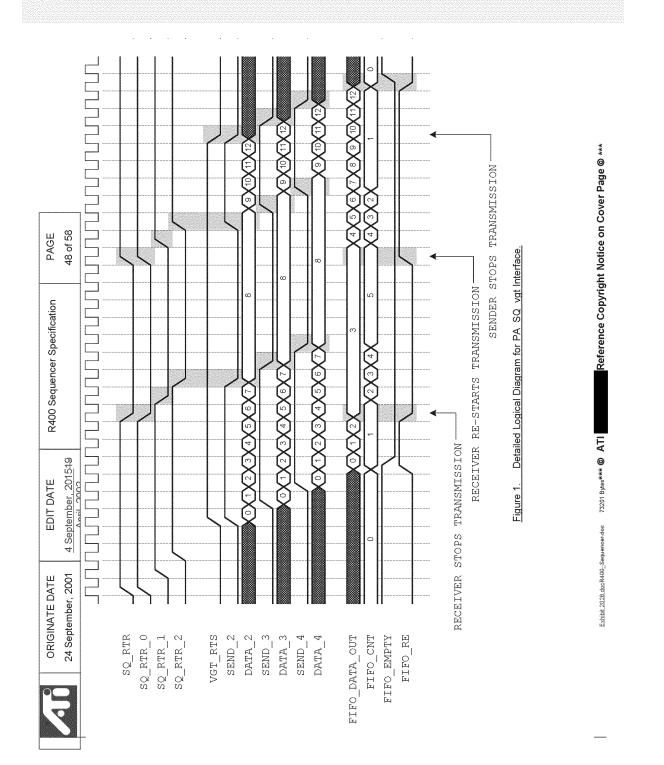

| 27.2.5  | VGT to SQ : Vertex in  | terface             |                    | <u>45</u> 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 27.2.6  | SQ to SX: Control bus  | \$                  |                    | <u>49</u> 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 27.2.7  | SX to SQ : Output file | control             |                    | <u>49</u> 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 27.2.8  | SQ to TP: Control bus  | \$                  |                    | 5041                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 27.2.9  |                        |                     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 27.2.10 |                        |                     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 27.2.11 |                        |                     |                    | *******                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 27.2.12 |                        |                     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 27.2.12 |                        |                     | Set                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 27.2.13 |                        |                     | Jet                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 27.2.14 |                        |                     |                    | ********                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         |                        |                     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 27.2.16 | SQ TO CP: RBBM bus     |                     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

ATI Ex. 2011 IPR2023-00922 Page 3 of 58

|                                | ORIGINATE DATE<br>24 September, 2001 | EDIT DATE<br>4 September, 201519        | R400 Sequencer Specification | PAGE<br>4 of 58 |  |  |

|--------------------------------|--------------------------------------|-----------------------------------------|------------------------------|-----------------|--|--|

|                                | 24 September, 2001                   | 4 September, 2015+8<br>April 2002       |                              | 4 01 06         |  |  |

| 27.2.17 CP to SQ: RBBM bus     |                                      |                                         |                              |                 |  |  |

| 27.2.18 SQ to CP: State report |                                      |                                         |                              |                 |  |  |

|                                |                                      | * * * * * * * * * * * * * * * * * * * * |                              | <u>58</u> 44    |  |  |

Exhibit 2028.docR400\_Sequencer.dec 73201 Bytes\*\*\* © ATI

Reference Copyright Notice on Cover Page © \*\*\*

AMD1044\_0017311

ATI Ex. 2011 IPR2023-00922 Page 4 of 58

|                                  | ORIGINATE DATE     | EDIT DATE                                                                              | DOCUMENT-REV. NUM.                                                         | PAGE      |  |

|----------------------------------|--------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------|--|

|                                  | 24 September, 2001 | <u>4 September, 2015</u> 19                                                            | GEN-CXXXXX-REVA                                                            | 5 of 58   |  |

| Revision                         | Changes:           | April 2002                                                                             |                                                                            | 1         |  |

| Rev 0.1 (Laur                    | ent Lefebvre)      | First dra                                                                              | ıft.                                                                       |           |  |

| Date: May 7, 2                   |                    |                                                                                        |                                                                            |           |  |

| Rev 0.2 (Laure                   |                    |                                                                                        | d the interfaces to reflect the change                                     |           |  |

| Date : July 9, 2                 |                    |                                                                                        | led some details in the arbitration see                                    |           |  |

| Rev 0.3 (Laure                   |                    |                                                                                        | ed the Sequencer spec after the me                                         | eting on  |  |

| Date : August<br>Rev 0.4 (Laure  |                    | August :                                                                               | the dynamic allocation method for                                          | rogistor  |  |

| Date : August                    |                    |                                                                                        | an example (written in part by Vic                                         |           |  |

|                                  | ,                  |                                                                                        | ixels/vertices in the sequencer.                                           | ,         |  |

| Rev 0.5 (Laure                   | ent Lefebvre)      |                                                                                        | iming diagrams (Vic)                                                       |           |  |

| Date : Septem                    |                    |                                                                                        | · /                                                                        |           |  |

| Rev 0.6 (Laure                   |                    |                                                                                        | d the spec to reflect the new                                              | / R400    |  |

| Date : Septem                    |                    |                                                                                        | ture. Added interfaces.                                                    |           |  |

| Rev 0.7 (Laure                   |                    |                                                                                        | constant store management, ins                                             |           |  |

| Date : October                   | 5, 2001            |                                                                                        | anagement, control flow management                                         | ent and   |  |

| Rev 0.8 (Laure                   | ont Lefebyre)      |                                                                                        | pendant predication.<br>d the control flow method to be                    | e more    |  |

| Date : October                   |                    |                                                                                        | Also updated the external interfaces                                       |           |  |

| Rev 0.9 (Laure                   |                    |                                                                                        | rated changes made in the 10/18/01                                         |           |  |

| Date : October                   |                    |                                                                                        | eting. Added a NOP instruction, r                                          |           |  |

|                                  |                    | the co                                                                                 | nditional_execute_or_jump. Added                                           |           |  |

|                                  |                    | register                                                                               |                                                                            |           |  |

| Rev 1.0 (Laure                   |                    | Refined                                                                                | interfaces to RB. Added state register                                     | ers.      |  |

| Date : October                   |                    | A                                                                                      |                                                                            | - خامله ا |  |

| Rev 1.1 (Laure                   |                    | Added SEQ→SP0 interfaces. Changed delta<br>precision. Changed VGT→SP0 interface. Debug |                                                                            |           |  |

| Date : October                   | 20, 2001           | Methods added.                                                                         |                                                                            |           |  |

| Rev 1.2 (Laure                   | ent Lefebvre)      | Interfaces greatly refined. Cleaned up the spec.                                       |                                                                            |           |  |

| Date : Novemb                    |                    |                                                                                        |                                                                            |           |  |

| Rev 1.3 (Laure                   |                    | Added t                                                                                | he different interpolation modes.                                          |           |  |

| Date : Novemb                    |                    |                                                                                        |                                                                            |           |  |

| Rev 1.4 (Laure                   |                    |                                                                                        | the auto incrementing counters. C                                          |           |  |

| Date : Decemb                    | per 6, 2001        |                                                                                        | →SQ interface. Added content on o                                          | constant  |  |

| Day 1 E (Laure                   | ant Lofobura)      |                                                                                        | ment. Updated GPRs.                                                        | worosit   |  |

| Rev 1.5 (Laure<br>Date : Decemb  |                    |                                                                                        | ed from the spec all interfaces that<br>tied to the SQ. Added explanati    |           |  |

| Date . Decenni                   | 501 11, 2001       | constan                                                                                |                                                                            | PA→SQ     |  |

|                                  |                    |                                                                                        | nization fields and explanation.                                           |           |  |

| Rev 1.6 (Laure                   | ent Lefebvre)      |                                                                                        | nore details on the staging register                                       | Added     |  |

| Date : January                   |                    |                                                                                        | bout the parameter caches. Chang                                           |           |  |

| -                                |                    |                                                                                        | truction to a Conditionnal_call inst                                       |           |  |

|                                  |                    |                                                                                        | details on constant manageme                                               | nt and    |  |

| D 4 7 4                          |                    |                                                                                        | the diagram.                                                               |           |  |

| Rev 1.7 (Laure                   | ,                  |                                                                                        | Real Time parameter control in                                             | the SX    |  |

| Date : Februar<br>Rev 1.8 (Laure |                    |                                                                                        | e. Updated the control flow section.<br>erfaces to the SX block. Added the | ond of    |  |

| Rev 1.8 (Laure<br>Date : March 4 |                    |                                                                                        | modifier, removed the end of                                               |           |  |

| Date . March 4                   | T, 2002            | instructi                                                                              |                                                                            | Jiause    |  |

| Rev 1.9 (Laure                   | ent Lefebvre)      |                                                                                        | gement of the CF instruction bits in                                       | order to  |  |

| Date : March 1                   |                    |                                                                                        | byte alignement.                                                           |           |  |

| Rev 1.10 (Lau                    |                    |                                                                                        | I the interfaces and added a sec                                           | tion on   |  |

| Date : March 2                   | 25, 2002           | exportin                                                                               | g rules.                                                                   |           |  |

| Rev 1.11 (Lau                    | ,                  |                                                                                        | CP state report interface. Last versio                                     | n of the  |  |

| Date : April 19                  |                    |                                                                                        | h the old control flow scheme                                              |           |  |

| Rev 2.0 (Laure                   |                    | New cor                                                                                | ntrol flow scheme                                                          |           |  |

| Date : April 19                  | , 2002             |                                                                                        |                                                                            |           |  |

|                                  |                    |                                                                                        |                                                                            |           |  |

Reference Copyright Notice on Cover Page © \*\*\*

Exhibit 2028.docR400\_Sequencer.dec 73201 Bytes\*\*\* © ATI

AMD1044\_0017312

| ORIGINATE DATE     | EDIT DATE           | R400 Sequencer Specification | PAGE    |

|--------------------|---------------------|------------------------------|---------|

| 24 September, 2001 | 4 September, 201519 |                              | 6 of 58 |

## 1. Overview

The sequencer is based on the R300 design. It The sequencer chooses two ALU clauses threads and a fetch clause hread to execute, and executes all of the instructions in a clause-block before looking for a new clause of the same type. Two ALU clauses, threads are executed interleaved to hide the ALU latency. Each vector will have eight fetch and eight ALU clauses, but clauses do not need to contain instructions. A vector of pixels or vertices ping-pongs along the sequencer FIFO, bouncing from fetch reservation station to alu reservation station. A FIFO exists between each reservation stage, holding up vectors until the vector currently occupying a reservation stations has left. A vector at a reservation station can be chosen to execute. The sequencer looks at all eight alu reservation stations to choose an alu clause to execute and all eight fetch stations to choose a fetch clause to execute. The arbitrator will give priority to clauses/reservation stations closer to the bottom of the pipelineolder threads. It will not execute an alu clause until the fetch fetches initiated by the previous fetch clause have completed. There are two separate sets of reservations stations, one for pixel vectors and one for vertices vectors. This way a pixel can pass a vertex and a vertex can pass a pixel.

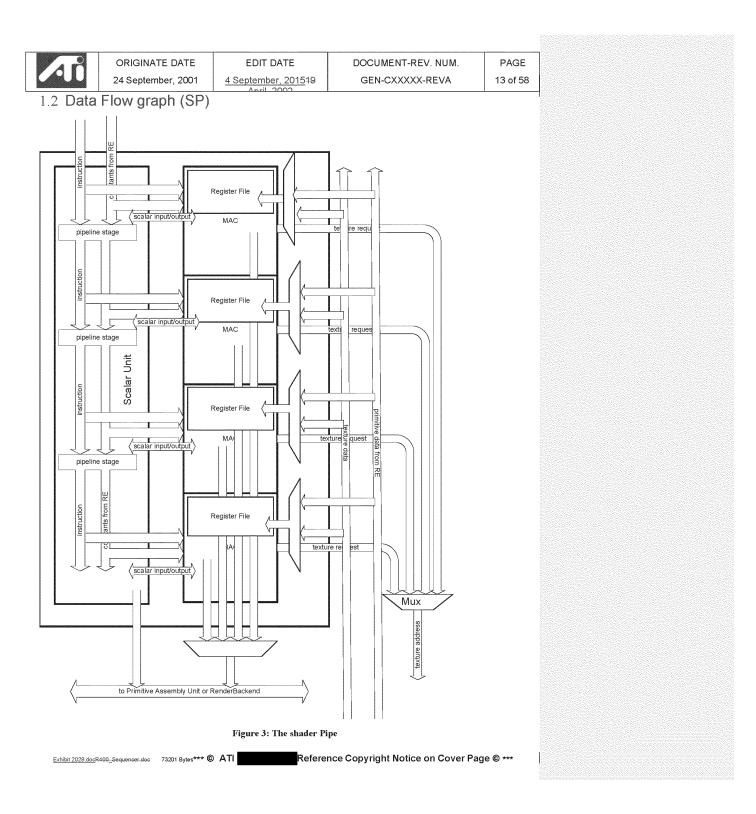

To support the shader pipe the sequencer also contains the shader instruction cache, constant store, control flow constants and texture state. The four shader pipes also execute the same instruction thus there is only one sequencer for the whole chip.

The sequencer first arbitrates between vectors of 64 vertices that arrive directly from primitive assembly and vectors of 16 quads (64 pixels) that are generated in the scan converter.

The vertex or pixel program specifies how many GPRs it needs to execute. The sequencer will not start the next vector until the needed space is available in the GPRs.

Reference Copyright Notice on Cover Page © \*\*\*

AMD1044\_0017313

ATI Ex. 2011 IPR2023-00922 Page 6 of 58

| ORIGINATE DATE     | EDIT DATE           | R400 Sequencer Specification | PAGE    |  |

|--------------------|---------------------|------------------------------|---------|--|

| 24 September, 2001 | 4 September, 201519 |                              | 8 of 58 |  |

Exhibit 2028.docR400\_Sequencer.doc 73201 Bytes\*\*\* © ATI

Reference Copyright Notice on Cover Page © \*\*\*

AMD1044\_0017315

ATI Ex. 2011 IPR2023-00922 Page 8 of 58

|           | ORIGINATE DATE     | EDIT DATE           | DOCUMENT-REV. NUM. | PAGE    |  |

|-----------|--------------------|---------------------|--------------------|---------|--|

|           | 24 September, 2001 | 4 September, 201549 | GEN-CXXXXX-REVA    | 9 of 58 |  |

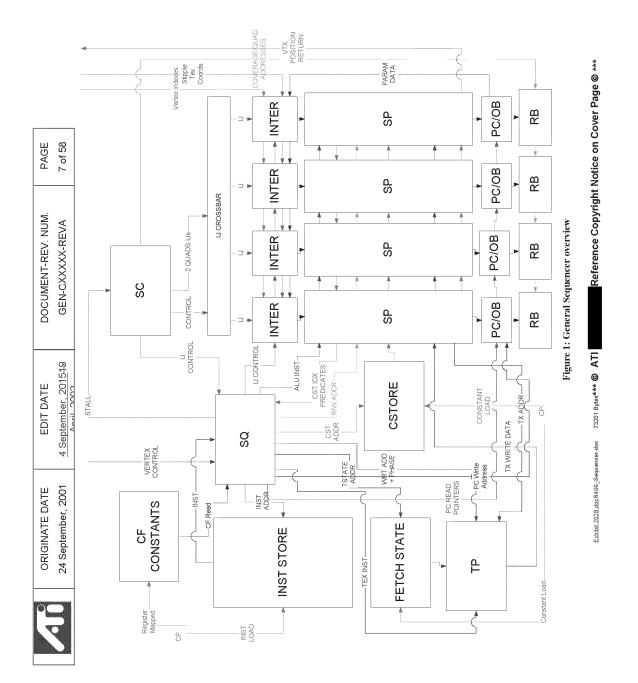

| 1.1 Top l | _evel Block Diagr  | am                  |                    |         |  |

Exhibit 2028.docR400\_Sequencer.doc 73201 Bytes\*\*\* © ATI

AMD1044\_0017316

ATI Ex. 2011 IPR2023-00922 Page 9 of 58

Exhibit 2028.docR400\_Sequencer.doc 73201 Bytes\*\*\* C ATI

Reference Copyright Notice on Cover Page © \*\*\*

AMD1044\_0017317

ATI Ex. 2011 IPR2023-00922 Page 10 of 58

ATI Ex. 2011 IPR2023-00922 Page 11 of 58

| ORIGINATE DATE     | EDIT DATE                   | R400 Sequencer Specification | PAGE     |

|--------------------|-----------------------------|------------------------------|----------|

| 24 September, 2001 | <u>4 September, 2015</u> 19 |                              | 12 of 58 |

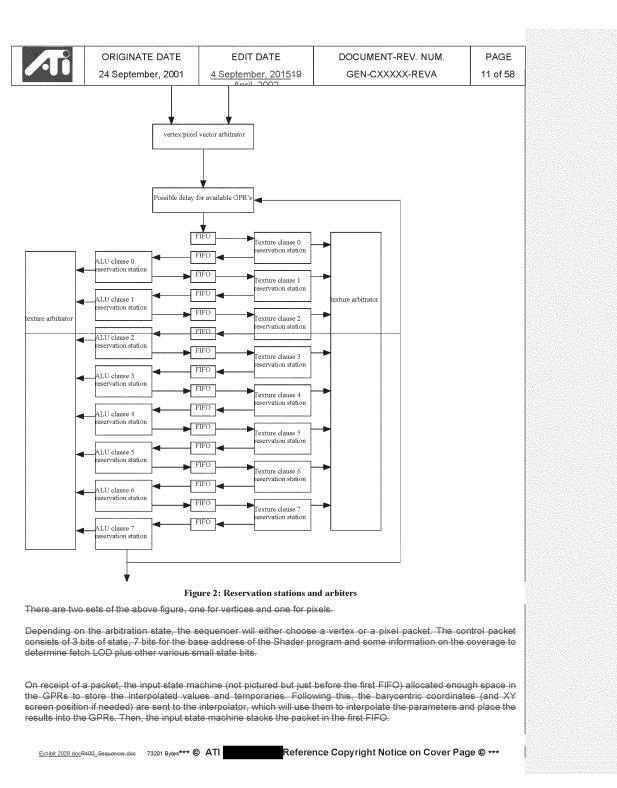

On receipt of a command, the level 0 fetch machine issues a fetch request to the TP and corresponding GPR address for the fetch address (ta). A small command (tomd) is passed to the fetch system identifying the current level number (0) as well as the GPR write address for the fetch return data. One fetch request is sent every 4 clocks causing the texturing of sixteen 2x2s worth of data (or 64 vertices). Once all the requests are sent the packet is put in FIFO 1.

Upon receipt of the return data, the fetch unit writes the data to the register file using the write address that was provided by the level 0 fetch machine and sends the clause number (0) to the level 0 fetch state machine to signify that the write is done and thus the data is ready. Then, the level 0 fetch machine increments the counter of FIFO 1 to signify to the ALU 0 that the data is ready to be processed.

On receipt of a command, the level 0 ALU machine first decrements the input FIFO 1 counter and then issues a complete set of level 0 shader instructions. For each instruction, the ALU state machine generates 3 source addresses, one destination address and an instruction. Once the last instruction has been issued, the packet is put into FIFO 2.

There will always be two active ALU clauses at any given time (and two arbiters). One arbiter will arbitrate over the odd instructions (4 clocks cycles) and the other one will arbitrate over the even instructions (4 clocks cycles). The only constraints between the two arbiters is that they are not allowed to pick the same clause number as the other one is currently working on if the packet is not of the same type (render state).

If the packet is a vertex packet, upon reaching ALU clause 3, it can export the position if the position is ready. So the arbiter must prevent ALU clause 3 to be selected if the positional buffer is full (or can't be accessed). Along with the positional data, if needed the sprite size and/or edge flags can also be sent.

A special case is for multipass vertex shaders, which can export 12 parameters per last 6 clauses to the output buffer. If the output buffer is full or doesn't have enough space the sequencer will prevent such a vertex group to enter an exporting clause.

Multipass pixel shaders can export 12 parameters to memory from the last clause only (7).

All other clauses process in the same way until the packet finally reaches the last ALU machine (7).

Only one pair of interleaved ALU state machines may have access to the register file address bus or the instruction decode bus at one time. Similarly, only one fetch state machine may have access to the register file address bus at one time. Arbitration is performed by three arbiter blocks (two for the ALU state machines and one for the fetch state machines). The arbiters always favor the higher number state machines, preventing a bunch of half finished jobs from clogging up the register files.

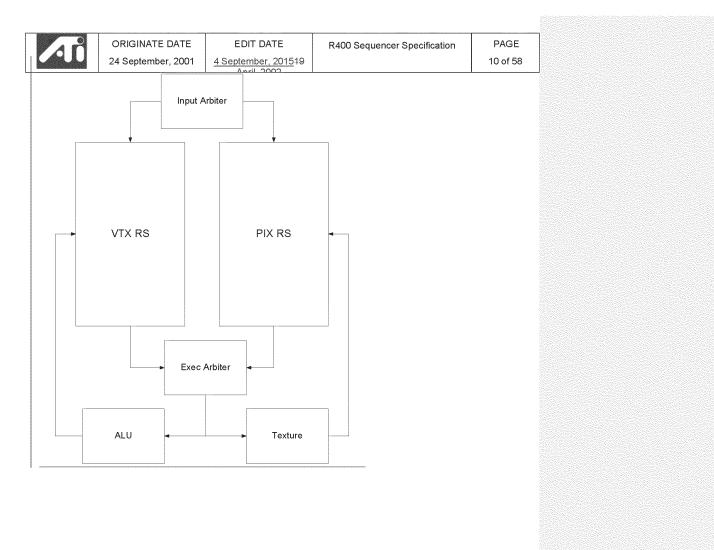

Under this new scheme, the sequencer (SQ) will only use one global state management machine per vector type (pixel, vertex) that we call the reservation station (RS).

Reference Copyright Notice on Cover Page © \*\*\*

AMD1044\_0017319

ATI Ex. 2011 IPR2023-00922 Page 12 of 58

ATI Ex. 2011 IPR2023-00922 Page 13 of 58

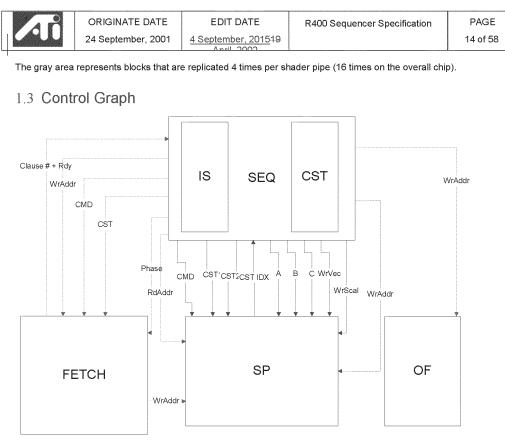

#### Figure 4: Sequencer Control interfaces

In green is represented the Fetch control interface, in red the ALU control interface, in blue the Interpolated/Vector control interface and in purple is the output file control interface.

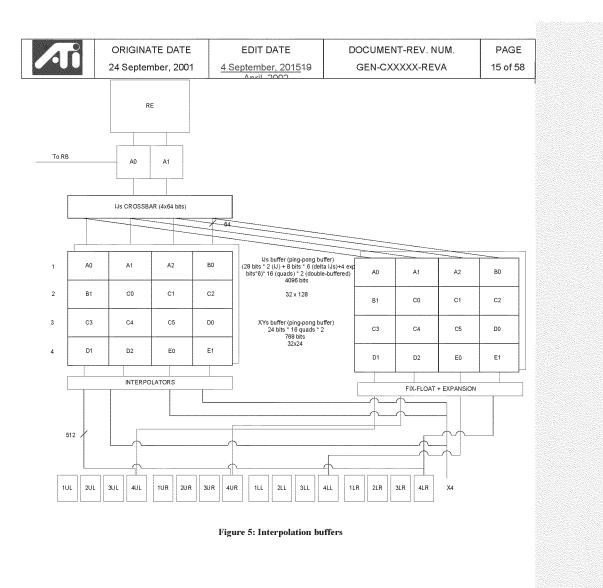

# 2. Interpolated data bus

The interpolators contain an IJ buffer to pack the information as much as possible before writing it to the register file.

Exhibit 2028.docR400\_Sequencer.doc 73201 Bytes\*\*\* ⓒ ATI

Reference Copyright Notice on Cover Page © \*\*\*

AMD1044\_0017321

ATI Ex. 2011 IPR2023-00922 Page 14 of 58

Exhibit 2028.docR400\_Sequencer.doc 73201 Bytes\*\*\* C ATI

Reference Copyright Notice on Cover Page © \*\*\*

AMD1044\_0017322

ATI Ex. 2011 IPR2023-00922 Page 15 of 58

|                                      | 23                      | I            |             |         |        | 1 > % 7                   | 245                    | <u>_</u> 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                       |           |

|--------------------------------------|-------------------------|--------------|-------------|---------|--------|---------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------|

|                                      | 22 L                    |              |             |         |        | V V<br>32-48-<br>35 51    | V V<br>36-52-<br>39 55 | V V<br>40-56-<br>43 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <pre>&lt; V &lt; V 44-60- 47 63</pre> | $\times$  |

|                                      | 21 T                    |              |             |         |        | > 4 6<br>0 0              | 53 c <                 | 24- 4<br>27- 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33 <sup>2</sup> % <                   | L         |

|                                      | 1                       | _            |             |         |        | > ° <                     | > 4                    | ⇒ ⇔ <del>⊊</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | → <sup>1</sup> 2 <                    |           |

|                                      | T19                     |              |             |         |        |                           |                        | о<br>Ш                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | μ                                     |           |

|                                      | T18 T19 T20 T21 T22 T23 |              |             |         |        |                           |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8                                     |           |

| თ                                    |                         |              |             | × ₪     | ×Ξ     |                           | 8                      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | S                                     |           |