|                      | ORIGINATE DATE                      | EDIT DATE                                                 | DOCUMENT-REV. NUM.                                                     | PAGE          |

|----------------------|-------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------|---------------|

|                      | 14 August, 200144                   | 4 September, 201524                                       | GEN-CXXXXX-REVA                                                        | 1 of 20       |

| Author:              | Laurent Lefebvre                    | August 20016 August                                       |                                                                        |               |

|                      |                                     |                                                           |                                                                        |               |

| Issue To:            |                                     | Copy No:                                                  |                                                                        |               |

|                      |                                     |                                                           |                                                                        |               |

|                      | D400 C                              |                                                           | aifiantian                                                             |               |

|                      | R400 3                              | equencer Spe                                              | cincation                                                              |               |

|                      |                                     | <i></i>                                                   |                                                                        |               |

|                      |                                     | SEQ                                                       |                                                                        |               |

|                      |                                     |                                                           |                                                                        |               |

|                      |                                     | Version 0. <u>4</u> 2                                     |                                                                        |               |

| Overview: Th         | is is an architectural specifi      | cation for the R400 Sequen                                | cer block (SEQ). It provides an ov                                     | enview of the |

| re                   |                                     | cted uses of the block. It al                             | so describes the block interfaces,                                     |               |

| Dit                  | ocks, and provides internal si      | ate ulagranis.                                            |                                                                        |               |

|                      |                                     |                                                           |                                                                        |               |

|                      |                                     |                                                           |                                                                        |               |

| AUTOMATIC            | CALLY UPDATED FIELDS:               |                                                           |                                                                        |               |

| Document L           | Location: C:\p                      | erforce\r400\arch\doc\gfx\RE<br>0 Sequencer Specification | \R400_Sequencer.doc                                                    |               |

| Current inti         |                                     | APPROVALS                                                 |                                                                        |               |

|                      | Name/Dept                           |                                                           | Signature/Date                                                         |               |

|                      |                                     |                                                           |                                                                        |               |

|                      |                                     |                                                           |                                                                        |               |

|                      |                                     |                                                           |                                                                        |               |

| Remarks:             |                                     |                                                           |                                                                        |               |

|                      |                                     |                                                           |                                                                        |               |

|                      |                                     |                                                           | NFORMATION THAT CO<br>REST OF ATI TECHNOL                              |               |

| 506517               |                                     |                                                           | E OR DISCLOSURE.                                                       | OGIES         |

|                      |                                     |                                                           |                                                                        |               |

|                      |                                     |                                                           |                                                                        |               |

|                      |                                     |                                                           | ial in this document constitutes ar                                    |               |

| unpublished v        | vork. The copyright notice          | is not an admission that                                  | provide notice that ATI owns a cop<br>publication has occurred. This w | ork contains  |

|                      |                                     |                                                           | of this document may be used, re<br>sion of ATI Technologies Inc."     | eproduced, or |

|                      |                                     |                                                           |                                                                        |               |

| Exhibit 2010 doc8400 | _Sequencer.doc 25584 Bytes*** ⓒ A   | Classic Reference C                                       | Copyright Notice on Cover Page @                                       | ) ***         |

| EXHIBIT 2010.00C     | _sequences.auc 25564 Bytes **** @ A | PM08/13/01 03:17 PM07/13/01 02:10 P                       | M                                                                      | 09/04/15 12:4 |

|                      |                                     |                                                           |                                                                        |               |

ATI 2010 LG v. ATI IPR2015-00325

AMD1044 0016660

**DOCKET A L A R M** Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

|  | ORIGINATE DATE    | EDIT DATE           | R400 Sequencer Specification | PAGE    |

|--|-------------------|---------------------|------------------------------|---------|

|  | 14 August, 200114 | 4 September, 201524 |                              | 2 of 20 |

|  |                   |                     |                              |         |

2

3.

4.

5.

6

8....

<u>Q</u>\_\_\_\_

#### Table Of Contents

| 1. OVERVIEW                                                                                     |  |  |  |  |

|-------------------------------------------------------------------------------------------------|--|--|--|--|

| 1.1         Top Level Block Diagram         54           1.2         Data Elaw graph         67 |  |  |  |  |

| 1.2         Data Flow graph                                                                     |  |  |  |  |

|                                                                                                 |  |  |  |  |

| 2.         INTERPOLATED DATA BUS 1210           3.         INSTRUCTION STORE                    |  |  |  |  |

| 4. CONSTANT STORE                                                                               |  |  |  |  |

| 5. LOOPING AND BRANCHES 1344                                                                    |  |  |  |  |

| 6. REGISTER FILE ALLOCATION 1314                                                                |  |  |  |  |

| 7. TEXTURE ARBITRATION                                                                          |  |  |  |  |

| 8. ALU ARBITRATION                                                                              |  |  |  |  |

| 9. HANDLING STALLS                                                                              |  |  |  |  |

| 10. CONTENT OF THE RESERVATION                                                                  |  |  |  |  |

| STATION FIFOS1513                                                                               |  |  |  |  |

| 11. THE OUTPUT FILE (RB FIFO AND                                                                |  |  |  |  |

| PARAMETER CACHE)1513                                                                            |  |  |  |  |

| 12. INTERFACES                                                                                  |  |  |  |  |

| 12.1 External Interfaces                                                                        |  |  |  |  |

|                                                                                                 |  |  |  |  |

| 12.1.1 Sequencer to Shader                                                                      |  |  |  |  |

| Engine Bus                                                                                      |  |  |  |  |

| 12.1.2 Shader Engine to Output                                                                  |  |  |  |  |

| File 1513                                                                                       |  |  |  |  |

| 12.1.3 Shader Engine to Texture                                                                 |  |  |  |  |

| Unit Bus (Fast Bus)1614                                                                         |  |  |  |  |

| 12.1.4 Sequencer to Texture Unit bus                                                            |  |  |  |  |

| (Slow Bus) 1614                                                                                 |  |  |  |  |

| 12.1.5 Shader Engine to RE/PA Bus                                                               |  |  |  |  |

| 1614                                                                                            |  |  |  |  |

|                                                                                                 |  |  |  |  |

| 12.1.6 PA? to sequencer                                                                         |  |  |  |  |

| 13. EXAMPLES OF PROGRAM                                                                         |  |  |  |  |

| EXECUTIONS                                                                                      |  |  |  |  |

| 13.1.1 Sequencer Control of a Vector                                                            |  |  |  |  |

| of Vertices 1714                                                                                |  |  |  |  |

| 13.1.2 Sequencer Control of a Vector                                                            |  |  |  |  |

| of Pixels 1846                                                                                  |  |  |  |  |

| 13.1.3 Notes                                                                                    |  |  |  |  |

| 14. OPEN ISSUES                                                                                 |  |  |  |  |

| 1. OVERVIEW                                                                                     |  |  |  |  |

| 1.1 Top Level Block Diagram                                                                     |  |  |  |  |

| 1.2 Data Flow graph7                                                                            |  |  |  |  |

| 1.3 Control Graph                                                                               |  |  |  |  |

|                                                                                                 |  |  |  |  |

| <del>12.1.2</del> —s | hader Engine to Output       |

|----------------------|------------------------------|

| File1                | 3                            |

| <del>12.1.3</del> S  | hader Engine to Texture      |

| Unit Bus (F          | ast Bus)                     |

| <del>12.1.4</del> s  | equencer to Texture Unit bus |

| (Slow Bus) 1         | 4                            |

| <del>12.1.5</del> —s | hader Engine to RE/PA Bus 14 |

| 12.1.6 P             | A to sequencer14             |

|                      | SUES                         |

|                      | EW3                          |

| 1.1 Top Leve         | HBlock Diagram4              |

|                      | E ARBITRATION9               |

| 3. ALU-ARI           | BITRATION9                   |

| 4. HANDLI            | NG-STALLS                    |

| 5. CONTEN            | IT OF THE RESERVATION        |

| STATION FIF          | DS10                         |

| 6. INTER             | FACES                        |

| 6.1 Externa          | al Interfaces 10             |

| 6.1.1-Se             | quencer to Shader Engine     |

| Bus 10               |                              |

| 6.1.2Sh              | ader Engine to Output File   |

|                      |                              |

INTERPOLATED DATA BUS ......10

INSTRUCTION STORE ......10

CONSTANT STORE ......11

LOOPING AND BRANCHES ......11

REGISTER FILE ALLOCATION......11

ALU ARBITRATION .....12 HANDLING STALLS ......13

10.

CONTENT OF THE RESERVATION

STATION FIFOS

13

11.

THE OUTPUT FILE (RB FIFO AND

PARAMETER CACHE)

13

12.

INTERFACES

13.

12.

14.

External Interfaces

13.

12.1.1

Sequencer to Shader

Engine Bus

13

Exhibit 2010.docR400\_Sequencer.doc 25584 Bytes\*\*\* C ATI

DOCKET

Α

Reference Copyright Notice on Cover Page © \*\*\* 09/04/15 12:48

AMD1044 0016661

Find authenticated court documents without watermarks at docketalarm.com.

|                                                             | ORIGINATE DATE                                                                  | EDIT DATE           | DOCUMENT-REV. NUM.                                                                                      | PAGE    |  |  |

|-------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------|---------|--|--|

|                                                             | 14 August, 200114                                                               | 4 September, 201524 | GEN-CXXXXX-REVA                                                                                         | 3 of 20 |  |  |

| 6.1.4 Sequencer to Texture Unit bus 7. OPEN ISSUES          |                                                                                 |                     |                                                                                                         |         |  |  |

|                                                             | (Slow Bus)                                                                      |                     |                                                                                                         |         |  |  |

| 6.1.5-8                                                     | Shader Engine to RE/P                                                           | A-Bus11             |                                                                                                         |         |  |  |

|                                                             |                                                                                 |                     |                                                                                                         |         |  |  |

| Devision                                                    | Changes                                                                         |                     |                                                                                                         |         |  |  |

| Revision                                                    | Changes:                                                                        |                     |                                                                                                         |         |  |  |

| Rev 0.1 (Laurent Lefebvre)                                  |                                                                                 |                     | First draft.                                                                                            |         |  |  |

| Date: May 7, 2                                              | 001                                                                             |                     |                                                                                                         |         |  |  |

| Rev 0.2 (Laure                                              | Rev 0.2 (Laurent Lefebvre) Changed the interfaces to reflect the changes in the |                     |                                                                                                         |         |  |  |

| Date : July 9, 2001                                         |                                                                                 |                     | SP. Added some details in the arbitration section.                                                      |         |  |  |

| Rev 0.3 (Laurent Lefebvre)                                  |                                                                                 |                     | Reviewed the Sequencer spec after the meeting on                                                        |         |  |  |

| Date : August 6, 2001                                       |                                                                                 |                     | August 3, 2001.                                                                                         |         |  |  |

| <u>Rev 0.4 (Laurent Lefebvre)</u><br>Date : August 24, 2001 |                                                                                 |                     | Added the dynamic allocation method for register<br>file and an example (written in part by Vic) of the |         |  |  |

| Dute : August 24, 2001                                      |                                                                                 |                     | flow of pixels/vertices in the sequencer.                                                               |         |  |  |

|                                                             |                                                                                 |                     | finalision non monta sina sina sina sina sina nina nina sina s                                          |         |  |  |

|                                                             |                                                                                 |                     |                                                                                                         |         |  |  |

|                                                             |                                                                                 |                     |                                                                                                         |         |  |  |

Exhibit 2010.docR400\_Sequencer.doc 25584 Bytes\*\*\* © ATI

Reference Copyright Notice on Cover Page © \*\*\*

DOCKET ALARM Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

AMD1044 0016662

| ORIGINATE DATE    | EDIT DATE           | R400 Sequencer Specification | PAGE    |

|-------------------|---------------------|------------------------------|---------|

| 14 August, 200114 | 4 September, 201524 |                              | 4 of 20 |

#### 1. Overview

The sequencer first arbitrates between vectors of 16-(maybe 32) vertices that arrive directly from primitive assembly and vectors of 84-quads (16 pixels)-(32-pixels)-that are generated in the raster engine.

The vertex or pixel program specifies how many GPR's it needs to execute. The sequencer will not start the next vector until the needed space is available.

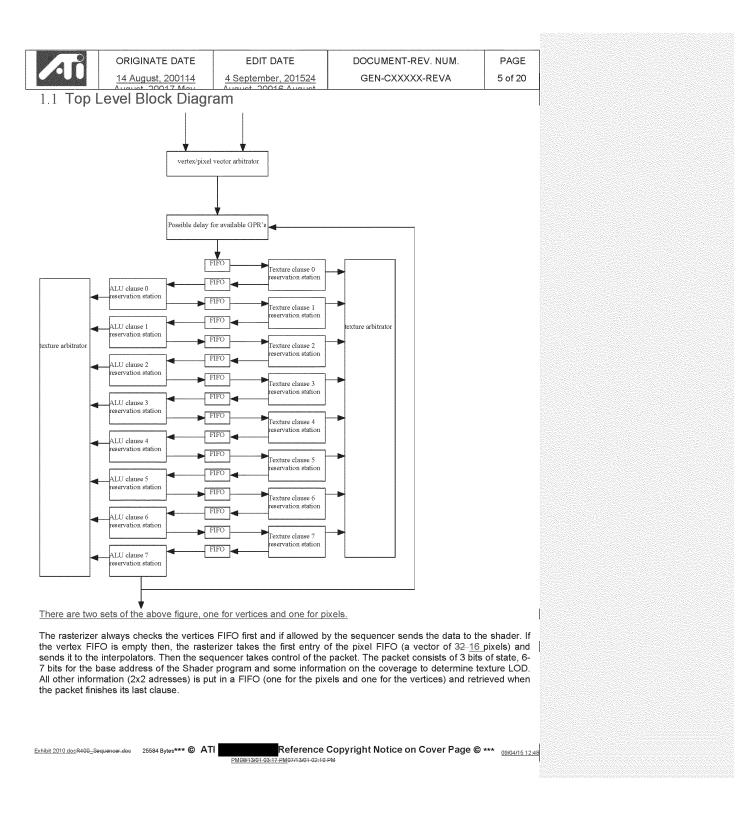

The sequencer is based on the R300 design. It chooses an-two\_ALU clauses and a texture clause to execute, and executes all of the instructions in a<u>a</u> clause before looking for a new clause of the same type. <u>Two ALU clauses are executed interleaved to hide the ALU latency</u>. Each vector will have eight texture and eight ALU clauses, but clauses do not need to contain instructions. A vector of pixels or vertices ping-pongs along the sequencer FIFO, bouncing from texture reservation station to alu reservation station. A FIFO exists between each reservation stage, holding up vectors until the vector currently occupying a reservation station has left. A vector at a reservation station can be chosen to execute. The sequencer looks at all eight alu reservation stations to choose an alu clause to execute and all eight texture stations to choose a texture clause to execute. The arbitrator will give priority to clauses/reservation stations closer to the tep-bottom of the pipeline. It will not execute an alu clause until the texture fetches initiated by the previous texture clause have completed. <u>There are two separate sets of reservation stations, one for pixel vectors and one for vertices vectors. This way a pixel can pass a vertex and a vertex can pass a pixel.</u>

To support the shader pipe the raster engine also contains the shader instruction cache and constant store. There are only one constant store for the whole chip and one instruction store. These will be shared among the four shader pipes.

Exhibit 2010.docR400\_Sequencer.doc 25584 Bytes\*\*\* C ATI

Reference Copyright Notice on Cover Page © \*\*\* 09/04/15 12:48

DOCKET

AMD1044 0016663

Find authenticated court documents without watermarks at <u>docketalarm.com</u>.

AMD1044 0016664

Find authenticated court documents without watermarks at docketalarm.com.

DOCKET

Α

## DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time alerts** and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### LAW FIRMS

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### FINANCIAL INSTITUTIONS

Litigation and bankruptcy checks for companies and debtors.

### E-DISCOVERY AND LEGAL VENDORS

Sync your system to PACER to automate legal marketing.