### A RECORD ON THE PROPERTY OF TH

# TO ALL TO WHOM THESE PRESENTS SHALL COME: UNITED STATES DEPARTMENT OF COMMERCE United States Patent and Trademark Office

March 8, 2022

THIS IS TO CERTIFY THAT ANNEXED IS A TRUE COPY FROM THE RECORDS OF THIS OFFICE OF THE FILE WRAPPER AND CONTENTS OF:

APPLICATION NUMBER: 09/343,431

FILING DATE: June 30, 1999 PATENT NUMBER: 6,157,589 ISSUE DATE: December 5, 2000

> By Authority of the Under Secretary of Commerce for Intellectual Property and Director of the United States Patent and Trademark Office

> > Trudie Wallace Wellower Certifying Officer

| SSUE CLASSIFICATION                                                                                            |                                                                                                                                                            |                                                      | 25.0                                                                            | <u>.</u>                                     |                                         |                 | 57589<br>           |  |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------|-----------------|---------------------|--|

|                                                                                                                | U.S. UTILIT                                                                                                                                                | V DATE!                                              | NT ADD                                                                          | LICATIO                                      | N                                       |                 |                     |  |

|                                                                                                                |                                                                                                                                                            | I.P.E.                                               | 14                                                                              | PATENT DA                                    |                                         |                 |                     |  |

| •                                                                                                              | SCANNED A.C                                                                                                                                                | n.Boal                                               | t-                                                                              | nec 1                                        | 5 200                                   |                 |                     |  |

|                                                                                                                |                                                                                                                                                            | 1                                                    |                                                                                 | · · · · · · · · · · · · · · · · · · ·        |                                         |                 |                     |  |

| ECTOR CLASS 365                                                                                                | SUBCLASS                                                                                                                                                   | ART                                                  | runit 28                                                                        | 24 E                                         | XAMINE                                  | R<br>lo         |                     |  |

|                                                                                                                |                                                                                                                                                            | rest to the                                          | 0.10                                                                            | FILED WITH:                                  | DIS                                     | SK (CRF)        | FICHE               |  |

| 15 09343431<br>1489F RET 2667278                                                                               | 17 - 000004                                                                                                                                                | RT ID: VI                                            |                                                                                 |                                              | (Attache                                | ed in pocket on | right inside flap)  |  |

| M -A3-01-3-01-0                                                                                                | 016-4-02-08                                                                                                                                                | #1 C                                                 |                                                                                 |                                              |                                         |                 |                     |  |

| SKP:RF051857860 —                                                                                              | NHM                                                                                                                                                        | or: Thomps                                           |                                                                                 |                                              |                                         |                 |                     |  |

| R                                                                                                              | RECORDS MANAG                                                                                                                                              | HALF                                                 |                                                                                 |                                              |                                         |                 |                     |  |

| PR                                                                                                             | EPARED AND                                                                                                                                                 | APPRO                                                | VED FO                                                                          | OR ISSU                                      | Ε                                       |                 |                     |  |

|                                                                                                                | ISSUING C                                                                                                                                                  | N ACCU                                               | TO ATIC                                                                         |                                              |                                         | 9               |                     |  |

| ORIGINAL                                                                                                       | ISSUING C                                                                                                                                                  | LASSIF                                               |                                                                                 | JN<br>EFERENCE(S                             | <u> </u>                                |                 |                     |  |

| CLASS SUBCLASS                                                                                                 | S CLASS                                                                                                                                                    | St                                                   | en neg vinsk stans, men var i genzen.<br>Sammer i Fransk skriver vinsk skriver. | NE SUBCLAS                                   | ra romana an<br>Romana alkaber          | .ock)           |                     |  |

| 365 226                                                                                                        | 365                                                                                                                                                        | 328                                                  |                                                                                 |                                              |                                         |                 |                     |  |

| NTERNATIONAL CLASSIFICATI                                                                                      | ON                                                                                                                                                         |                                                      |                                                                                 |                                              |                                         | 1000            |                     |  |

| 110 8/00                                                                                                       |                                                                                                                                                            |                                                      |                                                                                 |                                              |                                         |                 |                     |  |

|                                                                                                                |                                                                                                                                                            |                                                      |                                                                                 |                                              |                                         |                 |                     |  |

|                                                                                                                |                                                                                                                                                            |                                                      |                                                                                 |                                              |                                         |                 |                     |  |

|                                                                                                                |                                                                                                                                                            | •                                                    |                                                                                 | Continued on                                 | Issue Slip                              | Inside File     | Jacket              |  |

| 10-20-00 For                                                                                                   | mal Drawings( <u>_</u>                                                                                                                                     | ≥shts)set                                            |                                                                                 | 6-                                           | 30                                      | 99              |                     |  |

| TERMINAL                                                                                                       | DRA                                                                                                                                                        | WINGS                                                |                                                                                 |                                              | CLAIM                                   | S ALLOV         | /ED                 |  |

| └─ DISCLAIMER                                                                                                  | 7 1                                                                                                                                                        | , ,                                                  | Print Fig.                                                                      | Total Cla                                    | aims                                    | Print Cl        | aim for O.G.        |  |

| · ·                                                                                                            | 3/                                                                                                                                                         | 4                                                    | <i></i>                                                                         |                                              |                                         | <u> </u>        |                     |  |

|                                                                                                                |                                                                                                                                                            |                                                      |                                                                                 | NOTICE                                       | OF ALL                                  | OWANCE          | MAILED              |  |

| ubsequent to (date)                                                                                            |                                                                                                                                                            |                                                      | (Date)                                                                          | r - 7//                                      | 1/07                                    |                 |                     |  |

| ubsequent to (date) as been disclaimed.                                                                        | (Assistant Examine                                                                                                                                         | m)<br>/                                              |                                                                                 | 36°,                                         | 100/15 / /                              |                 |                     |  |

| ubsequent to (date) as been disclaimed.  b) The term of this patent shall ot extend beyond the expiration date | kant                                                                                                                                                       | eve_                                                 |                                                                                 | AF.                                          | 1001                                    | ·               | 7.1                 |  |

| ubsequent to (date) as been disclaimed.  b) The term of this patent shall ot extend beyond the expiration date | Group 28<br>AU 282                                                                                                                                         | eve_                                                 |                                                                                 | Amount                                       |                                         | E FEE           | (W                  |  |

| ubsequent to (date) as been disclaimed.  b) The term of this patent shall ot extend beyond the expiration date | bourt<br>Group 28<br>AU 282<br>Vu A.                                                                                                                       | 200 )<br>4                                           |                                                                                 | Amount                                       | Due /                                   | Da              | te Paid             |  |

| ubsequent to (date) as been disclaimed.  b) The term of this patent shall ot extend beyond the expiration date | komb<br>Group 28<br>AU 282                                                                                                                                 | 200 )<br>4                                           | (Date)                                                                          | \$1,210.c                                    | Due                                     | Da              | te Paid             |  |

| ubsequent to                                                                                                   | Group 28<br>AU 282<br>VU A.                                                                                                                                | Le maminer                                           | 1/18/08                                                                         | \$1,210.0<br>158                             | Due                                     | Da              | te Paid             |  |

| a) The term of this patent ubsequent to                                                                        | bourt<br>Group 28<br>AU 282<br>Vu A.                                                                                                                       | Le maminer                                           | (Date)                                                                          | \$1,210.c                                    | Due                                     | Da              | te Paid             |  |

| ubsequent to                                                                                                   | Group 28 AU 282 Vu A.  (Finimeaning) (Legal Instruments Exartricted. Unauthorized discloss                                                                 | Le miner                                             | hibited by the                                                                  | \$1,210.0<br>158<br>[P3]<br>United States Co | Due | Da<br>) O       | te Paid  3-9-0  BER |  |

| ubsequent to                                                                                                   | Group 28 AU 282 Vu A.  (Firmments Example) (Legal Instruments Example) (Legal Instruments Example) (Legal Instruments Example) (Legal Instruments Example) | Le Marniner  miner)  ure may be protororized employe | (Date)                                                                          | \$1,210.c                                    | Due | Da<br>) O       | te Paid  3-9-0  BER |  |

| ubsequent to                                                                                                   | Group 28 AU 282 Vu A.  (Firmments Example) (Legal Instruments Example) (Legal Instruments Example) (Legal Instruments Example) (Legal Instruments Example) | Le Marniner  miner)  ure may be protororized employe | (Date)                                                                          | \$1,210.0<br>158<br>[P3]<br>United States Co | Due | Da<br>) O       | te Paid  3-9-0  BER |  |

| ERIAL NUMBER                                                          |            | FILING DATE                            | CLASS           | GRO                        | P ART UNIT             | ATTORNEY D                                     | OCKET NO.          |

|-----------------------------------------------------------------------|------------|----------------------------------------|-----------------|----------------------------|------------------------|------------------------------------------------|--------------------|

| 09/343,431                                                            |            | 06/30/99                               | 365             |                            | 2818                   | GR98P19                                        | 989                |

| GUNNAR KRAUS                                                          | E, MUENCHI | EN, FED REP                            | GERMANY.        |                            |                        |                                                |                    |

| **CONTINUING<br>VERIFIED                                              | DOMESTIC   | DATA*****                              | ****            | ***                        |                        |                                                |                    |

| <u> </u>                                                              | None       |                                        |                 |                            |                        |                                                |                    |

| **371 (NAT'I<br>VERIFIED                                              | STAGE) D   | ATA******                              | *****           | **                         |                        |                                                |                    |

| <u> </u>                                                              | NoNE       | =                                      |                 |                            |                        |                                                |                    |

|                                                                       |            |                                        |                 |                            | · .                    |                                                |                    |

|                                                                       |            |                                        |                 |                            |                        |                                                |                    |

| **FOREIGN AN                                                          |            | REP GERMANY                            | 198 29 2        | 287.2                      | 06/30/98               |                                                |                    |

|                                                                       |            | FILING LICE                            |                 |                            |                        | TOTAL                                          | INDEPENDENT        |

| oreign Priority claime<br>5 USC 119 (a-d) con<br>erified and Acknowle | edaed      | 04                                     | ifter Allowance | STATE OR<br>COUNTRY<br>DEX | SHEETS<br>DRAWING<br>3 | CLAIMS<br>13                                   | CLAIMS<br>2        |

| LERNER AND<br>PO BOX 248<br>HOLLYWOOD                                 | 0          | G PA                                   | , many          |                            |                        |                                                |                    |

|                                                                       |            | TOR MEMORY D                           |                 | METHOD FO                  | Ř IŅŢIALIZI            | NG A                                           |                    |

| FILING FEE<br>RECEIVED<br>\$890                                       | No.        | hority has been<br>to charge/cr<br>for | edit DEPOSIT    | <b>ACCOUNT</b>             | 1.17 E                 | Fees (Filing)<br>Fees (Process<br>Fees (Issue) | sing Ext. of time) |

#

| SERIAL NUMBER                                    | l          | FILING DATE                      | CLASS                   | GROUP ART                    | UNIT       | ATTORNEY DOC | KET NO.       |

|--------------------------------------------------|------------|----------------------------------|-------------------------|------------------------------|------------|--------------|---------------|

| 09/343                                           | ,431       | 06/30/99                         | 365                     | 2818                         |            | GR98P1989    |               |

| GUNNAR KI<br>GUNNAR KI<br>GUNNAR KI<br>GUNNAR KI | RAUSE, MUE | ENCHEN, FED REP                  | GERMANY.                |                              |            |              |               |

| **CONTIN                                         |            | STIC DATA*****                   | *****                   | ** <b>*</b>                  |            |              |               |

| **371 (N<br>VERIFIE                              |            | E) DATA******                    | *****                   | *                            |            |              |               |

|                                                  | _          |                                  |                         |                              |            | •            |               |

|                                                  |            |                                  | ·                       |                              |            |              |               |

|                                                  |            |                                  |                         |                              |            |              |               |

| **FOREIG<br>VERIFIE                              |            | TIONS*********<br>ED REP GERMANY | .*<br>198 29 <b>2</b> 8 | 7.2 .06/                     | 30/98      |              |               |

|                                                  |            |                                  |                         |                              |            |              |               |

|                                                  |            |                                  | -                       |                              |            |              |               |

|                                                  |            | IGN FILING LICEN                 |                         |                              | te I       | TOTAL        | INDEPENDENT   |

| 35 USC 119 (a-c                                  | nowledged  | ☐yes ☐no<br>et ☐yes ☐no ☐Met a   |                         | TATE OR SHEE<br>COUNTRY DRAY | TS<br>WING | CLAIMS<br>13 | CLAIMS<br>2   |

| S PO BOX                                         | AND GREEN  | BERG PA                          | IIIIIII                 |                              |            |              |               |

| DYNAMIC<br>H DYNAMIC                             | SEMICOND   | UCTOR MEMORY DEV                 | VICE AND MET            | THOD FOR INTI                | IALIZING   | <b>A</b>     |               |

| FILING FEE<br>RECEIVED<br>\$890                  | No.        | Authority has been to charge/cre | edit DEPOSIT A          | ACCOUNT                      |            |              | Ext. of time) |

### LERNER AND GREENBERG, P.A.

PATENT ATTORNEYS AND ATTORNEYS AT LAW

2200 Hollywood Boulevard Hollywood, Florida 33020 Tel: (954) 925-1100 Fax: (954) 925-1101

e-mail: patents@patentusa.com

<u>Mailing Address:</u> Post Office Box 2480 Hollywood, FL 33022-2480

New York Office 153 E 57th Street Suite 15G New York, NY 10022

"Express Mail" mailing label number <u>EL080659885US</u> Date of Deposit <u>June 30, 1999</u>

XIOMARA D. JUNCO

I hereby certify that this paper or fee is being deposited with the United States Postal Service "Express Mail Post Office to Addressee" service under 37 CFR 1.10 on the date indicated above and is addressed to the Assistant Commissioner for Patents, Washington, D.C. 20231.

Docket No.: GR 98 P 1989

Gregory L. Mayback (FL Bar) Otto S. Kauder (Rog. Pat. Agent)

Adam A. Jorgensen (Reg. Pat. Agent)

Date: June 30, 1999

Hon. Commissioner of Patents and Trademarks Washington, D.C. 20231

Sir:

Enclosed herewith are the necessary papers for filing the following application for Letters Patent:

Applicant

**GUNNAR KRAUSE**

Title

DYNAMIC SEMICONDUCTOR MEMORY DEVICE AND

METHOD FOR INITIALIZING A DYNAMIC SEMICONDUCTOR

**MEMORY DEVICE**

3 sheets of formal drawings in triplicate. A check in the amount of \$760.00 covering the filing fee. Information Disclosure Statement and 1 Reference.

This application is being filed without a signed oath or declaration under the provisions of 37 CFR 1.53(d). Applicants await notification of the date by which the oath or declaration and the surcharge are due, pursuant to this rule.

The Patent and Trademark Office is hereby given authority to charge Deposit Account No. 12-1099 of Lerner and Greenberg, P.A. for any fees due or deficiencies of payments made for any purpose during the pendency of the above-identified application.

Respectfully submitted

For Applicant

LAURENCE A. GREENBERG REG. NO. 29,308

LAG:tg

| PATENT | APPLICATION | SERIAL NO. |

|--------|-------------|------------|

U.S. DEPARTMENT OF COMMERCE PATENT AND TRADEMARK OFFICE FEE RECORD SHEET

07/13/1999 KHARLING 00000038 09343431 01 FC:101 760.00 0P

PTO-1556 (5/87)

\*U.S. GPO: 1998-433-214/80404

### Abstract of the Disclosure:

09/343431

A dynamic semiconductor memory device of a random access type has an initialization circuit that controls the switching-on operation of the semiconductor memory device and of its circuit components.

5 The initialization circuit supplies a supply voltage stable signal once the supply voltage has been stabilized after the switching-on of the semiconductor memory device. The initialization circuit has an enable circuit that receives the supply voltage stable signal and further command signals externally applied to the

10 semiconductor memory device. The enable circuit supplies an will enable signal after a predetermined proper initialization sequence of the command signals applied to the semiconductor memory device is identified. The enable signal effects the unlatching of a control circuit provided for the proper operation of the

WREL/cgm

GR 98 P 1989

# DYNAMIC SEMICONDUCTOR MEMORY DEVICE AND METHOD FOR INITIALIZING A DYNAMIC SEMICONDUCTOR MEMORY DEVICE

### Background of the Invention:

#### Field of the Invention:

The invention relates to a dynamic semiconductor memory device of the random access type (DRAM/SDRAM) having an initialization circuit which controls a switching-on operation of the semiconductor memory device and of its circuit components. The initialization circuit supplies a supply voltage stable signal (POWERON) once a supply voltage has been stabilized after the switching-on of the semiconductor memory device. The invention also relates to a method for initializing such a dynamic semiconductor memory device, and also to the use of an enable circuit, that supplies an enable signal, for controlling the switching-on operation of the dynamic semiconductor memory device.

20

25

10

15

We think think many that

In the case of SDRAM semiconductor memories according to the JEDEC standard, it is necessary to ensure during the switch-on operation ("POWERUP") that the internal control circuits provided for the proper operation of the semiconductor memory device are reliably held in a defined desired state, in order to prevent undesirable activation of output transistors that would cause, on the data lines, a short circuit (so-called "bus contention" or "data

$\geq$

20

contention") or uncontrolled activation of internal current loads. The solution to the problem turns out to be difficult on account of a fundamental unpredictability of the time characteristic of the supply voltage and of the voltage level or levels at the external control inputs during the switch-on operation of the semiconductor memory. According to the specifications of the manufacturer an SDRAM component should ignore all commands which are present chronologically before a defined initialization sequence. The sequence consists of predetermined commands that must be applied in a defined chronological order. However, a series of functions and commands which are allowed during proper operation of the component are desired or allowed chronologically only after the initialization sequence. According to the JEDEC standard for SDRAM semiconductor memories, a recommended initialization sequence (so-called "POWERON-SEQUENCE") is provided as follows:

- a. the application of a supply voltage and a start pulse in order to maintain an NOP condition at the inputs of the component;

- b. the maintenance of a stable supply voltage of a stable clock signal, and of stable NOP input conditions for a minimum time period of 200 us;

- c. the preparation command for word line activation (PRECHARGE) for all the memory banks of the device;

- 4. the activation of eight or more refresh commands (AUTOREFRESH); and

- 5. the activation of a loading configuration register command (MODE-REGISTER-SET) for initializing the mode register.

After the identification of such a defined initialization sequence, the memory module is normally in a so-called IDLE state, that is to say it is precharged and prepared for proper operation. In the case of the SDRAM semiconductor memory modules that have been disclosed to date, all the control circuits of the component have been unlatched only with the POWERON signal. The signal POWERON is active if the internal supply voltages have reached the necessary values that are necessary for the proper operation of the component. The module is then in a position to recognize and execute instructions.

### Summary of the Invention:

It is accordingly an object of the invention to provide a dynamic semiconductor memory device and a method for initializing a dynamic semiconductor memory device which overcome the abovementioned disadvantages of the prior art methods and devices of this general type, which is as simple as possible in structural terms and which effectively prevents the risk of a short circuit

of the data lines and/or of uncontrolled activation of internal current loads.

With the foregoing and other objects in view there is provided, in accordance with the invention, a dynamic semiconductor memory device of a random access type, containing an initialization circuit controlling a switching-on operation and supplying a supply voltage stable signal once a supply voltage has been stabilized after the switching-on operation. The initialization circuit has a control circuit for controlling operations and an enable circuit receiving the supply voltage stable signal and externally applied further command signals. The enable circuit outputting an enable signal after a predetermined proper initialization sequence of the externally applied further command signals are identified and the enable signal effecting an unlatching of the control circuit.

Other and word off rough the sense of the first of the fi

25

The invention provides for the initialization circuit to have an enable circuit, which receives the supply voltage stable signal and the externally applied further command signals. The enable circuit generates the enable signal after the identification of the predetermined proper initialization sequence of the command signals is achieved. The enable signal effects the unlatching of the control circuit provided for the proper operation of the semiconductor memory device.

20

25

Following the principle of the invention, the enable signal (CHIPREADY) is generated and becomes active in dependence on further internal signals and the initialization sequence and then unlatches predetermined circuits. The predetermined circuits remain latched until the end of the predetermined initialization sequence. By way of example, commands are decoded but not executed and the output drivers are held at high impedance.

According to the preferred application in SDRAM memory devices according to the JEDEC standard, it is provided that the command signals, externally applied to the semiconductor memory device, of the initialization sequence are to be identified by the enable circuit. The command signals include a preparation command signal for word line activation (PRECHARGE), and/or a refresh command signal (AUTOREFRESH), and/or a loading configuration register command signal (MODE-REGISTER-SET).

According to an advantageous structural refinement of the initialization circuit according to the invention, it is provided that the enable circuit has at least one bistable multivibrator stage with a set input which receives the command signal (PRECHARGE, AUTOREFRESH, MODE-REGISTER-SET). The bistable multivibrator also has a reset input to which the supply voltage stable signal (POWERON), a signal derived therefrom, or a linked signal is applied. The bistable multivibrator further has an output at which the enable signal (CHIPREADY) is outputted.

20

25

In particular, the enable circuit has a plurality of bistable multivibrator stages respectively receiving the command signals.

In an expedient refinement of the invention, it is provided that the output of at least one of the bistable multivibrator stages is passed to a reset input of a further multivibrator stage. In this case, it may furthermore be provided that, in one of the bistable multivibrator stages, the supply voltage stable signal (POWERON) and the signal output from the output of the further multivibrator stage are passed, after having been logically combined by a gate, to the reset input of the multivibrator stage.

Other features which are considered as characteristic for the invention are set forth in the appended claims.

Although the invention is illustrated and described herein as embodied in a dynamic semiconductor memory device and a method for initializing a dynamic semiconductor memory device, it is nevertheless not intended to be limited to the details shown, since various modifications and structural changes may be made therein without departing from the spirit of the invention and within the scope and range of equivalents of the claims.

The construction and method of operation of the invention, however, together with additional objects and advantages thereof

And the same of the same of the title same of the same

25

will be best understood from the following description of specific embodiments when read in connection with the accompanying drawings.

### Brief Description of the Drawings:

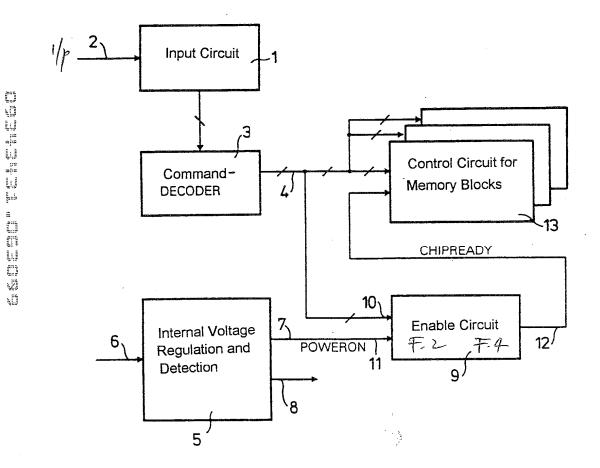

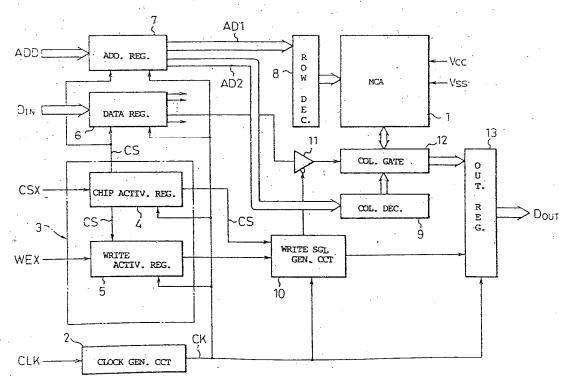

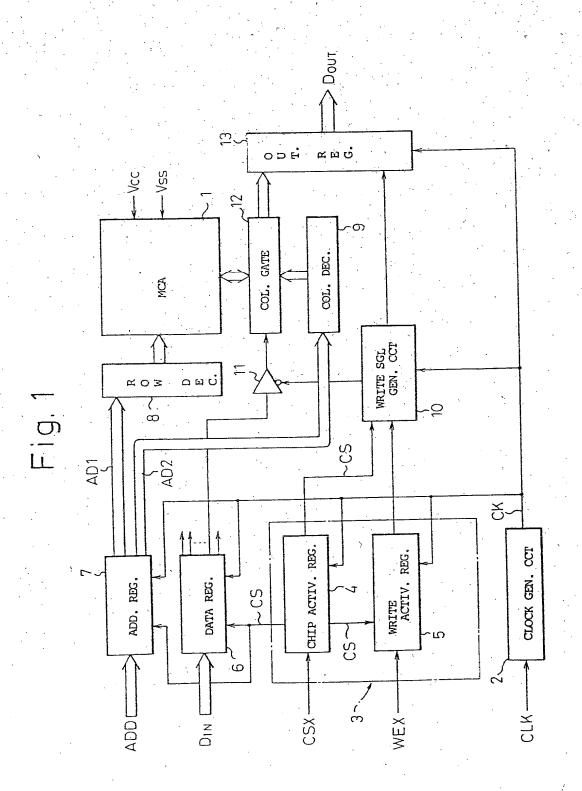

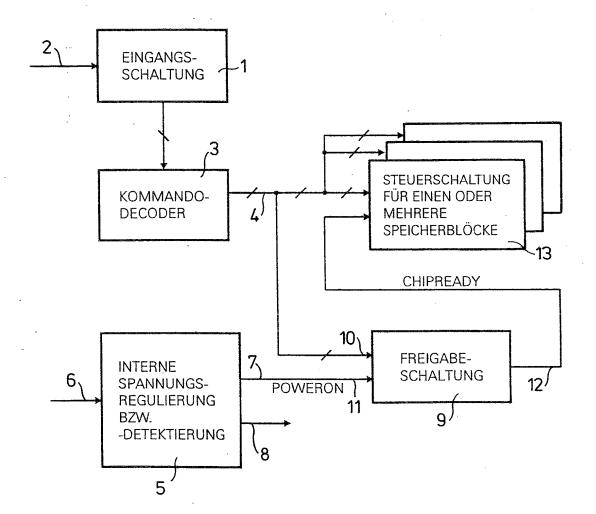

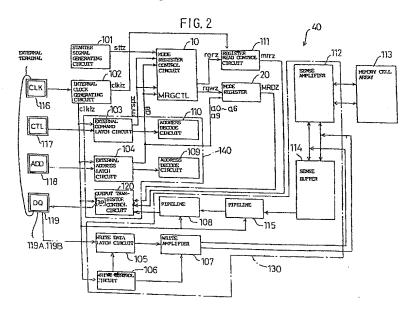

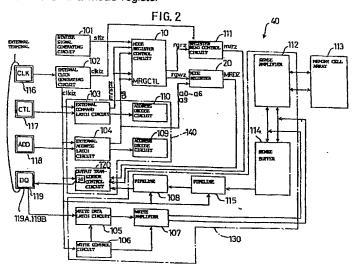

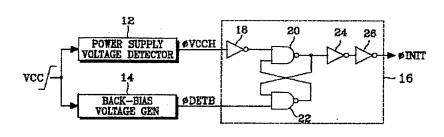

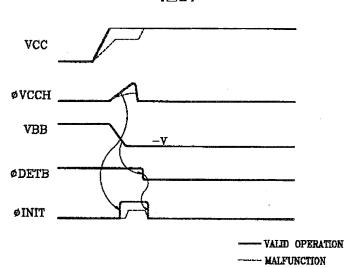

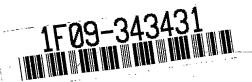

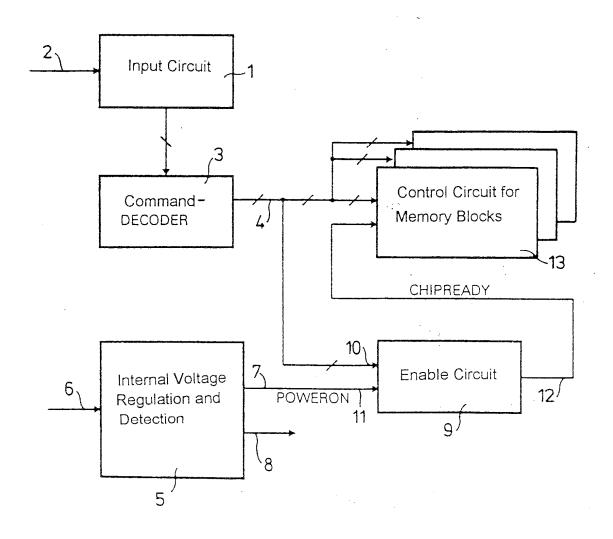

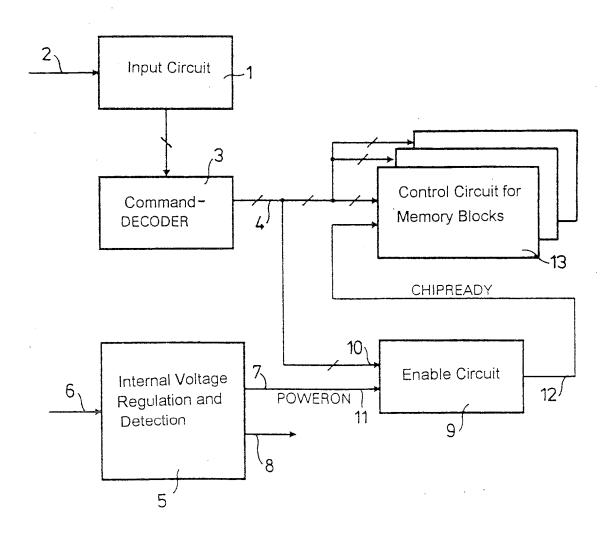

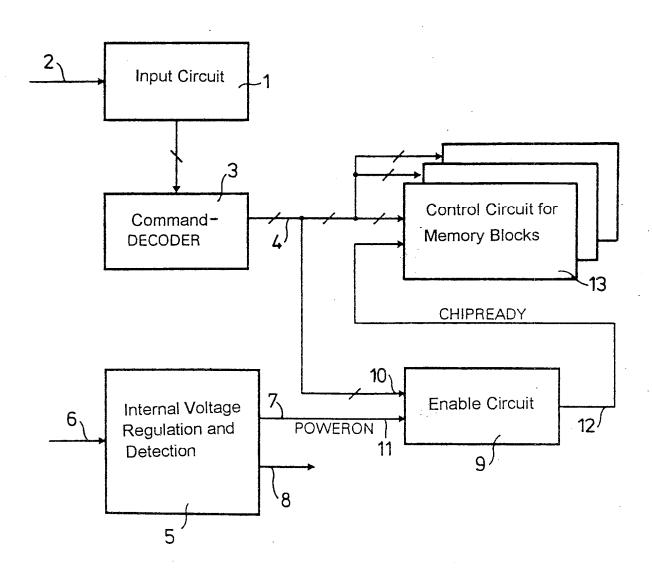

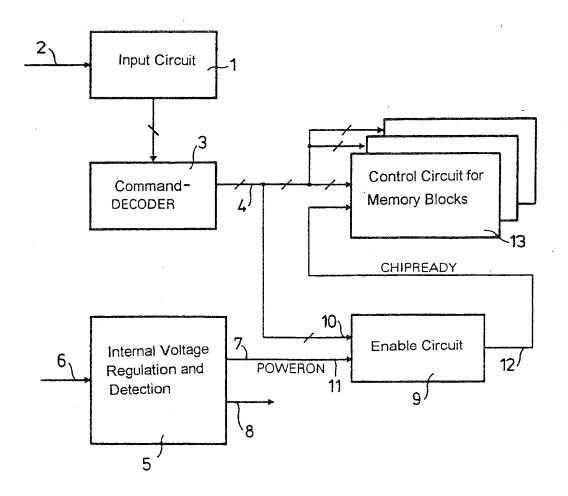

Fig. 1 is a diagrammatic, block diagram of components of an initialization circuit which controls a switching-on operation of a semiconductor memory and its circuit components according to the invention;

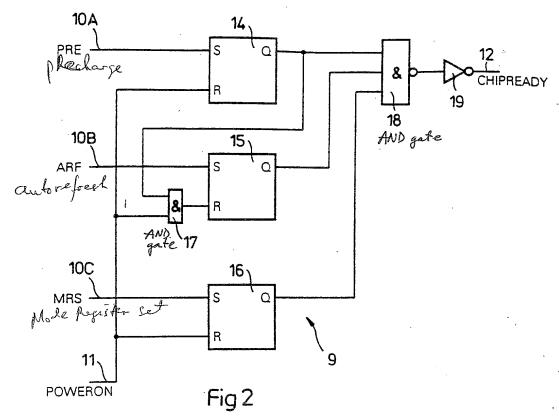

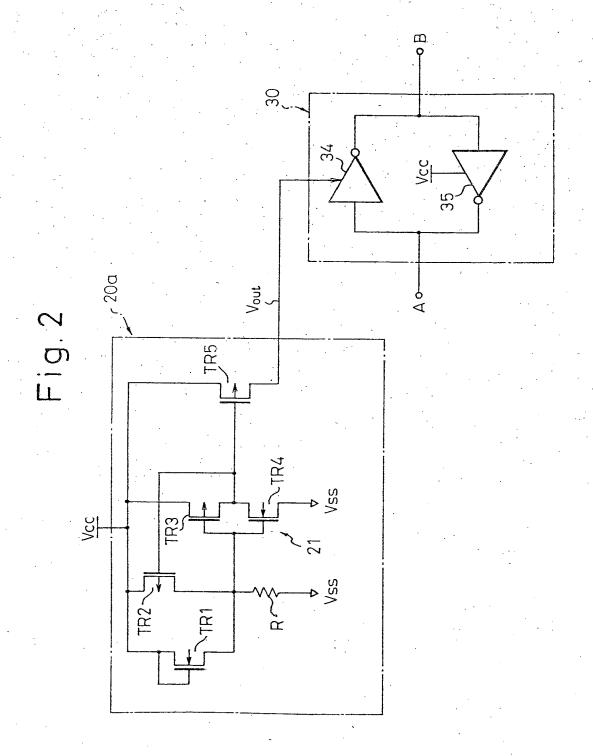

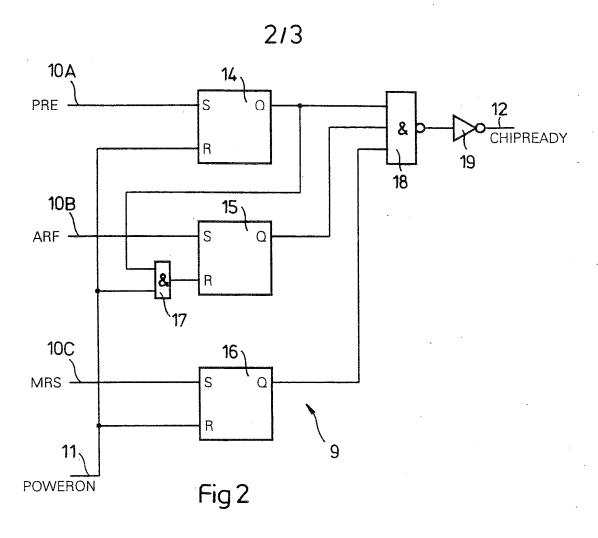

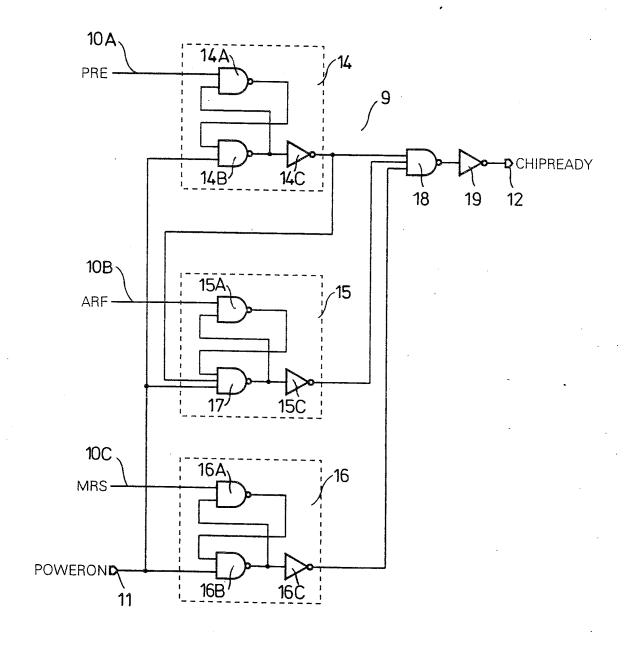

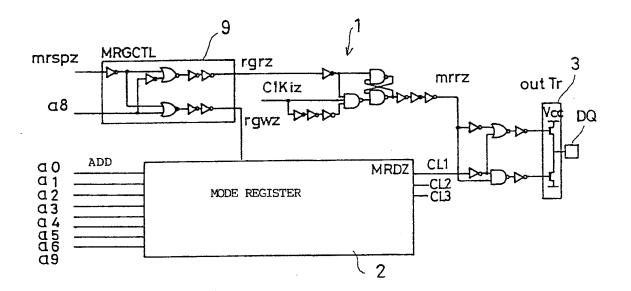

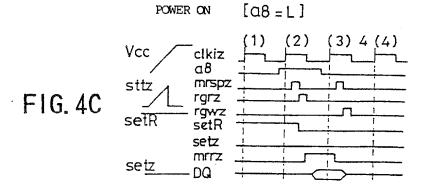

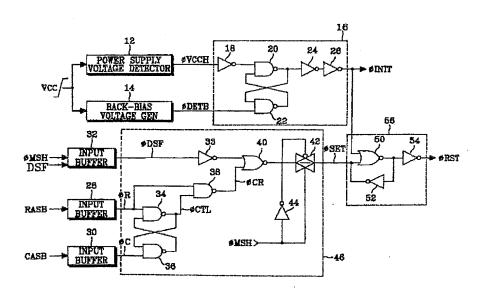

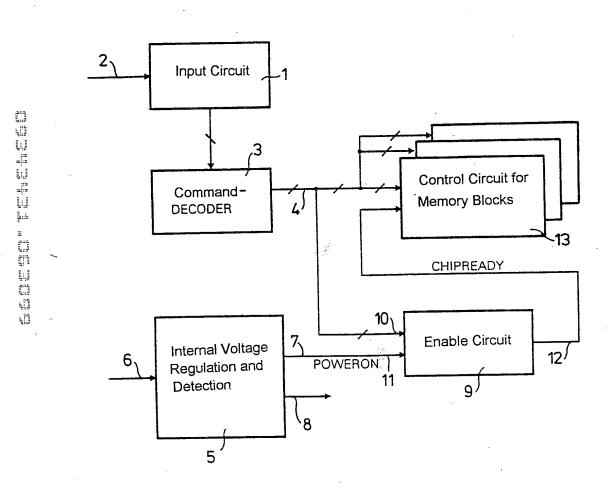

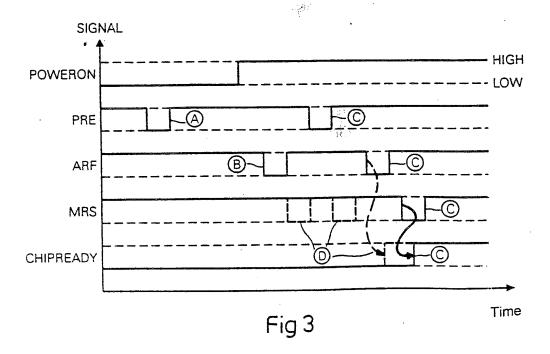

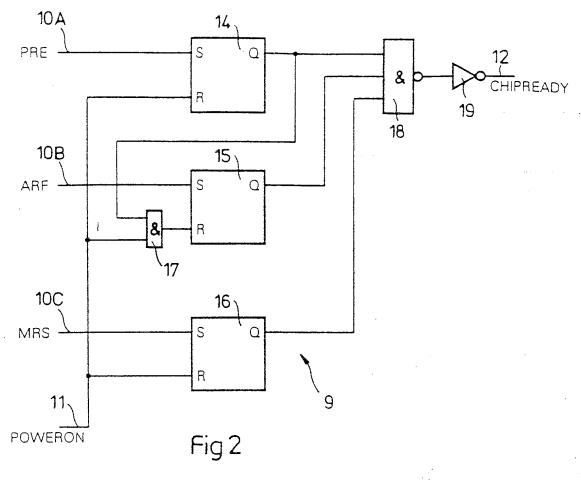

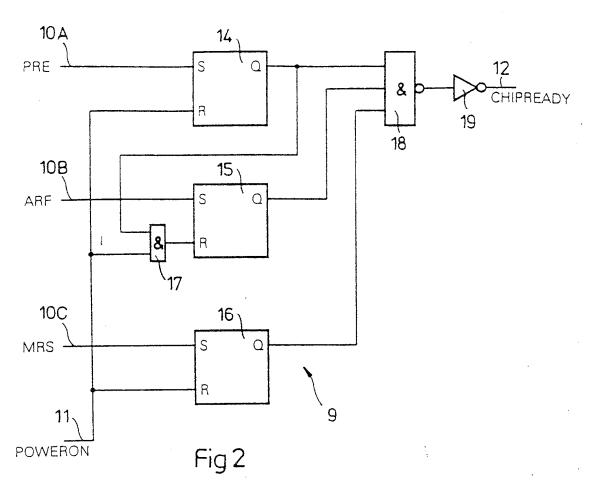

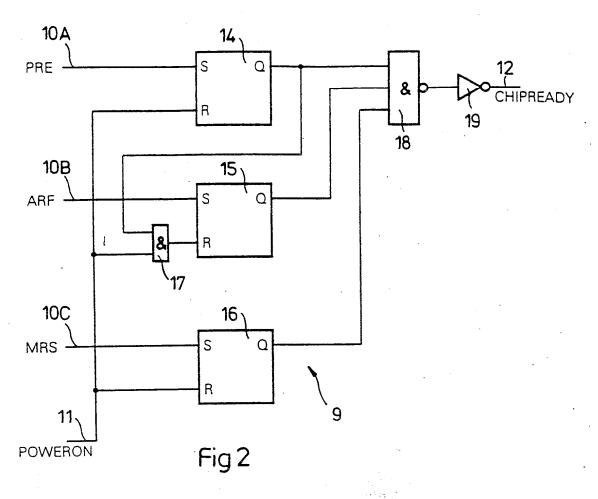

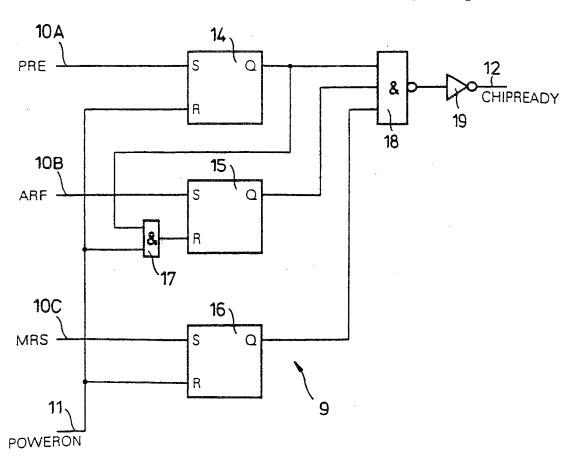

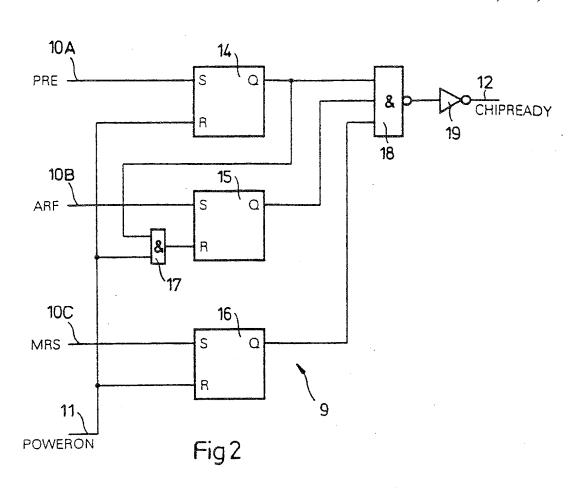

Fig. 2 is circuit diagram of an enable circuit that supplies an enable signal (CHIPREADY);

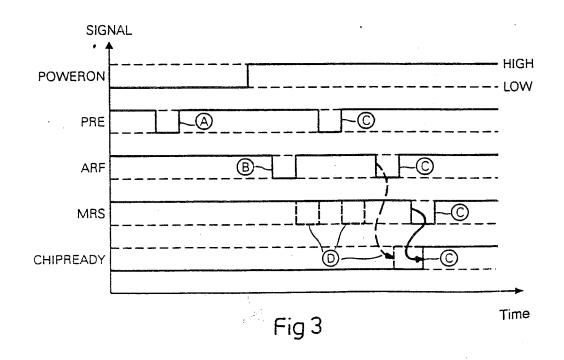

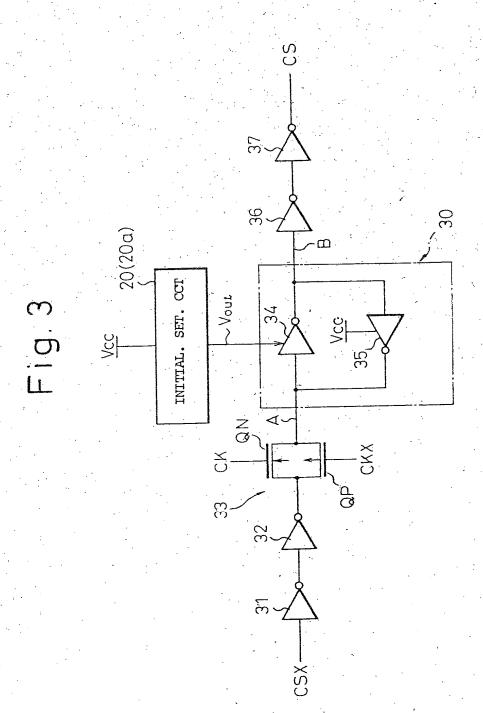

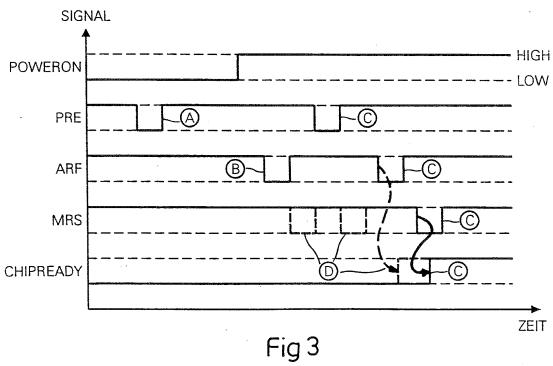

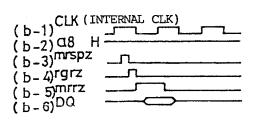

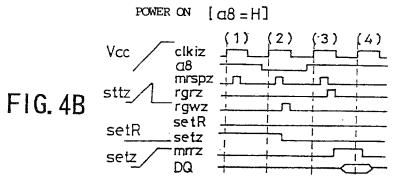

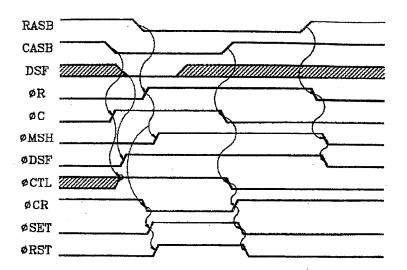

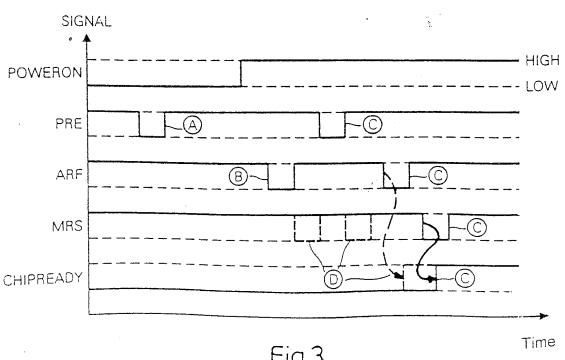

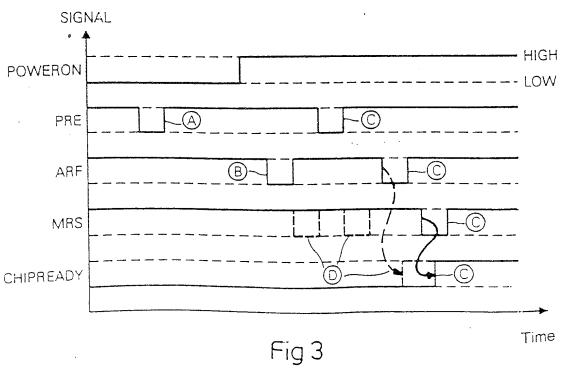

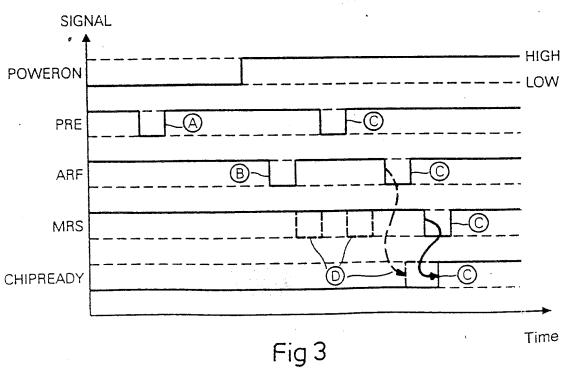

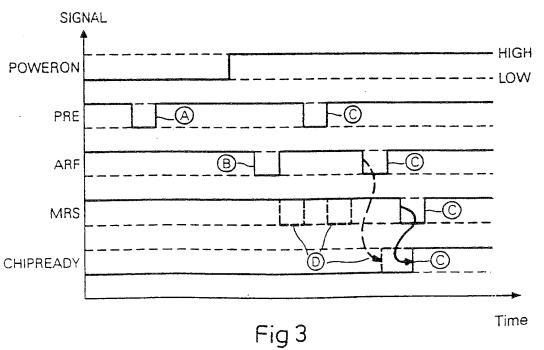

Fig. 3 is a time sequence diagram for elucidating a method of operation of the circuit according to Fig. 2; and

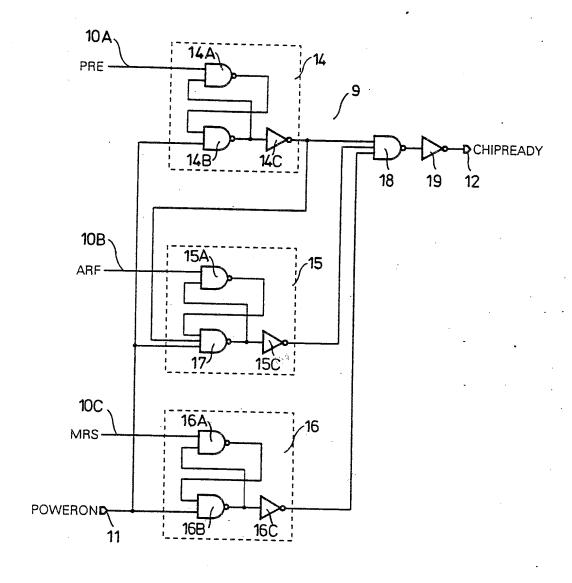

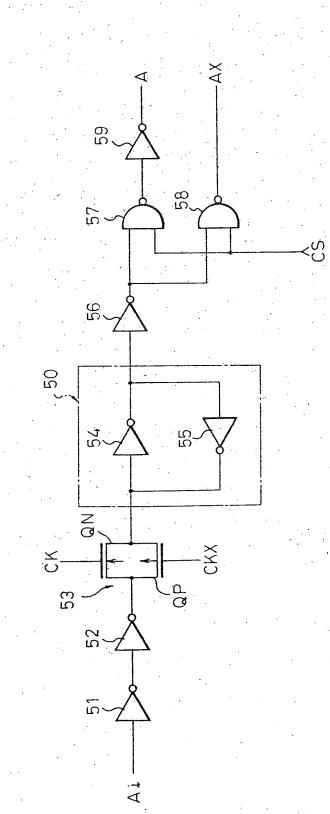

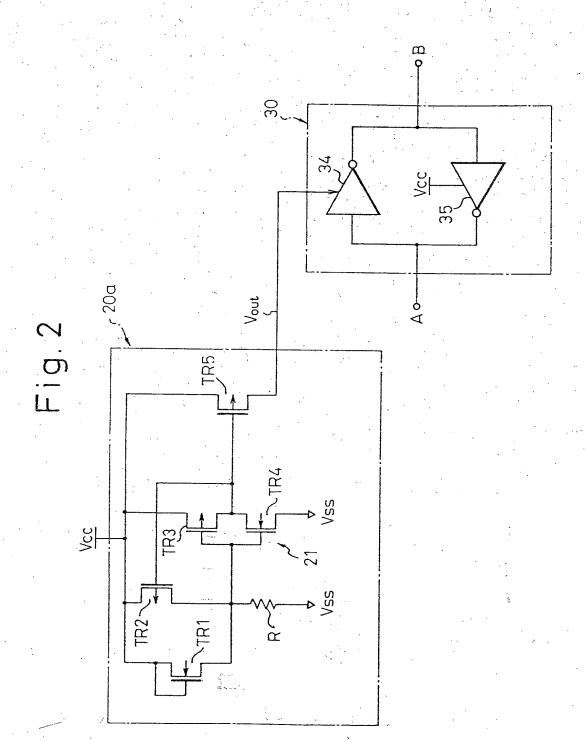

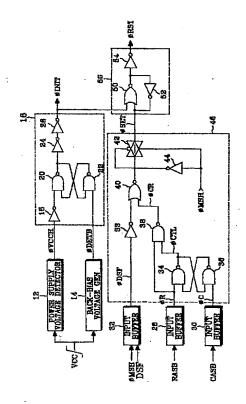

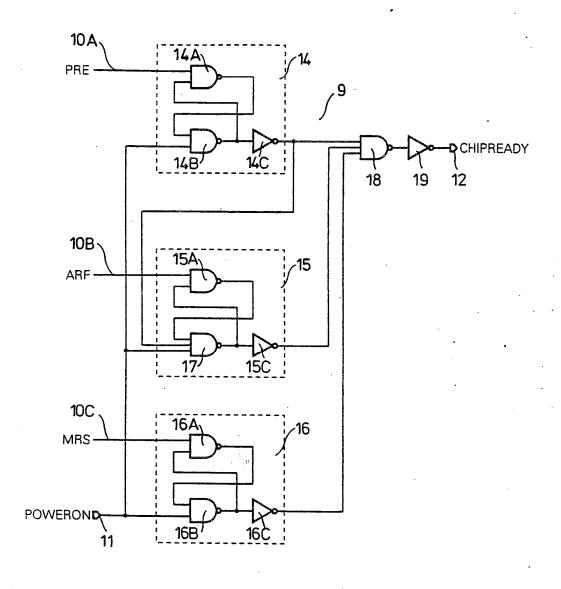

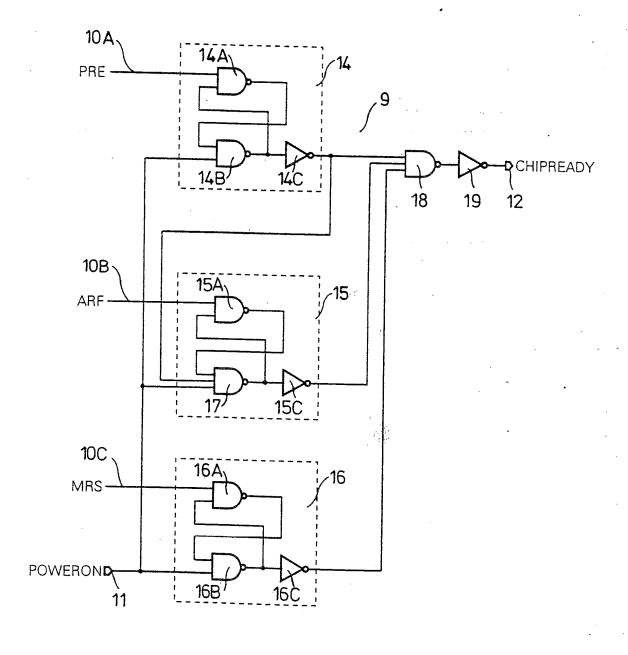

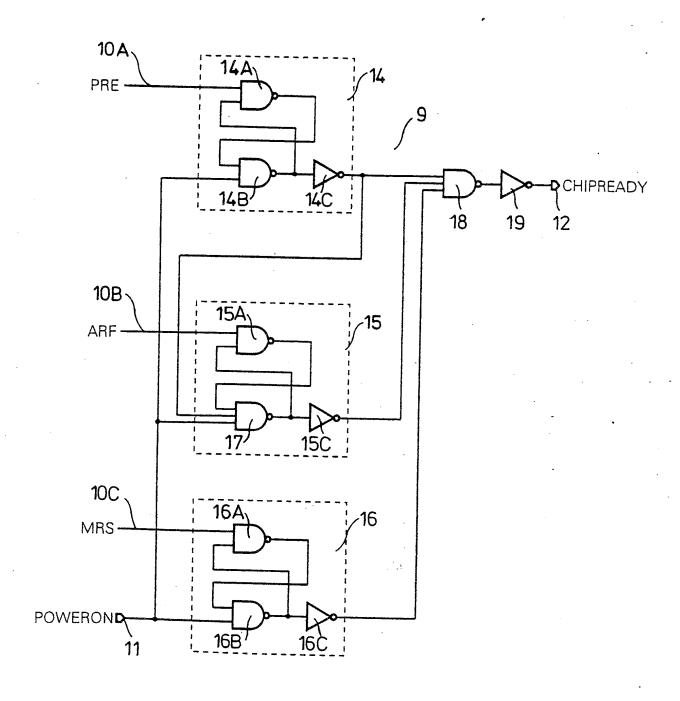

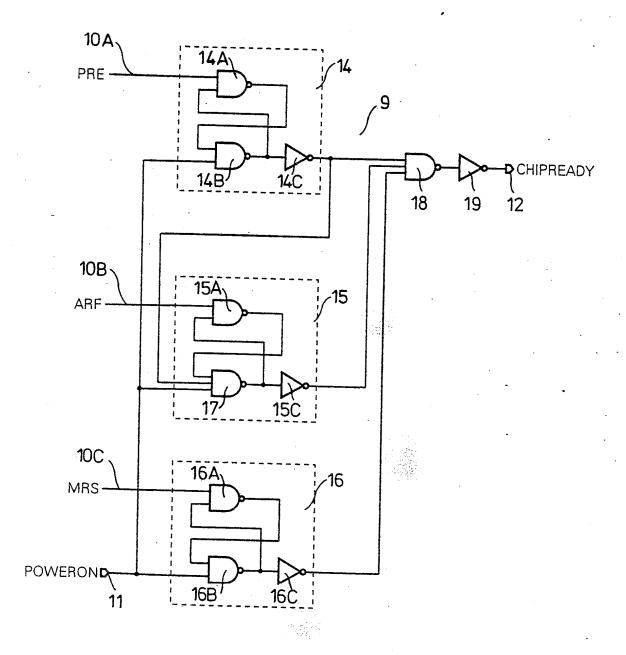

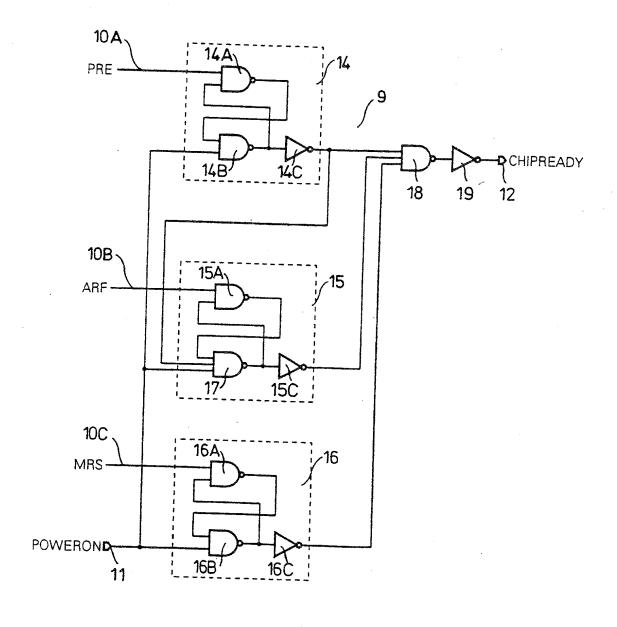

Fig. 4 is a circuit diagram of the enable circuit according to an exemplary embodiment of the invention.

### 20 <u>Description of the Preferred Embodiments</u>:

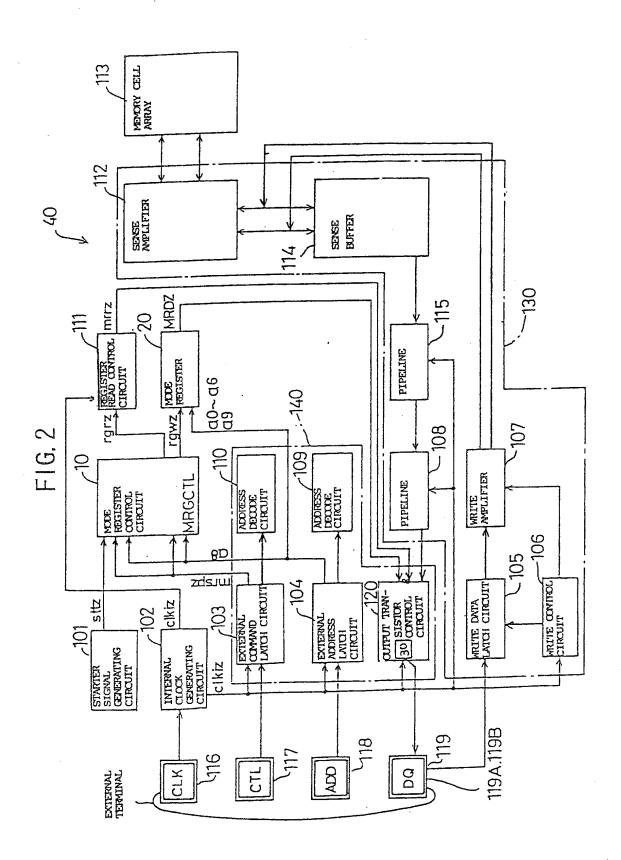

In all the figures of the drawing, sub-features and integral parts that correspond to one another bear the same reference symbol in each case. Referring now to the figures of the drawing in detail and first, particularly, to Fig. 1 thereof, there are shown circuit components, important for understanding the invention, of an SDRAM memory device operating according to the JEDEC standard.

The circuit components include an initialization circuit controlling a switching-on operation of the SDRAM memory device and its circuit components. The initialization circuit has an input circuit 1, to whose input 2 command and clock signals that are externally applied in reference to the semiconductor memory are provided. The command and clock signals are amplified and conditioned before being received by a command decoder 3 connected downstream of the input circuit 1 and at whose output 4, inter alia, the command signals PRE or PRECHARGE (preparation command for word line activation), ARF or AUTOREFRESH (refresh command) and MRS or MODE-REGISTER-SET (loading configuration register command) are output. The initialization circuit further has a circuit 5 for internal voltage regulation and/or detection, at whose input 6 the external supply voltages that are externally 15 applied to the semiconductor memory externally are fed in. The 🖺 circuit 5 has a first output 7 outputting a POWERON signal and a www.second output 8 supplying stabilized internal supply voltages. The method of operation and the structure of the circuits 1, 3 and 5 are sufficiently known to the person skilled in the art and therefore do not need to be explained in any more detail. What is important for understanding the invention is the fact that the circuit 5 supplies an active POWERON signal if, after the POWERUP phase of the SDRAM memory, the internal supply voltages present at the output 8 have reached the values necessary for proper operation of the component.

10

25

has an enable circuit 9 connected downstream of the circuits 3 and 5. The command signals PRE, ARF and MRS are applied to an input 10 of the enable circuit 9 and the POWERON signal is applied to an input 11 of the enable circuit 9. An enable signal CHIPREADY is supplied at an output 12 of the enable circuit 9 after the identification of a predetermined proper initialization sequence of the command signals applied to the semiconductor memory device is achieved. The enable signal effects unlatching of control circuits 13 provided for proper operation of the semiconductor memory device. The internal control circuits 13 serve inter alia for sequence control for one or more of the memory blocks of the SDRAM memory and are known as such.

Quality and made it made it made all the first that the first that

43

20

25

According to the invention, the initialization circuit furthermore

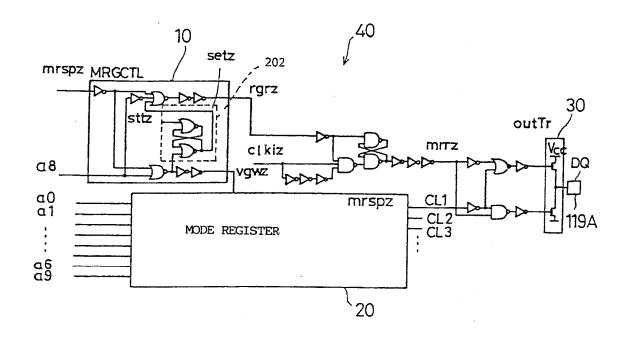

Fig. 2 shows a preferred exemplary embodiment of the enable circuit 9 according to the invention. The enable circuit 9 contains three bistable multivibrator stages 14, 15 and 16 each having a set input S, a reset input R, and also an output Q. An AND gate 17 connected upstream of the reset input R of the multivibrator stage 15 and an AND gate 18 connected downstream of all the outputs Q of the multivibrator stages 14, 15, 16 are further provided. The enable circuit further has an inverter 19 connected downstream of the AND gate 18. The enable signal CHIPREADY being output at the output 12 of the inverter 19 and the enable signal CHIPREADY is active HIGH, that is to say activated when its voltage level is at logic HIGH. The command signals PRE,

ARF, MRS applied to the respective set inputs S of the bistable multivibrator stages 14, 15, 16 are each active LOW, that is to say these signals are active when their voltage level is at logic LOW, while the POWERON signal is again active HIGH. The POWERON signal is applied directly to the reset inputs R in the case of the multivibrator stages 14 and 16 and is firstly applied to one input of the AND gate 17 in the case of the multivibrator stage 15, the signal output from the output Q of the multivibrator stage 14 is applied to the other input of the AND gate 17, the output of the AND gate 17 is connected to the reset input of the multivibrator stage 15 multivibrator stage 15.

10

20

25

The method of operation of the enable circuit 9 illustrated in

Fig. 2 is such that activation of the enable signal CHIPREADY at

the output 12 to logic HIGH is generated only when a predetermined

chronological initialization sequence of the command signals PRE,

ARF and MRS and activation of the POWERON signal to the logic

level HIGH are detected. Only then are the control circuits 13

unlatched on account of the activation of the enable signal

CHIPREADY; the control circuits 13 remaining latched prior to

this.

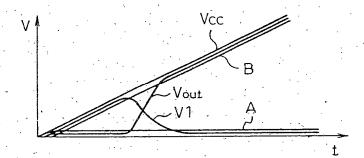

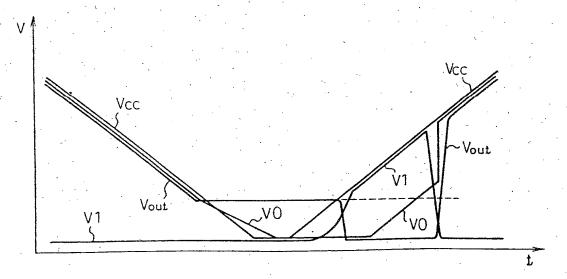

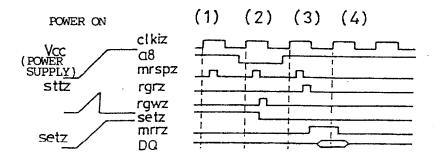

In the schematic time sequence diagram according to Fig. 3, exemplary command sequences during the switching-on operation of the semiconductor memory device are illustrated in order to elucidate the method of operation of the enable circuit 9.

In the case situation A, the signal PRECHARGE is activated to active LOW too early relative to the activation of the POWERON signal, with the result that, the enable signal CHIPREADY is not yet activated to logic HIGH since the proper initialization sequence requires a waiting time before the first command. signal swing of the command PRECHARGE according to case situation A is thus correctly ignored. In case situation B, the chronological order of the activation of the signal AUTOREFRESH to logic LOW is incorrect since the proper initialization sequence prescribes a previous PRECHARGE command before the AUTOREFRESH command. The signal swing of the AUTOREFRESH signal to logic LOW according to case situation B is therefore likewise ignored, and the enable signal does not go to logic HIGH. In case situation C, 15 a correct chronological order of the commands PRECHARGE, AUTOREFRESH, MODE-REGISTER-SET is present conforming to the JEDEC standard, in a logically consistent manner, since the POWERON signal is also at logic HIGH, an enable signal CHIPREADY at logic HIGH is now supplied. Illustrated using dashed lines, another further conceivable initialization sequence that is allowed and therefore triggers an enable signal is represented by the symbol D; activation of the command MODE-REGISTER-SET to logic LOW is allowed at any time after the activation of the POWERON signal.

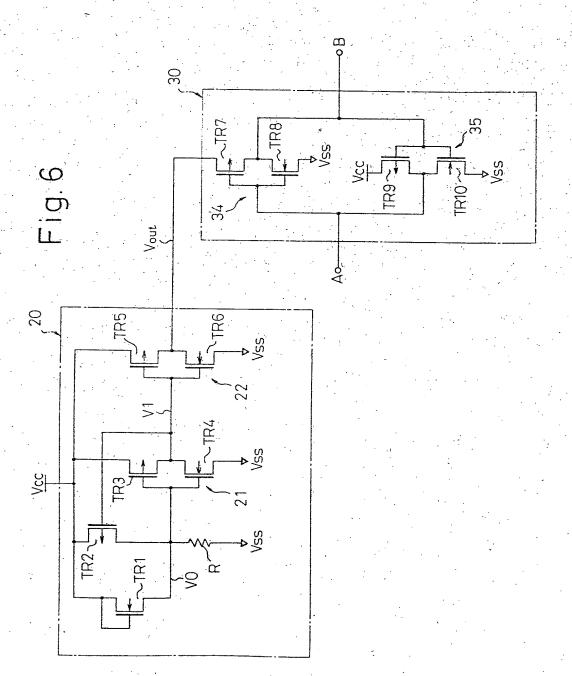

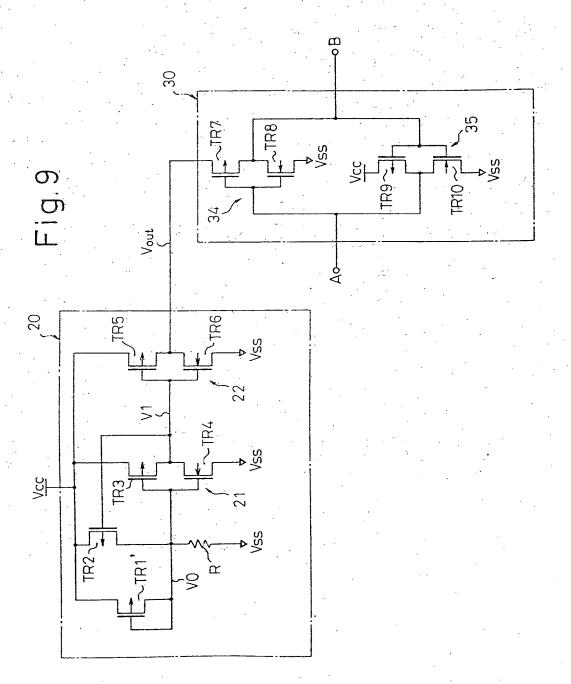

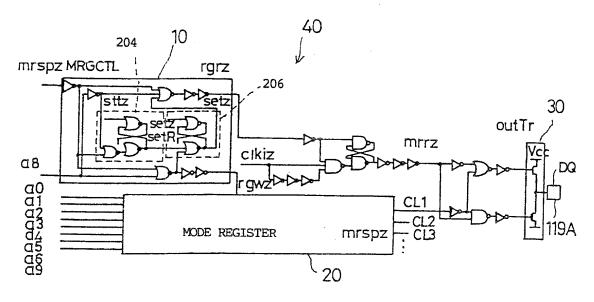

Fig. 4 shows further details of a preferred exemplary embodiment of the enable circuit 9 according to the invention.

20

25

exemplary embodiment, each of the bistable multivibrators 14, 15, 16 is constructed from in each case two NAND gates 14A, 14B, 15A, 17, 16A, 16B and also an inverter 14C, 15C and 16C, which are connected to one another in the manner illustrated. The NAND gate 17 is provided with three inputs in the bistable multivibrator 15.

#### I Claim:

1. A dynamic semiconductor memory device of a random access type, comprising:

an initialization circuit controlling a switching-on operation and supplying a supply voltage stable signal once a supply voltage has been stabilized after the switching-on operation, said initialization circuit having a control circuit for controlling operations and an enable circuit receiving the supply voltage power can proper for the stable signal and externally applied further command signals, said enable circuit outputting an enable signal after a predetermined proper initialization sequence of the externally applied further command signals being identified and the enable signal effecting an unlatching of said control circuit.

- 2. The semiconductor memory device according to claim 1, wherein the externally applied further command signals forming the predetermined proper initialization sequence to be identified by said enable circuit includes at least one of a preparation command signal for word line activation, a refresh command signal, and a loading configuration register command signal.

- 3. The semiconductor memory device according to claim 1, wherein said enable circuit has at least one bistable multivibrator stage having a set input receiving the externally applied further command signals, a reset input receiving one of the supply voltage

stable signal, a signal derived from the supply voltage stable signal and a linked signal, and an output outputting said enable signal.

- 4. The semiconductor memory device according to claim 3, wherein said at least one bistable multivibrator stage is a plurality of bistable multivibrator stages respectively receiving one of the externally applied further command signals.

- 5. The semiconductor memory device according to claim 4, wherein said output of one of said plurality of bistable multivibrator stages is passed to said reset input of another of said plurality of bistable multivibrator stages.

- 6. The semiconductor memory device according to claim 4, including an AND gate receiving the supply voltage stable signal and a signal output from said output of one of said plurality of bistable multivibrator stages, said AND gate outputting an output signal received at said reset input of another of said plurality of bistable multivibrator stages.

- 7. The semiconductor memory device according to claim 4, wherein said plurality of bistable multivibrator stages are each formed of an RS flip-flop constructed from one of at least two NOR and at least two NAND gates.

- 8. The semiconductor memory device according to claim 1, wherein the identification of an initialization sequence that is identified as the predetermined proper initialization sequence by said enable circuit and generates the enable signal constitutes a command sequence conforming to a JEDEC standard.

- 9. The semiconductor memory device according to claim 1, wherein said control circuit has output drivers remaining latched during the switching-on operation until said enable signal is generated by said enable circuit.

- 10. The semiconductor memory device according to claim 1, wherein the predetermined proper initialization sequence includes one of the following chronologically successive command sequences:

- a) firstly PRE, secondly ARF, thirdly MRS;

- b) firstly PRE, secondly MRS, thirdly ARF; and

- c) firstly MRS, secondly PRE, or thirdly ARF;

where,

ARF = the refresh command signal, and

MRS = the loading configuration register command signal.

11. An improved method for initializing a dynamic semiconductor memory device of a random access type via an initialization circuit controlling a switching-on operation of the dynamic semiconductor memory device and of its circuit components, the improvement which comprises:

supplying, via the initialization circuit, a supply voltage stable signal once a supply voltage has been stabilized after the switching-on operation of the dynamic semiconductor memory device; and

supplying, via an enable circuit of the initialization circuit, an enable signal, the initialization circuit receiving the supply voltage stable signal and further command signals externally applied to the dynamic semiconductor memory device, after an identification of a predetermined proper initialization sequence of the further command signals the enable signal being generated and effecting an unlatching of a control circuit provided for a proper operation of the dynamic semiconductor memory device.

12. The method according to claim 11, which comprises providing at least one of a preparation command signal for word line activation, a refresh command signal, and a loading configuration register command signal as the further command signals.

13. The method according to claim 11, which comprises maintaining a latched condition of output drivers of the dynamic semiconductor memory device during the switching-on operation until the enable signal is generated by the enable circuit.

Docket No.: GR 98 P 1989

## COMBINED DECLARATION AND POWER OF ATTORNEY IN ORIGINAL APPLICATION

As a below named inventor, I hereby declare that: my residence, post office address and citizenship are as stated below next to my name; that I verily believe that I am the original, first and sole inventor (if only one name is listed below) or an original, first and joint inventor (if plural names are listed below) of the subject matter which is claimed and for which a patent is sought on the invention entitled:

## DYNAMIC SEMICONDUCTOR MEMORY DEVICE AND METHOD FOR INITIALIZING A DYNAMIC SEMICONDUCTOR MEMORY DEVICE

described and claimed in the specification bearing that title, that I understand the content of the specification, that I do not know and do not believe the same was ever known or used in the United States of America before my or our invention thereof, or patented or described in any printed publication in any country before my or our invention thereof or more than one year prior to this application, that the same was not in public use or on sale in the United States of America more than one year prior to this application, that the invention has not been patented or made the subject of an inventor's certificate issued before the date of this application in any country foreign to the United States of America on an application filed by me or my legal representatives or assigns more than twelve month prior to this application, that I acknowledge my duty to disclose information of which I am aware which is material to the examination of this application under 37 C.F.R. 1.56a, and that no application for patent or inventor's certificate of this invention has been filed earlier than the following in any country foreign to the United States prior to this application by me or my legal representatives or assigns:

German Application No. 198 29 287.2, filed June 30, 1998, the International Priority of which is claimed under 35 U.S.C. §119.

I hereby appoint the following attorney(s) and/or agent(s) to prosecute this application and to transact all business in the Patent and Trademark Office connected therewith:

HERBERT L. LERNER (Reg.No.20,435)

LAURENCE A. GREENBERG (Reg.No.29,308)

WERNER H. STEMER (Reg.No.34,956)

RALPH E. LOCHER (Reg.No.41,947)

Address all correspondence and telephone calls to:

POST OFFICE BOX 2480

HOLLYWOOD, FLORIDA 33022-2480

TEL: (954) 925-1100 FAX: (954) 925-1101

I hereby state that I have reviewed and understand the contents of the above-identified specification, including the claims, as amended by any amendment referred to above.

I hereby declare that all statements made herein of my own knowledge are true and that all statements made on information and belief are believed to be true; and further that these statements were made with the knowledge that willful false statements and the like so made are punishable by fine or imprisonment, or both, under Section 1001 Title 18 of the United States Code and that such willful false statements may jeopardize the validity of the application or any patent issued thereon.

| JLL NAME OF SOLE INVENTOR:                      |                                                                    |  |  |  |  |

|-------------------------------------------------|--------------------------------------------------------------------|--|--|--|--|

| E:                                              |                                                                    |  |  |  |  |

|                                                 |                                                                    |  |  |  |  |

| I, GERMANY                                      |                                                                    |  |  |  |  |

| GERMANY                                         |                                                                    |  |  |  |  |

| SCHLIERSEESTRASS<br>D-81541 MUENCHEN<br>GERMANY |                                                                    |  |  |  |  |

|                                                 |                                                                    |  |  |  |  |

|                                                 |                                                                    |  |  |  |  |

|                                                 | E:<br>I, GERMANY<br>GERMANY<br>SCHLIERSEESTRAS<br>D-81541 MUENCHEN |  |  |  |  |

Fig 1

Fig 4

### UNITED STATES LUPARTMENT OF COMMERCE Patent and Trademark Office Address: COMMISSIONER OF PATENTS AND TRADEMARKS

Washington, D.C. 20231

| APPLICATION NUMBER | FILING/RECEIPT DATE | FIRST NAMED APPLICANT                   | ATTORNEY DOOKET NO FITTE  |

|--------------------|---------------------|-----------------------------------------|---------------------------|

|                    |                     | 1 11 11 11 11 11 11 11 11 11 11 11 11 1 | ATTORNEY DOCKET NO./TITLE |

|                    |                     |                                         |                           |

09/343,431

If all various discussion and the co

06/30/99

KRAUSE

<u>-</u>

GR98P1989

0212/0727

LERNER AND GREENBERG PA PO BOX 2480 HOLLYWOOD FL 33022-2480

NOT ASSIGNED

2818

DATE MAILED:

07/27/99

### NOTICE TO FILE MISSING PARTS OF APPLICATION Filing Date Granted

An Application Number and Filing Date have been assigned to this application. The items indicated below, however, are missing. Applicant is given TWO MONTHS FROM THE DATE OF THIS NOTICE within which to file all required items and pay any fees required below to avoid abandonment. Extensions of time may be obtained by filing a petition accompanied by the extension fee under the provisions of 37 CFR 1:136(a). If any of items 1 or 3 through 5 are indicated as missing, the SURCHARGE set forth in 37 CFR 1.16(e) of \$65.00 for a small entity in compliance with 37 CFR 1.27, or \$130.00 for a non-small entity, must also be timely submitted in reply to this NOTICE to avoid abandonment. to this NOTICE to avoid abandonment.

| If all required items on this form are filed within the period set above, the total amount owed by applicant as a □ small entity (statement filed) □ non-small entity is \$                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>1. The statutory basic filing fee is:</li> <li>missing.</li> <li>insufficient.</li> <li>Applicant must submit \$ to complete the basic filing fee and/or file a small entity statement claiming such status (37 CFR 1.27).</li> </ul>                                                                        |

| 2. The following additional claims fees are due:                                                                                                                                                                                                                                                                      |

| \$total claims over 20.                                                                                                                                                                                                                                                                                               |

| \$independent claims over 3.                                                                                                                                                                                                                                                                                          |

| \$for multiple dependent claim surcharge.  Applicant must either submit the additional claim fees or cancel additional claims for which fees are due.                                                                                                                                                                 |

| 3. The oath or declaration: is missing or unsigned. does not cover the newly submitted items. An oath or declaration in compliance with 37 CFR 1. 63, including residence information and identifying the application by                                                                                              |

| the above Application Number and Filing Date is required.  4. The signature(s) to the oath or declaration is/are by a person other than inventor or person qualified under 37 CFR 1.42, 1.43 or 1.47.  A properly signed oath or declaration in compliance with 37 CFR 1.63, identifying the application by the above |

| Application Number and Filing Date, is required.                                                                                                                                                                                                                                                                      |

| □ 5. The signature of the following joint inventor(s) is missing from the oath or declaration:                                                                                                                                                                                                                        |

| An oath or declaration in compliance with 37 CFR 1.63 listing the names of all inventors and signed by the omitted inventor(s), identifying this application by the above Application Number and Filing Date, is required.                                                                                            |

| 6. A \$50.00 processing fee is required since your check was returned without payment (37 CFR 1.21(m)).                                                                                                                                                                                                               |

| 7. Your filing receipt was mailed in error because your check was returned without payment.                                                                                                                                                                                                                           |

| 8. The application was filed in a language other than English.<br>Applicant must file a verified English translation of the application, the \$130.00 set forth in 37 CFR 1.17(k), unless previously submitted, and a statement that the translation is accurate (37 CFR 1.52(d)).                                    |

| □ 9. OTHER:                                                                                                                                                                                                                                                                                                           |

| Direct the reply and any questions about this notice to "Attention: Box Missing Parts."                                                                                                                                                                                                                               |

| A copy of this notice MUST be returned with the reply.                                                                                                                                                                                                                                                                |

Customer Service Center

Initial Patent Examination Division (703) 308-1202

FORM PTO-1533 (REV. 9/98)

U.S. GPO: 1998-446-824

PART 1 - ATTORNEY/APPLICANT COPY

Jun.29. 1999 5:25PM

No.2363 P. 21

Docket No.: GR 98 P 1989

## COMBINED DECLARATION AND POWER OF ATTORNE IN ORIGINAL APPLICATION

As a below named inventor, I hereby declare that: my residence, post office address and citizenship are as stated below next to my name; that I verily believe that I am the original, first and sole inventor (if only one name is listed below) or an original, first and joint inventor (if plural names are listed below) of the subject matter which is claimed and for which a patent is sought on the invention entitled:

# DYNAMIC SEMICONDUCTOR MEMORY DEVICE AND METHOD FOR INITIALIZING A DYNAMIC SEMICONDUCTOR MEMORY DEVICE

described and claimed in the specification bearing that title, that I understand the content of the specification, that I do not know and do not believe the same was ever known or used in the United States of America before my or our invention thereof, or patented or described in any printed publication in any country before my or our invention thereof or more than one year prior to this application, that the same was not in public use or on sale in the United States of America more than one year prior to this application, that the invention has not been patented or made the subject of an inventor's certificate issued before the date of this application in any country foreign to the United States of America on an application filled by me or my legal representatives or assigns more than twelve month prior to this application, that I acknowledge my duty to disclose information of which I am aware which is material to the examination of this application under 37 C.F.R. 1.56a, and that no application for patent or inventor's certificate of this invention has been filled earlier than the following in any country foreign to the United States prior to this application by me or my legal representatives or assigns:

German Application No. 198 29 287.2, filed June 30, 1998, the International Priority of which is claimed under 35 U.S.C. §119.

I hereby appoint the following attorney(s) and/or agent(s) to prosecute this application and to transact all business in the Patent and Trademark Office connected therewith:

HERBERT L. LERNER (Reg.No.20,435)

LAURENCE A. GREENBERG (Reg.No.29,308)

WERNER H. STEMER (Reg.No.34,956)

RALPH E. LOCHER (Reg.No.41,947)

Address all correspondence and telephone calls to:

LERNER AND GREENBERG, P.A.

POST OFFICE BOX 2480

HOLLYWOOD, FLORIDA 33022-2480

TEL: (954) 925-1100 FAX: (954) 925-1101

I hereby state that I have reviewed and understand the contents of the above-identified specification, including the claims, as amended by any amendment referred to above.

I hereby declare that all statements made herein of my own knowledge are true and that all statements made on information and belief are believed to be true; and further that these statements were made with the knowledge that willful false statements and the like so made are punishable by fine or imprisonment, or both, under Section 1001 Title 18 of the United States Code and that such willful false statements may jeopardize the validity of the application or any patent issued thereon.

| F | U  | <br>NΑ  | ME   | OF  | SOL | E 11  | Ν\  | /EN          | ١T | O' | F | ł | : |

|---|----|---------|------|-----|-----|-------|-----|--------------|----|----|---|---|---|

| J | O. | <br>IAC | /IA1 | OI. | OUL | . 🗀 🔢 | A s | / <b>二</b> [ | ЧI | v  | ľ |   | 7 |

**GUNNAR KRAUSE**

INVENTOR'S SIGNATURE:

Residence: MUENCHEN, GERMANY

Country of Citizenship:

**GERMANY**

Post Office Address:

SCHLIERSEESTRASSE 8

D-81541 MUENCHEN

**GERMANY**

Docket # <u>GR98 P 1989</u> Applic. # <u>O9 3 H3, H3 /</u>

Applicant: Krause

Lerner and Greenberg, P.A.

Post Office Box 2480

Hollywood, FL 33022-2480

Tel: (954) 925-1100 Fax: (954) 925-1101

Sector

Docket No.

GR 98 P. 15

I hereby certify that this correspondence is being deposited with the United States Postal Service with sufficient postage as first elope addressed to: Assistant Commissioner for Patents, Washington, D.C. 20231.

ED STATES PATENT AND TRADEMARK OFFICE

Applicant

Gunnar Krause

Appl. No.

09/343,431

Filed

June 30, 1999

Title

Dynamic Semiconductor Memory Device And Method For Initializing

A Dynamic Semiconductor Memory Device

Art Unit

2818

### LETTER

Hon. Commissioner of Patents and Trademarks, Washington, D.C. 20231

#### Sir:

The above-mentioned new patent application was filed on June 30, 1999 without a signed oath or declaration, under the provision of 37 C.F.R. 1.53(f).

In accordance with the above-mentioned rule, enclosed herewith is the original signed declaration as required by the Notice To File Missing Parts Of Application dated July 27, 1999.

The undersigned hereby states that the application filed in the Patent and Trademark Office is the application which the inventor(s) executed by signing the declaration. MPEP 601.01(a)(6)

The fee required for the late filing of an oath or declaration in the amount of \$130.00 is also enclosed,

tfully submitted.

**MAYBACK** NO. 40,719

Date: September 27, 1999

Lerner and Greenberg, P.A. Post Office Box 2480

Hollywood, FL 33022-2480

Tel:

(954) 925-1100

Fax:

(954) 925-1101

Docket No.: GR 98 P 1989

### IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

**Applicant**

**GUNNAR KRAUSE**

Filed

Concurrently herewith

Title

DYNAMIC SEMICONDUCTOR MEMORY DEVICE AND

METHOD FOR INITIALIZING A DYNAMIC SEMICONDUCTOR

MEMORY DEVICE

### **INFORMATION DISCLOSURE STATEMENT**

Hon. Commissioner of Patents and Trademarks, Washington, D.C. 20231

Sir:

In accordance with 37 C.F.R. 1.98 copies of the following patents and/or publications are submitted herewith:

U.S. Patent No. 5,307,319 (Kohketzu et al.), dated April 26, 1994.

If no translation of pertinent portions of any foreign language patents or publications mentioned above is included with the aforementioned copies of those applications, patents and/or publications, it is because no existing translation is readily available to the applicant.

Respectfully submitted

LAURENCE A. GREENBERG REG. NO. 29,308

Date: June 30, 1999

Lerner and Greenberg, P.A.

Post Office Box 2480

Hollywood, FL 33022-2480

Tel: (954) 925-1100 Fax: (954) 925-1101

/tg

SHEET 1 OF 1

| FORM PTO-1449 (SUBSTITUTE)  U.S. DEPARTMENT OF COMMERCE PATENT AND TRADEMARK OFFICE |           |                                                   |           | Attorney Docket No.: Appl. No. GR 98 P 1989  Applicant  Applicant |             |              |           |    |  |  |

|-------------------------------------------------------------------------------------|-----------|---------------------------------------------------|-----------|-------------------------------------------------------------------|-------------|--------------|-----------|----|--|--|

| •                                                                                   |           |                                                   |           | GUNNAR KRAUSE                                                     |             |              |           |    |  |  |

|                                                                                     | TEME      | TON DISCLOSURE<br>NT BY APPLICANT<br>CFR 1.98(b)) |           | Filing Date Group Art Unit JUNE 30, 1999                          |             |              |           |    |  |  |

|                                                                                     |           | · · · · · · · · · · · · · · · · · · ·             |           | ·                                                                 |             |              |           |    |  |  |

| EXAMINER<br>INITIALS                                                                |           | PATENT NO.                                        | DATE      | PATENTEE                                                          | CLASS       | SUB<br>CLASS | FILI      |    |  |  |

| <i>ي</i> نو                                                                         | Α         | 5,307,319                                         | 04/94     | Kohketsu et al.                                                   | -           |              |           |    |  |  |

|                                                                                     | В         |                                                   |           |                                                                   |             |              |           |    |  |  |

|                                                                                     | С         |                                                   |           |                                                                   |             |              |           |    |  |  |

|                                                                                     | D         |                                                   |           |                                                                   |             |              |           |    |  |  |

|                                                                                     | Е         |                                                   |           |                                                                   |             |              |           |    |  |  |

|                                                                                     | F         |                                                   |           |                                                                   |             |              |           |    |  |  |

|                                                                                     | G         |                                                   |           |                                                                   |             |              |           |    |  |  |

|                                                                                     | Н         |                                                   |           |                                                                   |             |              |           |    |  |  |

|                                                                                     | 1         |                                                   |           |                                                                   |             |              |           |    |  |  |

|                                                                                     |           | FOREI                                             | GN PATE   | NT DOCUMENT                                                       | •           |              | •         |    |  |  |

|                                                                                     | 1         | DOOL IMENITALO                                    |           | 001111771                                                         |             | SUB          | TRA       |    |  |  |

|                                                                                     | J         | DOCUMENT NO.                                      | DATE      | COUNTRY                                                           | CLASS       | CLASS        | YES       | NO |  |  |

|                                                                                     | K         |                                                   |           |                                                                   |             |              | 1         |    |  |  |

|                                                                                     | L         |                                                   |           |                                                                   |             |              |           |    |  |  |

|                                                                                     | M         |                                                   |           |                                                                   |             |              |           |    |  |  |

|                                                                                     | N         |                                                   |           |                                                                   |             |              |           |    |  |  |

|                                                                                     | 1         |                                                   |           |                                                                   |             |              | <u> </u>  |    |  |  |

| OTH                                                                                 | iER D     | OCUMENTS (Incl                                    | uding Aut | thor, Title, Date, Pe                                             | ertinent Pa | ages, etc    | .)        |    |  |  |