#### US005428803A

## United States Patent [19]

Chen et al.

[11] Patent Number:

5,428,803

[45] Date of Patent:

Jun. 27, 1995

#### [54] METHOD AND APPARATUS FOR A UNIFIED PARALLEL PROCESSING ARCHITECTURE

[75] Inventors: Steve S. Chen, Eau Claire; Douglas R. Beard, Eleva; George A. Spix, Eau

Claire; Edward C. Priest, Eau Claire; John M. Wastlick, Eau Claire; James M. VanDyke, Eau Claire, all of Wis.

[73] Assignee: Cray Research, Inc., Chippewa Falls,

Wis.

[21] Appl. No.: 912,964

[22] Filed: Jul. 10, 1992

[56] References Cited

### U.S. PATENT DOCUMENTS

| 4,130,865 | 12/1978 | Heart et al 395/200       |

|-----------|---------|---------------------------|

| 4,365,292 | 12/1982 | Barnes et al 395/800      |

| 4,400,768 | 8/1983  | Tomlinson                 |

| 4,445,171 | 4/1984  | Neches 395/325            |

| 4,636,942 | 1/1987  | Chen et al 395/725        |

| 4,707,781 | 11/1987 | Sullivan et al 395/425    |

| 4,720,780 | 1/1988  | Dolecek 395/800           |

| 4,745,545 | 5/1988  | Schiffleger 395/325       |

| 4,754,398 | 6/1989  | Pribnow 395/200           |

| 4,827,403 | 5/1989  | Steele, Jr. et al 395/800 |

| 4,834,483 | 5/1989  | Arthurs et al 385/46      |

| 4,873,626 | 10/1989 | Gifford 395/325           |

| 4,891,751 | 1/1990  | Call et al 395/800        |

| 4,901,230 | 2/1990  | Chen et al 395/325        |

| 5,055,999 | 10/1991 | Frank et al 395/425       |

| 5,056,000 | 10/1991 | Chang 395/325             |

| 5,072,371 | 12/1991 | Benner et al 395/200      |

| 5,081,575 | 1/1992  | Hiller et al 395/325      |

| 5,113,523 | 5/1992  | Colley et al 395/800      |

| 5,165,038 | 11/1992 | Beard et al 395/800       |

| 5,179,702 | 1/1993  | Spix et al 395/650        |

| 5,197,130 | 3/1993  | Chen et al 395/325        |

| 5,208,914 | 5/1993  | Wilson et al 395/275      |

|           |         |                           |

#### OTHER PUBLICATIONS

Fast Interrupt Mechanism for a Multiprocessor System, Ser. No.: 07/536,199, filed on Jun. 11, 1990.

(List continued on next page.)

Primary Examiner—Alyssa H. Bowler

Assistant Examiner—G. Donaghue

Attorney, Agent, or Firm—Schwegman, Lundberg &

Woessner

#### [57] ABSTRACT

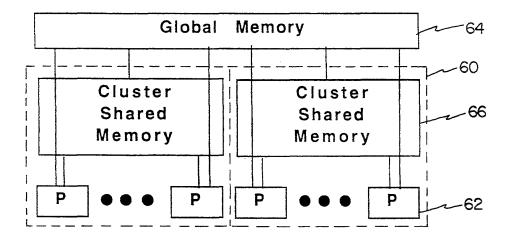

A unified parallel processing architecture connects together an extendible number of clusters of multiple numbers of processors to create a high performance parallel processing computer system. Multiple processors are grouped together into four or more physically separable clusters, each cluster having a common cluster shared memory that is symmetrically accessible by all of the processors in that cluster; however, only some of the clusters are adjacently interconnected. Clusters are adjacently interconnected to form a floating shared memory if certain memory access conditions relating to relative memory latency and relative data locality can create an effective shared memory parallel programming environment. A shared memory model can be used with programs that can be executed in the cluster shared memory of a single cluster, or in the floating shared memory that is defined across an extended shared memory space comprised of the cluster shared memories of any set of adjacently interconnected clusters. A distributed memory model can be used with any programs that are to be executed in the cluster shared memories of any non-adjacently interconnected clusters. The adjacent interconnection of multiple clusters of processors to a create a floating shared memory effectively combines all three type of memory models, pure shared memory, extended shared memory and distributed shared memory, into a unified parallel processing architecture.

### 24 Claims, 12 Drawing Sheets

## OTHER PUBLICATIONS

Almasi, G. and Gottlieb, A., *Highly parallel Computing*, Benjamin Cummings 1989, Chpt. 1, "Overview", pp. 2–29, Chap. 8, Interconnection Networks pp. 278–299, Chapt. 10 MIMD Parallel Architectures pp. 354–475. Gajski, D., Milutinovic, V., Siegel, H., and Furht, B. *Computer Architecture*, The Computer Society of the IEEE, (1987), Chpt. 2, "Topics in Parallel Processing and Multiprocessing", pp. 81–171.

Hennesy, J. and Patterson, D., Computer Architecture: *A Quantative Approach*, Morgan Kaufman (1990), Chap. 10, "Future Directions", pp. 570–592.

Hwang, K. and DeGroot, D., Parallel Processing for Supercomputers and Artificial Intelligence, McGraw Hill Publ., (1989) Chpt. 2, pp. 31-67.

Kain, R., Computer Architecture, Prentice Hall, (1989), vol. 1, Chpt. 3, "Shared Resource Synchronization", pp. 178-250.

ETA 10 System Overview: EOS, Tech. Note, Publ. 1006, ETA Systems, Sep. 30, 1988.

Clementi, E., Logan, D., Saarninen, J., "ICAP/3090: Parallel Processing For Large Scale Scientific and Engineering Problems", *IBM Systems Journal*, vol. 27, No. 4 (1988) pp. 475–509.

4 (1988) pp. 475–509.

Pfister, G., "The IBM Research Parallel Processor Prototype (RP3): Introduction and Architecture", Int'l Conf. on Parallel Processing, Aug. 1985, pp. 764–771.

Murakami, K., Akira, F., Sueyoshi, T. and Tomita, S., "An Overview of the Kyushi University Reconfigurable Parallel Processor", Aug. 1988, pp. 130–137.

Kuck, D., Davidson, E., Lawrie, D. and Sameh, A., "Parallel Supercomputing Today and the Cedar Approach", Science, vol. 231, Feb. 1986, pp. 967–974.

proach", Science, vol. 231, Feb. 1986, pp. 967-974. Goodman, J. and Woest, P., "The Wisconsin Multicube: A New Large Scale Cache-Coherent Multiprocessor", Proc. of the 1988 Int'l Conf. on Parallel Processing, IEEE, Feb. 1988, pp. 422-431.

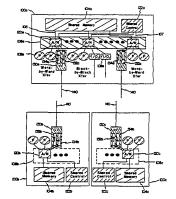

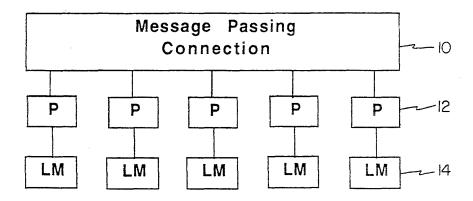

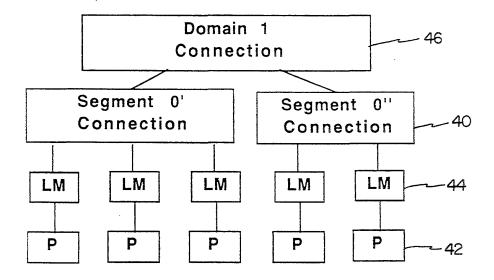

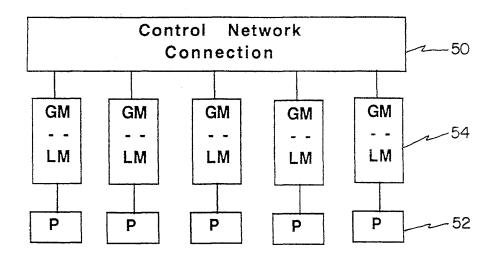

# PRIOR ART DISTRIBUTED MEMORY MODEL

Fig. 1a

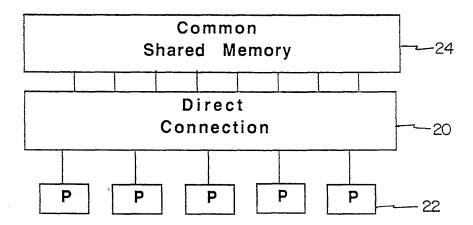

PRIOR ART SHARED MEMORY MODEL

Fig. 1b

June 27, 1995

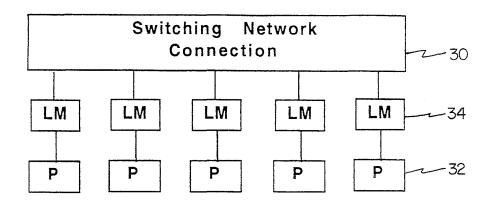

# PRIOR ART **EXTENDED SHARED MEMORY** SWITCHING NETWORK MODEL

Fig. 2a

PRIOR ART **EXTENDED SHARED MEMORY** HEIRARCHICAL RING MODEL

Fig. 2b

# PRIOR ART **EXTENDED SHARED MEMORY** RECONFIGURABLE MODEL

Fig. 2c

PRIOR ART **EXTENDED SHARED MEMORY** CLUSTER/GLOBAL MEMORY INTERCONNECT

Fig. 2d

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

## **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.