# Passive Cancellation of Common-Mode Electromagnetic Interference in Switching Power Converters

# **Daniel Cochrane**

Thesis Submitted to the Faculty of the Virginia Polytechnic

Institute and State University in Partial Fulfillment of the

Requirements for the Degree of

Master of Science

in

**Electrical Engineering**

Dan Y. Chen

Dusan Boroyevic

Jason S. Lai

August 10, 2001 Blacksburg, VA

Keywords: EMI, Noise Cancellation, Noise Reduction Switching

Power Supplies

# **Abstract**

It is well known that common-mode (CM) conducted electromagnetic interference (EMI) is caused by the common-mode current flowing through the parasitic capacitance of transistors, diodes, and transformers to ground in the power circuit. Because of the potential for interference with other systems as well as governmental regulations, it is necessary to attenuate this noise. Ordinarily this must be accomplished by using a magnetic choke on the input power lines, which can result in large penalties to the overall size, weight, and cost of the completed system.

In order to lessen the requirement for this magnetic choke, there has been in recent years a desire to introduce noise cancellation techniques to the area of EMI. This text introduces a method of canceling the common-mode EMI by using a compensating transformer winding and a capacitor. Compared with active cancellation techniques, it is much simpler and requires no additional transistors and gate-drive circuitry since it merely adds a small copper winding and a small capacitor. By using this technique the size of the EMI filter can be reduced, especially for applications requiring high currents.

In this thesis a survey of CM noise reduction techniques is presented, encompassing conventional and active cancellation techniques. The new method for passive noise cancellation is presented, which is then applied to families of isolated DC/DC converters, non-isolated DC/DC converters, and DC/AC inverters and motor drives. The method, results, and ramifications of this technique are presented in order of appearance.

# Acknowledgement

I would like to express my gratitude to my advisor Dr. Dan Y. Chen, for his unfailing help and support during my time at Virginia Tech. It would have been quite impossible for me to complete this thesis without his extensive knowledge and advice.

I would also like to thank my committee members, Dr. Dusan Boroyevic and Dr. Jason Lai, for their support of my research. In addition, I would like to thank the faculty, staff and students at the Center for Power Electronics at Virginia Tech for their friendship and technical help, with particular thanks to the following: Carl Tinsley, Jeremy Ferrel, Robert Gannett, Erik Hertz, Cory Papenfuss, and Troy Nergard.

Finally, I must thank my parents, Alan and Vivian Cochrane, for their love and support in my various endeavors throughout the years.

This work was partially funded by the Office of Naval Research under contract number N000140010610, and made use of ERC Shared Facilities supported by the National Science Foundation under Award Number EEC-9731677

# Table of Contents

| Chapter 1. A Brief Overview of EMI                                        | 1  |

|---------------------------------------------------------------------------|----|

| 1.1. What is EMI?                                                         | 1  |

| 1.1.1. The Basics                                                         | 1  |

| 1.1.2. Standards                                                          | 3  |

| 1.1.3. Testing                                                            | 6  |

| 1.2. Sources and Traps                                                    | 9  |

| 1.2.1. Active Components                                                  | 9  |

| 1.2.2. Passive Components                                                 | 10 |

| 1.2.3. Layout                                                             | 11 |

| Chapter 2. Existing EMI Reduction Techniques                              | 13 |

| 2.1. Conventional Methods                                                 | 13 |

| 2.2. Active Cancellation                                                  | 14 |

| 2.3. Passive Cancellation                                                 | 19 |

| 2.4. Remarks                                                              | 20 |

| Chapter 3. Proposed Passive Cancellation in Isolated DC/DC Converters     | 21 |

| 3.1. Introduction to the Proposed Technique                               | 21 |

| 3.2. Buck Derived Converters                                              | 23 |

| 3.2.1. Half-Bridge DC/DC                                                  | 23 |

| 3.2.1.1. General Description                                              | 23 |

| 3.2.1.2. Construction of Prototype                                        | 24 |

| 3.2.1.3. Experimental Test Results                                        | 25 |

| 3.2.2. Single-Switch Forward Converter                                    | 33 |

| 3.2.2.1. General Description                                              | 33 |

| 3.2.2.2. Experimental Test Results                                        | 33 |

| 3.3. Buck-Boost Derived Converters                                        | 36 |

| 3.3.1. Flyback Converter                                                  | 36 |

| 3.4. Remarks                                                              | 41 |

| Chapter 4. Proposed Passive Cancellation in Non-Isolated DC/DC Converters | 42 |

| 4.1. Buck Converters                                                      | 42 |

| 4.1.1. Description of Technique and Model Results                         | 42 |

| 4.1.2. Limitations of the Technique                                       | 49 |

| 4.2. Boost Converters                                                     | 50 |

| 4.3. Buck-Boost Converters                                                        | 52  |

|-----------------------------------------------------------------------------------|-----|

| 4.4. Remarks                                                                      | 58  |

| Chapter 5. Proposed Passive Cancellation in DC/AC Inverters and Motor Drives      | 59  |

| 5.1. Method 1: Modifying the Output Filter                                        | 59  |

| 5.1.1. Description of Technique and Model Results                                 | 59  |

| 5.1.2. Limitations Due to Load Interaction                                        | 62  |

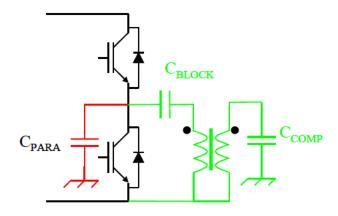

| 5.2. Method 2: The Phase Leg Cancellation Circuit                                 | 69  |

| 5.2.1. General Description                                                        | 69  |

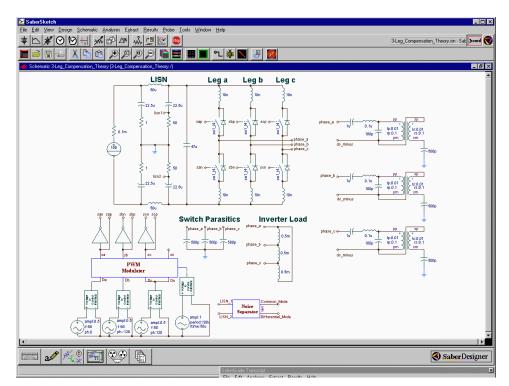

| 5.2.2. Analysis Using Saber                                                       | 70  |

| 5.2.3. Construction of the Experimental Cancellators                              | 75  |

| 5.2.4. Experimental Test Results                                                  | 81  |

| 5.3. Remarks                                                                      | 88  |

| Chapter 6. Conclusions and Future Work                                            | 90  |

| 6.1. Summary and Overview                                                         | 90  |

| 6.2. Future Research Topics                                                       | 92  |

| Bibliography                                                                      | 94  |

| Vita                                                                              | 96  |

|                                                                                   |     |

| List of Figures                                                                   |     |

| Figure 1: Examples of Conducted and Radiated EMI Propagation                      | 2   |

| Figure 2: Flow Chart of Source to Victim Coupling Paths                           | 2   |

| Figure 3: Comparison of Conducted Emissions Limits for FCC Part 15, Subpart J and | l   |

| CISPR, Publication 22                                                             | 5   |

| Figure 4: MIL-STD-461E Conducted EMI Limits, CE102                                | 5   |

| Figure 5: MIL-STD-461E Conducted Emissions Test Setup                             | 6   |

| Figure 6: MIL-STD-461E, CE102 Measurement Setup                                   | 7   |

| Figure 7: Typical and MIL-STD-461E LISN                                           | 8   |

| Figure 8: LISN Impedance Comparison                                               | 8   |

| Figure 9: Packaging Parasitics for Active Device                                  | 10  |

| Figure 10: Transformer with Lumped Reactive Parasitics                            | 11  |

| Figure 11: Typical EMI Line Filter Topology Incorporating CM and DM Components    | s14 |

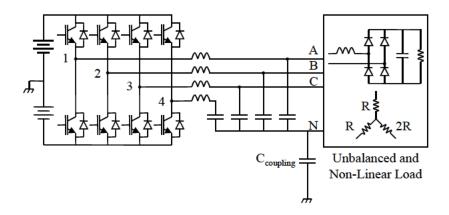

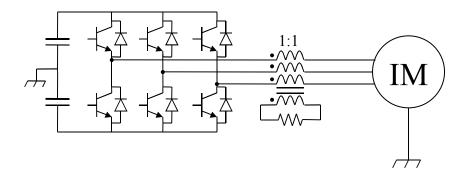

| Figure 12: Typical Three-Phase Voltage Source Inverter                            | 15  |

| Figure 13: 3-Phase 4-Leg VSI with Active CM Filter                                | 16  |

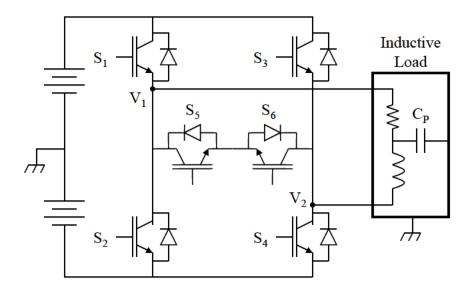

| Figure 14: Single-Phase Inverter with Active CM Voltage Cancellation              | 17  |

| Figure 15: Balanced Buck Converter Topology                                            | 18 |

|----------------------------------------------------------------------------------------|----|

| Figure 16: Auxiliary Active Circuit for CM Voltage Cancellation                        | 18 |

| Figure 17: CM Transformer for Damping of Noise Currents                                | 20 |

| Figure 18: Proposed Method of CM Noise Cancellation                                    | 21 |

| Figure 19: Half-Bridge Isolated DC/DC Topology Incorporating Passive Cancellation      | 23 |

| Figure 20: Half-Bridge Prototype                                                       | 24 |

| Figure 21: Winding Structure of Half-Bridge Transformer with Compensation Winding      | 25 |

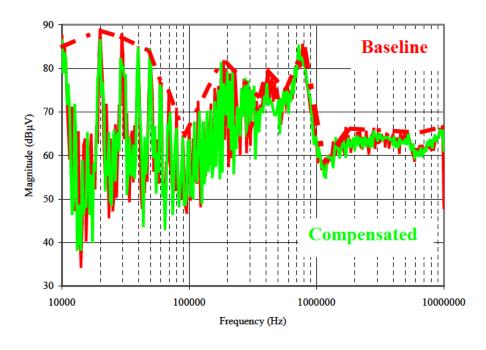

| Figure 22: Test-Setup inside EMI Chamber for Half-Bridge Experiment                    | 25 |

| Figure 23: Test-Setup outside EMI Chamber for Half-Bridge Experiment                   | 26 |

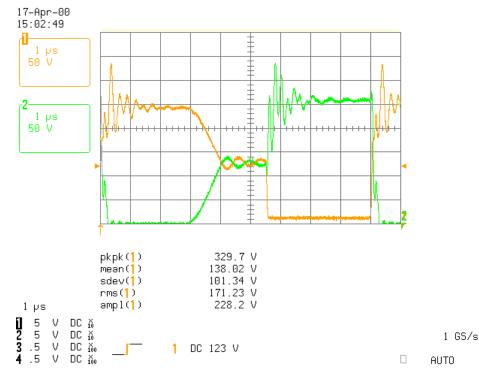

| Figure 24: Half-Bridge CM Voltage Waveforms                                            | 27 |

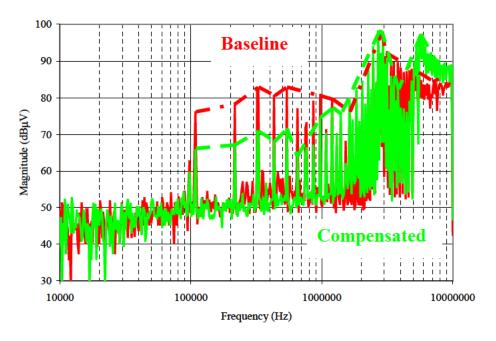

| Figure 25: Half-Bridge CM Baseline and 56pF Compensation (Poor Transformer)            | 28 |

| Figure 26: Half-Bridge CM Comparison with 750pF of Added $C_{PARA}$ (Poor Transformer) | 29 |

| Figure 27: Half Bridge Results with $C_{PARA} = 56pF$ (Good Transformer)               | 29 |

| Figure 28: Half Bridge Results with $C_{PARA} = 112pF$ (Good Transformer)              | 30 |

| Figure 29: Final Half-Bridge CM Results                                                | 31 |

| Figure 30: Final Half-Bridge DM Results                                                | 32 |

| Figure 31: Off-Line Forward Converter Incorporating Passive CM Cancellation            | 33 |

| Figure 32: Forward Converter FET and Diode Waveforms                                   | 34 |

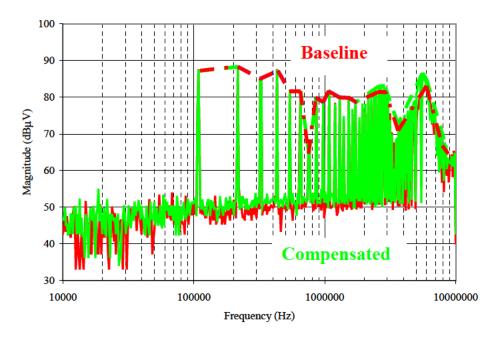

| Figure 33: Experimental CM Noise Comparison for Forward Converter                      | 35 |

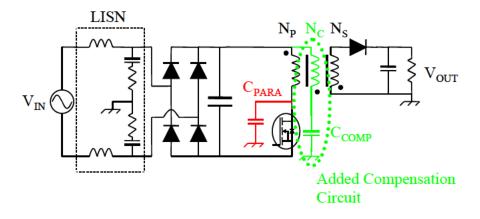

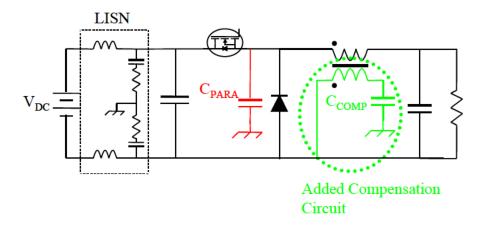

| Figure 34: Isolated Flyback Topology Incorporating Passive CM Cancellation             | 36 |

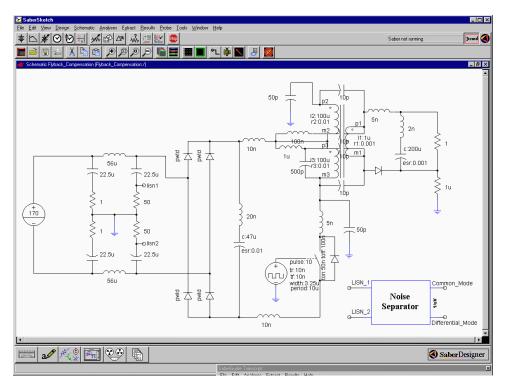

| Figure 35: Saber Model for Noise Compensated Flyback Converter                         | 38 |

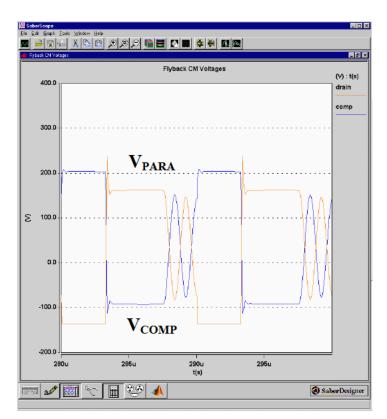

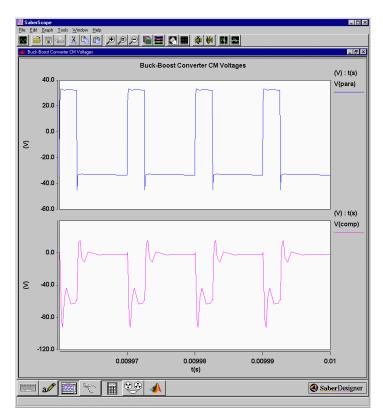

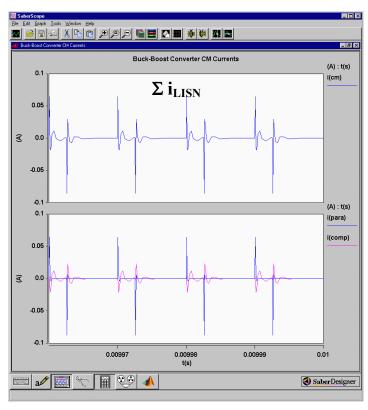

| Figure 36: Simulated Parasitic and Compensating Voltages for Flyback Converter         | 39 |

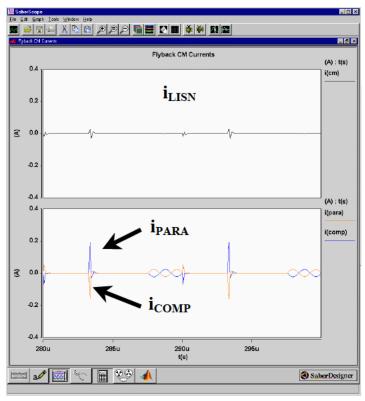

| Figure 37: Simulated Parasitic and Compensating Currents in Flyback Converter          | 39 |

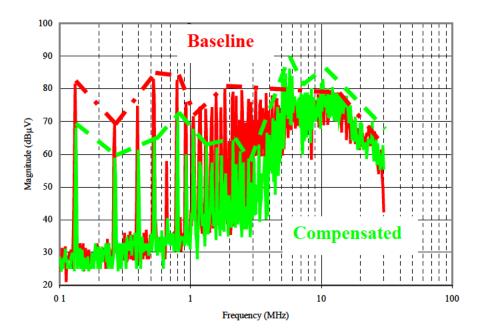

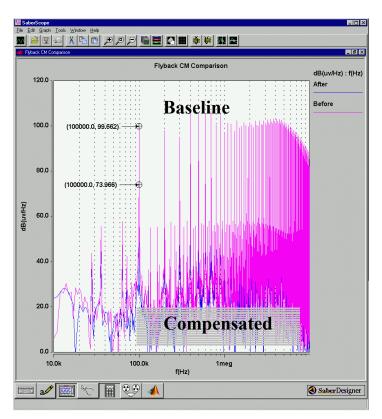

| Figure 38: Simulated CM Spectrum Comparison for Flyback Converter                      | 40 |

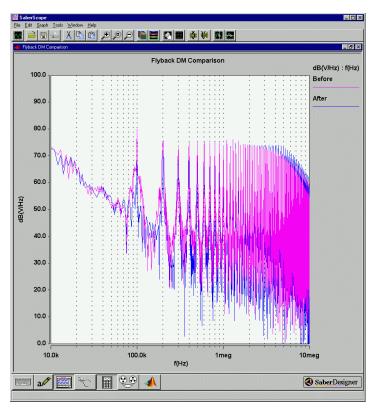

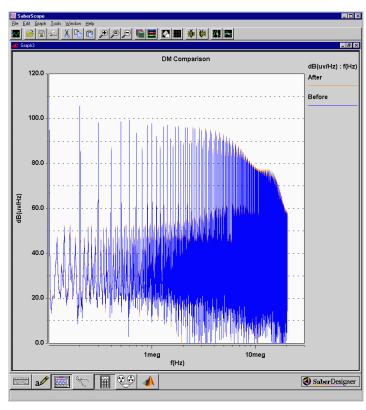

| Figure 39: Simulated DM Spectrum Comparison for Flyback Converter (Unchanged)          | 40 |

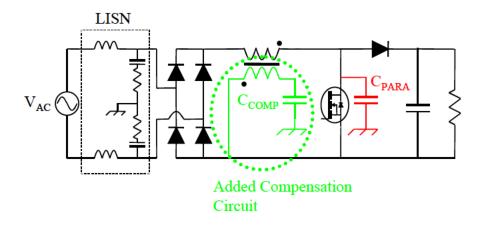

| Figure 40: Buck Converter Incorporating Passive CM Noise Cancellation                  | 42 |

| Figure 41: Saber Model for CM Noise Compensated Buck Converter                         | 44 |

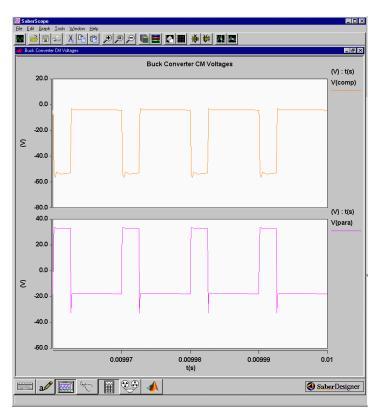

| Figure 42: Buck Converter CM Voltages                                                  | 45 |

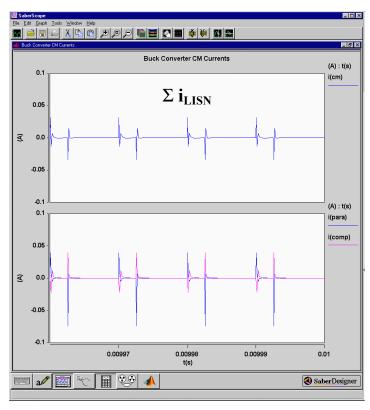

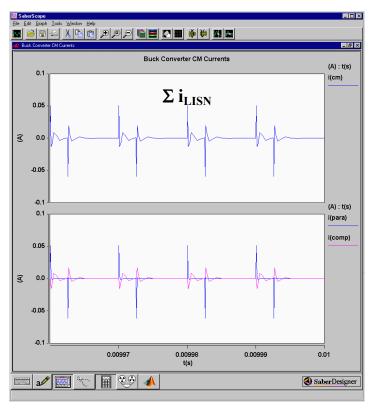

| Figure 43: Buck Converter CM Currents.                                                 | 45 |

| Figure 44: Buck Converter CM Noise Spectrum Comparison                                 | 46 |

| Figure 45: Buck Converter DM Noise Spectrum Comparison                                 | 46 |

| Figure 46: Buck Converter CM Voltages, High Input Capacitor ESL                        | 47 |

| Figure 47: Buck Converter CM Currents, High Input Capacitor ESL                        | 47 |

| Figure 48: Buck Converter CM Voltages, High Leakage Inductance                         | 48 |

| Figure 49: Buck Converter CM Currents, High Leakage Inductance                                  | 48 |

|-------------------------------------------------------------------------------------------------|----|

| Figure 50: Boost Converter Incorporating Passive CM Noise Cancellation                          | 50 |

| Figure 51: Boost Converter Parasitic and Compensating Voltage Waveforms                         | 51 |

| Figure 52: Boost Converter CM Noise Spectrum Comparison                                         | 52 |

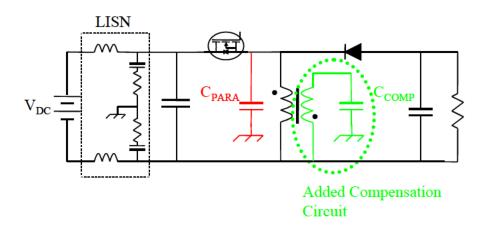

| Figure 53: Buck-Boost Converter Incorporating Passive CM Noise Cancellation                     | 52 |

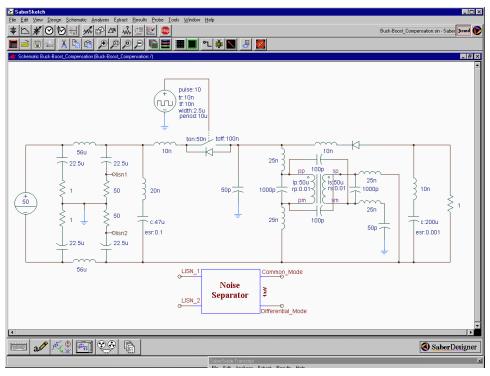

| Figure 54: Saber Model for CM Noise Compensated Buck-Boost Converter                            | 53 |

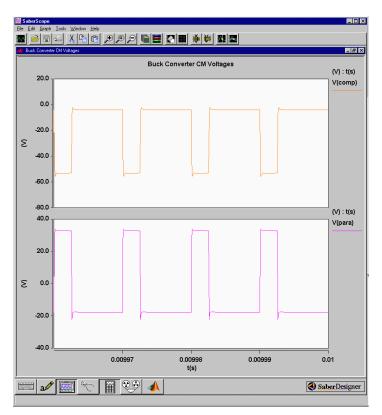

| Figure 55: Buck-Boost Converter CM Voltages                                                     | 54 |

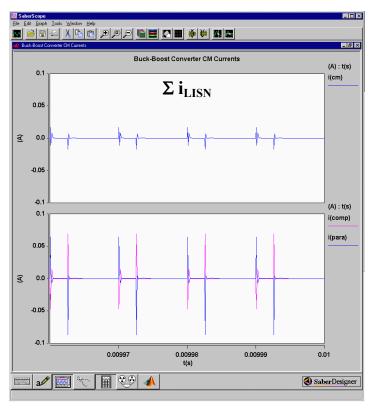

| Figure 56: Buck-Boost Converter CM Currents                                                     | 54 |

| Figure 57: Buck-Boost Converter CM Noise Spectrum Comparison                                    | 55 |

| Figure 58: Buck-Boost Converter DM Noise Spectrum Comparison                                    | 55 |

| Figure 59: Buck-Boost Converter CM Voltages, High Input Capacitor ESL                           | 56 |

| Figure 60: Buck-Boost Converter CM Currents, High Input Capacitor ESL                           | 56 |

| Figure 61: Buck-Boost Converter CM Voltages, High Leakage Inductance                            | 57 |

| Figure 62: Buck-Boost Converter CM Currents, High Leakage Inductance                            | 57 |

| Figure 63: Inverter CM Reduction by Modified Output Filter                                      | 59 |

| Figure 64: Saber Model for Half-Bridge PWM Inverter Output Filter Test                          | 60 |

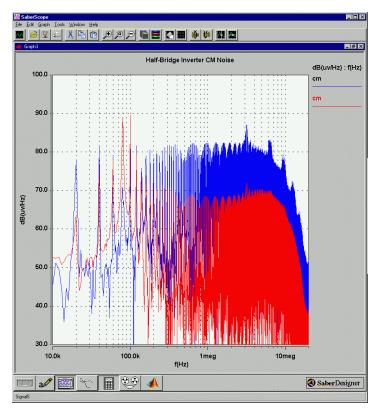

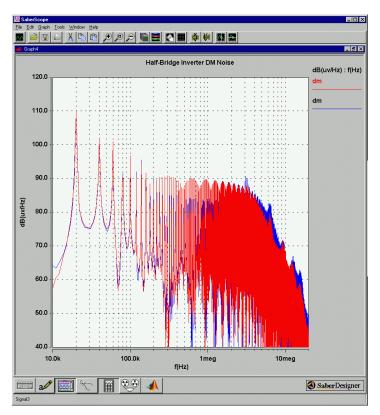

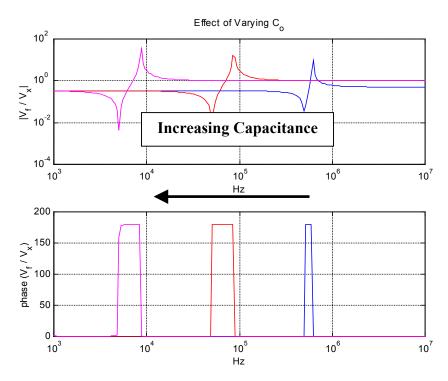

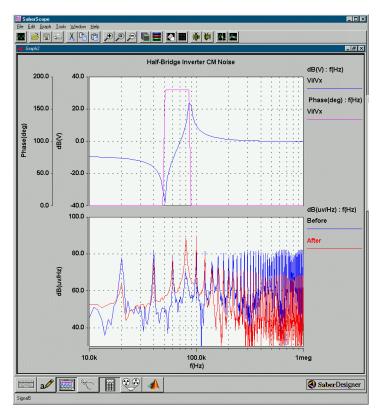

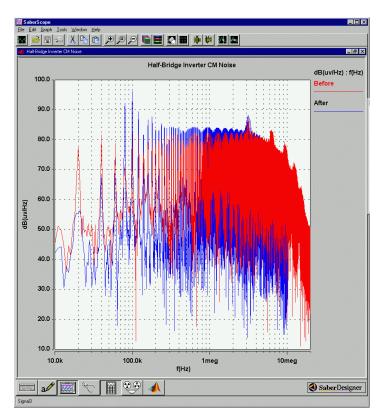

| Figure 65: Half-Bridge Inverter CM Noise Spectrum                                               | 61 |

| Figure 66: Half-Bridge Inverter DM Noise Spectrum                                               | 62 |

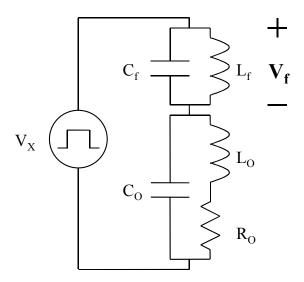

| Figure 67: Equivalent Circuit of Half-Bridge Inverter Filter and Load                           | 63 |

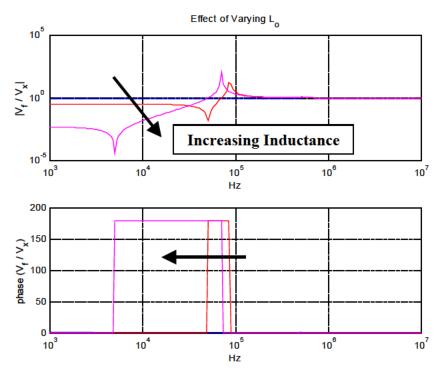

| Figure 68: Bridge Transfer Function for $L_o = 1\mu H$ 10mH                                     | 64 |

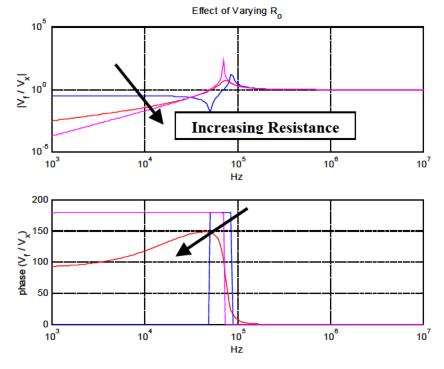

| Figure 69: Bridge Transfer Function for $R_o = 0.01$ —100k                                      | 64 |

| Figure 70: Bridge Transfer Function for $C_0 = 1 \text{nF} - 10 \mu \text{F}$                   | 65 |

| Figure 71: Half-Bridge Inverter CM Noise Spectrum with Bridge Transfer Function                 | 66 |

| Figure 72: Half-Bridge Inverter CM Comparison with Increases C <sub>COMP</sub>                  | 67 |

| Figure 73: Half-Bridge Inverter CM Voltages, Leakage = 0.1%                                     | 68 |

| Figure 74: Half-Bridge Inverter CM Currents, Leakage = 10%                                      | 68 |

| Figure 75: Generic Phase-Leg Cancellation Circuit                                               | 69 |

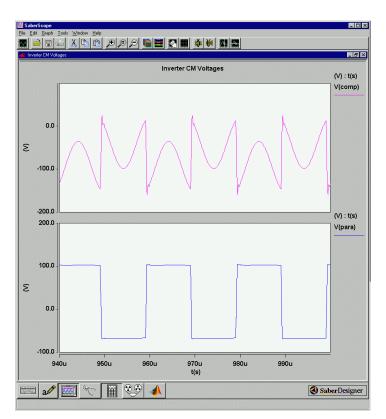

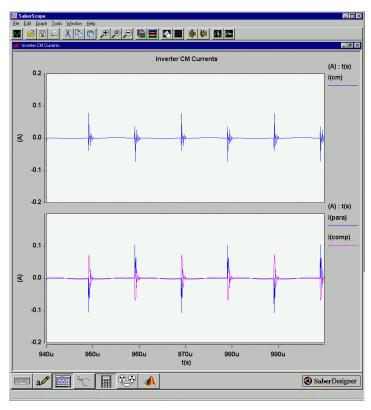

| Figure 76: 3-Φ Inverter Saber Model with CM Cancellators                                        | 71 |

| Figure 77: Inverter Parasitic and Compensating Waveforms with Non-Ideal Cancellator,            |    |

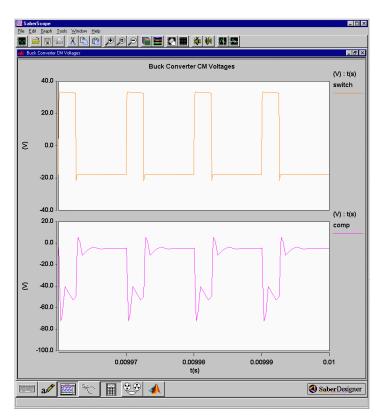

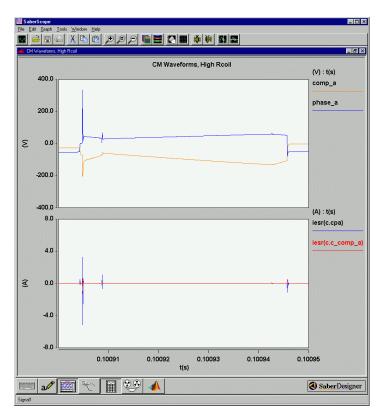

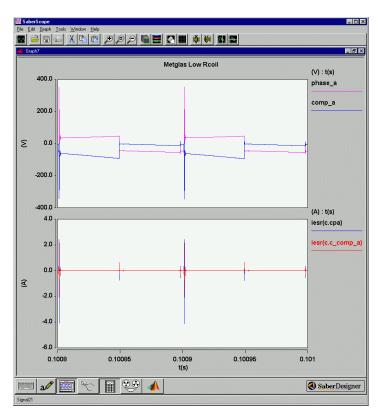

| High R <sub>COIL</sub>                                                                          | 71 |

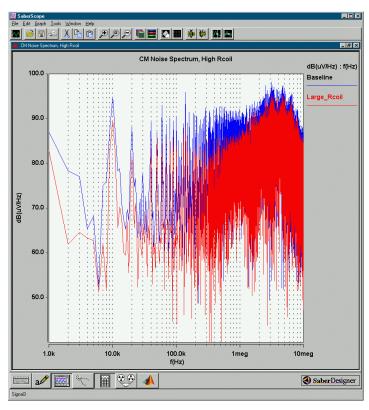

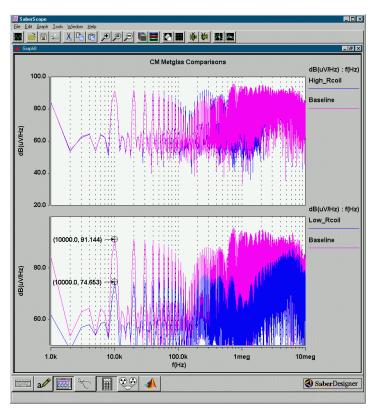

| Figure 78: 3-Φ Inverter CM Noise Spectrum Comparison with Cancellator                           | 72 |

| Figure 79: 3-Φ Inverter DM Noise Spectrum Comparison with Cancellator                           | 72 |

| Figure 80: 3-Φ Inverter CM Noise Spectrum Comparison with Cancellator, Small C <sub>BLOCK</sub> | 73 |

| Figure 81: 3-Φ Inverter CM Noise Spectrum Comparison with Cancellator, Large R <sub>COU</sub>   |    |

| Figure 82: Inverter Parasitic and Compensating Waveforms with Cancellator, Large |    |

|----------------------------------------------------------------------------------|----|

| R <sub>COIL</sub>                                                                | 74 |

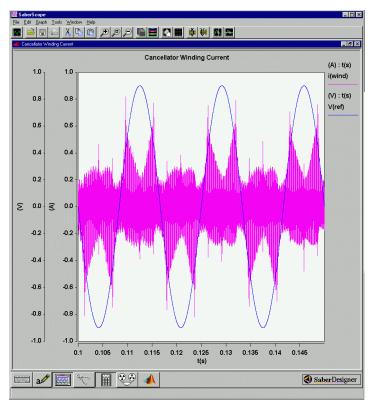

| Figure 83: Cancellator Sees 60 Hz Inverter Output Frequency                      | 74 |

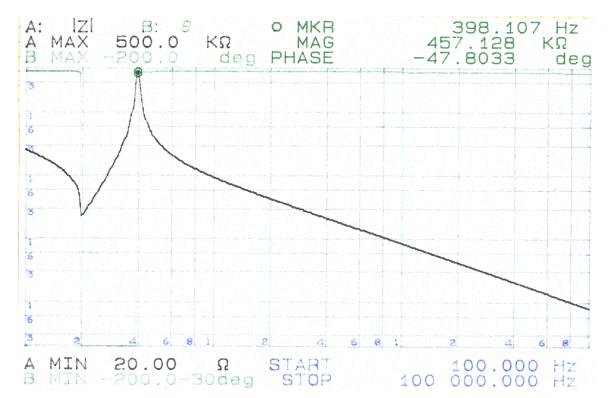

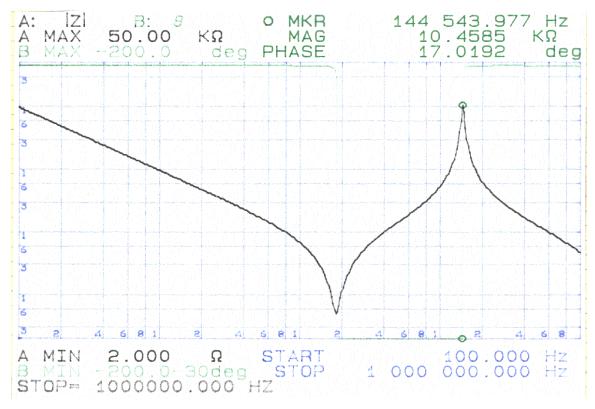

| Figure 84: Phase-Leg Cancellation Circuit (Metglas)                              | 77 |

| Figure 85: Phase-Leg Cancellation Circuit (Air / Metglas Core Comparison)        | 77 |

| Figure 86: Primary Side Impedance of Metglas Cancellator                         | 78 |

| Figure 87: Primary Side Impedance of Air Core Cancellator                        | 78 |

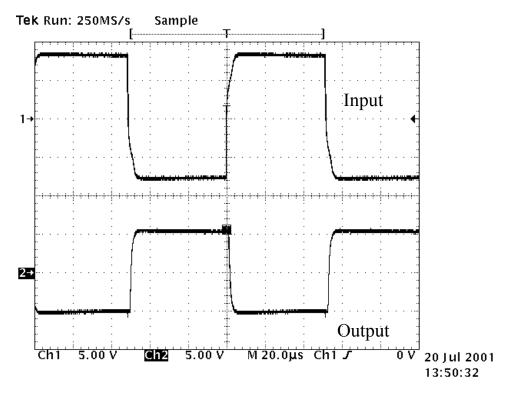

| Figure 88: Pulse Response of Metglas Core Phase-Leg Cancellator at 10 kHz        | 79 |

| Figure 89: Pulse Response of Air Core Phase-Leg Cancellator at 10 kHz            | 79 |

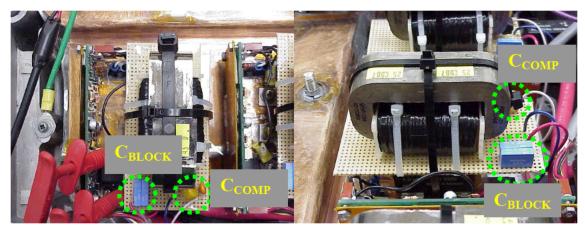

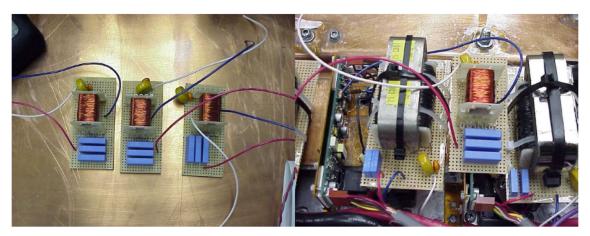

| Figure 90: Installation of Phase-Leg Cancellation Circuit                        | 80 |

| Figure 91: Inverter Test Setup (Right Side)                                      | 81 |

| Figure 92: Inverter Test Setup Close-up                                          | 81 |

| Figure 93: Inverter Test Setup (Left Side)                                       | 82 |

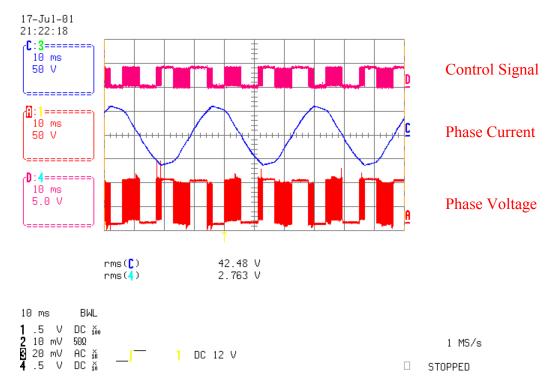

| Figure 94: Inverter Power Waveforms                                              | 83 |

| Figure 95: Inverter CM Noise Spectrum (Metglas) is Unchanged                     | 84 |

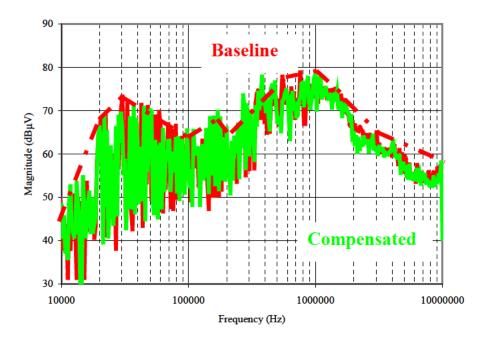

| Figure 96: Inverter DM Noise Spectrum (Metglas) is Unchanged                     | 84 |

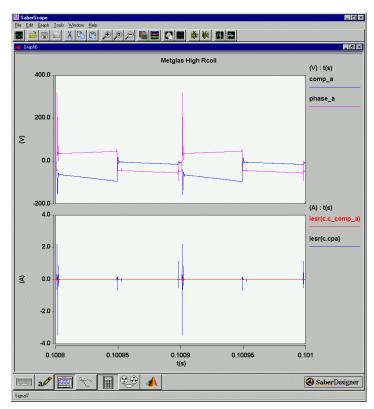

| Figure 97: Simulated Metglas Cancellator, High R <sub>COIL</sub>                 | 85 |

| Figure 98: Simulated Metglas Cancellator, High R <sub>COIL</sub>                 | 86 |

| Figure 99: Simulated Metglas CM Noise Spectrum Comparisons                       | 86 |

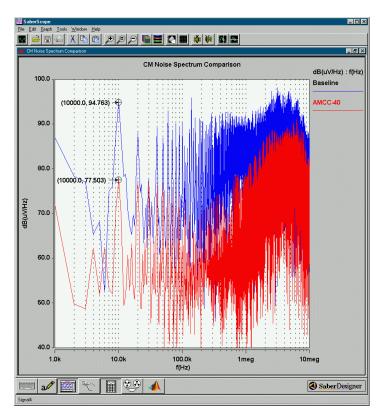

| Figure 100: Inverter CM Results with AMCC-40 Core and #27 Wire                   | 87 |

| Figure 101: Inverter CM Noise Spectrum (Air Core)                                | 88 |

| Figure 102: Inverter DM Noise Spectrum (Air Core) is Unchanged                   | 88 |

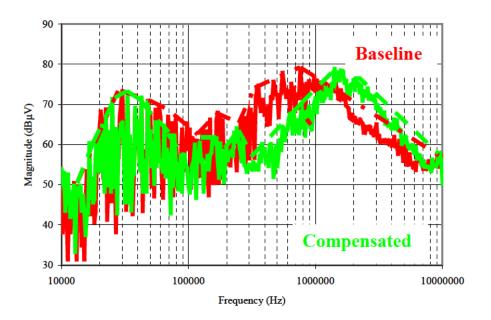

| Figure 103: Noise Spectrum Attenuation Example                                   | 91 |

| Figure 104: CM Filter for Example                                                | 91 |

| List of Tables                                                                   |    |

| Table 1: List of Common EMI Regulations                                          | 3  |

| Table 2: Design Details of Half-Bridge Prototype                                 | 24 |

| Table 3: Test Settings for HP4195A in Half-Bridge Experiments                    | 26 |

| Table 4: Comparison for Selected Switching Harmonics (Heat Sink Ungrounded)      | 30 |

| Table 5: Final Half-Bridge Switching Harmonic Comparison                         | 32 |

| Table 6: Design Details of Forward Converter Prototype                           | 34 |

| Table 7: Test Settings for HP4195A in Forward Converter Experiments              | 35 |

| Table 8: Metglas Transformer Design Details                                      | 76 |

| Table 9: AMCC-25 Core Information                                                | 76 |

| Table 10: Transformer Parameter Comparison.                 | . 80 |

|-------------------------------------------------------------|------|

| Table 11: Test Settings for HP4195A in Inverter Experiments | . 82 |

# Chapter 1. A Brief Overview of EMI

Before we look at the main topic of this thesis text, it is necessary to present some basic background information. This chapter briefly summarizes some of the most important topics of the field of EMI as they relate to this particular subject. Starting with the fundamental definitions, we will then look at some of the regulations pertaining to this subject before looking at the causes of noise.

#### 1.1. What is **EMI**?

#### 1.1.1. The Basics

What is EMI? Simply put, EMI, or electromagnetic interference, is undesirable noise that interferes with the normal operation of electronics. Michel Mardiguian puts it the following:

"Generally, electromagnetic interference occurs when an electrical disturbance from either a natural phenomenon (e.g., electrostatic discharge [ESD], lightning, and so on) or an electrical or electronic equipment causes an undesired response in another equipment."

Specifically, we can categorize EMI into four different groups:

- 1. Conducted emissions

- 2. Radiated emissions

- 3. Conducted susceptibility

- 4. Radiated susceptibility

The first two groups deal with the undesirable emanations from a particular piece of equipment, and the second two groups deal with a piece of equipment's ability to reject interference from external sources of noise. In this thesis I will be focusing on the first type of EMI: conducted emissions.

In practice this interference can have various degrees of manifestation ranging from nuisance, such as interference with a portable radio when walking under a power line, to catastrophic, such

\_

<sup>&</sup>lt;sup>1</sup> Mardiguian, pg 1

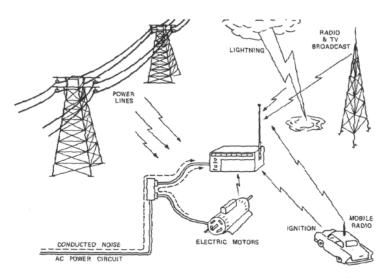

as an electronic communications device interfering with a aircraft navigation equipment<sup>2</sup>. Ott gives a diagram shown in Figure 1 that illustrates some of the myriad ways that EMI can be propagated.

Figure 1: Examples of Conducted and Radiated EMI Propagation<sup>3</sup>

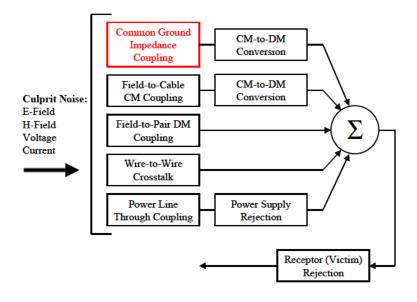

Figure 2: Flow Chart of Source to Victim Coupling Paths<sup>4</sup>

<sup>&</sup>lt;sup>2</sup> CAA News, referenced in bibliography, specifies several instances of cell phones triggering various system malfunctions in commercial aircraft.

<sup>&</sup>lt;sup>3</sup> Ott, pg. 3

Figure 2 is a simple flow chart showing how the noise sources are coupled into a noise victim; this can be the system itself or some other nearby susceptible equipment. The particular method of coupling that this thesis will focus on eliminating is the highlighted box "Common Ground Impedance Coupling".

As electronic equipment has increased in popularity we have been seeing a great deal of interest in incorporating switch-mode power converters to reduce the size, weight, and cost of said equipment. In order to increase the performance and/or the efficiency of these power converters the switching frequency has been increasing with concomitant increases in the levels of EMI. Techniques of reducing this EMI by cheap and simple means should therefore be of great interest to persons involved in the design of switch-mode power conversion equipment.

#### 1.1.2. Standards

Because of the difference in motivation between protecting the designer's product against susceptibility to other products emissions and protecting other products from emissions from the designer's product, various government bodies have instituted standards which set specific limits on the quantities of radiated and conducted noise emissions in order for a product to be sold within that country. In the United States these regulatory bodies are the Federal Communications Commission (FCC) and the Department of Defense (DOD). In Europe all standards are set by the European Economic Consortium (EEC). There is also an international body called the International Special Commission (IEC), which has no regulatory authority but which sets standards that can then be adopted by individual nations in order to facilitate international trade. Table 1 summarizes these various standards.

**Table 1: List of Common EMI Regulations**

| Standard               | Description                                                        |  |

|------------------------|--------------------------------------------------------------------|--|

| FCC Part 15, Subpart J | FCC General standard for digital electronics                       |  |

| EN55011                | EU standard for industrial, scientific, and medical equipment      |  |

| EN55013                | EU standard for broadcast receivers                                |  |

| EN55014                | EU standard for motor and thermal appliances, and electrical tools |  |

| EN55015                | EU standard for electrical lighting                                |  |

| EN55022                | EU standard for information technology (IT) equipment              |  |

| CISPR Publication 22   | CISPR standards for digital electronics                            |  |

| MIL-STD-461E           | DOD standards for electrical equipment                             |  |

<sup>&</sup>lt;sup>4</sup> Mardiguian, pg. 16

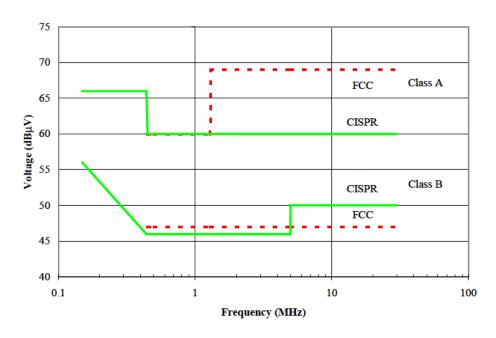

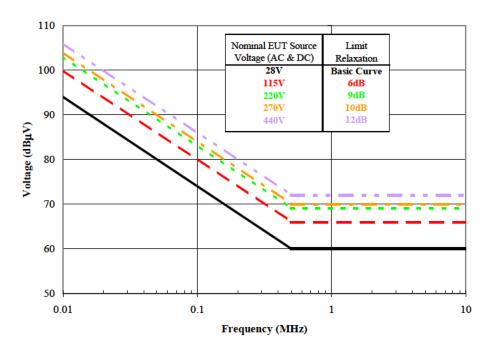

While all of the aforementioned standards include both conducted and radiated specifications as well as regulations concerning electromagnetic compatibility, only the conducted noise interference specifications will be discussed in this thesis in the interest of reducing extraneous noise. Figure 3 and Figure 4 (The EN standards follow CISPR specifications) compare the limits of each of these standards. The non-military specifications differentiate between types of electronic equipment; a Class A device is intended for use in commercial or industrial environments while a Class B device is intended for consumer applications<sup>5</sup>. Typically no military equipment is intended for use in consumer applications, so the military specification differentiates between equipment based on input voltage and adds special rules if the equipment is to be used in an electromagnetically sensitive environment such as that in a submarine or spacecraft.

The most important difference between all of these specifications is the frequency band that they cover. The CISPR and the EU regulations specify a bandwidth of 150 kHz-30 MHz, while the FCC is more lax in calling for a starting frequency of 450 kHz. MIL-STD-461E is much stricter on the low frequency side (10 kHz), although the high side of the specification only goes to 10 MHz. What this translates into is that the corner frequency of the input EMI filter will have to be lowered for the stricter standards, which can mean a considerable increase in the size and cost of the compliant system. Naturally this also increases the motivation for eliminating the EMI by techniques other than filtering.

-

<sup>&</sup>lt;sup>5</sup> Ott, pg 8

Figure 3: Comparison of Conducted Emissions Limits for FCC Part 15, Subpart J and CISPR, Publication 22<sup>6</sup>

Figure 4: MIL-STD-461E Conducted EMI Limits, CE1027

<sup>7</sup> MIL-STD-461E, pg. 38

<sup>&</sup>lt;sup>6</sup> Ibid., pg. 15

# 1.1.3. Testing

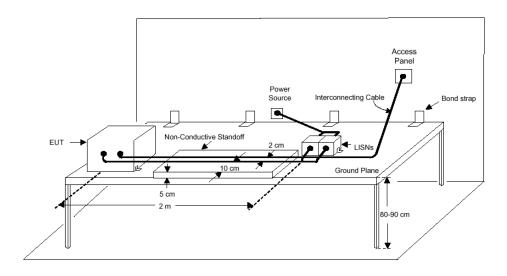

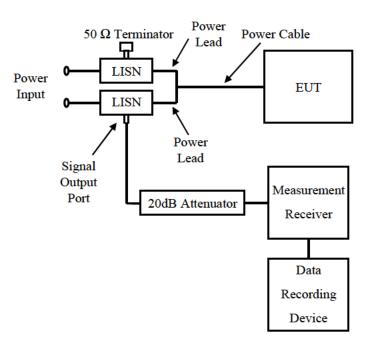

Each regulatory body has a specific standard of performing EMI tests. Figure 5 shows the conducted emission test setup for MIL-STD-461E by means of example. The equipment under test (EUT) is placed on a copper ground plane that is electrically isolated from the surrounding area. Power leads to the EUT have a Line Impedance Stabilization Network (LISN) placed in series to provide a common power line impedance over the frequency of interest. The LISN also serves as the measurement point for the conducted mode testing, as shown in the MIL-STD-461E, CE102 measurement setup in Figure 6.

Figure 5: MIL-STD-461E Conducted Emissions Test Setup<sup>8</sup>

-

<sup>&</sup>lt;sup>8</sup> MIL-STD-461E, pg. 19

Figure 6: MIL-STD-461E, CE102 Measurement Setup9

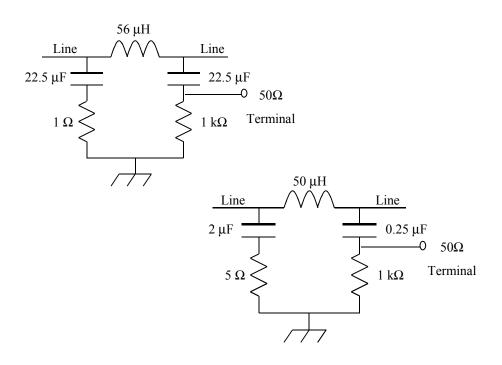

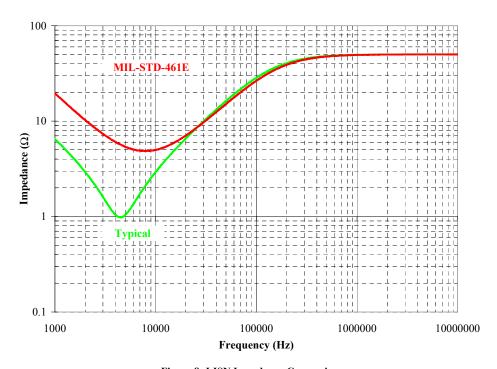

As stated before, the purpose of the LISN is to provide a common 50  $\Omega$  line impedance for comparing test results. However, this 50  $\Omega$  impedance is only specified of the frequencies to be tested for noise. This means that for practical purposes, different LISNs must be used for different regulations testing. Figure 7 give the schematics of the LISNs used for FCC and MIL-STD-461E testing. Figure 8 compares their impedances. It is obvious that the typical LISN will give good results for the FCC test that starts at 450 kHz, but the system designer should be aware of the limitations of the -461E LISN. The 10 kHz—500 kHz portion of the CE102 test will have a much lower impedance than the higher frequencies. This can possibly create issues with an input filter (See Section 2.1) designed for the larger line impedance. Of course, these problems will be magnified if the wrong LISN is used, since the typical LISN drops to slightly less than 1  $\Omega$  at low frequency versus 5  $\Omega$  for the -461E LISN.

<sup>&</sup>lt;sup>9</sup> Ibid., pg. 40

Figure 7: Typical and MIL-STD-461E LISN<sup>10</sup>

Figure 8: LISN Impedance Comparison

<sup>&</sup>lt;sup>10</sup> Ozenbaugh, pg. 23

# 1.2. Sources and Traps

# 1.2.1. Active Components

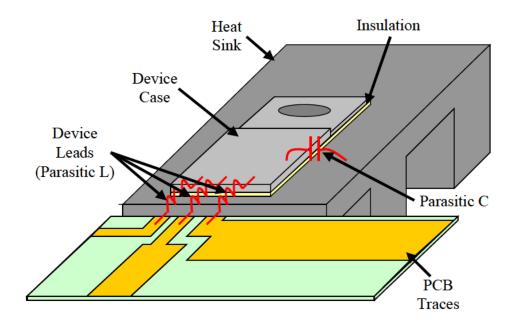

Any power electronics switch will be a noise source due to parasitics in the device packaging. There will be a parasitic inductance  $L_P$  from the package leads, and there will be a parasitic capacitance  $C_P$  due to the thermal management (heat sink) used to protect the device. Figure 9 illustrates this.

The parasitic  $L_P$  causes high frequency ringing in the voltage waveform across the switch due to  $L_P^{di}/_{dt}$ . This has the effect of both increasing the stress on the switch as well as serving as a source of DM noise current from the interaction of the high frequency voltage components with the Miller capacitances of the switch.

The voltage waveform that develops between the device and ground will interact with the parasitic  $C_P$  to create CM noise currents that will flow into the ground plane. This parasitic is the focus of this thesis. Naturally if the heat sink can be floated the noise will be eliminated, but this raises safety issues and in any event may not be possible due to mechanical considerations.

In addition to the packaging parasitics, there will also be noise sources related to the device physics. Effects such as diode reverse-recovery can create additional high-frequency noise as well as increased switching stresses. These high-frequency effects, are outside the bounds of this thesis, however, and will not be discussed in detail.

Figure 9: Packaging Parasitics for Active Device

# 1.2.2. Passive Components

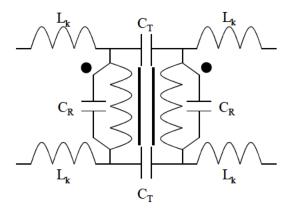

Perhaps the chief source of CM EMI, apart from the active components described above, is the isolation transformer. More specifically, it is the cross-coupling capacitance between the windings that serves as a path for CM noise to flow through the system. Figure 10 shows a simple two-winding transformer with the following major parasitic components: leakage inductance  $L_k$ , interwinding capacitance  $C_R$ , and cross-coupling capacitance  $C_T$ . This capacitance can be minimized by separating the windings (increasing the leakage flux) or by using a Faraday shield in the construction of the transformer. The Faraday shield is simply an isolated section of aluminum or copper foil that is wrapped between the primary and secondary windings and then connected to ground.

Figure 10: Transformer with Lumped Reactive Parasitics

Another important source of common-mode noise is the winding to frame capacitance in an electric machine. This capacitance can be quite significant for large machines, and will result in large leakage currents flowing back into the utility interface and/or interfering with the motor current control and ground-fault interrupt breakers. In addition to the possible external interference, there has also been some discussion related to reduced reliability of motor roller bearings due to the electrical breakdown of the of the lubricating film by common-mode noise currents.<sup>11</sup>

Of course, there are also the parasitics present in any resistor, capacitor, or inductor that will serve to limit the upper operating frequency of the element. A capacitor is limited by the inductance of its leads while the inductor is limited by its interwinding capacitance. Inductors have the additional problem of stray magnetic fields causing radiated noise. These fields are caused by leakage flux that is not contained in the core. Resistors will have stray inductance and/or capacitance depending on the method of manufacture (wirewound, film, or composition).<sup>12</sup>

## 1.2.3. Layout

Control of the radiated EMI is normally emphasized in the layout. However, one must also be aware of all the coupling capacitances between cables, buses, and the mechanical assemblies that provide a potential path to the ground plane. For example, the parasitic capacitance between the transistor and its heat sink may not be an issue if the capacitive coupling between the heat sink

<sup>&</sup>lt;sup>11</sup> A detailed description of this phenomenon is given by Busse, referenced in bibliography.

<sup>12</sup> Ott, pg. 146

and the chassis is minimized. This may not be possible if the heat sink requires forced-air cooling, because the coupling between the heat sink and a nearby fan may by quite significant.

# **Chapter 2. Existing EMI Reduction Techniques**

In the following chapter several means of dealing with common-mode noise are presented, starting with conventional CM EMI reduction techniques then moving into some previously proposed active noise cancellation methods. The final part of the chapter presents the principles of the proposed new method of passive cancellation.

#### *2.1.* Conventional Methods

One way to reduce EMI is to reduce the <sup>dv</sup>/<sub>dt</sub> and <sup>di</sup>/<sub>dt</sub> of the switches. This can be accomplished by changing the gate drive circuitry of the switches or by incorporating snubbers into the topology. These techniques have the advantage of reducing the noise created, but there is the very important downside of increased power dissipation in the switches that may require additional derating (larger devices) and in any event may reduce system efficiency below what can be tolerated. Snubbers are typically also dissipative themselves and will therefore noticeably reduce the overall efficiency as well as increase the system size and complexity. As the rated power of the system is increased the penalty of these options become increasingly intolerable.

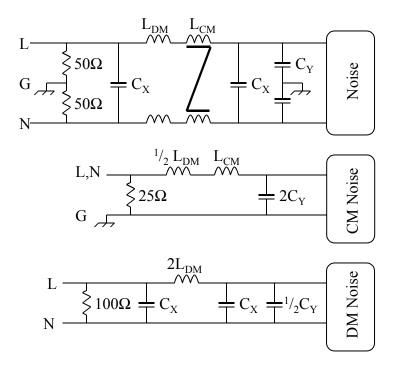

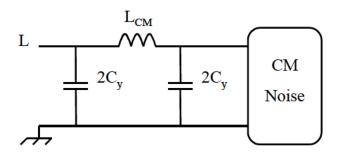

When other methods of reducing conducted noise have been exhausted, the brute-force method is to use a line filter at the utility interface of the system. In practice the incorporation of these filters are practically unavoidable if EMI regulations are to be complied with. Normally these filters are composed solely of passive components in a low-pass filter configuration. Figure 11 shows a typical topology along with the equivalent CM and DM circuits. The design of the filter is accomplished by means of a noise separator<sup>13</sup> to isolate the CM and DM noise spectrum and then designing the filter using the individual equivalent circuits<sup>14</sup>. The differential capacitors C<sub>X</sub> act to short circuit differential noise currents, while the line-to-ground capacitors C<sub>Y</sub> short circuit the common-mode noise currents. The CM choke L<sub>CM</sub> is created by winding two identical coils in the same direction on a single magnetic core. If a tight magnetic coupling is maintained between the two coils the leakage inductance is minimized and there will be little differential impedance seen at line frequencies. The CM choke therefore presents a high impedance to only the common-

<sup>&</sup>lt;sup>13</sup> See Ting Guo

<sup>&</sup>lt;sup>14</sup> Fu-Yuan Shih develops the design methodology in detail. Note that this technique is only applicable to the topology presented in the paper and in Figure 11. A more generalized approach can be found Richard Ozenbaugh's book EMI Filter Design.

mode noise currents, which allows the filter as a whole to minimize interference with the desired power line frequency. The downside to this is that the filter inductors must carry the full power current, which results in components that are large and expensive.

In conclusion to this section, EMI filters are a very effective method of attenuating conducted emissions but this can be a very expensive solution to the noise problem. It will therefore be greatly beneficial to look for other ways in which conducted interference can be cheaply reduced, therefore reducing the size and cost of the filter.

Figure 11: Typical EMI Line Filter Topology Incorporating CM and DM Components<sup>15</sup>

# 2.2. Active Cancellation

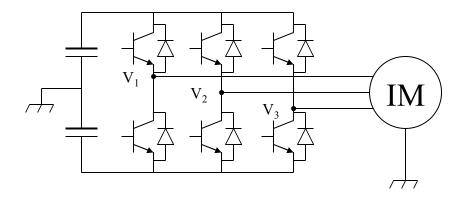

Recently there have been a number of articles dealing with methods of active common-mode cancellation. The principle behind the first group of these techniques is to vary the modulation scheme so that the circuit remains balanced at all times. All of the techniques in this first group have been proposed by A. Julian and others at the University of Wisconsin-Madison. For the three-phase voltage-source-inverter (VSI) in Figure 12 the CM voltage is given by  $V_{\text{CM}} = \frac{V_1 + V_2 + V_3}{3} \text{, therefore the object of the modulation scheme should be to maintain}$

<sup>&</sup>lt;sup>15</sup> Shih, pg 171.

$V_1 + V_2 + V_3 = 0$  at all times. Normally this requires that additional switches must be added to the circuit. For the case of the VSI in Figure 12 this modulation strategy requires that a fourth phase leg must be incorporated into the topology, although this leg can be derated with respect to the other phase legs so long as a balanced load is present. The modulation scheme can then achieve zero common-mode voltage by ensuring that two top switches and two bottom switches are on at all times, so that  $V_1 + V_2 + V_3 + V_4 = 0$ . In practice this will result in approximately 20 dBV<sup>16</sup> of reduction in the voltage across the ground conductor compared to the original three-phase VSI. The drawback to this scheme, other than the need for additional switches and gate drives, is that current ripple is increased and output DM waveform shaping is deteriorated.<sup>17</sup>

Figure 12: Typical Three-Phase Voltage Source Inverter

<sup>&</sup>lt;sup>16</sup> A. Julian, pg. 986

<sup>&</sup>lt;sup>17</sup> P. Ide, pg. 202

Figure 13: 3-Phase 4-Leg VSI with Active CM Filter<sup>18</sup>

Zhihong Ye recently proposed a method for reducing the common-mode emissions of a three-phase, 4 leg inverter. The fourth leg is normally used in this application to mitigate the magnitude of the neutral wire current due to unbalanced and/or non-linear loads that can occur in applications such as shipboard avionics support. In this case the modification involved the addition of a series capacitor to the neutral leg and the modification of the o channel control design (The d and q channels are independent of the o channel and can remain unchanged). This topology change and control methodology has the advantage of being able to reduce both CM high-frequency components and the low frequency components that are present for unbalanced and non-linear loads. The disadvantages to this technique is that it reduces the maximum modulation index from M = 1 to M = 0.866, requiring a higher DC bus voltage for the same output voltage. It also doubles the magnitude of the DM current ripple, which will require a larger DM filter to meet the ripple specifications of the inverter design.

<sup>&</sup>lt;sup>18</sup> Z. Ye, pg. 1

Figure 14: Single-Phase Inverter with Active CM Voltage Cancellation 19

The single-phase inverter in Figure 14 achieves common-mode cancellation by the addition of the switches  $S_5$  and  $S_6$  to form a bi-directional device. Since the common-mode voltage is applied to the parasitic capacitance  $C_P$  during the zero switching states when the diodes in the phase legs  $(S_1$  through  $S_4$ ) freewheel. In this modified topology,  $S_5$  and  $S_6$  are turned on during the freewheeling period drive this common-mode voltage to zero (In practice this is roughly 20 dB $\mu$ V measured across a LISN). The voltage rating of the added switches is the same as those in the phase legs, but the required current rating is approximately  $\frac{1}{2}$ .

Figure 15 is an example of a buck converter topology that has been balanced to realize common-mode noise cancellation by using a split-winding inductor and an additional switch in addition to a bipolar source. The control scheme remains identical to the unmodified topology, and the net change in MOSFET costs is reduced since the voltage rating of the individual switches is halved<sup>20</sup>. The main difficulty is the need for a bipolar supply as this may require modifications to the overall power conversion system.

<sup>19</sup> A. Rao, pg. 1

<sup>&</sup>lt;sup>20</sup> A. Rockhill notes in his paper that the cost of a 500V MOSFET is approximately one-third of a 1000V device.

Figure 15: Balanced Buck Converter Topology<sup>21</sup>

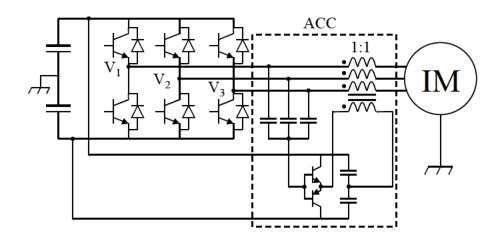

Figure 16: Auxiliary Active Circuit for CM Voltage Cancellation<sup>22</sup>

<sup>&</sup>lt;sup>21</sup> A. Rockhill, pg. 940

$<sup>^{22}</sup>$  S. Ogasawara, "An Active Circuit for Cancellation..."<br/>pg. 836

The final example of active noise cancellation is the active common-noise canceler (ACC) proposed by S. Ogasawara in Figure 16. This technique as proposed only mitigates the CM noise applied to the motor load to increase motor reliability and reduce the electric shock hazard caused by excess ground current. Although not expressly worked out, it would not be difficult to extend this auxiliary circuit to the line filter choke to eliminate the CM voltage seen at the LISN.

The operation of the ACC is as follows: The three capacitors on the inverter output serve to detect a CM voltage, which is then passed through the push-pull amplifier and applied across the CM transformer (choke with added winding) to cancel the original CM voltage. The two capacitors across the amplifier prevent a DC current from flowing in the added winding of the transformer. Experimental results show a reduction of approximately 15 dBµV.<sup>23</sup> The drawback of this method, apart from the need for a CM choke that can handle the rated current of the inverter, is the power dissipation in the linear amplifier. This is given by the equation

$$P_D = \frac{V_{DC}^2}{64 \cdot L_M \cdot f_{SW}}^{24}$$

, where  $V_{DC}$  is the DC link voltage,  $L_M$  is the magnetizing inductance of the

CM choke, and  $f_{SW}$  is the switching frequency of the inverter. It is clear that one has a tradeoff between either a large choke or large transistors.

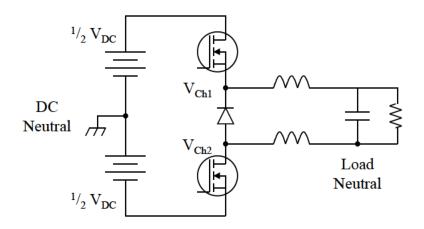

#### 2.3. Passive Cancellation

Passive noise cancellation techniques are not typically considered, because the general perception is that an active technique will always be more flexible and yield better performance. This may be a true statement in many areas of electronics, but there are still cases where a passive solution can yield simpler, cheaper, and better results than an active solution.

A search of the existing literature yields a few papers dealing with passive cancellation; the one that is discussed here is proposed<sup>25</sup> by S. Ogasawara, which involves a CM choke that has an added winding whose terminals are shorted by a resistor. If an appropriate value of resistance is chosen then the magnitude of the motor leakage current can be reduced by a factor of  $^{1}/_{4}$  to  $^{1}/_{3}$ . The addition of this circuit can also reduce the required size of the CM choke by approximately  $^{1}/_{3}$ .

<sup>24</sup> Ibid. pg. 837

<sup>&</sup>lt;sup>23</sup> Ibid. pg. 838

<sup>&</sup>lt;sup>25</sup> S. Ogasawara, "Modeling and Damping of High-Frequency Currents..."

Figure 17: CM Transformer for Damping of Noise Currents<sup>26</sup>

## 2.4. Remarks

There are a number of limitations to the presented methods of noise cancellation. With the active techniques there is first and foremost the added cost of additional power switching modules and their associated gate drives and control circuits. Furthermore other design considerations may preclude the choice of an EMI-friendly modulation scheme. The passive technique presented immediately above demands the full current rating of the converter since it is based on the CM choke. While this technique may be useful if a choke is already present, it is unlikely to be looked upon favorably in a clean-sheet design, especially so given the relatively small reduction in noise currents.

Because of this it would be of some usefulness to have another option. This would be something small and simple that can be easily incorporated into an existing product or design and still allows the designer full freedom to use any desired method of control for the main power circuitry. This also means that the noise cancellation circuitry should be in shunt with the primary power flow to ensure a small size. It is with these motivations in mind that the new passive cancellation technique is presented and applied in the remaining part of this thesis.

\_

<sup>&</sup>lt;sup>26</sup> Ibid. pg. 1109

# Chapter 3. Proposed Passive Cancellation in Isolated DC/DC Converters

In the following chapter we will look at how common-mode cancellation can be applied to some common isolated power converter topologies. This will be broken up into two sections dealing with buck-derived converters and buck-boost-derived converters. Boost-derived converters will not be discussed since they are not commonly used, although this should not be taken to say that the techniques discussed herein are not applicable to those topologies.

# 3.1. Introduction to the Proposed Technique

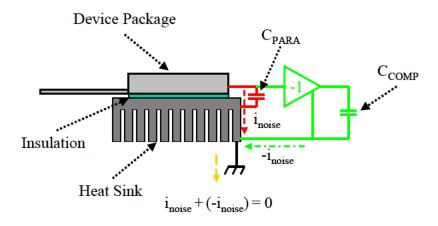

Figure 18: Proposed Method of CM Noise Cancellation

Figure 18 shows the essential concept behind the new method of common-mode noise cancellation. The device <sup>dv</sup>/<sub>dt</sub> across the parasitic capacitance between the package and the heat sink causes a noise current to flow into the ground plane, as described in the previous chapter. Noise cancellation compensates for this noise current by sensing the device <sup>dv</sup>/<sub>dt</sub>, reversing it, and then applying it across a compensating capacitor. This causes a new current of equal magnitude and phase shifted by 180° to that of the noise current to flow into the ground plane. These two currents then sum to zero by Kirschoff's Current Law and the common-mode noise voltage across

the 50  $\Omega$  LISN resistor will be greatly attenuated. Note that this differs from the previously described methods in that it targets the noise currents rather than the overall CM voltage.

This effect can also be explained in terms of energy transfer. What happens is that the noise compensator demands energy at precisely the instant that the noise source pushes energy into the ground plane. Obviously this means that timing is critical for this to work, which means that the practical compensation circuit must contain circuitry with minimal propagation delay.

The other critical parameters that must be taken into account are the required voltage and current ratings. The voltage rating comes from the voltage seen across the switching device, and the current rating comes from the magnitude of canceling current that the noise compensator must push into the ground plane. These two parameters eliminate digital and signal-level analog devices from use in the noise compensator. While voltage sensors can reduce the voltage seen by the compensator, there are at present no cheap integrated analog or digital solutions that can push the required amounts of peak current that the noise compensator requires.

While common op-amps and digital electronics will not work for this application, magnetics can fill the job with very little difficulty. In the remaining portion of this thesis this will be explained further, but under most circumstances a small transformer using a cheap ferrite core will realize excellent results. This solution has the advantage of needing no control or auxiliary power circuitry, which yields a very simple and compact method of eliminating noise that is completely independent of the operation of the rest of the power conversion system.

# 3.2. Buck Derived Converters

# 3.2.1. Half-Bridge DC/DC

# 3.2.1.1. General Description

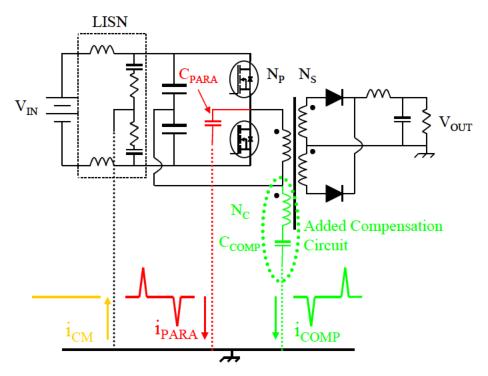

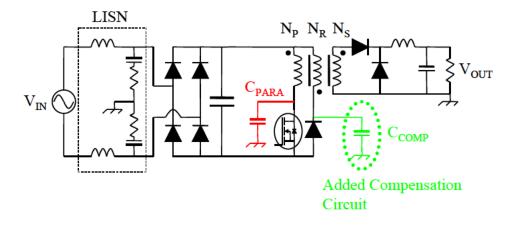

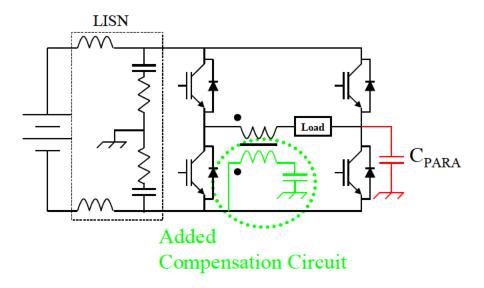

Figure 19: Half-Bridge Isolated DC/DC Topology Incorporating Passive Cancellation

Figure 19 shows how the well known half-bridge isolated topology can be modified to incorporate common-mode cancellation. Shown here is a ground plane into which are injected the parasitic  $^{dv}/_{dt}$  currents (in red) from the switching elements, and the anti-noise currents (in green) injected by the added compensation circuit. In an ideal situation these two currents will then sum to zero, resulting in a much reduced common-mode current flowing into the LISN resistors. By utilizing the existing power transformer in the circuit, an additional winding  $N_C$  can be incorporated into the winding structure. Since  $N_C$  only needs to carry the anti-noise current created by  $C_{COMP}$ , it can use much smaller wire than that used by the main primary and secondary windings  $N_P$  and  $N_S$ . In practice this will be #30 AWG wire or larger depending on the mechanical considerations of the particular design. The other added component is the compensation capacitor  $C_{COMP}$ . This is used to generate the anti-noise current that will cancel out the parasitic noise current generated by  $C_{PARA}$ . The value of  $C_{COMP}$  is determined by the size of

$C_{PARA}$  and the turns ratio  $N_P:N_C$ . If this ratio is 1:1 then  $C_{COMP}$  should be set equal to  $C_{PARA}$ ; otherwise it should be sized such that  $i_{COMP} = C_{PARA} \cdot \frac{dV}{dt}$ .

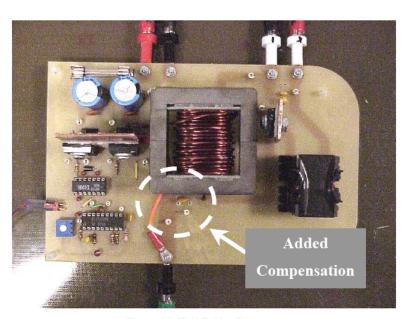

# 3.2.1.2. Construction of Prototype

In order to test this compensation technique, a simple prototype was constructed with the parameters of Table 2. The overhead view of the completed prototype can be seen in Figure 19. The transistor  $C_{PARA}$  was measured to be 70 pF using a HP4194 impedance analyzer on the Cs-Rs setting by taking a mean value between 100 kHz and 1 MHz.

| Table 2: Design Details of Half-E | Bridge Prototype |

|-----------------------------------|------------------|

|                                   | 400 ***          |

| Input Voltage             | $100 \text{ V}_{DC}$ |

|---------------------------|----------------------|

| Output Voltage            | 3.3 V                |

| Output Current (max)      | 10 A                 |

| Frequency                 | 110 kHz              |

| Turns Ratio (Pri:Com:Sec) | 5:5:1                |

| Bridge MOSFET             | IRFP350              |

| Bridge Diodes             | 31DF2                |

| Output Rectifier Diodes   | 30CPQ050             |

| Controller                | UC2526A              |

| Driver                    | IR2110               |

| Output Inductor           | 65 μH                |

| Output Capacitors         | 68 μF                |

| Input Capacitors          | 47 μF                |

Figure 20: Half-Bridge Prototype

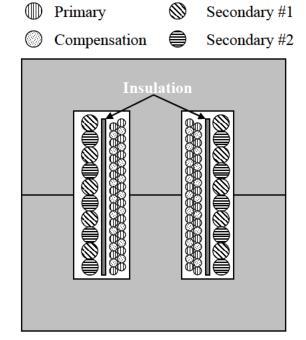

Figure 21: Winding Structure of Half-Bridge Transformer with Compensation Winding

# 3.2.1.3. Experimental Test Results

Figure 22: Test-Setup inside EMI Chamber for Half-Bridge Experiment

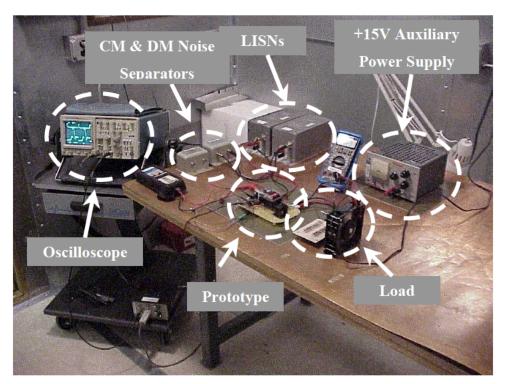

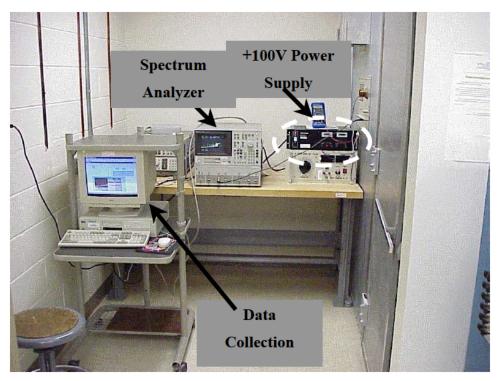

Figure 23: Test-Setup outside EMI Chamber for Half-Bridge Experiment

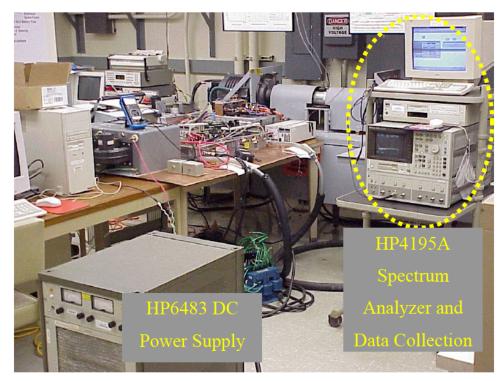

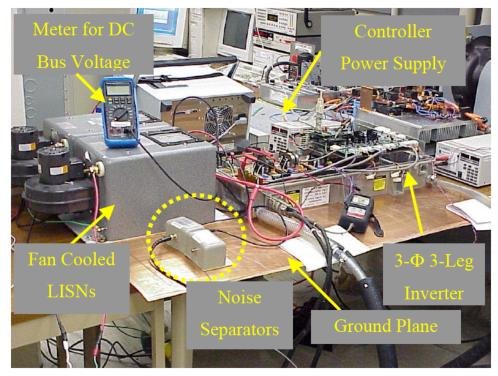

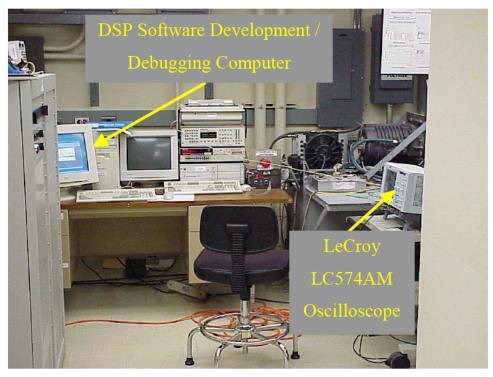

All EMI experiments were done using the test setup in Figure 22 and Figure 23. The circuit itself was placed on a piece of PCB FR-4 material and the circuit ground connection was connected to the ground plane. The auxiliary supply for the control circuits was similarly placed on a piece of PCB to minimize the noise that would couple from it into the ground plane and interfere with the measurement. The main DC power supply was placed outside and connected to the circuit (via the LISNs shown in the photograph) through an access hole in the wall of the EMI chamber. The load consisted of 30 1W-30 $\Omega$  resistors in parallel.

Time domain information was collected using a LeCroy LC574AM digital oscilloscope (Not shown in picture), while the Tektronics 2445 analog oscilloscope shown in Figure 22 was used for routine troubleshooting. Both oscilloscopes were turned off for EMI measurements. A PC running an evaluation version of HP-VEE 5.01 was used to collect data from the spectrum analyzer. Table 3 shows the settings used for the spectrum analyzer in all tests.

Table 3: Test Settings for HP4195A in Half-Bridge Experiments

| Resolution Bandwidth (RBW) | 1kHz   |

|----------------------------|--------|

| Start Frequency            | 10kHz  |

| End Frequency              | 10MHz  |

| Attenuation on Input       | 50dBm  |

| Video Filter               | Off    |

| IF Range                   | Normal |

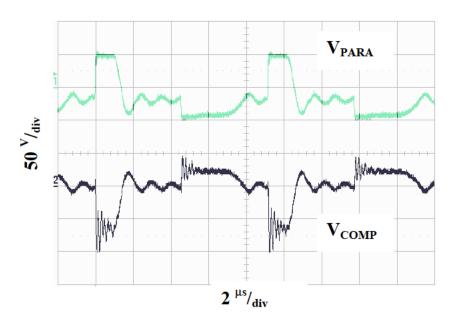

Figure 24: Half-Bridge CM Voltage Waveforms

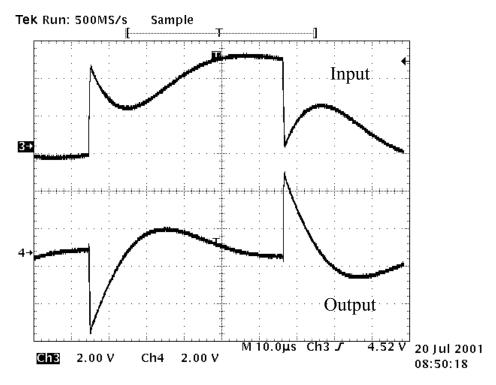

Figure 24 show the voltage from the lower MOSFET drain to ground ( $V_{PARA}$ ) and the voltage from the compensating winding to ground ( $V_{COMP}$ ). The leakage inductance in the transformer causes some high-frequency ringing, but you can clearly see that the switching  $^{dv}/_{dt}$  is accurately replicated by the compensating winding. The effect of the ringing will be to increase the high-frequency portion of the CM EMI, but HF noise is not as difficult to filter as the existing LF noise.

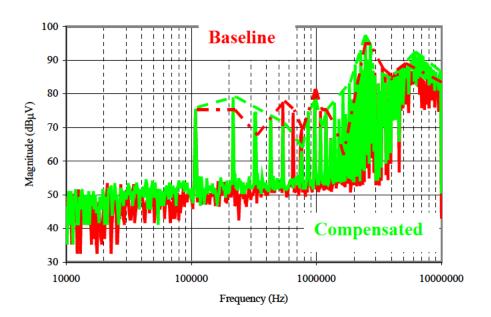

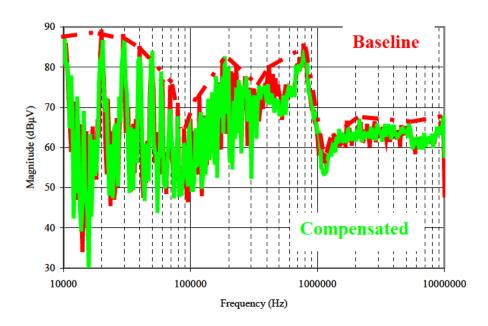

Once the circuit was verified to be operating properly a baseline measurement was taken of the CM noise spectrum. A compensating capacitance of 56 pF was then added to the circuit to see the effect of the noise cancellation technique. This value was chosen because it was the closest standard value 1000 V capacitor freely available in the lab. Unfortunately this had little to no effect, as seen in Figure 25, and the reasons for this became clear once some additional testing was performed. The compensation technique worked quite well when I added a lot of capacitance to the original C<sub>PARA</sub> (Figure 26), and the resulting spectrum was very similar to the original baseline. This seemed to indicate that the original C<sub>PARA</sub> was not contributing the bulk of the common-mode EMI, but rather the transformer cross-coupling capacitance was causing additional noise to couple into the ground plane through the compensating winding. When the transformer was reexamined on the HP4194 impedance analyzer, the cross-coupling capacitance was found to be on the order of 150pF, which was much greater than the measured 70pF for the MOSFET.

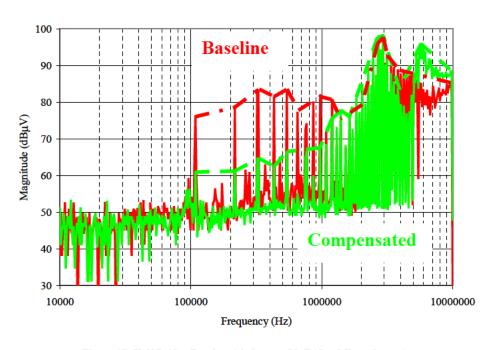

Based on these results the transformer was then rewound, but this time a layer of black electrical tape was inserted between the primary and secondary windings while still interleaving the primary and compensating windings. The significantly reduced the cross-coupling capacitance without interfering with the operation of the circuit. Once the first transformer was replaced with this one, several tests were run in which the heat sink was left ungrounded so that there was no parasitic capacitance from the device itself. By doing this it was then easy to see how significant the transformer EMI was, and it was also relatively simply to test the effectiveness of the canceling winding for different magnitudes of C<sub>PARA</sub> by inserting a capacitor into the circuit in place of the MOSFET C<sub>PARA</sub>. The results of these tests can be seen below in Figure 27, Figure 28, and Table 4.

Figure 25: Half-Bridge CM Baseline and 56pF Compensation (Poor Transformer)

Figure 26: Half-Bridge CM Comparison with 750pF of Added CPARA (Poor Transformer)

Figure 27: Half Bridge Results with  $C_{PARA} = 56pF$  (Good Transformer)

Figure 28: Half Bridge Results with  $C_{PARA} = 112 pF$  (Good Transformer)

Table 4: Comparison for Selected Switching Harmonics (Heat Sink Ungrounded)

|    | Baseline                | 56pF            |                   |                     | 112pF           |                   |                     |

|----|-------------------------|-----------------|-------------------|---------------------|-----------------|-------------------|---------------------|

| N  | No Added<br>Capacitance | No Compensation | With Compensation | $dB\mu V$ Reduction | No Compensation | With Compensation | $dB\mu V$ Reduction |

| 1  | 62                      | 76              | 61                | 15                  | 83              | 55                | 28                  |

| 2  | 63                      | 79              | 61                | 18                  | 85              | 61                | 24                  |

| 3  | 67                      | 83              | 64                | 19                  | 90              | 62                | 28                  |

| 4  | 64                      | 81              | 62                | 19                  | 87              | 58                | 29                  |

| 5  | 68                      | 83              | 66                | 17                  | 90              | 58                | 32                  |

| 6  | 58                      | 77              | 55                | 22                  | 85              | 53                | 32                  |

| 7  | 64                      | 74              | 66                | 8                   | 78              | 68                | 10                  |

| 8  | 55                      | 80              | 60                | 20                  | 88              | 60                | 28                  |

| 9  | 69                      | 82              | 68                | 14                  | 89              | 71                | 18                  |

| 10 | 67                      | 72              | 68                | 4                   | 82              | 68                | 14                  |

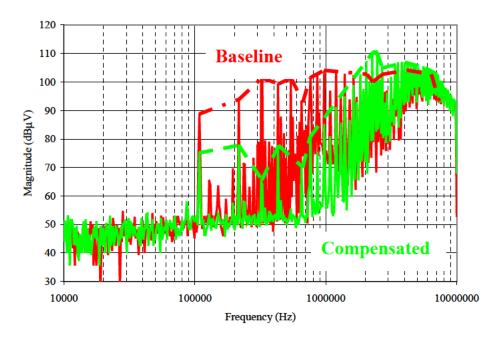

For the final tests, the heat sink was grounded as in the original and 56pF of compensation capacitance was added to equal the measured 70pF of C<sub>PARA</sub>. The results of these tests can be seen in Figure 29, Figure 30, and Table 5. It can be seen from these results that the compensation technique can eliminate the effect of the MOSFET C<sub>PARA</sub>, but the motivation for this will depend a great deal on how dominant this parasitic is in contributing to the EMI spectrum. We can also see from Figure 30 that the differential-mode EMI is unaffected—so this is not a case of shifting the EMI from one place to another. Of course, the ringing caused by the compensating winding will increase the high-frequency CM EMI, but from the standpoint of EMI filter design this penalty does not greatly impact the savings gained from reducing the low-frequency harmonics. Using additional capacitors the compensating capacitance could be more precisely tuned to the value of C<sub>PARA</sub> so that the improvement would be closer to the level in the 56pF column of Table 4. My view, however, was that the additional time spent would be of little usefulness from the standpoint of proving this technique. The end result of these experiments is that this technique is very feasible for practical applications and can realize noticeable improvement in the EMI spectrum for very little cost.

Figure 29: Final Half-Bridge CM Results

Figure 30: Final Half-Bridge DM Results

Table 5: Final Half-Bridge Switching Harmonic Comparison

|    |          | 56pF         | $dB\mu V$ |

|----|----------|--------------|-----------|

| N  | Baseline | Compensation | Reduction |

| 1  | 76       | 65           | 11        |

| 2  | 78       | 69           | 9         |

| 3  | 83       | 71           | 12        |

| 4  | 80       | 68           | 12        |

| 5  | 82       | 71           | 11        |

| 6  | 77       | 64           | 13        |

| 7  | 73       | 66           | 7         |

| 8  | 79       | 69           | 10        |

| 9  | 81       | 74           | 7         |

| 10 | 79       | 77           | 2         |

#### 3.2.2. Single-Switch Forward Converter

## 3.2.2.1. General Description

Figure 31: Off-Line Forward Converter Incorporating Passive CM Cancellation

The single-switch forward converter shown above in Figure 31 can also be easily modified to incorporate passive CM noise cancellation. For this topology, the reset winding serves as the mechanism for sensing and reversing the switching  $^{dv}/_{dt}$ , and therefore the only thing necessary to do is to add the compensating capacitance from the reset diode cathode to ground.

#### 3.2.2.2. Experimental Test Results

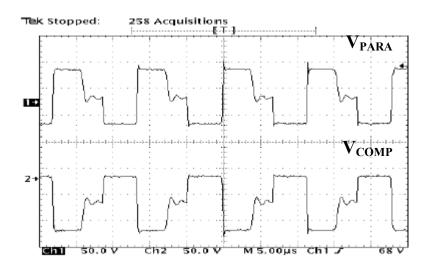

Table 6 gives the essential design details for an open-loop control 100 W prototype that was constructed to test this concept. Figure 32 illustrates how the FET CM voltage is seen by the compensating capacitor for the experimental prototype. As with the half-bridge converter discussed in the previous section, transformer leakage inductance creates a certain amount of high frequency ringing which will cause some degradation in the high-frequency cancellation, but as before the motivation behind this technique is to reduce the low-frequency portion of the spectrum to reduce the size of the input line filter.

**Table 6: Design Details of Forward Converter Prototype**

| Input Voltage             | $120 V_{AC}$ |

|---------------------------|--------------|

| Output Voltage            | 12 V         |

| Output Current (max)      | 8 A          |

| Frequency                 | 110 kHz      |

| Turns Ratio (Pri:Com:Sec) | 2:2:1        |

| MOSFET                    | BUK456-200A  |

| Reset Diode               | BYV29-500    |

| Rectifier Diodes          | 30DF2        |

| Output Diodes             | 18TQ050      |

| Controller                | UC3823BN     |

| Output Inductor           | 20 μΗ        |

| Output Capacitors         | 22 μF        |

| Input Capacitor           | 1000 μF      |

Figure 32: Forward Converter FET and Diode Waveforms

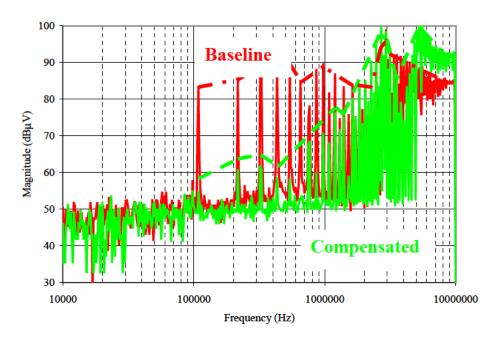

Table 7 shows the settings for the HP4195A spectrum analyzer used for these tests. Note that the start and stop frequencies differ from the half-bridge tests. This does not change the results, but was done because at the time the author was using the CISPR specifications as a guideline. With the half-bridge prototype the author was being supported by funds from the Office of Naval Research, and therefore it was thought prudent to use MIL-STD-461E guidelines instead. Apart from that detail, all other aspects of the test setup are the same as in the above section, and therefore will not be reiterated.

Table 7: Test Settings for HP4195A in Forward Converter Experiments

| Resolution Bandwidth (RBW) | 10kHz  |

|----------------------------|--------|

| Start Frequency            | 100kHz |

| End Frequency              | 30MHz  |

| Attenuation on Input       | 50dBm  |

| Video Filter               | Off    |

| IF Range                   | Normal |

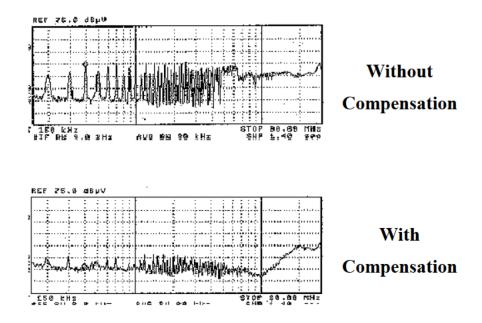

Figure 33: Experimental CM Noise Comparison for Forward Converter

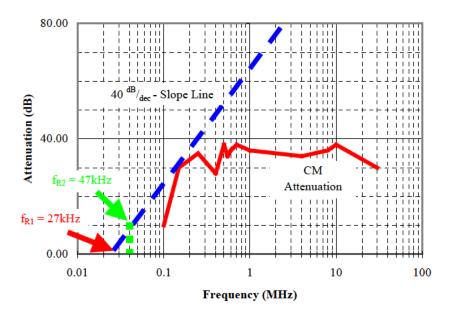

Figure 33 shows the results of noise cancellation for the forward converter experiment. By adding 86 pF of compensating capacitance, the first harmonic was reduced by  $\sim 15$  dB $\mu$ V. Noise cancellation remains between 10 and 15 dB $\mu$ V up to approximately 500 kHz, where high-frequency ringing from the transformer leakage inductance begins to make negatively affect the results. Above 10 MHz the two spectrums are approximately the same, indicating that the transformer and the compensating capacitor are no longer operating effectively.

#### 3.3. Buck-Boost Derived Converters

#### 3.3.1. Flyback Converter

Figure 34: Isolated Flyback Topology Incorporating Passive CM Cancellation

As with buck derived converters, buck-boost derived isolated topologies such as the flyback can also be modified to incorporate passive CM noise cancellation. The method of doing this is very similar to that of the forward converter, and is shown in Figure 34. Of course, since the flyback converter does not use a reset winding, the compensation winding  $N_C$  must be added to the main power transformer. Since the  $N_C$  winding uses small gauge wire, then it would be a fairly cheap addition to the transformer as  $N_C$  can be interwound with the primary winding  $N_P$  for a 1:1 turns ratio.

To demonstrate the operation of this circuit simulated results using the Saber simulation package will be shown. While these results will naturally not be as convincing as experimental data, the amount of time necessary to build prototypes for each of the examples given in this text would be quite large. Therefore a certain number of these topologies will use simulations incorporating many of the parasitic elements seen in a prototype in order to demonstrate the feasibility of the noise cancellation concept for the particular topology.

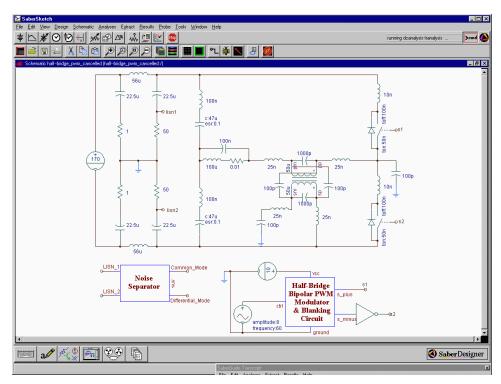

The Saber model of the flyback converter is shown below in Figure 35. It includes the commercial LISN model and a mathematical block that separates the CM and DM noise voltages. The diodes used are all piece-wise linear models with a  $V_{DD}$  of 1 V. The input capacitor was considered to be of electrolytic type, and therefore has sufficient ESL for a resonant frequency of ~150 kHz and an ESR of 0.01  $\Omega$ . The output capacitor is modeled as several electrolytics in parallel with a high-frequency ceramic, and therefore has an ESL of 2 nH and a ESR of 0.001  $\Omega$  for the capacitance value of 200  $\mu$ F. The MOSFET is modeled as an ideal switch with turn-on time of 50 ns and turn-off of 100 ns, with an anti-parallel diode with the same characteristics as the others. Also included is a packaging inductance value of 5 nH and a  $C_{PARA}$  equal to 50 pF.

The model of the transformer takes into account leakage inductance, resonant frequency, and cross-coupling capacitance. The turns ratio is 10:10:1 (primary:compensation:secondary). Leakage inductance was considered to be 1% of the magnetizing inductance of 100  $\mu$ H. I decided to set the resonant frequency of the transformer at 700 kHz, and accordingly made the bypass capacitance to be 500pF. Cross-coupling capacitance is a difficult thing to model correctly due to the inherently distributed nature of the capacitance, but I decided to model this a four capacitances of equal value (10 pF), distributed in such a way as to allow noise currents to pass between all three winding.

It should be noted that the input voltage source is DC rather than 60 Hz AC. This is because and AC source would require significantly more time for the converter to reach steady-state, and would require special options to properly handle when taking the FFT of the LISN noise voltages. Since the noise that this source would contribute would only affect the very low frequency portion of the CM and DM noise spectrums, I believed this to be a justifiable abstraction for the model.

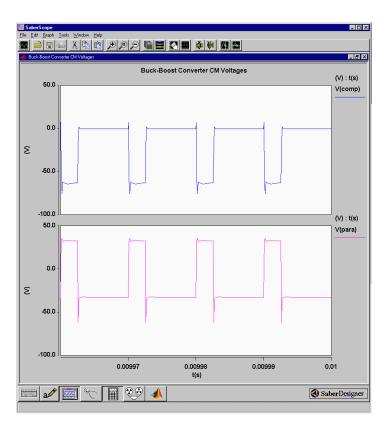

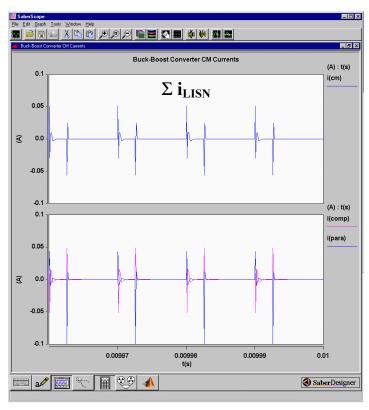

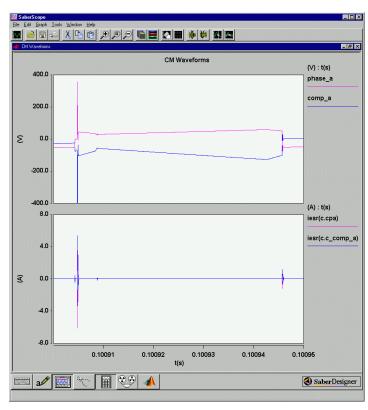

Figure 35: Saber Model for Noise Compensated Flyback Converter

The results of the simulation are shown below in Figure 36 through Figure 39. Figure 36 shows the parasitic and compensating voltages, while Figure 37 shows the corresponding currents. Also shown in Figure 37 is the sum of the LISN currents, which demonstrates the level of cancellation. In the simulations, the effect of leakage inductance is not manifested as severely as in the experimental results. This is due not only to the reduced complexity of the model, but also with the method of simulation. Since a discrete time step is used, the results will tend to be less accurate for higher frequencies because of the effect of the Nyquist sampling criterion.

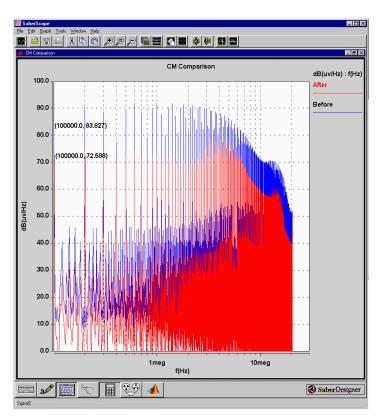

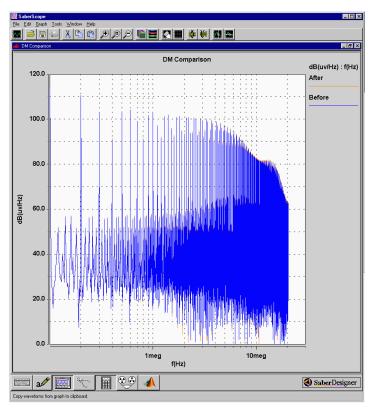

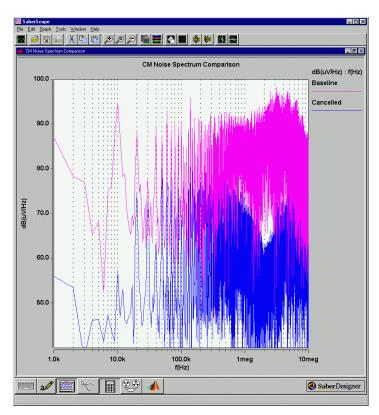

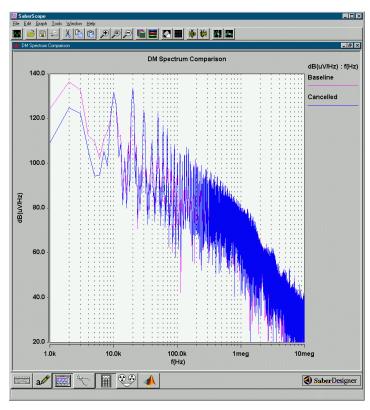

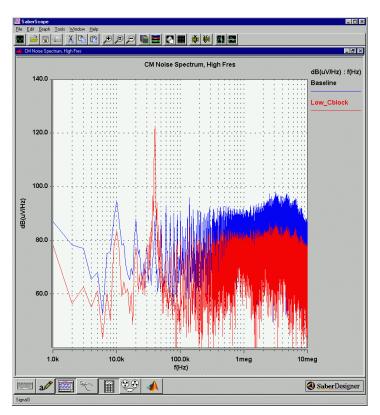

Figure 38 compares the CM noise spectrums and Figure 39 compares the DM noise spectrums of the compensated and uncompensated converter models. These results were achieved by using the FFT analysis option of Saber, and using the following options: fixed transient time step of 0.1  $\mu$ s, transient data from 285  $\mu$ s-295  $\mu$ s, 1024 points, and a Rectangular window. The simulation predicts approximately 20 dB $\mu$ V of reduction for the low frequencies, reducing to 5-10 dB $\mu$ V at the high frequencies. As before, the DM noise spectrum is unchanged from before.

Figure 36: Simulated Parasitic and Compensating Voltages for Flyback Converter

Figure 37: Simulated Parasitic and Compensating Currents in Flyback Converter

Figure 38: Simulated CM Spectrum Comparison for Flyback Converter

Figure 39: Simulated DM Spectrum Comparison for Flyback Converter (Unchanged)

#### 3.4. Remarks

We have seen in this chapter how passive CM noise cancellation can be applied to conventional power converter topologies with success. Isolated topologies are perhaps the easiest and cheapest topologies to incorporate passive noise cancellation, since the compensation winding can be added to an existing transformer structure. In the case of the single-switch forward converter, adding noise cancellation is very trivial and there is little reason to not include it as a general design rule. The issues with regards to incorporation are as follows: ensure tight coupling between the primary and compensating winding so as to maximize the switch  $^{dv}/_{dt}$  pickup, and minimize cross-coupling capacitance between the compensating and secondary windings. The former can be accomplished by interleaving the two windings during construction, and the latter can be accomplished by the use of a few cents worth of electrical tape, as shown in the section on the half-bridge converter.

# Chapter 4. Proposed Passive Cancellation in Non-Isolated DC/DC Converters

While applications of a passive CM noise cancellation scheme are perhaps most obvious for the front-end converter, it is no less important that these techniques be applied elsewhere in a distributed power system if the individual conversion units see a large  $\Delta V$  from input to output. In this chapter methods are presented for achieving noise cancellation by modifying the filter inductors of the common families of non-isolated DC/DC converters: buck, boost, and buckboost.

#### 4.1. Buck Converters

#### 4.1.1. Description of Technique and Model Results

Figure 40: Buck Converter Incorporating Passive CM Noise Cancellation

Figure 40 shows how the common buck converter topology is modified to incorporate passive CM noise cancellation. This method is common to all the non-isolated topologies discussed in this chapter, as will be shown. The compensation winding is simply interwound with the filter inductor winding, to yield a 1:1 turns ratio and to ensure tight coupling between the primary and

compensating windings and to minimize leakage inductance. This technique allows the inductor design to proceed almost independent of the decision to incorporate passive cancellation, since the required filter inductance is normally quite adequate for the purposes of noise cancellation.

Simulated results are presented in the following graphs, and Figure 41 illustrates the Saber model used in these simulations. The same LISN model as used in the flyback converter from the last chapter is also used in this model. An ideal switch with  $t_{on}$  and  $t_{off}$  parameters and a piecewise linear diode model are used to approximate a MOSFET switching at 100 kHz, and 50 pF is used as the source to heat sink capacitance  $C_{PARA}$  (This assumes a TO-220 or similar type package). Note that there could also be a capacitance from the MOSFET drain to heat sink, but since the  $\frac{dv}{dt}$  on the drain side is much smaller the effect of this parasitic is negligible and was therefore not included. Also included are package inductances for the MOSFET and commutating diode.

The input and output filter inductances are modeled here as electrolytics in parallel with low-ESL ceramic capacitors. Some results are shown later illustrating the necessity of a small ESL on these capacitors. The transformer (filter inductor) model uses a linear core model with an infinite  $B_{SAT}$  and a permeability of 1. The inductance value of 50  $\mu$ H was chosen simply because it represented a reasonable value for the purposes of these tests. Parallel capacitances are used to simulate a resonant frequency of 700 kHz. A relatively large cross-coupling capacitance of 200 pF is used in this model to simulate the two windings being very closely spaced, and this capacitance is split into two parts and connected in a "criss-cross" fashion. This was done because it is assumed that the cross-coupling capacitance is very small between sections of the windings at opposite ends of the bobbin. The close spacing should also result in a very small leakage inductance, so a value of 0.1% was chosen and split into two equal parts for each side of the transformer.

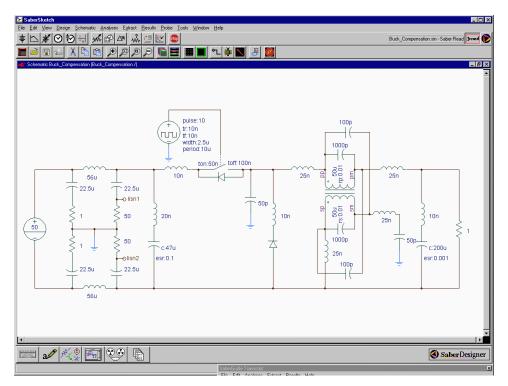

Figure 41: Saber Model for CM Noise Compensated Buck Converter

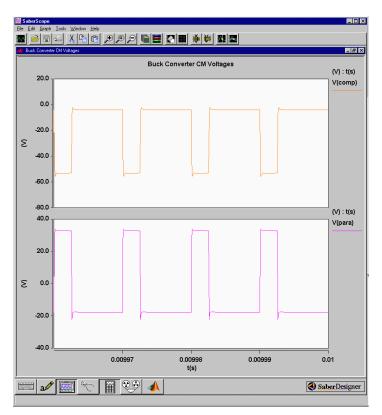

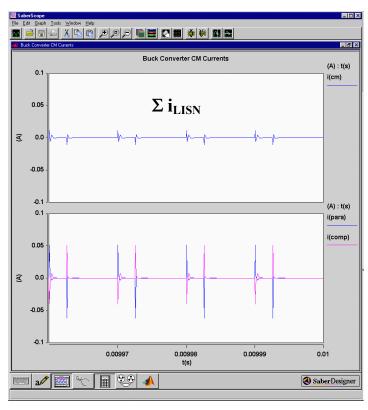

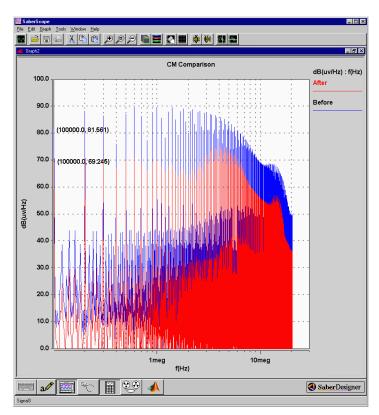

Figure 42 and Figure 43 show the parasitic and compensating voltages and currents under conditions when the noise cancellation technique is operating as it should. Under these circumstances one should expect approximately 10-15 dB $\mu$ V of attenuation in the CM noise spectrum seen across the 50 $\Omega$  LISN resistors with no appreciable degradation in the DM noise spectrum. This is illustrated in Figure 44 and Figure 45.

Figure 42: Buck Converter CM Voltages

Figure 43: Buck Converter CM Currents

Figure 44: Buck Converter CM Noise Spectrum Comparison

Figure 45: Buck Converter DM Noise Spectrum Comparison

Figure 46: Buck Converter CM Voltages, High Input Capacitor ESL

Figure 47: Buck Converter CM Currents, High Input Capacitor ESL

Figure 48: Buck Converter CM Voltages, High Leakage Inductance

Figure 49: Buck Converter CM Currents, High Leakage Inductance

#### 4.1.2. Limitations of the Technique

Circumstances in which the noise cancellation technique does not work are shown in the voltage and currents plots of Figure 46 through Figure 49. These circumstances encompass two main situations. The first limitation is encountered by the magnitude of the ESL of the input capacitor. Inductances act as <sup>di</sup>/<sub>dt</sub> limitors in the overall circuit, and it should be immediately apparent that the large value of series inductance in the LISN limits the current-sourcing ability of the main power source of the converter. The energy for these pulsating currents must therefore be supplied by this input capacitor, but it's own series inductance will also limit its current sourcing capabilities. For the original working simulation this parasitic component was set at 10 nH.. As this value is increased the ability of the capacitor to source the high-frequency currents required by the compensating transformer becomes more and more limited. At 100 nH of ESL the noise compensation circuit is completely ineffective. As you can see in Figure 46 the voltage seen by the compensating is very similar to the parasitic CM voltage but in Figure 47 it is quite obvious that there is something that is limiting the current through the compensating capacitor.

The other serious limitation is the leakage inductance of the compensating transformer. Figure 48 and Figure 49 illustrate the ineffectiveness of the compensating circuit when the transformer leakage inductance is increased from 0.1% to 10% of the transformer magnetizing inductance. As the primary winding of the transformer is essentially serving as a voltage sensor in order to measure the switch <sup>dv</sup>/<sub>dt</sub>, the waveform tends to be split between the leakage inductance and the magnetizing inductance. So long as the leakage inductance remains small in comparison with the magnetizing inductance the distortion is negligible, but eventually the <sup>dv</sup>/<sub>dt</sub> seen by the compensating capacitor becomes too degraded for effective use.

While the problems of ESL and leakage inductance are serious limitations, they can be easily avoided. In order to bring the input capacitor ESL down to an acceptable level, a low-ESL capacitor can be paralleled. Leakage inductance can also be easily minimized by closely winding the primary and compensating windings. For the experiments done in this thesis the two windings were twisted together and wound at the same time. This resulted in leakages much less than 0.1% and quite acceptable results. Leakage inductance still causes problems at high frequency since it stays relatively constant while the magnetizing inductance quickly drops off after the transformer resonant frequency. As discussed in the previous chapter, though, this is of less importance given the low frequency gains.

One important question the reader may have is the effect of different loads on the noise cancellation circuits. Various light and heavy resistive and inductive loads were simulated, and no noticeable degradation was observed. A problem does occur at extreme choices of duty cycle, because the natural ringing during turn-on and turn-off does not have sufficient time to be damped out and can therefore introduce errors into the <sup>dv</sup>/<sub>dt</sub> measurement.

#### 4.2. Boost Converters

Figure 50: Boost Converter Incorporating Passive CM Noise Cancellation<sup>27</sup>

CM noise cancellation for the standard boost converter topology is illustrated by the diagram in Figure 50. This section is unique in this thesis because it presents work not performed by the author. Work on the boost converter was presented at the Applied Power Electronics Conference (APEC 2000) by Wu Xin and others from Zhejiang University and Hong Kong University in the Peoples Republic of China. As far as this writer can determine after exhaustive literature and patent searches, this and one other paper<sup>28</sup> are the only other publicly known works that have been done in the field of power converter passive noise cancellation. Since their work is publicly

<sup>28</sup> F. Costa's work is discussed in Chapter 5.1.1.

<sup>&</sup>lt;sup>27</sup> W. Xing, pg. 179