# MAX5088/MAX5089

## 2.2MHz, 2A Buck Converters with an Integrated High-Side Switch

#### **General Description**

The MAX5088/MAX5089 high-frequency, DC-DC converters with an integrated n-channel power MOSFET provide up to 2A of load current. The MAX5088 includes an internal power MOSFET to enable the design of a nonsynchronous buck topology power supply. The MAX5089 is for the design of a synchronous buck topology power supply. These devices operate from a 4.5V to 5.5V or 5.5V to 23V input voltage and a 200kHz to 2.2MHz resistor-programmable switching frequency. The voltage-mode architecture with a peak switch current-limit scheme provides stable operation up to a 2.2MHz switching frequency. The MAX5088 includes a clock output for driving a second DC-DC converter 180° out-of-phase and a power-on-reset (RESET) output. The MAX5089 includes a power-good output and a synchronous rectifier driver to drive an external low-side MOSFET in the buck converter configuration for high efficiency.

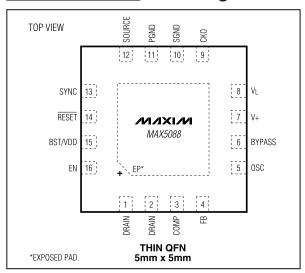

The MAX5088/MAX5089 protect against overcurrent conditions by utilizing a peak current limit as well as overtemperature shutdown providing a very reliable and compact power source for point-of-load regulation applications. Additional features include synchronization, internal digital soft-start, and an enable input. The MAX5088/MAX5089 are available in a thermally enhanced, space-saving 16-pin TQFN (5mm x 5mm) package and operate over the -40°C to +125°C temperature range.

#### **Applications**

xDSL Modem Power Supply

Automotive Radio Power Supply

Servers and Networks

IP Phones/WLAN Access Points

#### Selector Guide

| PART       | CONFIGURATION          | FEATURES                                   |

|------------|------------------------|--------------------------------------------|

| MAX5088ATE | Nonsynchronous<br>Buck | RESET Output,<br>Clock Output              |

| MAX5089ATE | Synchronous Buck       | PGOOD Output,<br>Synchronous FET<br>Driver |

Pin Configurations continued at end of data sheet.

#### **Features**

- ♦ 4.5V to 5.5V or 5.5V to 23V Input Voltage Range

- ♦ Output Voltage Adjustable Down to 0.6V

- ◆ 2A Output Current

- Synchronous Rectifier Driver Output (MAX5089) for Higher Efficiency

- Resistor-Programmable Switching Frequency from 200kHz to 2.2MHz

- External Synchronization and Enable (On/Off) Inputs

- Clock Output for Driving Second Converter 180° Out-Of-Phase (MAX5089)

- ♦ Integrated 150mΩ High-Side n-Channel Power MOSFET

- Power-On Reset Output (MAX5088)/Power-Good Output (MAX5089)

- **♦ Short-Circuit Protection**

- **♦ Thermal-Shutdown Protection**

- ♦ Thermally Enhanced 16-Pin TQFN Package Dissipates 2.7W

#### **Ordering Information**

| PART        | TEMP RANGE      | PIN-<br>PACKAGE | PKG<br>CODE |  |  |

|-------------|-----------------|-----------------|-------------|--|--|

| MAX5088ATE+ | -40°C to +125°C | 16 TQFN         | T1655-2     |  |  |

| MAX5089ATE+ | -40°C to +125°C | 16 TQFN         | T1655-2     |  |  |

<sup>+</sup>Denotes lead-free package.

#### Pin Configurations

#### MIXIM

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

| V+ to PGND                              | 0.3V to +25V                |

|-----------------------------------------|-----------------------------|

| BST/VDD, DRAIN to SGND                  | 0.3V to +30V                |

| SGND to PGND                            | 0.3V to +0.3V               |

| BST/VDD to SOURCE                       | 0.3V to +6V                 |

| SOURCE to SGND                          | 0.6V to +25V                |

| SOURCE or DRAIN Maximum Peak Curr       | ent5A for 1ms               |

| V <sub>L</sub> to SGND0.3V to the lower | of $+6V$ and $(V + + 0.3V)$ |

| SYNC, EN, DL, CKO, OSC, COMP,           |                             |

| FB to SGND                              | $0.3V$ to $(V_L + 0.3V)$    |

PGOOD Maximum Input Current .....±50mA

RESET, PGOOD to SGND .....-0.3V to +6V BYPASS to SGND .....-0.3V to +2.2V VL and BYPASS Short-Circuit Duration to SGND .....Continuous

BYPASS, CKO, OSC, COMP, FB, EN, SYNC, RESET,

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V+ = V_L = 5V \text{ or } V+ = 5.5V \text{ to } 23V, V_{EN} = 5V, T_A = T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted.}$  Circuits of Figures 5 and 6. Typical values are at  $T_A = T_J = +25^{\circ}\text{C}$ .) (Note 1)

| PARAMETER                                           | SYMBOL            | CONDITIONS                                                                                                | MIN  | TYP | MAX  | UNITS |  |

|-----------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------|------|-----|------|-------|--|

| SYSTEM SPECIFICATIONS                               | •                 |                                                                                                           |      |     |      |       |  |

| 1 17/11 0                                           |                   |                                                                                                           | 5.5  |     | 23.0 | V     |  |

| Input Voltage Range                                 | V+                | $V+=V_L$                                                                                                  | 4.5  |     | 5.5  | V     |  |

| V+ Operating Supply Current                         | IQ                | $V+ = 12V$ , $V_{FB} = 0.8V$<br>$R_{OSC} = 10k\Omega$ , no switching                                      |      | 1.8 | 2.5  | mA    |  |

| V+ Standby Supply Current                           | ISTBY             |                                                                                                           |      | 1   | 1.4  | mA    |  |

| Efficiency                                          | η                 | Nonsynchronous (MAX5088),<br>fsw = 1.25MHz, V+ = 12V, I <sub>OUT</sub> = 1.5A,<br>V <sub>OUT</sub> = 3.3V |      | 79  |      | - %   |  |

|                                                     |                   | Synchronous (MAX5089),<br>fsw = 300kHz, V+ = 12V, I <sub>OUT</sub> = 1.5A,<br>V <sub>OUT</sub> = 3.3V     |      | 90  |      | 76    |  |

| V <sub>L</sub> REGULATOR (V <sub>L</sub> )/BYPASS O | UTPUT (BYPA       | SS)                                                                                                       |      |     |      |       |  |

| V <sub>L</sub> Undervoltage Lockout                 | V <sub>UVLO</sub> | V <sub>L</sub> falling                                                                                    |      | 4.1 | 4.3  | V     |  |

| V <sub>L</sub> Undervoltage Lockout<br>Hysteresis   | V <sub>HYST</sub> |                                                                                                           |      | 137 |      | mV    |  |

| V <sub>L</sub> Output Voltage                       | VL                | $V+ = 5.5V$ to 23V, $I_{VL} = 0$ to 40mA                                                                  | 5.0  | 5.2 | 5.5  | V     |  |

| BYPASS Output Voltage                               | VBYPASS           | $V + = V_L = 5.2V$                                                                                        | 1.98 | 2   | 2.02 | V     |  |

| BYPASS Load Regulation                              | ΔVBYPASS          | IBYPASS steps from 0 to 50μA,<br>V+ = V <sub>L</sub> = 5.2V                                               | 0    | 1.2 | 10   | mV    |  |

2 /VI/IXI/VI

<sup>\*</sup>As per JEDEC51 Standard (multilayer board).

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+ = V_L = 5V \text{ or } V+ = 5.5V \text{ to } 23V, V_{EN} = 5V, T_A = T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted.}$  Circuits of Figures 5 and 6. Typical values are at  $T_A = T_J = +25^{\circ}\text{C}$ .) (Note 1)

| PARAMETER                                  | SYMBOL                   | CONDITIONS                                                       |                          | MIN    | TYP   | MAX    | UNITS            |

|--------------------------------------------|--------------------------|------------------------------------------------------------------|--------------------------|--------|-------|--------|------------------|

| SOFT-START                                 |                          |                                                                  |                          | •      |       |        |                  |

| Digital Soft-Start Period                  |                          | Internal 6-bit DAC                                               |                          |        | 4096  |        | Clock<br>periods |

| Soft-Start Steps                           |                          |                                                                  |                          |        | 64    |        | Steps            |

| ERROR AMPLIFIER (FB and COI                | ИP)                      |                                                                  |                          | •      |       |        | •                |

| FB to COMP Transconductance                | дм                       |                                                                  |                          | 1.20   | 1.8   | 2.75   | mS               |

| FB Input Bias Current                      | I <sub>FB</sub>          |                                                                  |                          |        |       | 250    | nA               |

| FB Input Voltage Set Point                 | V <sub>FB</sub>          |                                                                  |                          | 0.5940 | 0.601 | 0.6095 | V                |

| COMP Sink-and-Source Current<br>Capability | ICOMP                    |                                                                  |                          | 100    | 150   |        | μA               |

| INTERNAL MOSFETs                           | 1                        | 1                                                                |                          | U.     |       |        | ı                |

| On-Resistance n-Channel Power MOSFET       | Ron                      | V+ = V <sub>L</sub> = 5.2V, I <sub>SINK</sub> = 100mA            |                          |        | 0.150 | 0.302  | Ω                |

| Leakage Current                            | I <sub>LEAK</sub>        | V <sub>EN</sub> = 0V, V <sub>DRAIN</sub> = 23V,<br>SOURCE = PGND |                          |        |       | 20     | μΑ               |

| Minimum Output Current                     | lout                     | V <sub>OUT</sub> = 3.3V, V+                                      | = 12V (Note 2)           |        | 2     |        | А                |

| Current Limit                              | ILIMIT                   |                                                                  |                          | 2.2    | 2.8   | 3.5    | Α                |

| On-Resistance Internal Low-Side Switch     | Ronlsw                   | ISWITCH = 50mA, V+ = V <sub>L</sub> = 5.2V                       |                          |        | 20    | 38     | Ω                |

| SYNCHRONOUS RECTIFIER DR                   | VER (DL) (MA)            | X5089 Only)                                                      |                          | •      |       |        | •                |

| On-Resistance nMOS                         | RONDLN                   | Isink = 0.1A                                                     |                          |        | 1     | 6.7    | Ω                |

| On-Resistance pMOS                         | RONDLP                   | ISOURCE = 0.1A                                                   |                          |        | 1.9   | 11.1   | Ω                |

| Peak Sink Current                          | lidl_sink                |                                                                  |                          |        | 1     |        | А                |

| Peak Source Current                        | IDL_SOURCE               |                                                                  |                          |        | 0.75  |        | А                |

| OSCILLATOR (OSC)/SYNCHRON                  | IIZATION (SYN            | C)/CLOCK OUTP                                                    | UT (CKO) (MAX5088 (      | Only)  |       |        |                  |

| Clock Output-High Level                    | Vскон                    | $V_L = 5.2V$ , $I_{SOUR}$                                        | CE = 5mA                 | 3.54   |       |        | V                |

| Clock Output-Low Level                     | VCKOL                    | V <sub>L</sub> = 5.2V, I <sub>SINK</sub> = 5mA                   |                          |        |       | 0.4    | V                |

| Switching Frequency                        | fsw                      | V+ = V <sub>L</sub> = 5.2V                                       | $R_{OSC} = 5.62 k\Omega$ | 1900   | 2100  | 2400   | kHz              |

|                                            |                          |                                                                  | $R_{OSC} = 41.2k\Omega$  | 275    | 312   | 350    |                  |

|                                            |                          |                                                                  | $R_{OSC} = 10k\Omega$    | 1130   | 1250  | 1380   |                  |

| Minimum Controllable On-Time               | ton_min                  |                                                                  |                          |        | 120   |        | ns               |

| Maximum Duty Cycle                         | $D_{MAX}$ $f_{SW} = 2.2$ | 6. 0.0041.                                                       | MAX5088                  | 82     | 87.5  |        | %                |

|                                            |                          | ISW = 2.2IVIHZ                                                   | MAX5089                  | 82     | 87.5  |        |                  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+ = V_L = 5V \text{ or } V+ = 5.5V \text{ to } 23V, V_{EN} = 5V, T_A = T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted. Circuits of Figures 5 and 6. Typical values are at } T_A = T_J = +25^{\circ}\text{C.})$  (Note 1)

| PARAMETER                                                               | SYMBOL            | CONDITIONS                                                                       | MIN | TYP  | MAX  | UNITS   |

|-------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------|-----|------|------|---------|

| SYNC Frequency Range (Note 3)                                           | fsync             |                                                                                  | 200 |      | 2200 | kHz     |

| Sync Input to SOURCE Rising-<br>Edge Phase Delay (Note 4)               | SYNCPHASE         | $R_{OSC} = 10k\Omega$ , $f_{SYNC} = 1.2MHz$                                      |     | 65   |      | degrees |

| Clock Output Phase Delay With<br>Respect to SOURCE Waveform<br>(Note 5) | CKOPHASE          | $R_{OSC} = 10k\Omega$ , SYNC = GND (MAX5088 only)                                |     | 115  |      | degrees |

| SYNC High Threshold                                                     | Vsynch            |                                                                                  | 2.0 |      |      | V       |

| SYNC Low Threshold                                                      | VSYNCL            |                                                                                  |     |      | 0.8  | V       |

| Minimum SYNC High Pulse Width                                           | tsync_H           |                                                                                  |     | 100  |      | ns      |

| EN, RESET (MAX5088)/PGOOD (I                                            | MAX5089)          |                                                                                  |     |      |      | 1       |

| EN Threshold                                                            | VIH               |                                                                                  | 2.0 |      |      | V       |

| EN Miesnoid                                                             | VIL               |                                                                                  |     |      | 0.8  | ]       |

| EN Input Bias Current                                                   | IEN               |                                                                                  |     |      | 250  | nA      |

| RESET Threshold (Note 6)                                                | V <sub>TH</sub>   | V <sub>FB</sub> = V <sub>OUT</sub>                                               | 90  | 92.5 | 95   | % Vout  |

| PGOOD Threshold (Note 6)                                                | V <sub>TH</sub>   | V <sub>FB</sub> = V <sub>OUT</sub>                                               | 90  | 92.5 | 95   | % Vout  |

| FB to RESET or FB to PGOOD Propagation Delay                            | t <sub>FD</sub>   |                                                                                  |     | 3    |      | μs      |

| RESET Active Timeout Period                                             | t <sub>RP</sub>   |                                                                                  | 140 | 200  | 254  | ms      |

| RESET, PGOOD Output Voltage                                             | VoL               | ISINK = 3mA                                                                      |     |      | 0.4  | V       |

| RESET, PGOOD Output Leakage<br>Current                                  | ILEAK             | $V+ = V_L = 5.2V$ , $V_{\overline{RESET}}$ or $V_{PGOOD} = 6V$ , $V_{FB} = 0.8V$ |     |      | 2    | μА      |

| THERMAL SHUTDOWN                                                        |                   |                                                                                  |     | •    |      |         |

| Thermal Shutdown                                                        | T <sub>SHDN</sub> | Temperature rising                                                               |     | +170 |      | °C      |

| Thermal-Shutdown Hysteresis                                             |                   |                                                                                  |     | 25   |      | °C      |

- Note 1: 100% tested at +125°C. Limits over temperature are guaranteed by design.

- **Note 2:** Output current may be limited by the power dissipation of the package. See the *Power Dissipation* section in the *Applications Information* section.

- **Note 3:** SYNC input frequency is equal to the switching frequency.

- Note 4: From the SYNC rising edge to SOURCE rising edge.

- Note 5: From the rising edge of the SOURCE waveform to the rising edge of the CKO waveform.

- Note 6: RESET goes high 200ms after Vout crosses this threshold, PGOOD goes high after Vout crosses this threshold.

4 /VI/IXI/VI

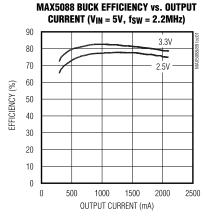

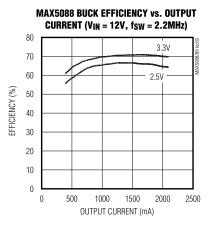

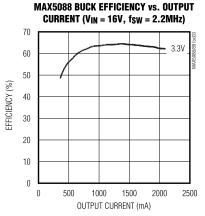

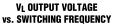

#### **Typical Operating Characteristics**

$(V + = V_L = 5.2V, T_A = +25^{\circ}C, Figures 5 and 6, unless otherwise noted.)$

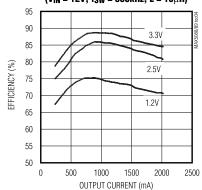

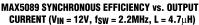

#### MAX5089 SYNCHRONOUS EFFICIENCY vs. OUTPUT CURRENT (Vin = 12V, fsw = 330kHz, L = 15µH)

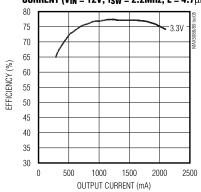

#### $\label{eq:max5089} \begin{array}{l} \text{Max5089 output voltage vs. output} \\ \text{Current (Vin = 12V, Vout = 3.3V, fsw = 2.2MHz)} \end{array}$

5

# DOCKET

## Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

#### **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

#### **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

#### **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

#### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

#### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.