US007721130B2

## (12) United States Patent

#### Prete et al.

#### (54) APPARATUS AND METHOD FOR SWITCHING AN APPARATUS TO A POWER SAVING MODE

- (75) Inventors: Edoardo Prete, Munich (DE); Hans-Peter Trost, Munich (DE); Anthony Sanders, Haar (DE); Dirk Scheideler, Munich (DE); Georg Braun, Holzkirchen (DE); Steve Wood, Munich (DE); Richard Johannes Luyken, Munich (DE)

- (73) Assignee: Qimonda AG, Munich (DE)

- Subject to any disclaimer, the term of this (\*) Notice: patent is extended or adjusted under 35 U.S.C. 154(b) by 656 days.

- (21) Appl. No.: 11/604,666

- (22)Filed: Nov. 27, 2006

#### (65)**Prior Publication Data**

US 2008/0126816 A1 May 29, 2008

- (51) Int. Cl. G06F 1/00 (2006.01)G06F 1/26 (2006.01)G06F 1/32 (2006.01)

- (52) U.S. Cl. ...... 713/323; 713/300; 713/320; 711/5; 711/106; 711/167; 711/170; 365/221

- Field of Classification Search ...... 713/300, (58)713/323, 320; 711/170, 106, 5, 167; 365/221 See application file for complete search history.

#### (56)**References** Cited

#### U.S. PATENT DOCUMENTS

5,357,621 A \* 10/1994 Cox ..... 711/172

northbount +

#### US 7,721,130 B2 (10) **Patent No.:** (45) Date of Patent:

## May 18, 2010

| 6,378,018    | B1 *   | 4/2002  | Tsern et al 710/313    |

|--------------|--------|---------|------------------------|

| · · ·        |        |         |                        |

| 6,650,594    | B1 *   | 11/2003 | Lee et al 365/233.15   |

| 2004/0148482 | A1 $*$ | 7/2004  | Grundy et al 711/167   |

| 2004/0193829 | A1 $*$ | 9/2004  | Woo et al 711/170      |

| 2006/0184287 | A1 $*$ | 8/2006  | Belady et al 700/291   |

| 2006/0248355 | A1 $*$ | 11/2006 | Thayer 713/300         |

| 2007/0076502 | A1 $*$ | 4/2007  | Pyeon et al 365/221    |

| 2007/0083701 | A1 $*$ | 4/2007  | Kapil 711/106          |

| 2007/0143542 | A1 $*$ | 6/2007  | Watanabe et al 711/114 |

| 2007/0283178 | A1*    | 12/2007 | Dodeja et al 713/324   |

#### OTHER PUBLICATIONS

Nasr, Marwan Rami, "FBSIM and the Fully Buffered DIMM Memory System Architecture," Thesis, 2005, pp. 1-128, University of Maryland.

\* cited by examiner

Primary Examiner—Thomas Lee Assistant Examiner-Vincent T Tran (74) Attorney, Agent, or Firm-Slater & Matsil, L.L.P.

#### ABSTRACT (57)

An apparatus being connectable as a latch stage into a asynchronous latch chain comprises a reception interface, wherein upon receipt of the first signal at the reception interface, the apparatus switches to one of the first power saving mode and a second power saving mode, depending on the second signal at the reception interface and wherein the apparatus offers a first power consumption and a first wake-up time in the first power saving mode, and a second power consumption and a second wake-up time in the second power saving mode.

#### 33 Claims, 2 Drawing Sheets

Find authenticated court documents without watermarks at docketalarm.com.

λ **X** – Find authenticated court documents without watermarks at docketalarm.com.

G

**U.S.** Patent

May 18, 2010

Sheet 1 of 2

US 7,721,130 B2

**U.S.** Patent

May 18, 2010

Sheet 2 of 2

US 7,721,130 B2

5

#### APPARATUS AND METHOD FOR SWITCHING AN APPARATUS TO A POWER SAVING MODE

#### TECHNICAL FIELD

The present invention relates to an apparatus and method for switching an apparatus to a power saving mode, for instance to an apparatus being connectable, as a latch stage into an asynchronous latch chain, for instance, a memory 10 buffer for a memory bus in a memory system.

#### BACKGROUND

Modern computer systems offer a significant amount of 15 computing power, as well as a large memory capacity, which enables fast and highly complex computations, as well as fast handling and processing of data. However, in modern computer systems, a key issue is the power management and power consumption. For instance, in the field of mobile com- 20 puting, the available power is limited by the accumulators and/or the batteries available. Moreover, in the field of stationary computers, power consumption is a great issue, as the power dissipated has to be transported away from the components preventing overheating of the respective circuitries 25 and components.

Many computer systems and components of computer systems offer a power saving mode, in which components of the computer system are turned off or shut down. An example for a computer system or a subsystem of a computer system 30 offering such a power saving mode is the memory system, which is employed in personal computers (PC), servers and workstations. One memory system employed in the mentioned computer systems is referred to as the so-called fully buffered DIMM system or a FBDIMM system 35 (FBDIMM=Fully Buffered Dual Inline Memory Module; DIMM=Dual Inline Memory Module).

Today's concept, especially for high-speed interfaces in FBDIMM systems, however, offers only a single mode to reduce the power consumption of the system. Therefore, a 40 compromise between the power saving and the time needed to switch back from the power saving mode to an active mode, or a normal mode of operation, has to be made since this time is crucial for the system performance.

In other words, measures taken to reduce the power con- 45 sumption exhibits a strong negative influence on the performance of the computer system, especially the computing power and the available and effective bandwidth of bus structures, which are required for the transport of data between different components of the computer system, for instance, 50 between a processor and the memory. In this context analog circuits used in interfaces exhibit, for example, a large power saving potential but suffer from the fact that they need a long time to recover again since, for instance, control loops and other feedback loops are needed to reach and maintain a 55 stable working point and a stable working condition, before these interfaces can provide a reliable and fast data communication between the components attached.

#### SUMMARY OF THE INVENTION

An embodiment of an apparatus being connectable, as a latch stage into an asynchronous latch chain comprises a reception interface, wherein upon receipt of a first signal at wherein the apparatus offers a first power consumption and a first wake-up time in the first power saving mode and a second power consumption and a second wake-up time in the second power saving mode.

An embodiment of an apparatus being connectable, as a latch stage into an asynchronous latch chain comprises a reception interface, wherein upon receipt of a first signal at the reception interface the apparatus switches to one of the first power saving mode and a second power saving mode, depending on the second signal at the reception interface, wherein the apparatus offers a first power consumption and a first wake-up time in the first power saving mode and a second power consumption and a second wake-up time in the second power saving mode, wherein the first power consumption is higher than the second power consumption and wherein the first wake-up time is shorter than the second wake-up time.

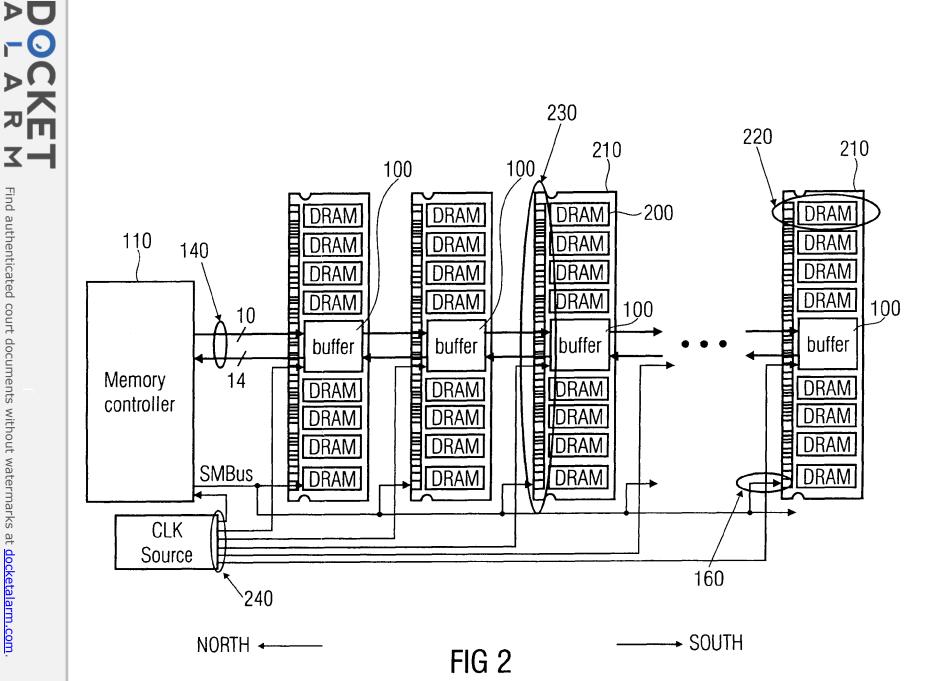

According to a further embodiment of the present invention, a memory system comprises a memory controller, a plurality of memory modules coupled to the memory controller in an asynchronous latch chain configuration, the plurality of memory modules comprising a first memory module and a second memory module, wherein the first memory module is positioned nearer to the memory controller than the second memory module within the asynchronous latch chain, wherein the first memory module offers a first power consumption and a first wake-up time in a first power saving mode, wherein the second memory module offers a second power consumption and second wake-up time in a second power saving mode, wherein each memory module of the plurality of memory modules comprises a reception interface, wherein upon receipt of a first signal from the memory controller at the reception interface, the first memory module switches to the first power saving mode and the second memory module switches to the second power saving mode, wherein the first power consumption is higher than the second power consumption and wherein the first wake-up time is shorter than the second wake-up time.

#### BRIEF DESCRIPTION OF THE DRAWINGS

Embodiments of the present invention are described hereinafter, making reference to the attached drawings.

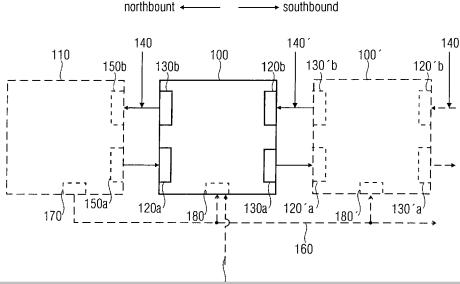

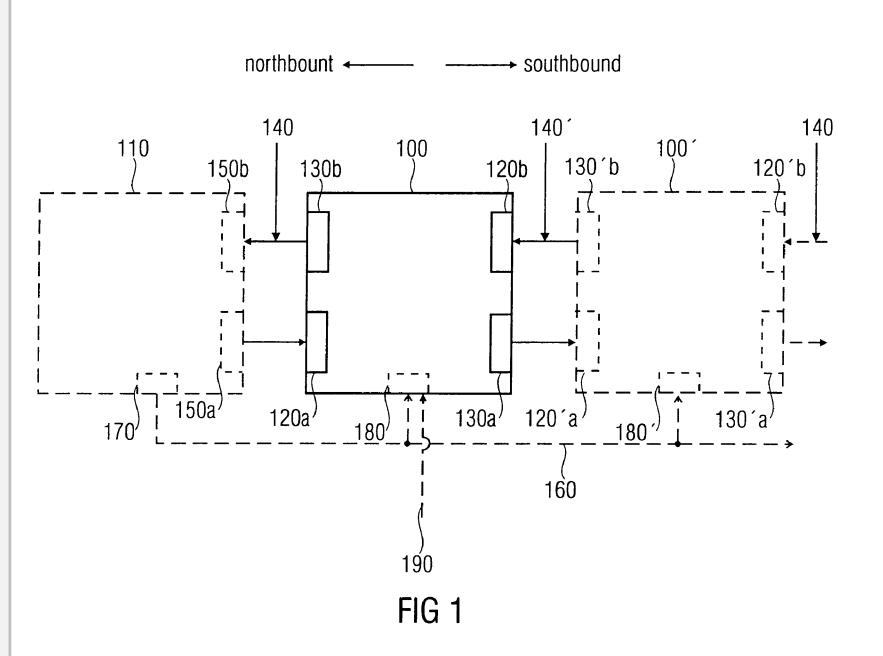

FIG. 1 shows a schematic block diagram of an embodiment of an apparatus according to a first embodiment of the present invention; and

FIG. 2 shows a schematic block diagram of a second embodiment of an apparatus and an embodiment of a memory system according to a second embodiment of the present invention.

#### DETAILED DESCRIPTION OF ILLUSTRATIVE EMBODIMENTS

FIGS. 1 and 2 show block diagrams of an embodiment of an apparatus being connectable as a latch stage into an asynchronous latch chain and an embodiment of a memory system. Before a second embodiment of the present invention is described with respect to FIG. 2, a first embodiment of an 60 apparatus being connectable as a latch stage into an asynchronous latch chain is explained with respect to the schematic representation of an embodiment of the apparatus and an embodiment of a memory system shown in FIG. 1.

FIG. 1 shows an embodiment of an apparatus 100 intethe reception interface the apparatus switches to one of the 65 grated into an embodiment of a memory system according to

Find authenticated court documents without watermarks at docketalarm.com.

apparatus 100' and a memory controller 110 forming an asynchronous latch chain or a daisy chain as will be explained below.

In a so-called daisy chain configuration, components of the daisy chain, which are also referred to as latch stages of the asynchronous latch chain, communicate only with their direct neighbors, for instance, via a wiring scheme comprising interfaces and signal lines of a bus structure. Hence, only neighboring devices are directly coupled to each other. Furthermore, usually in a daisy chain no web like structures are 10 formed and the coupling of the devices does not loop back, for instance, from the first device to the last device in the daisy chain.

In other words, a typical daisy chain configuration in electrical and electronic engineering is a wiring scheme in which, 15 for example, a first device is coupled or wired to a second device, the second device is coupled to a third device, the third device is coupled to a fourth device, and so on. However, the connections of this daisy chain usually do not form webs or loop backs, as discussed above.

In many daisy chain configurations, each of the devices, therefore, comprises circuits working as repeaters or amplifiers to counteract the natural attenuation of the signals when they are transmitted from one device to the next device. In the case of digital signals being exchanged between the different 25 components of a daisy chain, the digital signals may be transferred via an electrical bus as, for instance, in the case of memory devices. In these cases, however, a bus termination might be advisable to implement to prevent reflections and other disturbances of the signals. However, in the case of 30 digital signals, the digital signals may be electrically regenerated or recreated in each device in the daisy chain, as long as they are not modified.

In other words, a signal transmitted over the bus is passed along through each device's interface circuits instead of being 35 transmitted to all devices (simultaneously) by the devices sharing the same bus. Hence, for instance, transmitting a signal from the first device in the daisy chain to the third device in the daisy chain requires the second device to receive the signal from the first device and to forward or to regenerate 40 the signal to be transmitted to the third device of the daisy chain.

Especially in the field of memory devices, the first or central device in the daisy chain is very often the memory controller 110. Especially in the field of memory devices, the 45 communication in the direction of the memory controller or towards the memory controller 110 is referred to as "northbound" while the opposite direction, the communication from the memory controller to the further devices in the daisy chain is usually referred to as "southbound".

Although embodiments of the present invention are not limited to an application in the field of memory devices, this terminology is adapted in the framework of the present application, as it allows a simple designation of a direction of the communication in the daisy chain or in an asynchronous latch  $\,$  55  $\,$ chain.

Turning back to FIG. 1, the apparatus 100 comprises four sub-interfaces 120a, 120b, 130a and 130b. To be more precise, sub-interface 120a is part of a reception interface of the apparatus 100, which is dedicated to receiving northbound 60 signals on a bus 140 coupling the apparatus 100 and the memory controller 110. The second sub-interface 120b, which is dedicated for receiving northbound signal from the further apparatus 100' which is coupled to the apparatus 100 by a bus 140'. Both buses 140 and 140' comprise in the 65 sub-interfaces 130a and 130b, as well as, if the interface 180

4

Accordingly, the apparatus 100 further comprises, apart from the sub-interface 120a coupled to the southbound bus structure of the bus 140, the further sub-interface 130a coupled to the southbound bus structure of the bus 140'. With respect to the northbound communication and the northbound bus structures of the buses 140 and 140' the apparatus 100 comprises apart from the interface 120b coupled to the northbound bus structure of the bus 140', the further sub-interface 130*b* coupled to the northbound bus structure of the bus 140.

While the two sub-interfaces 120a and 120b are dedicated to receiving signals southbound via the bus 140 and northbound via the bus 140', respectively, the sub-interfaces 130a and 130b are dedicated to transmitting or sending signals over the southbound bus structure of the bus 140' and the northbound bus structure of the bus 140, respectively.

As a consequence, the two sub-interfaces 120a and 120b are part of a reception interface of the apparatus 100, while the sub-interfaces 130a and 130b are part of a transmission interface of the apparatus 100. The further apparatus 100' of the 20 memory system shown in FIG. 1 comprises also four subinterfaces 120'a, 120'b, 130'a and 130'b, which are dedicated for receiving or sending signals via the buses 140' and 140", coupled to the further apparatus 100'. Compared to the apparatus 100, the bus 140' is coupled to the sub-interfaces 120'a and 130'b of the further apparatus 100', while the bus 140" is coupled to the sub-interfaces 130'a and 120'b.

The embodiment of the memory system shown in FIG. 1 further comprises the memory controller 110, which is coupled to the embodiment of the apparatus 100 via the bus 140. The southbound bus structure of the bus 140 is coupled to a sub-interface 150a of the memory controller 110 while the northbound bus structure of the bus 140 is coupled to a sub-interface 150b of the memory controller 110. The subinterface 150a is, therefore, adapted for transmitting or sending signals via the southbound bus structure of the bus 140 to the sub-interface 120a of the apparatus 100, which is adapted for receiving the signals. Accordingly, the sub-interface 150b of the memory controller 110 is adapted to receiving signals sent via the northbound bus structure of the bus 140, provided by the sub-interface 130b of the apparatus 100.

As a further option, the memory controller **110**, the apparatus 100 and the further apparatus 100' can be coupled to a signal line 160, which can, for instance, be an individual signal line or part of a unidirectional or bidirectional bus. The signal line 160 is coupled to an optional interface 170 of the memory controller 110 and two interfaces 180 and 180' of the apparatus 100 and the further apparatus 100' respectively. The signal line 160 can, for instance, be employed by the memory controller 110 to provide the apparatuses 100 and 100' with commands, data, status requests and other signals, so that the interfaces 180 and 180' of the apparatus 100 and the further apparatus 100' are capable of receiving signals from the memory controller. In this case, the interfaces 180 and 180' are also part of the reception interfaces of the apparatus 100 and the further apparatus 100', respectively.

The reception interface of the apparatus 100 comprises all interfaces, connectors, (mechanical) jumpers, switches (DIP switches) and terminals, which are designated for and/or capable of receiving signals. In the embodiment of a memory system shown in FIG. 1, the reception interface of the apparatus 100 comprises the sub-interfaces 120a and 120b and, if present, the optional interface 180.

Accordingly, the transmission interface, also referred to as the sending interface of the apparatus 100, comprises the

Find authenticated court documents without watermarks at docketalarm.com

## DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time alerts** and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

## LAW FIRMS

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

## FINANCIAL INSTITUTIONS

Litigation and bankruptcy checks for companies and debtors.

## E-DISCOVERY AND LEGAL VENDORS

Sync your system to PACER to automate legal marketing.