## LP2998 DDR-II and DDR-I Termination Regulator

#### **General Description**

The LP2998 linear regulator is designed to meet JEDEC SSTL-2 and JEDEC SSTL-18 specifications for termination of DDR-SDRAM and DDR-II memory. The device contains a high-speed operational amplifier to provide excellent response to load transients. The output stage prevents shoot through while delivering 1.5A continuous current as required for DDR-SDRAM termination. The LP2998 also incorporates a  $\rm V_{SENSE}$  pin to provide superior load regulation and a  $\rm V_{REF}$  output as a reference for the chipset and DIMMs.

An additional feature found on the LP2998 is an active low shutdown  $(\overline{SD})$  pin that provides Suspend To RAM (STR) functionality. When  $\overline{SD}$  is pulled low the V<sub>TT</sub> output will tristate providing a high impedance output; while, V<sub>REF</sub> remains active. A power savings advantage can be obtained in this mode through lower quiescent current.

#### **Features**

- Source and sink current

- Low output voltage offset

- No external resistors required

- Linear topology

- Suspend to Ram (STR) functionality

- Low external component count

- Thermal Shutdown

- Available in SO-8, PSOP-8 packages

#### **Applications**

- DDR-I and DDR-II Termination Voltage

- SSTL-18 Termination

- SSTL-2 and SSTL-3 Termination

- HSTL Termination

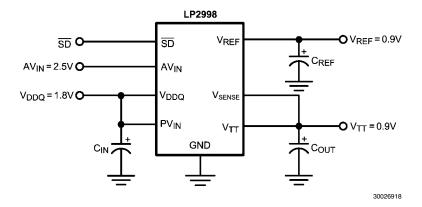

#### **Typical Application Circuit**

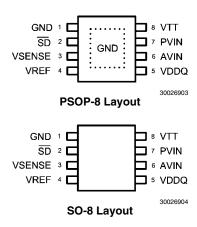

## **Connection Diagrams**

## **Pin Descriptions**

| SO-8 Pin or PSOP-8 Pin | Name                                                          | Function                                                    |  |  |  |

|------------------------|---------------------------------------------------------------|-------------------------------------------------------------|--|--|--|

| 1                      | GND                                                           | Ground.                                                     |  |  |  |

| 2                      | SD                                                            | Shutdown.                                                   |  |  |  |

| 3                      | VSENSE                                                        | Feedback pin for regulating V <sub>TT</sub> .               |  |  |  |

| 4                      | VREF                                                          | Buffered internal reference voltage of V <sub>DDQ</sub> /2. |  |  |  |

| 5                      | VDDQ                                                          | Input for internal reference equal to V <sub>DDQ</sub> /2.  |  |  |  |

| 6                      | AVIN                                                          | Analog input pin.                                           |  |  |  |

| 7                      | PVIN                                                          | Power input pin.                                            |  |  |  |

| 8                      | 8 VTT Output voltage for connection to termination resistors. |                                                             |  |  |  |

|                        | EP                                                            | Exposed pad thermal connection. Connect to soft Ground.     |  |  |  |

## **Ordering Information**

| Order Number | Package Type | NSC Package Drawing | Supplied As              |

|--------------|--------------|---------------------|--------------------------|

| LP2998MA     | SO-8         | M08A                | 95 Units per Rail        |

| LP2998MAX    | SO-8         | M08A                | 2500 Units Tape and Reel |

| LP2998MR     | PSOP-8       | MRA08A              | 95 Units Tape and Reel   |

| LP2998MRX    | PSOP-8       | MRA08A              | 2500 Units Tape and Reel |

151°C/W

43°C/W

1kV

#### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

PVIN, AVIN, VDDQ to GND

No pin should exceed AVIN -0.3V to +6V Storage Temp. Range  $-65^{\circ}$ C to +150 $^{\circ}$ C Junction Temperature  $150^{\circ}$ C Lead Temperature (Soldering, 10 sec)  $260^{\circ}$ C

SO-8 Thermal Resistance  $(\theta_{JA})$ PSOP-8 Thermal Resistance  $(\theta_{JA})$ Minimum ESD Rating (Note 2)

### **Operating Range**

Junction Temp. Range (Note 3)  $-40^{\circ}$ C to  $+125^{\circ}$ C AVIN to GND 2.2V to 5.5V

**Electrical Characteristics** Specifications with standard typeface are for  $T_J = 25^{\circ}\text{C}$  and limits in **boldface type** apply over the full **Operating Temperature Range** ( $T_J = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ ) (Note 4). Unless otherwise specified, VIN = AVIN = PVIN = 2.5V.

| Symbol             | Parameter                                                                                       | Conditions                                  | Min   | Тур      | Max       | Units           |

|--------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------|-------|----------|-----------|-----------------|

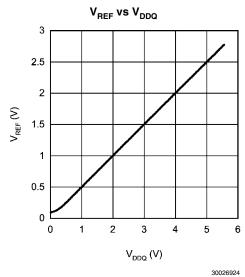

|                    | V <sub>REF</sub> Voltage (DDR I)                                                                | VIN = VDDQ = 2.3V                           | 1.135 | 1.150    | 1.185     | V               |

| V <sub>REF</sub>   |                                                                                                 | VIN = VDDQ = 2.5V                           | 1.235 | 1.250    | 1.285     | V               |

|                    |                                                                                                 | VIN = VDDQ = 2.7V                           | 1.335 | 1.350    | 1.385     | V               |

|                    | V <sub>REF</sub> Voltage (DDR II)                                                               | PVIN = VDDQ = 1.7V                          | 0.837 | 0.850    | 0.887     | V               |

|                    |                                                                                                 | PVIN = VDDQ = 1.8V                          | 0.887 | 0.910    | 0.937     | V               |

|                    |                                                                                                 | PVIN = VDDQ = 1.9V                          | 0.936 | 0.950    | 0.986     | V               |

| Z <sub>VREF</sub>  | V <sub>REF</sub> Output Impedance                                                               | $I_{REF} = -30 \text{ to } +30 \mu\text{A}$ |       | 2.5      |           | kΩ              |

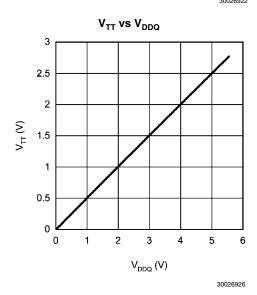

|                    | V <sub>TT</sub> Output Voltage (DDR I) (Note 7)                                                 | $I_{OUT} = 0A$                              |       |          |           |                 |

|                    |                                                                                                 | VIN = VDDQ = 2.3V                           | 1.120 | 1.150    | 1.190     | V               |

|                    |                                                                                                 | VIN = VDDQ = 2.5V                           | 1.210 | 1.250    | 1.290     | V               |

|                    |                                                                                                 | VIN = VDDQ = 2.7V                           | 1.320 | 1.350    | 1.390     | V               |

|                    |                                                                                                 | $I_{OUT} = +/-1.5A$                         |       |          |           |                 |

|                    |                                                                                                 | VIN = VDDQ = 2.3V                           | 1.125 | 1.150    | 1.190     | V               |

| V <sub>TT</sub>    |                                                                                                 | VIN = VDDQ = 2.5V                           | 1.225 | 1.250    | 1.290     | V               |

|                    |                                                                                                 | VIN = VDDQ = 2.7V                           | 1.325 | 1.350    | 1.390     |                 |

|                    | V <sub>TT</sub> Output Voltage (DDR II) (Note 7)                                                | $I_{OUT} = 0A$ , $AVIN = 2.5V$              |       |          |           |                 |

|                    |                                                                                                 | PVIN = VDDQ = 1.7V                          | 0.822 | 0.850    |           | V               |

|                    |                                                                                                 | PVIN = VDDQ = 1.8V                          | 0.874 | 0.900    |           | V               |

|                    |                                                                                                 | PVIN = VDDQ = 1.9V                          | 0.923 | 0.950    | 0.988     | V               |

|                    |                                                                                                 | $I_{OUT} = +/-0.5A$ , AVIN = 2.5V           |       | 0.050    | 0.000     | .,              |

|                    |                                                                                                 | PVIN = VDDQ = 1.7V                          | 0.820 | 0.850    | 0.890     | V               |

|                    |                                                                                                 | PVIN = VDDQ = 1.8V                          | 0.870 | 0.900    | 0.940     | V<br>V          |

|                    | V Output Voltage Offset (V V ) for DDD I (Note 7)                                               | PVIN = VDDQ = 1.9V                          | 0.920 | 0.950    | 0.990     |                 |

|                    | $V_{TT}$ Output Voltage Offset ( $V_{REF} - V_{TT}$ ) for DDR I (Note 7)                        | $I_{OUT} = 0A$                              | -30   | 0        | 30        | mV              |

|                    |                                                                                                 | I <sub>OUT</sub> = -1.5A                    | -30   | 0        | 30        | mV              |

| V00                | W O L LV II O W L W L V D D D II (N L Z)                                                        | I <sub>OUT</sub> = +1.5A                    | -30   | 0        | 30        | mV              |

| VOS <sub>Vtt</sub> | V <sub>TT</sub> Output Voltage Offset (V <sub>REF</sub> – V <sub>TT</sub> ) for DDR II (Note 7) | I - 0A                                      | -30   | 0        | 20        | mV              |

|                    |                                                                                                 | $I_{OUT} = 0A$                              |       | 0        | 30<br>30  |                 |

|                    |                                                                                                 | $I_{OUT} = -0.5A$                           | -30   |          |           | mV              |

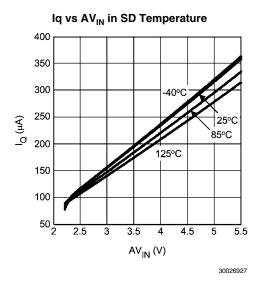

|                    | Quiescant Current (Note 5)                                                                      | $I_{OUT} = +0.5A$                           | -30   | 0<br>320 | 30<br>500 | mV<br>^         |

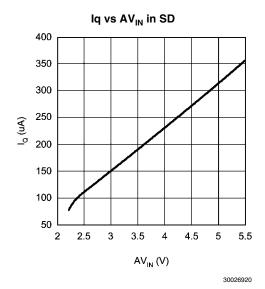

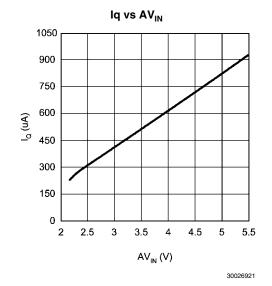

| I <sub>Q</sub>     | Quiescent Current (Note 5)  VDDQ Input Impedance                                                | I <sub>OUT</sub> = 0A                       |       | 100      | 300       | μA              |

| Z <sub>VDDQ</sub>  | Quiescent current in shutdown (Note 6)                                                          | SD = 0V                                     |       | 115      | 150       | <u>kΩ</u><br>μΑ |

| I <sub>SD</sub>    | Shutdown leakage current                                                                        | SD = 0V                                     |       | 2        | 5         | <del></del>     |

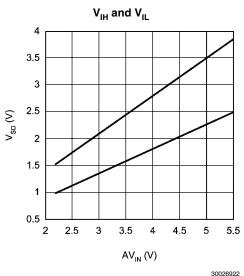

| U <sub>Q_SD</sub>  | Minimum Shutdown High Level                                                                     | OD = 0V                                     | 1.9   |          |           | <u>μΑ</u><br>V  |

| V <sub>IH</sub>    | Maximum Shutdown Low Level                                                                      |                                             | 1.9   |          | 0.8       |                 |

| V <sub>IL</sub>    |                                                                                                 | SD = 0V                                     |       | 4        |           |                 |

| lv<br>             | V <sub>TT</sub> leakage current in shutdown                                                     | $V_{TT} = 1.25V$                            |       | 1        | 10        | μ <b>A</b>      |

| I <sub>SENSE</sub> | V <sub>SENSE</sub> Input current                                                                |                                             |       | 13       |           | nA              |

| Symbol              | Parameter                   | Conditions | Min | Тур | Max | Units |

|---------------------|-----------------------------|------------|-----|-----|-----|-------|

| T <sub>SD</sub>     | Thermal Shutdown (Note 6)   |            |     | 165 |     | °C    |

| T <sub>SD_HYS</sub> | Thermal Shutdown Hysteresis |            |     | 10  |     | °C    |

- **Note 1:** Absolute maximum ratings indicate limits beyond which damage to the device may occur. Operating range indicates conditions for which the device is intended to be functional, but does not guarantee specific performance limits. For guaranteed specifications and test conditions see Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

- Note 2: The human body model is a 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor into each pin.

- Note 3: At elevated temperatures, devices must be derated based on thermal resistance. The device in the SO-8 package must be derated at  $\theta_{JA}$  = 151.2° C/W junction to ambient with no heat sink.

- Note 4: Limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlation using Statistical Quality Control (SQC) methods. The limits are used to calculate National's Average Outgoing Quality Level (AOQL).

- Note 5: Quiescent current defined as the current flow into AVIN.

- Note 6: The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_{J(MAX)}$ , the junction to ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature and the regulator will go into thermal shutdown.

- Note 7:  $V_{TT}$  load regulation is tested by using a 10 ms current pulse and measuring  $V_{TT}$ .

## **Typical Performance Characteristics**

# DOCKET

## Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

### **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

#### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

#### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.