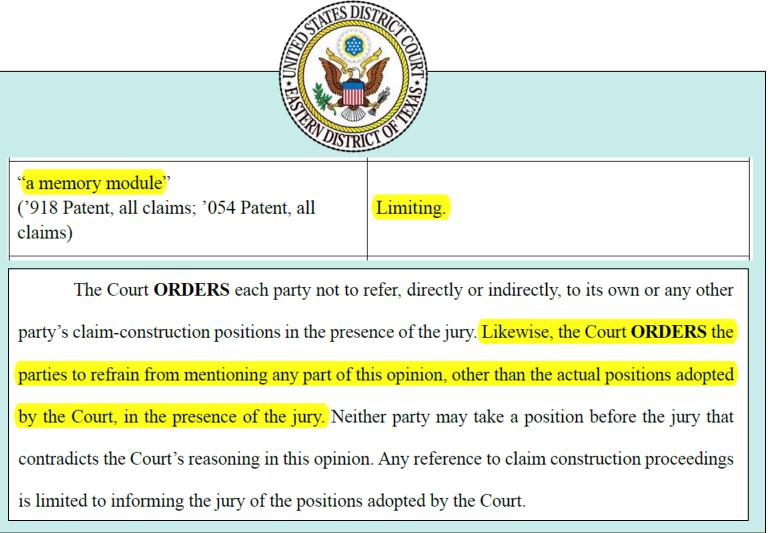

#### UNITED STATES PATENT AND TRADEMARK OFFICE

#### **BEFORE THE PATENT TRIAL AND APPEAL BOARD**

SAMSUNG ELECTRONICS CO., LTD., MICRON TECHNOLOGY, INC., MICRON SEMICONDUCTOR PRODUCTS, INC., and MICRON TECHNOLOGY TEXAS LLC,<sup>†</sup>

Petitioner,

v.

NETLIST, INC.,

Patent Owner

IPR2022-00996 Patent 11,016,918 B2

#### **EXHIBIT 1079:**

#### Petitioner's Demonstratives for Oral Argument on September 11, 2023

<sup>&</sup>lt;sup>†</sup> Micron Technology, Inc., Micron Semiconductor Products, Inc., and Micron Technology Texas LLC filed a motion for joinder and a petition in IPR2023-00406 and have been joined as petitioners in this proceeding.

#### Petitioner Samsung Electronics Co., Ltd.'s Oral Argument for PTAB Hearing

Samsung Electronics Co., Ltd. v. Netlist, Inc., IPR2022-00996 and IPR2022-00999 (U.S. Patent Nos. 11,016,918 and 11,232,054) September 11, 2023

#### **Table of Contents**

#### **Overview of the Patents and Grounds**

02

#### **Grounds 1-3 involving Harris**

**Petitioner's Motion to Exclude**

03

**Grounds 4-5 involving Spiers**

# OVERVIEW 01

#### OVERVIEW OF '918 AND '054 PATENTS, AND INSTITUTED GROUNDS

DEMONSTRATIVE EXHIBIT - NOT EVIDENCE

# '918 AND '054 PATENTS

DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

#### '918 Patent

| (12) United States Patent                                                                                                                                                                                                                                                                                                                           | (10) Patent No.: US 11,01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6,918 B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chen et al.                                                                                                                                                                                                                                                                                                                                         | (45) Date of Patent: Ma                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | y 25, 2021                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <ul> <li>(54) FLASH-DRAM HYBRID MEMORY MODULE</li> <li>(71) Applicant: Netlist, Inc., Irvine, CA (US)</li> <li>(72) Inventors: Chi-She Chen, Walnut, CA (US);<br/>Jeffrey C. Solomon, Irvine, CA (US);<br/>Scott H. Milton, Irvine, CA (US);<br/>Jayesh Bhakta, Cerritos, CA (US)</li> <li>(73) Assignee: Netlist, Inc., Irvine, CA (US)</li> </ul> | <ul> <li>Related U.S. Application Data</li> <li>No. 14/840,865, filed on Aug. 31, 2015, now Pat. No. 9,928,186, which is a continuation of application No. 14/489,269, filed on Sep. 17, 2014, now Pat. No. 9,158,684, which is a continuation of application No. 13/559,476, filed on Jul. 26, 2012, now Pat. No. 8,874,831, which is a continuation-in-part of application No. 12/240,916, filed on Sep. 29, 2008, now Pat. No. 8,301,833, which is a continuation of application No. 12/131,873, filed on Jun. 2, 2008, now abandoned.</li> <li>(60) Provisional application No. 60/941,586, filed on Jun. 1, 2007, provisional application No. 61/512,871, filed on Jul. 28, 2011.</li> </ul> | 1. A memory module comprising:<br>a printed circuit board (BCB) having an interface configured to fit not a<br>corresponding slot connector of a host system, the interface including a plurality of edge<br>connections configured to couple power, data, address and control signals between the<br>memory module and the host system;<br>a first buck converter configured to provide a first regulated voltage<br>having a first voltage amplitude;<br>a second buck converter configured to provide a second regulated<br>voltage having a second voltage amplitude; |

a third buck converter configured to provide a third regulated voltage having a third voltage amplitude;

a converter circuit configured to provide a fourth regulated voltage having a fourth voltage amplitude; and

a plurality of components coupled to the PCB, each component of the plurality of components coupled to one or more regulated voltages of the first, second, third and fourth regulated voltages, the plurality of components comprising:

a plurality of synchronous dynamic random access memory (SDRAM) devices coupled to the first regulated voltage, and

[1] at least one circuit coupled between a first portion of the plurality of edge connections and the plurality of SDRAM devices,

[2] the at least one circuit operable to (i) receive a first plurality of address and control signals via the first portion of the plurality of edge connections, and (ii) output a second plurality of address and control signals to the plurality of SDRAM devices,

[3] the at least one circuit coupled to both the second regulated voltage and the fourth regulated voltage,

[4] wherein a first one of the second and fourth voltage amplitudes is less than a second one of the second and fourth voltage amplitudes.

**BAKER BOTTS**

#### '054 Patent

| (12) United States Patent<br>Chen et al.                                               | <ul> <li>(10) Patent No.: US 11,232,054 B2</li> <li>(45) Date of Patent: *Jan. 25, 2022</li> </ul>                                                                  |                            |  |  |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|

|                                                                                        | Related U.S. Application Data                                                                                                                                       |                            |  |  |

| (54) FLASH-DRAM HYBRID MEMORY MODULE                                                   | (63) Continuation of application No. 17/138,766, filed on<br>Dec. 30, 2020, now Pat. No. 11,016,918, which is a                                                     |                            |  |  |

| (71) Applicant: Netlist, Inc., Irvine, CA (US)                                         | continuation of application No. 15/934,416, filed on<br>Mar. 23, 2018, now abandoned, which is a continu-<br>ation of application No. 14/840,865, filed on Aug. 31, | 1. A memory m              |  |  |

| (72) Inventors: Chi-She Chen, Walnut, CA (US);<br>Jeffrey C. Solomon, Irvine, CA (US); | 2015, now Pat. No. 9,928,186, which is a continu-<br>ation of application No. 14/489,269, filed on Sep. 17,<br>2014, now Pat. No. 9,158,684, which is a continu-    | corresponding              |  |  |

| Scott H. Milton, Irvine, CA (US);                                                      | ation of application No. 13/559,476, filed on Jul. 26, 2012, now Pat. No. 8,874,831, which is a continu-                                                            | edge connectio             |  |  |

| Jayesh Bhakta, Cerritos, CA (US)                                                       | ation-in-part of application No. 12/240,916, filed on<br>Sep. 29, 2008, now Pat. No. 8,301,833, which is a                                                          | between the m              |  |  |

| (73) Assignee: NETLIST, INC., Irvine, CA (US)                                          | continuation of application No. 12/131,873, filed on Jun. 2, 2008, now abandoned.                                                                                   |                            |  |  |

|                                                                                        |                                                                                                                                                                     | provide <b>at lea</b> s    |  |  |

|                                                                                        |                                                                                                                                                                     | in alu al a a <b>at</b> la |  |  |

1. A memory module comprising:

a printed circuit board (PCB) having an interface configured to fit into a corresponding slot connector of a host system, the interface including a plurality of edge connections configured to couple power, data, address and control signals between the memory module and the host system;

a voltage conversion circuit coupled to the PCB and configured to provide **at least three regulated voltages**, wherein the voltage conversion circuit includes **at least three buck converters** each of which is configured to produce a regulated voltage of the **at least three regulated voltages**;

[1] a plurality of components coupled to the PCB, each component of the plurality of components coupled to at least one regulated voltage of the at least three regulated voltages,

[2] the plurality of components including a plurality of synchronous dynamic random access memory (SDRAM) devices and

[3] a first circuit that is coupled to the plurality of SDRAM devices and to a first set of edge connections of the plurality of edge connections,

[4] wherein the first circuit is coupled to first and second regulated voltages of the at least three regulated voltages, and

[5] wherein the plurality of SDRAM devices are coupled to the first regulated voltage of the at least three regulated voltages.

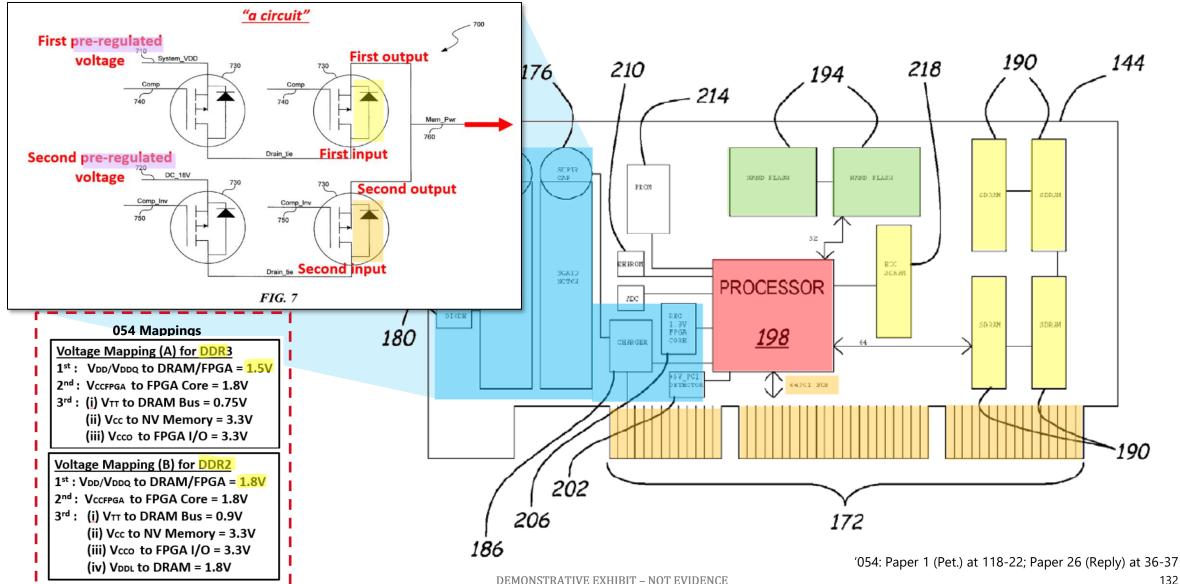

054: EX1001 ('054 Patent) at Claim 1

#### '918 and '054 Patent Overview

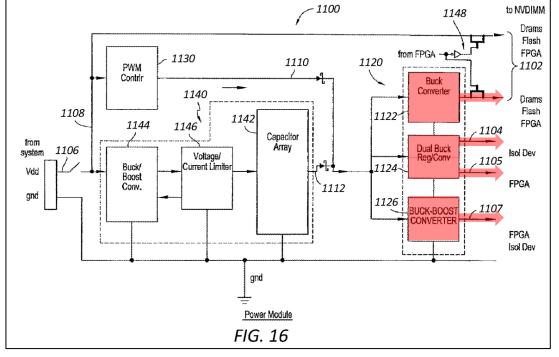

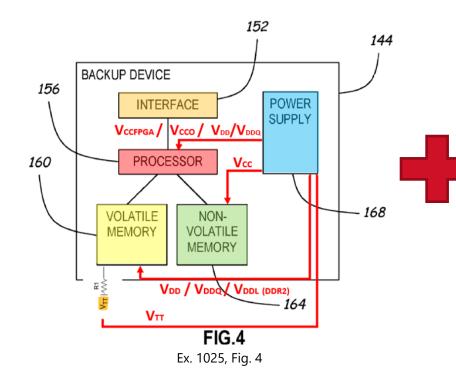

FIG. 12 is a block diagram of an example memory system 1010 compatible with certain embodiments described 15 herein. The memory system 1010 can be coupled to a host computer system and can include a volatile memory subsystem 1030, a non-volatile memory subsystem 1040, and a controller 1062 operatively coupled to the non-volatile memory subsystem 1040. In certain embodiments, the 20 memory system 1010 includes at least one circuit 1052 configured to selectively operatively decouple the controller 1062 from the volatile memory subsystem 1030.

Power may be supplied to the volatile memory subsystem **1030** from a first power supply (e.g., a system power supply) 55 when the memory system **1010** is in the first state and from a second power supply **1080** when the memory system **1010** is in the second state.

For example, the interface 1022 can comprise a plurality of edge connections which fit into a corresponding slot connector of the host system. The interface 1022 of certain embodiments provides a conduit for power voltage as well as data, address, and control signals between the memory system 1010 and the host system.

'918: EX1001 (918 Patent) at Fig. 12, 21:14-23, 25:54-58, 22:1-6; Paper 1 (Pet.) at 5-7; EX1003 at ¶¶68-81 '054: EX1001 (054 Patent) at Fig. 12, 21:14-23, 25:54-58, 22:1-6; Paper 1 (Pet.) at 4-6; EX1003 at ¶¶62-75

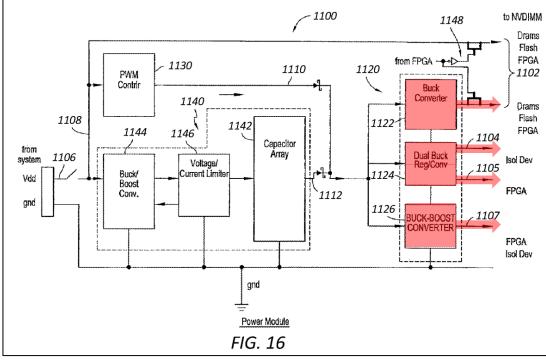

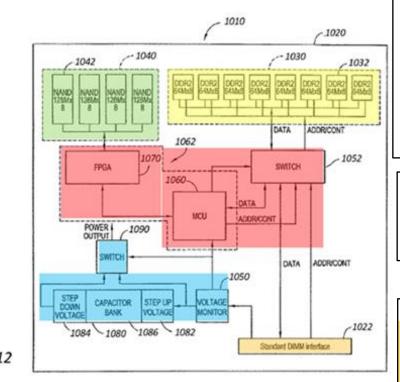

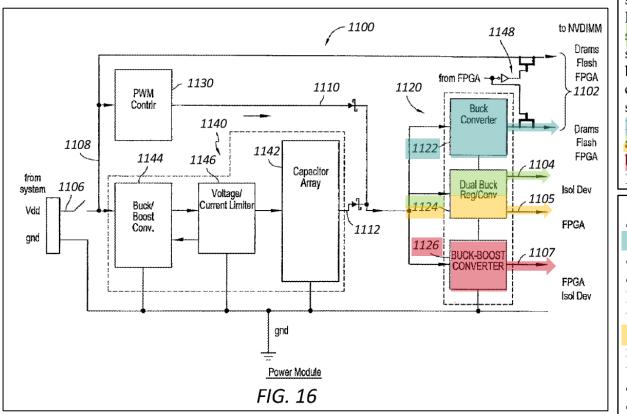

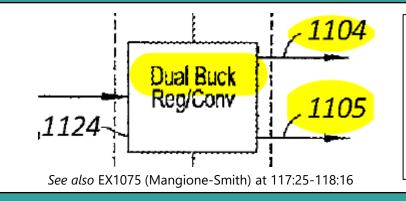

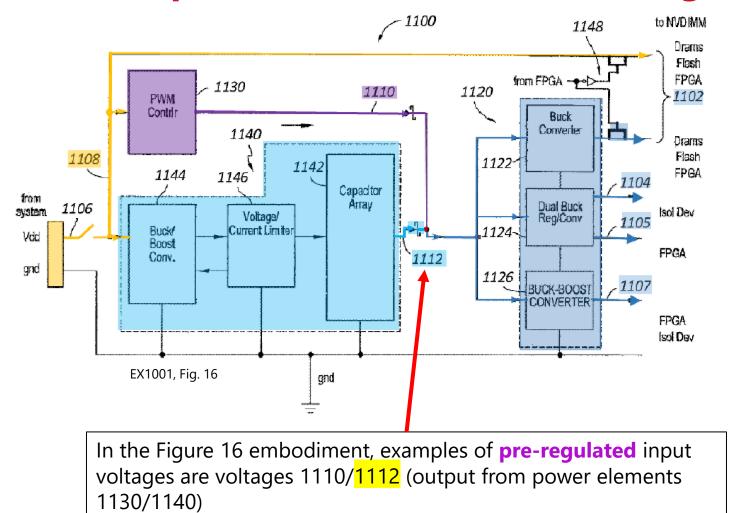

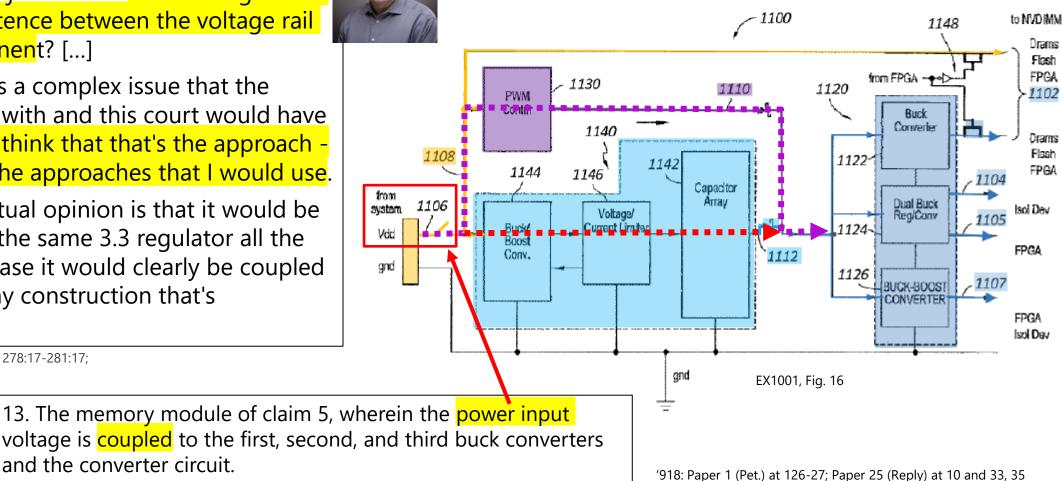

#### '918 and '054 Patent Overview

The conversion element 1120 can comprise one or more buck converters and/or one or more buck-boost converters. The conversion element 1120 may comprise a plurality of sub-blocks 1122, 1124, 1126 as schematically illustrated by FIG. 16, which can provide more voltages in addition to the second voltage 1104 to the memory system 1010. The sub-blocks may comprise various converter circuits such as buck-converters, boost converters, and buck-boost converter circuits for providing various voltage values to the memory system 1010. For example, in one embodiment, sub-block 1122 comprises a buck converter, sub-block 1124 comprises a dual buck converter, and sub-block 1126 comprises a buck-boost converter as schematically illustrated by FIG. 16.

#### For

example, the buck-converter of sub-block **1122** can provide 1.8V at 2A for about 60 seconds to the volatile memory elements 1032 (e.g., DRAM), the non-volatile memory elements 1042 (e.g., flash), and the controller 1062 (e.g., an FPGA) in one embodiment. The sub-block 1124 can provide the second voltage 1104 as well as another reduced voltage 1105 to the memory system 1010. In one example embodiment, the second voltage 1104 is 2.5V and is used to power the at least one circuit 1052 (e.g., isolation device) and the other reduced voltage 1105 is 1.2V and is used to power the controller 1062 (e.g., FPGA). The subblock 1126 can provide yet another voltage 1107 to the memory system 1010. For example, the voltage 1107 may be 3.3V and may be used to power both the controller 1062 and the at least one circuit 1052.

'918: EX1001 at Fig. 16, 29:18-31, 29: 39-54; Paper 1 (Pet.) at 5-7; EX1003 at ¶¶68-81 '054: EX1001 at Fig. 16, 29:18-31, 29:39-54; Paper 1 (Pet.) at 4-6; EX1003 at \$\$ DEMONSTRATIVE EXHIBIT - NOT EVIDENCE

8

# INSTITUTED GROUNDS & PRIOR ART

DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

#### **Instituted Grounds**

| Grounds         | '918 Claims '054 Claims                     |             | Prior art                        |

|-----------------|---------------------------------------------|-------------|----------------------------------|

| 1               | Claims 1-3, 8, 14-<br>15, 23 Claims 1-3, 15 |             | <i>Harris</i> + FBDIMM Standards |

| 2               | 2 Claims 1-30 Cla                           |             | Ground 1 + Amidi                 |

| 3               | Claims 1-30                                 | Claims 1-30 | Ground 2 + Hajeck                |

| 4               | Claims 1-30                                 | Claims 1-30 | <b>Spiers</b> + Amidi            |

| 5 Claims 1-30 C |                                             | Claims 1-30 | Ground 4 + Hajeck                |

# Prior Art: Harris (U.S. Patent Pub. No. 2006/0174140) [EX1023] (19) United States (12) Patent Application Publication Harris et al. (10) Pub. No.: US 2006/0174140 A1 (43) Pub. Date: Aug. 3, 2006

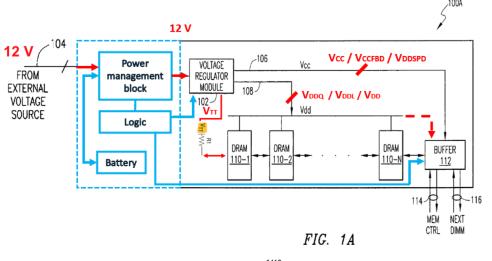

-106

108-

DRAM

110 - 1

Vcc

Vdd

FIG. 1A

DRAM

110-N

DRAM

110 - 2

VOLTAGE

REGULATOR

102

MODULE

104

FROM

EXTERNAL

VOLTAGE

SOURCE

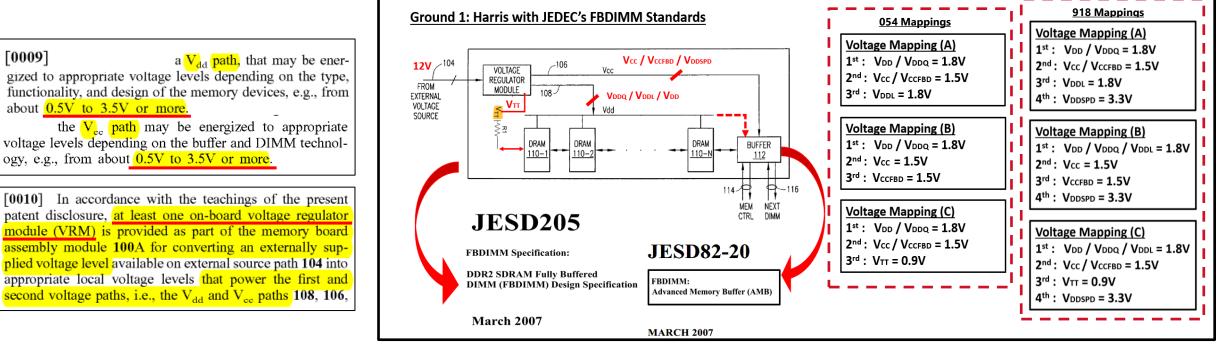

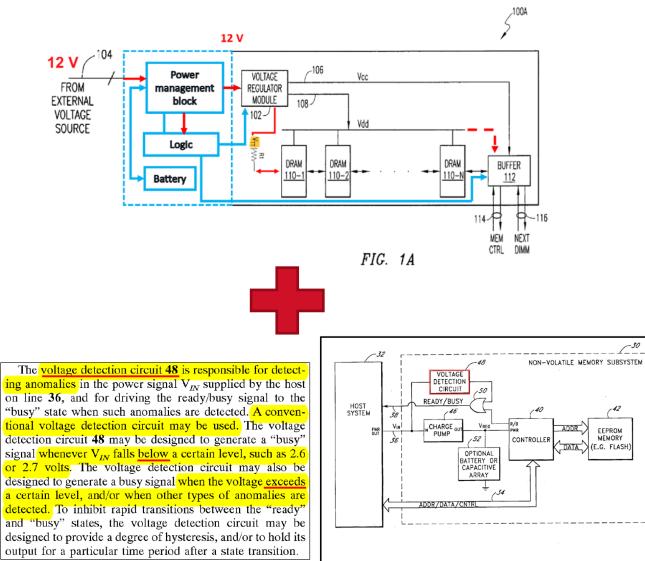

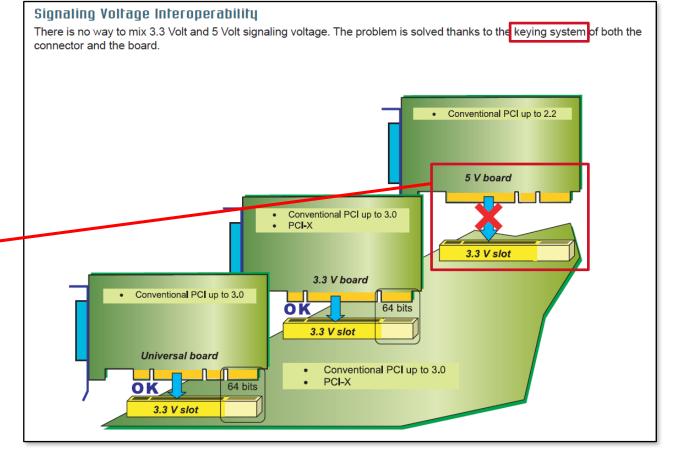

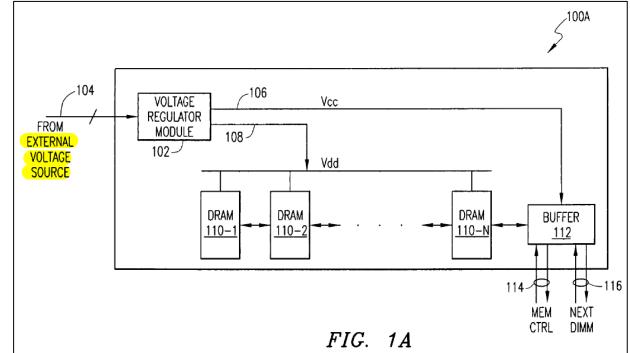

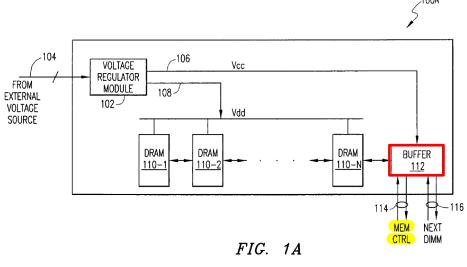

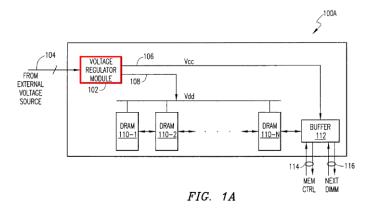

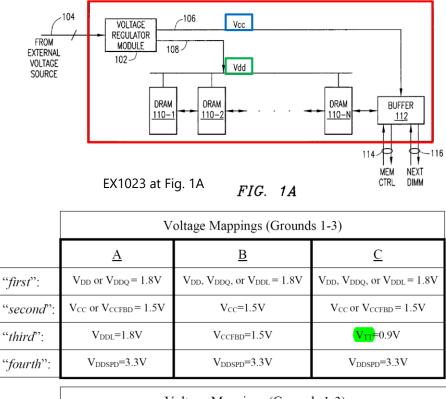

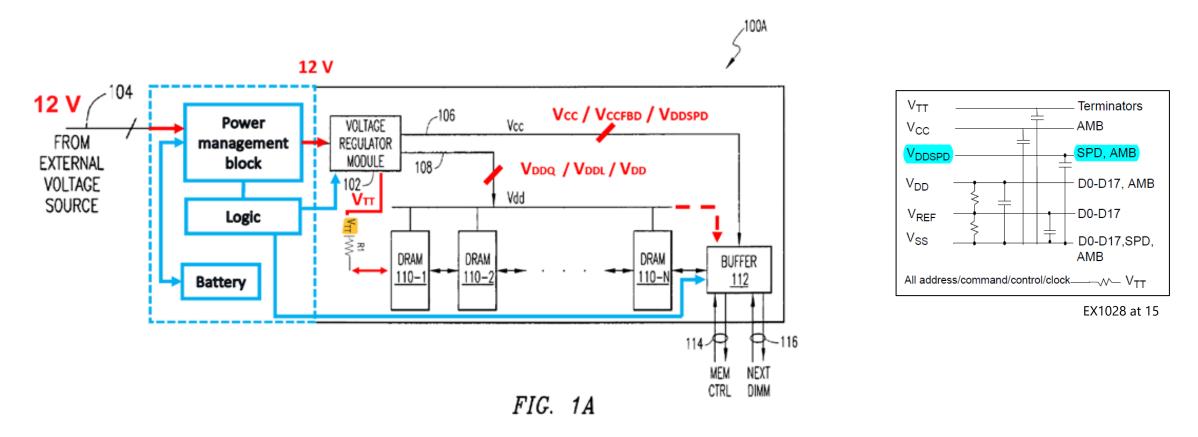

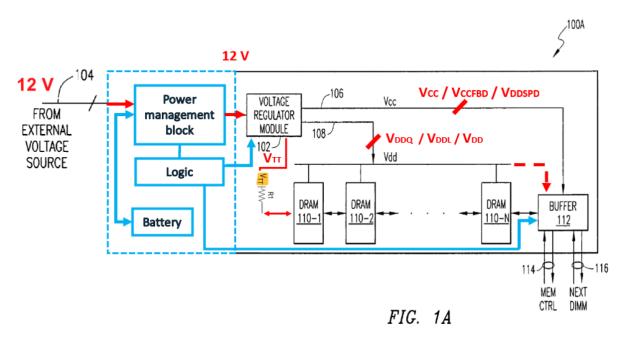

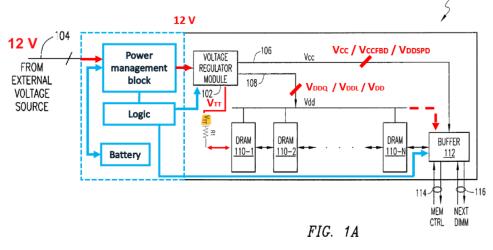

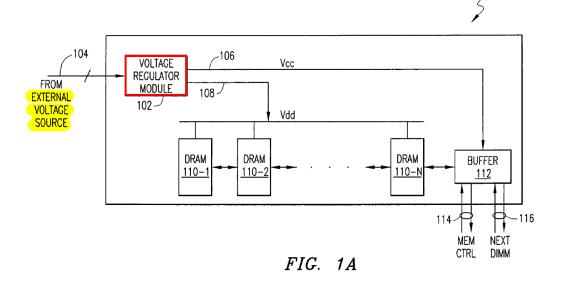

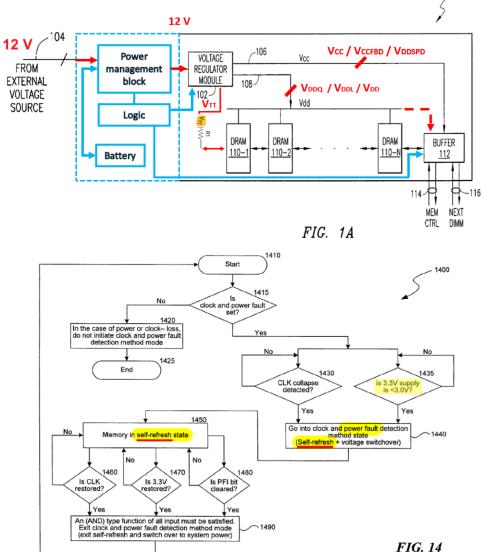

[0002]To cope with power requirements, industry standard memory modules, e.g., Dual In-line Memory Modules (DIMMS) populated with dynamic random access memory (DRAM) devices, are provided with power supply rails (on a relatively large number of pins) that are powered from system board or main board voltage sources, and are specific to the memory technology.

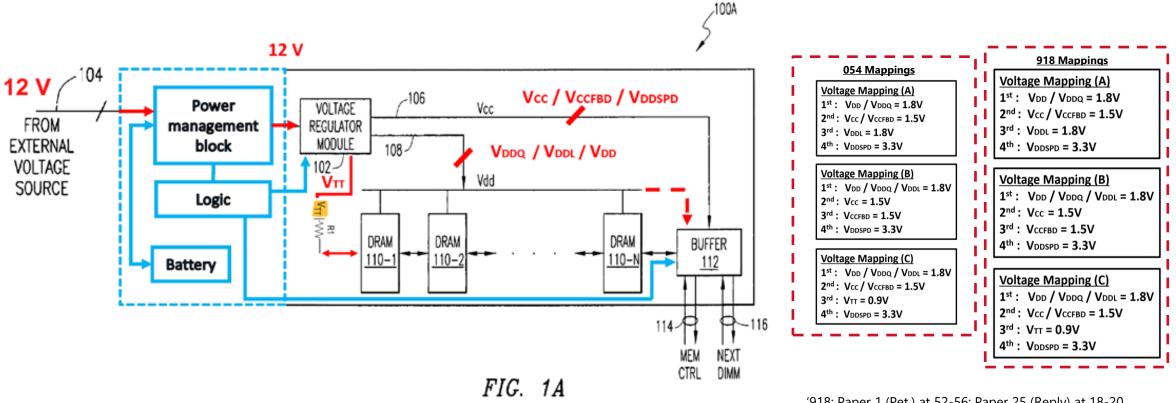

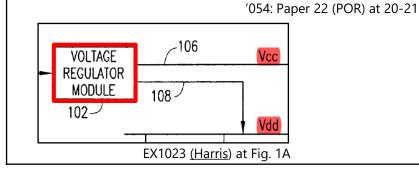

[0010] In accordance with the teachings of the present patent disclosure, at least one on-board voltage regulator module (VRM) is provided as part of the memory board assembly module 100A for converting an externally supplied voltage level available on external source path 104 into appropriate local voltage levels that power the first and second voltage paths, i.e., the  $V_{dd}$  and  $V_{cc}$  paths 108, 106,

[0012] By way of example, a standard FBD module requires  $28 V_{dd}$  pins (for DRAM devices) and  $8 V_{ee}$  pins (for buffer and logic) and associated Ground returns, resulting in a total of 72 pins that provide a power supply interface for up to two x4 DRAM ranks (36 devices) and buffer logic. A voltage-independent FBD design incorporating the embodiment of **FIG. 1A** is capable of replacing these power supply interface pins with as few as six +12V pins (from an external voltage source), with local conversion to  $V_{dd}$  (to DRAM) and  $V_{ee}$  (to buffer/logic) being added. Alternatively, using

[0014] It should be readily recognized that the external voltage sources may comprise any combination of known or heretofore unknown voltage supplies, either regulated or unregulated, and even including variable voltages.

EX1023 (Harris) '918: Paper 1 (Pet.) at 10; Paper 25 (Reply) at 2-7 '054: Paper 1 (Pet.) at 9-10; Paper 26 (Reply) at 2-8

about 0.5V to 3.5V or more.

Jan. 31, 2005

gized to appropriate voltage levels depending on the type,

functionality, and design of the memory devices, e.g., from

voltage levels depending on the buffer and DIMM technol-

ogy, e.g., from about 0.5V to 3.5V or more.

the V<sub>cc</sub> path may be energized to appropriate

Filed:

BUFFER

112

**4**-116

NEXT

DIMM

Þ

CTRI

114

[0009]

11

a  $V_{dd}$  path, that may be ener-

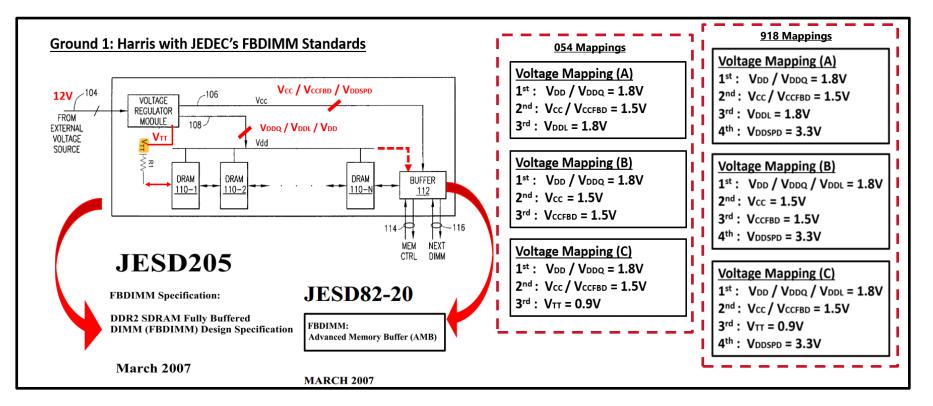

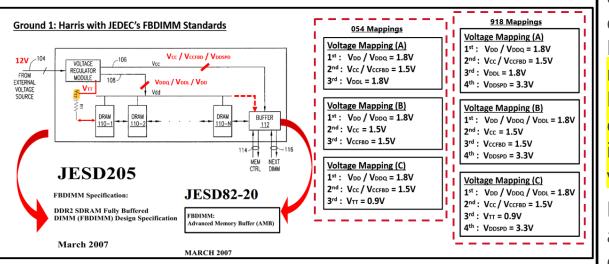

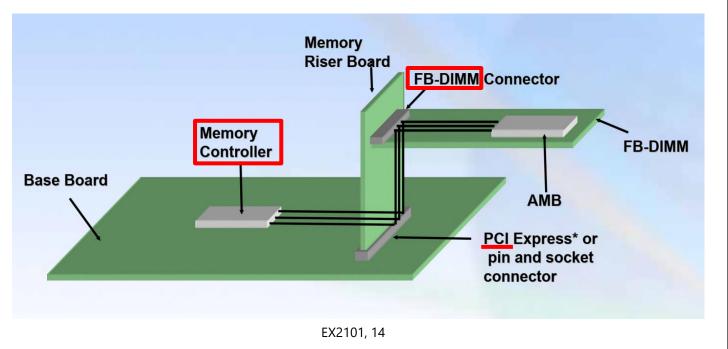

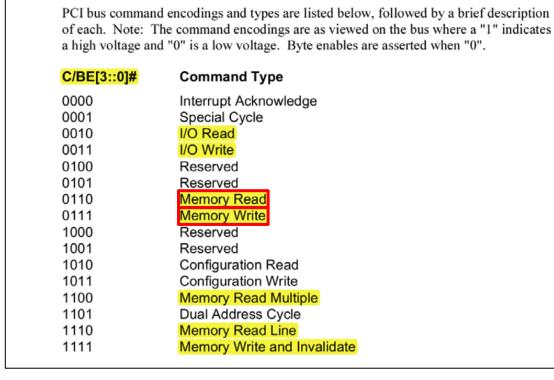

### Prior Art: FBDIMM Standards [EX1027, EX1028]

| Exhibit           |                                                                            | Description                                                                                  | Exemplary Teachings                                                          |                       |                                 |                       | hings                                                                                  |                                                                                     |

|-------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------|---------------------------------|-----------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| JEDEC<br>STANDARD |                                                                            | "JESD82-20" – FBDIMM:<br>Advanced Memory Buffer<br>(AMB) standard, published in              | Voltages for the "AMB buffer" on the FBDIMM memory module:<br>Power Supplies |                       |                                 |                       |                                                                                        |                                                                                     |

|                   | FBDIMM:<br>Advanced Memory Buffer (AMB)                                    | March of 2007 by JEDEC                                                                       | VCC (24 pins)                                                                | А                     | 1.5V nominal supply for core IO |                       |                                                                                        |                                                                                     |

| EX1027            |                                                                            | , , , , , , , , , , , , , , , , , , ,                                                        | VCCFBD (8 pins)                                                              | А                     | 1.5V nominal                    |                       |                                                                                        | eed IO                                                                              |

| EXIU21            | JESD82-20<br>JESD82-20<br>MAKETBE<br>RECOLD STATE HERIOGOOD ASSOCIATION    |                                                                                              | VDD (24 pins)                                                                | A                     | <mark>1.8V</mark> nominal       | supply for I          | DDR IO                                                                                 |                                                                                     |

|                   |                                                                            |                                                                                              | VSS (156 pins)                                                               |                       | Ground                          | 1.6.4                 |                                                                                        |                                                                                     |

|                   |                                                                            |                                                                                              | VDDSPD                                                                       | А                     | 3.3V nominal                    | supply for S          | SMB receiver                                                                           | rs and ESD diodes                                                                   |

|                   | JEDEC ZELA                                                                 |                                                                                              |                                                                              |                       |                                 |                       |                                                                                        | EX1027 at p. 83                                                                     |

| JEDEC             |                                                                            | "JESD205" – DDR2 SDRAM                                                                       | Voltages for other components on the FBDIMM memory module:                   |                       |                                 |                       |                                                                                        |                                                                                     |

|                   | STANDARD                                                                   | Fully Buffered DIMM (FBDIMM)<br>Design Specification, published<br>in March of 2007 by JEDEC |                                                                              |                       | min                             | typ                   | max                                                                                    |                                                                                     |

|                   | FBDIMM Specification:                                                      |                                                                                              |                                                                              |                       | 1.7                             | <mark>1.8</mark>      | 1.9                                                                                    | (DRAM <mark>V<sub>DD</sub>V<sub>DDQ</sub>,</mark> AMB <mark>V<sub>DDQ</sub>)</mark> |

| EX1028            | DR22 SDRAM Fully Buffered<br>DIMM (FBDIMM) Design Specification<br>JESD205 |                                                                                              | Supply voltages (nominal)                                                    | 1.455 <sup>1</sup>    | <mark>1.5</mark>                | 1.575 <sup>1</sup>    | (AMB <mark>V<sub>CC</sub>/V<sub>CCFBD</sub>)</mark>                                    |                                                                                     |

|                   |                                                                            |                                                                                              | .,                                                                           | 0.453*V <sub>DD</sub> | 0.5*V <sub>DD</sub>             | 0.547*V <sub>DD</sub> | (DRAM Interface V <sub>TT</sub> )<br>This supply should track as 0.5 * 1.8 volt supply |                                                                                     |

|                   | JEDEC SOLID STATE TECHNOLOGY ASSOCIATION                                   |                                                                                              |                                                                              |                       | 3.0                             | <mark>3.3</mark>      | 3.6                                                                                    |                                                                                     |

|                   | JEDEC ZELA                                                                 |                                                                                              |                                                                              |                       | 1                               |                       |                                                                                        | EX1028 at p. 9                                                                      |

EX1027-EX1028 (FBDIMM Standards)

'918: Paper 1 (Pet.) at 11; Paper 25 (Reply) at 9, 15-16, 19 '054: Paper 1 (Pet.) at 10-11; Paper 26 (Reply) at 10, 16-17, 20

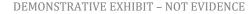

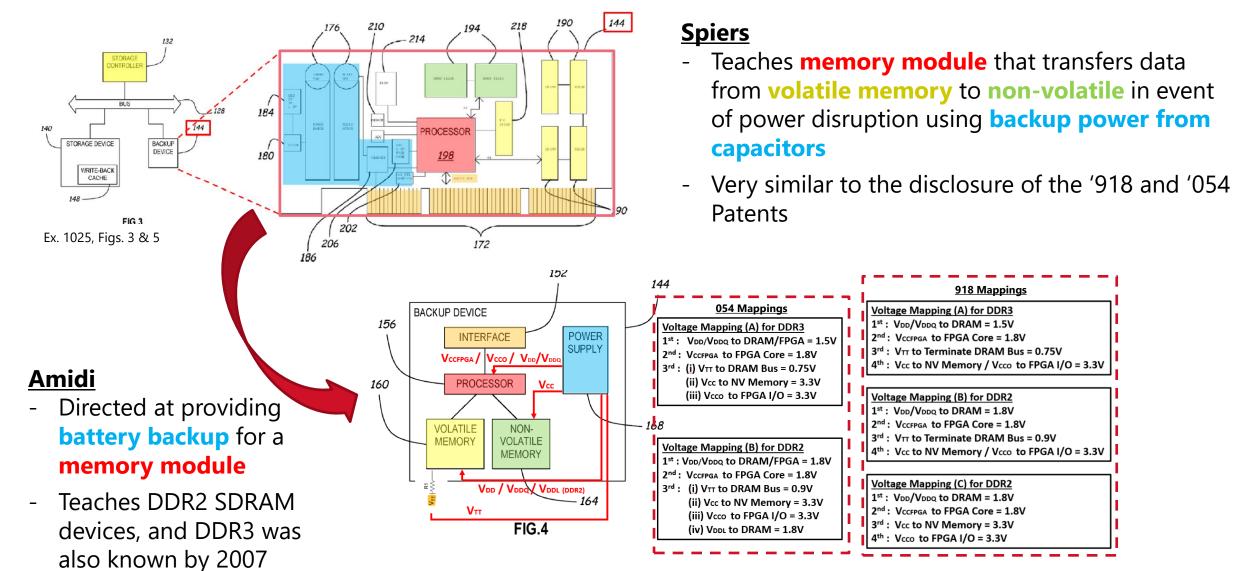

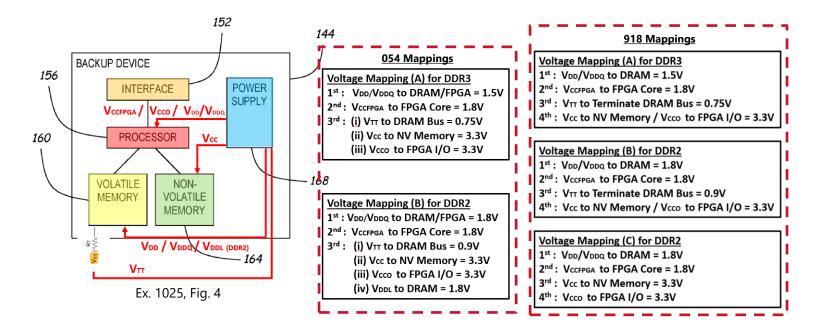

## Prior Art: <u>Amidi</u> (U.S. Patent No. 7,724,604) [EX1024]

(12) United States Patent Amidi et al.

US 7,724,604 B2 May 25, 2010

DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

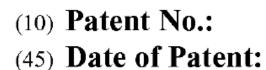

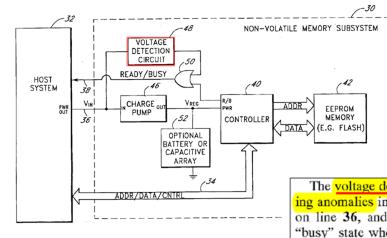

## Prior Art: <u>Hajeck</u> (U.S. Patent No. 6,856,556) [EX1038]

(12) United States Patent Hajeck

(10) Patent No.: US 6,856,556 B1

(45) Date of Patent: Feb. 15, 2005

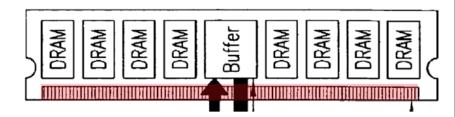

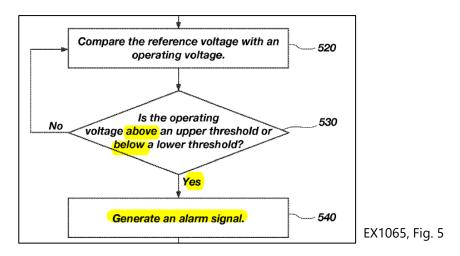

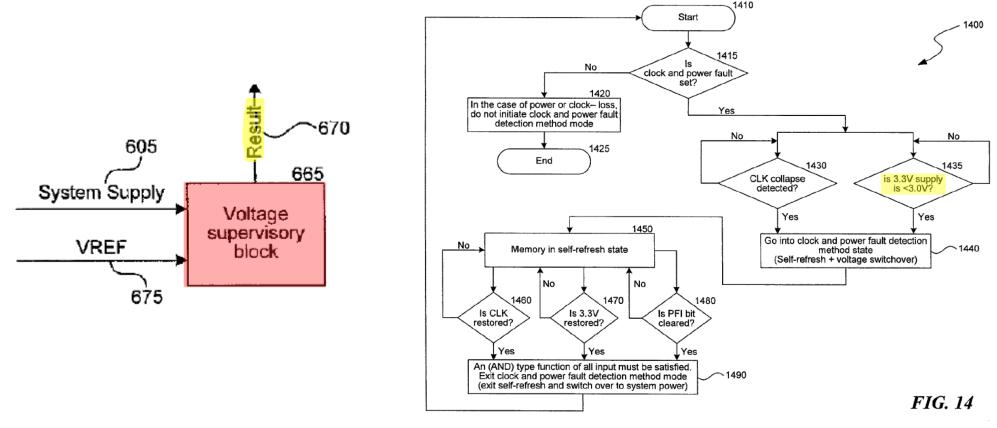

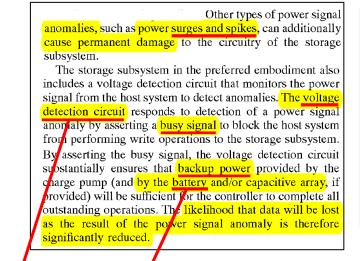

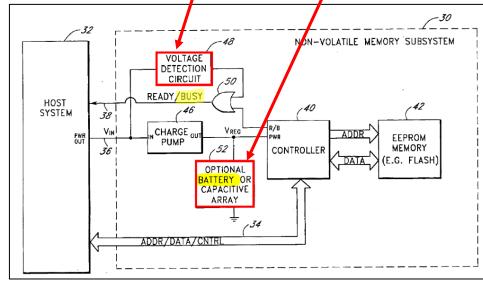

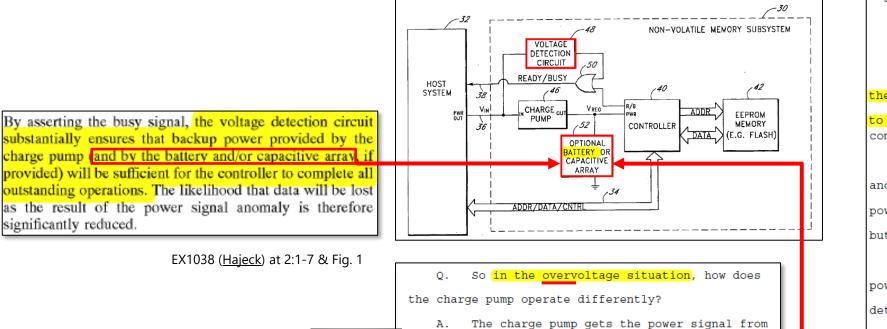

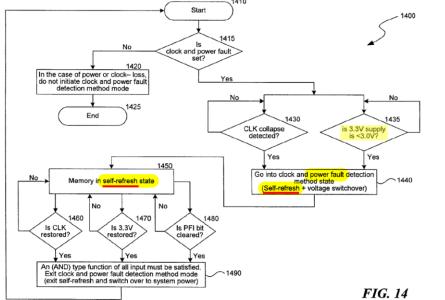

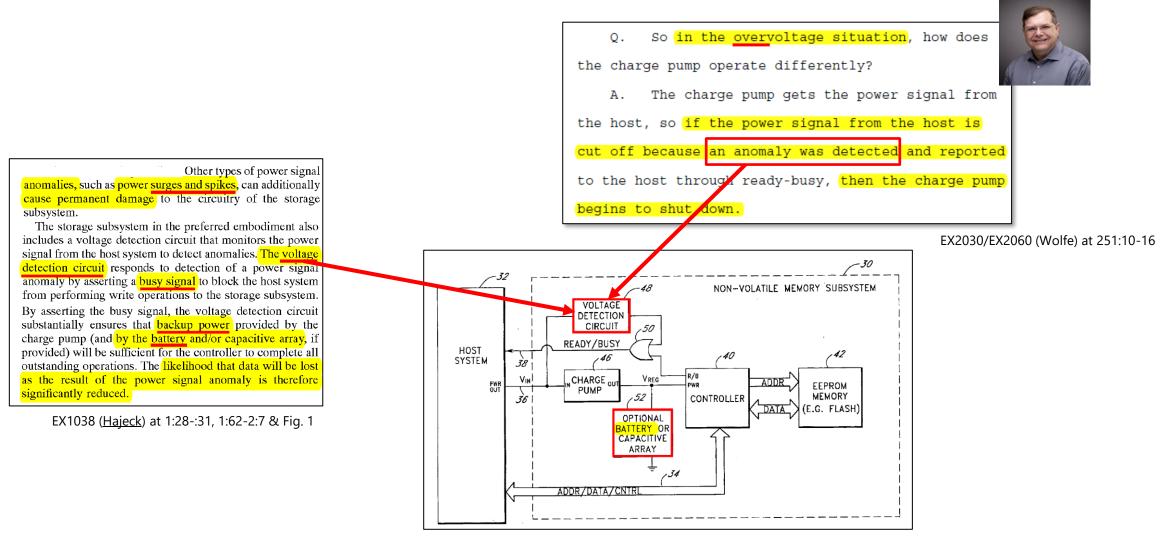

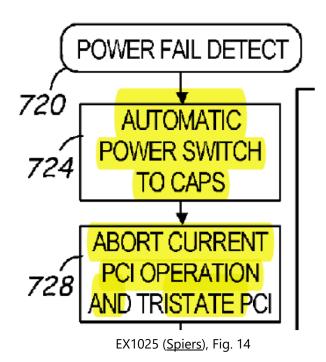

The voltage detection circuit **48** is responsible for detecting anomalies in the power signal  $V_{IN}$  supplied by the host on line **36**, and for driving the ready/busy signal to the "busy" state when such anomalies are detected. A conventional voltage detection circuit may be used. The voltage detection circuit **48** may be designed to generate a "busy" signal whenever  $V_{IN}$  falls <u>below</u> a certain level, such as 2.6 or 2.7 volts. The voltage detection circuit may also be designed to generate a busy signal when the voltage <u>exceeds</u> a certain level, and/or when other types of anomalies are detected. To inhibit rapid transitions between the "ready" and "busy" states, the voltage detection circuit may be designed to provide a degree of hysteresis, and/or to hold its output for a particular time period after a state transition.

EX1038 (Hajeck), 3:30-:43 & Fig. 1

'918: Paper 1 (Pet.) at 12-13; Paper 25 (Reply) at 22, 35-37

'054: Paper (Pet.) at 12-13; Paper 26 (Reply) at 21-22, 35 14

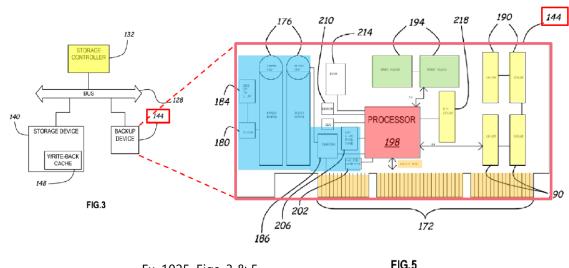

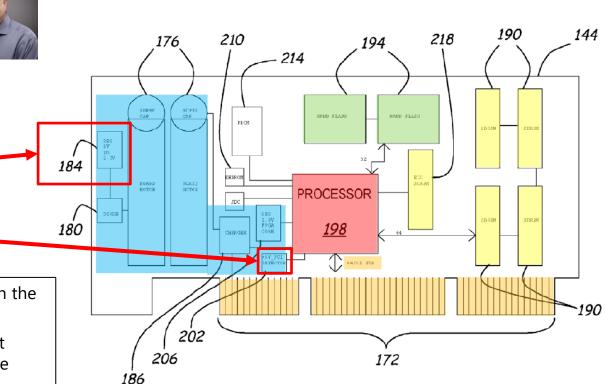

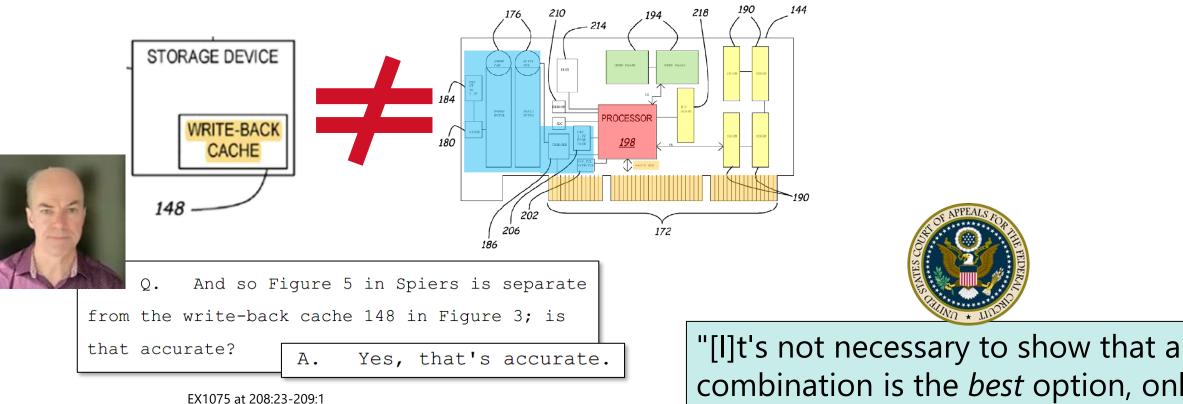

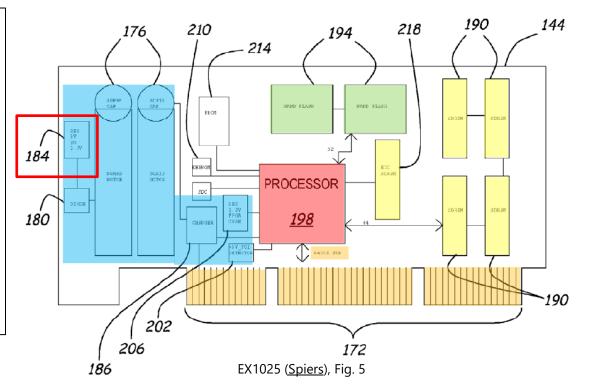

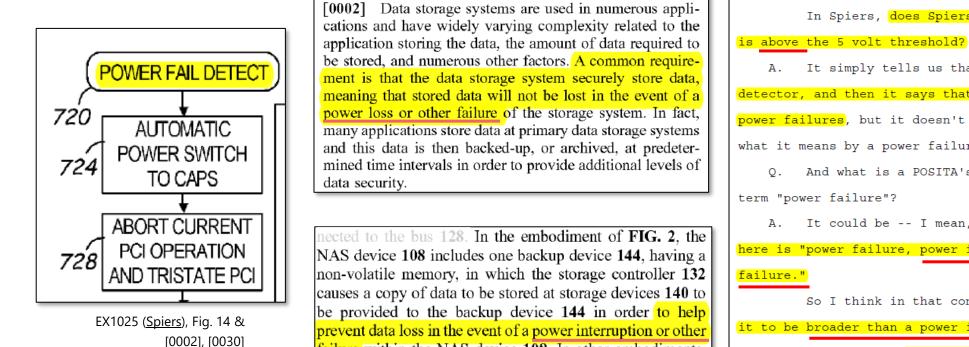

## Prior Art: <u>Spiers</u> (U.S. Patent Pub. No. 2006/0080515) [EX1025]

- (19) United States

- (12) Patent Application Publication (10) Pub. No.: US 2006/0080515 A1 Spiers et al. (43) Pub. Date: Apr. 13, 2006

# GROUNDS 1-3 (<u>HARRIS</u>) 02

DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

# SUMMARY OF COMBINATIONS

DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

## **Ground 1: <u>Harris</u> + <u>JEDEC's FBDIMM Standards</u>**

#### <u>Harris</u>

- One or more Voltage Regulator Modules <u>on the</u> <u>memory module</u> with buck converters to convert from 12V to lower voltages for various components

- Memory module can be "Fully buffered DIMM" (i.e., FBDIMM)

#### **FBDIMM Standards**

Specify particular voltages for various components on an FBDIMM

'918: Paper 1 (Pet.) at 14-19 '054: Paper 1 (Pet.) at 14-19

## **Ground 1:** <u>Harris</u> + <u>JEDEC's FBDIMM Standards</u>

"Where a prior art patent discloses a **range of values**, showing a claimed value falls within that range meets a party's burden of establishing the narrower claim would have been obvious where there is no reason to think the result would be unpredictable."

*Gen. Hosp. Corp. v. Sienna Biopharms., Inc.*, 888 F.3d 1368, 1373 (Fed. Cir. 2018); *see also, e.g., Iron Grip Barbell Co. v. USA Sports, Inc.*, 392 F.3d 1317, 1320-23 (Fed. Cir. 2004) (claim to three grips obvious in light of prior art teaching one, two, and four grips)

'918: Paper 1 (Pet.) at 27-28 '054: Paper 1 (Pet.) at 27

#### Ground 2: adds Amidi

#### <u>Amidi</u>

- Adds battery backup and "logic" for detecting power faults

- Also uses buck converters

'918: Paper 1 (Pet.) at 52-56; Paper 25 (Reply) at 18-20 '054: Paper 1 (Pet.) at 41-45; Paper 26 (Reply) at 19-21

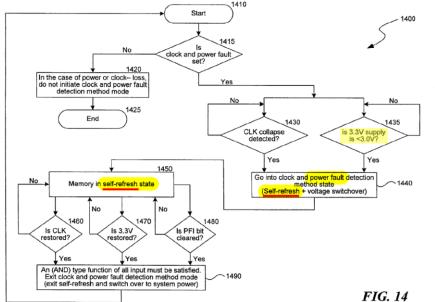

## **Ground 3: adds Hajeck**

#### **Hajeck**

- Teaches voltage detection circuit

- Specifically includes monitoring both overvoltage and undervoltage conditions

'918: Paper 1 (Pet.) at 12-13, 52-56, 75-76 '054: Paper 1 (Pet.) at 12-13, 41-45, 70-71

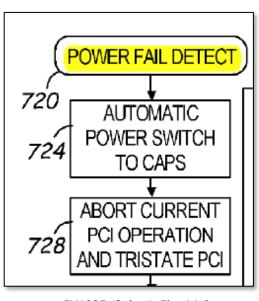

**FIG.1**

-30

EEPROM

MEMORY

# EDGE CONNECTIONS RECEIVE POWER FROM HOST

## GROUND 1 (<u>HARRIS</u> + <u>FBDIMM STANDARDS</u>)

DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

### The Institution Decision correctly found that Ground 1 teaches "edge connections configured to couple power...signals"

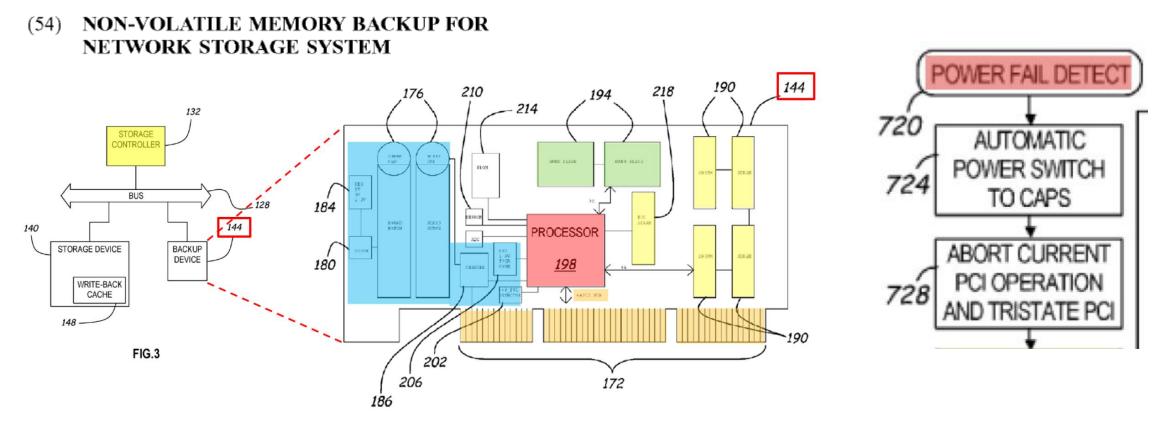

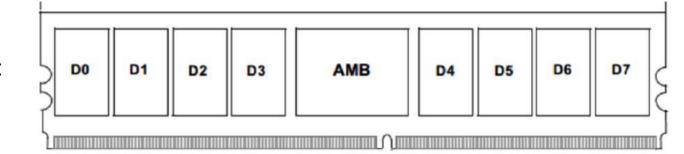

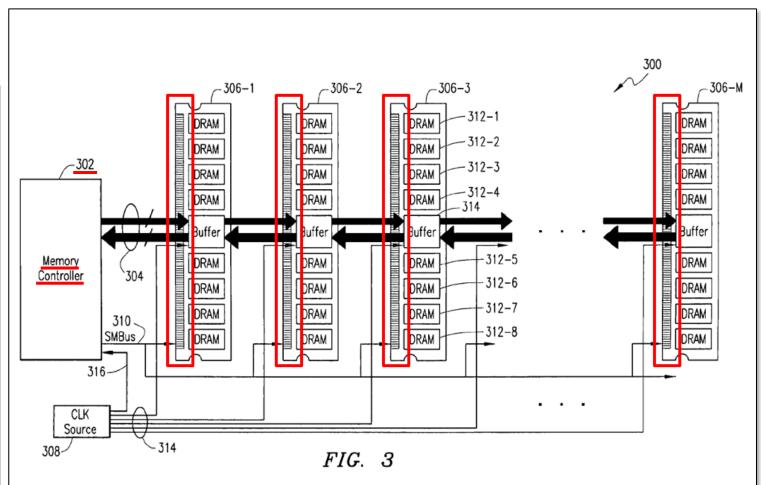

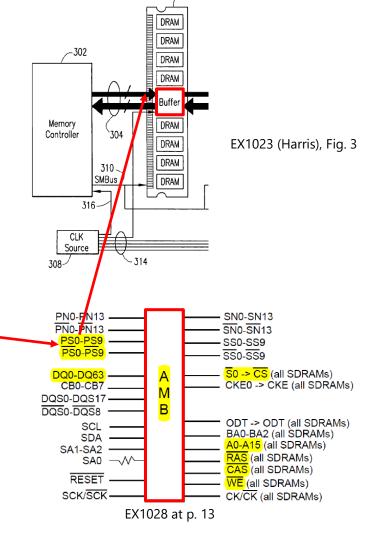

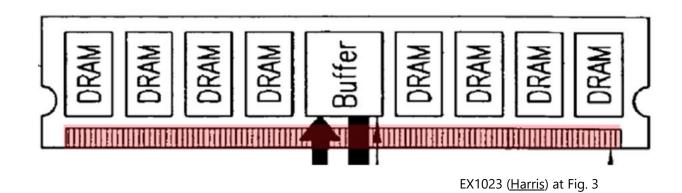

EX1023, Fig. 3

Patent Owner argues that Petitioner has not made a prima facie case that Harris discloses a memory module having a PCB interface that receives power from the host system. Prelim. Resp. 14-20. Harris states, however, that DRAM devices may be "powered from system board or main board voltage sources." Ex. 1023 ¶ 2. Harris also discloses that "external voltage sources" may comprise any combination of *known* or heretofore unknown voltage supplies, either regulated or unregulated, and even including variable voltages." Ex. 1023 ¶ 14 (emphasis added). Patent Owner does not argue that voltage supplied by a host system is not a "known" voltage supply as referenced by Harris. Furthermore, Petitioner indicates that the FBDIMM Standards show that the buffer AMB may be connected to a host, suggesting that the FBDIMM may derive its power from the host. Pet. 24 (showing figure at Ex. 1027, 4). These facts point to the conclusion that Harris's external voltage source may be the host system notwithstanding Patent Owner's arguments to the contrary.

# <u>Harris</u> teaches replacing standard "power supply interface pins" with <u>fewer</u> 12V pins

[0002]To cope with power requirements, industry standard memory modules, e.g., Dual In-line Memory Modules (DIMMS) populated with dynamic random access memory (DRAM) devices, are provided with power supply rails (on a relatively large number of pins) that are powered from system board or main board voltage sources, and are specific to the memory technology.

[0010] In accordance with the teachings of the present patent disclosure, at least one on-board voltage regulator module (VRM) is provided as part of the memory board assembly module 100A for converting an externally supplied voltage level available on external source path 104 into appropriate local voltage levels that power the first and second voltage paths, i.e., the  $V_{dd}$  and  $V_{ce}$  paths 108, 106,

**[0012]** By way of example, a standard FBD module requires 28  $V_{dd}$  pins (for DRAM devices) and 8  $V_{ee}$  pins (for buffer and logic) and associated Ground returns, resulting in a total of 72 pins that provide a power supply interface for up to two x4 DRAM ranks (36 devices) and buffer logic. A voltage-independent FBD design incorporating the embodiment of **FIG. 1A** is capable of replacing these power supply interface pins with as few as six +12V pins (from an external voltage source), with local conversion to  $V_{dd}$  (to DRAM) and  $V_{ee}$  (to buffer/logic) being added. Alternatively, using

[0014] It should be readily recognized that the external voltage sources may comprise any combination of known or heretofore unknown voltage supplies, either regulated or unregulated, and even including variable voltages.

24

#### Supplying power via edge connections was "standard"

You would agree that it's very common Q. for a memory module to receive power from the

edge connections along the bottom of the memory

module that plugs into the host system; right?

A. Yes, that is standard approach. But Harris directly, in my opinion, teaches against that.

EX1075 (Mangione-Smith) at 163:16-22

#### **FBDIMM**:

EX1028 (JEDEC's FBDIMM Standards), p.38

Harris (FBDIMM):

EX1023 (Harris) at Fig. 3

'918: Paper 1 (Pet.) at 16-21; Paper 25 (Reply) at 2-7 '054: Paper 1 (Pet.) at 16-21; Paper 26 (Reply) at 2-8

## **Harris** teaches supplying power from the host via edge connections

#### Q. And Figure 3 of Harris shows a memory controller <u>302</u> that's part of the host system; correct? A. Yes, that's correct.

EX1075 (Mangione-Smith) at 167:23-168:1

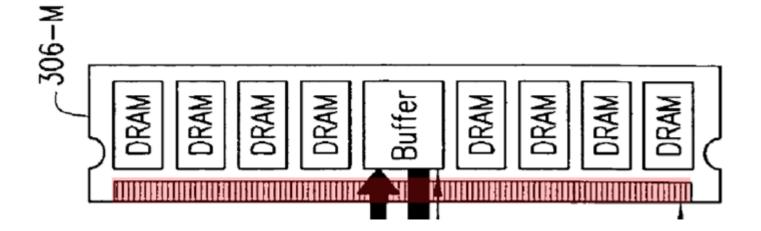

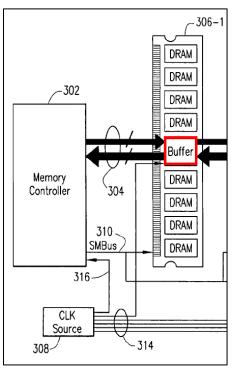

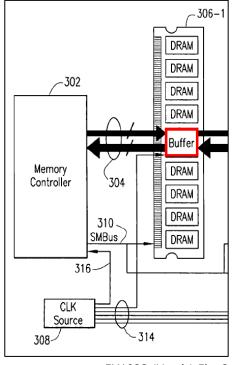

[0017] FIG. 3 is a block diagram of an exemplary memory assembly 300 according to one embodiment. A memory controller 302 is operable to drive a bidirectional memory link 304 to which a plurality of memory boards 306-1 through 306-M are coupled in a daisy-chain fashion at their respective buffers. As exemplified by the memory board **306-3**, each memory board includes eight DRAM devices 312-1 through 312-8, with a buffer component 314. A clock source 308 is operable to drive a plurality of clock signals to the memory boards via a clock bus 314. Additionally, the clock source 308 is also operable to drive a clock signal 316 to the memory controller 302 for providing a time base with respect to its operations. A system management bus (SM bus) 310 coupled to the memory boards 306-1 through **306**-M is driven by the memory controller **302**. Although not explicitly shown in this FIGURE, each memory board also receives a supply voltage that is locally converted by an on-board VRM for powering the DRAM and buffer components therein. In one arrangement, the supply voltage may be sourced from the memory controller 302 or from a separate voltage source.

EX1023 [0017], Fig. 3 (annotated)

## <u>Harris's reference to removing the "keyway" confirms industry</u> standard practice of supplying power using edge connections

[0013] It is contemplated that local supply voltage conversion for double-rank DIMMs can be accommodated with a form factor design of approximately about one square inch (both sides of the printed circuit board), and at a component height compatible with applicable Joint Electron Device Engineering Council (JEDEC) standards. Further, since the +12V power supply is not used directly by DRAM devices or buffer/logic components of the memory assembly, a wide tolerance (e.g., around +/-15%) can be accommodated, allowing low cost power distribution for system boards (such as, e.g., motherboards, cell boards, et cetera) wherein design requirements for bypass/hold-up capacitors may be relaxed or minimized. By way of an additional variation in implementation, the form factor associated with the memory assembly module 100A may be suitably modified (e.g., removing the board's connector keyway) so as to ensure that a memory assembly module embodying the teachings of the present disclosure is not interchangeable with the standard DIMM, thereby preventing any accidental damage.

EX1023 at [0013], Fig. 3

EX2016 at 6-7; see also EX2030/2060, 117:7-:21; EX2101, 21-22; EX1075, 171:21-175:20

'918: Paper 25 (Reply) at 5-6 '054: Paper 26 (Reply) at 6-7

#### Harris's "external" voltage just needs to be external to the module

Harris mentions external power source in, Ο. for example, Figure 1A; correct? External voltage source. Α. What is "external voltage source"? Ο. It's one that comes from off the DIMM. Α. So in your mind, a voltage source that comes Q. from the host is also an external voltage source? With respect to Harris' figures, I would Α. think that's correct. And so when Harris mentions external source Q. path 104, to you that just means a path to a voltage source that's off the DIMM; is that correct? Yes. Α.

EX1023 (Harris) at Fig. 1A

'918: Paper 21 (POR) at 5; Paper 25 (Reply) at 2-7 '054: Paper 22 (POR) at 7; Paper 26 (Reply) at 2-8

EX2030/EX2060 (Wolfe) at 66:7-19

#### <u>Harris's "external" voltage can come from the host computer</u>

1

| 22 | Are you aware of any computer systems at the 13:03         |

|----|------------------------------------------------------------|

| 23 | time of the invention that are suitable for use with 13:04 |

| 24 | FB-DIMM that provides unregulated supply voltages 13:04    |

| 25 | for the memory systems? 13:04                              |

| 1  | A. The one described in Harris. 13:04                      |

| 2  | Q. So you're assuming that the power supply for 13:04      |

| з  | Harris FB-DIMM comes from the host system; correct? 13:04  |

| 4  | MR. CHANDLER: Objection. Form. 13:04                       |

| 5  | THE WITNESS: I think a person of ordinary 13:04            |

| 6  | skill would generally assume that the external 13:05       |

| 7  | voltage source 104 comes from the host computer. 13:05     |

EX2030/EX2060 (Wolfe) at 91:22-92:7; see also id. 129:24-130:17

| 20         | Q. Where in Harris does it disclose that the        | 11:32 |   |

|------------|-----------------------------------------------------|-------|---|

| 21         | external voltage source comes from host system?     | 11:32 |   |

| 22         | A. Well, I think there's a couple things that       | 11:32 |   |

| 23         | push us in that direction.                          | 11:33 | 1 |

| 24         | Q. Okay.                                            | 11:33 | X |

| 25         | A. One is that Harris tells us that these are       | 11:33 |   |

| 1          | supplied on the DIMM pins. And normally, all the    | 11:33 | L |

| 2          | pins to a DIMM connect to the host. So that would   | 11:34 | L |

| 3          | lead one to expect that voltage to come from the    | 11:34 |   |

| 4          | host.                                               | 11:34 | L |

| 5          | Secondly, there are claims on a computer            | 11:34 |   |

| 6          | system that describe that voltage that would be     | 11:34 |   |

| 7          | indicative. In general, the discussion of the       | 11:34 |   |

| 8          | external voltage source is in the context of a      | 11:34 |   |

| 9          | memory board assembly. So, again, that would lead   | 11:34 |   |

| L <b>O</b> | one to think that it's external from the memory     | 11:34 |   |

| 1          | board assembly and not necessarily external from    | 11:34 |   |

| 12         | anything else.                                      | 11:34 |   |

| L3         | And then on top of all that, I think there          | 11:34 |   |

| 4          | is just some commonsense that anyone who's designed | 11:34 |   |

| 15         | or built a computer understands that there is       | 11:34 | L |

| 16         | typically a single-power supply, the host power     | 11:35 |   |

| 17         | supply, and that for both safety and convenience    | 11:35 |   |

| 8          | reasons, memories are powered from the host power   | 11:35 |   |

| 9          | supply, that it would be very difficult to make a   | 11:35 |   |

| 20         | safe and reliable system where memories were not    | 11:35 |   |

| 21         | powered by the computer system.                     | 11:35 |   |

|            |                                                     |       |   |

'054: Paper 26 (Reply) at 3 '918: Paper 25 (Reply) at 2

# <u>Harris</u> [0019] proposes eliminating <u>board-specific</u> power supply in favor of a "technology-independent" 12V supply, not eliminating <u>all</u> power from the host

[0019] Based on the foregoing Detailed Description, it should be appreciated that an implementation of the embodiments described herein thus provides a technology-independent voltage distribution scheme for memory devices wherein system board power supply and associated voltage plane(s) are eliminated. Accordingly, power supply design's complexity as well as the cost of memory-specific power distribution are reduced. Cost savings may include, for example, elimination of system-board-specific power supply or regulator output, associated bypass capacitor arrangements, heavy etch or power planes. Also, under the technology-independent voltage distribution scheme disclosed herein, cost of memory power regulation scales with populated memory devices, rather than being pre-provisioned for maximum memory capacity as is typically the case in existing systems. Additionally, one or more of the following advantages may be realized in an exemplary voltage distribution embodiment: provision of tighter, lower inductance regulation which decreases voltage variability and increases timing margins; reduction in the pin count on DIMM connector to system board or memory riser card (whereby a smaller connector or wider pin spacing may be accommodated); improved signal integrity due to reduced crosstalk on the same size connector; and reservation of extra pins for implementing additional standard or proprietary functions.

**[0020]** Because voltage-independent embodiments disclosed herein can provide upgradeability and extensibility without changing system board power distribution, transitioning to newer DRAM technologies (e.g., at lower operating voltages) is more cost-effective as well as simpler to implement. Further, the embodiments are amenable to dual +12V power supply rail implementations so that industry-standard form factors can be advantageously accommodated.

EX1023 at [0019-0020] '918: Pet. 19; EX1003, ¶221 '054: Pet. 19; EX1003, ¶222 Netlist misinterprets paragraph [0019] of Harris to conclude that "system" board power supply...[is] eliminated" entirely. POR 4-5, 8, 10-11. To the contrary, Harris proposes avoiding the need for *different* system board voltages ---such as "3.3V, 2.5V, 1.8V, 1.5V and beyond," EX1023, [0002] — by simply supplying a *single* voltage (i.e., "12V")<sup>2</sup> to the memory module, *id.* [0012-13], so that an "on-board voltage regulator module [e.g., 102 above] [can] generate appropriate local voltage levels" on the memory module, id. [0003]. As Dr. Wolfe explained, Harris's "technology-independent voltage distribution scheme" eliminates the need for a "system-board-specific power supply," id. [0019], not all power, EX2030, 116:10-117:6.

> '918: Paper 25 (Reply) at 4-5 '054: Paper 26 (Reply) at 5-6

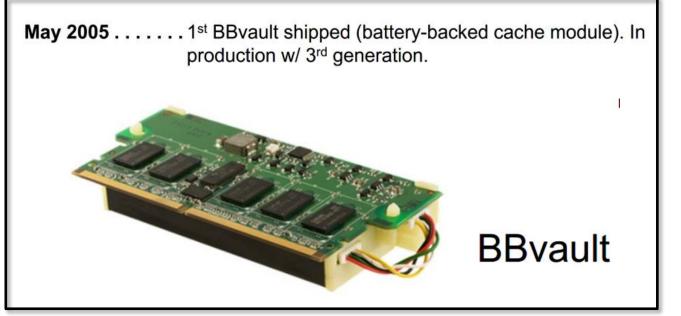

# Netlist's expert admits that it was known to use a <u>side</u> connector to a battery, and an <u>edge</u> connector to the host, making both obvious

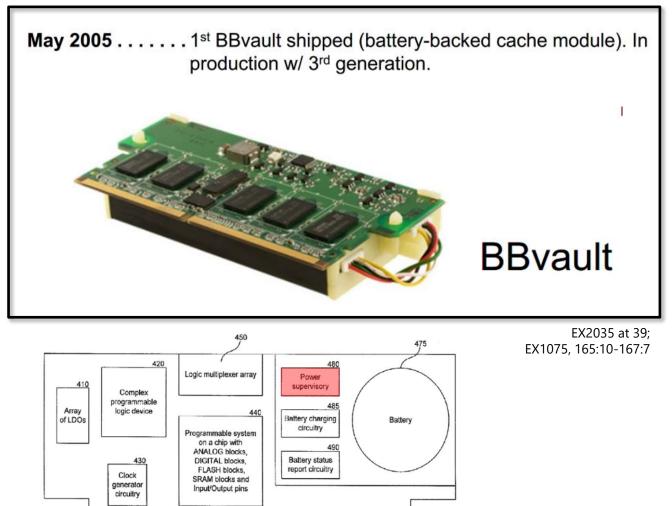

EX2035, 39

Last page of Exhibit 2035 it shows Q. BBvault, which you reference in paragraph 59 of your declarations; correct? Yes, that's correct. Α. BBvault is a memory module that was Ο. released back in 2005; correct? Yes, that's correct. Α. And the side connection on the BBvault memory module connects to a battery backup; correct? in addition to that side connection on BBvault, there is also edge connections along the bottom of the memory module that permit BBvault to plug in to a host system and receive power along the edge connections on the bottom of the memory module; correct? Yes, that's correct. Α. So the side connection on the BBvault 0

memory is for battery backup, while the edge

are for power from the host system; correct?

the battery backup and are used when the power coming in from the host system along the edge

connections along the bottom of the memory module

A. Yes. The side connections are -- go to

And this was known by 2005; correct?

"[J]ust because 'better alternatives' may exist in the prior art 'does not mean that an inferior combination is inapt for obviousness purposes."

> Dome Pat. L.P. v. Lee, 799 F.3d 1372, 1381 (Fed. Cir. 2015)

> > '918: Paper 25 (Reply) at 2-7 '054: Paper 26 (Reply) at 2-8

EX1075 (Mangione-Smith) at 165:10-166:12

connectors is not used.

A. Yes.

# DATA, ADDRESS, AND CONTROL SIGNALS FROM THE HOST

## GROUND 1 (<u>HARRIS</u> + <u>FBDIMM STANDARDS</u>)

DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

# The Institution Decision correctly found that Ground 1 teaches "data, address and control <u>signals</u> between the memory module and the host system"

EX1023, Fig. 1A

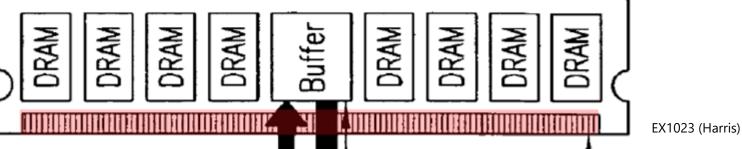

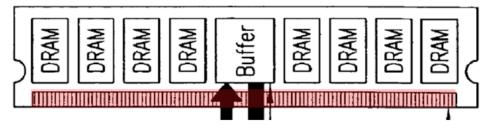

Petitioner further contends that Harris, consistent with the FBDIMM Standards, discloses that the edge connections are "configured to couple power, data, address and control *signals* between the memory module and the host system." Pet. 21–25. Petitioner contends that the power signal corresponds to Harris's voltage 104 in Figure 1A. Id. at 21 (citing Ex. 1023 ¶¶ 10, 12, 19). Petitioner contends that Harris's buffer 112 in Figure 1A is called "AMB" (Advanced Memory Buffer) in the FBDIMM Standards. Pet. 23–24. Petitioner indicates that Harris's buffer 112 receives data, address, and control *signals* via memory controller interface 114 and transmits these signals to DRAMs 110-1 to 110-N in Figure 1A. Pet. 22–25 (citing Ex. 1023 9 ("buffer/logic component 112 is provided for buffering command/address (C/A) space as well as data space at least for a portion of memory devices 110-1 through 110-N"). In addition, Petitioner argues that the FBDIMM Standards indicate that buffer AMB receives data *signals* DQ0–DQ63; address signals A0–A15; and control signals RAS, CAS, WE, CS, etc. Pet. 22– 23 (citing Ex. 1028, 13).

#### • • • •

Based on our review and consideration of the current record, we determine that Petitioner has adequately shown that the combination of Harris and the FBDIMM Standards teaches this limitation for purposes of institution.

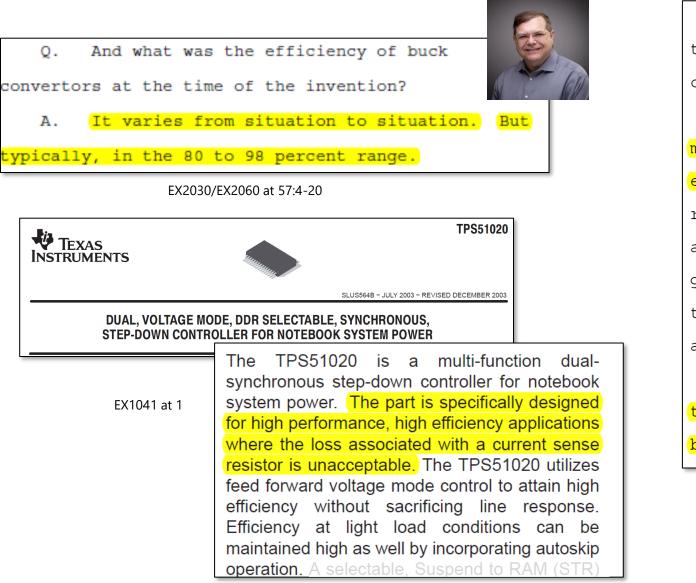

# The AMB Buffer in an FBDIMM (like <u>Harris</u>) receives data, address, and control <u>signals</u> from the host

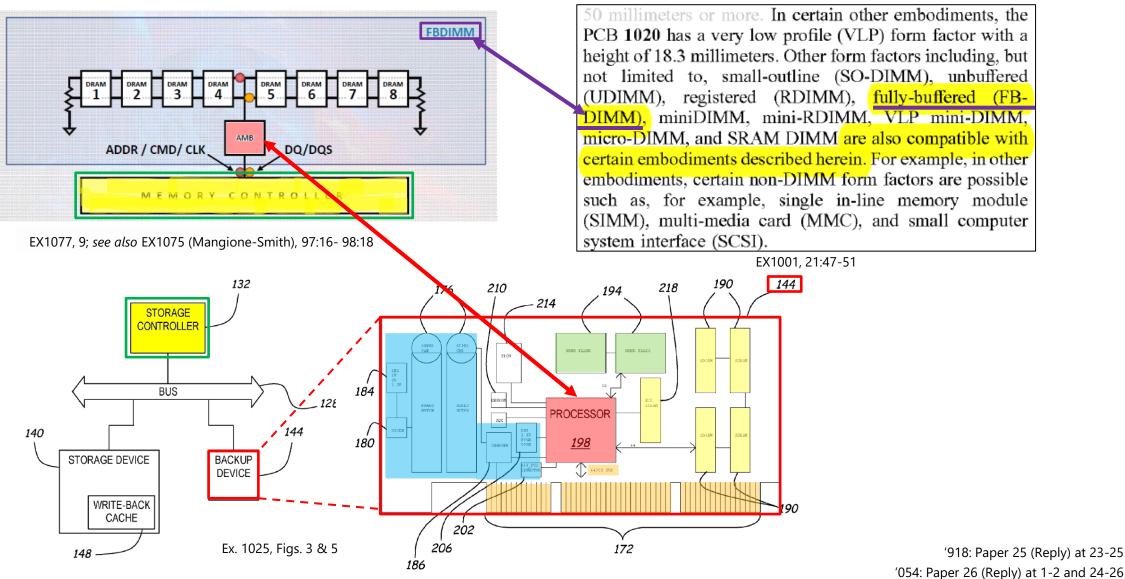

EX1077 at 9

Q. So when the host computer wants to send a read or write command to an FBDIMM, that read or write command and the associated address information is sent as packetized serial <u>signals</u>; correct?

A. Yes, that's correct.

Q. And similarly, when the host computer wants to send data to an FBDIMM that data is sent as packetized serial signals; correct?

A. Yes, that's correct.

Q. And then in the fourth line of paragraph 31 of your declarations, you explain that the AMB on the FBDIMM receives the data address and control information that was sent by the host computer using packetized serial signals; and the AMB decodes that information and generates the data address and control signals needed by the DDR2 SDRAM memory devices; correct? A. Yes, that's correct. That's what it says.

EX1075 (Mangione-Smith) at 156:4-:23; see also id. at 219:2-:11 ("signals")

'054: Paper 26 (Reply) at 8-9 '918: Paper 25 (Reply) at 7-8

# The AMB Buffer in an FBDIMM (like <u>Harris</u>) receives data, address, and control <u>signals</u> from the host

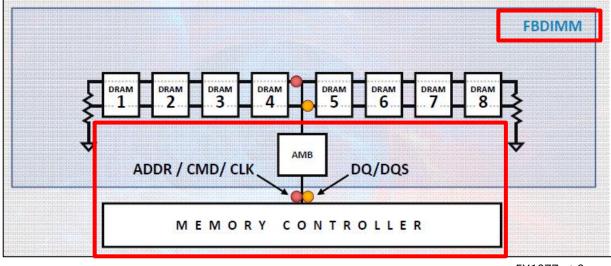

#### 1.1 Advanced Memory Buffer Overview

The Advanced Memory Buffer (AMB) reference design complies with the *FB-DIMM Architecture and Protocol Specification*. It supports DDR2 SDRAM main memory. The Advanced Memory Buffer allows buffering of memory traffic to support large memory capacities. All memory control for the DRAM resides in the host, including memory request initiation, timing, refresh, scrubbing, sparing, configuration access, and power management. The Advanced Memory Buffer interface is responsible for handling FBD channel and memory requests to and from the local DIMM and for forwarding requests to other DIMMs on the FBD channel.

Acts as DRAM memory buffer for all read, write, and configuration accesses addressed to the DIMM.

| Signal                  | Туре | Description                                                                                                                                                                                                                                                                                 |  |

|-------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Channel Interface       | e    |                                                                                                                                                                                                                                                                                             |  |

| PN[13:0]                | 0    | Northbound Output Data: High speed serial signal. Read path from AMB toward host on primary side of the DIMM connector.                                                                                                                                                                     |  |

| PN[13:0]                | 0    | Northbound Output Data Complement                                                                                                                                                                                                                                                           |  |

| SN[13:0]                | I    | Northbound Input Data: High speed serial signal. Read path from the previous AMB toward this AMB on secondary side of the DIMM connector.                                                                                                                                                   |  |

| SN[13:0]                | I    | Northbound Input Data Complement                                                                                                                                                                                                                                                            |  |

| PS[9:0]                 | I    | Southbound Input Data: High speed serial signal. Write path from host toward AMB on primary side of the DIMM connector.                                                                                                                                                                     |  |

| DQ[63:0]                | I/O  | Data                                                                                                                                                                                                                                                                                        |  |

| DQS[17:0]               | I/O  | Data Strobe: DDR2 data and check-bit strobe.                                                                                                                                                                                                                                                |  |

| DQS[17:0]               | I/O  | Data Strobe Complement: DDR2 data and check-bit strobe complements.                                                                                                                                                                                                                         |  |

| A0A-A15A,<br>A0B-A15B   | 0    | Address: Used for providing multiplexed row and column address to SDRAM.                                                                                                                                                                                                                    |  |

| BA0A-BA2A,<br>BA0B-BA2B | 0    | Bank Active: Used to select the bank within a rank.                                                                                                                                                                                                                                         |  |

| RASA, RASB              | 0    | <b>Row Address Strobe</b> : Used with $\overline{CS}$ , $\overline{CAS}$ , and $\overline{WE}$ to specify the SDRAM command.                                                                                                                                                                |  |

| CASA, CASB              | 0    | Column Address Strobe: Used with $\overline{CS}$ , $\overline{RAS}$ , and $\overline{WE}$ to specify the SDRAM command.                                                                                                                                                                     |  |

| WEA, WEB                | 0    | Write Enable: Used with $\overline{CS}$ , $\overline{CAS}$ , and $\overline{RAS}$ to specify the SDRAM command.                                                                                                                                                                             |  |

| CS0A-CS1A,<br>CS0B-CS1B | 0    | Chip Select: Used with $\overline{CAS}$ , $\overline{RAS}$ , and $\overline{WE}$ to specify the SDRAM command.<br>These signals are used for selecting one of two SDRAM ranks. $\overline{CS0}$ is used to<br>select the first rank and $\overline{CS1}$ is used to select the second rank. |  |

'918: Pet. at 22-25; Paper 25 (Reply) at 7-8 '054: Pet. at 22-25; Paper 26 (Reply) at 8-9

## The claims require "signals," not "dedicated pins"

| The claims require "signals"                                                                                                                                     | not "dedicated pins"                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ['918 claim 1] A memory module comprising: a                                                                                                                     | BY [NETLIST] ATTORNEY LINDSAY:                                                                                                                                     |

| printed circuit board (PCB) having an interface<br>configured to fit into a corresponding slot<br>connector of a host system, the interface including            | Q. Are there any <b>pins that are dedicated to data</b> signals shown in the table in that you just described?                                                     |

| a plurality of edge connections configured to couple <i>power, data, address and control <u>signals</u></i>                                                      | THE WITNESS: No, I don't believe so.                                                                                                                               |

| between the memory module and the host system;                                                                                                                   | Q. Are there any <i>dedicated address pins</i> in the table that you just described?                                                                               |

| ['054 claim 1] 1. A memory module comprising: a printed circuit board (PCB) having an interface                                                                  | THE WITNESS: No. There are <b>no dedicated</b><br><b>address signal pins</b> shown in this table.                                                                  |

| configured to fit into a corresponding slot<br>connector of a host system, the interface including                                                               | Q. And are there any <i>dedicated control signal pins</i> shown in the table?                                                                                      |

| a plurality of edge connections configured to<br>couple <b>power, data, address and control</b> <u>signals</u><br>between the memory module and the host system; | THE WITNESS: No, there are <b>no dedicated control</b><br><b>signal pins</b> shown in this table.<br>EX1075 (Mangione-Smith) at 214:24-215:20 (objections omitted) |

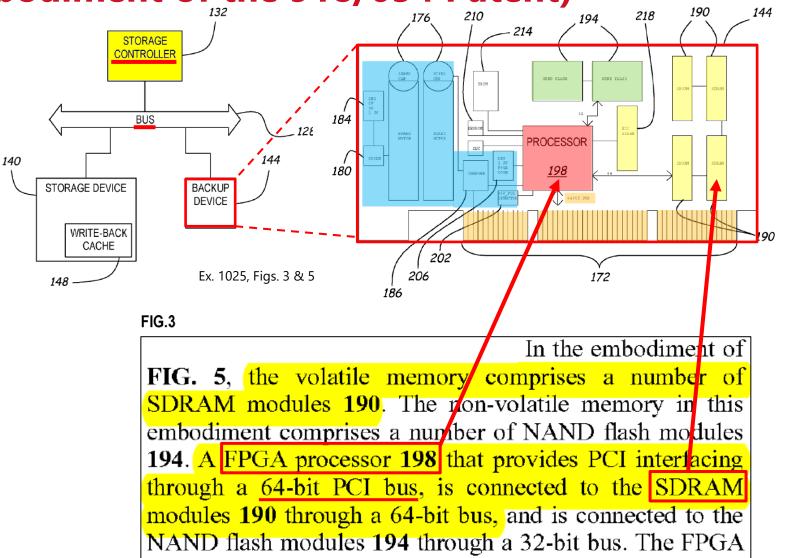

# Netlist's theory would exclude FBDIMMs, contrary to the preferred embodiment of the '918 and '054 Patents

### <u>'918 and '054 Patents</u>

Other form factors including, but not limited to, small-outline (SO-DIMM), unbuffered (UDIMM), registered (RDIMM), fully-buffered (FB-DIMM), miniDIMM, mini-RDIMM, VLP mini-DIMM, micro-DIMM, and SRAM DIMM are also compatible with certain embodiments described herein.

918: EX1001 at 21:46-51 054: EX1001 at 21:46-51

"A claim construction that excludes a preferred embodiment is **rarely, if ever correct** and would require highly persuasive evidentiary support."

Kaufman v. Microsoft Corp., 34 F.4th 1360, 1372 (Fed. Cir. 2022) (emphasis added)

## OBVIOUS TO USE THREE ('054) OR FOUR ('918) BUCK CONVERTERS

## GROUND 1 (<u>HARRIS</u> + <u>FBDIMM STANDARDS</u>)

DEMONSTRATIVE EXHIBIT – NOT EVIDENCE

# The Institution Decision correctly found that Ground 1 renders obvious the use of <u>four</u> buck converters

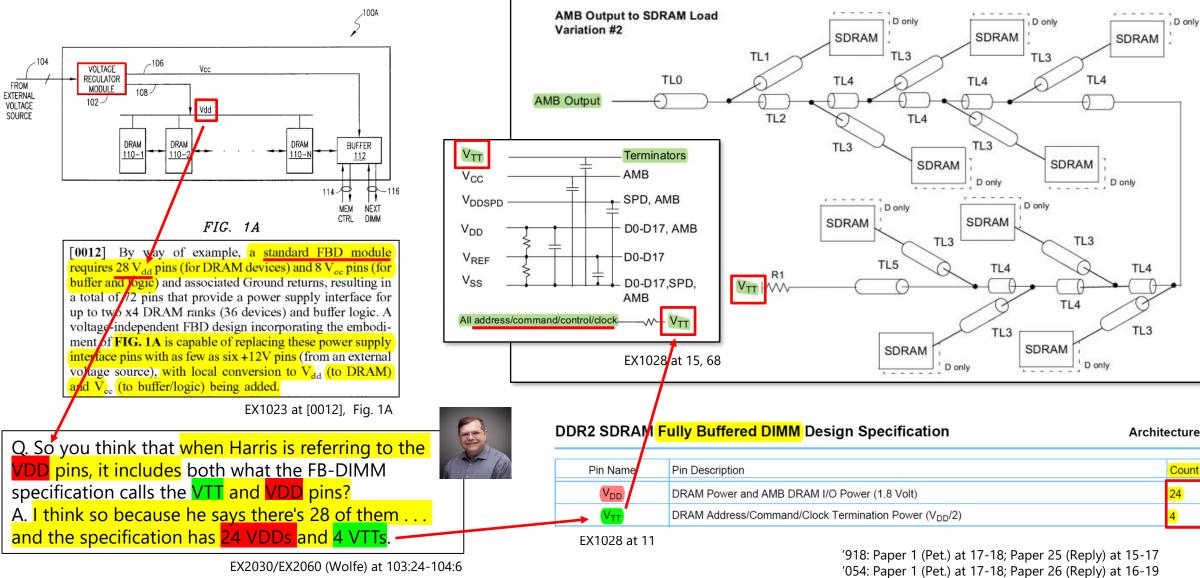

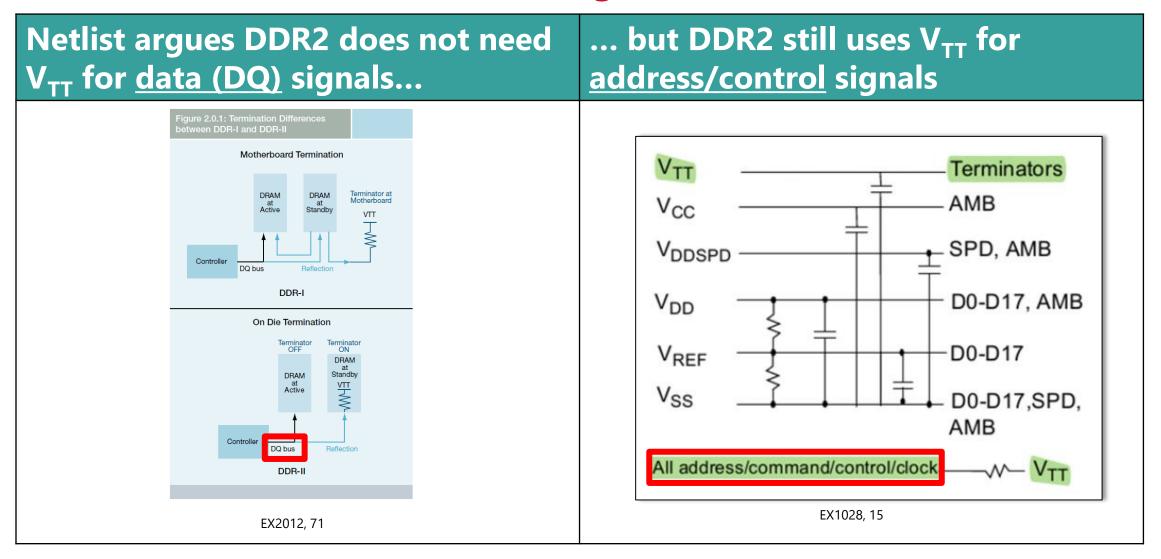

Patent Owner argues that Harris requires at most two or three buck converters to provide the voltages needed and thus, does not disclose the four claimed converters. Prelim. Resp. 20-25. Specifically, Patent Owner contends that Harris discloses a single converter generating two regulated voltages, so Harris does not disclose four converters as claimed. Prelim. Resp. 21-22. Petitioner showed sufficiently that the FBDIMM Standards mentioned in Harris call for at least four voltages, and that given Harris's teaching of a converter, it would have been obvious to one of ordinary skill in the art to use multiple converters, including well-known buck converters, to generate the four voltages needed. Pet. 26-31....

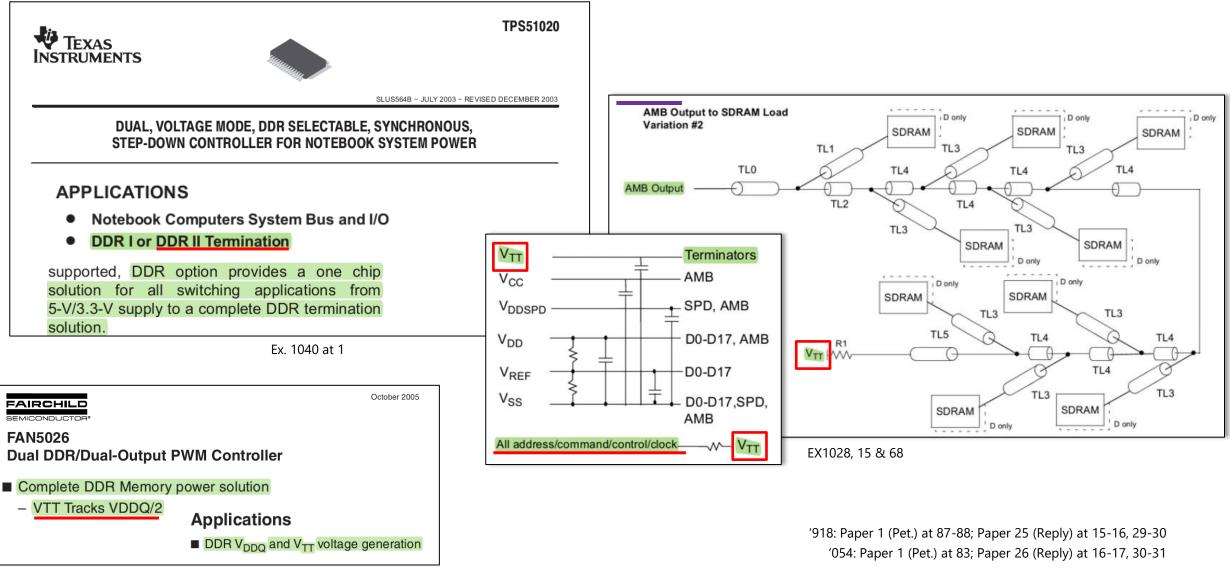

Patent Owner contends that Petitioner did not make the case that a person of ordinary skill in the art would have used a third buck converter, as opposed to a linear regulator, to provide termination voltage VTT. Prelim. Resp. 29–33. Petitioner explained sufficiently that "buck converters" were well-known as a highly-efficient way to step down voltages without generating excess heat or requiring large cooling devices, providing further motivation to use buck converters. Pet. 29–30.

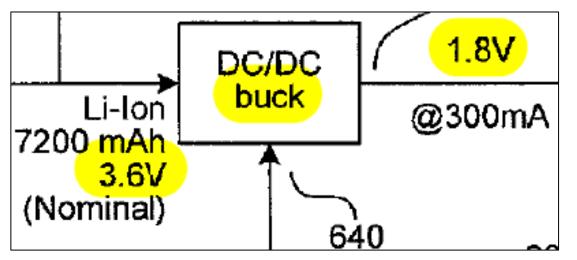

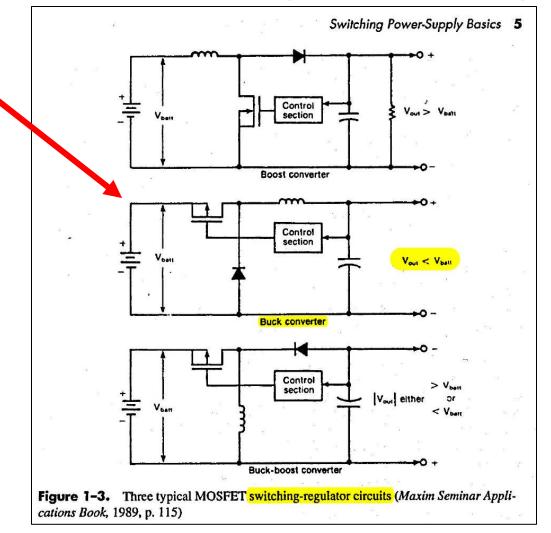

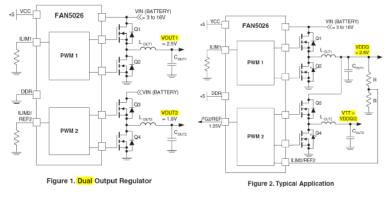

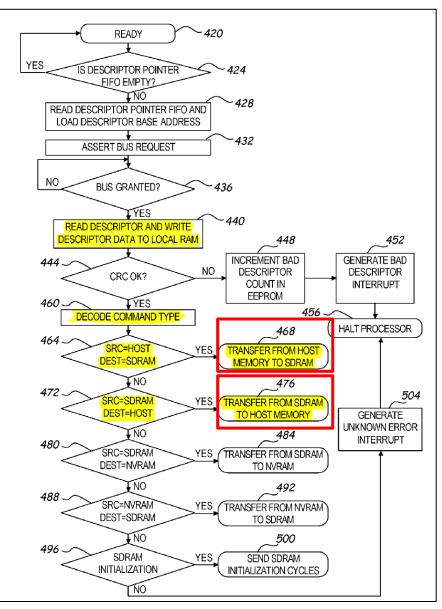

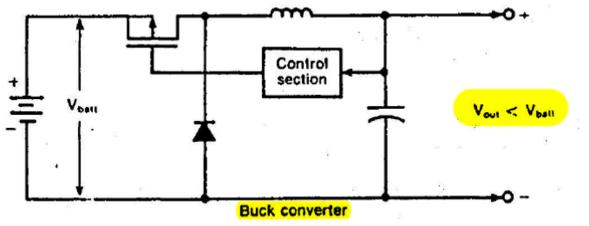

### **Obvious to use buck converters to provide lower, regulated voltages**

[0010] Preferably, a high-frequency switching voltage converter capable of generating tightly-controlled voltage levels may be implemented as the on-board VRM 102 for purposes of the present patent disclosure. For instance, multi-phase synchronous Pulse-Width Modulated (PWM) controllers, Low Drop-Out (LDO) controllers, et cetera, that are capable of accepting unregulated supply voltages in a broad range may be configured to operate as a local voltage supply for the memory module 100A.

EX1023 (Harris) at [0010]

EX1024 (<u>Amidi</u>) at Fig. 6

EX1058 at p. 5; see also EX1075 (Mangione-Smith) at 103:21-111:17

<sup>'</sup>918: Paper 1 (Pet.) at 29-30 and 90-91; Paper 25 (Reply) at 10, 18 and 29-30 <sup>'</sup>054: Paper 1 (Pet.) at 29-30 and 85-86; Paper 26 (Reply) at 11, 19 and 30-31

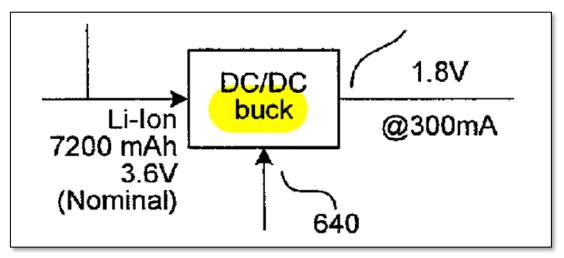

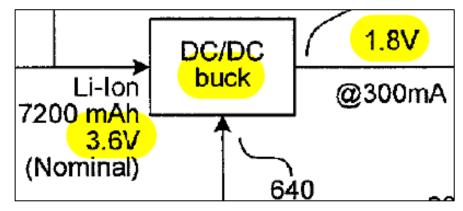

### **Obvious to use buck converters to provide lower, regulated voltages**

Q. All right. Would you agree that buck converters were known in the art by the time of the '918 and '054 patents?

A. Yes. For example, I was familiar with them at least as -- back in the 1996 time frame.

EX1075 (Mangione-Smith) at 104:23-105:2

Q. And you did not provide any analysis on the cost of buck converters versus LDOs that can be used to generate the needed voltage rail; correct? MR. CHANDLER: Object to form. THE WITNESS: Not a specific comparison, other than to say that both are available at very low cost today and both would be feasible to provide SPD power, and that the trend over the years has been to move all computer power supplies to buck converters.

EX2030/EX2060 (Wolfe) at 140:15-24

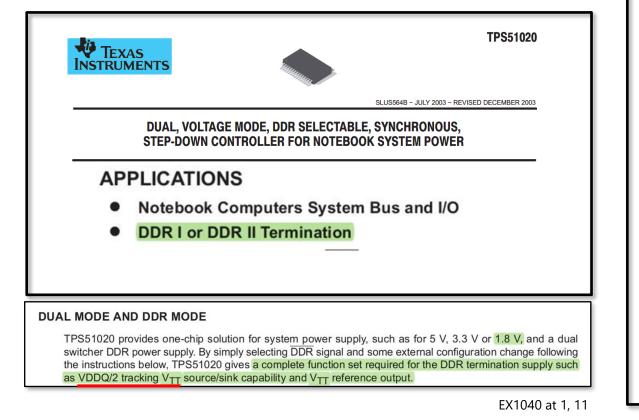

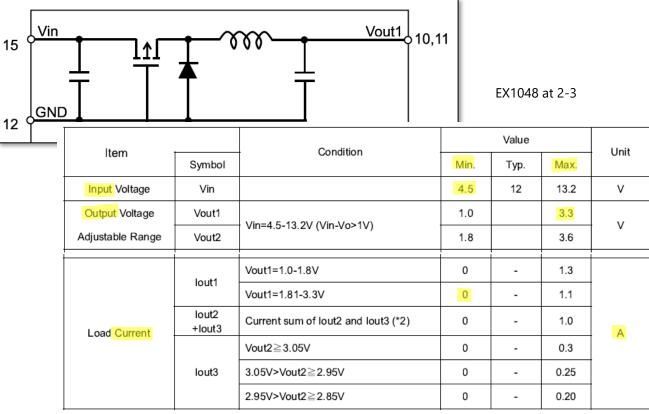

Further, "buck converters" were well-known as a *highly-efficient* way to step down voltages without generating excess heat or requiring large cooling devices, providing a further motivation (beyond Harris's express disclosure above) to implement <u>Harris</u>'s voltage regulator using "[buck] converter[s]." EX1003, ¶237; EX1059, 5:23-30 ("Switch mode buck converters have become popular due to two attractive features: first, they are *more efficient* than traditional low drop out regulators (LDO) (e.g., up to 95%) and second, they can provide relatively high currents with lower power dissipation on chip than an LDO can."); EX1058, p.5 (explaining the "*high efficiency* of switching regulators"); see also, e.g., EX1040, pp.1 ("high efficiency"), 23-24 (Figs.22-25); EX1041, pp. 1, 13

("high efficiency"); EX1048, p.3; EX1062, p.11; EX1064, ¶[0101].

918: Pet. at 29-30 054: Pet. at 29 (similar)

'918: Paper 1 (Pet.) at 29-30 and 90-91; Paper 25 (Reply) at 10, 18 and 29-30 '054: Paper 1 (Pet.) at 29-30 and 85-86; Paper 26 (Reply) at 11, 19 and 30-31

### **Obvious to use buck converters to provide lower, regulated voltages**

"[J]ust because 'better alternatives' may exist in the prior art 'does not mean that an inferior combination is inapt for obviousness purposes.'"

Dome Pat. L.P. v. Lee, 799 F.3d 1372, 1381 (Fed. Cir. 2015)

"[I]t's not necessary to show that a combination is the *best* option, only that it be a *suitable* option."

> Intel Corp. v. PACT XPP Schweiz AG, 61 F.4th 1373, 1380-81 (Fed. Cir. 2023) (reversing Board)

'918: Paper 25 (Reply) at 18 and 29-30 '054: Paper 1 (Pet.) at 29-30 and 85-86; Paper 26 (Reply) at 19 and 30-32

## 1. <u>Harris</u> is not limited to <u>one</u> buck converter

| Netlist argues <u>Harris</u> is limited to <u>one</u> buck converter                                                                                                                                                                                                                                             | but <u>Harris</u> teaches " <u>at least</u> one"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Harris expressly discloses using a<br><i>single</i> converter to provide at least<br>two of the voltages in each of<br>Petitioner's voltage mappings.<br>EX2031, ¶¶75-79. Specifically,<br>Harris discloses " <i>a</i> high-frequency<br>switching voltage converter capable<br>of generating tightly-controlled | [0010] In accordance with the teachings of the present patent disclosure, at least one on-board voltage regulator module (VRM) is provided as part of the memory board assembly module 100A Preferably, <u>a</u> high-frequency switching voltage converter capable of generating tightly-controlled voltage levels may be implemented as the on-board VRM 102 for purposes of the present patent disclosure What is claimed is: 1. A memory board assembling, comprising: at least one voltage regulator module and "a" is interpreted as "one or more" |

| voltage level <u>s</u> ." EX1023, FIG. 1A,<br>[0010]<br>A high-frequency<br>switching voltage<br>converter                                                                                                                                                                                                       | "[T]his court has repeatedly emphasized that an indefinite article<br><b>'a' or 'an'</b> in patent parlance <b>carries the meaning of 'one or</b><br><b>more'</b> in open-ended claims containing the transitional phrase<br>'comprising.' " That "a" or "an" can mean "one or more" is best<br>described as a rule, rather than merely as a presumption or even<br>a convention.                                                                                                                                                                        |

| '918: Paper 21 (POR) at 18-19<br>'054: Paper 22 (POR) at 20-21                                                                                                                                                                                                                                                   | <i>Baldwin Graphic Sys., Inc. v. Siebert, Inc.,</i><br>512 F.3d 1338, 1342-43 (Fed. Cir. 2008)                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# 1. <u>Harris</u> is not limited to <u>one</u> buck converter — Figure 1A shows <u>multiple</u> buck converters

### What Netlist calls <u>one</u> converter (with two outputs)...

...is <u>two</u> converters according to the 918/054 Patent...

Harris expressly discloses using a *single* converter to provide at least two of the voltages in each of Petitioner's voltage mappings. EX2031, ¶¶75-79. Specifically, Harris discloses "*a* high-frequency switching voltage converter capable of generating tightly-controlled voltage level<u>s</u>." EX1023, FIG. 1A, [0010]

2. The memory module of claim 1, wherein the <u>first</u> and <u>third</u> buck converters are further configured to operate as a <u>dual</u> buck converter.

### ... and has been construed as two converters (given the two outputs)

| Term                                                                                                                                                 | The Court's Construction                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| <ul> <li>'dual buck converter''</li> <li>('918 Patent, Claims 2, 17, 28)</li> <li>'dual-buck converter''</li> <li>('054 Patent, Claim 15)</li> </ul> | "a buck converter with <u>two</u> regulated voltage outputs"                          |

| F                                                                                                                                                    | EX2032, 34; see also id. 18-21<br>EX1075, 124:22-125:8, 126:9-:18; EX2030, 97:13-98:3 |

'918: Paper 25 (Reply) at 10-13 '054: Paper 26 (Reply) at 11-14

# 1. <u>Harris</u> is not limited to <u>one</u> buck converter — it was common for a single chip to have <u>multiple</u> buck converters

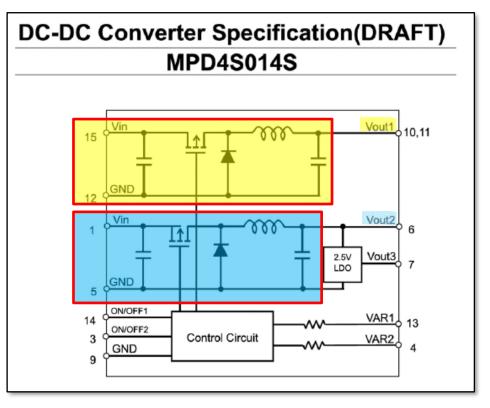

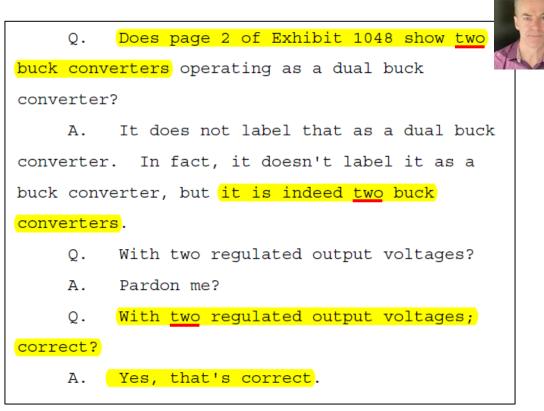

EX1048 at 2

EX1075 (Mangione-Smith) at 129:13-:24

'918: Paper 25 (Reply) at 10-13 '054: Paper 26 (Reply) at 11-14

## 1. <u>Harris</u> is not limited to <u>one</u> buck converter — it was common for a single chip to have <u>multiple</u> buck converters

As another example, Fairchild offered a FAN5026 "Dual-Output PWM

Controller" with two different outputs (each anywhere from 0.9V to 5.5V), such as

2.5V and 1.8V similar to Ground 1A or 1B, or VDDQ and VTT like Ground 1C:

| FA | IR | C | н |  |

|----|----|---|---|--|

|    |    |   |   |  |

SEMICONDUCTOR®

#### FAN5026 Dual DDR/Dual-Output PWM Controller

#### **Circuit Description**

#### Overview

The FAN5026 is a multi-mode, dual channel PWM controller intended for graphic chipset, SDRAM, DDR DRAM or other low output voltage power applications in PC's, VGA Cards and set top boxes. The IC integrates a control circuitry for two synchronous buck converters. The output voltage of each controller can be set in the range of 0.9V to 5.5V by an external resistor divider.

October 2005

Applications

DDR V<sub>DDQ</sub> and V<sub>TT</sub> voltage generation

EX1041, pp.1-2, 9; see also id., pp.7-8 (similar).

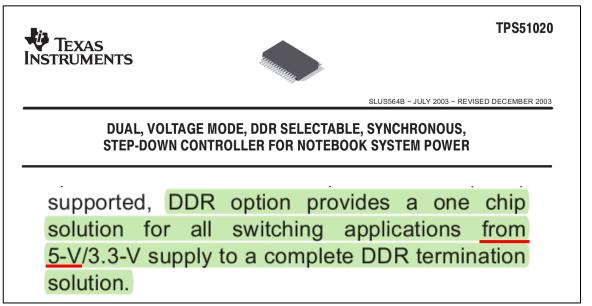

As another example, Texas Instruments offered a TPS51020 "Dual" buck converter, e.g., for V<sub>DDO</sub> and V<sub>TT</sub> voltages for DDR or DDR2 memory devices (similar to Ground 1C where "first"=V<sub>DDO</sub> and "third"= V<sub>TT</sub>): **TPS51020** TEXAS INSTRUMENTS SLUS564B - JULY 2003 - REVISED DECEMBER 2003 DUAL, VOLTAGE MODE, DDR SELECTABLE, SYNCHRONOUS, STEP-DOWN CONTROLLER FOR NOTEBOOK SYSTEM POWER \_\_\_. APPLICATIONS Notebook Computers System Bus and I/O DDR I or DDR II Termination EX1040, pp.1, 11 ("TPS51020 gives a complete function set required for the DDR termination supply such as VDDQ/2 tracking VTT").

> '918: Pet. at 38-40 '054: Pet. at 38-40

### 1. <u>Harris</u> is not limited to <u>one</u> buck converter — it was common to use <u>multiple</u> buck converters for <u>multiple</u> outputs

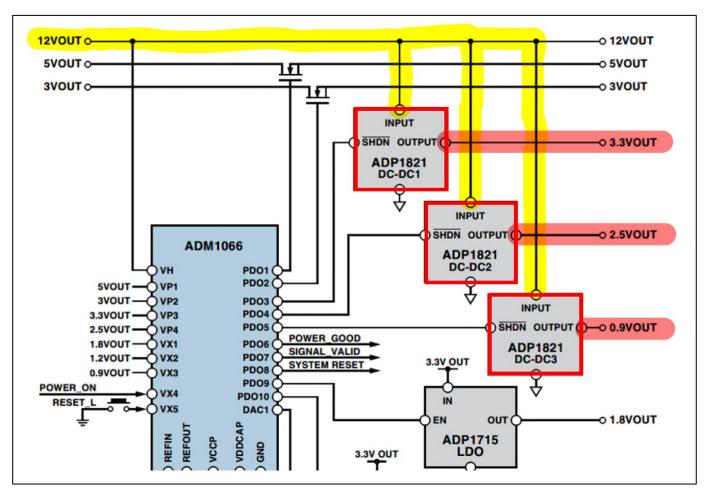

EX1062, 15; see also EX1075, 134:22-141:23; EX1078, 1 (ADP1821 datasheet)

Q. Okay. And but it was well known at the time of the invention that you can have a single-voltage converter to generate two different voltage levels; correct?

MR. CHANDLER: Objection. Form.

THE WITNESS: It was possible under some circumstances, but certainly not the most common thing to do. Normally, if you need to generate multiple output voltages, you would use multiple regulators, especially in a high-current situation

EX2030/EX2060 (Wolfe) at 53:16-:25

'918: Paper 25 (Reply) at 10-13 '054: Paper 26 (Reply) at 11-14

# 1. <u>Harris</u> is not limited to <u>one</u> buck converter — and <u>space</u> is not disclosed as a problem in <u>Harris</u> or the 918/054 Patents

[0010] In accordance with the teachings of the present patent disclosure, at least one on-board voltage regulator module (VRM) is provided as part of the memory board assembly module 100A for converting an externally supplied voltage level available on external source path 104 into appropriate local voltage levels that power the first and second voltage paths, i.e., the  $V_{dd}$  and  $V_{cc}$  paths 108, 106,

[0013] It is contemplated that local supply voltage conversion for double-rank DIMMs can be accommodated with a form factor design of approximately about one square inch (both sides of the printed circuit board), and at a component height compatible with applicable Joint Electron Device Engineering Council (JEDEC) standards.

EX1023 (Harris) at Fig. 1A, [0010], [0013]

| Q. Okay. Certainly, the LDO design would take       |

|-----------------------------------------------------|

| up less space; correct?                             |

| MR. CHANDLER: Objection                             |

| THE WITNESS: Not necessarily.                       |

| (Clarification requested by Reporter.)              |

| MR. CHANDLER: Object to form.                       |

| BY MS. ZHONG:                                       |

| Q. Why not?                                         |

| A. It depends on the external components, the       |

| packaging. You have to actually do the analysis.    |

| Both are viable solutions and, again, since buck    |

| converters, especially low current buck converters, |

| are designed for some very small battery powered    |

| systems like cell phones, or even smaller things,   |

| they often can be extremely small.                  |

EX2030/EX2060 (Wolfe) at 89-1:15

'918: Paper 25 (Reply) at 10-13 '054: Paper 26 (Reply) at 11-14

# 1. <u>Harris</u> is not limited to <u>one</u> buck converter — and chips can be stacked to save <u>space</u>

Q. And in what circumstances would you

want to use a <u>stacked</u>/dual-die memory device?

A. Sorry. There's a fellow who was making the noise earlier outside my window.

When you wanted to increase the capacity of the memory system.

Q. And could you explain that a little more.

A. Sure. The physical space on a DIMM would require a certain amount of space, a rectangle or, typically, a square -- I guess it's rectangular -- for one of these integrated circuits. If they were <u>stacked</u>, you've now doubled the amount of memory stored in the same amount of physical space -- two-dimensional physical space. It certainly has a little additional height.

#### EX1075 (Mangione-Smith) at EX1075, 74:22-75:25, 77:10-:17

'918: Paper 25 (Reply) at 10-13, 19-20 '054: Paper 26 (Reply) at 11-14, 20-21

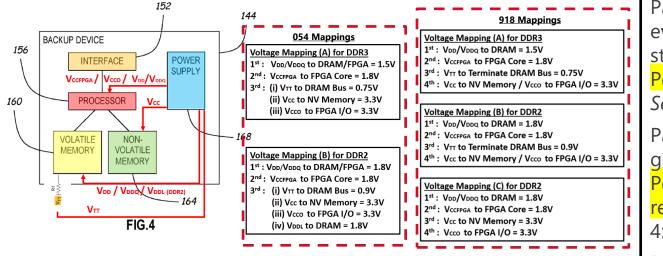

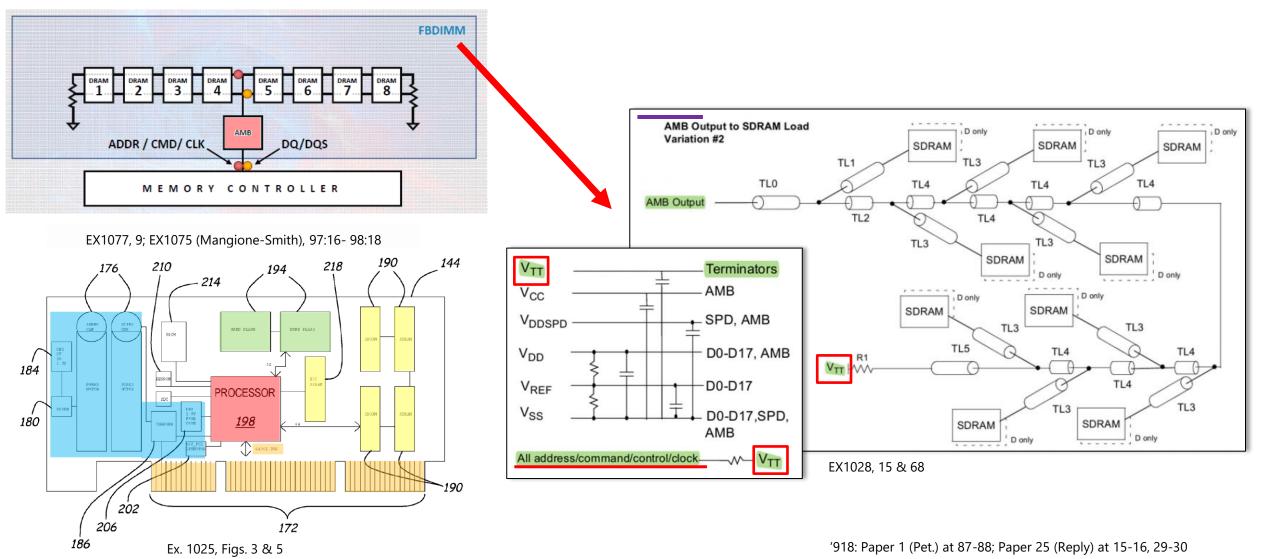

# 2. The Institution Decision correctly found it obvious to use different buck converters for different voltages (e.g., V<sub>DD</sub> vs. V<sub>DDL</sub>)

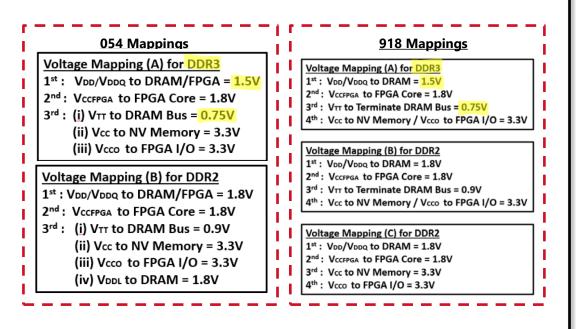

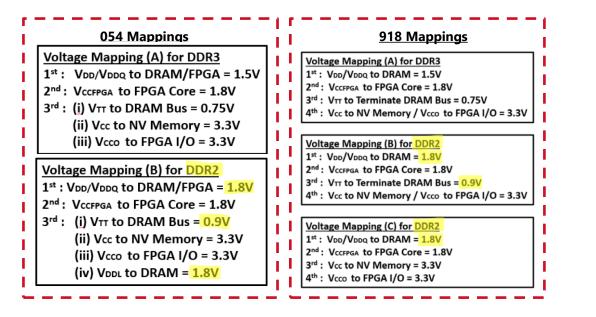

|           | Voltage Mappings (Grounds 1-3) |                                            |                                            |

|-----------|--------------------------------|--------------------------------------------|--------------------------------------------|

|           | <u>A</u> <u>B</u> <u>C</u>     |                                            |                                            |

| "first":  | $V_{DD}$ or $V_{DDQ} = 1.8V$   | $V_{DD}$ , $V_{DDQ}$ , or $V_{DDL} = 1.8V$ | $V_{DD}$ , $V_{DDQ}$ , or $V_{DDL} = 1.8V$ |

| "second": | $V_{CC}$ or $V_{CCFBD} = 1.5V$ | V <sub>cc</sub> =1.5V                      | $V_{CC}$ or $V_{CCFBD} = 1.5V$             |

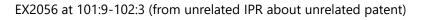

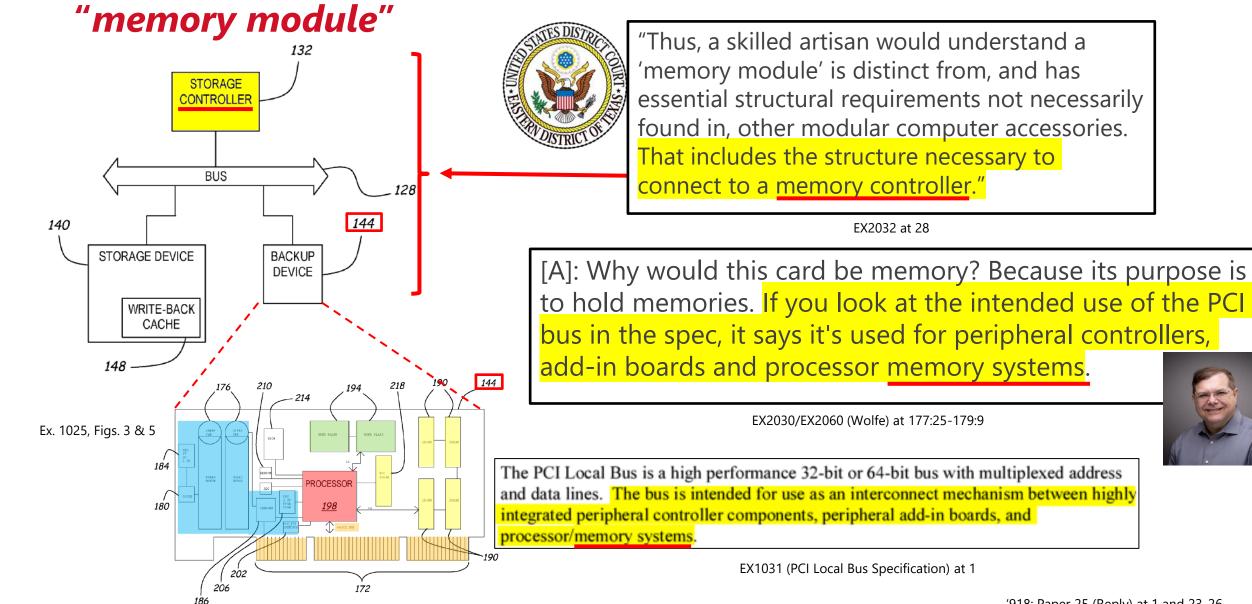

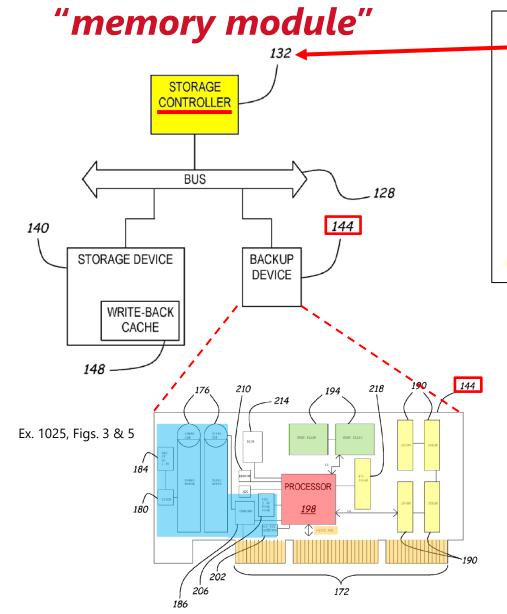

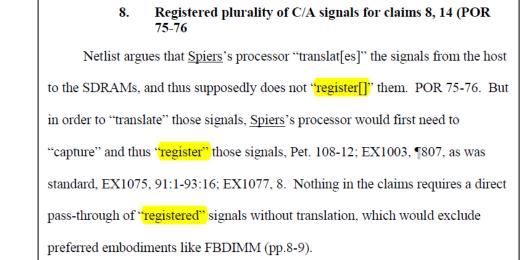

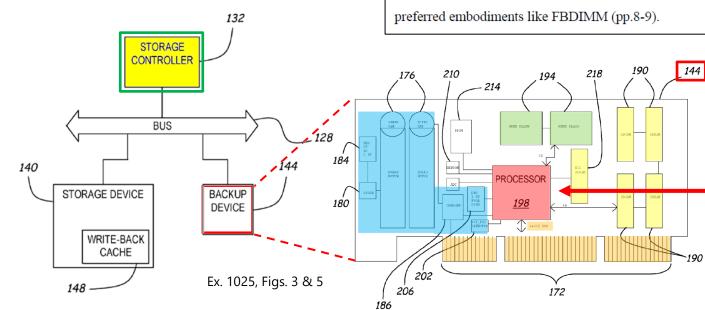

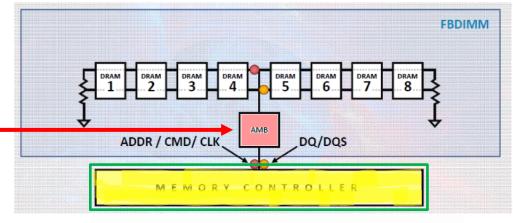

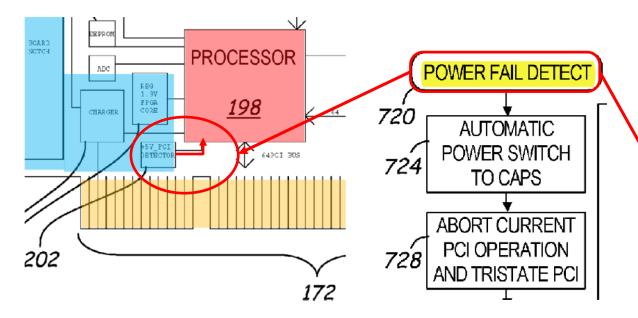

| "third":  | V <sub>DDL</sub> =1.8V         | V <sub>CCFBD</sub> =1.5V                   | V <sub>TT</sub> =0.9V                      |