# **LatticeXP Family Data Sheet**

Version 04.2, March 2006

# LatticeXP Family Data Sheet Introduction

December 2005 Data Sheet

## **Features**

# Non-volatile, Infinitely Reconfigurable

- Instant-on powers up in microseconds

- No external configuration memory

- Excellent design security, no bit stream to intercept

- Reconfigure SRAM based logic in milliseconds

- SRAM and non-volatile memory programmable through system configuration and JTAG ports

# **■** Sleep Mode

Allows up to 1000x static current reduction

## ■ TransFR<sup>TM</sup> Reconfiguration (TFR)

• In-field logic update while system operates

# **■** Extensive Density and Package Options

- 3.1K to 19.7K LUT4s

- 62 to 340 I/Os

- Density migration supported

## ■ Embedded and Distributed Memory

- 54 Kbits to 414 Kbits sysMEM<sup>™</sup> Embedded Block RAM

- Up to 79 Kbits distributed RAM

- Flexible memory resources:

- Distributed and block memory

#### ■ Flexible I/O Buffer

- Programmable sysIO<sup>™</sup> buffer supports wide range of interfaces:

- LVCMOS 3.3/2.5/1.8/1.5/1.2

- LVTTL

- SSTL 18 Class I

- SSTL 3/2 Class I, II

- HSTL15 Class I, III

- HSTL 18 Class I, II, III

- PCI

- LVDS, Bus-LVDS, LVPECL

# **■** Dedicated DDR Memory Support

• Implements interface up to DDR333 (166MHz)

# ■ sysCLOCK<sup>™</sup> PLLs

- Up to 4 analog PLLs per device

- · Clock multiply, divide and phase shifting

# **■** System Level Support

- IEEE Standard 1149.1 Boundary Scan, plus ispTRACY™ internal logic analyzer capability

- Onboard oscillator for configuration

- Devices operate with 3.3V, 2.5V, 1.8V or 1.2V power supply

Table 1-1. LatticeXP Family Selection Guide

| Device                       | LFXP3            | LFXP6            | LFXP10           | LFXP15           | LFXP20           |

|------------------------------|------------------|------------------|------------------|------------------|------------------|

| PFU/PFF Rows                 | 16               | 24               | 32               | 40               | 44               |

| PFU/PFF Columns              | 24               | 30               | 38               | 48               | 56               |

| PFU/PFF (Total)              | 384              | 720              | 1216             | 1932             | 2464             |

| LUTs (K)                     | 3.1              | 5.8              | 9.7              | 15.4             | 19.7             |

| Distributed RAM (KBits)      | 12               | 23               | 39               | 61               | 79               |

| EBR SRAM (KBits)             | 54               | 72               | 216              | 324              | 396              |

| EBR SRAM Blocks              | 6                | 8                | 24               | 36               | 44               |

| V <sub>CC</sub> Voltage      | 1.2/1.8/2.5/3.3V | 1.2/1.8/2.5/3.3V | 1.2/1.8/2.5/3.3V | 1.2/1.8/2.5/3.3V | 1.2/1.8/2.5/3.3V |

| PLLs                         | 2                | 2                | 4                | 4                | 4                |

| Max. I/O                     | 136              | 188              | 244              | 300              | 340              |

| Packages and I/O Combination | ons:             |                  |                  |                  | 1                |

| 100-pin TQFP (14 x 14 mm)    | 62               |                  |                  |                  |                  |

| 144-pin TQFP (20 x 20 mm)    | 100              | 100              |                  |                  |                  |

| 208-pin PQFP (28 x 28 mm)    | 136              | 142              |                  |                  |                  |

| 256-ball fpBGA (17 x 17 mm)  |                  | 188              | 188              | 188              | 188              |

| 388-ball fpBGA (23 x 23 mm)  |                  |                  | 244              | 268              | 268              |

| 484-ball fpBGA (23 x 23 mm)  |                  |                  |                  | 300              | 340              |

© 2005 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand

## Introduction

The LatticeXP family of FPGA devices combine logic gates, embedded memory and high performance I/Os in a single architecture that is both non-volatile and infinitely reconfigurable to support cost-effective system designs.

The re-programmable non-volatile technology used in the LatticeXP family is the next generation ispXP™ technology. With this technology, expensive external configuration memories are not required and designs are secured from unauthorized read-back. In addition, instant-on capability allows for easy interfacing in many applications.

The ispLEVER® design tool from Lattice allows large complex designs to be efficiently implemented using the LatticeXP family of FPGA devices. Synthesis library support for LatticeXP is available for popular logic synthesis tools. The ispLEVER tool uses the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the LatticeXP device. The ispLEVER tool extracts the timing from the routing and backannotates it into the design for timing verification.

Lattice provides many pre-designed IP (Intellectual Property) ispLeverCORE™ modules for the LatticeXP family. By using these IPs as standardized blocks, designers are free to concentrate on the unique aspects of their design, increasing their productivity.

# LatticeXP Family Data Sheet Architecture

December 2005 Data Sheet

# **Architecture Overview**

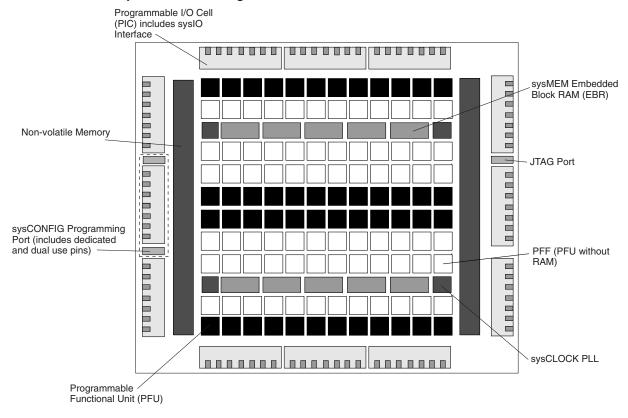

The LatticeXP architecture contains an array of logic blocks surrounded by Programmable I/O Cells (PIC). Interspersed between the rows of logic blocks are rows of sysMEM Embedded Block RAM (EBR) as shown in Figure 2-1.

On the left and right sides of the PFU array, there are Non-volatile Memory Blocks. In configuration mode this non-volatile memory is programmed via the IEEE 1149.1 TAP port or the sysCONFIG™ peripheral port. On power up, the configuration data is transferred from the Non-volatile Memory Blocks to the configuration SRAM. With this technology, expensive external configuration memories are not required and designs are secured from unauthorized read-back. This transfer of data from non-volatile memory to configuration SRAM via wide busses happens in microseconds, providing an "instant-on" capability that allows easy interfacing in many applications.

There are two kinds of logic blocks, the Programmable Functional Unit (PFU) and Programmable Functional unit without RAM/ROM (PFF). The PFU contains the building blocks for logic, arithmetic, RAM, ROM and register functions. The PFF block contains building blocks for logic, arithmetic and ROM functions. Both PFU and PFF blocks are optimized for flexibility, allowing complex designs to be implemented quickly and efficiently. Logic Blocks are arranged in a two-dimensional array. Only one type of block is used per row. The PFU blocks are used on the outside rows. The rest of the core consists of rows of PFF blocks interspersed with rows of PFU blocks. For every three rows of PFF blocks there is a row of PFU blocks.

Each PIC block encompasses two PIOs (PIO pairs) with their respective sysIO interfaces. PIO pairs on the left and right edges of the device can be configured as LVDS transmit/receive pairs. sysMEM EBRs are large dedicated fast memory blocks. They can be configured as RAM or ROM.

The PFU, PFF, PIC and EBR Blocks are arranged in a two-dimensional grid with rows and columns as shown in Figure 2-1. The blocks are connected with many vertical and horizontal routing channel resources. The place and route software tool automatically allocates these routing resources.

At the end of the rows containing the sysMEM Blocks are the sysCLOCK Phase Locked Loop (PLL) Blocks. These PLLs have multiply, divide and phase shifting capability; they are used to manage the phase relationship of the clocks. The LatticeXP architecture provides up to four PLLs per device.

Every device in the family has a JTAG Port with internal Logic Analyzer (ispTRACY) capability. The sysCONFIG port which allows for serial or parallel device configuration. The LatticeXP devices are available for operation from 3.3V, 2.5V, 1.8V and 1.2V power supplies, providing easy integration into the overall system.

Figure 2-1. LatticeXP Top Level Block Diagram

## **PFU and PFF Blocks**

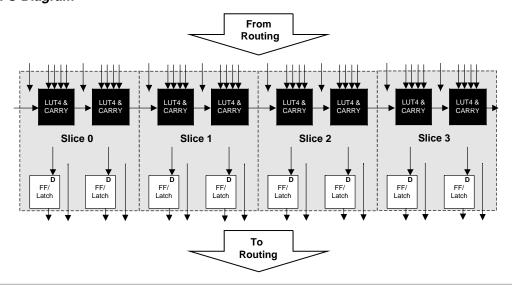

The core of the LatticeXP devices consists of PFU and PFF blocks. The PFUs can be programmed to perform Logic, Arithmetic, Distributed RAM and Distributed ROM functions. PFF blocks can be programmed to perform Logic, Arithmetic and ROM functions. Except where necessary, the remainder of the data sheet will use the term PFU to refer to both PFU and PFF blocks.

Each PFU block consists of four interconnected slices, numbered 0-3 as shown in Figure 2-2. All the interconnections to and from PFU blocks are from routing. There are 53 inputs and 25 outputs associated with each PFU block.

Figure 2-2. PFU Diagram

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

# API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

# **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.