# INTRODUCTION TO DIGITAL ELECTRONICS

# John Crowe and Barrie Hayes-Gill

Δ

# **Introduction to Digital Electronics**

#### John Crowe and Barrie Hayes-Gill

Both Lecturers in the Department of Electrical and Electronic Engineering University of Nottingham

4

R

M

Δ

OXFORD AMSTERDAM BOSTON LONDON NEW YORK PARIS

Newnes An imprint of Elsevier Science Linacre House, Jordan Hill, Oxford OX2 8DP 200 Wheeler Road, Burlington, MA 01803

First published by Arnold 1998 Reprinted 2001, 2002, 2003

Copyright © 1998, John Crowe and Barrie Hayes-Gill. All rights reserved

The right of John Crowe and Barrie Hayes-Gill to be identified as the authors of this work has been asserted in accordance with the Copyright, Designs and Patents Act 1988

No part of this publication may be reproduced in any material form (including photocopying or storing in any medium by electronic means and whether or not transiently or incidentally to some other use of this publication) without the written permission of the copyright holder except in accordance with the provisions of the Copyright, Designs and Patents Act 1988 or under the terms of a licence issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London, England W1T 4LP. Applications for the copyright holder's written permission to reproduce any part of this publication should be addressed to the publisher.

Permissions may be sought directly from Elsevier's Science and Technology Rights Department in Oxford, UK: phone: (+44) (0) 1865 843830; fax: (+44) (0) 1865 853333; e-mail: permissions@elsevier.co.uk.

You may also complete your request on-line via the Elsevier Science homepage (http://www.elsevier.com), by selecting 'Customer Support' and then 'Obtaining Permissions'

#### British Library Cataloguing in Publication Data

A catalogue record for this book is available from the British Library

#### Library of Congress Cataloguing in Publication Data

A catalogue record for this book is available from the Library of Congress

ISBN 0340645709

DOCKE

For information on all Newnes publications visit our website at www.newnespress.com

#### Typeset by AFS Image Setters Ltd, Glasgow

#### 208 Choosing a means of implementation

larger current to be passed within the same size transistor. In addition the higher the mobility, the faster the switching speed. In fact N-channel mobility is 2–3 times that of P-channel carriers and hence the NMOS logic operates at 2–3 times the speed of PMOS.

One problem of the NMOS gates (and for that matter PMOS) is that the upper transistor load is just acting as a resistor. When the lower transistor is on then current will flow from  $V_{dd}$  to  $V_{ss}$  and hence these types of devices consume a moderate amount of power. Consequently in 1978 both PMOS and NMOS devices were combined on to the same chip to produce the Complementary Metal Oxide Semiconductor family or CMOS as it is more commonly known.

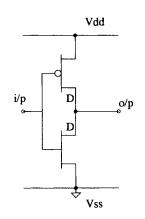

#### 9.3.3 CMOS inverter

A CMOS inverter is shown in Fig. 9.11. It consists of one NMOS and one PMOS transistor. The PMOS device is indicated by the negation sign (i.e. a bubble) on its gate and has a negative threshold voltage of typically -1 V. To turn on a PMOS device we require a voltage,  $V_{GS}$ , more negative than -1 V. Notice that the two drains of the two MOS transistors are connected together and form the output whilst the two gates form the single input. Due to the difference in the mobilities of the two devices the PMOS device is made with its W/L ratio 2–3 times larger than the NMOS device. This results in the two transistors having the same value of K so that both will have the same electrical performance.

The circuit operation depends upon the individual gate-source voltages. When the input voltage is 5V then the NMOS  $V_{GS}$  is 5 V and hence this device is on. However, the PMOS  $V_{GS}$  is 0 V and so this device is turned off. The output voltage is thus pulled down to 0 V. Now with the input at 0 V the NMOS  $V_{GS}$  is 0 V and hence is turned off. However, the PMOS  $V_{GS}$  is -5V and is thus turned on (remember a voltage more negative than the threshold voltage is needed to turn on a PMOS device) With the PMOS device on the output voltage is pulled up to

#### **CMOS** inverter power dissipation

You should notice that when the input is steady at either a high or a low voltage (static condition) then one transistor is always off between  $V_{dd}$  and  $V_{ss}$ . Hence the current flowing is extremely small – equal to the leakage current of the off transistor which is typically 100 nA. As a result of this the static power dissipation is extremely low and it is this reason that has made CMOS such a popular choice of technology.

For input voltages between  $V_{\rm T}$  and  $V_{\rm dd} - V_{\rm T}$  then the individual MOS transistors will be switched on by an amount dictated by Equations 9.1 and 9.2 and thus current will flow from  $V_{dd}$  to  $V_{ss}$ . When the input voltage is  $V_{dd}/2$  both transistors will be turned on by the same amount and hence the current will rise to a maximum and power will be dissipated. On many integrated circuits, several thousand gates exist and hence this power dissipation can be large. It is for this reason that the input voltage to a CMOS circuit must not be held at  $V_{\rm dd}/2$ . When the inputs are switching the power dissipated is called dynamic power dissipation. However, as long as the input signals have a fast rise and fall time then this form of dynamic power dissipation is small. The main cause of dynamic power dissipation, however, in a CMOS circuit is due to the charge and discharge of capacitance at each gate output. The dynamic power dissipation of a CMOS gate is therefore dependent upon the number of times a capacitor is charged and discharged. Hence as the frequency of switching increases so the dynamic power dissipation increases. The dynamic power dissipation for a CMOS gate is equal to

$$P_{\rm dynamic} = C_{\rm L} \times V_{\rm dd}^2 \times f \tag{9.3}$$

where f is the switching frequency and  $C_L$  is the load capacitance.

The total power dissipated in a CMOS inverter is thus the sum of the static and dynamic components.

#### Example 9.9

Compare the power dissipated by a CMOS inverter driving a  $50 \,\text{pF}$  load at (a)  $10 \,\text{kHz}$  and (b)  $10 \,\text{MHz}$ . What average current flows in each case. Assume a  $5 \,\text{V}$  power supply.

#### Solution

(a) 10 kHz:

$$P_{\text{dynamic}} = C_1 \times V_{\text{dd}}^2 \times f = 50 \times 10^{-12} \times 25 \times 10 \times 10^3 = 12.5 \,\mu\text{W}$$

Also:

$$P_{\text{dynamic}} = V_{\text{dd}} \times I_{\text{average}} \Longrightarrow I_{\text{average}} = 12.5 \times 10^{-6} / 5 = 2.5 \,\mu\text{A}$$

(b) 10 MHz:

# DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time alerts** and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### LAW FIRMS

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### FINANCIAL INSTITUTIONS

Litigation and bankruptcy checks for companies and debtors.

### E-DISCOVERY AND LEGAL VENDORS

Sync your system to PACER to automate legal marketing.