### (19) World Intellectual Property Organization International Bureau

#

### (43) International Publication Date 3 April 2003 (03.04.2003)

### PCT

# (10) International Publication Number WO 03/027828 A1

(51) International Patent Classification<sup>7</sup>: G06F 3/06, 12/02, G11C 16/10, 16/34

(21) International Application Number: PCT/GB02/04381

(22) International Filing Date:

27 September 2002 (27.09.2002)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data: 0123415.2 28 September 2001 (28.09.2001) G

(71) Applicant (for all designated States except US): LEXAR MEDIA, INC. [US/US]; 47421 Bayside Parkway, Fremont, CA 94538 (US).

(72) Inventors; and

(75) Inventors/Applicants (for US only): GOROBETS,

Sergey, Anatolievich [GB/GB]; 1Fl, 16 East Mayfield, Edinburgh EH9 1SE (GB). BENNETT, Alan, David [GB/GB]; 2 Thorburn Road, Edinburgh EH13 OBQ (GB). SINCLAIR, Alan, Welsh [GB/GB]; 12/4 Damside, Edinburgh EH4 3BB (GB).

- (74) Agents: BERESFORD, Keith, Denis, Lewis et al.; Beresford & Co., 2-5 Warwick Court, High Holborn, London WC1R 5DH (GB).

- (81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM),

[Continued on next page]

(54) Title: METHOD OF WRITING DATA TO NON-VOLATILE MEMORY

(57) Abstract: According to a first aspect of the invention, there is provided a controller connected to a non-volatile memory and including a volatile memory, wherein the controller maintains lists in volatile memory of blocks in the non-volatile memory allocated for storage of logical sector data and of blocks recently erased in the non-volatile memory.

3/027828 A1

### WO 03/027828 A1

I TABLE BULLER I A BURLEBURG DIK I I I I BURLEBURG DIKE BURLEBURG BURLEBURG BURLEBURG.

European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, SK, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

with international search report

before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

### METHOD OF WRITING DATA TO NON-VOLATILE MEMORY

The present invention relates to a method of writing data to non volatile memory and in particular to a method of writing data to flash memory in order to ensure the uniform distribution of use over a prolonged period of operation.

In known memory systems it is common for non volatile memory such as the flash memory of the memory systems to have wear out mechanisms within their physical structures which mean that a block within the flash memory may experience failure after a cumulative number of operations. However, known data management methods typically do not perform block erasure in Flash memory in real time leading to the accumulation of blocks in Flash memory which contain obsolete versions of sectors. It is also the case that in known systems the physical address for writing a sector is dependant on the logical address of the sector thus logically non-contiguous sectors are written in non-contiguous physical address and logical to physical.

In particular an object of the present invention is to reduce the number of read and write accesses to the

WO 03/027828

PCT/GB02/04381

non-volatile memory for control data structures, thereby increasing the write speed of the memory system for host data.

A second object of the invention is to obtain even use of blocks in the non-volatile memory for storage of data over a long period of operation, and to avoid "hotspots" in non-volatile memory usage, thereby increasing the reliability of the memory system.

According to a first aspect of the invention, there is provided a controller connected to a non-volatile memory and including a volatile memory, wherein

the controller maintains lists in volatile memory of blocks in the non-volatile memory allovated for storage of logical sector data and of blocks recently erased in the non-volatile memory

the controller transfers information from the lists in volatile memory to control data structures in the non-volatile memory less frequently than the contents of the lists in volatile memory are changed

such that the lists in volatile memory can be reconstructed at any time from existing information in the non-volatile memory.

Preferably, information from the lists in volatile memory is transferred to control data structures in the non-volatile memory concurrently with logical to physical

WO 03/027828

mapping information for sectors from other lists in volatile memory.

According to a second aspect of the invention, there is provided a controller connected to a non-volatile memory and including a volatile memory, wherein

the controller maintains a first list of all blocks in the non-volatile memory which are in the erased state and which are not included in other lists

the controller maintains a second list of blocks in the non-volatile memory which have been recently erased.

These and other aspects of the invention will become apparent from the following description taken in combination with the following drawings in which is shown:

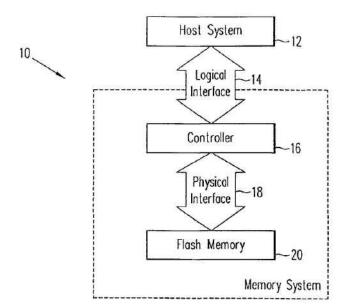

Figure 1 - a host system and flash memory system arrangement which the present invention is implemented;

Figure 2 - the hardware architecture of the controller of the system of Figure 1 in which the present invention is implemented;

Figure 3 - the layered firmware structure which performs the media management operations according to the present invention;

Figure 4a - schematic representation of the write operation according to the present invention;

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

### **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.