#### US005721862A

## United States Patent [19]

### Sartore et al.

[11] Patent Number:

5,721,862

[45] Date of Patent:

\*Feb. 24, 1998

#### [54] ENHANCED DRAM WITH SINGLE ROW SRAM CACHE FOR ALL DEVICE READ OPERATIONS

[75] Inventors: Ronald H. Sartore, San Diego, Calif.; Kenneth J. Mobley, Colorado Springs,

Colo.; Donald G. Carrigan, Monument, Colo.; Oscar Frederick Jones, Jr., Colorado Springs, Colo.

[73] Assignee: Ramtron International Corporation,

Colorado Springs, Colo.

[\*] Notice: The term of this patent shall not extend

beyond the expiration date of Pat. No.

5,699,317.

[21] Appl. No.: 460,665

[22] Filed: Jun. 2, 1995

#### Related U.S. Application Data

[63] Continuation of Ser. No. 319,289, Oct. 6, 1994, which is a continuation-in-part of Ser. No. 824,211, Jan. 22, 1992, abandoned.

[52] U.S. Cl. ...... 395/445; 365/189.04; 365/189.05

## [56] References Cited

#### U.S. PATENT DOCUMENTS

| 4,577,293 |         | Matick et al 365/189    |

|-----------|---------|-------------------------|

| 4,608,668 |         | Uchida.                 |

| 4.725.945 | 2/1988  | Kronstadt 364/200       |

| 4,794,559 | 12/1988 | Greeberger 365/49       |

| 4,870,622 | 9/1989  | Aria et al 365/230.02   |

| 4.894,770 | 1/1990  | Ward et al 364/200      |

| 4,926,385 | 5/1990  | Fujishima et al         |

| 4,943,944 | 7/1990  | Sakui et al 365/189.05  |

| 5.025,421 | 6/1991  | Cho 365/230.5           |

| 5,111,386 | 5/1992  | Fujishima et al 395/425 |

(List continued on next page.)

#### FOREIGN PATENT DOCUMENTS

41 18 804A1 12/1991 Germany .

60-258791 12/1985 Japan .

63-81692 4/1988 Japan .

1-159891 6/1989 Japan .

#### OTHER PUBLICATIONS

Niijima, et al., "QRAM-Quick Access Memory System", IEEE International Conference on Compute Design: V.L.S.I. In Computers and Processors, pp. 417-420 (Sep. 17, 1990).

(List continued on next page.)

Primary Examiner—Tod R. Swann

Assistant Examiner—Keith W. Saunders

Attorney, Agent, or Firm—William J. Kubida, Esq.; Richard

A. Bachand, Esq.; Peter J. Meza, Esq.

#### 57] ABSTRACT

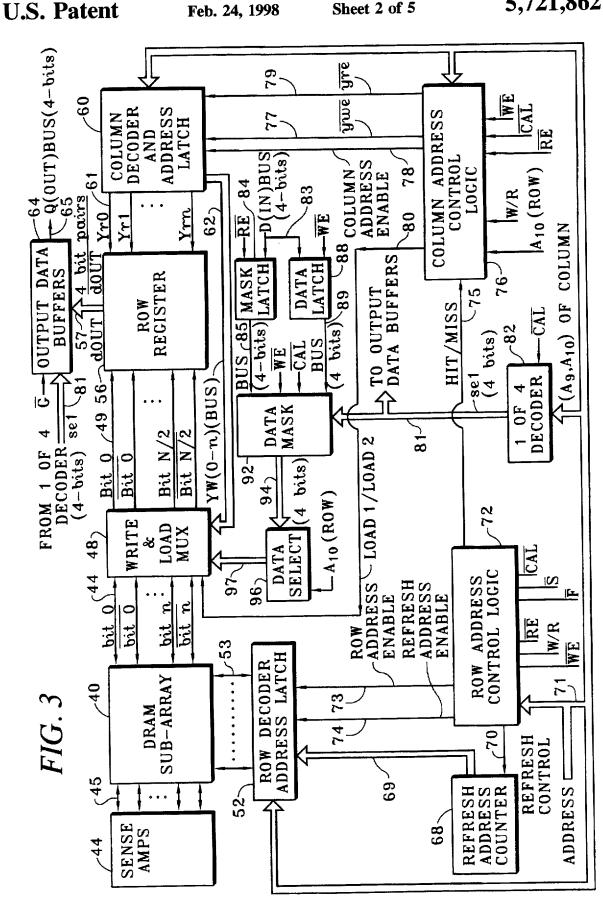

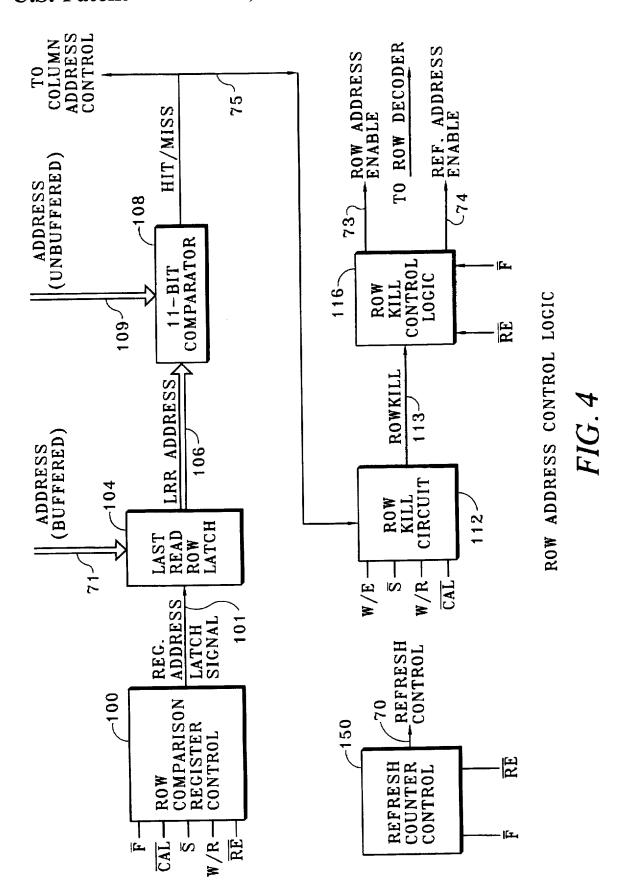

An enhanced DRAM contains embedded row registers in the form of latches. The row registers are adjacent to the DRAM array, and when the DRAM comprises a group of subarrays, the row registers are located between DRAM subarrays. When used as on-chip cache, these registers hold frequently accessed data. This data corresponds to data stored in the DRAM at a particular address. When an address is supplied to the DRAM, it is compared to the address of the data stored in the cache. If the addresses are the same, then the cache data is read at SRAM speeds. The DRAM is decoupled from this read. The DRAM also remains idle during this cache read unless the system opts to precharge or refresh the DRAM. Refresh or precharge occur concurrently with the cache read. If the addresses are not the same, then the DRAM is accessed and the embedded register is reloaded with the data at that new DRAM address. Asynchronous operation of the DRAM is achieved by decoupling the row registers from the DRAM array, thus allowing the DRAM cells to be precharged or refreshed during a read of the row register. Additionally, the row registers/memory cache is sized to contain a row of data of the DRAM array. Furthermore, a single column decoder addresses corresponding locations in both the memory cache and the DRAM array. And finally, all reads are only from the memory cache.

### 36 Claims, 5 Drawing Sheets

#### U.S. PATENT DOCUMENTS

| 5,148,346 | 9/1992 | Nakada 365/189.03       |

|-----------|--------|-------------------------|

| 5,179,687 |        | Hidaka et al 395/425    |

| 5,184,320 | 2/1993 | Dye 365/49              |

| 5,184,325 | 2/1993 | Lipouski                |

| 5,214,610 |        | Houston 365/189.05      |

| 5,226,009 | 7/1993 | Arimoto 365/189.04      |

| 5,226,139 | 7/1993 | Fujishima et al 395/425 |

| 5,226,147 | 7/1993 | Fujishima et al 395/425 |

| 5,249,282 | 9/1993 | Segers 395/449          |

| 5,305,280 |        | Hayano 365/230.03       |

| 5,329,489 | 7/1994 | Diefendorff 365/189.05  |

| 5,381,370 | 1/1995 | Lacey et al 365/200     |

| 5,390,308 | 2/1995 | Ware et al 395/405      |

| 5,421,000 |        | Fortino et al 395/445   |

| 5,471,601 |        | Gonzales 395/403        |

|           |        |                         |

#### OTHER PUBLICATIONS

Bursky, "Combination DRAM-SRAM Removes Secondary Caches", Electronic Design, vol. 40, No. 2, pp. 39-43 (Jan. 23, 1992).

Goodman and Chiang, "The Use of Static Column RAM as a Memory Hierarchy," The 11th Annual Symposium on Computer Architecture, IEEE Computer Society Press, 1984, pp. 167–174.

Dosaka, et al., "A 100MHz 4Mb Cobe Cache DRAM with Fast Copy-back Scheme," *Digest of Technical Papers*, 1992 IEEE International Solid-State Circuits Conference, pp. 148-149 (Jun. 1992).

Ohta, et al., "A 1Mb DRAM with 33Mhz Serial I/O Ports," Digest of Technical Papers, 1986 IEEE International Solid-State Circuits Conference, pp. 274–275 (1986).

Hitachi, "Video RAM," Specification for parts HM53461 and HM53462, pp. 30-33.

Sartore, R.H., "New Generation of Fast, Enhanced DRAMS Replace Static RAM Caches in High-End PC Workstations." (Jul. 9, 1991).

**U.S.** Patent

FIG. 1

PRIOR ART

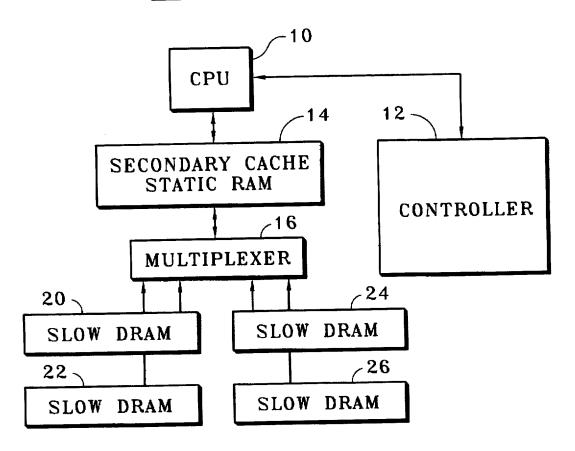

CPU

CPU

CONTROL LOGIC

34

ENHANCED DRAM

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

## **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.