US009997240B2

## $\begin{array}{c} \text{(12)} \ \, \textbf{United States Patent} \\ \text{Rao} \end{array}$

## (10) Patent No.: US 9,997,240 B2 (45) Date of Patent: \*Jun. 12, 2018

## (54) LIFETIME MIXED LEVEL NON-VOLATILE MEMORY SYSTEM

(71) Applicant: Greenthread, LLC, Dallas, TX (US)

(72) Inventor: G. R. Mohan Rao, Allen, TX (US)

(73) Assignee: Greenthread, LLC, Dallas, TX (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days. days.

This patent is subject to a terminal dis-

claime

(21) Appl. No.: 14/950,553

(22) Filed: Nov. 24, 2015

(65) Prior Publication Data

US 2016/0155496 A1 Jun. 2, 2016

#### Related U.S. Application Data

(60) Continuation of application No. 14/525,411, filed on Oct. 28, 2014, now Pat. No. 9,196,385, which is a (Continued)

(51) Int. Cl.

G11C 16/04 (2006.01)

G11C 11/56 (2006.01)

(Continued)

(52) U.S. CI.

CPC ...... *G11C 11/5635* (2013.01); *G06F 11/1068* (2013.01); *G06F 11/1072* (2013.01); (Continued)

(58) Field of Classification Search

CPC ........ G11C 11/5621; G11C 2211/5641; G11C 2029/1806; G11C 29/50004; G11C 29/76;

(Continued)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

7,855,916 B2 12/2010 Rao 8,825,941 B2\* 9/2014 Moshayedi ........ G06F 11/1441 711/103 (Continued)

(Continued)

#### OTHER PUBLICATIONS

Intel, Understanding the Flash Translation Layer (FTL) Specification, Dec. 1998.

(Continued)

Primary Examiner — Harry W Byrne

Assistant Examiner — R Lance Reidlinger

(74) Attorney, Agent, or Firm — Munck Wilson Mandala,

LLP

#### (57) ABSTRACT

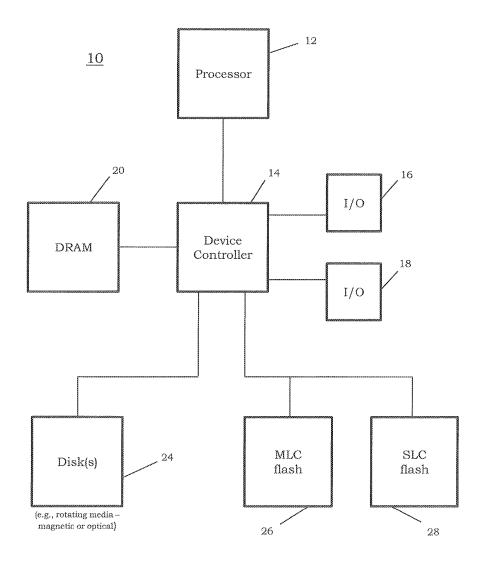

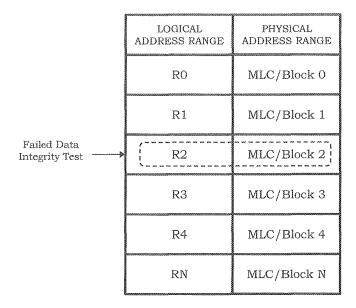

A controller for managing at least one MLC non-volatile memory module and at least one SLC non-volatile memory module. The flash controller is adapted to determine if a range of addresses listed by an entry and mapped to said at least one MLC non-volatile memory module fails a data integrity test. In the event of such a failure, the controller remaps said entry to an equivalent range of addresses of said at least one SLC non-volatile memory module. The flash controller is further adapted to determine which of the blocks in the MLC and SLC non-volatile memory modules are accessed most frequently and allocating those blocks that receive frequent writes to the SLC non-volatile memory module and those blocks that receive infrequent writes to the MLC non-volatile memory module.

#### 10 Claims, 5 Drawing Sheets

#### Related U.S. Application Data

division of application No. 13/455,267, filed on Apr. 25, 2012, now Pat. No. 8,891,298.

(60) Provisional application No. 61/509,257, filed on Jul. 19. 2011.

#### (51) Int. Cl. G11C 16/34 (2006.01)G06F 12/02 (2006.01)G06F 11/10 (2006.01)G11C 29/52 (2006.01)G11C 29/00 (2006.01)G11C 16/16 (2006.01)

(52) U.S. Cl.

CPC ..... G06F 12/0246 (2013.01); G11C 11/5621 (2013.01); G11C 11/5678 (2013.01); G11C 16/16 (2013.01); G11C 16/3495 (2013.01); G11C 29/52 (2013.01); G11C 29/76 (2013.01); G06F 2212/7202 (2013.01); G11C 2211/5641 (2013.01)

#### (58) Field of Classification Search

CPC . G11C 29/765; G06F 11/1068; G06F 11/1072 See application file for complete search history.

#### (56)References Cited

#### U.S. PATENT DOCUMENTS

| 8,891,298    | B2 * | 11/2014 | Rao G11C 16/3495       |  |

|--------------|------|---------|------------------------|--|

|              |      |         | 365/148                |  |

| 9,196,385    | B2 * | 11/2015 | Rao G11C 16/3495       |  |

| 2009/0268513 | A1   | 10/2009 | De Ambroggi et al.     |  |

| 2009/0307418 | A1   | 12/2009 | Chen et al.            |  |

| 2009/0327591 | A1*  | 12/2009 | Moshayedi G06F 11/1441 |  |

|              |      |         | 711/103                |  |

| 2010/0058018 | A1   | 3/2010  | Kund et al.            |  |

| 2010/0172179 | A1*  | 7/2010  | Gorobets G06F 12/0246  |  |

|              |      |         | 365/185.09             |  |

| 2010/0325352 | A1*  | 12/2010 | Schuette G06F 3/0613   |  |

|              |      |         | 711/103                |  |

| 2011/0060870 | A1   | 3/2011  | Rao                    |  |

| 2011/0271043 | A1   | 11/2011 | Segal et al.           |  |

|              |      |         | -                      |  |

#### OTHER PUBLICATIONS

Tae-Sun Chung et al., A Survey of Flash Translation Layer, Journal of Systems Architecture 55, pp. 332-343, 2009. Seagate Technology LLC, The Transition to Advanced Format 4K

Sector Hard Drives, Apr. 2010.

Roberto Bez et al., Introduction to Flash Memory, Proceedings of the IEEE, vol. 91, No. 4, Apr. 2003.

Dingsong Wei et al., WAFTL: A Workload Adaptive Flash Translation Layer with Data Partition, IEEE 27th Symposium on Massive Storage Systems and Technologies (MSST), May 23-27, 2011.

Taeho Kgil et al., Improving NAND Flash Based Disk Caches, International Symposium on Computer Architecture, Copyright

Samsung Electronics Co., Ltd. ,7th International Symposium on Advanced Gate Stack Technology, RRAM Technology from an Industrial Perspective, Process Development Team/RRAM PJT In-Gyu Baek, Sep. 2010.

Paolo Pavan et al., Flash Memory Cells-An Overview, Proceedings of the IEEE, vol. 85, No. 8, Aug. 1997.

Yoshihisa Iwata et al., A High-Density NAND EEPROM with Block-Page Programming for Microcomputer Applications, IEEE Journal of Solid-State Circuits, vol. 25, No. 2, Apr. 1990.

Tae-Sung Jung et al., A 117-mm2 3.3-V Only 128-Mb Multilevel NAND Flash Memory for Mass Storage Applications, IEEE Journal of Solid-State Circuits, vol. 31, No. 11, Nov. 1996.

Masayoshi Ohkawa et al., A 98 mm2 Die Size 3.3V 64-Mb Flash Memory with FN-NOR Type Four-Level Cell, IEEE Journal of Solid-State Circuits, vol. 31, No. 11, Nov. 1996.

Masaki Momodomi et al., An Experimental4-Mbit CMOS EEPROM with a NAND-Structured Cell, IEEE Journal of Solid-State Circuits, vol. 24, No. 5, Oct. 1989.

Ken Takeuchi et al., A Multipage Cell Architecture for High-Speed Programming Multilevel NAND Flash Memories, IEEE Journal of Solid-State Circuits, vol. 33, No. 8, Aug. 1998.

Shigeru Atsumi et al., A Channel-Erasing 1.8-V-Only 32-Mb NOR Flash EEPROM with a Bitline Direct Sensing Scheme, IEEE Journal of Solid-State Circuits, vol. 35, No. 11, Nov. 2000.

Taehee Cho et al., A Dual-Mode NAND Flash Memory: 1-Gb Multilevel and High-Performance 512-Mb Single-Level Modes, IEEE Journal of Solid-State Circuits, vol. 36, No. 11, Nov. 2001. Douglas J. Lee et al., Control Logic and Cell Design for a 4K NVRAM, IEEE Journal of Solid-State Circuits, vol. SC-18, No. 5, Oct. 1983.

Duane H. Oto et al., High-Voltage Regulation and Process Considerations for High-Density 5 V-Only E2PROM's, IEEE Journal of Solid-State Circuits, vol. SC-18, No. 5, Oct. 1983.

Gheorghe Samachisa et al., A 128K Flash EEPROM Using Double-Polysilicon Technology, IEEE Journal of Solid-State Circuits, vol. SC-22, No. 5, Oct. 1987.

Nelson Duann, Silicon Motion, Inc., Flash Memory Summit, SIC & MIC Hybrid, Santa Clara, CA, Aug. 2008.

Simona Boboiia et al., Write Endurance in Flash Drives: Measurements and Analysis, Usenix Conference on File and Storage Technologies, San Jose, CA, Feb. 2010.

Simona Boboiia et al. Write Endurance in Flash Drives: Measurements and Analysis, Handout at Unsenix Conference on File and Storage Technologies, San Jose, CA, Feb. 2010.

Silicon Systems, Increasing Flash SSD Reliability, StorageSearch. com, Apr. 2005.

Ismael Chang Ghalimi, Intalio, An Intalio White Paper, Cloud Computing is Memory Bound, May 2010.

Hynix, 32Gb NAND Flash, HY27UKO8BGFM, Product Description Sheet, Feb. 2007.

Chris Evans, Consultant with Langton Blue, SearchStorage.co.UK, Enterprise MLC: How flash vendors are boosting MLC write endurance, Jun. 3, 2011.

Jesung Kim et al., A Space-Efficient Flash Translation Layer for Compactflash Systems, IEEE Transactions on Consumer Electronics, vol. 48, No. 2, May 2002.

Garth Goodson et al., Design Tradeoffs in a Flash Translation Layer, HPCA West 2010 (High Perf Comp Arch Conference, Bangalore,

Abdul Rub Aamer Mohammed, Improving Hot Data Identification for Hybrid SLC/MLC Device; CSci 8980-Advanced Storage Systems, Spring 2009.

Yang Hu, Achieving Page-Mapping FTL Performance at Block-Mapping FTL Cost by Hiding Address Translation, 26th IEEE Symposium on Massive Storage Systems and Technologies (MSST) May 3-7, 2010.

Clinton w. Smullen, IVet al., Accelerating Enterprise Solid-State Disks with Non-Volatile Merge Caching, 2010 International Green Computing Conference, Aug. 15-18, 2010.

Monolithic 3D, Inc. Introducing our monolithic 3D resistive memory architecture, http://www.monolithic3d.com/2/post/2011/ 06/introducing-our-3d-resistive-memory-architecture.html, Jun. 27,

Song Jiang et al., S-FTL: An Efficient Address Translation for Flash Memory by Exploiting Spatial Locality, Proceedings of the MSST 2011, May 2011.

Greg Atwood et al., Intel Strata Flash TM Memory Technology Overview, Intel Technology Journal Q4 1997.

Moinuddin K. Qureshi et al., Morphable Memory System: A Robust Architecture for Exploiting Multi-Level Phase Change Memories, International Symposium on Computer Architecture, Saint-Malo, France, Jun. 19-23, 2010.

Abhishek Rajimwale et al., Block Management in Solid-State Devices, Usenix Conference, Jun. 14-19, 2009.

#### (56) **References Cited**

#### OTHER PUBLICATIONS

Brendan Gregg et al., Sun Storage 7000 Unified Storage System L2ARC: Second Level Adaptive Replacement Cache, Oracle White Paper—Sun Storage 7000 Unified Storage System L2ARC, May

Chunqiang Tang, FVD: a High-Performance Virtual Machine Image Format for Cloud, USENIX Conference Jun. 2011.

Anand Lal Shimpi, AnandTech, The Crucial m4 (Micron C400) SSD Review, Mar. 31, 2011.

Anand Lal Shimpi, AnandTech, The Intel SSD 320 Review: 25nm

G3 is Finally Here, Mar. 28, 2011.

Micron Technology, Inc., TN-29-42: Wear-Leveling Techniques in NAND Flash Devices Introduction, Oct. 2008.

\* cited by examiner

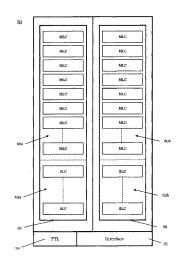

<u>FIG. 1</u>

FIG.2A

|                               | LOGICAL<br>ADDRESS RANGE | PHYSICAL<br>ADDRESS RANGE |

|-------------------------------|--------------------------|---------------------------|

|                               | R0                       | MLC/Block 0               |

|                               | R1                       | MLC/Block 1               |

| Remapping to SLC flash module | R2                       | SLC/Block 0               |

|                               | R3                       | MLC/Block 3               |

|                               | R4                       | MLC/Block 4               |

|                               | RN                       | MLC/Block N               |

FIG.2B

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

### **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

#### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.