# 1 Market and applications for NAND Flash memories

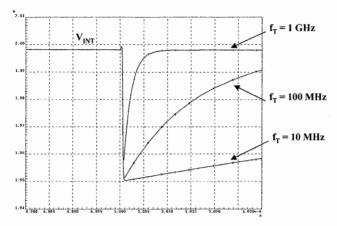

Gregory Wong\*

### 1.1 Introduction

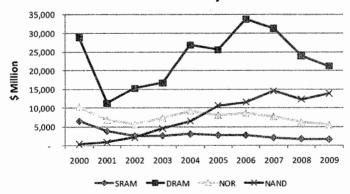

In the year 2000, the total semiconductor memory revenues of SRAM, DRAM, NOR Flash and NAND Flash memories amounted \$46 billion. As the decade closed in 2009, total revenues are projected to have declined 8.7% to \$42 billion. Of the major memory segments, only NAND Flash memory revenues have grown in the past decade at a CAGR of almost 50% (see Fig. 1.1).

Standalone SRAM saw a steady decline (CAGR -14.5%) throughout the decade from \$6.5 billion in 2000 to \$1.6 billion in 2009 as the L2 cache became integrated on the CPU and as low power DRAM replaces SRAM due to its lower cost structure.

After the bursting of the Internet bubble, DRAM declined by over 61% in 2001 before climbing back to \$33.8 billion in 2006. The latter half of the decade saw excessive oversupply resulting in a decline in revenues to \$21.2 billion in 2009.

# **Semiconductor Memory Revenues**

Fig. 1.1. Semiconductor memory revenues (Source: WSTS, Forward Insights)

<sup>\*</sup> Forward Insights, greg@forward-insights.com

R. Micheloni et al., *Inside NAND Flash Memories*, DOI 10.1007/978-90-481-9431-5\_1, © Springer Science+Business Media B.V. 2010

The NOR Flash market has shrunk almost 50% from \$10.3 billion in 2000 to \$5.5 billion in 2009 as NAND Flash penetrated the cell phone market in the latter half of the decade.

NAND Flash experienced some volatility during the decade but its extremely low cost structure has allowed it to enable new applications such as digital photography, portable storage, portable audio and video and multi-functional portable devices. NAND Flash started the decade at \$370 million and surpassed NOR Flash revenues in 2005. It grew 37 times to close out the decade at \$13.8 billion.

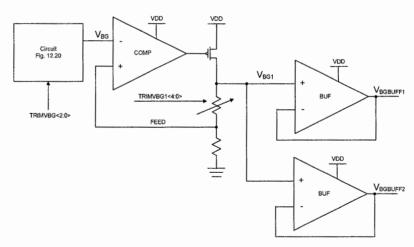

# 1.2 Flash memory architectures

Flash memory was invented by Dr. Fujio Masuoka of Toshiba Corp. in 1984. Based on Masuoka's invention, Intel Corp. commercialised common ground NOR Flash memory in 1988 seeing a non-volatile storage medium to storage program codes including a PC's BIOs and firmware for various consumer products. NOR Flash was also the basis for the first Flash memory cards and non-volatile solid state drives in the 1990s.

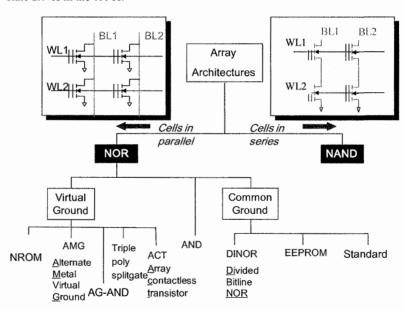

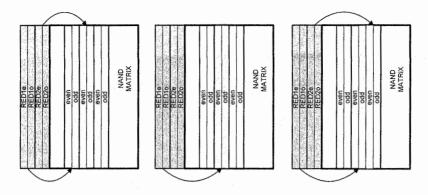

Fig. 1.2. Flash memory array architectures (Source: Forward Insights)

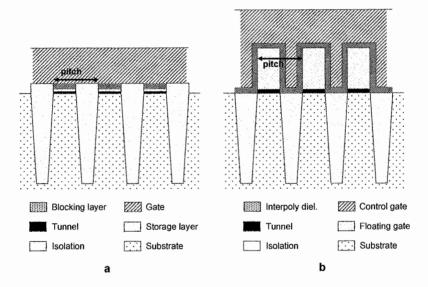

Toshiba Corp. introduced NAND Flash memory in 1988 which promised lower cost per bit than NOR Flash and faster program and erase throughput. Unlike NOR Flash which is organized on a byte or word basis, NAND Flash is organized into pages and erased on a block basis. A block consists of 64 or more pages. The organization of the NAND Flash is conducive to lower cost per bit but not suitable for random access. NAND Flash is therefore employed as a data storage medium similar to optical media and hard disk drives.

The two main array architectures are summarized in Fig. 1.2. NOR Flash memory employs a parallel array architecture where each cell may be accessed via a contact (Fig. 1.3). The direct cell access is the reason for the superior random performance of NOR Flash. The NOR array may be classified into the virtual ground or common ground array. A variety of device variations of these two classification have been introduced by various companies such as Saifun's NROM, Sharp's ACT and Renesas' AND, AG-AND and DINOR, however the mainstream NOR Flash is the common ground implementation manufactured by the likes of Numonyx, Samsung and Winbond.

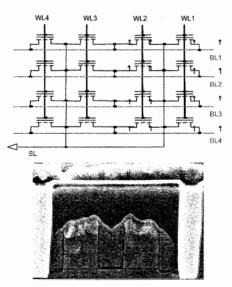

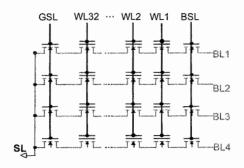

In contrast, the memory cells in NAND Flash are organized serially. Figure 1.4 shows 32 memory cells sandwiched between two large select transistors and two contacts. Random performance is slow due to the fact that there are no contacts directly accessing the memory cells. However, because there are only two contacts every 32 memory cells, the effective cell size is much smaller than for NOR Flash resulting in a smaller chip size and lower cost per bit. The cell size of NAND Flash is generally in the 4  $\rm F^2$  range where F is the design rule of the chip. Due to the parallel architecture of NOR Flash, its cell size is relatively large at 10  $\rm F^2$ .

Fig. 1.3. NOR array architecture (Source: Forward Insights)

4

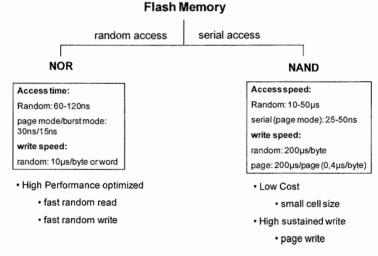

The device characteristics of NAND and NOR Flash memories are compared in Fig. 1.5. NOR Flash exhibits superior random read and write performance versus NAND Flash.

Fig. 1.4. NAND array architecture (Source: Forward Insights)

Fig. 1.5. NAND versus NOR (Source: Forward Insights)

However, NAND exhibits fast page writes due to the ability to write 4-8 kB simultaneously resulting in very high sequential write throughput. The serial architecture and small cell size make NAND Flash optimized for low cost mass storage whereas NOR Flash is optimized for performance code storage and execution.

# 1.3 Multi-bit per cell storage

### 1.3.1 Memories scaling

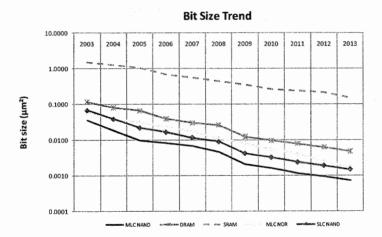

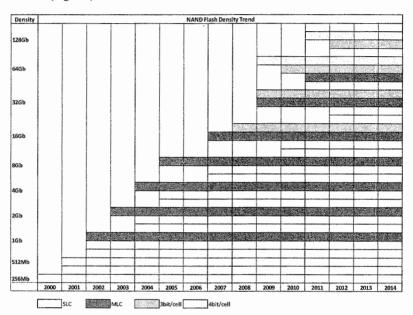

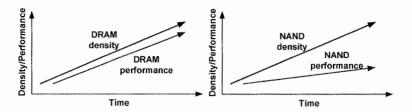

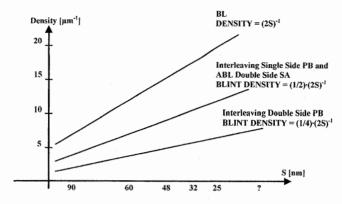

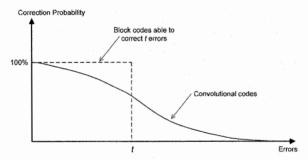

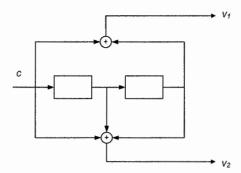

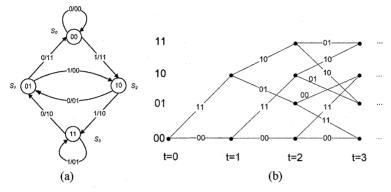

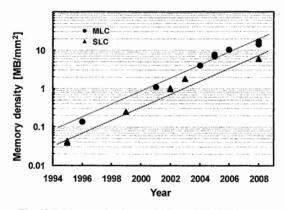

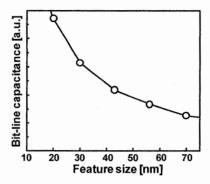

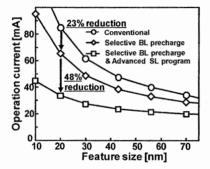

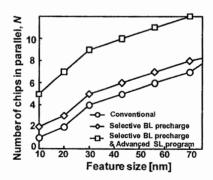

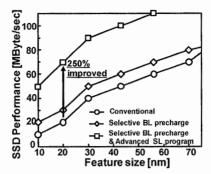

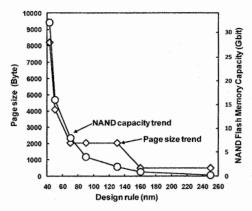

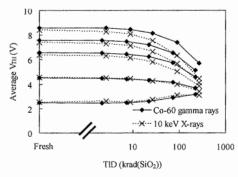

Where other semiconductor memories were on a 2 year cadence for new process technology introduction, NAND Flash memories have historically been on a 1 year cadence. This accelerated process scaling resulted in the bit size of SLC NAND overtaking MLC NOR in 2005 as shown in Fig. 1.6. MLC NAND is by far the lowest cost semiconductor memory with none of the memory technologies even close to being cost competitive. This is mainly due to the very small cell size combined with multi-level cell capability.

Fig. 1.6. Scaling (Source: Forward Insights)

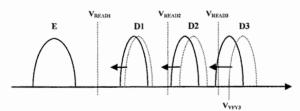

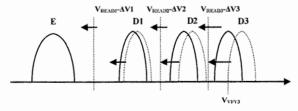

### 1.3.2 Multi-level cell concept

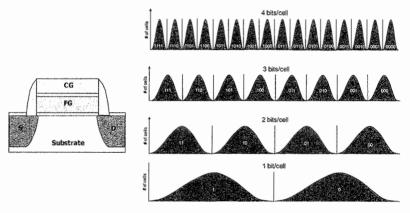

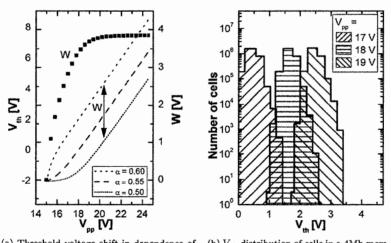

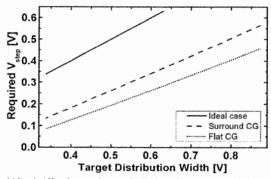

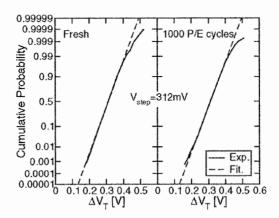

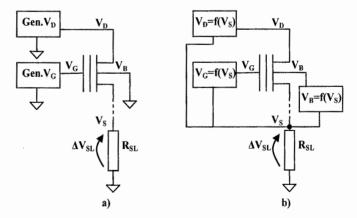

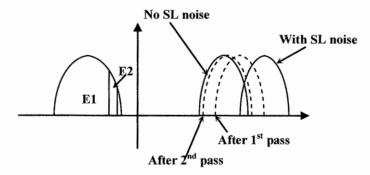

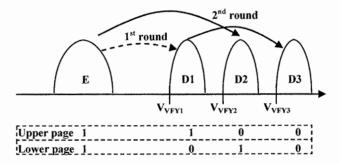

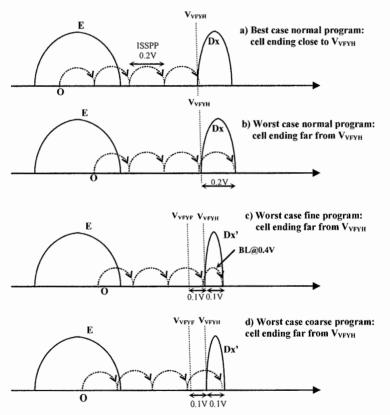

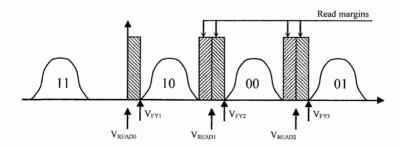

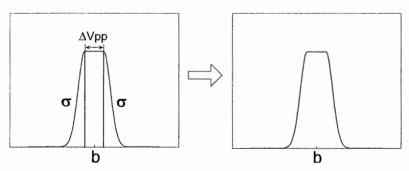

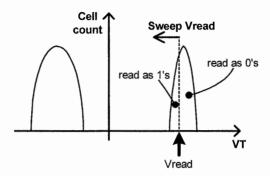

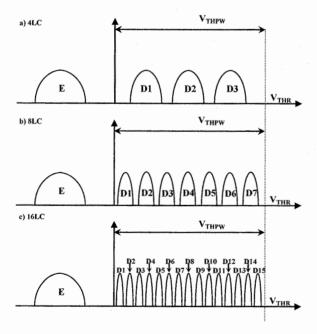

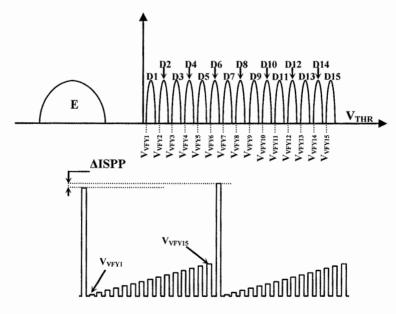

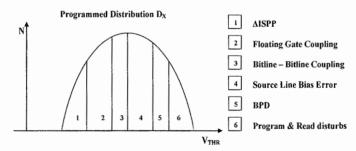

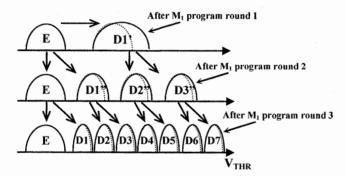

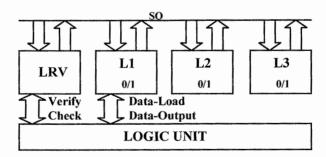

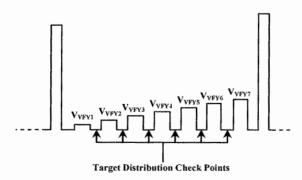

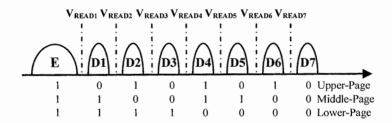

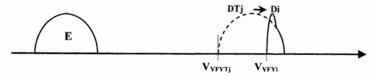

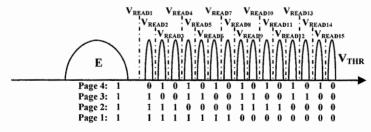

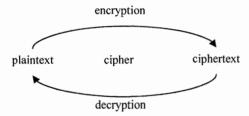

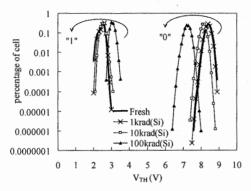

Figure 1.7 illustrates the concept of multi-level cell storage in Flash memories. Conventional SLC or single-level cell storage distinguishes between a '1' and '0' by having no charge or charge present on the floating gate of the Flash memory cell. By increasing the number of charge or voltage threshold (Vt) levels, more

than 1-bit per cell may be stored. Two bits per cell (MLC) storage is enabled by increasing the number of Vt levels to four representing 11, 10, 01 and 00. Similarly by increasing the number of voltage threshold levels to eight and 16, 3-bit per cell and 4-bit per cell storage is enabled.

The benefit of multi-level cell storage is that storage capacity may be increased without a corresponding increase in process complexity. The same fab equipment used to manufacture silicon wafers for SLC products may be used to manufacture MLC, 3-bit per cell and 4-bit per cell devices. However, multi-level cell storage requires accurate placement of the Vt charge levels so that the charge distributions don't overlap as well as accurate sensing of the different charge levels. As the number of Vt levels increases the time it takes for accurate programming and sensing increases. Additional circuitry and programming algorithms are necessary to ameliorate the degradation of the performance and endurance of such devices.

However in effect, transitioning from SLC to MLC to 3-bit to 4-bit per cell technology is equivalent to a partial shrink of the device from one process technology generation to the next without additional capital investment.

Fig. 1.7. Multi-level storage in floating gate NAND Flash memory

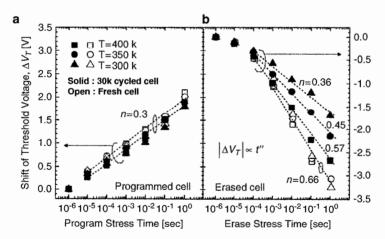

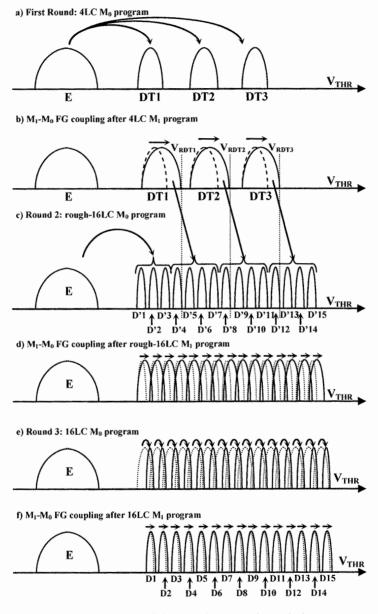

### 1.3.3 NAND scaling

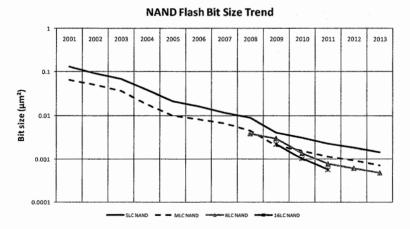

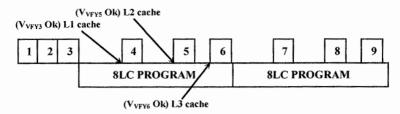

Figure 1.8 shows the bit size trend for SLC, MLC, 8LC (3-bit per cell) and 16LC (4-bit per cell) technologies. The bit size is a proxy for the cost. The first MLC NAND Flash chip was introduced at the end of 2001 by SanDisk and Toshiba. It was a 1 Gb chip based on 0.16  $\mu m$  process technology. Subsequent MLC generations were introduced on an almost yearly basis.

The first commercial production of 8LC began in 2008 also by SanDisk and Toshiba. The device, a 16 Gb product based on 56 nm process technology was introduced at a process technology one generation behind the mainstream MLC

products. As a result, the device was short-lived since the MLC products based on 43 nm technology were more cost-competitive than the 8LC product. However in 2010, the cost benefits of 8LC technology are expected to be realized as 8LC is manufactured on the same process technology as MLC.

As with 8LC, 16LC also from SanDisk and Toshiba was introduced in 2009 on a mature process technology – 43 nm. As a result, the first product – a 64 Gb chip – is not cost competitive with the mainstream 32 nm MLC products. It is mainly being used as a learning vehicle. Only when 16LC can be manufactured on the leading edge process technology will the full cost benefits be realized.

Note that the cost per bit reduction becomes progressively smaller as one transitions from SLC to MLC to 8LC to 16LC. An approximate 40–50% reduction can be obtained moving from SLC to MLC but this figure drops to 20% for MLC to 8LC and 10% for 8LC to 16LC. As a result, the economic benefit of 16LC may not be enough to justify the additional design efforts to implement it.

One of the main scaling challenges is that the number of electrons stored in the floating gate is decreasing significantly with each process generation. This has consequences for the sensing of the data value stored and data retention. These issues combined with inter-cell interference will make 16LC a less scalable technology. To overcome these challenges, innovative programming algorithms and signal processing techniques filter the signal from the noise will be required for future generations of NAND Flash.

Fig. 1.8. NAND Flash bit size trend (Source: Forward Insights)

### 1.3.4 Capacity

Until 2006, MLC chip density was doubling every year. This doubling of chip density is being extended to 18 months to 2 years as the scaling challenges

increase. As MLC became mainstream, SLC began to lag behind in process migration and density transition. For example, it will take 3 years for the transition from 8 to 16 Gb SLC chips.

The benefit of 8LC and 16LC is the ability to enable monolithic chip densities which would not be possible with SLC and MLC. For example, the first 16LC device was the first monolithic chip with a capacity of 64 Gb. It is expected that 8LC and 16LC will continue to lead the introduction of the highest capacity devices (Fig. 1.9).

Fig. 1.9. NAND Flash density roadmap (Source: Forward Insights)

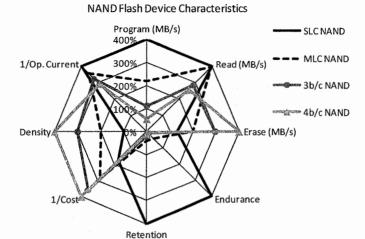

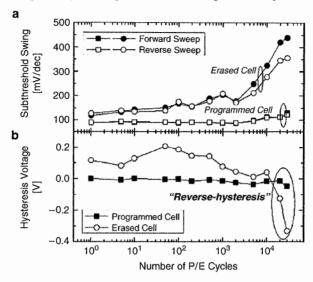

#### 1.3.5 Device characteristics

The lower costs associated with multi-level cell technology does not come for free. The lower cost comes at the expense of reduced performance and endurance. A comparison of the device characteristics for SLC, MLC, 3- and 4-bit per cell is summarized in Fig. 1.10. Significant degradation in endurance, retention and write performance occurs with increasing number of bits per cell. Read performance and operating current are also negatively impacted.

Fig. 1.10. NAND device characteristics (Source: Forward Insights)

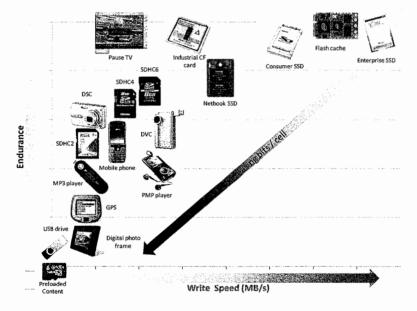

Fig. 1.11. Applications for multi-bit per cell NAND Flash memories (Source: Forward Insights)

Of course, the trade-off is higher capacity and lower cost per bit. Erase performance actually improves due to the larger block size.

The implication of the disparate device characteristics is that the applications usage model will dictate the type of devices that will be used.

Figure 1.11 provides a simplified overview of the applications based on two key parameters — endurance and write speed. Applications with less demanding endurance and write performance requirements are better suited for devices with multi-bit per cell storage. Content storage and archiving may be facilitated by 4-bit per cell devices. Consumer applications that are largely read intensive such as MP3/PMP players, Flash memory cards, personal navigation devices can use 3-bit per cell devices. MLC may be found in consumer and netbook solid state drives and SLC for solid state drives in the enterprise. However, for certain enterprise applications especially read intensive with low duty cycles, MLC may be sufficient.

# 1.4 Market and applications

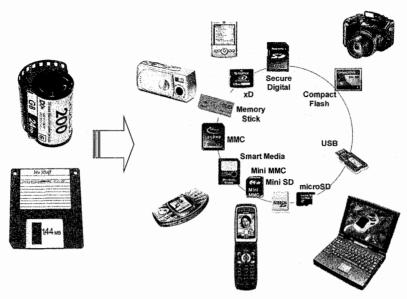

### 1.4.1 Removable portable storage

The application which triggered the rise of NAND Flash was digital photography and digital storage. The first Flash memory card format, Compact Flash I incorporated NOR Flash at its inception in 1994. The SmartMedia card introduced in 1995 was the first removable media format to incorporate NAND Flash followed by the MultiMedia Card in 1997, Memory Stick in 1998, Secure Digital in 1999, and xD-Picture Card in 2002. Miniaturized "mini" and "micro" versions of these cards have been subsequently introduced.

Figure 1.12 shows the plethora of Flash memory card form factors that have replaced analog film. In fact, Flash memory cards store not only images but also audio and video enabling portable transport of files from one device to another. USB Flash drives introduced in 2000 by Trek and IBM have driven the floppy disk to extinction.

### 1.4.2 Embedded storage

NAND Flash is employed for code/data storage or data storage in a variety of portable and mobile applications such as cellular phones, MP3/PMP players, digital video camcorders and personal navigation devices. NAND Flash may be embedded in applications in several ways.

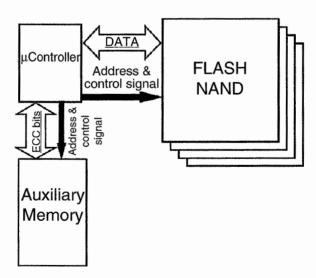

Raw NAND – NAND Flash chips are soldered onto the PCB of the device with the host-side handling the Flash translation layer (FTL), bad block management and error correction (ECC). For example, MP3/PMP players employ a Flash controller to manage the raw NAND.

Fig. 1.12. Removable portable storage

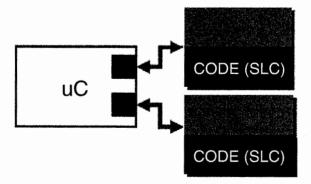

NAND with on-chip controller — The NAND Flash devices are used for code and data storage with only the Flash translation layer managed by the host. In some instances, these devices such as ONENAND from Samsung, Toshiba and Numonyx and mDOC (mobile Disk-on-Chip) from SanDisk come with a NOR Flash interface and act as a replacement for the NOR Flash.

Multi-chip Package (MCP) – The NAND Flash is combined with both a NOR Flash and low power DRAM or just a DRAM for code and data storage. MCPs are primarily used in mobile phones.

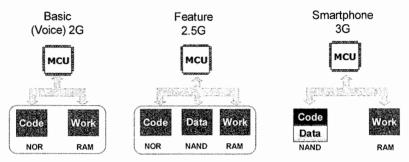

An overview of memory architectures for different mobile phones is presented in Fig. 1.13. The architectures depend on the functionality of the phones.

The primary function of entry level mobile phones is voice communications. The phones are generally capable of SMS and basic web browsing. As a result, large memory capacity is not a requirement. Entry level mobile phones employ a XIP (execute in place) architecture whereby the program code is stored and directly executed from the NOR Flash and pseudo-SRAM is used as the working memory. This memory system is cost optimized solution for small memory densities and low power.

Feature phones provide voice, MMS, camera, audio, video and web browsing functionality. Higher capacity for data storage is therefore necessary. Feature phones combine three memories – NOR Flash for code execution, NAND Flash for data storage and RAM as a working memory. This architecture is essentially a XIP with additional NAND Flash for data storage.

Smartphones have morphed into convergence devices. In addition to the feature phone capabilities, these devices are designed for multi-tasking – running more than one application at the same time, e-mailing and infotainment.

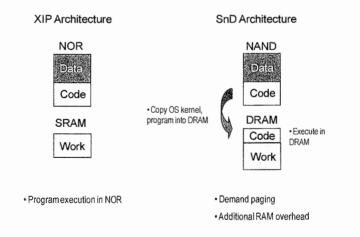

The store and download (SnD) architecture used in smartphones employs a PC-like approach. Instead of storing in NOR Flash, the code is stored in NAND Flash, copied into DRAM and executed from DRAM. In this scenario, code has to be swapped in and out of the DRAM for execution. Since the RAM has to act as both a code execution and work memory, the RAM capacity is larger than the RAM required in the NOR/NAND/RAM implementation in feature phones. Because of the very low cost per bit of NAND Flash, this architecture is cost optimized for medium/large memory capacity requirements at the expense of higher power consumption and longer boot time than the XIP implementation.

Fig. 1.13. Memory system architectures in mobile phones

Fig. 1.14. Store and download versus XIP architecture

Figure 1.14 contrasts the SnD and XIP architectures.

Managed NAND solutions – NAND Flash device ECC requirements and in some cases page sizes and block sizes are changing with each new technology generation. Instead of having to continually update the host firmware to manage these details, these changes are managed within the device by combining raw NAND and a controller in a package. All the FTL, bad block management and ECC are handled within the package allowing the host to perform only a simplified read/write to the device. The host side requires a basic driver to interface with the managed NAND device typically using a eMMC or eSD protocol. The raw NAND and managed NAND implementations are illustrated in Fig. 1.15.

Fig. 1.15. Managed NAND versus raw NAND (Source: Micron Technology)

### 1.4.3 Solid state drives

The first SSDs pioneered by StorageTek in 1978 were RAM-based SSDs. It wasn't until late 1980s and early 1990s when the first Flash-based SSDs were developed. Western Digital demonstrated a 2.5" NAND Flash SSD in 1989, however the main promoters of Flash-based SSDs, SanDisk and Intel, based their SSDs on NOR Flash technology in the early 1990s. Due to the higher cost of NOR Flash versus DRAM, Flash-based SSDs were relegated to niche markets.

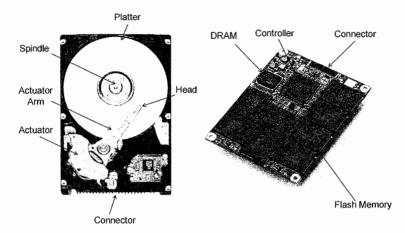

However, the remarkable and rapid price decline of NAND Flash memory in recent years which has driven analog film and the floppy disk to extinction is now enabling NAND Flash memory to penetrate the realm of hard disk drives (HDDs). Solid state drives (SSDs) offer the promise of significantly better performance and reliability due to the lack of mechanical parts.

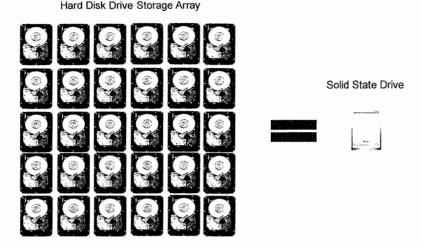

Fig. 1.16. Solid state drive versus hard disk drive (Source: Toshiba Corp., Forward Insights)

Figure 1.16 details the major components of an SSD and HDD. The HDD, being based on storage in a spinning magnetic platter, requires an actuator and actuator arm to move the head to the appropriate sector to be read or written. This movement of the read head results in extremely long latencies in the milliseconds and a DRAM buffer is used to hide the seek time. The HDD controller, particularly if it is a system-on-chip, incorporates the processor, servo control logic, interface, error correction code, disk sequencer and buffer controller.

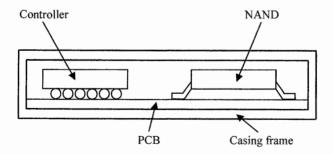

In contrast, the SSD contains no mechanical parts and consists of a few major components: NAND Flash memory, SSD controller, connector, DRAM, PCB and passives. In addition, because of the small size of NAND Flash memory, the SSD form factor is not limited to standard 1.8, 2.5 or 3.5" HDD form factors but can also come in module form.

NAND-based SSDs started out in industrial and military where ruggedness and reliability are a priority. In 2006, the first SSD for personal computers was introduced followed by SSDs for enterprise computing.

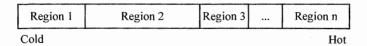

Table 1.1 summarizes the NAND Flash/SSD usage models in the different market segments. There are several ways NAND Flash or SSDs may utilized. Firstly, it can act as an alternate storage device, in many cases replacing a HDD for latency or reliability improvement and power consumption reduction. An optimized OS or file-system is required to obtain the full benefits of the SSD.

Secondly, the SSD may act as an I/O accelerator. I/O acceleration is primarily used in the enterprise computing environment. A software driver is required for this approach.

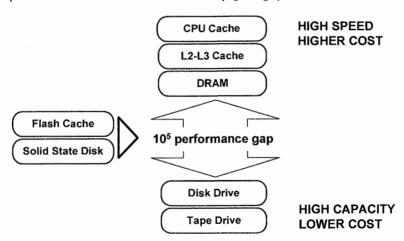

Thirdly, the SSD/NAND Flash may be part of the tiered system memory and replace part of the DRAM. Due to the better economics of NAND Flash versus DRAM, this allows an increase in system memory storage capacity with the

benefits of reduced power consumption. To manage this tiered system memory, the kernel memory manager needs to be designed to manage the Flash memory.

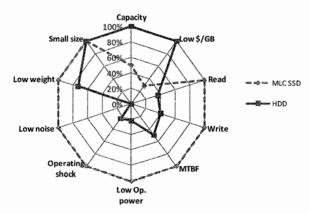

A comparison of SSD and HDD in PCs (Fig. 1.17) shows that SSDs are superior to HDDs in all aspects except for cost and capacity. The cost and capacity are related since the major impediment to higher SSD capacities is the high cost per gigabyte.

Table 1.1. NAND usage model

| NAND Usage Model       | Consumer | Enterprise   | Industrial | Military |

|------------------------|----------|--------------|------------|----------|

| Alternate Storage      | √        | <b>V</b>     | 7          | 7        |

| I/O Accelerator        |          | $\checkmark$ |            |          |

| Extended System Memory | √ .      | √            |            |          |

In the enterprise space, high throughput and low access latency are critical. Enterprise HDDs employ several techniques to improve system throughput and decrease the access latency. High performance 15 k rpm HDDs may be organized in a RAID configuration with the data being striped across multiple disks thereby increasing the bandwidth of the total system. Adding HDDs increase system bandwidth but result in increased space, power and cooling requirements.

"Short-stroking" the HDDs whereby data is placed on the outer tracks of the disk to reduce the seek time of the mechanical heads reduces system access latencies. However, this entails that only part of the HDD is being used to achieve the required performance resulting in excess storage capacity than would otherwise be necessary. As illustrated in Fig. 1.18, one SSD can replace several striped, short-stroked HDDs.

### SSDs vs. HDDs in PCs - Performance Characteristics

Fig. 1.17. 2.5" SSDs versus HDDs in PCs – performance characteristics (Source: Forward Insights)

Fig. 1.18. Enterprise SSD value proposition

Figure 1.19 shows that although on a price per GB basis, HDDs are far superior to SSDs, the cost for an HDD system to obtain comparable metrics in terms of \$/IOPS, IOPS/GB or IOPS/W is far higher than for SSDs. This is just the storage comparison. When the total system is considered, far fewer SSDs will be required for a given performance than HDDs. If the maintenance, power and space savings are included, the economics of using SSDs are even more attractive.

| SPECIFICATION  | Enterprise Class SSD | Enterprise Class HDD | Delta  |

|----------------|----------------------|----------------------|--------|

| Capacity (GB)  | 146                  | 73                   | 100%   |

| Price (\$)     | 12,500               | 389                  | 3113%  |

| Performance    | 1                    |                      |        |

| Random         | 1                    |                      | 1      |

| Read           | 52,000 IOP\$         | 300 IOPS (est)       | 17233% |

| Write          | 18,000 IOPS          | 300 IOPS (est)       | 5900%  |

| Power          | i                    |                      | l      |

| Operating mode | 8.4W                 | 10-12W               | -24%   |

| \$ / GB        | 85.62                | 5.33                 | 1607%  |

| \$ / IOPS      |                      |                      | l      |

| Read           | 0.24                 | 1.30                 | -81%   |

| Write          | 0.69                 | 1.30                 | -46%   |

| IOPS / GB      |                      |                      | i      |

| Read           | 356                  | 4                    | 8567%  |

| Write          | 123                  | 4                    | 2900%  |

| IOPS / W       |                      |                      |        |

| Read           | 6,190                | 27                   | 22598% |

| Write          | 2,143                | 27                   | 7757%  |

Fig. 1.19. Enterprise SSD versus HDD key metrics

### 1.5 Market outlook

In the early years, the NAND Flash market was driven by removable storage applications such as the Flash memory card following by the USB Flash drive. In 2004, NAND Flash began to replace 1" HDD in MP3 players led by Apple's iPod Mini. The era of high capacity embedded Flash storage in mobile phones began with the 4 and 8 GB iPhone from Apple Corp. in 2007. Prior to 2007, smartphones only had relatively low density Flash on-board and in some models, high density storage was supplemented via a slot which allowed the insertion of a Flash memory card. The iPhone is not just a phone but a convergence device incorporating camera, video, audio and gaming functionalities supported by content and applications from an online store.

Following the iPhone's lead, smartphone from other handset manufacturers are increasing the embedded Flash memory storage of their devices and mobile market is forecast to become the major consumer of NAND Flash gigabytes within the next 5 years.

The next frontier after consumer and communications is computing. NAND Flash-based SSDs are expected to become a new driver of NAND Flash bit consumption beyond 2012 driven by adoption of SSDs in mainstream consumer PCs.

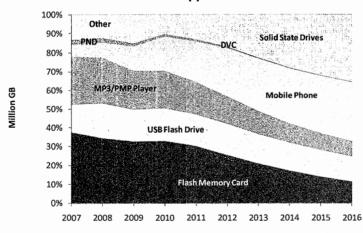

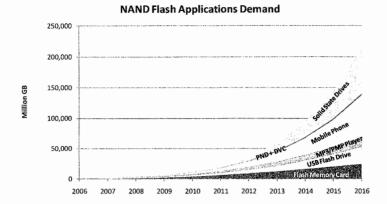

The NAND Flash industry's historical triple digit bit growth ended in 2009 as a result of the global economic downturn. As technology transitions slow down, bit growth is forecast to experience a more moderate 69% CAGR from 2007 to 2016 (Figs. 1.20 and 1.21).

### **NAND Flash Applications Demand**

Fig. 1.20. NAND Flash applications demand (% GB) (Source: Forward Insights)

Fig. 1.21. NAND Flash applications demand (Source: Forward Insights)

NAND Flash memory is facing serious scaling issues and it is within the next 5 years, that a successor technology is expected take the reins and fuel the insatiable storage demands of emerging applications.

# 2 NAND overview: from memory to systems

R. Micheloni<sup>1</sup>, A. Marelli<sup>2</sup> and S. Commodaro<sup>3</sup>

### 2.1 Introduction

It was in 1965, just after the invention of the bipolar transistor by W. Shockley, W. Brattain and J. Bardeen, that Gordon Moore, co-founder of Intel, observed that the number of transistors per square centimeter in a microchip doubled every year. Moore thought that such trend would have proven true for the years to come as well, and indeed in the following years the density of active components in an integrated circuit kept on doubling every 18 months. For example, in the 18 months that elapsed between the Pentium processor 1.3 and the Pentium-4, the number of transistors grew from 28 to 55 million.

Today, a standard desktop PC has processors whose operating frequency is in the order of some gigahertz, while its memory can store as much information as terabytes.

In this scenario, a meaningful portion of the devices produced is represented by memories, one of the key components of any electronic systems.

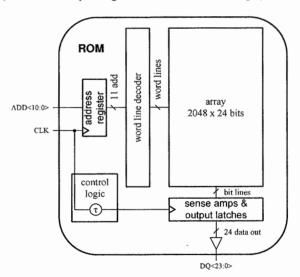

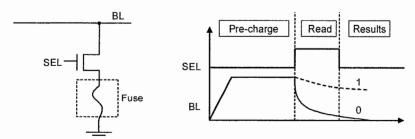

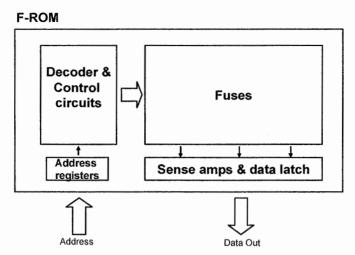

Semiconductor memories can be divided into two major categories: RAM, acronym for *Random Access Memories*, and ROM, acronym for *Read Only Memories*: RAM loses its content when power supply is switched off, while ROM virtually holds it forever. A third category lies in between, i.e. NVM, acronym for *Non-Volatile Memories*, whose content can be electrically altered but it is also preserved when power supply is switched off. These are more flexible than the original ROM, whose content is defined during manufacturing and cannot be changed by the consumer anymore.

The history of non-volatile memories began in the 1970s, with the introduction of the first EPROM memory (*Erasable Programmable Read Only Memory*). Since then, non-volatile memories have always been considered one of the most important families of semiconductors and, up to the 1990s, their interest was tied up more to their role as a product of development for new technologies than to their economic value. Since the early 1990s, with the introduction of non-volatile Flash memories into portable products like mobile phones, palmtop, camcorders, digital cameras and so on, the market of these memories has experienced a stunning increase.

<sup>1</sup> Integrated Device Technology, rino.micheloni@ieee.org

<sup>&</sup>lt;sup>2</sup> Integrated Device Technology, alessiamarelli@gmail.com

<sup>&</sup>lt;sup>3</sup> Pegasus MicroDesign, stefano commodaro@yahoo.it

R. Micheloni et al., Inside NAND Flash Memories, DOI 10.1007/978-90-481-9431-5 2,

<sup>©</sup> Springer Science+Business Media B.V. 2010

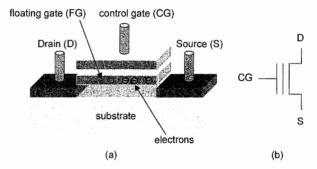

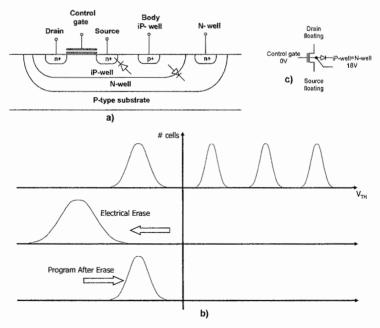

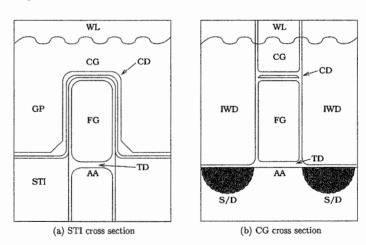

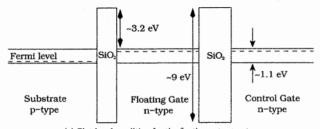

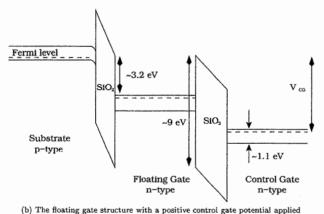

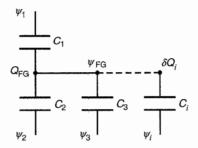

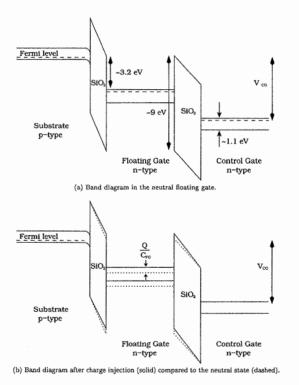

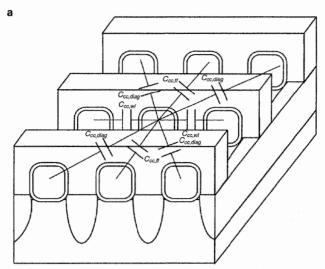

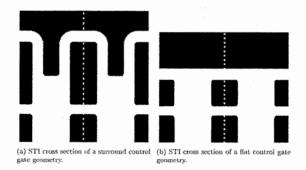

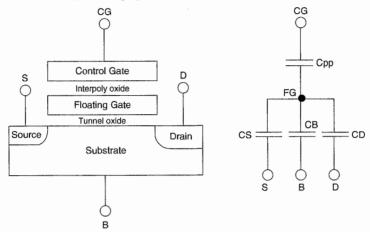

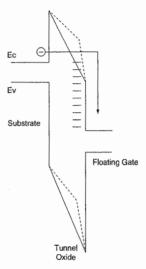

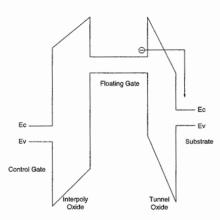

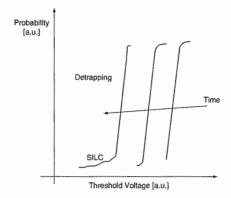

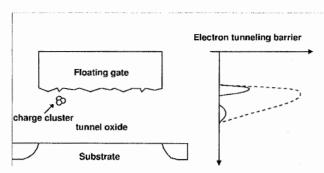

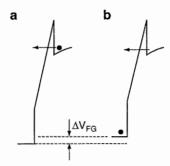

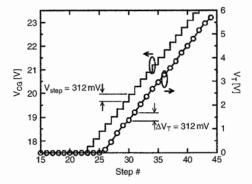

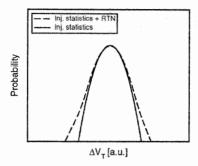

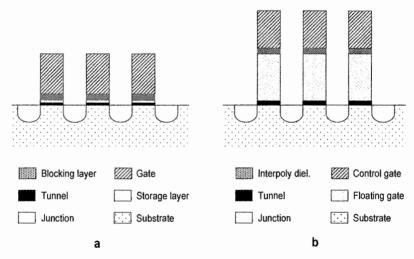

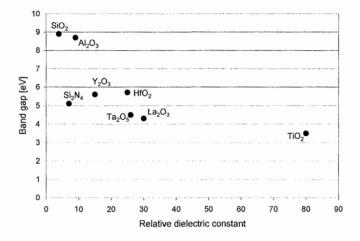

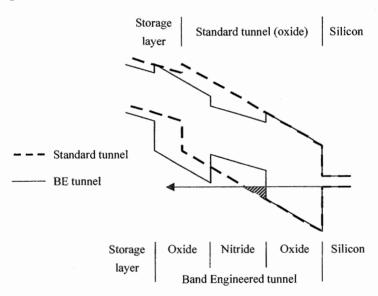

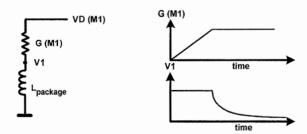

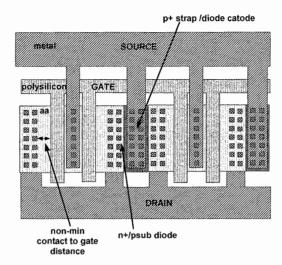

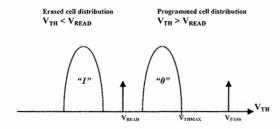

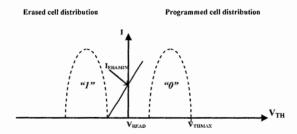

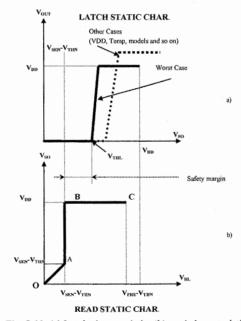

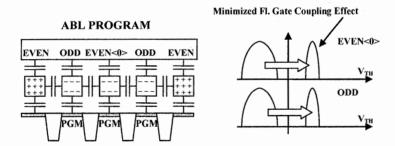

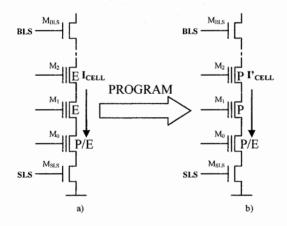

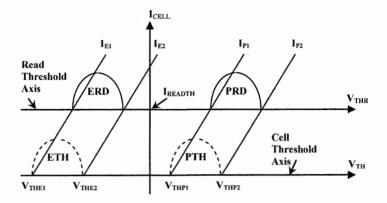

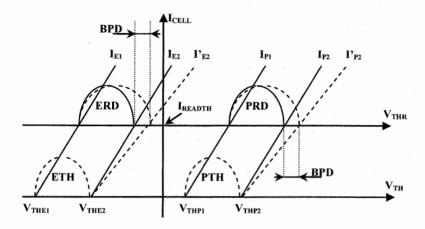

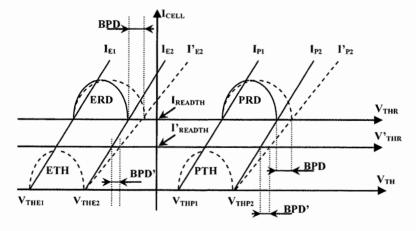

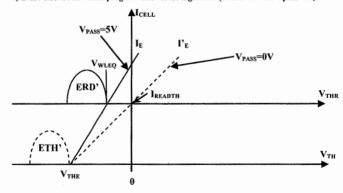

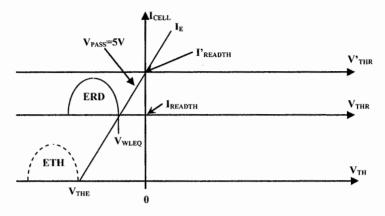

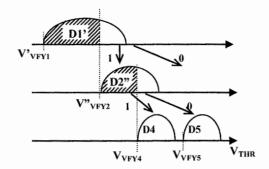

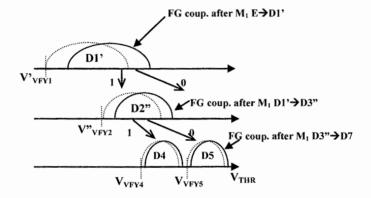

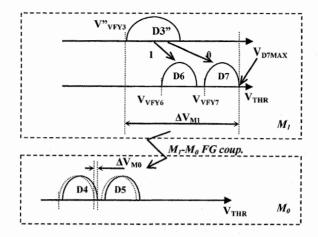

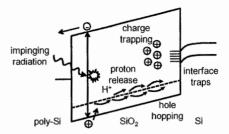

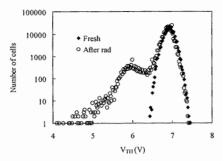

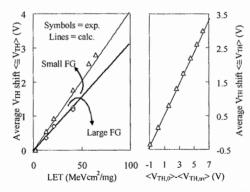

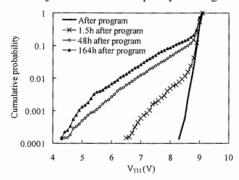

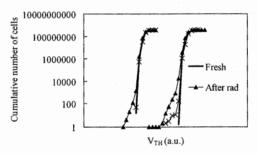

The most popular Flash memory cell is based on the *Floating Gate* (FG) technology, whose cross section is shown in Fig. 2.1. A MOS transistor is built with two overlapping gates rather than a single one: the first one is completely surrounded by oxide, while the second one is contacted to form the gate terminal. The isolated gate constitutes an excellent "trap" for electrons, which guarantees charge retention for years. The operations performed to inject and remove electrons from the isolated gate are called program and erase, respectively. These operations modify the threshold voltage V<sub>TH</sub> of the memory cell, which is a special type of MOS transistor. Applying a fixed voltage to cell's terminals, it is then possible to discriminate two storage levels: when the gate voltage is higher than the cell's V<sub>TH</sub>, the cell is on ("1"), otherwise it is off ("0").

It is worth mentioning that, due to floating gate scalability reasons, charge trap memories are gaining more and more attention and they are described in Chap. 5, together with their 3D evolution.

Fig. 2.1. (a) Floating gate memory cell and (b) its schematic symbol

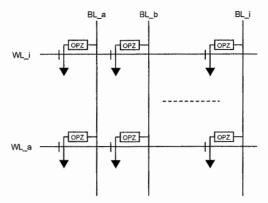

# 2.2 NAND memory

### 2.2.1 Array

The memory cells are packed to form a matrix in order to optimize silicon area occupation. Depending on how the cells are organized in the matrix, it is possible to distinguish between NAND and NOR Flash memories. This book is about NAND memories as they are the most widespread in the storage systems. NOR architecture is described in great details in [1].

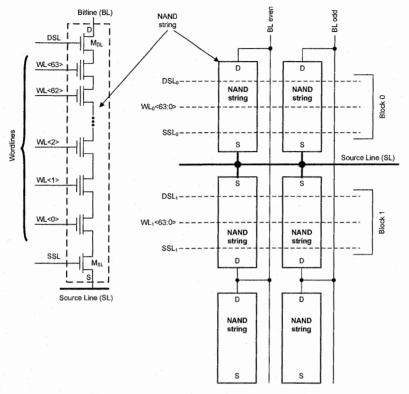

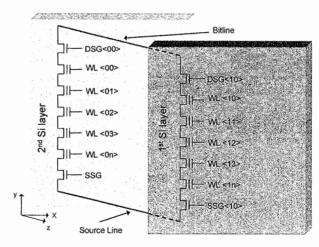

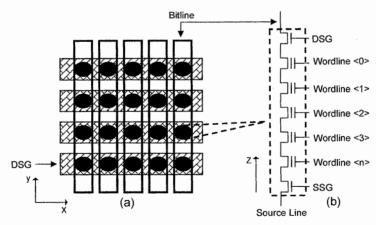

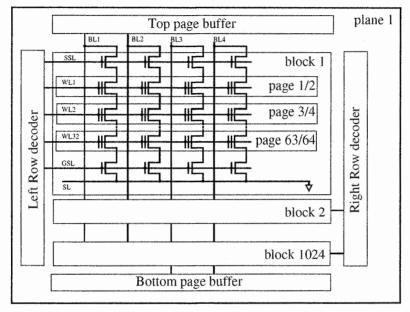

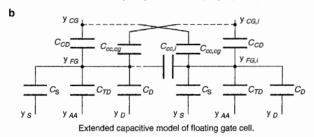

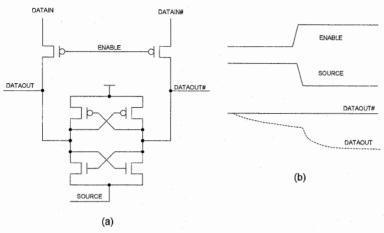

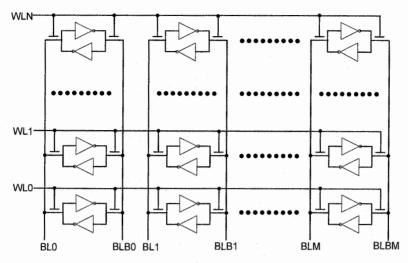

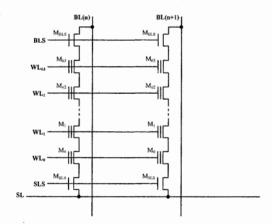

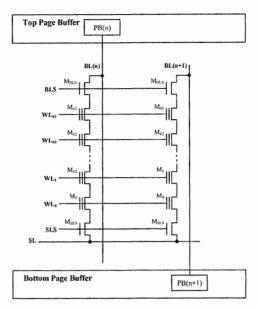

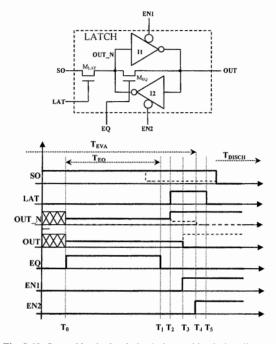

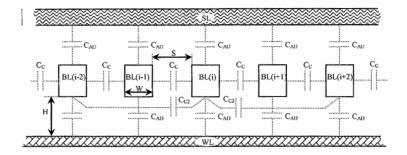

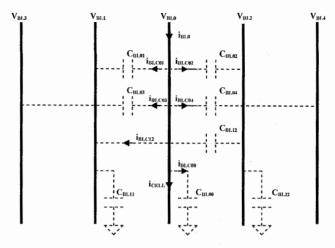

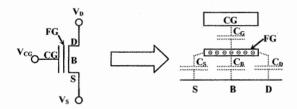

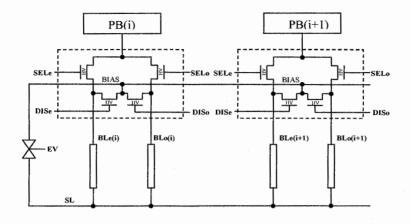

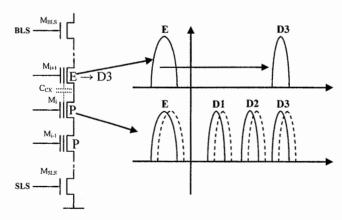

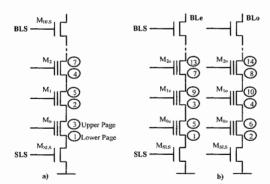

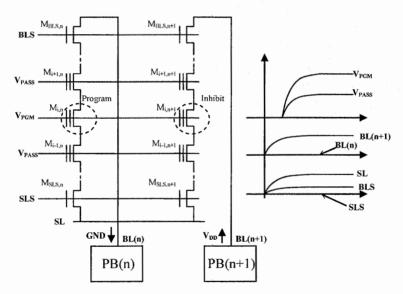

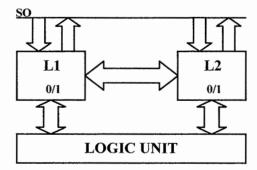

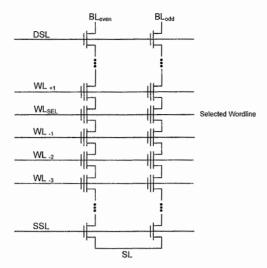

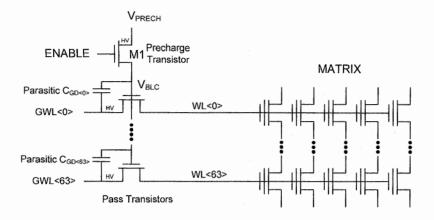

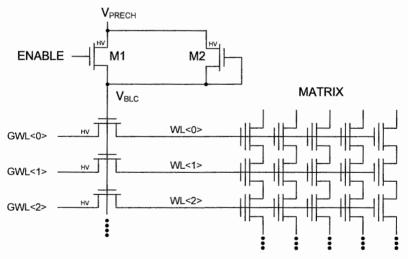

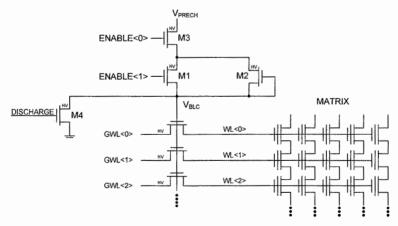

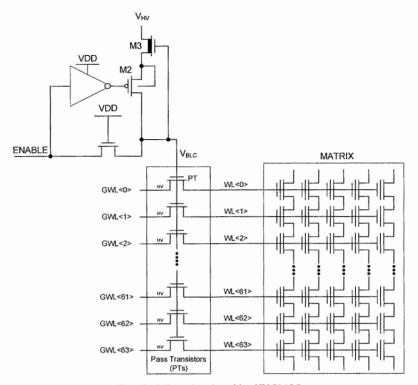

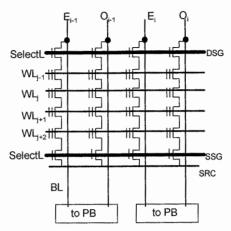

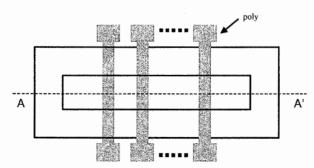

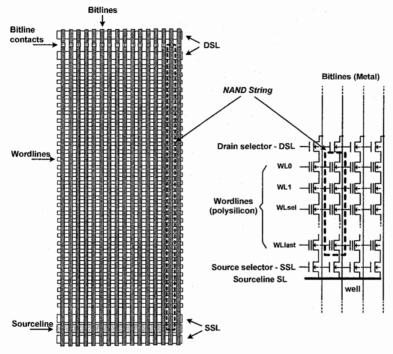

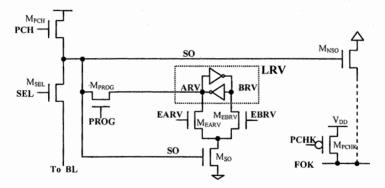

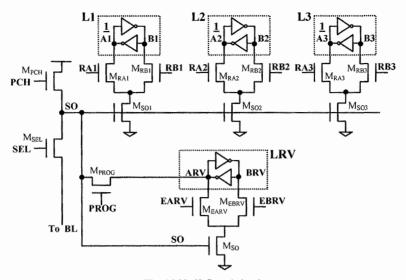

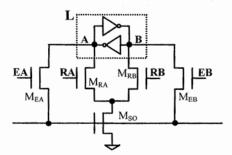

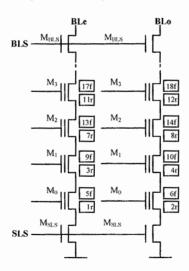

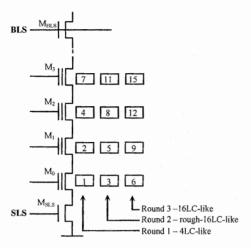

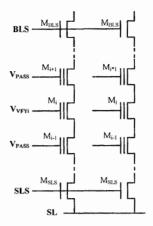

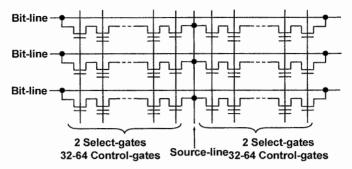

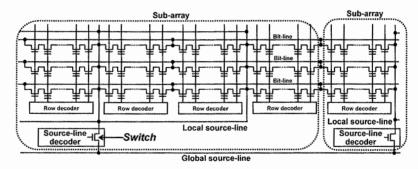

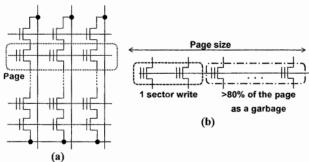

In the NAND string, the cells are connected in series, in groups of 32 or 64, as shown in Fig. 2.2. Two selection transistors are placed at the edges of the string, to ensure the connections to the source line (through  $M_{SL}$ ) and to the bitline (through  $M_{DL}$ ). Each NAND string shares the bitline contact with another string. Control gates are connected through wordlines (WLs).

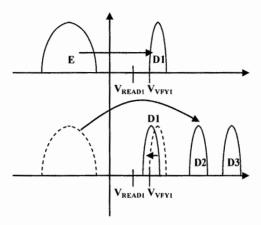

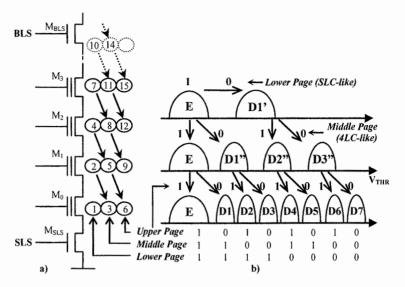

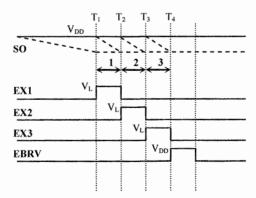

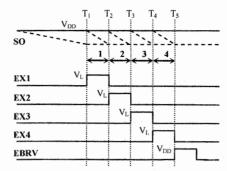

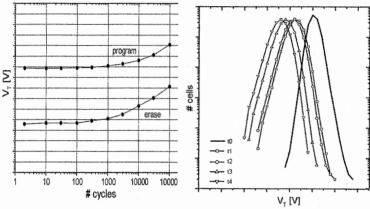

Fig. 2.2. NAND string (left) and NAND array (right)

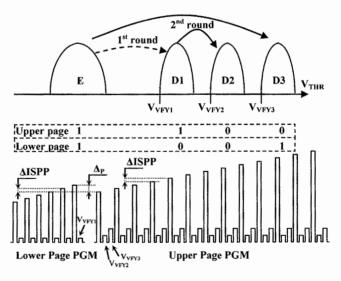

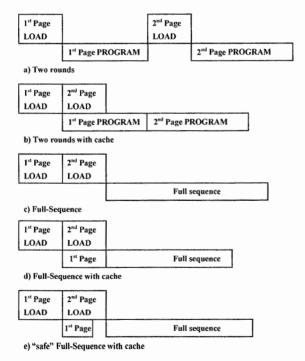

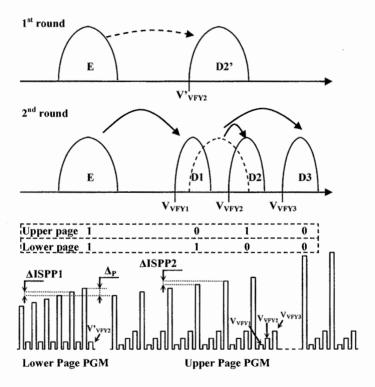

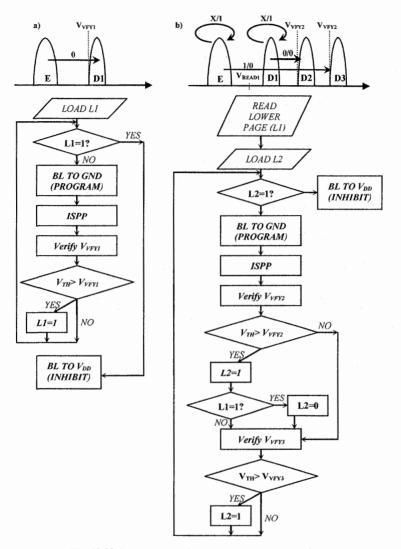

Logical pages are made up by cells belonging to the same wordline. The number of pages per wordline is related to the storage capabilities of the memory cell. Depending on the number of storage levels, Flash memories are referred to in different ways: SLC memories store 1 bit per cell, MLC memories (Chap. 10) store 2 bits per cell, 8LC memories (Chap. 16) store 3 bits per cell and 16LC memories (Chap. 16) store 4 bits per cell.

If we consider the SLC case with interleaved architecture (Chap. 8), even and odd cells form two different pages. For example, a SLC device with 4 kB page has a wordline of 65,536 cells.

Of course, in the MLC case there are four pages as each cell stores one *Least Significant Bit* (LSB) and one *Most Significant Bit* (MSB). Therefore, we have:

- MSB and LSB pages on even bitlines

- MSB and LSB pages on odd bitlines

All the NAND strings sharing the same group of wordlines are erased together, thus forming a Flash block. In Fig. 2.2 two blocks are shown: using a bus representation, one block is made up by  $WL_0$ <63:0> while the other one includes  $WL_1$ <63:0>.

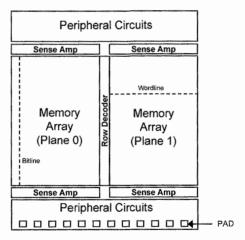

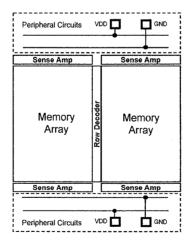

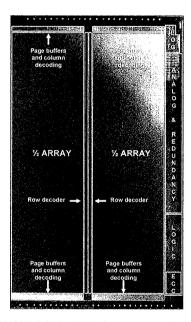

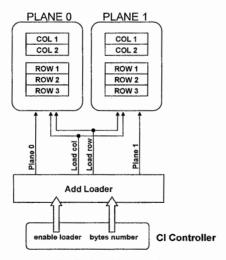

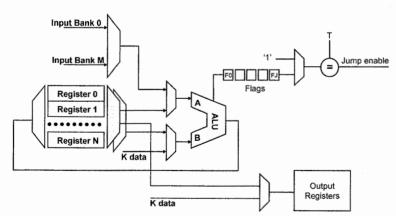

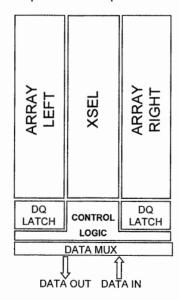

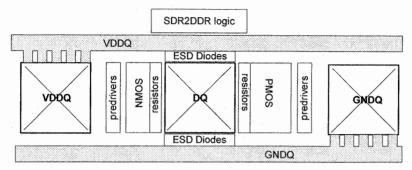

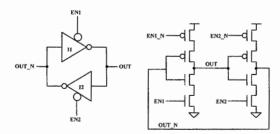

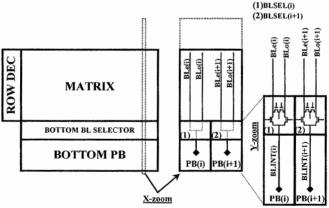

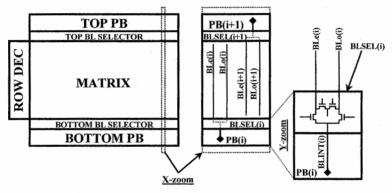

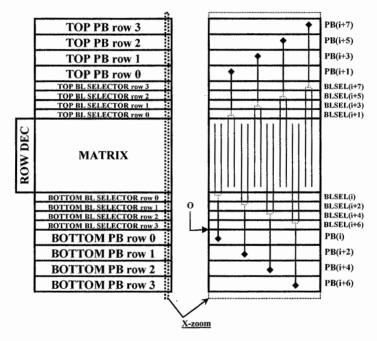

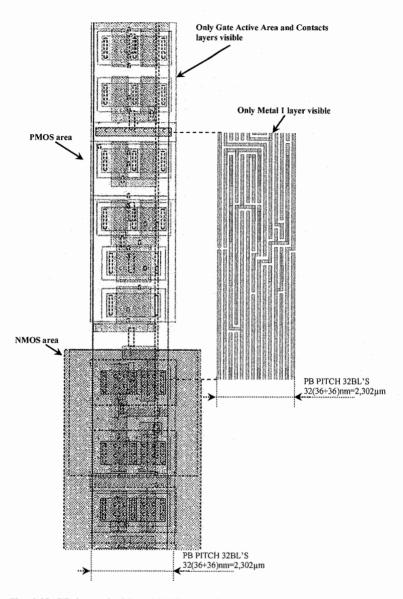

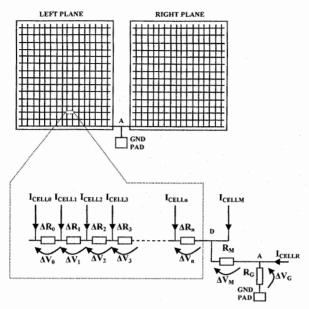

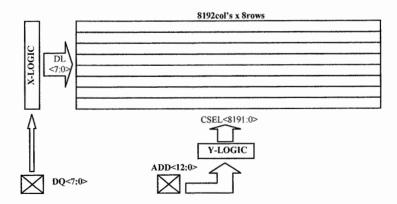

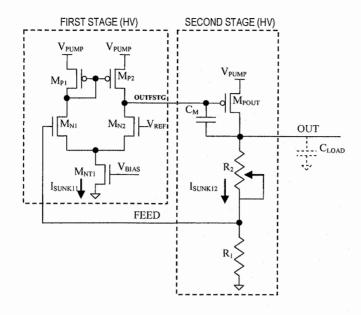

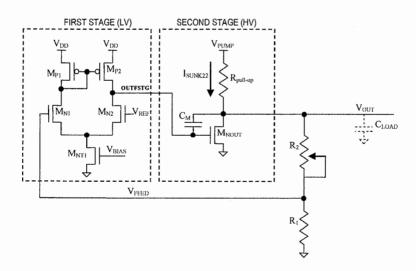

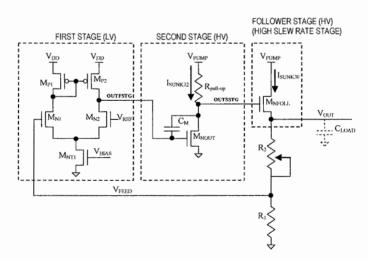

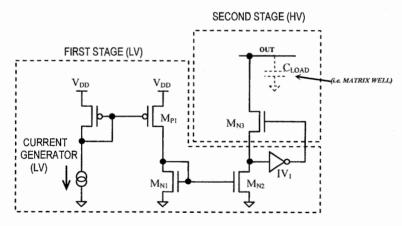

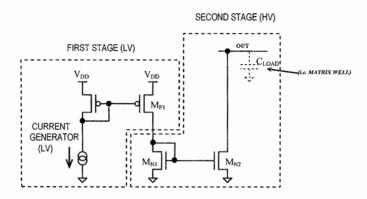

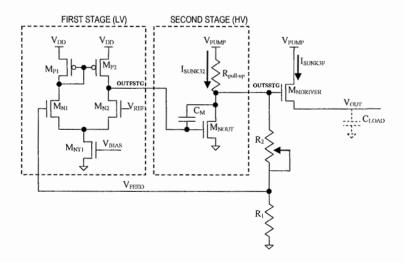

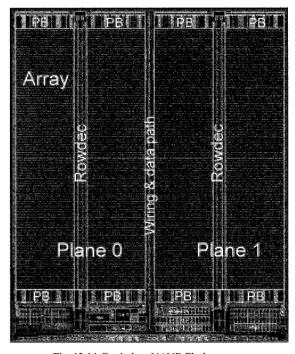

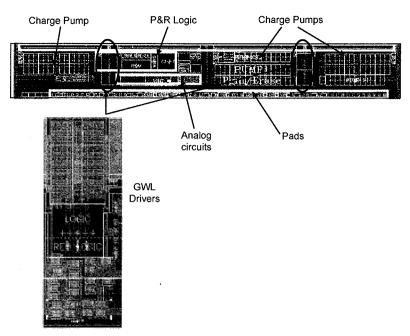

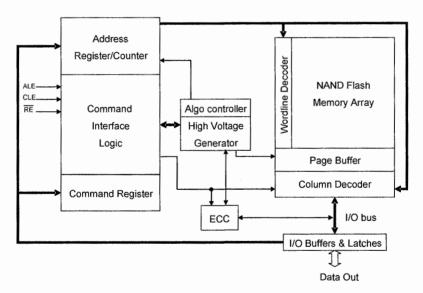

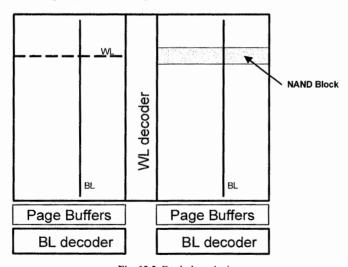

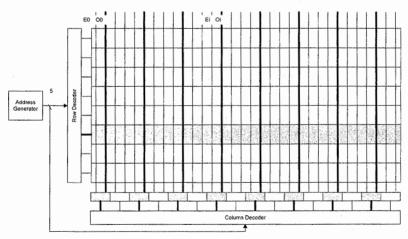

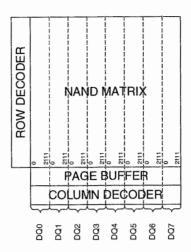

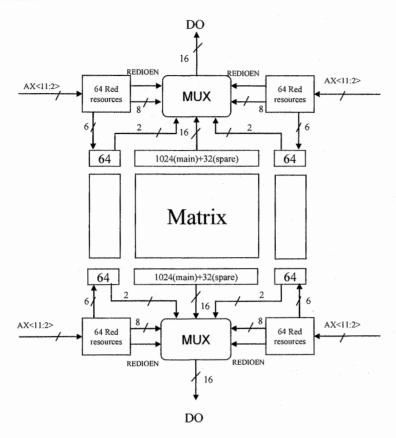

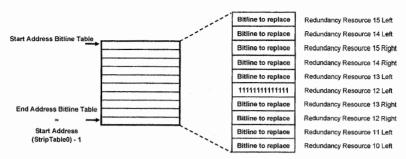

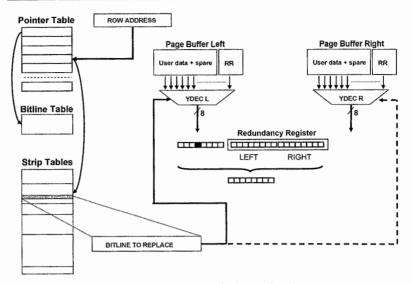

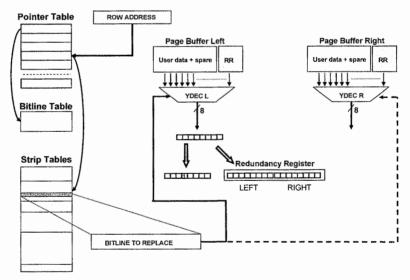

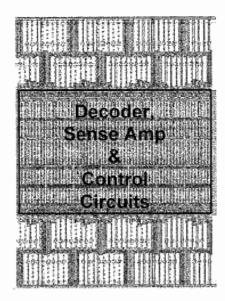

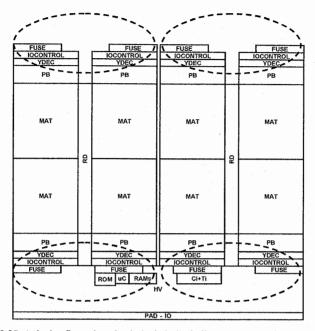

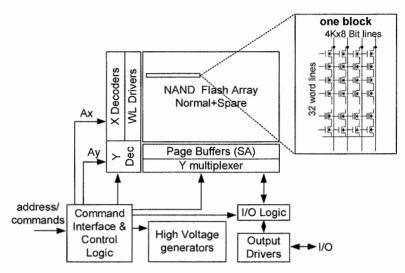

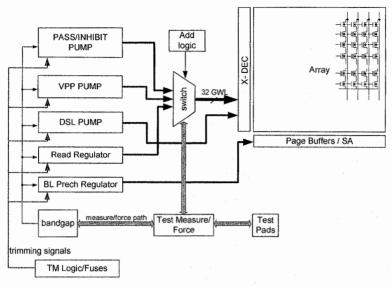

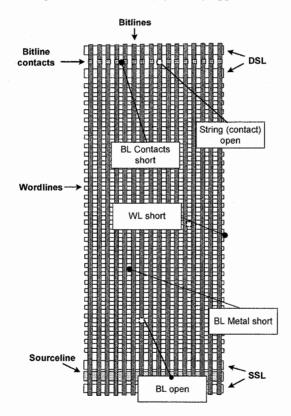

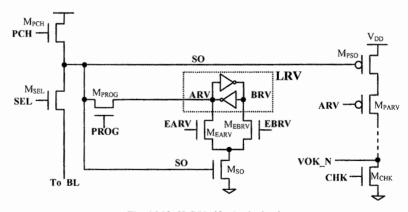

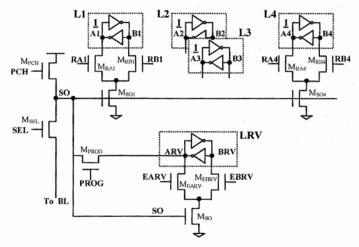

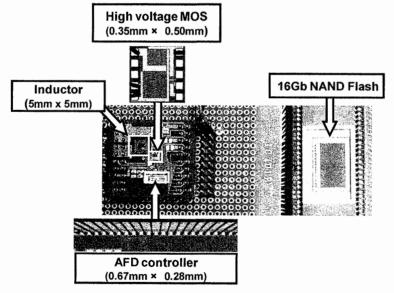

NAND Flash device is mainly composed by the memory array. Anyway, in order to perform read, program, and erase additional circuits are needed. Since the NAND die must be inserted in a package with a well-defined size, it is important to organize all the circuits and the array in the early design phase, i.e. it is important to define a floorplan.

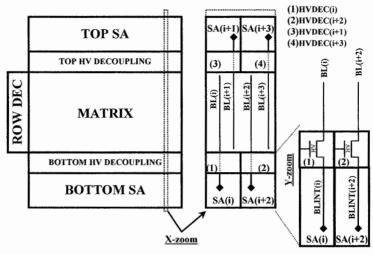

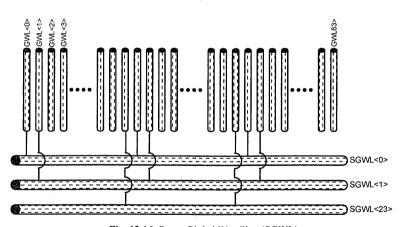

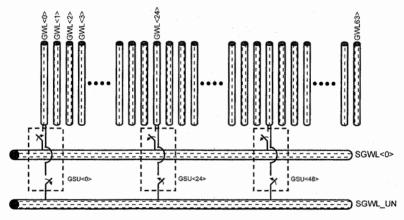

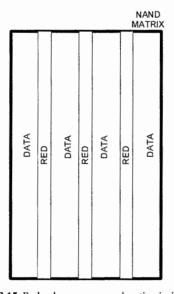

In Fig. 2.3 an example of a floorplan is given. The Memory Array can be split in different planes (two planes in Fig. 2.3). On the horizontal direction a Wordline is highlighted, while a Bitline is shown in the vertical direction.

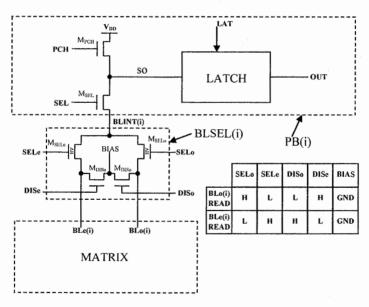

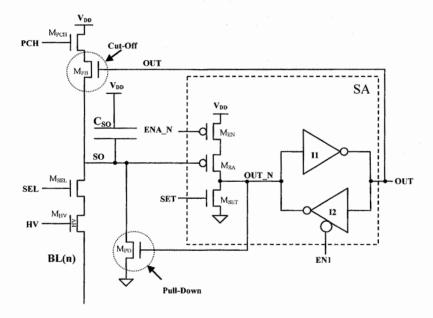

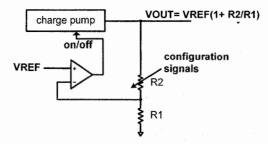

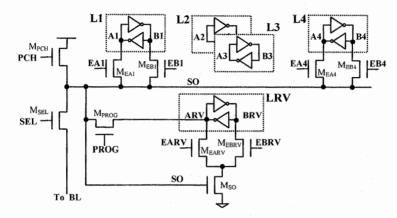

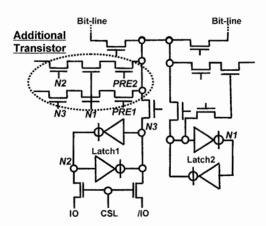

The Row Decoder is located between the planes: this circuit has the task of properly biasing all the wordlines belonging to the selected NAND string (Sect. 2.2.2). All the bitlines are connected to sense amplifiers (Sense Amp). There could be one or more bitlines per sense amplifier; for details, please, refer to Chap. 8. The purpose of sense amplifiers is to convert the current sunk by the memory cell to a digital value. In the peripheral area there are charge pumps and voltage regulators (Chap. 11), logic circuits (Chap. 6), and redundancy structures (Chap. 13). PADs are used to communicate with the external world.

Fig. 2.3. NAND Flash memory floorplan

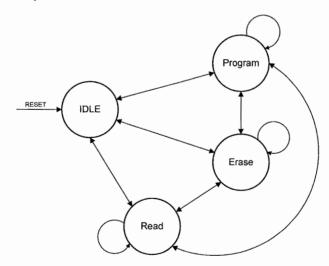

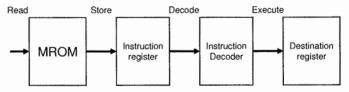

### 2.2.2 Basic operations

This section briefly describes the basic NAND functionalities: read, program, and erase.

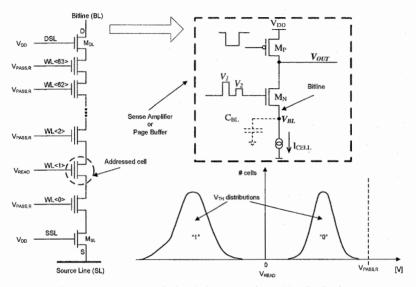

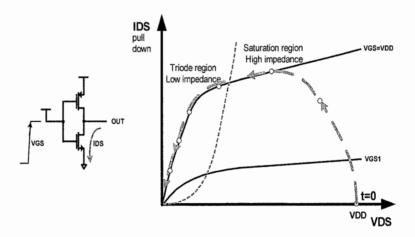

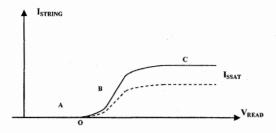

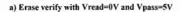

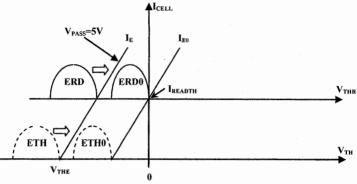

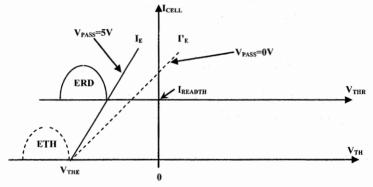

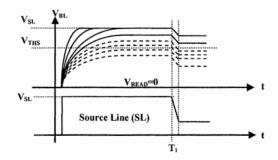

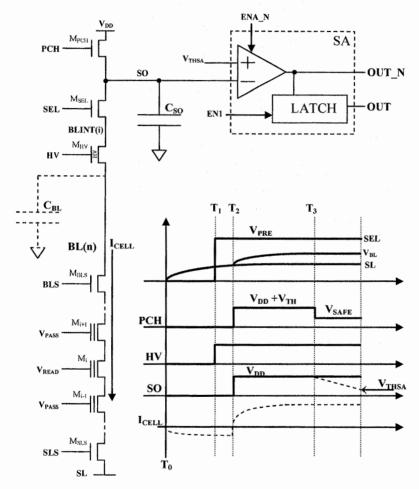

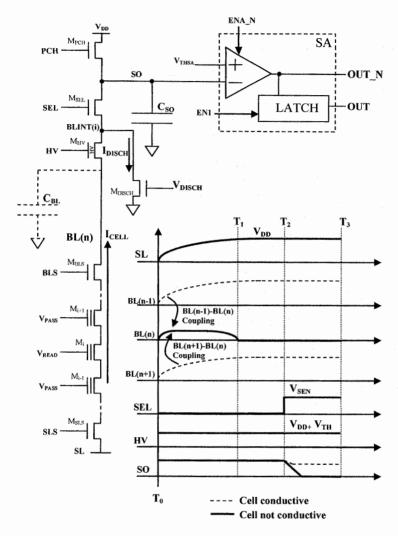

### Read

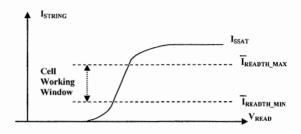

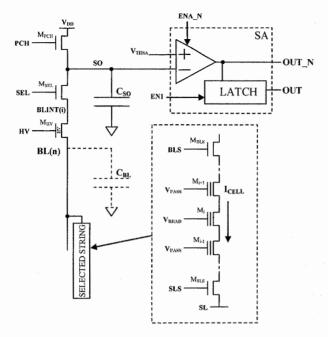

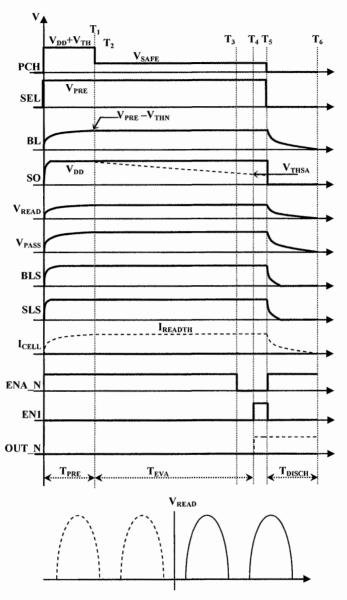

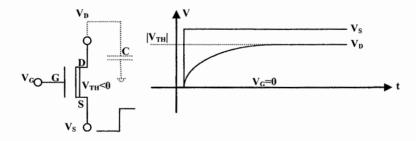

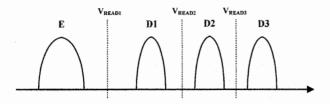

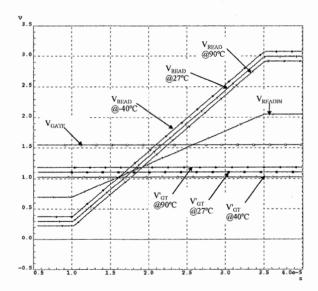

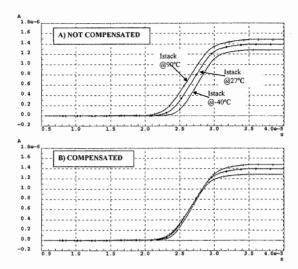

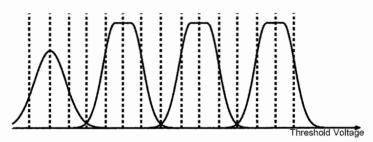

When we read a cell (Fig. 2.4), its gate is driven at  $V_{READ}$  (0 V), while the other cells are biased at  $V_{PASS,R}$  (usually 4–5 V), so that they can act as pass-transistors, regardless the value of their threshold voltages. In fact, an erased Flash cell has a  $V_{TH}$  smaller than 0 V; vice versa, a written cell has a positive  $V_{TH}$  but, however, smaller than 4 V. In practice, biasing the gate of the selected cell with a voltage equal to 0 V, the series of all the cells will conduct current only if the addressed cell is erased.

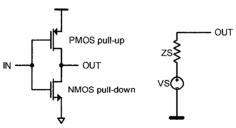

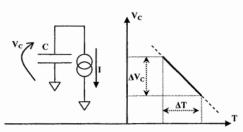

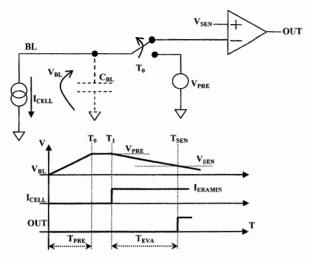

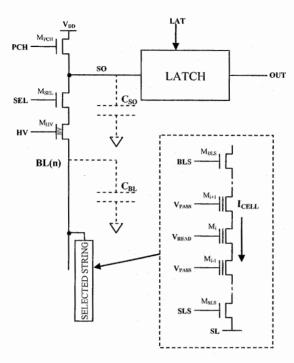

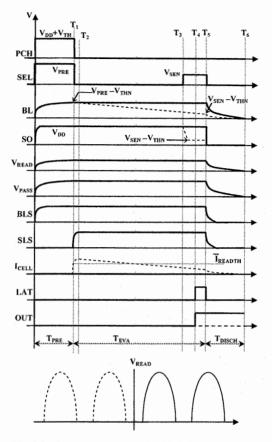

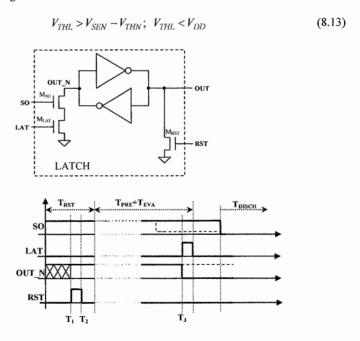

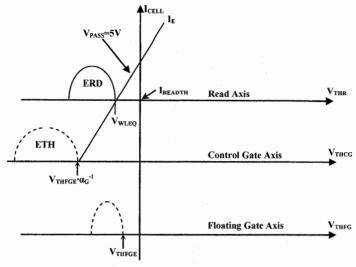

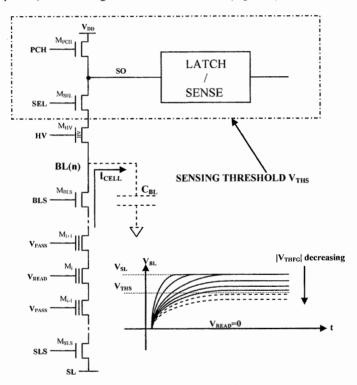

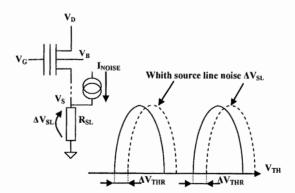

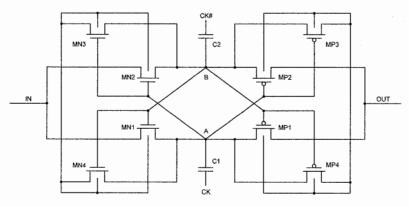

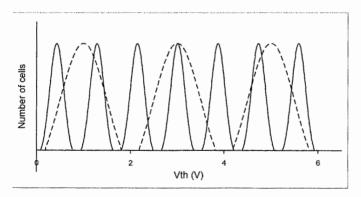

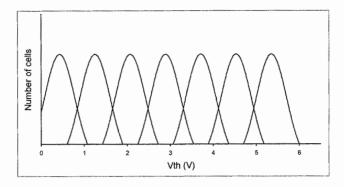

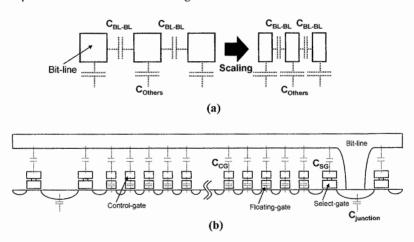

Fig. 2.4. NAND string biasing during read and SLC V<sub>TH</sub> distributions

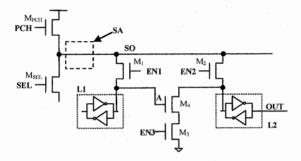

String current is usually in the range of 100–200 nA. The read technique is based on charge integration, exploiting the bitline parasitic capacitor. This capacitor is precharged at a fixed value (usually 1–1.2 V): only if the cell is erased and sinks current, then the capacitor is discharged. Several circuits exist to detect the bitline parasitic capacitor state: the structure depicted in the inset of Fig. 2.4 is present in almost all solutions. The bitline parasitic capacitor is indicated with C<sub>BL</sub> while the NAND string is equivalent to a current generator.

During the charge of the bitline, the gate of the PMOS transistor  $M_P$  is kept grounded, while the gate of the NMOS transistor  $M_N$  is kept at a fixed value  $V_1$ . Typical value for  $V_1$  is around 2 V. At the end of the charge transient the bitline will have a voltage  $V_{BL}$ :

$$V_{BL} = V_1 - V_{THN} (2.1)$$

where  $V_{THN}$  indicates the threshold voltage value of the NMSO  $M_N$ .

At this point, the  $M_N$  and  $M_P$  transistors are switched off.  $C_{BL}$  is free to discharge. After a time  $T_{VAL}$ , the gate of  $M_N$  is biased at  $V_2 < V_1$ , usually 1.6–1.4 V.

If a  $T_{VAL}$  time has elapsed long enough to discharge the bitline voltage under the value:

$$V_{RI} < V_2 - V_{THN} \tag{2.2}$$

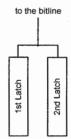

$M_{N}$  turns on and the voltage of node OUT ( $V_{OUT}$ ) becomes equal to the one of the bitline. Finally, the analog voltage  $V_{OUT}$  is converted into a digital format by using simple latches.

A more detailed analysis of read techniques is presented in Chap. 8.

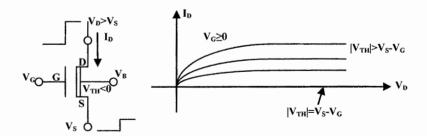

### Program

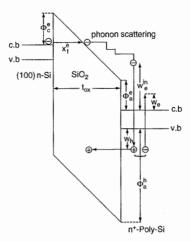

24

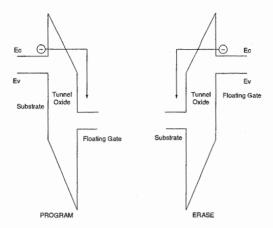

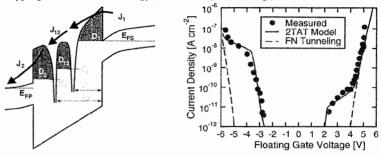

Programming of NAND memories exploits the quantum-effect of electron tunneling in the presence of a strong electric field (Fowler-Nordheim tunneling [2]). In particular, depending on the polarity of the electric field applied, program or erase take place. Please refer to Chap. 3 for more details.

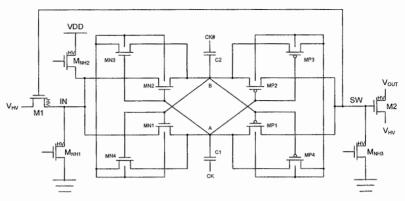

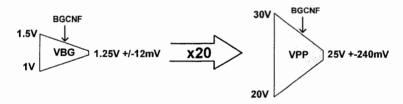

During programming, the number of electrons crossing the oxide is a function of the electric field: in fact, the greater such field is, the greater the injection probability is. Thus, in order to improve the program performances, it is essential to have high electric fields available and therefore high voltages (Chaps. 11 and 12). This requirement is one of the main drawbacks of this program method, since the oxide degradation is impacted by these voltages.

The main advantage is the current required, which is definitely low, in the range of nanoamperes per cell. This is what makes the Fowler-Nordheim mechanism suitable for a parallel programming of many cells as required by NAND page sizes.

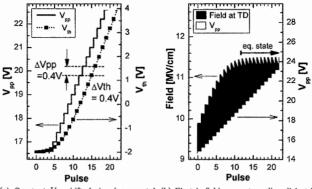

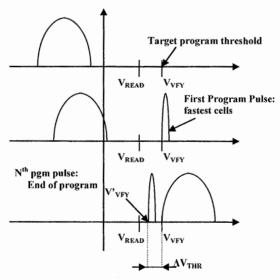

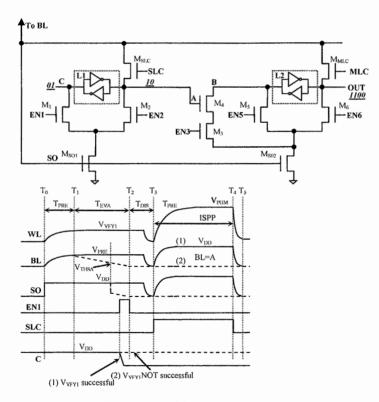

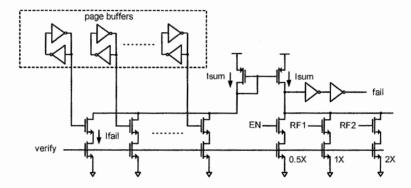

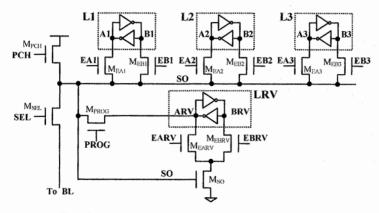

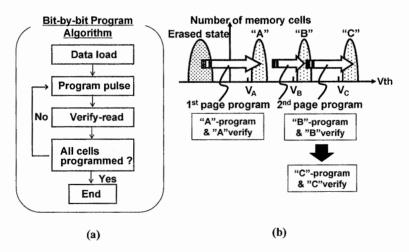

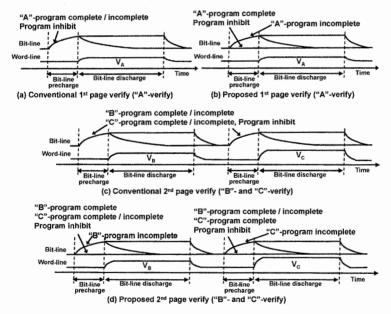

The algorithm used to program the cells of a NAND memory is a *Program & Verify* algorithm (Chaps. 3 and 12): verify is used to check whether the cell has reached the target distribution or not.

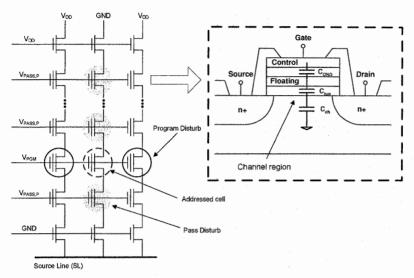

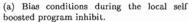

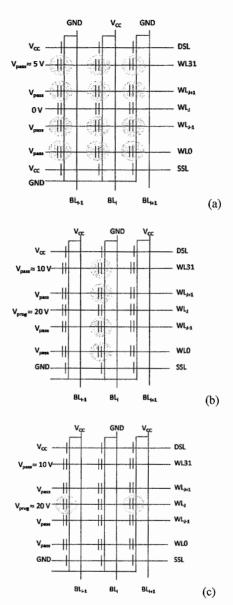

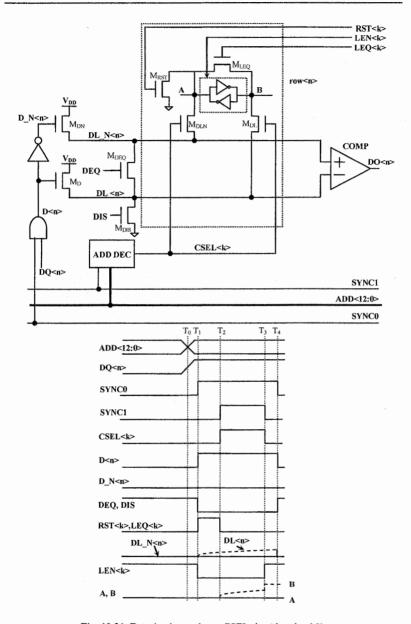

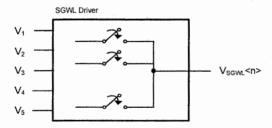

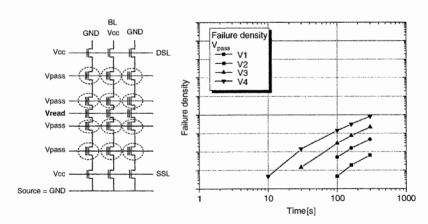

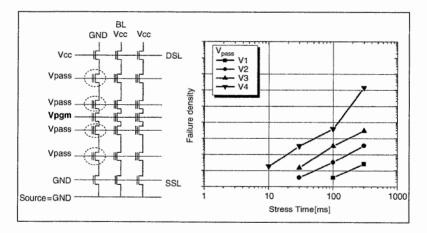

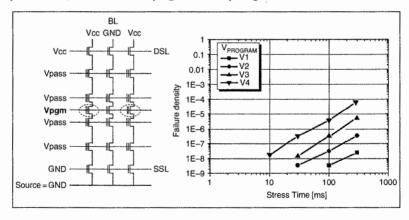

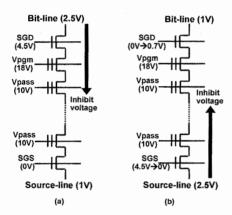

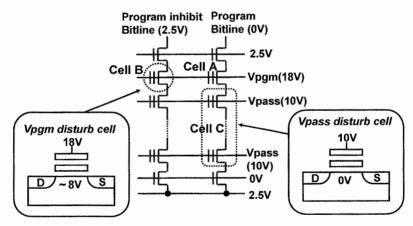

In order to trigger the injection of electrons into the floating gate, the following voltages are applied, as shown in Fig. 2.5:

- · VDD on the gate of the drain selector

- V<sub>PASS,P</sub> (8–10 V) on the unselected gates

- V<sub>PGM</sub> (20–25 V) on the selected gate (to be programmed)

- GND on the gate of the source selector

- · GND on the bitlines to be programmed

- V<sub>DD</sub> on other bitlines

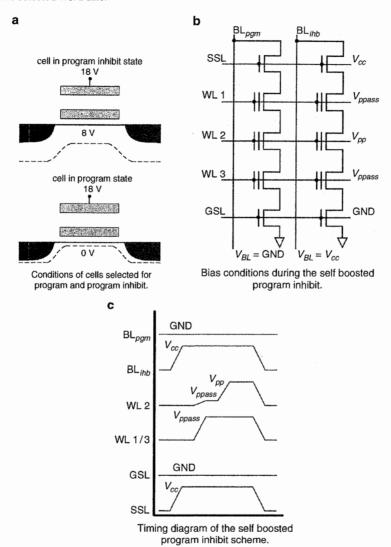

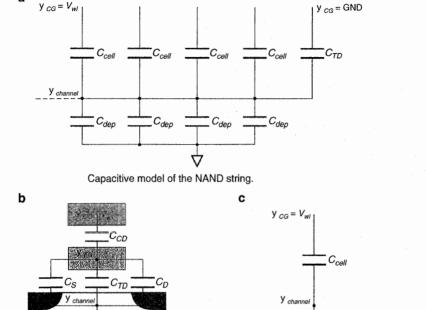

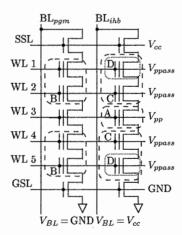

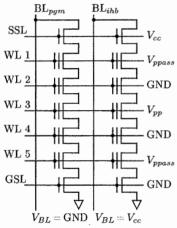

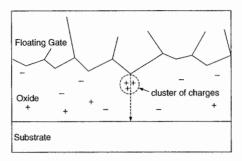

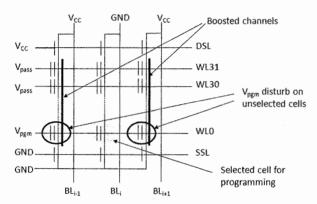

The so-called *self-boosting* mechanism (Chap. 3) prevents the cells sharing the same gate with the programmed one from undergoing an undesired program. The basic idea is to exploit the high potentials involved during programming through

the parasitic capacitors of the cell, in order to increase the potential of the region underneath the tunnel oxide (inset of Fig. 2.5).

Fig. 2.5. NAND string biasing during program and parasitic capacitors contributing to the self-boosting inhibit

When the bitlines are driven to  $V_{DD}$ , drain transistors are diode-connected and the corresponding bitlines are floating. When  $V_{PASS,P}$  is applied to the unselected wordlines, parasitic capacitors boost the potential of the channel, reducing the voltage drop across the tunnel oxide and, hence, inhibiting the tunneling phenomena.

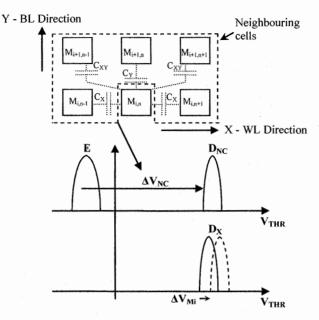

As the memory cells are organized in a matrix, all the cells along the wordline are biased at the same voltage even if they are not intended to be programmed, i.e. they are "disturbed". Two important typologies of disturbs are related to the program operation: the *Pass disturb* and the *Program disturb*, as shown in Fig. 2.5: their impact on reliability is described in Chap. 4.

#### Erase

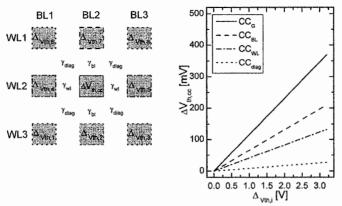

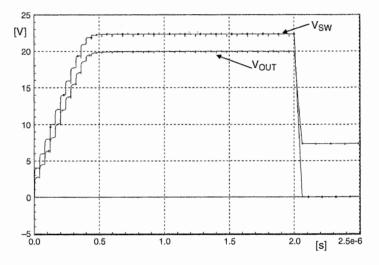

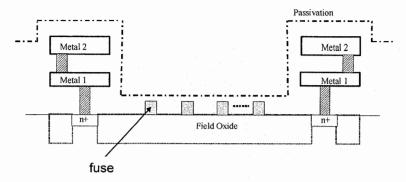

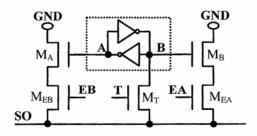

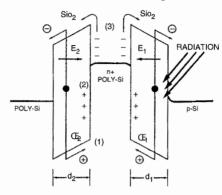

NAND memory is placed in a triple-well structure, as shown in Fig. 2.6a. Usually, each plane has its own triple-well. The source terminal is shared by all the blocks: in this way the matrix is more compact and the multiplicity of the structures which bias the iP-well is drastically reduced.

The electrical erase is achieved by biasing the iP-well with a high voltage and keeping grounded the wordlines of the sector to be erased (Fig. 2.6c). Therefore, NAND technologies don't need negative voltages. Again, the physical mechanism is the Fowler-Nordheim tunneling. As the iP-well is common to all the blocks,

erase of unselected blocks is prevented leaving their wordlines floating. In this way, when the iP-well is charged, the potential of the floating wordlines raises thanks to the capacitive coupling between the control gates and the iP-well (Fowler-Nordheim tunneling inhibited).

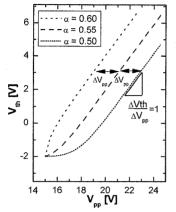

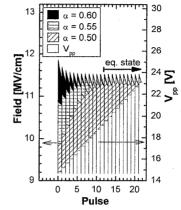

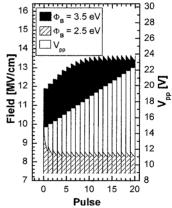

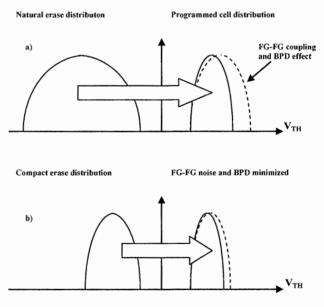

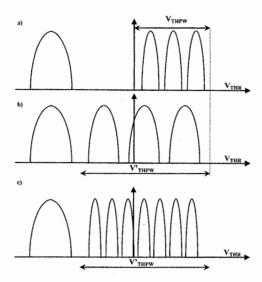

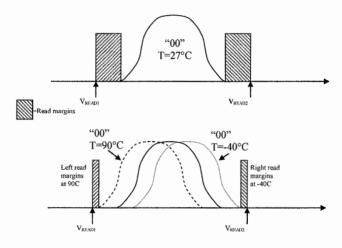

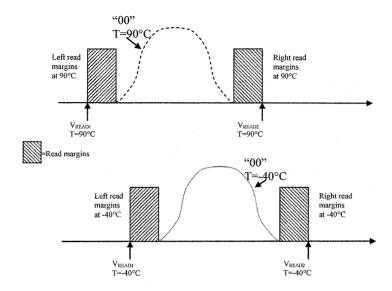

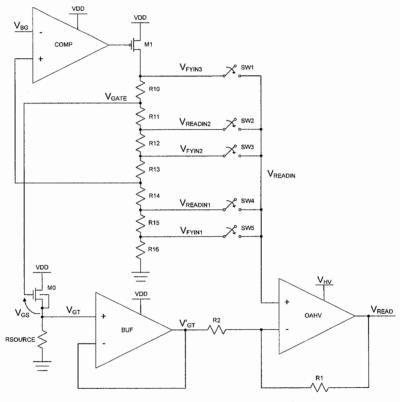

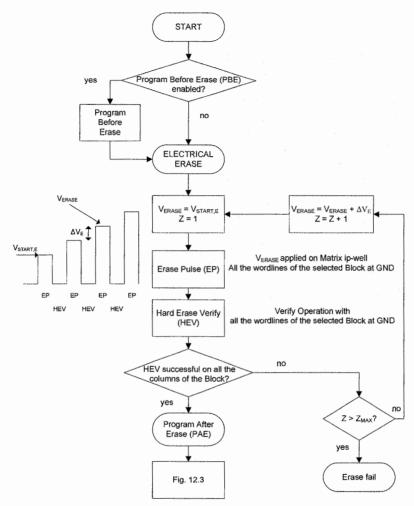

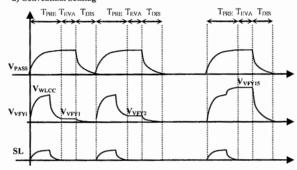

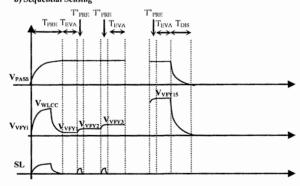

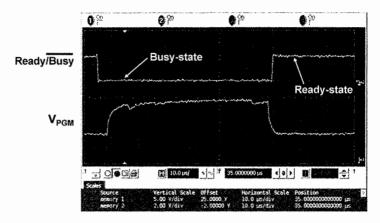

Figure 2.6b sketches the erase algorithm phases. NAND specifications are quite aggressive in terms of erase time. Therefore, Flash vendors try to erase the block content in few erase steps (possibly one). As a consequence, a very high electric field is applied to the matrix during the *Electrical Erase* phase. As a matter of fact, erased distribution is deeply shifted towards negative V<sub>TH</sub> values. In order to minimize floating gate coupling (Chap. 12), a *Program After Erase* (PAE) phase is introduced, with the goal of placing the distribution near the 0 V limit (of course, guaranteeing the appropriate read margin).

Typical erase time of a SLC block is about 1-1.5 ms; electrical erase pulse lasts 700-800 µs.

Technology shrink will ask for more sophisticated erase algorithms, especially for 3–4 bit/cell devices. In fact, reliability margins are usually shrinking with the technology node: a more precise, and therefore time consuming, PAE will be introduced, in order to contain the erased distribution width. In summary, erase time is going to increase to 4–5 ms in the new NAND generations.

Chapter 12 contains a detailed description of the whole erase algorithm.

Fig. 2.6. (a) NAND matrix in triple-well; (b) erase algorithm; (c) erase biasing on the selected block

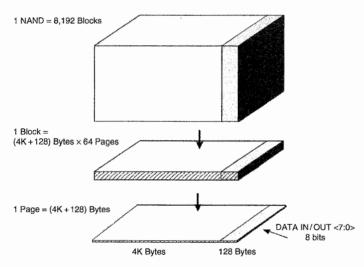

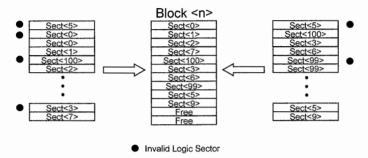

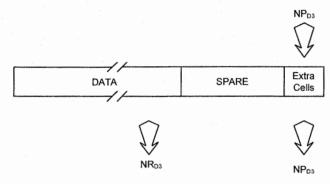

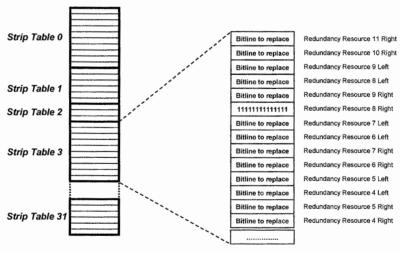

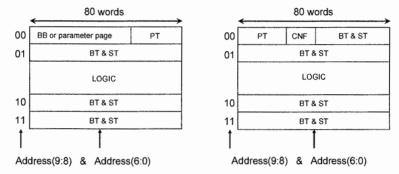

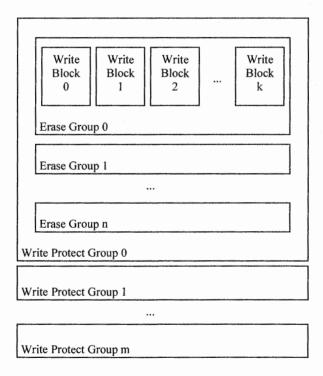

### 2.2.3 Logic organization

NAND memory contains information organized in a specified way. Looking at Fig. 2.7, a memory is divided in pages and blocks. A block is the smallest erasable unit. Generally, there are a power of two blocks within any device. Each block contains multiple pages. The number of pages within a block is typically a multiple of 16 (e.g. 64, 128). A page is the smallest addressable unit for reading and writing. Each page is composed of main area and spare area (Fig. 2.8). Main area can range from 4 to 8 kB or even 16 kB. Spare area can be used for ECC (Chap. 14) and system pointers (Chap. 17) and it is in the order of a couple of hundreds bytes every 4 kB of main area.

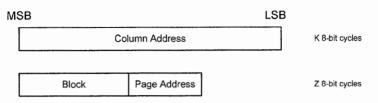

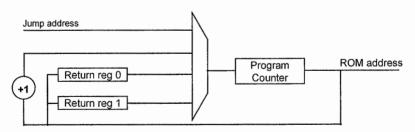

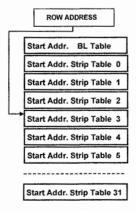

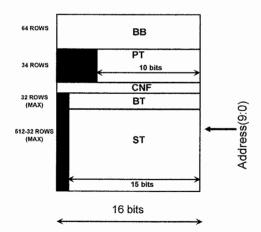

Every time we want to execute an operation on a NAND device, we must issue the address where we want to act. The address is divided in row address and column address (Fig. 2.9). Row address identifies the addressed page, while column address is used to identify the bytes inside the page. When both row and column addresses are required, column address is given first, 8 bits per address cycle. The first cycle contains the least significant bits. Row and column addresses cannot share the same address cycle.

The row address identifies the block and the page involved in the operation. Page address occupies the least significant bits.

Fig. 2.7. NAND memory logic organization

| MAIN AREA | SPARE AREA |

|-----------|------------|

Fig. 2.8. NAND page structure

Fig. 2.9. Address structure

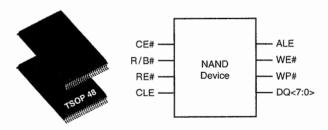

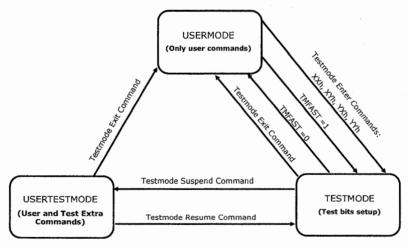

### 2.2.4 Pinout

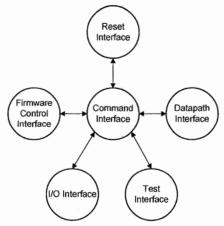

NAND devices communicate with the external user by means of pins (Fig. 2.10). These pins are monitored by the Command Interface (Chap. 6) which has the task to understand the functionality required to the memory in that moment.

Pins shown in the Fig. 2.10 are listed below.

- CE#: it is the Chip Enable signal. This input signal is "1" when the device is in stand-by mode, otherwise it is always "0".

- R/B#: it is the Ready/Busy signal. This output signal is used to indicate the target status. When low, the target has an operation in progress.

- RE#: it is the Read Enable signal. This input signal is used to enable serial data output.

- CLE: it is the Command Latch Enable. This input is used by the host to indicate that the bus cycle is used to input the command.

- ALE: it is the Address Latch Enable. This input is used by the host to indicate that the bus cycle is used to input the addresses.

- WE#: it is the Write Enable. This input signal controls the latching of input data. Data, command and address are latched on the rising edge of WE#.

- WP#: it is the Write Protect. This input signal is used to disable Flash array program and erase operations.

- DQ<7:0>: these input/output signals represent the data bus.

Fig. 2.10. TSOP package (left) and related pinout (right)

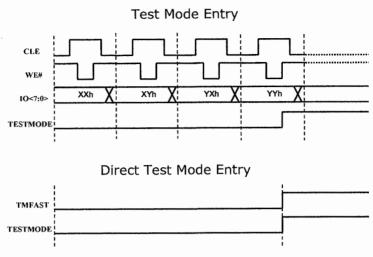

### 2.3 Command set

### 2.3.1 Read operation

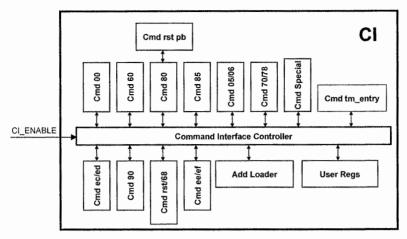

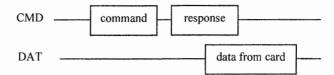

The read function reads the data stored at a specified address. In order to accomplish this goal, NAND device must recognize when a read operation is issued and the related addresses. After a busy time needed to execute the read algorithm, NAND device outputs the data sequence. Based on the device pin signals, the NAND Command Interface (CI, Chap. 6) is able to understand when a command is issued, when an address is issued or when it must perform data out.

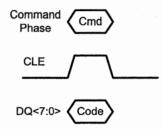

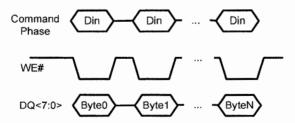

Figure 2.11 shows a command cycle ("Cmd"). CI recognizes a "Cmd" cycle if CLE is high. In that case, the 8-bit value on DQs represents the command code.

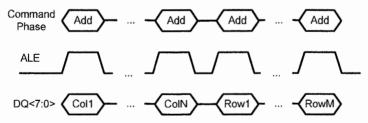

Figure 2.12 shows address cycles. Generally, all the operations need the addresses where they have to act. The address length depends on the operation and on the capacity of the NAND; anyway, N cycles are needed to input column addresses and M cycles are needed to input row addresses. CI recognized an address cycle if ALE is high. In the meanwhile, all other input signals are low and the DQs value is the address.

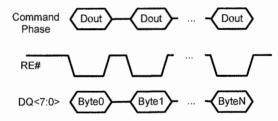

The last command phase used by the read operation is the data out, shown in Fig. 2.13. Data out is performed by toggling signal RE#: at every cycle a new data is available on DQs.

Fig. 2.11. Command cycle ("Cmd"): CLE is high, all other input signals are low

Fig. 2.12. Address cycle: ALE is high, all other inputs signals are low

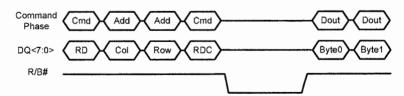

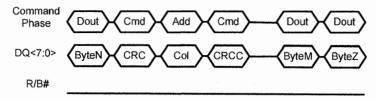

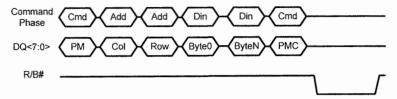

These basic cycles are used by the NAND to decode and perform every operation. Figure 2.14 shows the command sequence for a read operation. The first cycle is used to issue the read command "RD" (e.g. 00h). After the command cycle a number of cycles is used to provide the addresses. As described in Sect. 2.2 the column addresses are given first, followed by the row addresses. All the pins (ALE, CLE, RE#) not present in the figure must be driven as described above. Code "RDC" (Read Command Confirm, e.g. 30h) is used to confirm the read command. Finally, the device goes busy and the read operation starts. When NAND returns ready, the data output cycles start.

The above described read command outputs the entire Flash page, regardless the number of bytes we want to read. In some cases, a small move of data is required or we may want to read randomly inside a page. Command Change Read Column, also known as Random Data Output, is able to change the column address we are reading.

Figure 2.15 shows the Change Read Column sequence. After the usual read command is executed, it is possible to change the column address during data out. A command cycle "CRC" (Change Read Column, e.g. 05h) is issued, followed by the addresses of the locations we want to output from. Only fewer cycles are required with respect to the usual read command, since only the column addresses are needed. A confirm command cycle "CRCC" (Change Read Column Confirm, e.g. E0h) is used to enable the data out. It is worth noting that no additional busy time is necessary, because data are already stored in the page buffers.

Generally, the busy time in a read operation lasts for about 25–30 µs. One way to improve read throughput is the Read Cache Command (when available). With this command, it is possible to download data from the Flash memory, while page buffers are reading another page from the Flash array.

Fig. 2.13. "Dout" cycle: RE# is low, all other inputs signals are low

Fig. 2.14. Read command sequence

Fig. 2.15. Change Read Column sequence

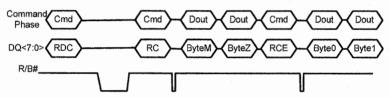

Sequential Read Cache Command sequence is shown in Fig. 2.16. A Read Command must be issued before Read Cache Command. After the device returns ready, the command code "RC" (Read Cache, e.g. 31h) is used to initiate data download from the matrix to page buffers. RB# goes low for a while and then N Dout cycles are used to output first page. Since no other addresses are input, the next sequential page is automatically read inside the NAND. When we don't need to read other pages, the last page is copied into the page buffers by using command "RCE" (Read Cache End, e.g. 3Fh).

Random Cache Read sequence is shown in Fig. 2.17: with this command it is possible to select the address of the page we want to cache.

Fig. 2.16. Sequential Cache Read command

Fig. 2.17. Random Cache Read command

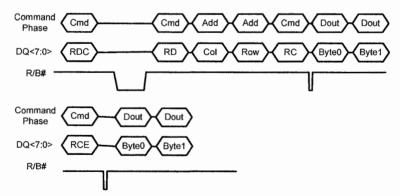

On multi-plane device, it is possible to issue a read command on multiple planes simultaneously. Figure 2.18 shows the command sequence for Multi-plane Read

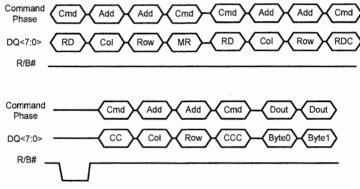

After the standard Read Command cycle "RD", the addresses of the page we want to read on plane 0 are issued. The command code "MR" (Multi-plane read, e.g. 32h) is used in the next command cycle so that the device is ready to receive the addresses belonging to plane 1. Once the new addresses and the Read Command Confirm Code "RDC" are given, the device goes busy to perform the read algorithm on both planes simultaneously. When the device returns ready, the command cycle CC (Choose Column, e.g. 06h) is used to select the address of the page we want to output, followed by a number of address cycles. The command code "CCC" (Choose Column Confirm, e.g. E0h) is a command confirm. Finally the Dout cycles are used to output the read data.

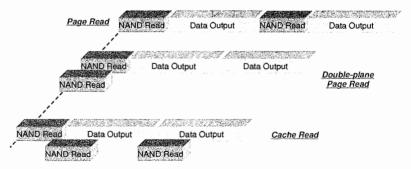

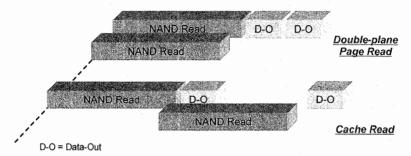

Since both the Read Cache command and the Multi-plane read have been introduced to increase performances, it is interesting to compare them. Figure 2.19 shows a comparison among Read, Cache Read and Multi-plane Read.

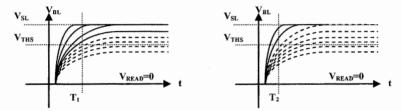

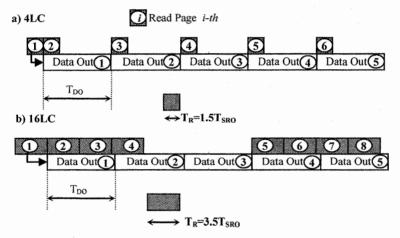

Fig. 2.18. Multi-plane read command

Fig. 2.19. Performance comparison among Read, Double-plane Read and Cache Read

Given  $T_{ALGO}$  the time needed to read from the NAND array, and  $T_{OUT}$  the time needed to download the page, the total time to perform the read of two pages with a standard read is T=2  $T_{ALGO}+2$   $T_{OUT}$ . If a multi-plane command is used,  $T_{ALGO}$  runs simultaneously on both planes and  $T=T_{ALGO}+2$   $T_{OUT}$ . Evaluating T in the Cache Read case is more difficult, because we have to consider the ratio between  $T_{ALGO}$  and  $T_{OUT}$ . If  $T_{OUT}$  is longer than  $T_{ALGO}$ , then  $T=T_{ALGO}+2$   $T_{OUT}$ . It follows that the performances of Cache Read and Double Plane Read are the same. On the contrary, if  $T_{ALGO}$  is longer than  $T_{OUT}$  (Chap. 16), it won't be possible anymore to mask  $T_{ALGO}$  with a single page data out (Fig. 2.20). In this case, Double-plane Read performs better than Cache Read.

Fig. 2.20. Performance comparison among Read, Double-plane Read and Cache Read with a NAND array read time longer than page data output

### 2.3.2 Program operation

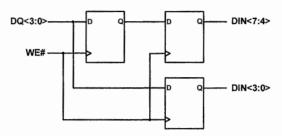

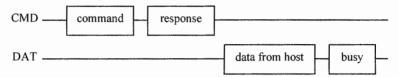

Purpose of program operation is to write a data sequence at a specified address. The basic cycles are those already described for read operation, such as Command cycle and Address cycle. The only added cycle is the "Din" cycle, represented in Fig. 2.21. Data in is performed by toggling signal WE#: at every cycle a new byte shall be made available on DQs.

Fig. 2.21. "Din" cycle: WE# is low, all other inputs signals are low

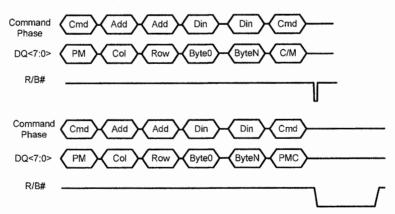

Program sequence is shown in Fig. 2.22. A command cycle to input "PM" code (Program, e.g. 80h) is followed by a number of address cycles to input the addresses where we want to write. Once the location is set, N "Din" cycles are used to input data into the page buffers. Finally a "PMC" (Program Confirm, e.g. 10h) command is issued to start the algorithm.

Fig. 2.22. Program command

As already described for read operation, also in the program case there could be the need to move a small amount of data. Change Write Column is used to change the column address where we want to load the data.

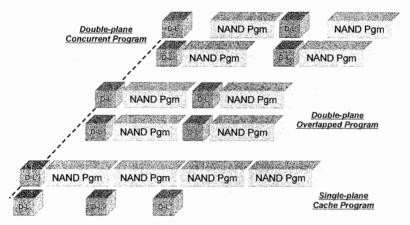

Program busy time can be very long: 150–200 µs. Program cache command or double-plane program are used to increase write throughput. Figure 2.23 shows the sequence for Cache Program and Double Plane Program.

The first cycles ("PM" cycle, address cycles and "Din" cycles) are the same as in the standard program. Instead of "PMC" a "C/M" command cycle is issued. "C/M" can be the Cache Program Code (e.g. 15h) or a Double Plane Command (e.g. 11h). Once another "PM" command is given, followed by the new addresses and the "PMC" command, the device goes busy and the program algorithm is performed simultaneously on both pages. It is worth noting that the above described Double plane program is generally known as Concurrent double-plane Program, because the program algorithm works simultaneously on both planes.

Fig. 2.23. Cache Program and Double-Plane Program commands

Overlapped Double-Plane Program is also available, where the program on the first plane starts as soon as data are loaded in the page buffers. In this case the NAND architecture must be able to perform the algorithm in an independent way on both planes.

The comparison between the above mentioned program commands is shown in Fig. 2.24.

Fig. 2.24. Performance comparison among Cache Program, Overlapped Double Plane program and Concurrent Double Plane Program

### 2.3.3 Erase operation

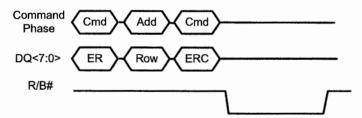

The Erase operation is used to delete data from the Flash array. As already described (Sect. 2.2.3), the smallest erasable unit for the NAND memory is the block. Figure 2.25 shows the Erase Command sequence.

The Erase command is very simple: a "ER" code is issued (Erase Command, e.g. 60h), followed by the block address and the "ERC" code (Erase Command Confirm, e.g. D0h). After that, the device goes busy to perform the algorithm.

Fig. 2.25. Erase command

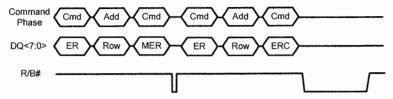

Since erase is the longest operation (about 1 ms), the Double-Plane Erase command has been introduced to erase two blocks at the same time. Figure 2.26 shows the command sequence for the Double-Plane Erase.

The standard erase cycles ("ER" command and row address cycles) are followed by a "MER" command (Multi-plane erase, e.g. D1h). Once both the plane 1 addresses and the "ERC" code are given, the device goes busy, erasing both blocks simultaneously.

Fig. 2.26. Double-Plane Erase command

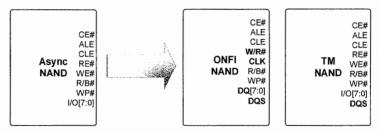

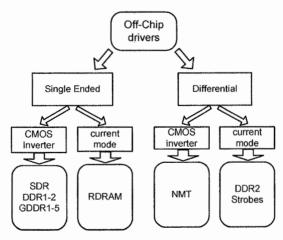

### 2.3.4 Synchronous operations

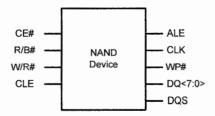

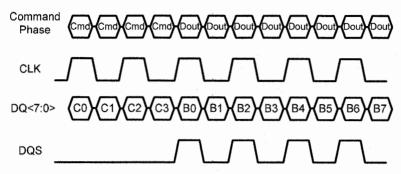

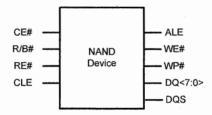

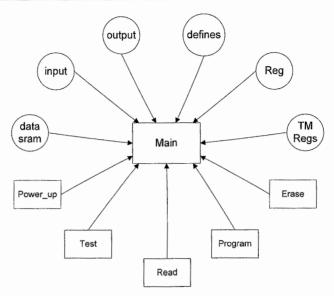

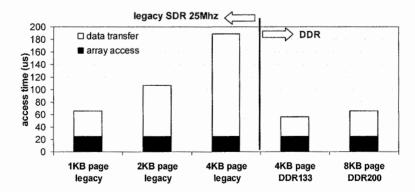

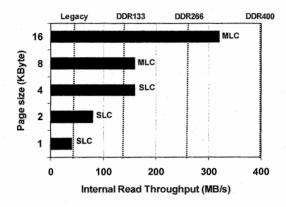

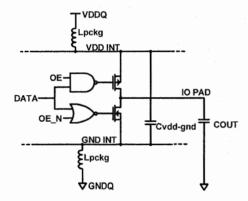

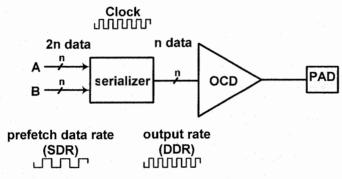

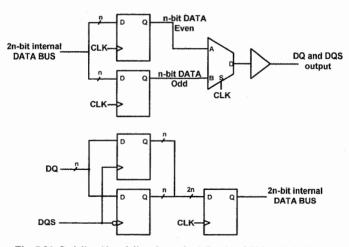

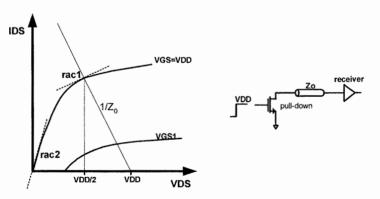

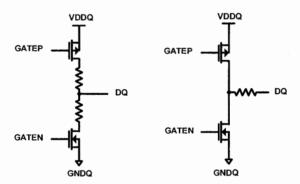

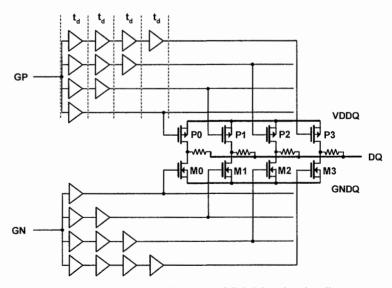

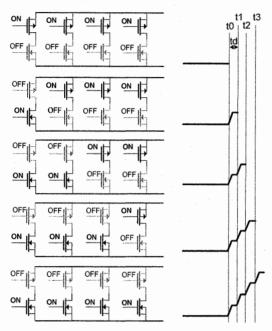

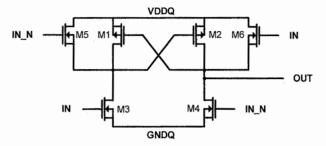

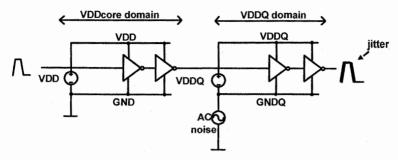

NAND read throughput is determined by array access time and data transfer across the DQ bus. The data transfer is limited to 40 MB/s by the asynchronous interface. As technology shrinks, page size increases and data transfer takes longer; as a consequence, NAND read throughput decreases, totally unbalancing the ratio between array access time and data transfer on the DQ bus. DDR interface (Chap. 7) has been introduced to balance this ratio.

Nowadays two possible solutions are available on the market. The first one, *Source Synchronous Interface* (SSI), is driven by the ONFI (Open NAND Flash Interface) organization established in 2006 with the purpose of standardizing the NAND interface. Other NAND vendors use the Toggle-Mode interface.

Figure 2.27 shows the NAND pinout for SSI. Compared to the *Asynchronous Interface* (ASI, Sect. 2.2), there are three main differences:

- RE# becomes W/R# which is the Write/Read direction pin.

- WE# becomes CLK which is the clock signal.

- DQS is an additional pin acting as the data strobe, i.e. it indicates the data valid window.

Fig. 2.27. Pinout of a NAND Flash supporting Source Synchronous Interface

Fig. 2.28. Source Synchronous Interface DDR sequence

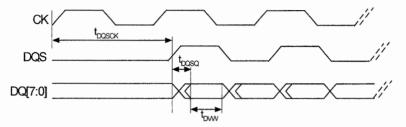

Hence, the clock is used to indicate where command and addresses should be latched, while a data strobe signal is used to indicate where data should be latched. DQS is a bi-directional bus and is driven with the same frequency as the clock.

Obviously, the basic command cycles described in the previous sections must be modified according to the new interface.

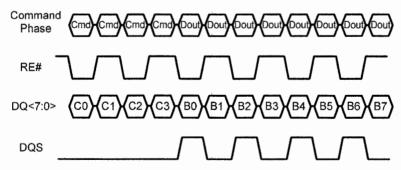

Figure 2.28 shows a "Cmd" sequence, followed by "Dout" cycles for SSI. Toggle-Mode DDR interface uses the pinout shown in Fig. 2.29.

Fig. 2.29. Pinout of a NAND Flash supporting Toggle-Mode Interface

Fig. 2.30. Toggle-Mode DDR sequence

It can be noted that only the DQS pin has been added to the standard ASI. In this case, higher speeds are achieved increasing the toggling frequency of RE#.

Figure 2.30 shows a "Cmd" sequence, followed by "Dout" cycles for Toggle-Mode interface.

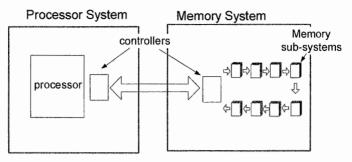

# 2.4 NAND-based systems

Flash cards, USB sticks and *Solid State Disks* (SSDs) are definitely the most known examples of electronic systems based on NAND Flash.

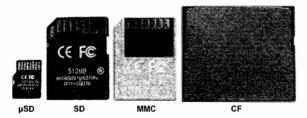

Several types of memory cards are available on the market [3–5], with different user interfaces and form factors, depending on the needs of the target application: e.g. mobile phones need very small-sized removable media like  $\mu SD$ . On the other hand, digital cameras can accept larger sizes as memory capacity is more important (CF, SD, MMC). Figure 2.31 shows different types of Flash cards.

The interfaces of the Flash cards (including USB sticks) support several protocols: parallel or serial, synchronous or asynchronous. Moreover, the Flash cards support hot insertion and hot extraction procedures, which require the ability to manage sudden loss of power supply while guaranteeing the validity of stored data.

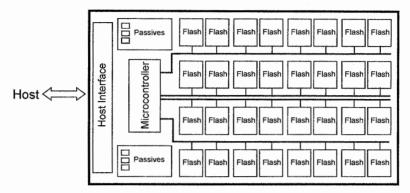

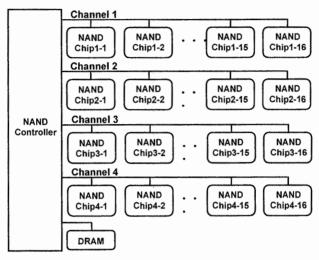

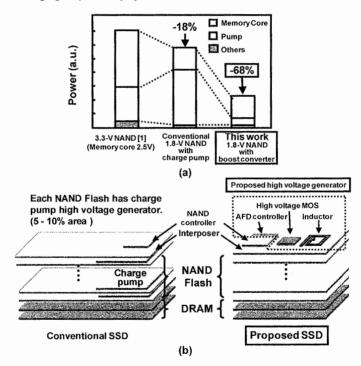

For the larger form factors, the card is a complete, small system where every component is soldered on a PCB and is independently packaged. For example, the NAND Flash memories are usually available in TSOP packages. It is also possible to include some additional components: for instance, an external DC-DC converter can be added in order to derive an internal power supply (CompactFlash cards can work at either 5 or 3.3 V), or a quartz can be used for a better clock precision. Usually, reasonable filter capacitors are inserted for stabilizing the power supply. Same considerations apply to SSDs; the main difference with Flash cards is the system capacity as shown in Fig. 2.32 where multiple NANDs are organized in different channels in order to improve performances.

For small form factors like  $\mu SD$ , the size of the card is comparable to that of the NAND die. Therefore, the memory chip is mounted as bare die on a small substrate. Moreover, the die thickness has to be reduced in order to comply with the thickness of  $\mu SD$ , considering that several dies are stacked, i.e. mounted one on top of each other.

Fig. 2.31. Popular Flash card form factors

All these issues cause a severe limitation to the maximum capacity of the card; in addition external components, like voltage regulators and quartz, cannot be used. In other words, the memory controller of the card has to implement all the required functions.

The assembly stress for small form factors is quite high and, therefore, system testing is at the end of the production. Hence, production cost is higher (Chap. 15).

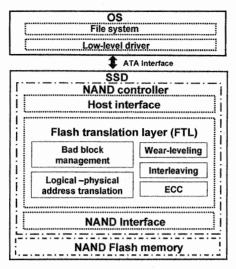

Fig. 2.32. Block diagram of a SSD

Fig. 2.33. Functional representation of a Flash card (or SSD)

For a more detailed description of Flash cards, please, refer to Chap. 17. SSDs are described in Chap. 18.

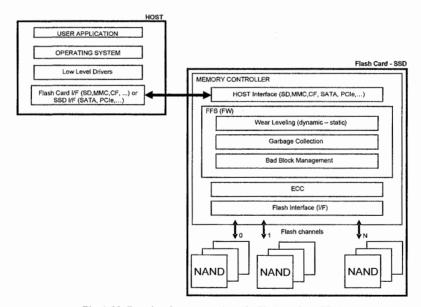

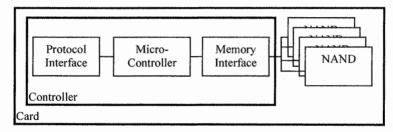

Figure 2.33 shows a functional representation of a memory card or SSD: two types of components can be identified: the memory controller and the Flash memory components. Actual implementation may vary, but the functions described in the next sections are always present.

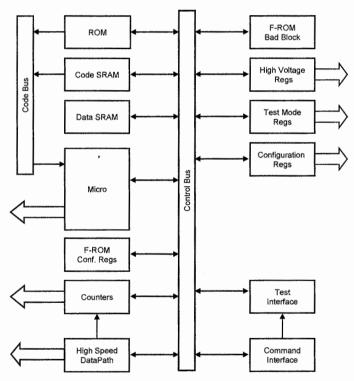

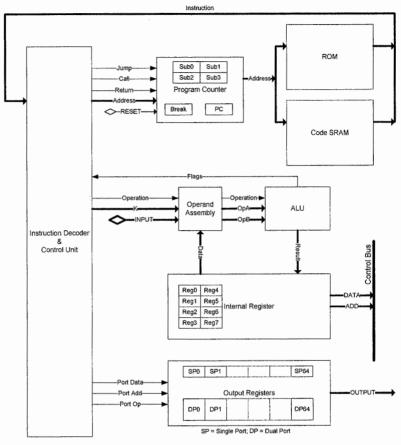

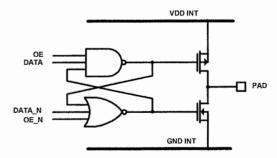

#### 2.4.1 Memory controller

The aim of the memory controller is twofold:

- To provide the most suitable interface and protocol towards both the host and the Flash memories

- To efficiently handle data, maximizing transfer speed, data integrity and information retention

In order to carry out such tasks, an application specific device is designed, embedding a standard processor – usually 8–16 bits – together with dedicated hardware to handle timing-critical tasks.

For the sake of discussion, the memory controller can be divided into four parts, which are implemented either in hardware or in firmware. Proceeding from the host to the Flash, the first part is the host interface, which implements the required industry-standard protocol (MMC, SD, CF, etc.), thus ensuring both logical and electrical interoperability between Flash cards and hosts. This block is a mix of hardware – buffers, drivers, etc. – and firmware – command decoding performed by the embedded processor – which decodes the command sequence invoked by the host and handles the data flow to/from the Flash memories.

The second part is the Flash File System (FFS) [6]: that is, the file system which enables the use of Flash cards, SSDs and USB sticks like magnetic disks. For instance, sequential memory access on a multitude of sub-sectors which constitute a file is organized by linked lists (stored on the Flash card itself) which are used by the host to build the File Allocation Table (FAT).

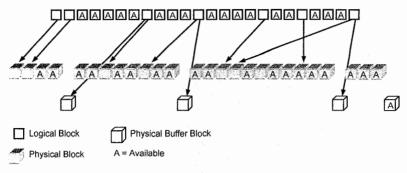

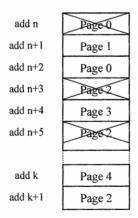

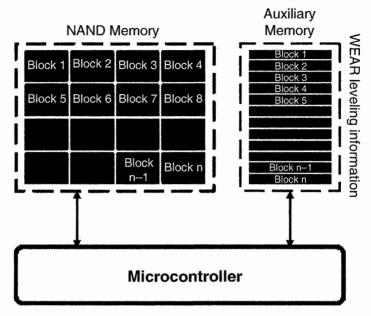

The FFS is usually implemented in form of firmware inside the controller, each sub-layer performing a specific function. The main functions are: Wear leveling Management, Garbage Collection and Bad Block Management. For all these functions, tables are widely used in order to map sectors and pages from logical to physical (Flash Translation Layer or FTL) [7, 8], as shown in Fig. 2.34.

The upper block row is the logical view of the memory, while the lower row is the physical one. From the host perspective, data are transparently written and overwritten inside a given logical sector: due to Flash limitations, overwrite on the same page is not possible, therefore a new page (sector) must be allocated in the physical block and the previous one is marked as invalid. It is clear that, at some point in time, the current physical block becomes full and therefore a second one (Buffer) is assigned to the same logical block.

The required translation tables are always stored on the memory card itself, thus reducing the overall card capacity.

Fig. 2.34. Logical to physical block management

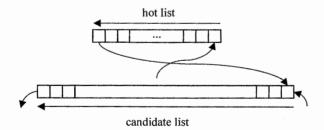

#### Wear leveling

Usually, not all the information stored within the same memory location change with the same frequency: some data are often updated while others remain always the same for a very long time — in the extreme case, for the whole life of the device. It's clear that the blocks containing frequently-updated information are stressed with a large number of write/erase cycles, while the blocks containing information updated very rarely are much less stressed.

In order to mitigate disturbs, it is important to keep the aging of each page/block as minimum and as uniform as possible: that is, the number of both read and program cycles applied to each page must be monitored. Furthermore, the maximum number of allowed program/erase cycles for a block (i.e. its endurance) should be considered: in case SLC NAND memories are used, this number is in the order of 100 k cycles, which is reduced to 10 k when MLC NAND memories are used.

Wear Leveling techniques rely on the concept of logical to physical translation: that is, each time the host application requires updates to the same (logical) sector, the memory controller dynamically maps the sector onto a different (physical) sector, keeping track of the mapping either in a specific table or with pointers. The out-of-date copy of the sector is tagged as both invalid and eligible for erase. In this way, all the physical sectors are evenly used, thus keeping the aging under a reasonable value.

Two kinds of approaches are possible: Dynamic Wear Leveling is normally used to follow up a user's request of update for a sector; Static Wear Leveling can also be implemented, where every sector, even the least modified, is eligible for re-mapping as soon as its aging deviates from the average value.

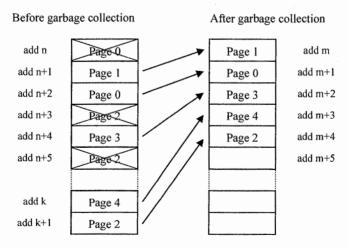

#### Garbage collection

Both wear leveling techniques rely on the availability of free sectors that can be filled up with the updates: as soon as the number of free sectors falls below a given threshold, sectors are "compacted" and multiple, obsolete copies are deleted.

This operation is performed by the Garbage Collection module, which selects the blocks containing the invalid sectors, copies the latest valid copy into free sectors and erases such blocks (Fig. 2.35).

In order to minimize the impact on performance, garbage collection can be performed in background. The equilibrium generated by the wear leveling distributes wear out stress over the array rather than on single hot spots. Hence, the bigger the memory density, the lower the wear out per cell is.

Fig. 2.35. Garbage collection

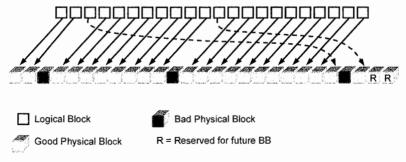

#### Bad block management

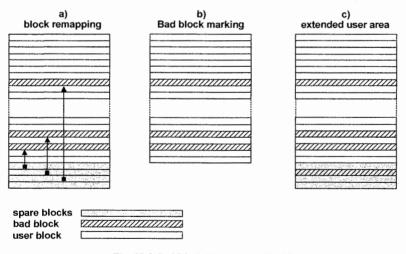

No matter how smart the Wear Leveling algorithm is, an intrinsic limitation of NAND Flash memories is represented by the presence of so-called *Bad Blocks* (BB), i.e. blocks which contain one or more locations whose reliability is not guaranteed.

The Bad Block Management (BBM) module creates and maintains a map of bad blocks, as shown in Fig. 2.36: this map is created during factory initialization of the memory card, thus containing the list of the bad blocks already present during the factory testing of the NAND Flash memory modules. Then it is updated during device lifetime whenever a block becomes bad.

Fig. 2.36. Bad Block Management (BBM)

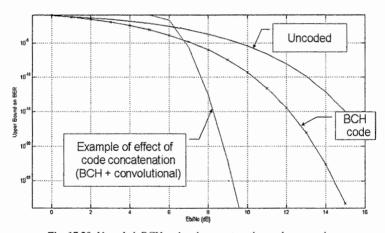

#### **FCC**

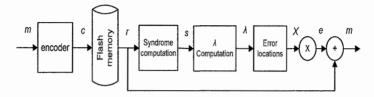

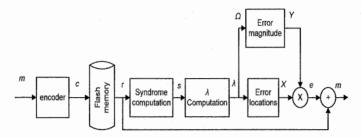

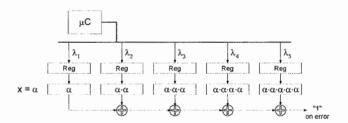

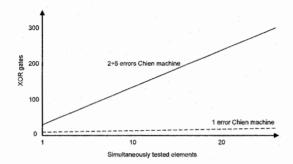

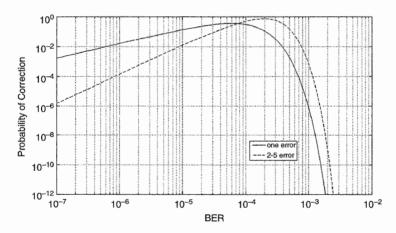

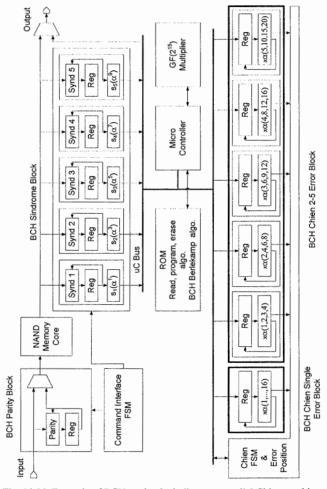

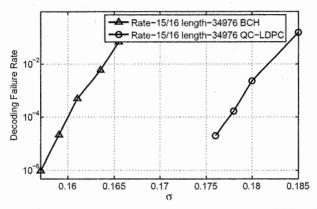

This task is typically executed by a specific hardware inside the memory controller. Examples of memories with embedded ECC are also reported [9–11]. Most popular ECC codes, correcting more than one error, are Reed–Solomon and BCH [12]. While the encoding takes few controller cycles of latency, the decoding phase can take a large number of cycles and visibly reduce read performance as well as the memory response time at random access.

There are different reasons why the read operation may fail (with a certain probability):

- Noise (e.g. at the power rails)

- V<sub>TH</sub> disturbances (read/write of neighbor cells)

- · Retention (leakage problems)

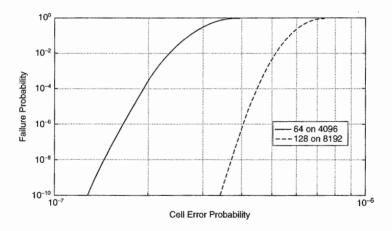

The allowed probability of failed reads after correction is dependent on the use case of the application. Price sensitive consumer application, with a relative low number of read accesses during the product life time, can tolerate a higher probability of read failures as compared to high-end applications with a high number of memory accesses. The most demanding applications are cache modules for processors.

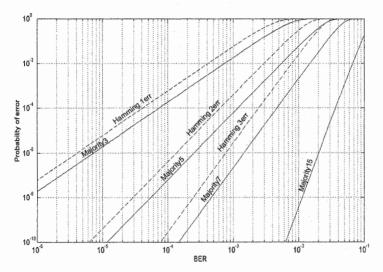

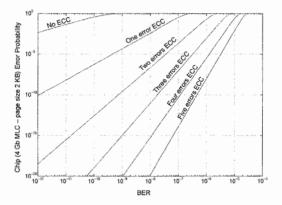

The reliability that a memory can offer is its intrinsic error probability. This probability could not be the one that the user wishes. Through ECC it is possible to fill the discrepancy between the desired error probability and the error probability offered by the memory (Chap.14).

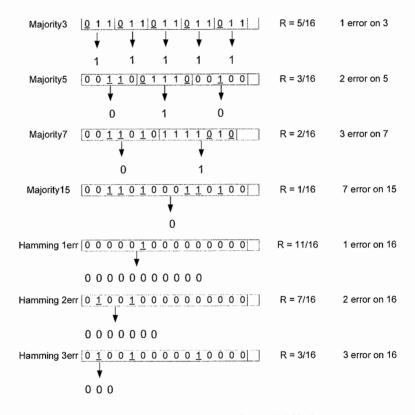

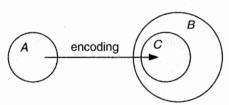

The object of the theory of error correction codes is the addition of redundant terms to the message, such that, on reading, it is possible to detect the errors and to recover the message that has most probably been written.

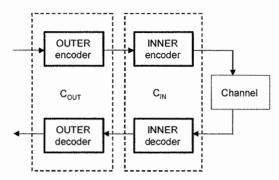

Methods of error correction are applied for purpose of data restoration at read access. Block code error correction is applied on sub-sectors of data. Depending on the used error correcting schemes, different amount of redundant bits called parity bits are needed.

Between the length n of the code words, the number k of information bits and the number t of correctable errors, a relationship known as Hamming inequality exists, from which it is possible to compute the minimum number of parity bits:

$$\sum_{i=0}^{l} \binom{n}{i} \le 2^{n-k} \tag{2.3}$$

It is not always possible to reach this minimum number: the number of parity bits for a good code must be as near as possible to this number. On the other hand, the bigger the size of the sub-sector is, the lower the relative amount of spare area (for parity bits) is. Hence, there is an impact in Flash die size.

BCH and Reed-Solomon codes have a very similar structure, but BCH codes require less parity bits and this is one of the reasons why they were preferred for an ECC embedded in the NAND memory [11].

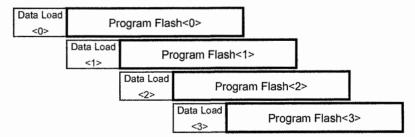

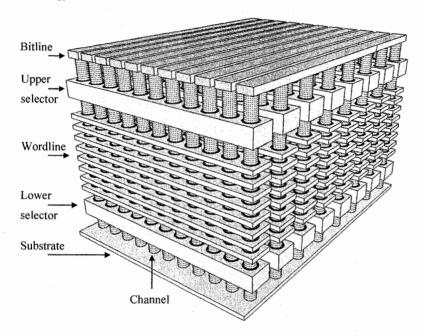

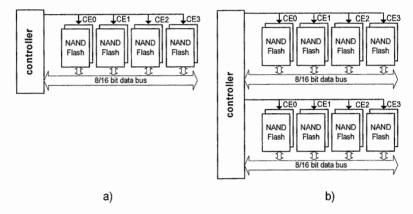

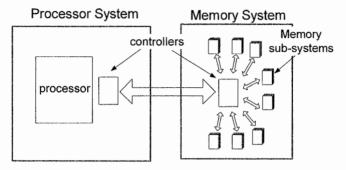

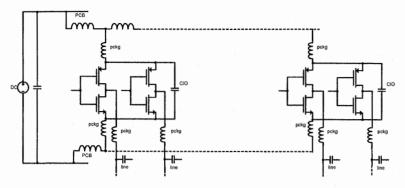

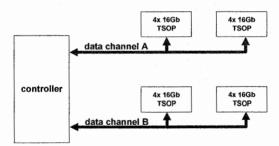

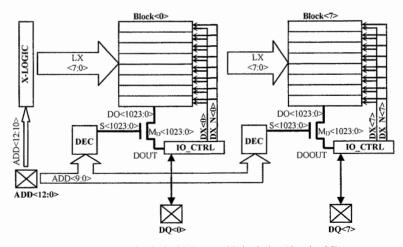

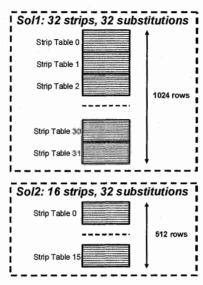

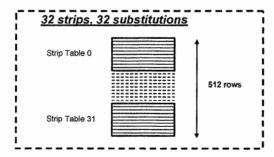

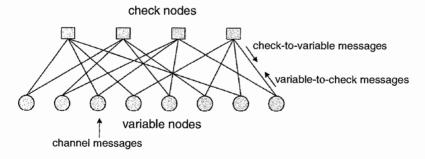

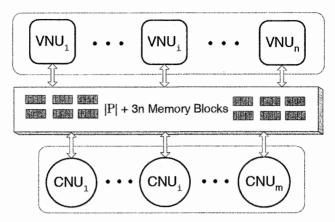

#### 2.4.2 Multi-die systems

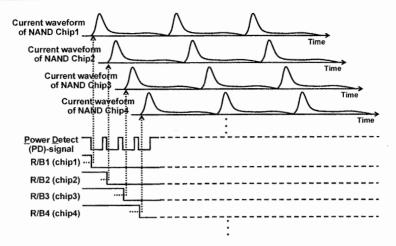

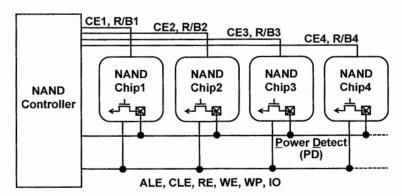

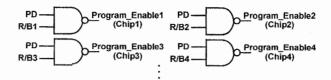

A typical memory system is composed by several NAND memories. Typically, an 8-bit bus, usually called channel, is used to connect different memories to the controller (Fig. 2.32). It is important to underline that multiple Flash memories in a system are both a means for increasing storage density and read/write performance [13].

Operations on a channel can be interleaved which means that another memory access can be launched on an idle memory while the first one is still busy (e.g. writing or erasing). For instance, a sequence of multiple write accesses can be directed to a channel, addressing different NANDs, as shown in Fig. 2.37: in this way, the channel utilization is maximized by pipelining data load, while the program operation takes place without requiring channel occupation. A system typically has two to eight channels operating in parallel (or even more).

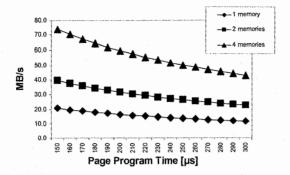

As shown in Fig. 2.38, using multiple memory components is an efficient way to improve data throughput while having the same page programming time.

The memory controller is responsible for scheduling the distributed accesses at the memory channels. The controller uses dedicated engines for the low level communication protocol with the Flash.

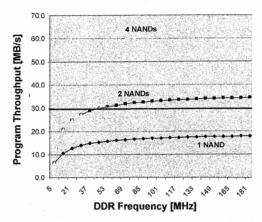

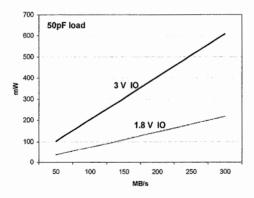

Moreover it is clear that the data load phase is not negligible compared to the program operation (the same comment is valid for data output): therefore increasing I/O interface speed is another smart way to improve general performance: high-speed interfaces, like DDR, have already been reported [14] and they are discussed in more details in Chap. 7. Figure 2.39 shows the impact of DDR frequency on program throughput. As the speed increases, more NAND can be operated in parallel before saturating the channel. For instance, assuming a target of 30 MB/s, 2 NANDs are needed with a minimum DDR frequency of about 50 MHz. Given a page program time of 200 µs, at 50 MHz four NANDs can operate in interleaved mode, doubling the write throughput. Of course, power consumption has then to be considered.

There are also hybrid architectures which combine different types of memory. Most common is usage of DRAM as memory cache. During write access the cache is used for storing data before transfer to the Flash. The benefit is that data updating, e.g. in tables, is faster and does not wear out the Flash.

Fig. 2.37. Interleaved operations on one Flash channel

Fig. 2.38. Program throughput with an interleaved architecture as a function of the NAND page program time

Fig. 2.39. Program throughput with an interleaved architecture as a function of the channel DDR frequency. 4 kB page program time is  $200~\mu s$

Another architecture uses a companion NOR Flash for purpose of "in-place execution" of software without pre-fetch latency. For hybrid solutions, a multi-die approach, where different memories are packaged in the same chip, is a possibility to reduce both area and power consumption.

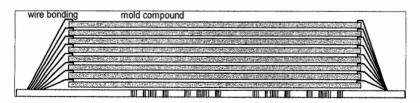

# 2.4.3 Die stacking

Reduced form factor has been one of the main drivers for the success of the memory cards; on the other hand, capacity requirement has grown dramatically to the extent that standard packaging (and design) techniques are no longer able to sustain the pace. In order to solve this issue, two approaches are possible: advanced die stacking and 3D technologies.

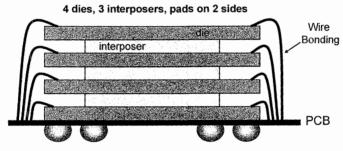

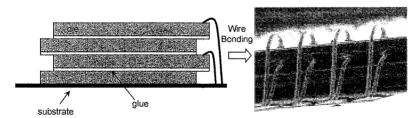

The standard way to increase capacity is to implement a multi-chip solution, where several dies are stacked together. The advantage of this approach is that it can be applied to existing bare die, as shown in Fig. 2.40: die are separated by means of a so-called interposer, so that there is enough space for the bonding wires to be connected to the pads.

On the other hand, the use of the interposer has the immediate drawback of increasing the height of the multi-chip, and height is one of the most relevant limiting factors for memory cards.

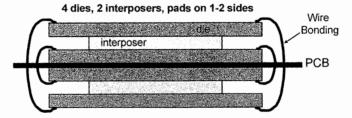

One way to overcome this issue is to exploit both sides of the PCB, as shown in Fig. 2.41: in this way, the PCB acts as interposer, and components are evenly flipped on the two sides of the PCB. Height is reduced, but there is an additional constraint on design: in fact, since the lower die is flipped, its pads are no longer matching those of the upper die. The only way to have corresponding pads facing one another is to design the pad section in such a way that pad to signal correspondence can be scrambled: that is, when a die is used as the bottom one, it is configured with mirrored-pads. Such a solution is achievable, but chip design is more complex (signals must be multiplexed in order to perform the scramble) and chip area is increased, since it might be necessary to have additional pads to ensure symmetry when flipping.

Fig. 2.40. Standard die stacking

Fig. 2.41. Flipped die stacking

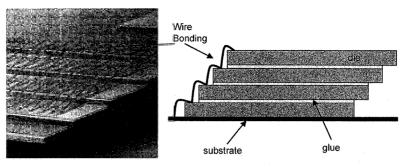

Fig. 2.42. Staircase die stacking: four dies, zero interposers, pads on one side

The real breakthrough is achieved by completely removing the interposer, thus using all the available height for silicon (apart from a minimum overhead due to the die-to-die glue). Figure 2.42 shows an implementation, where a staircase arrangement of the dies is used: any overhead is reduced to the minimum, bonding does not pose any particular issue and chip mechanical reliability is maintained (the disoverlap between dies is small compared to the die length, and therefore the overall stability is not compromised, since the upmost die does not go beyond the overall center of mass).

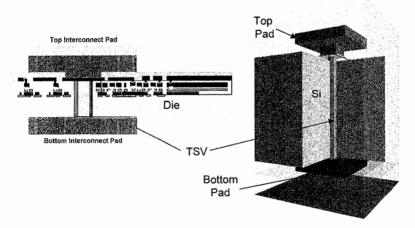

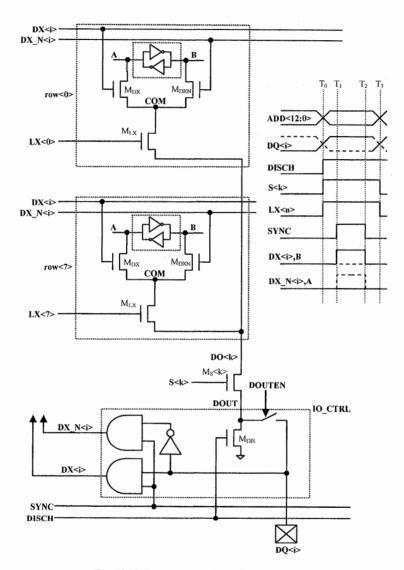

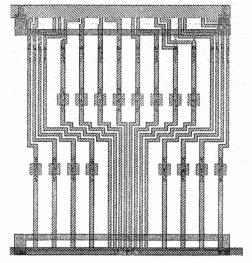

The drawback is that such a solution has a heavy impact on chip design, since all the pads must be located on the same side of the die. In a traditional memory component, pads are arranged along two sides of the device: circuitry is then evenly located next to the two pad rows and the array occupies the majority of the central area. Figure 2.43 shows the floorplan of a memory device whose pads lie on two opposite sides.

Fig. 2.43. Memory device with pads along opposite sides

If all pads lie on one side, as shown in Fig. 2.44, chip floorplan is heavily impacted [15]: most of the circuits are moved next to the pads in order to minimize the length of the connections and to optimize circuit placement. But some of the circuits still reside on the opposite side of the die (for instance, part of the decoding logic of the array and part of the page buffers, i.e. the latches where data are stored, either to be written to the memory or when they are read from the memory to be provided to the external world).

Of course, such circuits must be connected to the rest of the chip, both from a functional and from a power supply point of view. Since all pads are on the opposite side, including power supply ones, it is necessary to re-design the power rail distribution inside the chip, making sure that the size and geometry of the rails is designed properly, in order to avoid IR drops issues (i.e. the voltage at the end of the rail is reduced due to the resistive nature of the metal line).

One of the main disadvantages of staircase stacking is the increased size in the direction opposite to the pad row. Of course, this fact limits the number of dies, given a specific package.

Fig. 2.44. Memory device with pads along one side

Fig. 2.45. "Snake" die stacking

Once the design effort has been done, a possible alternative is the "snake" stacking as shown in Fig. 2.45. In this case, thanks to the double side bonding, the overall size can be clearly reduced.

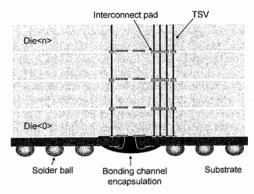

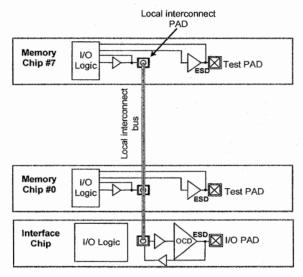

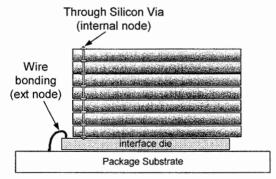

Recently, another stacking option came into the game: *Through Silicon Via* (TSV) [16–19]. With this technology, dies are directly connected without asking for a wire bonding, as depicted in Fig. 2.46. A 3-D view of one TSV connection is shown in Fig. 2.47. One of the main advantages is the reduction of the interconnection length and the associated parasitic *RC*. As a result, data transfer rate can be definitely improved, as well as power consumption.

Fig. 2.46. Multiple die stacking with TSV technology

Fig. 2.47. Die with TSV (left) and TSV 3-D view (right)

In fact, DRAM are the main drivers for TSV technology as, with the standard bonding technology, they cannot stack more than two dies in the same package.

The solutions presented so far exploit advances in stacking techniques, eventually requiring changes in chip design floorplan. Quite recently, advanced design and manufacturing solutions have been presented, where the 3D integration [20] is performed directly at chip level.

#### 2.4.4 3D memories and XLC storage

The 3D concept is simple: instead of stacking several dies, each of which being a fully-functional memory component, it is possible to embed in the same silicon die more than one memory array. In this way, all the control logic, analog circuits and the pads can be shared by the different memory arrays. In order to keep the area to the minimum, the memory arrays are grown one on top of the other, exploiting the most recent breakthroughs in silicon manufacturing technology.

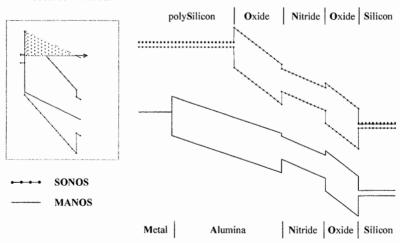

Two different solutions have been recently presented for NAND Flash memories: in one case [21, 22], the topology of the memory array is the usual one, and another array is diffused on top of it, as shown in Fig. 2.48, so that two layers exist. Therefore the NAND strings (i.e. the series of Flash memory cells which is the basic building block of the array) are diffused on the X–Y plane. Around the arrays, all the peripheral circuitry is placed in the first (i.e. lower) layer. The only exception is the wordline (WL) decoder. To avoid Fowler–Nordheim (FN) erasing of the unselected layer, all WLs in that layer must be floating, just like the WLs of unselected blocks in the selected layer. This function is performed by a layer-dedicated WL decoder.

Fig. 2.48. Three-dimensional horizontal memory array

The second approach [23, 24] is shown in Figs. 2.49 and 5.9: in this case the NAND strings are orthogonal to the die (along the Z direction). NAND string is on the plugs located vertically in the holes punched through whole stack of the gate plates. Each plate acts as control gate except the lowest plate which takes a role of the lower select gate. 3-D charge trap memories are described in Sect. 5.3.

The density of the memory can also be increased acting at cell level: in its simplest form, a non-volatile memory cell stores one bit of information: '1' when the cell is erased and '0' when it is programmed: Sensing techniques for measuring the amount of electrical charge stored in the floating gate are described in Chap. 8. This kind of storage is referred to as Single Level Cell (SLC).

The concept can be extended by having four different charge levels (corresponding to logic values 00, 01, 10, 11) inside the floating gate, thus leading to the so-called Multi Level Cell (MLC) approach, i.e. 2 bit/cell. Chapter 10 is entirely dedicated to MLC NAND devices.

Several devices implementing the 2 bit/cell technology are commercially available, and indeed MLC has become a synonym for 2 bits/cell. Almost all the Flash cards contain MLC devices as they are cheaper than SLC.

The circuitry required to read multiple bits out of a cell is of course more complex than in the case of single bit, but the saving in term of area (and the increase in density) is worth the complexity. The real disadvantage lies in reduced endurance and reliability.

In terms of endurance, as already mentioned previously, a SLC solution can withstand up to 100,000 program/erase cycles for each block, while a MLC solution is usually limited to 10,000. For this reason, wear leveling algorithms must be used, as already outlined in Sect. 2.4.1. In terms of reliability, it is clear that the more levels are used, the more read disturbs can happen, and therefore the ECC capability must be strengthened.

Fig. 2.49. Three dimensional vertical memory array: (a) top down view of 3-D vertical memory array; (b) equivalent circuit of the vertical NAND string

The concept has been extended recently to 3 bit/cell and 4 bit/cell, where 8 and 16 different charge levels are stored inside the same cell. This storage approach is known as XLC and it is described in Chap. 16.

#### References

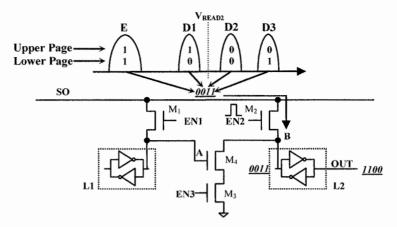

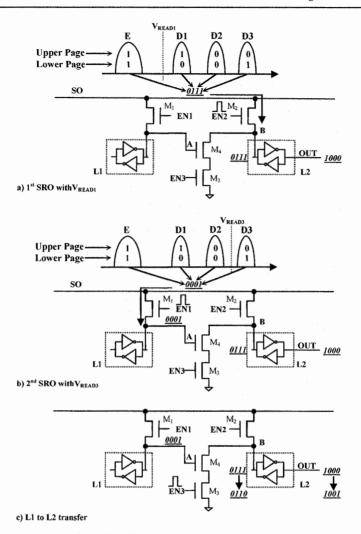

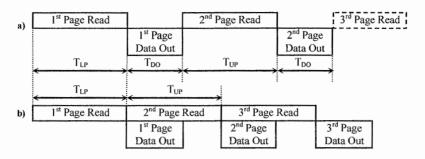

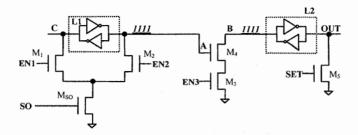

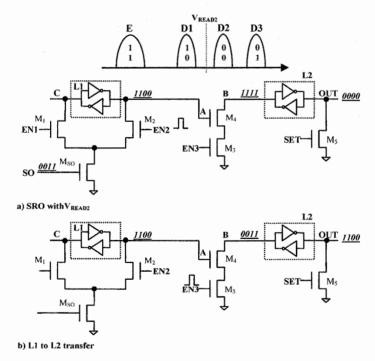

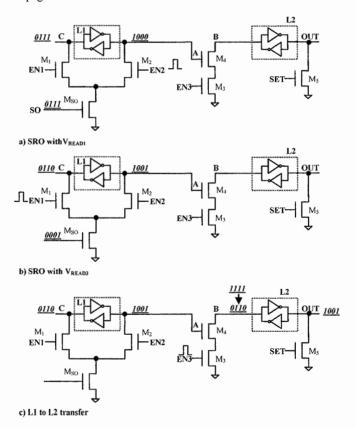

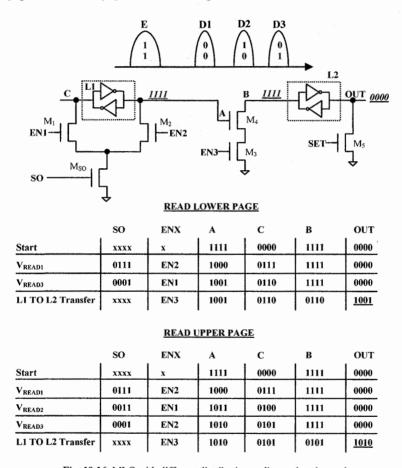

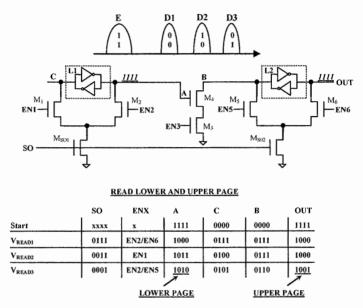

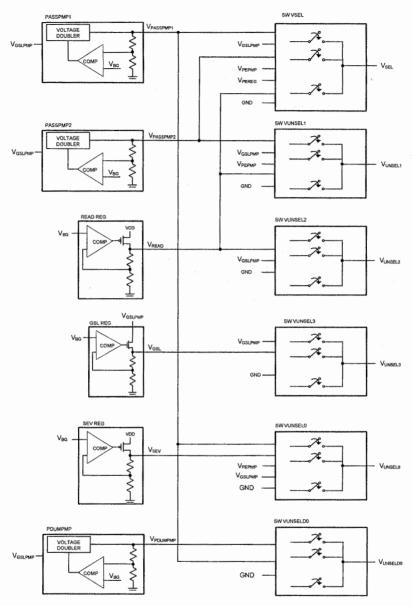

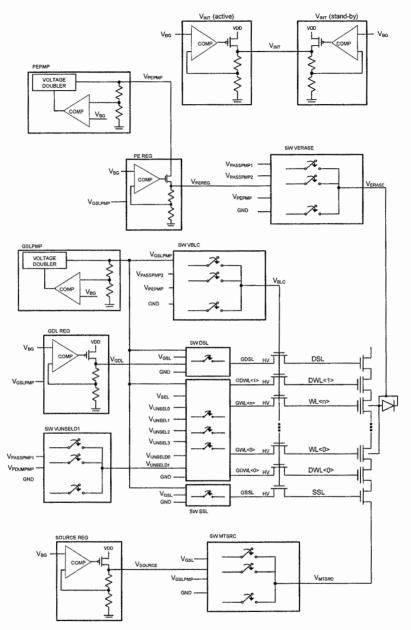

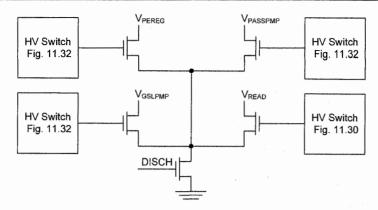

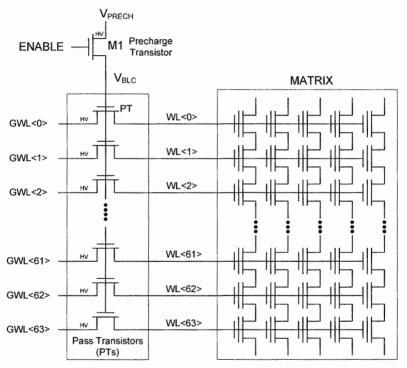

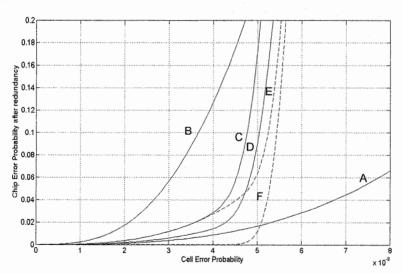

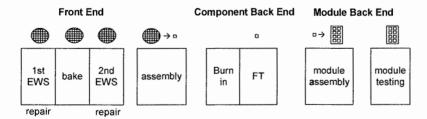

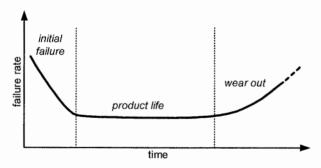

- G. Campardo, R. Micheloni, D. Novosel, "VLSI-Design of Non-Volatile Memories", Springer-Verlag, 2005.