|                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TILITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                  | ·                                                       | ney Dock                                                           |                                                                                                                                                                                                                               |                                                                                                                                                                  | 17,203A                                                                                                                                                                                                                                                                                                                                                                 | plays a valid OMB control numb                                                                                                                                                                                                                                                              |                |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| F                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | APPLICAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                  | First I                                                 | Inventor                                                           | Fran                                                                                                                                                                                                                          | ciscus                                                                                                                                                           | G. DeJong                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                             |                |

|                                                                           | TRAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | NSMITTAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                  | Title                                                   | TEST                                                               |                                                                                                                                                                                                                               | RCO                                                                                                                                                              | NNECTS BETV                                                                                                                                                                                                                                                                                                                                                             | EST UNIT AND METHOD OF<br>VEEN A FIRST AND A SECO                                                                                                                                                                                                                                           |                |

|                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | al applications under 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | , O.F.N. 1.03(0))                                                                                                                                                | Expre                                                   |                                                                    | abel No.                                                                                                                                                                                                                      |                                                                                                                                                                  | V312014                                                                                                                                                                                                                                                                                                                                                                 | 12445 7/16/0:                                                                                                                                                                                                                                                                               | 5              |

| See MPEP                                                                  | APPLICATION ELEMENTS<br>See MPEP chapter 600 concerning utility patent application contents.                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                  | 1                                                       | ADDR                                                               | ESS 1                                                                                                                                                                                                                         | <b>TO</b> :                                                                                                                                                      | Box Patent                                                                                                                                                                                                                                                                                                                                                              | ommissioner for Patents                                                                                                                                                                                                                                                                     | R              |

| 1. ⊠<br>2. □<br>3. ⊠<br>4. ⊠<br>5. Oath or<br>a. □<br>b. ⊠<br>i. [        | ee Transmittal<br>Submit an original ar<br>Applicant claims<br>bee 37 CFR 1.2<br>Descriptive title o<br>Cross Reference<br>Statement Regar<br>Reference to seq<br>or a computer pro<br>Background of th<br>Brief Summary of<br>Brief Description<br>Detailed Descript<br>Claim(s)<br>Abstract of the Di<br>rawing(s) (35 L<br>Declaration<br>Newly execute<br>Copy from a p<br>(for a continual<br><u>DELETION</u><br>Signed stateme<br>named in the pr<br>1.63(d)(2) and | Form (e.g., PTO/S<br>nd a duplicate for fee prois<br>as small entity status<br>7. [Tot:<br>ment set forth below]<br>of the Invention<br>to Related Application<br>ding Fed sponsored I<br>juence listing, a table,<br>ogram listing appendi:<br>le Invention<br>of the Drawings ( if fil-<br>ion<br>isclosure<br>J.S.C.113) [Tot<br>[Tot:<br>ed (original or copy<br>rior application (37<br>ation/divisional with<br>OF INVENTOR(<br>ent attached deleting i<br>rior application, see 3 | B/17)<br>cessing)<br>al Pages 21 ]<br>al Pages 21 ]<br>ans<br>R & D<br>x<br>led)<br>al Pages<br>c CFR 1.63 (d))<br>Box 18 completed<br>S)<br>nventor(s)<br>7 CFR | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1          | (<br>8. Nucle<br>(if a <u>p</u><br>a. □<br>b. Spe<br>i. [<br>ii. [ | Compute<br>cotide an<br>plicable,<br>Comput<br>cofficatio<br>CD-RC<br>paper<br>Stateme<br>ACCO<br>Assign<br>37 C.F.<br>(when<br>English<br>Informa<br>Statem<br>Prelimi<br>Return<br>(Should<br>Certifie<br>(if fore<br>Nonpu | r Pro<br>nd/or all n<br>er Re<br>n Se<br>DM o<br>ents v<br>MPA<br>ment<br>Res<br>there<br>n Trai<br>ation<br>(inary<br>Recce<br>d be<br>d Co<br>bilica<br>3)(i). | D-R in duplic<br>pgram (Appen<br>Amino Acid S<br>ecessary)<br>eadable Form<br>quence Listin<br>r CD-R (2 cop<br>ren fying ident<br>NYING APPI<br>Papers (cove<br>3.73(b) Staten<br>is an assigned<br>nslation Docu<br>Disclosure<br>IDS)/PTO-144<br>Amendment<br>eipt Postcard<br>specifically ite<br>py of Priority<br>inority is clain<br>ion Request<br>Applicant mu | ate, large table or<br>dix)<br>iequence Submission<br>(CRF)<br>g on:<br>ies); or<br>ity of above copies<br>ICATIONS PARTS<br>er sheet & document(s))<br>hent Power of<br>Attorney<br>ment ( <i>if applicable</i> )<br>Copies of IDS<br>49 Citations<br>(MPEP 503)<br>pmized)<br>Document(s) | 16235 U.S. PTO |

| or in an Ap<br>Cont<br>Prior ap<br>For CONTIN<br>under Box<br>The Incorpo | Dication Data Sh<br>nuation  <br>Dication information<br>UATION or DIVIS<br>Sb, is considered                                                                                                                                                                                                                                                                                                                                                                             | neet under 37 CFR 1<br>Divisional<br>On: Examiner<br>SIONAL APPS only:<br>1 a part of the disclo<br>be relied upon wher<br>ar Code Label                                                                                                                                                                                                                                                                                                                                                 | 1.76:<br>Continuation-in-p<br>Craig S. Miller<br>The entire disclosu                                                                                             | oart (Cli<br>re of th<br>anying<br>Inadve<br>ONDE<br>73 | e prior a<br>or divisi<br>ortently c<br>NCE AI                     | c<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()<br>()                                                                                                                                               | of prio<br>Group<br>In, fro<br>Ilcatic<br>om th                                                                                                                  | r application No<br>/ Art Unit: 285i<br>om which an oa<br>on and is herei<br>he submitted a                                                                                                                                                                                                                                                                             | r<br>hth or declaration is supplied<br>by incorporated by reference                                                                                                                                                                                                                         |                |

| Name                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <u></u>                                                                                                                                                          |                                                         |                                                                    |                                                                                                                                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                             |                |

| Address                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                  |                                                         |                                                                    |                                                                                                                                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                             |                |

| City                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | State                                                                                                                                                            |                                                         |                                                                    |                                                                                                                                                                                                                               |                                                                                                                                                                  | Zip Code                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                             |                |

| Country                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Telephone                                                                                                                                                        |                                                         |                                                                    |                                                                                                                                                                                                                               |                                                                                                                                                                  | Fax                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                             |                |

| Name (Pi                                                                  | int/Type)                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Eric M. Bram                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ana anina anina anina                                                                                                                                            | Reg                                                     | gistratio                                                          | n No. (At                                                                                                                                                                                                                     | tome                                                                                                                                                             | ey/Agent)                                                                                                                                                                                                                                                                                                                                                               | 37,285                                                                                                                                                                                                                                                                                      |                |

|                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                  | 1                                                       |                                                                    |                                                                                                                                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                             |                |

Burden Hour Statement: This form is estimated to take 0.2 hours to complete. Time will vary depending upon the needs of the individual case. Any comments on the amount of time you are required to complete this form should be sent to the Chief Information Officer, U.S. Patent and Trademark

Approved for use through 10/31/2002, OMB 0651-0032 U.S. Patent and Trademark Office: U.S. DEPARTMENT OF COMMERCE

Under the Paperwork Reduction Act of 1995, no persons are required to respond to a collection of information unless it displays a valid OMB control number.

**F** .

|                       |                                                          |                                                                   |             | Complete If Known |                 |                                                                                          |           |

|-----------------------|----------------------------------------------------------|-------------------------------------------------------------------|-------------|-------------------|-----------------|------------------------------------------------------------------------------------------|-----------|

| FE FE                 | E TRANSM                                                 | IITTAL                                                            | Applic      | ation Numb        | er              |                                                                                          | ·         |

|                       | for FY 20                                                | 02                                                                |             |                   | <u> </u>        |                                                                                          |           |

|                       |                                                          |                                                                   | Filing      |                   |                 |                                                                                          |           |

|                       | Patent fees are subject to ann                           | ual mulsion                                                       |             | Named Inver       | ntor F          | ranciscus G. DeJong                                                                      |           |

| •                     | atem less are subject to anno                            |                                                                   |             | iner Name         |                 |                                                                                          | ,         |

|                       |                                                          |                                                                   | Group       | / Art Unit        |                 |                                                                                          |           |

| TOTAL AMOU            | INT OF PAYMENT (\$                                       | 5) 750.00                                                         | Attorr      | ey Docket N       | NO. F           | PHN 17,203A                                                                              |           |

|                       | METHOD OF PAYMENT (ch                                    |                                                                   |             |                   |                 | E CALCULATION (continued)                                                                |           |

| 1. 🖾                  | The Commissioner is here<br>indicated fees and credit ar |                                                                   | 3. AD       | DITIONAL FI       | Sm              | nall                                                                                     |           |

| Deposit               |                                                          |                                                                   | Fee         | Entity<br>Fee F   | ee Fe           | Fee Description                                                                          | Fee       |

| Account               | 14-1270                                                  |                                                                   | Code<br>105 | •••               | of (\$)         | ) ·                                                                                      | Paid      |

| Number                |                                                          |                                                                   | 105         |                   | 05 65<br>27 25  | • •                                                                                      |           |

| Deposit               |                                                          |                                                                   |             |                   | -               | or cover sheet.                                                                          |           |

| Account<br>Name       |                                                          |                                                                   | 139         |                   | 39 13           | <b>V</b>                                                                                 |           |

| _                     | Additional Fee Required                                  |                                                                   | 147<br>112  |                   | 47 2,5<br>12 92 | 520 For filing a request for reexamination<br>20° Requesting publication of SIR prior to | <b>  </b> |

|                       | CFR 1.16 and 1.17                                        |                                                                   |             |                   |                 | Examiner action                                                                          |           |

| See 37 CF             |                                                          |                                                                   | 113         | 1,840* 1          | 13 1,6          | 840* Requesting publication of SIR after<br>Examiner action                              |           |

| 2. 🔲 Paymen           | t Enclosed:                                              |                                                                   | 115         | 110 2             | 15 55           | Extension for reply within first month                                                   |           |

| Check                 | Credit card Mor                                          |                                                                   | 116         | 400 2             | 16 20           | 0 Extension for reply within second<br>month                                             |           |

|                       | FEE CALCULATIO                                           |                                                                   | 117         |                   | 17 46           | 60 Extension for reply within third month                                                |           |

| 1. BASIC FIL          |                                                          | مراجعية إفغار المحمد المحمد بمحمد المحمد المحمد المحمد المحمد الم | 118         | 1,440 2           | 18 72           | 20 Extension for reply within fourth<br>month                                            |           |

| Large Entity S        |                                                          |                                                                   | 128         | 1,960 2           | 28 98           |                                                                                          |           |

|                       | ee Fee Fee Descrip                                       |                                                                   | 119         |                   | 19 16           | •••                                                                                      |           |

| (1)                   | Code (\$)<br>101 370 Utility filing fe                   | e 750                                                             | 120         | 320 2             | 20 16           | 60 Filing a brief in support of an appeal                                                |           |

|                       | 06 165 Design filing                                     |                                                                   | 121         | 280 23            | 21 14           |                                                                                          |           |

|                       | 07 255 Plant filing fe                                   |                                                                   | 138         | 1,510 1           | 38 1,5          | 510 Petition to institute a public use proceeding                                        |           |

|                       | 08 370 Reissue filing                                    |                                                                   | 140         | 110 2             | 40 55           | Petition to revive - unavoidable                                                         |           |

| 114 160 2             | 14 80 Provisional fi                                     | Iling fee                                                         | 141         | •                 | 41 64           |                                                                                          |           |

|                       | SUBTOTAL (1)                                             | (\$) 750                                                          | 142         | •                 | 42 64<br>43 23  |                                                                                          |           |

| 2. EXTRA CLAIM        | FFES                                                     |                                                                   | 144         |                   | 44 31           |                                                                                          |           |

|                       | Extra                                                    | Fee from Fee                                                      | 122         | 130 1;            | 22 13           | 0 Petitions to the Commissioner                                                          |           |

| Total Claims          |                                                          | K Paid = 0                                                        | 123         | 50 1              | 23 50           |                                                                                          |           |

| Independent<br>Claims |                                                          | x = 0                                                             | 126         | 180 1             | 26 18           | 30 Submission of Information Disclosure<br>Stmt                                          |           |

| Aultiple              |                                                          | <pre></pre>                                                       | 581         | 40 5              | 81 40           | Recording each patent assignment<br>per property (times number of<br>properties)         |           |

| Large Entity          | Small Entity                                             |                                                                   | 146         | 740 24            | 46 37           | Filing a submission after final rejection<br>(37 CFR § 1.129(a))                         |           |

| Fee Fee<br>Code (\$)  | Fee Fee Fee Desc Code (\$)                               | ription                                                           | 149         | 740 24            | 49 37           |                                                                                          |           |

| 103 18                |                                                          | excess of 20                                                      | 179         | 740 2             | 279 37          | 70 Request for Continued Examination (RCE)                                               |           |

| 102 84<br>104 280     | •                                                        | ent claims in excess of 3<br>ependent claim, if not paid          | 169         |                   |                 |                                                                                          |           |

| 109 84                | 209 42 ** Reissue                                        | independent claims over                                           | 169         | 900 1             | 169 90          | 00 Request for expedited examination<br>of a design application                          |           |

| 110 18                | 210 9 ** Reissue                                         | e claims in excess of 20 and                                      |             |                   |                 | -                                                                                        |           |

| 10 10                 | 210 9 over origin                                        | nal patent                                                        | Other f     | ee (specify) _    |                 |                                                                                          |           |

|                       | SUBTOTAL (2)                                             | ) (\$)0                                                           | ] [         |                   |                 |                                                                                          | L         |

| <b>tt</b> es event '  | nu said if anotos Foo Polesso                            |                                                                   | Redu        | ced by Basic      | Filing Fe       | ee Paid SUBTOTAL (3) (\$) 0                                                              |           |

| - or number previou   | sly paid, if greater; For Reissues                       | , see above                                                       |             |                   |                 |                                                                                          |           |

| SUBMITTED BY          |                                                          |                                                                   |             |                   |                 | Complete (if applicable)                                                                 |           |

|                       | Michael E Be                                             | 1h                                                                |             | 33,3              | 57              |                                                                                          |           |

| SUDMITTED OT      |                              | -                                | COIL                        |           |              |

|-------------------|------------------------------|----------------------------------|-----------------------------|-----------|--------------|

| Name (Print/Type) | Michael E Balk<br>Eriem-Bran | Registration No. Attorney/Agent) | 33,357<br><del>37,285</del> | Telephone | 914-333-9535 |

| Signature         | muluer                       | Bick                             |                             | Date      | 7/16/03      |

WARNING: Information on this form may become public. Credit card information should not be included on this form. Provide credit card information and authorization on PTO-2038.

Burden Hour Statement: This form is estimated to take 0.2 hours to complete. Time will vary depending upon the needs of the individual case. Any comments on the amount of time you are required to complete this form should be sent to the Chief Information Officer, U.S. Patent and Trademark Office, Washington, DC 20231. DO NOT SEND FEES OR COMPLETED FORMS TO THIS ADDRESS. SEND TO: Assistant Commissioner for Patents, Washington, DC 20231.

5

PCT/IB99/00172

CIRCUIT WITH INTERCONNECT TEST UNIT AND A METHOD OF TESTING INTERCONNECTS BETWEEN A FIRST AND A SECOND ELECTRONIC CIRCUIT

The invention relates to an electronic circuit comprising: a plurality of input/output (I/O) nodes for connecting the electronic circuit to a further electronic circuit via interconnects, a main unit for implementing a normal mode function of the electronic circuit, and a test unit for testing the interconnects, the electronic circuit having a normal mode in which the I/O nodes are logically connected to the main unit and a test mode in which the I/O nodes are logically connected to the test unit.

The invention further relates to a method of testing interconnects between a first electronic circuit and a second electronic circuit, the first electronic circuit comprising a main unit implementing a normal mode function of the first electronic circuit, and a test unit for

10 testing the interconnects, the method comprising the steps of logically connecting the test unit to the interconnects, and putting test data on the interconnects by the second electronic circuit.

Such a circuit is known from "Boundary-scan test, a practical approach", H. Bleeker, P. van den Eijnden and F. de Jong, Kluwer, Boston, 1993, ISBN 0-7923-9296-5, Figures 1-19, which shows an integrated (IC) in accordance with the boundary-scan test

- 15 standard IEEE Std. 1149.1. The known circuit has a main unit or core logic that is responsible for providing some arbitrary specified function in a normal mode of the circuit. The known circuit further has a test unit for in a test mode performing an interconnect test, i.e. a test whether the circuit is properly connected to a further circuit via its I/O nodes or IC pins. Efficient interconnect test of miniaturised and/or complex circuit assemblies is a necessary

- 20 part of the production process of such assemblies. The boundary-scan test technique is accepted as standardised solution for interconnect test. It is available in most of the leading microprocessor families and is supported for in-house developed application specific ICs through automated tools in the IC design process.

- The test unit of the known boundary-scan circuit includes a test control unit or 25 Test Access Port controller and a shift register or boundary-scan register along the circuit boundary, cells of the shift register being connected to I/O nodes corresponding to the interconnects to be tested. The test control unit has a state machine controlling states of the shift register, examples of such states being a shift state for shifting in/out data into the shift register and a capture state for capturing data originating from the interconnects into the shift

## CONFIRMATION COPY

5

25

## PCT/IB99/00172

register. The shift register is accessible from outside the circuit via a Test Data In (TDI) node and a Test Data Out (TDO) node. A Test Clock signal (TCK) and a Test Mode Select signal (TMS) are provided from outside the circuit to the test control unit for stepping through the various states. In the normal mode of the known circuit, the I/O nodes are logically connected to the main unit, thereby allowing the circuit to perform its normal mode function. In the test mode of the known circuit, the I/O nodes are logically connected to the test unit, thereby giving the test unit access to the interconnects.

Provided that also the further circuit is equipped with a test unit in accordance with the boundary-scan test standard, the interconnects between the two circuits can be tested according to the standard boundary-scan test method. Hereto, appropriate test data is first shifted into the shift registers of the two circuits and is subsequently applied to the interconnects. Then, response data originating from the interconnects is captured into the shift registers and subsequently shifted out of the shift registers for observation. From the response data it can be determined whether the circuits are properly interconnected. For a single

15 interconnect this means that to one of its ends a signal is applied and at the other end it is observed whether that signal is transmitted. In this way, an open circuit in an interconnect can be found. Additionally, a number of test patterns will be applied to the interconnects in order to check for short-circuits between neighbouring interconnects, or between an interconnect and a power supply line. Essentially, interconnect testing comes down to applying test data to one end of an interconnect and observing response data at another end, in such a way that open

circuits and short circuits are detected.

A problem with the boundary-scan approach is that for some circuits pin count and pin compatibility considerations inhibit the addition of extra pins to a circuit design for the TCK, TMS, TDI, TDO and the optional TRSTN signals. Moreover, the price-pressure in some semiconductor fields is such that it is considered to be too expensive to reserve area for interconnect test of the size as required by boundary-scan circuitry.

It is an object of the invention to provide a circuit as specified in the preamble, that allows interconnect testing with reduced overhead in terms of required I/O nodes and/or area. This object is achieved according to the invention in an electronic circuit, which is characterised in that in the test mode the test unit is operable as a low complexity memory via the I/O nodes. Low complexity memories are those memories that do not have to be put through a complex initialisation process before they can be accessed, and that have simple access protocols without dynamic restrictions. Such a test unit enables an alternative procedure

5

PCT/1B99/00172

for applying test data to one end of an interconnect and observing response data at the other end. If the low complexity memory has a read-only character and holds pre-stored test data at a number of addresses, the test unit produces this pre-stored test data at its side of the interconnects when address data and appropriate control data are applied to it by the further circuit via the interconnects. The further circuit then receives response data, which should be

- identical to the pre-stored test data. In this way, both the interconnects that are used to carry the address and control data and the interconnects that are used to carry the pre-stored data itself are tested. It is important that particular input data for the test unit, i.e. the address, result in output data from the test unit that are known a priori, i.e. the stored data. If the low

- 10 complexity memory allows both read and write access, the further circuit can apply test data to its side of the interconnects in a write mode of the test unit, thereby storing the test data in the test unit. In a subsequent read mode of the test unit, the further circuit can read back response data.

- Whether the test unit has a read-only or a read/write behaviour, it does not need a state machine like the boundary-scan state machine and can therefore be implemented consuming less area. Moreover, the simple operation of the test unit allows less pins or even no pins at all to be reserved for controlling the test unit in the test mode. For both a read-only and a read/write test unit, a subset of the interconnects is used as a data bus for exchanging the storage data. At least in the case that the test unit has a read/write behaviour, a further subset

- 20 of the interconnects is used as a control bus, including, for example, control lines for controlling the read and/or write process. At least in the case that the test unit has a read-only behaviour, a still further subset of the interconnects is used as an address bus for selecting the storage location to read from. An important aspect of the invention is that one is free how to map the data bus, the control bus and/or the address bus on the interconnects to be tested.

Access to the control bus, the address bus, and the data bus during test mode could be provided, for example, via boundary-scan circuitry of the further circuit. Then, with ordinary boundary-scan test equipment, data can be shifted in and out of the further circuit. In this way, data to be supplied to the control bus and/or the address bus and data returned by the test unit on the data bus can be handled. As a further example, if the further circuit is a

30 programmed microprocessor or Application-Specific IC (ASIC), the further circuit could perform the interconnect test in a stand alone fashion, without the need for external equipment for feeding the further circuit with the test data and for evaluating the response data. It is noted that the further circuit alternatively could consist of two or more separate circuits, together operating the test unit as a low complexity memory.

> IPR2021-01488 Apple EX1005 Page 5

### PCT/IB99/00172

An embodiment of the electronic circuit according to the invention is defined in Claim 2. A Read-Only Memory (ROM) is a suitable device for holding the data required by the interconnect test. When control data, in the form of an address and, if necessary, a limited number of further control signals, is applied to the circuit, the ROM outputs data pre-stored at that address on the data bus. It will be clear that in this way both the data bus, the address bus and, if present, the control bus are tested. A small number of test patterns pre-stored in the ROM would normally suffice for an interconnect test capable of detecting open circuits in interconnects and short circuits between interconnects. It will further be clear that for the test unit being operable as a low complexity memory, it is not required that the test unit is

implemented as a real ROM table. Especially if only a small number of test patterns is used, the test unit could be implemented as a combinatorial circuit, leading to more efficient area usage.

An embodiment of the electronic circuit according to the invention is defined in Claim 3. In relation with such a read/write register, the control bus at least controls whether the register is in a read mode or in a write mode, and the data bus is used for both supplying the data to be written to the test unit and for receiving the data to be read back from the test unit. In this embodiment, no address bus is needed since only a single register is used.

An embodiment of the electronic circuit according to the invention is defined in Claim 5. The test circuit of this embodiment requires comparatively little area of the substrate on which it is manufactured. Furthermore, it enables to test the interconnects in a single type of test and with a very good test coverage, i.e. a small set of patterns suffices to detect the possible defects in the interconnects. Furthermore, the diagnostic resolution of the test is very good since almost all faults have a unique signature.

High complexity memory devices are those devices which have complex

protocols for reading from and writing into their memory array. Therefore, as opposed to low complexity memories, high complexity memories are not suited as test units for interconnect testing, as the process of exchanging data is too complex and therefore takes too much time. Examples of high complexity memory devices are Synchronous Dynamic Random Access memories (SDRAMs) and non-volatile memory like flash memory devices. Besides complex

30 access protocols, high complexity memories often need initialisation and have dynamic restrictions. The initialisation is troublesome for testing because (almost) all control lines and address lines have to be connected correctly to succeed in initialisation. Although interconnect problems with control and address lines can be detected because the failing initialisation will

> IPR2021-01488 Apple EX1005 Page 6

15

10

5

10

25

5

block all access to the devices, the diagnosis of the failure, i.e. exactly which of the pins is not connected correctly has a very low resolution.

The dynamic restrictions of SDRAMs, usually identified by the refresh time and the maximum RAS pulse width, hamper interconnect test because the test patterns (i.e. writing into and reading from the memory array) have to meet the dynamic requirements. The speed of application of test patterns using a boundary-scan circuit is determined by the length of the boundary-scan register and the maximum test clock frequency. The test clock frequency is determined either by the circuit implementation of the boundary-scan circuit in the ICs on the board or by the maximum speed of the boundary-scan tester,

For these reasons, high complexity memories form a class of circuits that could very well benefit from adding a low complexity memory for enabling efficient interconnect testing. This is especially true because boundary-scan is hardly available in memory devices due to pin count and/or pin compatibility considerations.

An embodiment of the circuit according to the invention is described in Claim 6. This particular way of activating the test mode is possible because in most SDRAMs the first action to be performed after power up is prescribed to be a write action. Thus at power up, by utilising the read action for activating the test mode, the normal operation of the SDRAM is not effected. As an alternative, the circuit in accordance with the invention can be brought into test mode via a particular combination of input signals on the I/O nodes, or via a dedicated node that is dedicated to this function.

Non-volatile memories like flash memory devices hamper interconnect test, because writing into the memory array for test purposes is not allowed when the device is already pre-programmed. This test would destroy the functional data. An un-programmed device can be written into but has to be erased afterwards. Erasure of large memory blocks can take up to several seconds, lengthening considerably the board interconnect test.

By including a test unit in accordance with the invention, high complexity memories, including non-volatile memories, can undergo an efficient interconnect test. One could use the normal mode data bus, address bus and/or control bus for the test mode as well. To also test interconnects that provide signals that are specific for the high complexity

30 memory functionality, and therefore are not needed to control the test unit in the test mode, either the data bus or the address bus can be extended with these interconnects. The invention enables interconnect testing using test patterns which take only milliseconds to execute and for which test pattern generators are commercially available.

## PCT/IB99/00172

Low complexity memory types like Static Random Access Memories (SRAMs) and (Programmable) ROMs can readily be tested for their connectivity using neighbouring circuits equipped with boundary-scan or neighbouring microprocessors and/or ASICs. For interconnect testing of such low complexity memories no extra measures in the form of added test units have to be taken.

It is a further object of the invention to provide a method as specified in the preamble, which performs the interconnect test with reduced overhead in terms of required I/O nodes and/or area. This object is achieved according to the invention in a method, which is characterised in that the putting step comprises operating the first electronic circuit as a low complexity memory by the second electronic circuit.

Although the invention is presented in the context of boundary-scan testing, which mainly applies to testing interconnects between ICs on a carrier, such as a printed circuit board (PCB), the principles of the invention are equally applicable to the testing of interconnects between any two circuits, such as interconnects between cores within a single IC

15 or interconnects between ICs on distinct PCBs that are inserted into a cabinet.

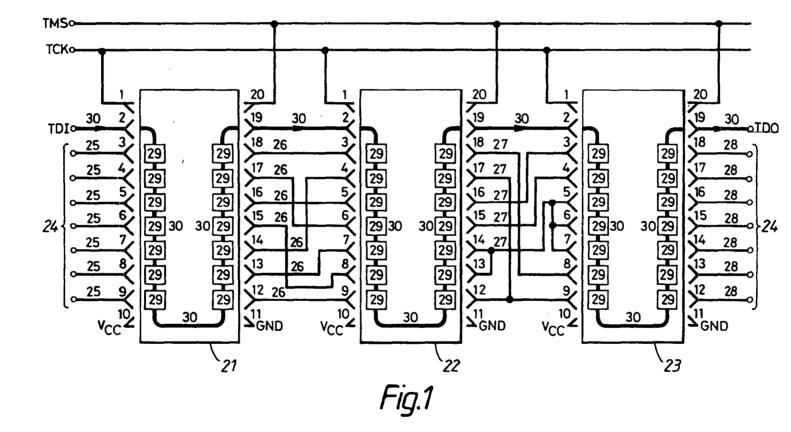

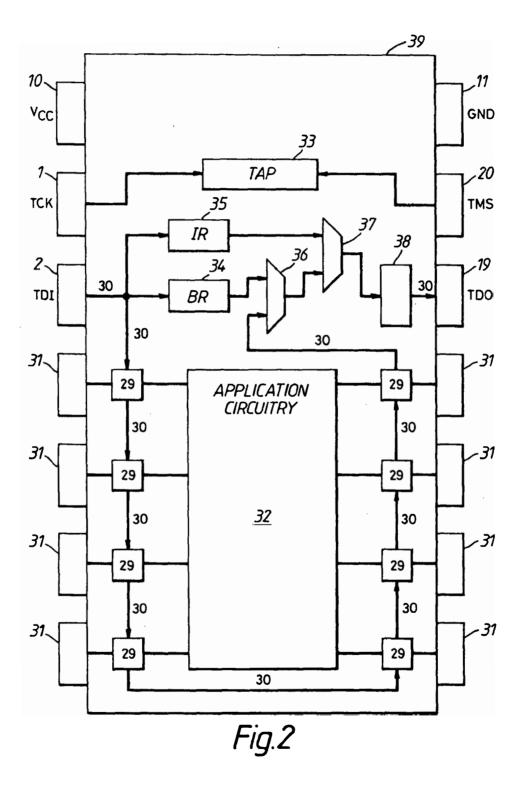

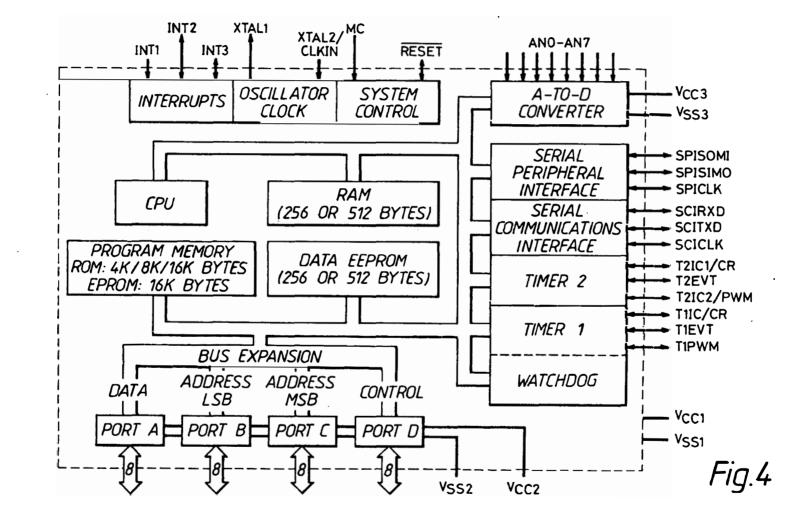

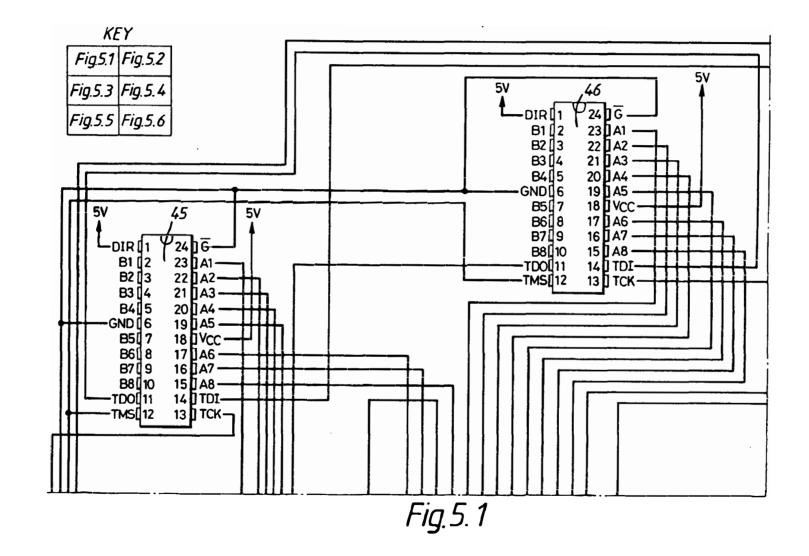

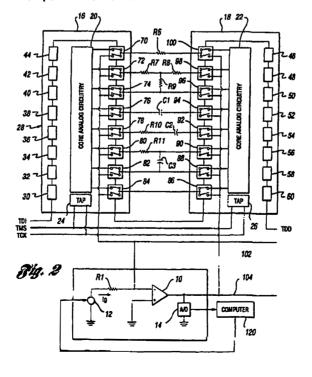

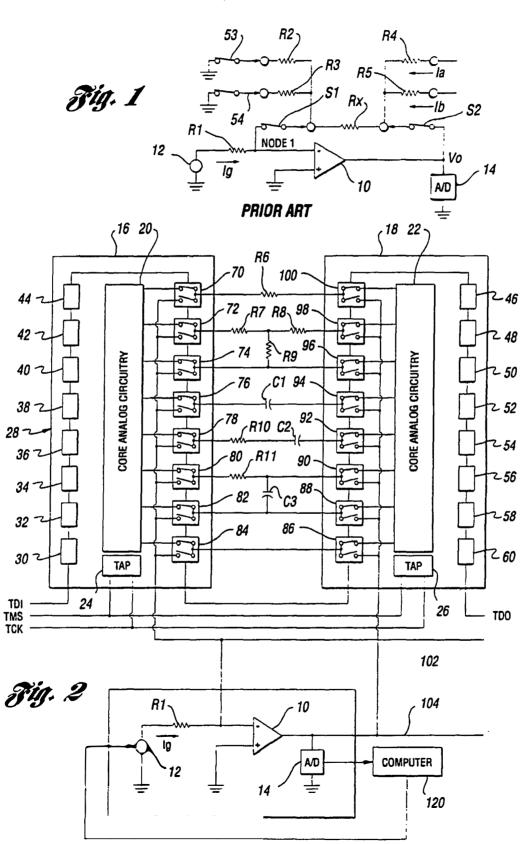

The invention and its attendant advantages will be further elucidated with the aid of exemplary embodiments and the accompanying schematic drawings, whereby:

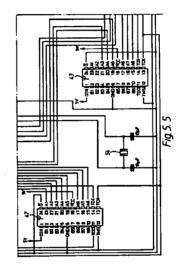

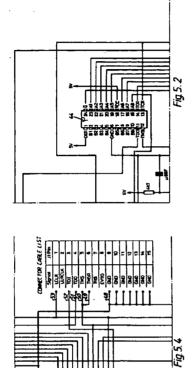

20 Figure 1 shows an embodiment of a circuit in accordance with the invention, Figure 2 shows a way to provide access during interconnect test to a circuit that is testable in accordance with the invention,

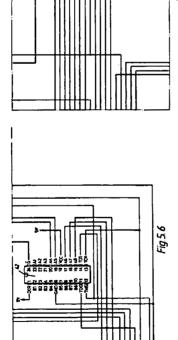

Figure 3 shows a further way to provide access during interconnect test to a circuit that is testable in accordance with the invention,

25

5

10

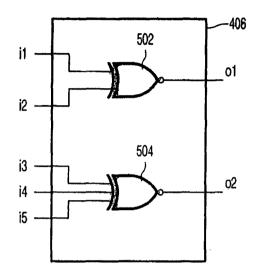

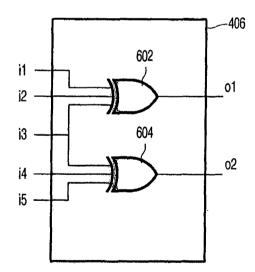

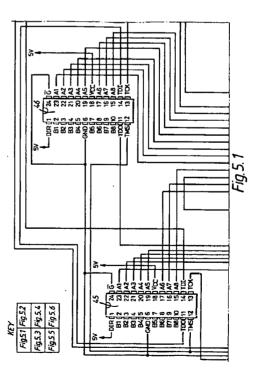

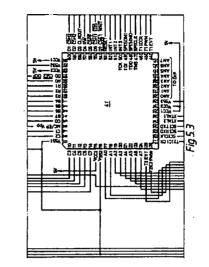

Figure 4 shows an alternative embodiment of the invention, Figure 5 schematically shows the test unit for five inputs and two outputs, and

Figure 6 schematically shows an alternative for the test unit for five inputs and two outputs.

Corresponding features in the various Figures are denoted by the same

30 reference symbols.

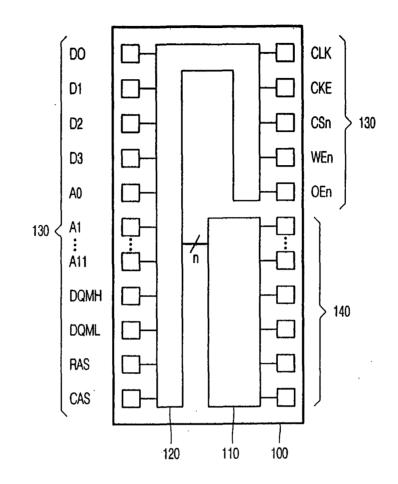

Figure 1 shows an embodiment of a circuit 100 in accordance with the invention. The circuit 100 has I/O nodes 130, 140, through which the circuit 100 is connectable to external circuits. An I/O node may be an input node, i.e. a node only suitable to

IPR2021-01488 Apple EX1005 Page 8

5

10

PCT/1B99/00172

receive signals, an output node, i.e. a node only suitable to send signals, or a bi-directional node, i.e. a node suitable to either receive or send signals. For performing its intended normal mode function, the circuit 100 has a main unit 110, which is, by way of example, assumed to be an SDRAM. Thus, the circuit 100 is in fact an SDRAM device. It is further assumed that the circuit 100 is part of an assembly, whereas interconnects between the circuit 100 and further parts of the assembly should be testable. Hereto, the circuit 100 has a test unit 120, which is connected to the main unit 110 via *n* parallel connections and to the I/O nodes 130. In a normal mode of the circuit 100, the test unit 120 is transparent, and signals can pass freely between the I/O nodes 130 and the main unit 110. In a test mode of the circuit 100, the main unit 110 is logically disconnected from the I/O nodes 130 and the test unit 120 is in control. It is noted that preferably, but not necessarily, all I/O nodes are arranged for interconnect testing. To indicate this, the I/O nodes 140 are not connected to the test unit 120, nodes 140.

SDRAM devices have a highly standardised pin lay-out. Figure 1 does not give an exact representation of such a pin-layout, but it schematically shows which I/O nodes are generally present on an SDRAM device. The circuit 100 has a data bus D0-D3, an address bus A0-A11, and a control bus including a Chip Select pin (CSn), an Output Enable pin (OEn), Write Enable pin (WEn), Clock pin (CLK), Clock Enable pin (CKE), Row Address Strobe pin (RAS), Column Address Strobe pin (CAS), and Data I/O Mask pins (DQML and DQMH).

20 The precise functions of these pins are not relevant for the invention. However, the standardised pin lay-out obstructs the addition of boundary-scan circuitry because of the required extra pins. Another reason for not using boundary-scan for interconnect testing of devices like circuit 100 is the enormous pressure on cost. As a result, the IC area available for extra features like interconnect testing is very limited. In accordance with the invention, as an

25 alternative to an ordinary boundary-scan test unit, the test unit 120 is operable as a low complexity memory. Such a test unit can be implemented very efficiently in terms of IC area and requires less or even zero extra pins.

A low complexity memory can have a read-only behaviour or a read/write behaviour. In accordance with the invention, a test unit has either kind of behaviour, or both

30 kinds of behaviour in subsequent phases of an interconnect test. In the circuit 100, during a first part of a preferred interconnect test, the test unit 120 has a read-only behaviour and during a subsequent second part of the interconnect test, the test unit 120 has a read/write behaviour. This two-step approach enables a thorough interconnect test that is especially suited for

SDRAMs like the circuit 100. The first part of the interconnect test aims at testing the address bus of the circuit 100 and is functionally described by:

8

After power up of the circuit 100, a test mode is active which allows read

access to the test unit 120. The test unit 120 is then operable as a ROM table. Alternatively, the test mode is activated by other means, such as a particular combination or sequence of signals applied to the I/O nodes 130, 140 of the circuit 100.

2. Read access to the test unit 120 is controlled by CSn=0, OEn=0 and WEn=1, and validated by a defined edge of the CLK and active level of the clock enable CKE.

10 3. The test unit's ROM table is addressed by the 'extended' address bus which is defined as the actual address bus, extended with the control signals RAS, CAS, DQML and DQMU.

4. The width of the ROM table is equal to the width of the data bus plus possible additional outputs of the circuit 100.

15 5. Each of the primary addresses (all but one address bits equal to '0', one address bit equal to '1') reads the all '1' data word. All other extended addresses read the all '0' data word.

The table below shows the contents of the ROM table for the SDRAM device

20 of circuit 100, with 12 bit wide address bus, RAS, CAS, DQML and DQMU and four data pins.

| extended address                        | data buş |

|-----------------------------------------|----------|

| bus                                     |          |

| AAAAAAAAAAAAARCDD                       | DDDD     |

| 119876543210AAQQ                        | 3210     |

| 10 SSMM                                 |          |

| LH                                      |          |

| 0000000000000000                        | 1111     |

| 000000000000000000000000000000000000000 | 1111     |

| 000000000000000000000000000000000000000 | 1111     |

| 000000000001000                         | 1111     |

| 000000000010000                         | 1111     |

| 000000000100000                         | 1111     |

| 000000001000000                         | 1111     |

| 00000001000000                          | 1111     |

| 000000100000000                         | 1111     |

| 00000100000000                          | 1111     |

| 0000010000000000                        | 1111     |

| 0000100000000000                        | 1111     |

| 0001000000000000                        | 1111     |

| 0010000000000000                        | 1111     |

| 0100000000000000                        | 1111     |

| 10000000000000000                       | 1111     |

PCT/IB99/00172

.

· · ·

.

With the above described functional behaviour of the circuit 100 after power

up, an efficient test for the extended address bits consist of just reading all primary addresses

- 5 (16 in the above case) and one other address. The test sequence covers the following faults:

- 1. any stuck-at 1 on an extended address pin

- 2. any stuck-at 0 on an extended address pin

- 3. any 2-net AND-type short between any pair of address pins

0000

- 4. any 2-net OR-type short between any pair of address pins

- 10 5. any stuck-at 1 on a data pin

'any other address'

5

6. any stuck-at 0 on a data pin

An interconnect with a stuck-at fault remains at either logic high or logic low, no matter what signals are applied to it. A 2-net AND-type short between a first and a second interconnect causes the two interconnects to carry the same logic value as determined by either one of the interconnects. A 2-net OR-type short between a first and a second interconnect causes the two interconnects to carry complementary logic values as determined by either one of the interconnects.

The above test sequence provides a diagnostic resolution down to a single pin. Note that this test concept is independent from the number of extended address lines or the number of data lines, nor is there any relation assumed between the two numbers.

The second part of the interconnect test aims at testing for shorts between the interconnects making up the data bus, and is functionally described by:

1. Write access is provided to a command register, which is loaded with the value of the

15 (actual) address bus.

2. There will be a certain combination of address bits, which, after being loaded into the aforementioned command register, select a single write/read register that logically forms part of the test unit, with a width equal to the width of the data bus. This combination of address bits is to be determined by the manufacturer of the device and to be specified in the data sheet.

This single write/read register can then be used to write data and read data. Algorithms are available to generate a minimal set of test patterns which cover all AND-type and OR-type shorts between any pair of data lines. The table below shows a set of test patterns for a 16-bit wide data bus.

| סמסססססססססססס   |

|------------------|

| 1111119876543210 |

| 543210           |

| 1111100000000000 |

| 0000011111100000 |

| 1110011100011000 |

| 1001011010010110 |

| 1100110011001100 |

| 0101010101010101 |

25

20

5

11

### PCT/IB99/00172

For dynamic memory devices, like the circuit 100, the above described two parts of the interconnect test have read and write access to the test unit which is not affected with any dynamic requirements. It will be clear that many variants can be imagined to either part. Moreover, one can also choose to implement only one of the above described two parts of the interconnect test. For flash devices, for example, the first part of the interconnect test is applicable for unprogrammed devices. The manufacturer may choose not to offer this facility for already programmed devices, to accomplish compatibility with EPROM devices (these access the main memory array when a first read is done after power up).

As mentioned above, the mechanism for switching the circuit from the normal 10 mode into the test mode may be implemented in different ways. In the SDRAM embodiment, the circuit is brought into the test mode by performing a read action after power up. Such a read action after power up, is a special action which does not form part of the normal actions for the circuit and has been given the special meaning of a command for switching into the test mode. In general, any pattern or sequence of patterns applied to one or more I/O nodes of the

15 circuit can be given the special meaning of a command for going into test mode, provided that this pattern or sequence is not used in the normal mode of the circuit. An alternative is to provide the circuit with a dedicated test control node, in addition to the I/O nodes, to control whether the circuit is to behave in the normal operational mode or in the test mode. The actual signal value on the test control node, in relation with predefined values corresponding to the 20 respective modes, brings the circuit into the desired mode.

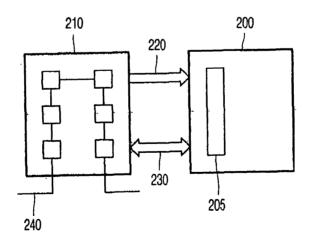

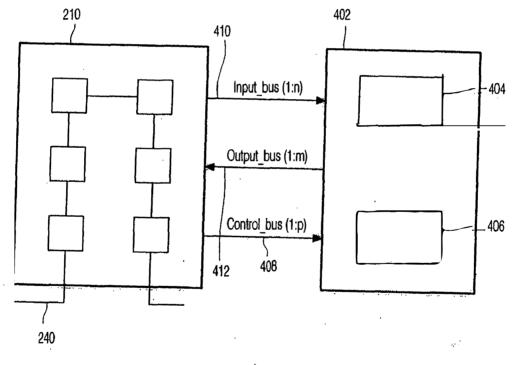

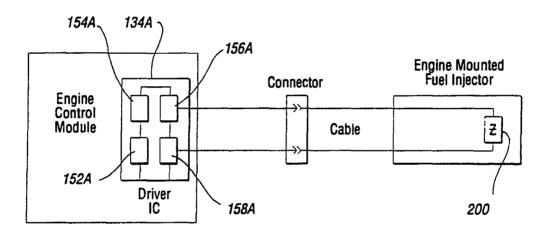

Figure 2 shows a way to provide access during interconnect test to a circuit 200 that is testable in accordance with the invention. The circuit 200 includes a test unit 205 that is operable as a low complexity memory. A neighbouring circuit 210, which has boundary-scan circuitry, can provide data to and receive data from the circuit 200 via a control and address

25 bus 220 and a bi-directional data bus 230. Alternatively, when only a ROM behaviour is implemented in the test unit 205, the data bus 230 would be uni-directional, i.e. from the circuit 200 to the circuit 210.

A number of interconnects make up the control and address bus 220 and the data bus 230. The function of these interconnects during a normal mode is irrelevant for the invention. When the circuit 200 is a memory device, there will also be a 'normal mode data bus'. The 'test mode data bus' 230 could partly or completely coincide with the normal mode data bus. The same applies to the control and address bus 220.

Via a boundary-scan chain 240 data is shifted into circuit 210, that data making up read and/or write commands to be supplied to the circuit 200. After a read command, the

5

10

PCT/IB99/00172

boundary-scan chain 240 captures data supplied to the data bus 230 by the circuit 200. That data subsequently are shifted out to be analysed externally.

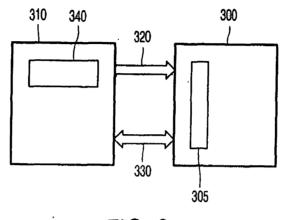

Figure 3 shows a further way to provide access during interconnect test to a circuit 300 that is testable in accordance with the invention. The circuit 300 includes a test unit 305 that is operable as a low complexity memory via control and address bus 320 and data bus 330. A neighbouring circuit 310, which is a microprocessor, executes the program with the necessary read and write commands. The test program and the test data are stored in a memory 340 of the circuit 310. Preferably, the circuit 310 also analyses the data obtained from the circuit 300. The circuit 310 could alternatively be an ASIC.

The above presented design-for-test method does not require any additional pins to the device for test access, meeting pin count and pin compatibility requirements of this type of memories. Silicon area overhead is limited to the (small) ROM table, or functional equivalent, the read/write data register (possibly to be combined with existing logic) and the associated decoding logic. Standardisation of this approach by a body like EIS or JEDEC