# HIGH SPEED SYNCHRONOUS POWER MOSFET SMART DRIVER

August 31, 2000

TEL:805-498-2111 FAX:805-498-3804 WEB:http://www.semtech.com

#### DESCRIPTION

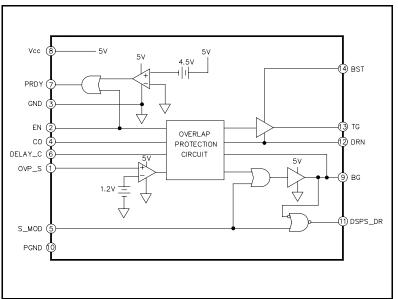

The SC1405 is a Dual-MOSFET Driver with an internal Overlap Protection Circuit to prevent shoot-through from V<sub>IN</sub> to GND in the main switching and synchronous MOSFET's. Each driver is capable of driving a 3000pF load in 20ns rise/fall time and has ULTRA-FAST propagation delay from input transition to the gate of the power FET's. The Overlap Protection circuit ensures that the second FET does not turn on until the top FET source has reached a voltage low enough to prevent shoot-through. The delay between the bottom gate going low to the top gate transitioning to high is externally programmable via a capacitor for optimal reduction of switching losses at the operating frequency. The bottom FET may be disabled at light loads by keeping S\_MOD low to trigger asynchronous operation, thus saving the bottom FET's gate drive current and inductor ripple current. An internal voltage reference allows threshold adjustment for an Output Over-Voltage protection circuitry, independent of the PWM feedback loop. Under-Voltage-Lock-Out circuit is included to guarantee that both driver outputs are low when the 5V logic level is less than or equal to 4.4V (typ) at supply ramp up (4.35V at supply ramp down). A CMOS output provides status indication of the 5V supply. A low enable input places the IC in stand-by mode thereby reducing supply current to less than 10µA. SC1405 is offered in a high pitch (.025" lead spacing) TSSOP package.

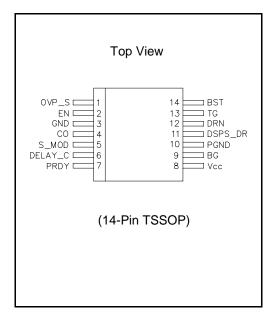

## PIN CONFIGURATION

#### **FEATURES**

- Fast rise and fall times (20ns typical with 3000pf load)

- 20ns max. Propagation delay (BG going low)

- Adaptive/programmable shoot-through protection

- Wide input voltage range (4.5-25V)

- Programmable delay between MOSFET's

- Power saving asynchronous mode control

- Output overvoltage protection/overtemp shutdown

- Under-Voltage lock-out and power ready signal

- Less than 10µA stand-by current (EN=low)

- Power ready output signal

#### **APPLICATIONS**

- High Density/Fast transient power supplies

- Motor Drives/Class-D amps

- High frequency (to 1.2 MHz) operation allows use of small inductors and low cost caps in place of electrolytics

- Portable computers

#### ORDERING INFORMATION

| DEVICE <sup>(1)</sup> | PACKAGE  | TEMP. RANGE (T <sub>J</sub> ) |

|-----------------------|----------|-------------------------------|

| SC1405TS.TR           | TSSOP-14 | 0 - 125°C                     |

#### Note:

(1) Only available in tape and reel packaging. A reel contains 2500 devices.

### **BLOCK DIAGRAM**

# HIGH SPEED SYNCHRONOUS POWER MOSFET SMART DRIVER

August 31, 2000

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter                              | Symbol                     | Conditions                                                | Maximum      | Units |

|----------------------------------------|----------------------------|-----------------------------------------------------------|--------------|-------|

| V <sub>cc</sub> Supply Voltage         | $V_{\text{MAX5V}}$         |                                                           | 7            | V     |

| BST to PGND                            | VMAX <sub>BST-PGND</sub>   |                                                           | 30           | V     |

| BST to DRN                             | VMAX <sub>BST-DRN</sub>    |                                                           | 7            | V     |

| DRN to PGND                            | VMAX <sub>DRN-PGN</sub>    |                                                           | 25           | V     |

| OVP_S to PGND                          | VMAX <sub>OVP_S-PGND</sub> |                                                           | 10           | V     |

| Input pin                              | CO                         |                                                           | -0.3 to 7.3  | V     |

| Continuous Power Dissipation           | Pd                         | Tamb = 25°C, $T_J$ = 125°C<br>Tcase = 25°C, $T_J$ = 125°C | 0.66<br>2.56 | W     |

| Thermal Resistance Junction to Case    | $\theta_{JC}$              |                                                           | 40           | °C/W  |

| Thermal Resistance Junction to Ambient | $	heta_{\sf JA}$           |                                                           | 150          | °C/W  |

| Operating Temperature Range            | $T_J$                      |                                                           | 0 to +125    | °C    |

| Storage Temperature Range              | $T_{\mathtt{STG}}$         |                                                           | -65 to +150  | °C    |

| Lead Temperature (Soldering) 10 sec    | $T_{LEAD}$                 |                                                           | 300          | °C    |

### NOTE:

(1) Specification refers to application circuit in Figure 1.

# **ELECTRICAL CHARACTERISTICS (DC OPERATING SPECIFICATIONS)**

Unless specified: -0 <  $\theta_J$  < 125°C;  $V_{CC}$  = 5V;  $4V \le V_{BST} \le 26V$

| PARAMETER                    | SYMBOL               | CONDITIONS                                     | MIN  | TYP  | MAX  | UNITS |  |  |

|------------------------------|----------------------|------------------------------------------------|------|------|------|-------|--|--|

| POWER SUPPLY                 | POWER SUPPLY         |                                                |      |      |      |       |  |  |

| Supply Voltage               | V <sub>cc</sub>      | V <sub>cc</sub>                                | 4.15 | 5    | 6.0  | V     |  |  |

| Quiescent Current            | Iq_stby              | EN = 0V                                        |      |      | 10   | μA    |  |  |

| Quiescent Current, operating | lq_op                | V <sub>CC</sub> = 5V,CO=0V                     |      | 1    |      | ma    |  |  |

| PRDY                         |                      |                                                |      |      | 1    |       |  |  |

| High Level Output Voltage    | V <sub>OH</sub>      | V <sub>CC</sub> = 4.6V, Iload = 10mA           | 4.5  | 4.55 |      | V     |  |  |

| Low Level Output Voltage     | V <sub>OL</sub>      | V <sub>CC</sub> < UVLO threshold, lload = 10μA |      | 0.1  | 0.2  | V     |  |  |

| DSPS_DR                      |                      |                                                |      |      | 1    |       |  |  |

| High Level Output Voltage    | V <sub>OH</sub>      | V <sub>CC</sub> = 4.6V, Cload = 100pF          | 4.15 |      |      | V     |  |  |

| Low Level Output Voltage     | V <sub>OL</sub>      | V <sub>CC</sub> = 4.6V, Cload = 100pF          |      |      | 0.05 | V     |  |  |

| UNDER-VOLTAGE LOCKOUT        |                      |                                                |      |      |      |       |  |  |

| Start Threshold              | $V_{START}$          |                                                | 4.2  | 4.4  | 4.6  | V     |  |  |

| Hysteresis                   | Vhys <sub>UVLO</sub> |                                                |      | 0.05 |      | V     |  |  |

| Logic Active Threshold       | V <sub>ACT</sub>     | EN is low                                      |      |      | 1.5  | V     |  |  |

August 31, 2000

# **ELECTRICAL CHARACTERISTICS (DC OPERATING SPECIFICATIONS) Cont.**

| PARAMETER                   | SYMBOL              | CONDITIONS                                                                                                                      | MIN   | TYP | MAX   | UNITS |

|-----------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-------|

| OVERVOLTAGE PROTECTION      | N                   |                                                                                                                                 |       |     |       |       |

| Trip Threshold              | $V_{TRIP}$          |                                                                                                                                 | 1.145 | 1.2 | 1.255 | V     |

| Hysteresis                  | Vhys <sub>OVP</sub> |                                                                                                                                 |       | 0.8 |       | V     |

| S_MOD                       | 1                   |                                                                                                                                 |       |     |       |       |

| High Level Input Voltage    | V <sub>IH</sub>     |                                                                                                                                 | 2.0   |     |       | V     |

| Low Level Input Voltage     | V <sub>IL</sub>     |                                                                                                                                 |       |     | 0.8   | V     |

| ENABLE                      |                     |                                                                                                                                 |       |     |       |       |

| High Level Input Voltage    | V <sub>IH</sub>     |                                                                                                                                 | 2.0   |     |       | V     |

| Low Level Input Voltage     | V <sub>IL</sub>     |                                                                                                                                 |       |     | 0.8   | V     |

| со                          | <u> </u>            |                                                                                                                                 |       |     |       |       |

| High Level Input Voltage    | V <sub>IH</sub>     |                                                                                                                                 | 2.0   |     |       | V     |

| Low Level Input Voltage     | V <sub>IL</sub>     |                                                                                                                                 |       |     | 0.8   | V     |

| THERMAL SHUTDOWN            |                     |                                                                                                                                 |       |     |       |       |

| Over Temperature Trip Point | T <sub>OTP</sub>    |                                                                                                                                 |       | 165 |       | °C    |

| Hysteresis                  | T <sub>HYST</sub>   |                                                                                                                                 |       | 10  |       | °C    |

| HIGH-SIDE DRIVER            |                     |                                                                                                                                 |       |     |       |       |

| Peak Output Current         | I <sub>PKH</sub>    |                                                                                                                                 |       | 1.5 |       | Α     |

| Output Resistance           | Rsrc <sub>TG</sub>  | duty cycle < 2%, tpw < 100 $\mu$ s,<br>$T_J = 125^{\circ}$ C, $V_{BST} - V_{DRN} = 4.5$ V,<br>$V_{TG} = 4.0$ V (src)+ $V_{DRN}$ |       | 1.4 |       | Ω     |

|                             | Rsink <sub>TG</sub> | or $V_{TG} = 0.5V (sink) + V_{DRN}$                                                                                             |       | 1.4 |       | Ω     |

| LOW-SIDE DRIVER             | 1                   |                                                                                                                                 |       |     |       |       |

| Peak Output Current         | I <sub>PKL</sub>    |                                                                                                                                 |       | 2   |       | Α     |

| Output Resistance           | Rsrc <sub>BG</sub>  | duty cycle < 2%, tpw < 100μs,<br>Τ <sub>⊥</sub> = 125°C                                                                         |       | 2   |       | Ω     |

|                             | Rsink <sub>BG</sub> | $V_{V_{-5}} = 4.6V$ , $V_{BG} = 4V$ (src),<br>or $V_{LOWDR} = 0.5V$ (sink)                                                      |       | 2   |       | Ω     |

# HIGH SPEED SYNCHRONOUS POWER MOSFET SMART DRIVER

August 31, 2000

# **ELECTRICAL CHARACTERISTICS (DC OPERATING SPECIFICATIONS) Cont.**

| PARAMETER                                | SYMBOL                                           | CONDITIONS                                                                              | MIN | TYP | MAX | UNITS |

|------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------|-----|-----|-----|-------|

| AC OPERATING SPECIFIC                    | CATIONS                                          |                                                                                         |     |     | I   | 1     |

| HIGH-SIDE DRIVER                         |                                                  |                                                                                         |     |     |     |       |

| rise time                                | tr <sub>TG</sub> ,                               | $CI = 3nF, V_{BST} - V_{DRN} = 4.6V,$                                                   |     | 16  | 25  | ns    |

| fall time                                | tf <sub>TG</sub>                                 | $CI = 3nF, V_{BST} - V_{DRN} = 4.6V,$                                                   |     | 17  | 27  | ns    |

| propagation delay time,<br>TG going high | tpdh <sub>TG</sub>                               | $CI = 3nF$ , $V_{BST} - V_{DRN} = 4.6V$ , $C$ -delay=0                                  |     | 35  | 56  | ns    |

| propagation delay time,<br>TG going low  | tpdl <sub>TG</sub>                               | $CI = 3nF, V_{BST} - V_{DRN} = 4.6V,$                                                   |     | 25  | 40  | ns    |

| LOW-SIDE DRIVER                          |                                                  |                                                                                         |     |     |     |       |

| rise time                                | tr <sub>BG</sub>                                 | $CI = 3nF, V_{V_{-5}} = 4.6V,$                                                          |     | 20  | 32  | ns    |

| fall time                                | tr <sub>BG</sub>                                 | $CI = 3nF, V_{V_{-5}} = 4.6V,$                                                          |     | 18  | 29  | ns    |

| propagation delay time<br>BG going high  | tpdh <sub>BGHI</sub>                             | $CI = 3nF, V_{V_{-}5} = 4.6V,$<br>$DRN \le 1V$                                          |     | 45  | 72  | ns    |

| progagation delay time<br>BG going low   | tpdl <sub>BG</sub>                               | $CI = 3nF, V_{V_{-}5} = 4.6V,$                                                          |     | 12  | 20  | ns    |

| UNDER-VOLTAGE LOCKOUT                    | - 1                                              |                                                                                         |     |     | 1   |       |

| V_5 ramping up                           | tpdh <sub>UVLO</sub>                             | EN is High                                                                              |     |     | 10  | us    |

| V_5 ramping down                         | tpdl <sub>UVLO</sub>                             | EN is High                                                                              |     |     | 10  | us    |

| PRDY                                     |                                                  |                                                                                         |     |     |     |       |

| EN is transitioning from low to high     | tpdhPRDY                                         | V_5 $\geq$ UVLO threshold, Delay<br>measured from EN $\geq$ 2.0V to<br>PRDY $\geq$ 3.5V |     |     | 10  | μs    |

| EN is transitioning from high to low     | tpdh <sub>uvLO</sub>                             | V_5 ≥ UVLO threshold. Delay measured from EN ≤ 0.8V tp PRDY ≤ 10% of V_5                |     |     | 500 | μs    |

| DSPS_DR                                  |                                                  |                                                                                         |     | •   |     |       |

| rise/fall time                           | tr <sub>DSPS_DR</sub> ,<br>tf <sub>DSPS_DR</sub> | CI = 100pf, V_5 = 4.6V,                                                                 |     |     | 20  | ns    |

| propagation delay,<br>DSPS_DR going high | tpdh <sub>DSPS_DR</sub>                          | S_MOD goes high and BG goes high or S_MOD goes low                                      |     |     | 10  | ns    |

| propagation delay<br>DSPS_DR goes low    | tpdl <sub>DSPS_DR</sub>                          | S_MOD goes high and BG goes low                                                         |     |     | 10  | ns    |

| OVERVOLTAGE PROTECTION                   |                                                  |                                                                                         |     |     |     |       |

| propagation delay<br>OVP_S going high    | tpdh <sub>OVP_S</sub>                            | $V_5 = 4.6V$ , $T_J = 125$ °C, $OVP_S \ge 1.2V$ to BG > 90% of $V_5$                    |     |     | 1   | μs    |

(1) This device is ESD sensitive. Use of standard ESD handling precautions is required.

# HIGH SPEED SYNCHRONOUS POWER MOSFFT SMADT DRIVED MOSFET SMART DRIVER

August 31, 2000

## **PIN DESCRIPTION**

| Pin# | Pin Name        | Pin Function                                                                                                                                                                                                                                       |  |  |

|------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1    | OVP_S           | Overvoltage protection sense. External scaling resistors required to set protection threshold.                                                                                                                                                     |  |  |

| 2    | EN              | When high, this pin enables the internal circuitry of the device. When low, TG, BG and PRDY are forced low and the supply current (5V) is less than 10µA.                                                                                          |  |  |

| 3    | GND             | Logic GND.                                                                                                                                                                                                                                         |  |  |

| 4    | СО              | TTL-level input signal to the MOSFET drivers.                                                                                                                                                                                                      |  |  |

| 5    | S_MOD           | When low, this signal forces BG to be low. When high, BG is not a function of this signal.                                                                                                                                                         |  |  |

| 6    | DELAY_C         | Sets the additional propagation delay for BG going low to TG going high. Total propagation delay= 20ns + 1ns/pF.                                                                                                                                   |  |  |

| 7    | PRDY            | This pin indicates the status of 5V. When 5V is less than 4.4V(typ) this output is driven low. When 5V is greater than or equals to 4.4V(typ) this output is driven to 5V level. This output has a 10mA drive capability and 10µA sink capability. |  |  |

| 8    | V <sub>cc</sub> | +5V supply. A .22-1 $\mu$ F ceramic capacitor should be connected from 5V to PGND very close to this pin.                                                                                                                                          |  |  |

| 9    | BG              | Output drive for the synchronous MOSFET.                                                                                                                                                                                                           |  |  |

| 10   | PGND            | Power ground. Connect to the synchronous FET power ground.                                                                                                                                                                                         |  |  |

| 11   | DSPS_DR         | Dynamic Set Point Switch Drive. TTL level output signal. When S_MOD is high, this pin follows the BG driver pin voltage.                                                                                                                           |  |  |

| 12   | DRN             | This pin connects to the junction of the switching and synchronous MOSFET's. This pin can be subjected to a -2V minimum relative to PGND without affecting operation.                                                                              |  |  |

| 13   | TG              | Output gate drive for the switching (high-side) MOSFET.                                                                                                                                                                                            |  |  |

| 14   | BST             | Bootstrap pin. A capacitor is connected between BST and DRN pins to develop the floating bootstrap voltage for the high-side MOSFET. The capacitor value is typically between 0.1µF and 1µF (ceramic).                                             |  |  |

## NOTE:

(1) All logic level inputs and outputs are open collector TTL compatible.

# **PIN CONFIGURATION**

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

# API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

# **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.