MICROCHIP TECHNOLOGY INC., Petitioner,

v.

HD SILICON SOLUTIONS LLC

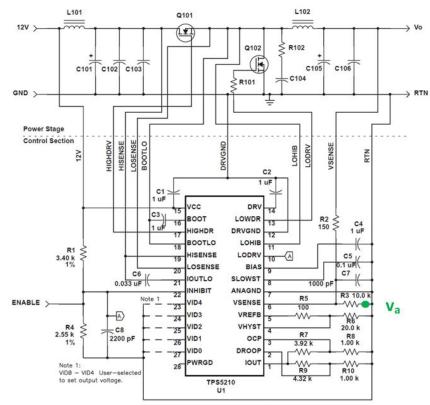

Patent Owner

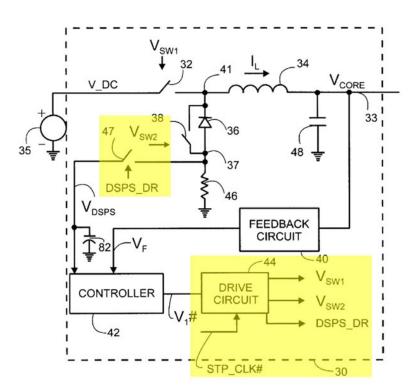

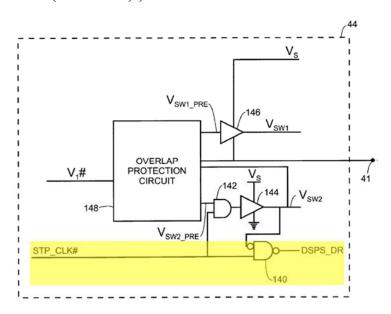

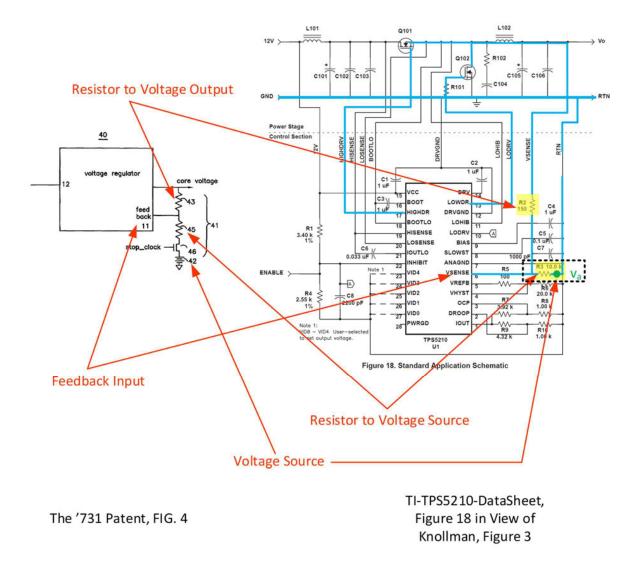

Case No. IPR2021-01420 Case No. IPR2021-01421 U.S. Patent No. 7,260,731 Issue Date: August 21, 2007

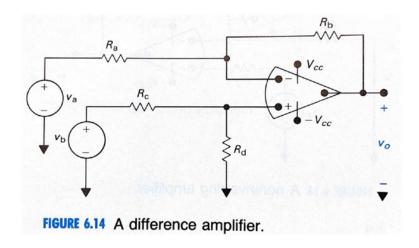

Title: SAVING POWER WHEN IN OR TRANSITIONING TO A STATIC MODE OF A PROCESSOR

# DECLARATION OF DONALD ALPERT, PH.D. IN SUPPORT OF PETITION FOR *INTER PARTES* REVIEW OF U.S. PATENT NO. 7,260,731

Mail Stop PATENT BOARD

Patent Trial and Appeal Board

United States Patent and Trademark Office

P.O. Box 1450

Alexandria, VA 22313-1450

# **TABLE OF CONTENTS**

| I.   | INT | RODU  | JCTION AND QUALIFICATIONS                      | 1  |

|------|-----|-------|------------------------------------------------|----|

|      | A.  | Intro | oduction                                       | 1  |

|      | B.  | Qua   | lifications and Experience                     | 2  |

|      | C.  | Mat   | erials Considered                              | 5  |

| II.  | LEG | AL P  | RINCIPLES                                      | 10 |

|      | A.  | Prio  | r Art                                          | 10 |

|      | В.  | Clai  | m Construction                                 | 11 |

|      | C.  | Anti  | icipation                                      | 14 |

|      | D.  | Obv   | riousness                                      | 15 |

| III. | LEV | EL O  | F ORDINARY SKILL IN THE ART                    | 21 |

| IV.  | TEC | HNO   | LOGY BACKGROUND                                | 22 |

|      | A.  | Pow   | ver and Energy Consumption of Computer Systems | 24 |

|      |     | 1.    | CMOS and Power                                 | 24 |

|      |     | 2.    | Slowing the Clock                              | 26 |

|      |     | 3.    | Stopping the Clock                             | 27 |

|      |     | 4.    | Dynamic Voltage-Frequency Scaling (DVFS)       | 28 |

|      | В.  | Reg   | isters and Static Random Access Memory (SRAM)  | 31 |

|      | C.  | Volt  | tage Regulation                                | 36 |

| V.   | THE | 731   | PATENT                                         | 49 |

|      | Δ   | Ove   | rview of the '731 natent                       | 49 |

|     | <b>B.</b> | Pros  | ecution History                                                                                                                 | 59  |

|-----|-----------|-------|---------------------------------------------------------------------------------------------------------------------------------|-----|

|     | C.        | Rebu  | uttal of Applicants' Remarks During Prosecution                                                                                 | 68  |

|     | D.        | The   | Challenged Claims                                                                                                               | 71  |

| VI. | APP       | LICAT | ΓΙΟΝ OF THE PRIOR ART TO ASSERTED CLAIMS                                                                                        | 80  |

|     | A.        | Brief | f Summary of Prior Art                                                                                                          | 81  |

|     |           | 1.    | NEC-Databook (Ex.1005)                                                                                                          | 83  |

|     |           | 2.    | Burd (Ex.1006)                                                                                                                  | 90  |

|     |           | 3.    | Nguyen (Ex.1007)                                                                                                                | 93  |

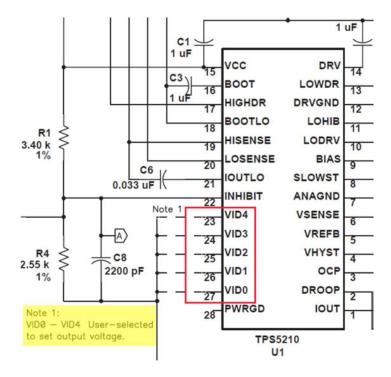

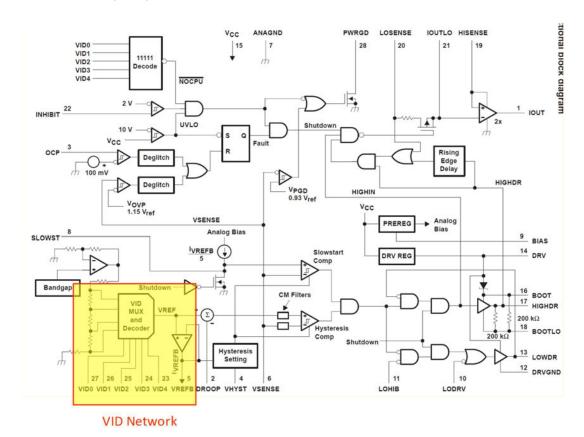

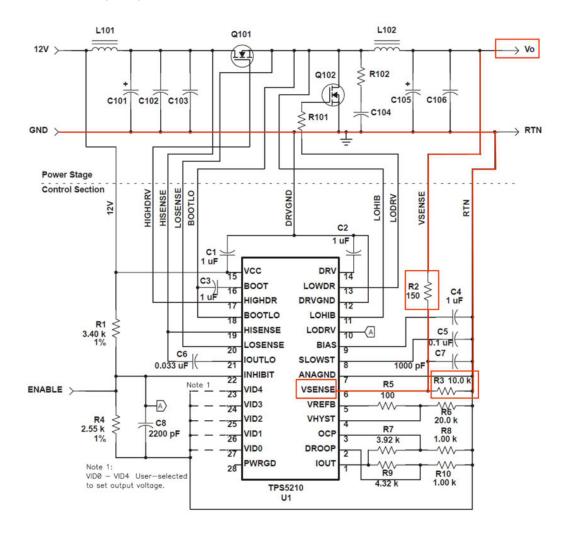

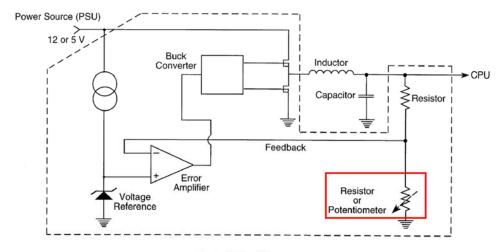

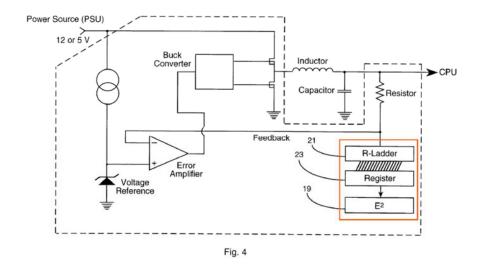

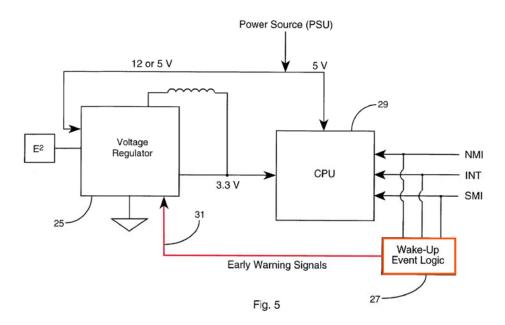

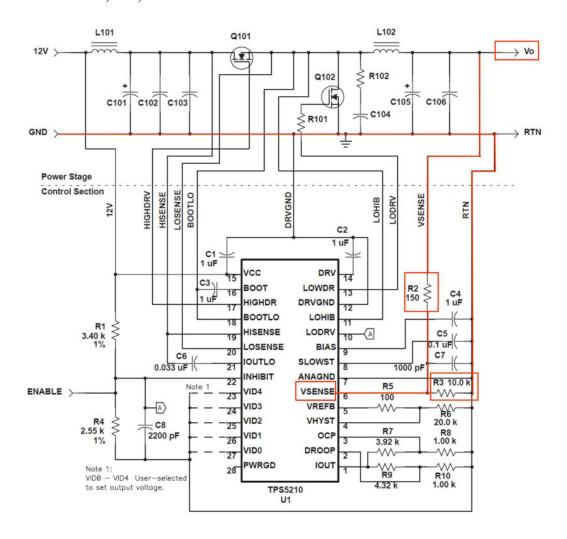

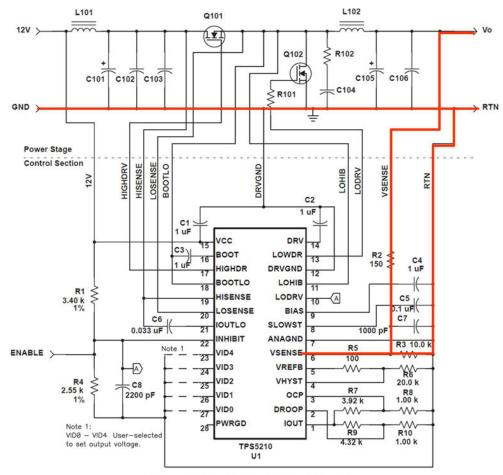

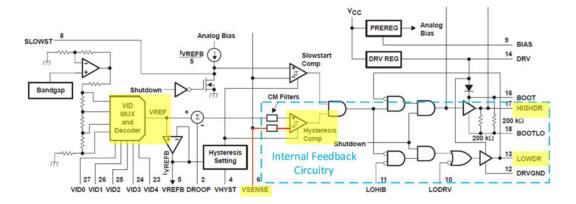

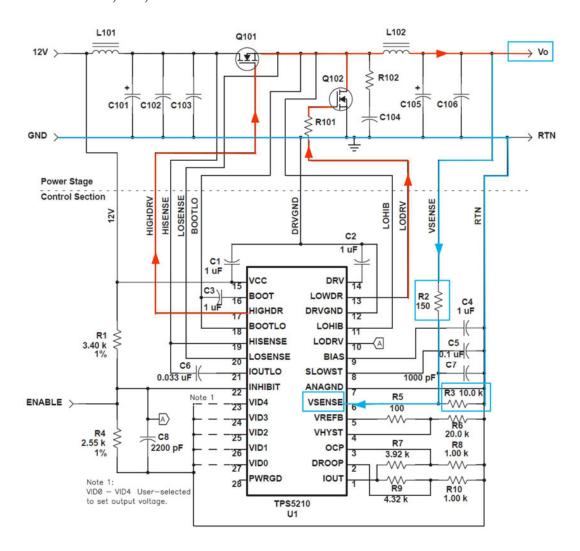

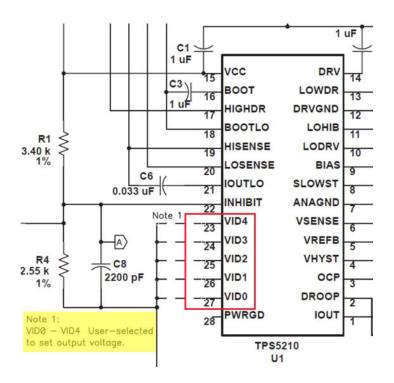

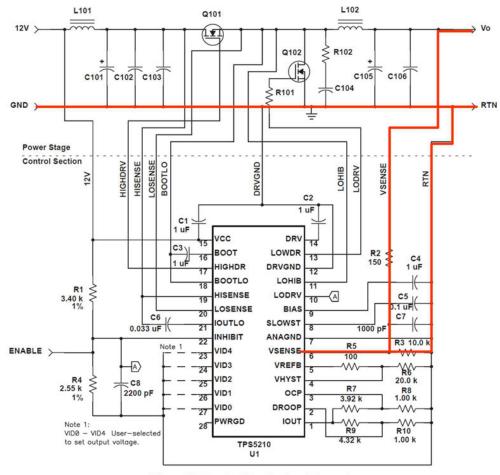

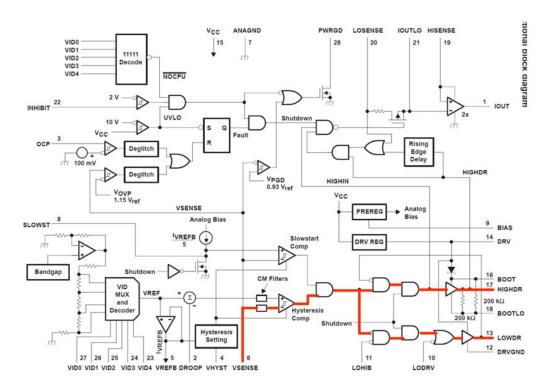

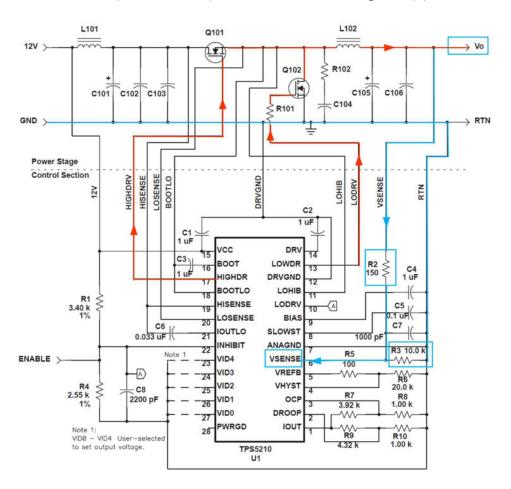

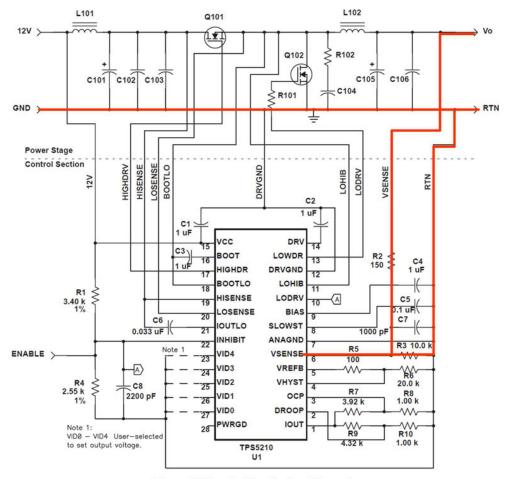

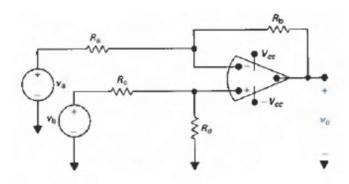

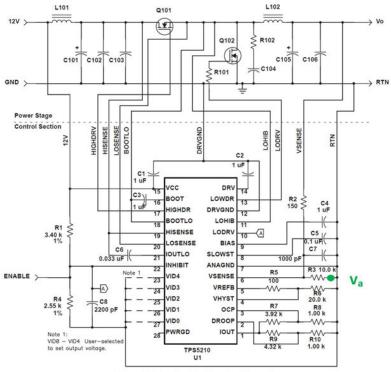

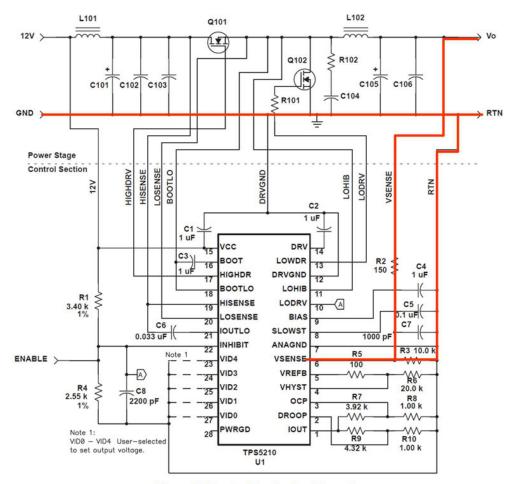

|     |           | 4.    | TI-TPS5210-Datasheet (Ex. TI-TPS5210-Datasheet)                                                                                 | 96  |

|     |           | 5.    | Kikinis (Ex.1009)                                                                                                               | 101 |

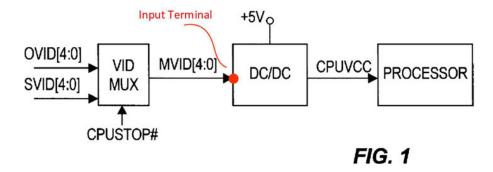

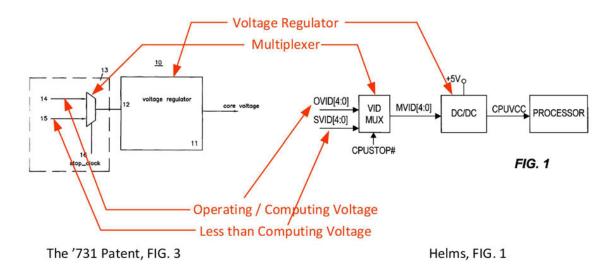

|     |           | 6.    | Helms (Ex.1010)                                                                                                                 | 104 |

|     |           | 7.    | Maxim-165X-Datasheet (Ex.1011)                                                                                                  | 107 |

|     |           | 8.    | MAX1711-Kit (Ex.1012)                                                                                                           | 110 |

|     |           | 9.    | Nilsson (Ex.1013)                                                                                                               | 112 |

|     | В.        | Over  | OUND 1: Claims 1, 3, 6, and 7 Are Unpatentable as Obviour NEC-Databook in View of Burd, further in View of the wledge of POSITA |     |

|     |           | 1.    | Motivation to Combine NEC-Databook and Burd                                                                                     | 113 |

|     |           | 2.    | Independent Claim 1                                                                                                             | 128 |

|     |           | 3.    | Claim 3                                                                                                                         | 160 |

|     |           | 4.    | Independent Claim 6                                                                                                             | 166 |

|     |           | 5.    | Claim 7                                                                                                                         | 172 |

|     | C.        |       | OUND 2: Claim 2 Is Unpatentable as Obvious Over NEC-book in View of Burd, Further in View of Nguyen                             | 175 |

|           | 1.    | Motivation to Combine NEC-Databook, Burd, and Nguyen.                                                                         | 175 |

|-----------|-------|-------------------------------------------------------------------------------------------------------------------------------|-----|

|           | 2.    | Claim 2                                                                                                                       | 178 |

| D.        | Datal | UND 3: Claim 4 Is Unpatentable as Obvious Over NECbook in View of TI-TPS5210-Datasheet, Further in View of his                | 184 |

|           | 1.    | Motivation to Combine NEC-Databook, TI-TPS5210-<br>Datasheet, and Kikinis                                                     | 184 |

|           | 2.    | Independent Claim 4                                                                                                           | 189 |

|           | 3.    | Claim 5                                                                                                                       | 207 |

| <b>E.</b> | Over  | UND 4: Claims 8-10 and 14 Are Unpatentable as Obvious<br>Helms in View of Maxim-165X-Datasheet, Further in View<br>AX1711-Kit | 211 |

|           | 1.    | Motivation to Combine Helms, Maxim-165X-Datasheet, and MAX1711-Kit                                                            | 211 |

|           | 2.    | Independent Claim 8                                                                                                           | 216 |

|           | 3.    | Claim 9                                                                                                                       | 256 |

|           | 4.    | Claim 10                                                                                                                      | 264 |

|           | 5.    | Claim 11                                                                                                                      | 278 |

|           | 6.    | Independent Claim 14                                                                                                          | 280 |

| F.        | Obvi  | OUND 5: Claim 12, 13, and 15-18 Are Unpatentable as ous Over Helms in View of TI-TPS5210-Datasheet, Further in of Nilsson     |     |

|           | 1.    | Motivation to Combine Helms, TI-TPS5210-Datasheet, and Nilsson                                                                | 287 |

|           | 2.    | Independent Claim 12                                                                                                          | 292 |

|           | 3.    | Independent Claim 13                                                                                                          | 315 |

|           | 4.    | Independent Claim 15                                                                                                          | 325 |

|       | 5.       | Claim 16                               | 332 |

|-------|----------|----------------------------------------|-----|

|       | 6.       | Claims 17 and 18                       | 333 |

| VII.  | NO SECON | DARY CONSIDERATIONS OF NON-OBVIOUSNESS | 333 |

| VIII. | CONCLUS  | ION                                    | 336 |

I, Donald Alpert, Ph.D., declare as follows:

## I. INTRODUCTION AND QUALIFICATIONS

## A. Introduction

- 1. I am an independent consultant with Camelback Computer

Architecture, LLC. My residence and place of business is at 2020 21<sup>st</sup> Street,

Sacramento, CA 95818. I am over the age of eighteen, and I am a citizen of the

United States.

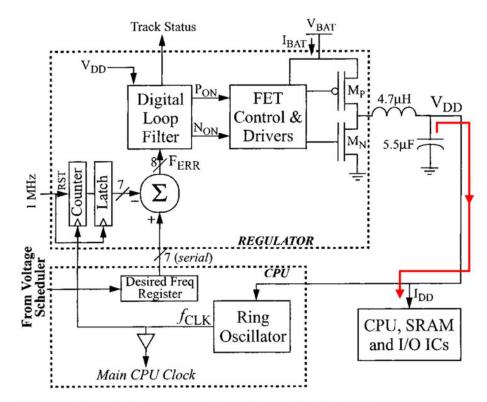

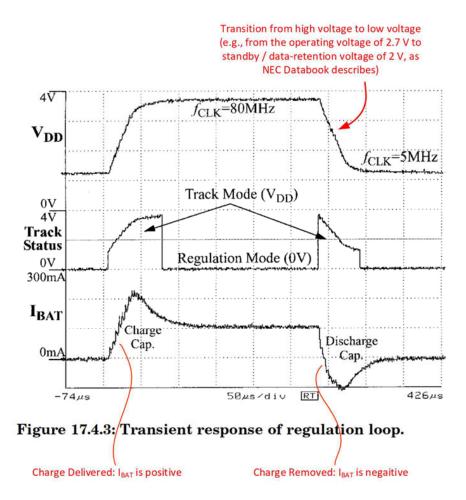

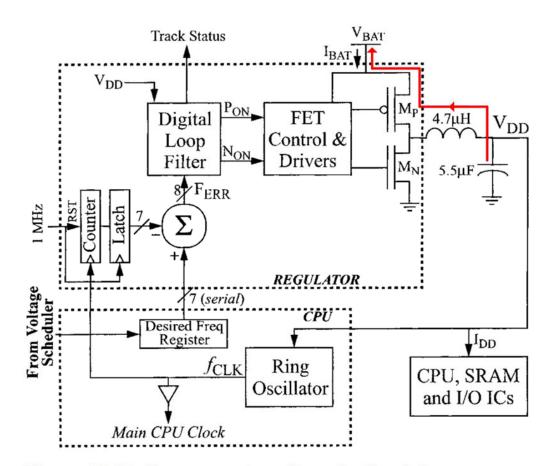

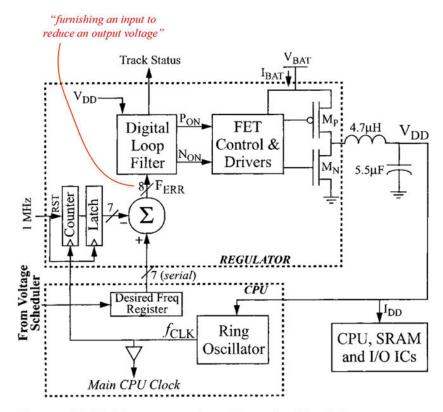

- 2. I have been retained by Microchip Technology, Inc. ("Microchip" or "Petitioner") as a technical expert witness in connection with the petition for *inter* partes review of U.S. Patent No. 7,260,731 ("'731 patent") ("Ex.1001.") I understand that the '731 patent claims priority to October 23, 2000. For purposes of my analysis herein, I have used this date as the relevant time period.

- 3. I have been asked by Petitioner to offer opinions regarding the '731 patent, including the interpretation of certain claim terms and the patentability of the claims in view of certain prior art references and the knowledge of a person of ordinary skill in the art ("POSITA"). This declaration sets forth the opinions I have reached to date regarding these matters.

- 4. In preparing this Declaration, I have reviewed the '731 patent, its prosecution history, and each of the documents I reference herein. In reaching my

opinions, I have relied upon my experience in the field and have also considered the viewpoint of a POSITA at the time of the '731 patent's priority date. As explained below, I am familiar with the level of skill of a POSITA regarding the technology at issue as of that time frame.

5. Camelback Computer Architecture is being compensated for my time working on this matter at my standard hourly rate of \$600 per hour, plus expenses. Neither Camelback Computer Architecture nor I have any personal or financial stake or interest in the outcome of the present proceeding, and the compensation is not dependent on the outcome of this IPR and in no way affects the substance of my statements in this declaration.

# **B.** Qualifications and Experience

- 6. My qualifications for forming the opinions set forth in this

Declaration are summarized here and explained in more detail in my curriculum

vitae, which is attached as Exhibit 1003.

- 7. I have 45 years of academic and industrial experience in applying, designing, studying, teaching, and writing about microprocessors and computer systems. I received an Electrical Engineering Ph.D. degree in 1984 from Stanford University. I earlier received an Electrical Engineering B.S. degree from MIT in 1973 and an Electrical Engineering M.S. degree from Stanford University in 1978.

I have taught classes in computer architecture at Stanford, Tel Aviv, and Arizona State Universities.

- From 1976 to 1977, I worked at Burroughs Corporation, where I 8. designed peripheral interface controllers, including those for serial data communications based on Intel 8080 microprocessor components. From 1980 to 1989, I was the lead architect for the design of three high-performance microprocessors at Zilog and National Semiconductor. Later, at Intel, I was the lead architect of the Pentium® Processor from 1989 to 1992 and of the 815 chipset from 1999 to 2000, both of which became the most widely used PC components of their time. The 815 chipset comprised two components: (1) a memory controller hub (MCH) that included a graphics controller and memory controller with interfaces to the CPU, 133 MHz SDRAM system memory modules, an optional, external graphics controller and (2) an I/O controller hub (ICH) that included various I/O controllers (e.g., network, hard drive, USB) for system peripheral devices and power management control registers. Additionally, I served as comanager for the Itanium processor design from 1993-1997.

- 9. I am a Senior Member of the Institute of Electrical and Electronics Engineers (IEEE), and served as the chair of the IEEE Technical Committee on Microprocessors and Microcomputers from 1999 to 2000. I was the keynote

speaker at the first Cool Chips conference, dedicated to the study of low-power microprocessors and systems. I have given invited lectures at several universities, and published ten papers in various professional journals and conference proceedings. My paper entitled "Architecture of the Pentium Processor," was selected as best paper in IEEE Micro for 1993. I am a named inventor on over 30 U.S. patents that pertain to microprocessors, computer systems, and related technology.

10. I have reviewed the '731 Patent, and I am familiar with the patent's subject matter, which is within the scope of my education and professional experience. Based at least on my background in academia, industry, and consulting, I am familiar with the issues and technology relating to processors, chipsets, memory, peripheral devices, and power management for computer systems. I have personally analyzed, developed, and tested such computer components and systems. More specifically, the Pentium® Processor and 815 chipset for which I was the lead architect at Intel implemented various features for supporting power management, including those related to Advanced Power Management (APM) and Advanced Configuration and Power Interface Specification (ACPI) industry standards.

## C. Materials Considered

11. The analysis that I provide in this Declaration is based on my education and experience in the field of computer systems, as well as the documents I have considered, including the '731 patent (Ex.1001) and its prosecution history (Ex.1004). The '731 patent states on its face that it issued from Application No. 09/694,433, filed on October 23, 2000. For the purposes of this Declaration, I have been instructed to assume October 23, 2000 as the effective filing date for the '731 patent. I have cited to the following documents in my analysis below:

# **LIST OF EXHIBITS**

| EXHIBIT No. | DESCRIPTION                                                                                                                                                                                             |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1001        | U.S. Patent No. 7,260,731 issued to Andrew Read, et al., (filed Oct. 23, 2000, issued Aug. 21, 2007)                                                                                                    |

| 1003        | Curriculum Vitae of Donald Alpert, Ph.D.                                                                                                                                                                |

| 1004        | Prosecution History for U.S. Patent Application No. 09/694,433, which issued as U.S. Patent No. 7,260,731                                                                                               |

| 1005        | Excerpts from Single-Chip Microcomputer Databook, NEC Electronics Inc. (May 1990)                                                                                                                       |

| 1006        | Thomas Burd et al., "A Dynamic Voltage Scaled Microprocessor System," in Digest of Technical Papers, 2000 IEEE Int. Solid-State Circuits Conf. (Feb. 2000) ("Burd")                                     |

| 1007        | U.S. Patent No. 5,955,871 to Nguyen ("Nguyen")                                                                                                                                                          |

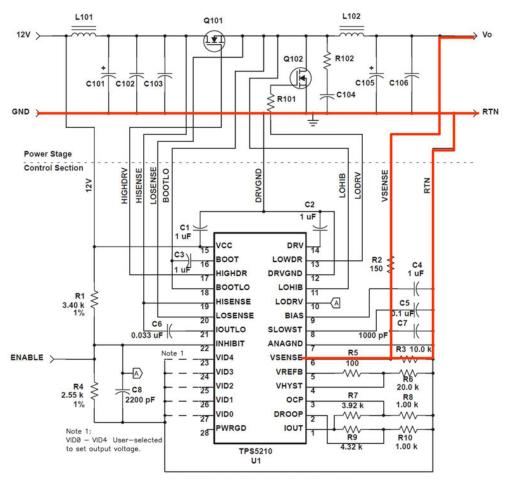

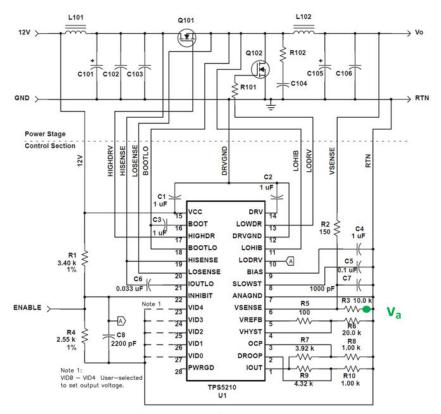

| 1008        | TPS5210 Programmable Synchronous-Buck Regulator Controller (as evidenced by Texas Instruments, Inc., "TPS5210 Programmable Synchronous-Buck Regulator Controller," (May 1999) ("TI-TPS5210-Datasheet")) |

| 1009        | U.S. Patent No. 5,919,262 to Kikinis et al. ("Kikinis")                                                                                                                                                 |

| 1010        | U.S. Patent No. 6,748,545 to Helms et al. ("Helms")                                                                                                                                                     |

| 1011        | Maxim MAX1652–MAX1655 High-Efficiency, PWM, Step-Down DC-DC Controllers (as evidenced by Maxim                                                                                                          |

| EXHIBIT No. | DESCRIPTION                                               |

|-------------|-----------------------------------------------------------|

|             | Integrated Inc., "High-Efficiency, PWM, Step-Down DC-     |

|             | DC Controllers in 16-Pin QSOP, MAX1652–MAX1655,"          |

|             | Rev. 1 (July 1998) ("Maxim-165X-Datasheet"))              |

| 1012        | Maxim Integrated, Inc., "MAX1711 Voltage Positioning      |

| 1012        | Evaluation Kit," Rev. 1 (June 2000) ("MAX1711-Kit"))      |

| 1012        | James W. Nilsson, "Electronic Circuits," (Addison Wesley, |

| 1013        | 4th ed.) (1993) ("Nilsson")                               |

| 1014        | Not Used                                                  |

| 1015        | U.S. Patent No. 3,941,989                                 |

| 1016        | U.S. Patent No. 4,293,927                                 |

| 1017        | CMOS, the Ideal Logic Family                              |

|             | Inki Hong, et al., "Synthesis Techniques for Low-Power    |

| 1018        | Hard Real-Time Systems on Variable Voltage Processors,"   |

| 1010        | in Proceedings of the 19th IEEE Real-Time Systems         |

|             | Symposium (Dec. 1998)                                     |

| 1019        | U.S. Patent No. 5,021,679                                 |

|             | "Terms, Definitions, and Letter Symbols for               |

| 1020        | Microcomputers, Microprocessors, and Memory Integrated    |

|             | Circuits," JEDEC Standard JESD-100A (Aug. 1993)           |

| 1021        | U.S. Patent No. 5,898,235                                 |

| 1022        | U.S. Patent No. 6,347,379                                 |

| EXHIBIT No. | DESCRIPTION                                                                                                                                                |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1023        | L. L. Vadasz, <i>et al.</i> , "Silicon-Gate Technology," IEEE Spectrum, vol. 6 no. 10 at 35 (October 1969)                                                 |

| 1024        | Not Used                                                                                                                                                   |

| 1025        | Not Used                                                                                                                                                   |

| 1026        | U.S. Patent No. 5,677,558                                                                                                                                  |

| 1027        | Bang S. Lee, "Technical Review of Low Dropout Voltage<br>Regulator Operation and Performance," Texas Instruments<br>Application Report SLVA072 (Aug. 1999) |

| 1028        | Bob Wolbert, "Micrel's Guide to Designing With Low-<br>Dropout Voltage Regulators," (Dec. 1998)                                                            |

| 1029        | Jim Williams, "Step-Down Switching Regulators," Linear<br>Technology Application Note 35 (Aug. 1989)                                                       |

| 1030        | U.S. Patent No. 5,731,731                                                                                                                                  |

| 1031        | Not Used                                                                                                                                                   |

| 1032        | Mobile Power Guidelines '99, Rev. 1.00, Intel Corporation (December 1, 1997                                                                                |

| 1033        | U.S. Patent No. 6,212,094                                                                                                                                  |

| 1034        | U.S. Patent No. 5,568,044 to Bittner ("Bittner")                                                                                                           |

| 1035        | Maxim Integrated, Inc., "High-Speed, Digitally Adjusted<br>Step-Down Controllers for Notebook CPUs,                                                        |

| EXHIBIT No. | DESCRIPTION                                                                                                                       |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------|

|             | MAX1710/MAX1711," Rev. 0 (Nov. 1998) ("MAX171X-1998-Datasheet")                                                                   |

| 1036        | Advanced Micro Devices, Inc., "AMD Athlon Processor<br>Datasheet," Rev. G (1999) ("Athlon-99-Datasheet")                          |

| 1037        | Advanced Micro Devices, Inc., "AMD Athlon Processor  Module Datasheet, Rev. M (June 2000) ("Athlon-00- Datasheet")                |

| 1038        | Advanced Micro Devices, Inc., "AMD 756 Peripheral Bus<br>Control Datasheet," Rev. B (August 1999) ("AMD-756-<br>Datasheet")       |

| 1039        | Advanced Configuration and Power Interface Specification, Rev. 1.0 (Dec. 22, 1996) (the "ACPI standard" or the "ACPI")            |

| 1040        | Bang Sup Lee, "Extended output voltage adjustment (0 V to 3.5 V) using the TI TPS5210 (SLYT195)," Analog Applications (Aug. 1999) |

| 1041        | U.S. Patent No. 5,457,421 to Tanabe ("Tanabe")                                                                                    |

| 1042        | High Speed Synchronous Power MOSFET Smart Driver SC1405 ("SC1405")                                                                |

| 1043        | U.S. Patent No. 5,565,761 to Hwang                                                                                                |

| 1044        | U.S. Patent No. 5,627,460 to Bazinet et al.                                                                                       |

| EXHIBIT NO. | DESCRIPTION                                             |

|-------------|---------------------------------------------------------|

|             | Maxim Integrated, Inc., "High-Speed, Digitally Adjusted |

| 1045        | Step-Down Controllers for Notebook CPUs,                |

| 1045        | MAX1710/MAX1711," Rev. 1 (Jul. 2000) ("MAX171X-         |

|             | 2000-Datasheet")                                        |

#### II. LEGAL PRINCIPLES

12. I am not an attorney. For purposes of this declaration, I have been informed about certain aspects of the law that are relevant to my analysis and opinions, as set forth below.

## A. Prior Art

13. I understand that the prior art to the '731 patent includes patents and printed publications in the relevant art that predate the '731 patent's priority date. As I explained previously, I have been instructed to assume for purposes of my analysis that October 23, 2000 is the relevant date for determining what is "prior art." In other words, I should consider as "prior art" anything publicly available prior to October 23, 2000. I further understand that, for purposes of this proceeding in the United States Patent Trial and Appeal Board, only patents and documents that have the legal status of a "printed publication" may be relied on as prior art.

## **B.** Claim Construction

- 14. I understand that under the legal principles, claim terms are generally given their ordinary and customary meaning, which is the meaning that the term in question would have to a POSITA at the time of the invention, *i.e.*, as of the effective filing date of the patent application. I further understand that a POSITA is deemed to read the claim term not only in the context of the particular claim in which a claim term appears, but in the context of the entire patent, including the specification.

- 15. I am informed by counsel that the patent specification, under the legal principles, has been described as the single best guide to the meaning of a claim term, and is thus highly relevant to the interpretation of claim terms. I understand for terms that do not have a customary meaning within the art, the specification usually supplies the best context of understanding the meaning of those terms.

- 16. I am further informed by counsel that other claims of the patent in question, both asserted and unasserted, can be valuable sources of information as to the meaning of a claim term. Because the claim terms are normally used consistently throughout the patent, the usage of a term in one claim can often illuminate the meaning of the same term in other claims. Differences among claims can also be a useful guide in understanding the meaning of particular claim

terms.

- 17. I understand that the prosecution history can further inform the meaning of the claim language by demonstrating how the inventors understood the invention and whether the inventors limited the invention in the course of prosecution, making the claim scope narrower than it otherwise would be.

Extrinsic evidence may also be consulted in construing the claim terms, such as my expert testimony.

- 18. I have been informed by counsel that, in IPR proceedings, a claim of a patent shall be construed using the same claim construction standard that would be used to construe the claim in a civil action filed in a U.S. district court (which I understand is called the "*Phillips*" claim construction standard), including construing the claim in accordance with the ordinary and customary meaning of such claim as understood by one of ordinary skill in the art and the prosecution history pertaining to the patent.

- 19. I have been instructed by counsel to apply the "*Phillips*" claim construction standard for purposes of interpreting the claims in this proceeding, to the extent they require an explicit construction. The description of the legal principles set forth above thus provides my understanding of the "*Phillips*" standard as provided to me by counsel.

- 20. I understand that some claims are independent, and that these claims are complete by themselves. Other claims refer to these independent claims and are "dependent" from those independent claims. The dependent claims include all the limitations of the claims on which they depend.

- 21. I am further informed and understand that certain claim elements recite "means for" or "means to," and may therefore be understood as reciting means-plus-function limitations. I am also informed and understand that, accordingly, the analysis of each of these claim elements may require the identification of a respective function recited in each of these claim elements, and the identification of a respective structure that is disclosed in the specification or file history of the '731 patent, where the respective identified structure is linked to and performs the respective recited function.

- 22. I am additionally informed and understand that to show that the prior art teaches any particular one of these claim elements, the prior art should disclose a structure that performs the function recited in the particular claim element, where the structure disclosed in the prior art is the same as or equivalent to the structure disclosed in the '731 patent that performs the recited function.

- 23. I am also informed and understand that the determination of equivalence under 35 U.S.C. §112 does not involve the function-way-result test

that is generally applied under the doctrine of equivalents in determining infringement of a claim. Rather, I am informed and understand, that equivalence is determined by comparing the prior art structure that performs the claimed function with the structure disclosed in the specification.

# C. Anticipation

24. I understand that to anticipate a patent claim under 35 U.S.C. § 102, a single asserted prior art reference must disclose each and every element of the claimed invention, either explicitly, implicitly, or inherently, to a POSITA. There must be no difference between the claimed invention and the disclosure of the alleged prior art reference as viewed from the perspective of a POSITA. Also, I understand that in order for a reference to be an anticipating reference, it must describe the claimed subject matter with sufficient clarity to establish that the subject matter existed and that its existence was recognized by persons of ordinary skill in the field of the invention. In addition, I understand that in order to establish that an element of a claim is "inherent" in the disclosure of an asserted prior art reference, extrinsic evidence (or the evidence outside the four corners of the asserted prior art reference) must make clear that the missing element is necessarily found in the prior art, and that it would be recognized as necessarily present by persons of ordinary skill in the relevant field.

25. In my opinions below, when I say that a POSITA would have understood, readily understood, or recognized that an element or aspect of a claim is disclosed by a reference, I mean that the element or aspect of the claim is disclosed to a POSITA.

## D. Obviousness

- 26. I understand that obviousness is a determination of law based on various underlying determinations of fact. In particular, these underlying factual determinations include (1) the scope and content of the prior art; (2) the level of ordinary skill in the art at the time the claimed invention was made; (3) the differences between the claimed invention and the prior art; and (4) the extent of any proffered objective indicia of nonobviousness. I understand that the objective indicia which may be considered in such an analysis include commercial success of the patented invention (including evidence of industry recognition or awards), whether the invention fills a long-felt but unsolved need in the field, the failure of others to arrive at the invention, industry acquiescence and recognition, initial skepticism of others in the field, whether the inventors proceeded in a direction contrary to the accepted wisdom of those of ordinary skill in the art, and the taking of licenses under the patent by others, among other factors.

- 27. To ascertain the scope and content of the prior art, it is necessary to

Declaration of Donald Alpert, Ph.D. in Support of Petition for *Inter Partes* Review of

U.S. Patent No. 7,260,731

first examine the field of the inventor's endeavor and the particular problem for which the invention was made. The relevant prior art includes prior art in the field of the invention, and also prior art from other fields that a POSITA would look to when attempting to solve the problem.

- 28. I understand that a determination of obviousness cannot be based on the hindsight combination of components selectively culled from the prior art to fit the parameters of the patented invention. Instead, it is my understanding that in order to render a patent claim invalid as being obvious from a combination of references, there must be some evidence within the prior art as a whole to suggest the desirability, and thus the obviousness, of making the combination in a way that would produce the patented invention.

- 29. I further understand that in an obviousness analysis, neither the motivation nor the purpose of the patentee dictates. What is important is whether there existed at the time of the invention a known problem for which there was an obvious solution encompassed by the patent's claims.

- 30. I also understand that the combination of familiar elements according to known methods is likely to be obvious when it yields predictable results. I also understand that an example of a solution in one field of endeavor may make that solution obvious in another related field, as well. I am informed that market

demands or design considerations may prompt variations of a prior art system or process, in the same field or a different one, where such variations may ordinarily be considered obvious, straightforward changes to what has been explicitly disclosed in the prior art.

- 31. I also understand that if a POSITA could have implemented a predictable variation without excessive experimentation, that variation would have been considered obvious. I understand that for similar reasons, if a technique has been used to improve one device or processor, and a POSITA would have recognized that that technique can improve a similar devices or process in the same way, implementing such an improvement would have been obvious, unless the implementation yields unexpected results or challenges in implementation.

- 32. I understand that the obviousness analysis need not seek out precise teachings directed to the specific subject matter of the challenged claim. Rather, I understand, that the analysis can take into account ordinary innovation and experimentation, *e.g.*, inferences and creative steps that a POSITA would employ, that yields predictable, benefits. In this regard, I understand that a POSITA is also a person of ordinary creativity.

- 33. I understand that sometimes it will be necessary to consider interrelated teachings of several prior art references, the demands or current

problems known in the design community or present in the marketplace, and/or the background knowledge of a POSITA. I understand that any of these factors may be considered to assess whether there was a reason to combine the teachings of the prior art references, where the combination would reveal the system or process claimed in the challenged patent.

- 34. I understand that the obviousness analysis is not limited to a formalistic conception of "teaching, suggestion, and motivation." I understand that in 2007, the Supreme Court issued its decision in *KSR Int'l Co. v. Teleflex Inc.*, 550 U.S. 398, 418 (2007), where the Court rejected the previous requirement of a "teaching, suggestion, or motivation to combine" known elements of prior art as a precondition for concluding that a combination of those elements would be obvious. It is my understanding that *KSR* confirms that any rational reason or motivation that would have been known to a POSITA, including common sense, one derived from the nature of the problem to be solved, *etc.*, can be sufficient to explain why such known prior art elements from one or more prior art references would have been combined.

- 35. I understand that a POSITA attempting to solve a particular problem will not be led only to those elements that the prior art explicitly discloses and/or are described as a solution to that particular problem. Rather, I understand that

under the *KSR* standard, steps suggested by common sense are important and should be considered. Common sense informs that disclosed elements or solutions may have obvious uses beyond the particular problem or application described in a reference. Common sense also suggests that if something can be done once it may be obvious to repeat it multiple times.

- 36. I understand that in many cases a POSITA will be able to fit the teachings of several prior art references together, like pieces of a puzzle. As such, any need or problem known in the same or related fields that the prior art considered can provide a reason for combining the teachings of the prior art with those of another prior art. In other words, the prior art references need not be directed towards solving the particular problem addressed in the challenged patent. I also understand that the individual prior art references themselves need not all be directed towards solving a single problem.

- 37. I understand that obviousness does not require that the elements not explicitly disclosed in one prior art reference (sometimes referred to as a primary reference) but disclosed in another prior art reference (sometimes referred to as a secondary reference) need not be shown to be bodily or actually incorporated into the structure of the primary reference. Rather, the test is what the combined teachings of those references would have informed a POSITA. Thus, I understand

that the disclosures of the prior art references need not be physically combinable, and that combining the teachings of references should be the focus of the analysis.

- 38. I understand that an invention that might otherwise be considered an obvious variation or modification of the prior art may nevertheless be considered unobvious if any of the prior art references discourages or leads away from such a modification. I further understand, however, that a reference does not "teach away" from a feature or its modification simply because the reference suggests that an alternative, such as another embodiment of an invention disclosed in a prior art patent, is better or preferred. I understand that the doctrine of teaching away requires a clear indication that the combination would not work or explicit disclosure that the combination would be undesirable.

- 39. I further understand that in many fields, especially in complex, well evolved technologies, often there is little explicit discussion of obvious techniques, variations, or combinations. In some cases, market demands, rather than scientific inquiry, drive design trends. There may be a design need or market pressure to solve a particular problem, and only a finite number of solutions may be known, neither of which may be the most suited or optimized to meet the design need or to solve the particular problem.

- 40. I understand that in such cases, a POSITA has good reason to pursue

the known solutions that are the available options within the POSITA's technical grasp. Should this lead to an anticipated success or a predictable beneficial result, it is likely the product not of innovation but of ordinary skill and common sense. In that instance, the combination and/or modification of the prior art technique(s) may be obvious because it was obvious to try.

41. Thus I understand, that the fact that a particular combination of prior art elements was "obvious to try," regardless of whether it was actually tried, may indicate that the combination of references disclosing those elements was also obvious, even if no one previously attempted the combination.

## III. LEVEL OF ORDINARY SKILL IN THE ART

42. I understand that an assessment of claims of the '731 patent should be undertaken from the perspective of a POSITA as of the earliest claimed priority date, which I understand is October 23, 2000. I have also been advised that to determine the appropriate level of a person having ordinary skill in the art, the following factors may be considered: (1) the types of problems encountered by those working in the field and prior art solutions thereto; (2) the sophistication of the technology in question, and the rapidity with which innovations occur in the field; (3) the educational level of active workers in the field; and (4) the educational level of the inventor.

- 43. In my opinion, a POSITA at the time of the alleged invention of the '731 patent would have possessed at least a bachelor's degree in electrical engineering, computer engineering, or computer science, with at least two years of experience in computer system development, including experience in developing power/voltage regulation systems for portable devices. A person could also have qualified as a POSITA with some combination of (1) more formal education (such as a master's of science degree) and less technical experience or (2) less formal education and more technical or professional experience in the fields listed above.

- 44. My opinions regarding the level of ordinary skill in the art are based on, among other things, my more than 40 years of experience in electrical and computer engineering, my understanding of the basic qualifications that would be relevant to an engineer or scientist tasked with investigating methods and systems in the relevant area, and my familiarity with the backgrounds of students, colleagues, co-workers, and employees, both past and present. Although my qualifications and experience exceed those of the hypothetical person having ordinary skill in the art defined above, my analysis and opinions regarding the '731 patent have been based on the perspective of a POSITA as of October 23, 2000.

## IV. TECHNOLOGY BACKGROUND

45. This section provides general technical background for computer

Declaration of Donald Alpert, Ph.D. in Support of Petition for *Inter Partes* Review of

U.S. Patent No. 7,260,731

systems, physical principles of power consumption, and methods for reducing power and energy consumption by computer systems while maintaining requirements for performance and responsiveness. Managing the power of computer systems involves technologies related to microelectronics, logic and memory circuits, power supplies, and operating systems.

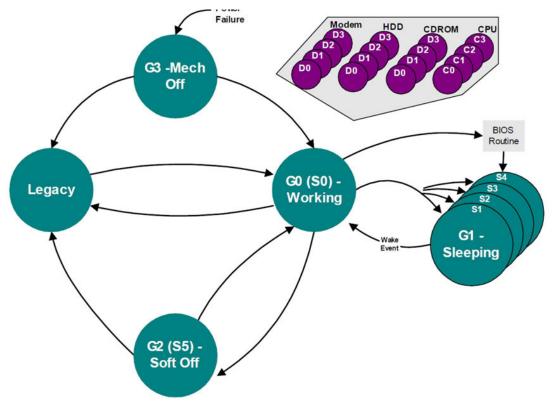

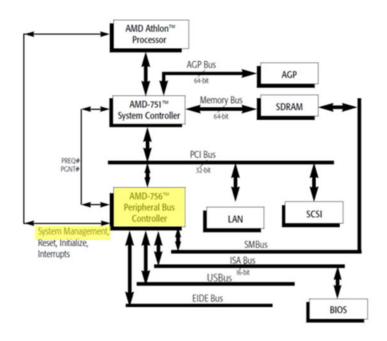

46. A computer system's hardware generally comprises three types of components, as described below and shown in the demonstrative figure:

**Processors**: A processor is a device that fetches and executes the instructions of a program.

**Memory**: Memory stores instructions executed by a processor and data manipulated by a processor

**Input/Output (I/O) Devices**: I/O devices provide auxiliary storage, communication between systems, and human interface.

# A. Power and Energy Consumption of Computer Systems

## 1. CMOS and Power

47. For more than 35 years, silicon CMOS (Complementary Metal-Oxide Semiconductor) has been the most widely used technology for microelectronic devices. CMOS technology uses two types of transistors, "complementary" n-type and p-type, to fabricate logic and memory circuits. The complementary nature of these transistors means that under conditions where one type of transistor switches on, the other type switches off. Thus, devices fabricated in CMOS have commonly been designed to operate statically; that is, when the inputs to the device are stable, no transistors are switching and the device consumes no "dynamic" power. In contrast, when inputs to the device are changing, transistors switch as a result, and the device consumes dynamic power.

- 48. CMOS technology has continually improved during this period from a feature size of about 1.5 μm in 1985 to 5 nm in 2020, thus reducing linear feature size by a factor of about 300 over 35 years. This reduction in size results in microelectronic structures that are generally much smaller, much faster, and require much less power. However, "leakage" current (e.g., a small current that leaks through the channel of a transistor when the transistor is turned off) has become an increasingly important factor as semiconductor feature size has decreased. As a result of leakage current, a device consumes power even when it is not performing useful work.

- 49. Combining the dynamic and leakage types of power above, the power consumed by a CMOS device can be represented by the relationship reproduced below:

(Ex.1032, Mobile Power Guidelines '99, Rev. 1.00, Intel Corporation, at 9 (December 1, 1997).) In this equation, the symbol "∝" means "proportional to." "Capacitance" is related to the "active area" of the device, which represents the total amount of circuitry. The term "DC Current" generally relates to analog circuits that draw current even when they are not active, such as sense amplifiers.

50. Thus, for an electronic device produced in CMOS technology, power consumption can be reduced by (i) slowing or stopping the clock or (ii) lowering or turning off the voltage supplied.

# 2. Slowing the Clock

51. One technique for reducing power consumed by a computer system is to reduce its clock frequency. For example, in 1974, it was known that one could reduce power consumption of a battery-powered, handheld calculator by slowing the calculator's clock frequency, as disclosed in U.S. Patent No. 3,941,989:

An object of the invention is to reduce the power consumption of calculators, and particularly of hand-held calculators which are battery powered, by supplying to the calculator only as much power as actually needed for each different mode of operation and by clocking the calculator at a rate which is only as high as actually needed for each different mode of operation.

(Ex.1015, U.S. Patent No. 3,941,989, 1:45-52.)

52. In such a system, the dynamic power is reduced in direct proportion to the reduction in frequency. Although power (energy/time) is reduced, the computer's performance is also reduced proportionally with frequency. Therefore, the system requires proportionally longer time to complete its computation, and the energy consumption remains unchanged.

## 3. Stopping the Clock

53. Another technique used in the 1970's to reduce power consumption of battery-powered, handheld calculators was to stop the clock when no calculation was occurring, such as after a period of time during which the user did not press any keys. Reducing the clock frequency to 0, *i.e.*, stopping the clock, eliminates all dynamic power. During this idle time, data can be retained, allowing calculation to resume when the user next presses a key. For example, U.S. Patent No. 4,293,927 discloses:

With such a construction, when no keying in operation is performed for a given period of time while the power source is turned on, the oscillation of the oscillating circuit is stopped to stop generation of the clock signal and to thereby stop all the circuit operations. However, the operation results in the memory continue to be held or stored. Therefore, the wasteful power consumption when an operator fails to turn off the power source switch may be prevented. Additionally, the data obtained before the oscillation of the oscillating circuit stops is held and therefore the data is held even in the course of the operation execution. Accordingly, there is no need to reenter the identical data at the restart of the operation, thereby to allow the calculator to smoothly enter the execution of the operation. In this respect, the key in operation is remarkably improved.

(Ex.1016, U.S. Patent No. 4,293,927, 2:53-68.)

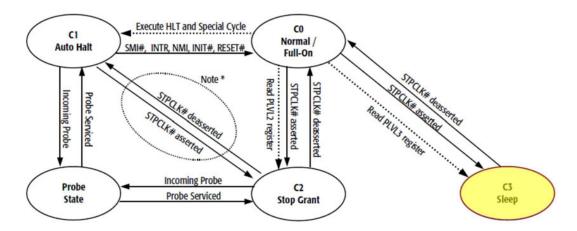

54. A processor that is idle with its clock stopped is said to be in sleep (or deep sleep or deeper sleep), doze, or nap state. Alternatively, other terms are used, such as halt, stop, or standby state. The transition from such an idle state to an active state is said to be waking, resuming, or releasing.

## 4. Dynamic Voltage-Frequency Scaling (DVFS)

- 55. Another characteristic of CMOS technology is that the maximum frequency at which a circuit can operate varies directly with the voltage. That is, operating the circuit at higher frequency requires higher voltage than operating the circuit at lower frequency. Thus, when the operating frequency is reduced, the voltage can also be reduced, effectively reducing dynamic power consumption linearly with frequency and quadratically with voltage. Hence, the energy consumed to perform a computation is also reduced.

- 56. It was therefore understood that a system's power consumption and energy could be minimized by operating the system at the minimum frequency required to perform its function, and by setting the power supply voltage to the minimum required for that frequency. For example, CMOS, the Ideal Logic Family states:

So, we can see that for a given design, and therefore fixed capacitive load[,] increasing the power supply voltage will increase the speed of the system. Increasing  $V_{\rm CC}$  increases speed but it also increases power

dissipation. This is true for two reasons. First, CV<sup>2</sup>f power increases. This is the power dissipated in a CMOS circuit, or any other circuit for that matter, when driving a capacitive load.

(Ex.1017, CMOS, the Ideal Logic Family at 2.)

57. CMOS, the Ideal Logic Family also states:

Minimizing system power dissipation: To minimize power consumption in a given system, it should be run at the minimum speed to do the job with the lowest possible power supply voltage. AC and DC transient power consumption both increase with frequency and power supply voltage. The AC power is described as CV<sup>2</sup>f power. This is the power dissipated in a driver driving a capacitive load. Obviously, AC power consumption increases directly with frequency and as the square of the power supply.

(*Id.* at 5.)

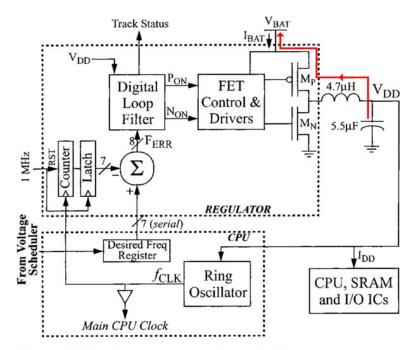

58. Consequently, by 2000 it was known that a computer processor could be designed to control power consumption by dynamically varying its voltage and frequency, a technique known **as dynamic voltage-frequency scaling (DVFS)**. Operating a processor in this manner requires a power supply that varies voltage. For example, Hong states:

The problem outlined above really arises because conventional systems are designed with a fixed supply voltage. However, there is no fundamental reason that the supply voltage has to be fixed. Instead,

it can in principle be varied dynamically at run time. Indeed, advances in power supply technology makes it possible to vary the generated supply voltage dynamically under external control. While many CMOS circuits have always been capable of operating over a range of supply voltages, it is the recent progress in power supply circuits that has made feasible systems with dynamically variable supply voltages. Since both the power consumed and the speed (maximal clock frequency) are a function of the supply voltage, such *variable voltage* systems can be made to operate at different points along their power *vs.* speed curves in a controlled fashion.

(Ex.1018, Inki Hong, *et al.*, "Synthesis Techniques for Low-Power Hard Real-Time Systems on Variable Voltage Processors," in Proceedings of the 19th IEEE Real-Time Systems Symposium at 1 (Dec. 1998) (citations omitted) (emphasis in original).)

59. For example, a handheld, battery-powered personal computer developed by Poqet Computer Corporation during the late-1980s included a processor that operated in a high-performance mode at 5 V and 6.6 MHz or in a low-power mode at 3 V and 2.3 MHz. The high-performance mode could be used for numerical data computation, and the low-power mode could be used for word processing applications. Additionally, the clock frequency and supply voltage could be further reduced below that required to operate the processor while the

processor's data is retained. (*See, e.g.*, Ex.1019, U.S. Patent No. 5,021,679, 1:8-3:57.)

## B. Registers and Static Random Access Memory (SRAM)

- dynamic power, but leakage power remains because the device continues to be connected to the voltage of the power supply. A processor's power consumption due to leakage can be completely eliminated by shutting off its supply voltage. Nevertheless, when the supply voltage is removed, the state required for the processor to execute instructions, such as data stored in registers and integrated memory, is lost. Hence, the time and energy consumed by the processor to save is state when turning off its supply voltage and then restoring its state when resuming its supply voltage can result in poor performance and wasted energy.

Consequently, it is beneficial for many computer applications that the processor retains its state while the clock is stopped so that computation can be resumed quickly and efficiently.

- 61. Within a processor, data can be stored by a register or memory when the clock is stopped by using a circuit with two cross-coupled inverters. Feedback through the coupling provides for two stable states with one inverter having its output low while the other inverter has its output high, thereby allowing one bit of

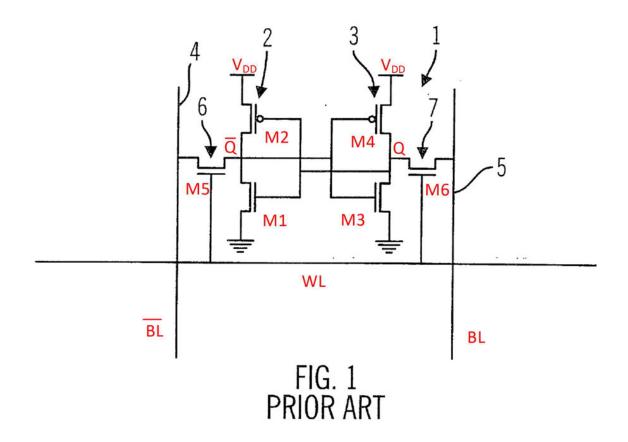

information to be stored. For example, FIG. 1 from U.S. Patent No. 6,212,094 to Rimondi, issued on April 3, 2001 and filed on November 25, 2998 (Ex.1033), annotated and reproduced below shows a circuit for such a bit-cell, where one inverter (output  $\overline{Q}$ ) comprises nMOS transistor M<sub>1</sub> and pMOS transistor M<sub>2</sub>, and the other inverter (output  $\overline{Q}$ ) comprises M<sub>3</sub> and M<sub>4</sub>.

(Ex.1033, FIG. 1 (annotated).)

62. A stored bit is accessed by driving the wordline (WL) signal High, which switches on nMOS transistors  $M_5$  and  $M_6$ . For read access, the true and complement bitlines (BL and  $\overline{BL}$ ) are precharged High, then WL is driven High,

and depending on the state of the bit, either BL or  $\overline{BL}$  is pulled Low by M<sub>3</sub> or M<sub>1</sub>. For write access, the bitlines (BL and  $\overline{BL}$ ) are strongly driven to the written value and its complement, then WL is driven High, and the stored bit (Q and  $\overline{Q}$ ) is driven to the written value.

63. During periods when the data is not being accessed, a condition known as *standby*, the data can be retained indefinitely. Furthermore, it was known before 2000 that the data could be retained even when the supply voltage was lowered to a value below that required to access the data. Industry standards refer to this usage as **data-retention mode**.

#### data retention mode

A standby or battery mode of operation in which the integrity of stored data is maintained although the supply voltage is below that specified for reading or writing.

(Ex.1020, "Terms, Definitions, and Letter Symbols for Microcomputers, Microprocessors, and Memory Integrated Circuits," JEDEC Standard JESD-100A, at 4 (Aug. 1993.)

64. Lowering the supply voltage during data-retention mode reduces leakage power consumption by decreasing both supply voltage and transistor

leakage current.<sup>1</sup> The minimum data retention voltage can be a few tenths of a volt above the threshold voltage<sup>2</sup> of typical transistors for the bit cell. (*See* Ex.1021, U.S. Patent No. 5,898,235, 2:52-62; *see also*, Ex.1022, U.S. Patent No. 6,347,379, 6:13-15.)

65. For example, an early 256-bit SRAM product developed by Intel in 1969 reduced power consumption by a factor of 20 (from 1 mW per bit to 50  $\mu$ W) for standby mode by reducing the supply voltage to the memory cells, when compared with normal operation.

1 D : 1 1 11

<sup>&</sup>lt;sup>1</sup> During operation and standby it is possible for data errors to occur as a result of noise and high-energy events, such as alpha particles from packaging material and cosmic rays from deep space. As supply voltage is lowered, less charge is stored in the bit circuit, so the rate of errors generally rises. Consequently, it is necessary to design and evaluate the storage circuitry and its supply voltage to ensure an acceptable error rate according to application requirements.

<sup>&</sup>lt;sup>2</sup> The threshold voltage of an MOSFET (Metal-Oxide-Silicon Field-Effect Transistor) is the minimum gate-to-source voltage that is needed to turn on the transistor, i.e., to form a conducting channel between the source and drain terminals.

Power dissipation is typically less than 2 mW per bit for normal operation. This, however, can be lowered to below 50  $\mu$ W. In standby mode-when the chip will only store information, but does not need to be accessed-- the peripheral power supply can be completely shut down. This "idle" cuts the total power drain by a factor of 2. Furthermore, the cell power can be reduced considerably by reducing the cell voltage to -2 volts. This generates only -7 volts across the memory bits and is adequate for holding information in the memory cells. Figure 12 shows typical power dissipation in both the cells and peripheral (decode, I/O) circuitry. In this mode of operation, the total power dissipation is less than 12 mW, and corresponds to less than 50  $\mu$ W/bit.

(Ex.1023, L. L. Vadasz, et al., "Silicon-Gate Technology," IEEE Spectrum, vol. 6 no. 10 at 35 (Oct. 1969).)

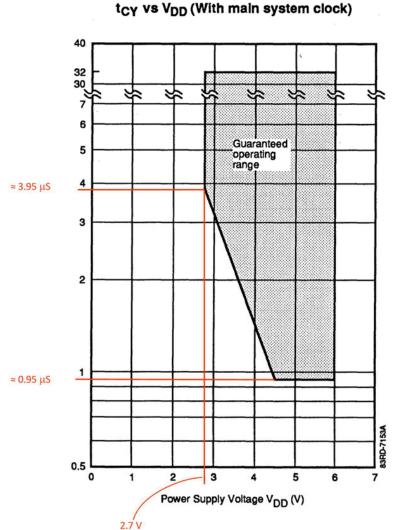

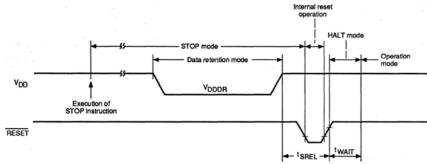

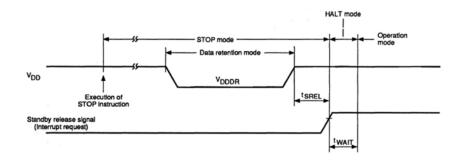

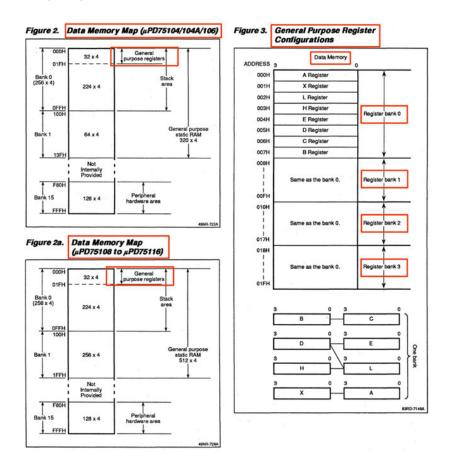

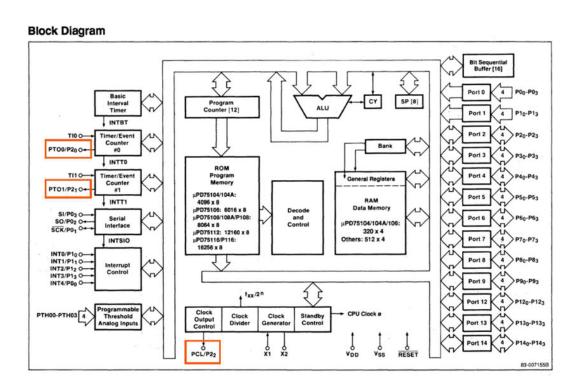

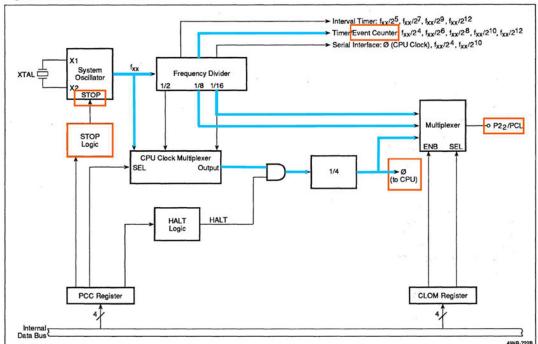

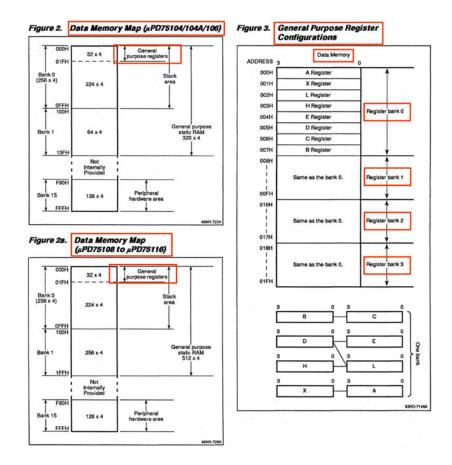

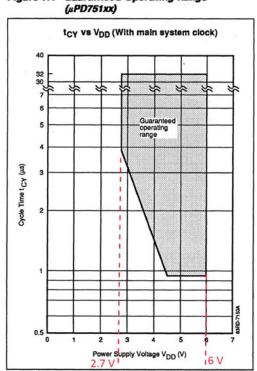

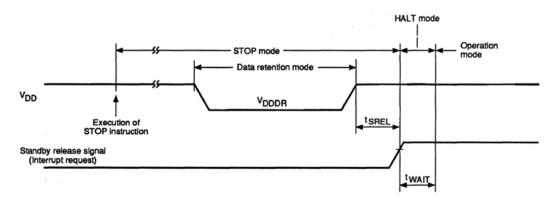

66. Such standby voltage-reduction techniques were also used for microprocessors to retain state while reducing leakage power consumption. For example, the μPD751xx microcomputer circuits produced by NEC operate between 2.7 V at 263 kHz and 6.0 V at 1.05 MHz. (*See* Ex.1005, NEC-Databook at 24-75; *see id.* at 61-62 (AC Characteristics and Figure 17).) The NEC microcomputers have standby modes that stop the CPU's clock, including a Data Retention mode that allows the supply voltage to be reduced to 2.0 V while retaining the contents of data memory, including general registers. (*Id.* at 32, 47,

and 64; *see id.* at 33 (Figures 2, 2a, and 3.) An interrupt can be used to exit Data Retention mode after the supply voltage is raised to resume normal operation. (*Id.* at 47 (Figure 10), 48 (Table 7), and 65 (Figure 19B).)

| Item                    | STOP Mode                                                                                                                     | HALT Mode                                                                          |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Setting the mode        | STOP Instruction                                                                                                              | HALT Instruction                                                                   |

| Clock oscillator        | The main system clock oscillator is stopped                                                                                   | Only CPU clock $\phi$ is stopped (oscillation continues)                           |

| Basic interval<br>timer | Operation stopped                                                                                                             | Can Operate (IRQBT is set by reference time interval)                              |

| Serial interface        | Can operate only when external SCK input is selected for serial clock. (Note 1)                                               | Can operate if other than CPU clock $oldsymbol{\phi}$ is specified as serial clock |

| Timer/event<br>counter  | Can operate only when Tln (n = 0, 1) pin input is selected for count clock                                                    | Can operate                                                                        |

| Clock output<br>circuit | Stops operation                                                                                                               | Can operate if other than CPU clock $\phi$ is specified                            |

| CPU                     | Operation stopped                                                                                                             | Operation stopped                                                                  |

| Retained data           | Contents of all registers (general registers, flags, mode registers, and output latches) and contents of data memory retained |                                                                                    |

| Release signal          | Interrupt request signal (enabled with interrupt enable flag) from operating hardware or RESET                                |                                                                                    |

#### Notes:

(*Id.* at 48 (Table 7).)

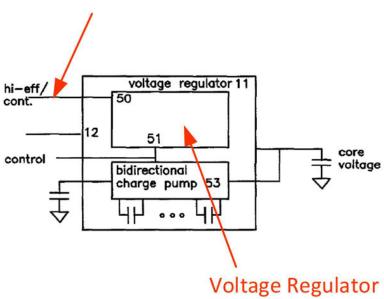

# C. Voltage Regulation

67. A voltage regulator is a device or a component that provides regulated output voltage to circuitry, such as a microprocessor. A voltage regulator can be an AC-DC converter, where the regulator receives AC input (*e.g.*, from the AC mains such as 120 VAC, 230 VAC, *etc.*) and provides a regulated DC output (*e.g.*, 12 VDC, 5 V DC, *etc.*) or a DC-DC converter, where the regulators receives and outputs DC power. A DC-DC converter can be a step-up (boost) converter, where the output voltage is greater than the input voltage, or a step-down (buck)

<sup>(1)</sup> Can also operate with Ti0 selected as the serial clock, but only when Timer/Event Counter 0 is operated with an external Ti0 input

converter, where the output voltage is less than the input voltage. A DC-DC converter/regulator is also commonly classified as a "linear regulator" or a "switching regulator," which are terms of art.

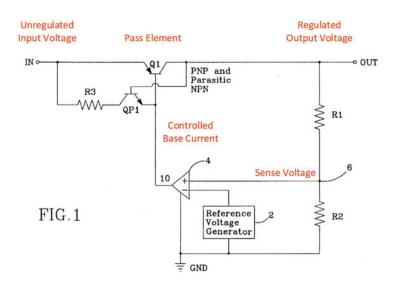

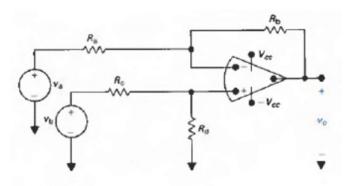

68. Generally in a linear regulator, a pass element (typically a transistor, such as a bipolar junction transistor (BJT) or a power field-effect transistor (power FET)) is connected in series with a load. (*See* U.S. Patent No. 5,677,558, 1:26-39; FIG. 1 (Ex.1026); Bang S. Lee, "*Technical Review of Low Dropout Voltage Regulator Operation and Performance*," Texas Instruments Application Report SLVA072 at 1 (Aug. 1999) ("Lee-Report") (Ex.1027.) In a typical linear regulator, the pass element is operated in its **linear region**, (*see* Ex.1026, 1:26-32; Ex.1027, 1-2; Figure 2), where the current passing through the pass element is proportional to a base current supplied to the pass element. (*See* Ex.1026, 3:61-4:3; FIG. 1.)

(Ex.1026, FIG. 1.)

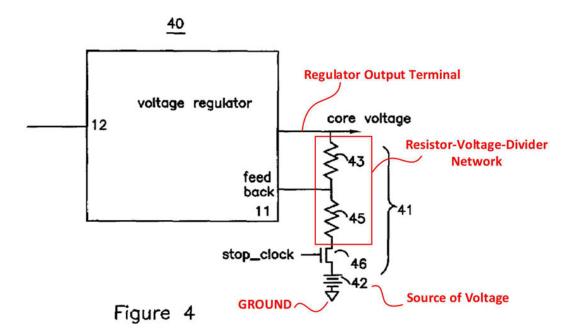

- desired output voltage. At that time, the base current is reduced, in substance, to zero and the pass element is turned off. As the output voltage dropped below, this change is sensed using a resistor-divider based feedback network, and the pass element is turned on again, and operated in the linear mode, until the output voltage reaches the desired level. The above describe cycle may continue indefinitely. (*See* Bob Wolbert, "Micrel's Guide to Designing With Low-Dropout Voltage Regulators," at 8 (Dec. 1998) (Ex.1028.) In a variation of a linear regulator, called "low drop-out" (LDO) regulator, the pass element may include only a single transistor. (*See id.* at 8, Figure 1-1; *see also*, *id.* at 10, Figures 1-3(A)-(C) (depicting different configurations of a linear regulator, including an LDO regulator).)

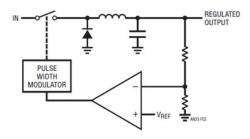

- 70. In general, in a "switching regulator" a pass element may be series connected between an unregulated input voltage and a load, *e.g.*, a microprocessor, to which the regulator provides a regulated output voltage. (*See* Jim Williams, "Step-Down Switching Regulators," Linear Technology Application Note 35 at 1; Figures 1 and 2 (Aug. 1989) ("Williams-Note") (Ex.1029); U.S. Patent No. 5,731,731, 1:23-26 (Ex.1030.) A switching regulator is not operated like a linear

regulator, however, *i.e.*, the pass element is not operated in the linear (or saturation) region until the output voltage reaches the desired value and is then turned off until the output voltage drops below the desired value.

71. Rather, the pass element is switched on and off, *i.e.*, switched between the saturation and cut-off regions, at a high frequency (*e.g.*, several kilohertz). (*See* Ex.1030, 1:26-38; Ex.1029 at 18, col. 2 (describing a switching frequency of 100 kHz).) The rapidly switching current at the output of the pass element is filtered using an inductor-capacitor (LC) filter that can store the energy supplied thereto and provide stabilized, regulated voltage to the load. (*See* Ex.1030, 1:26-38.)

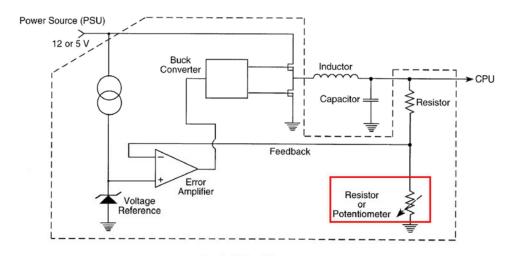

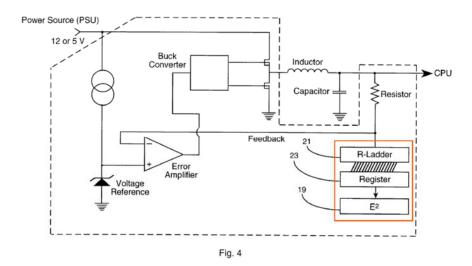

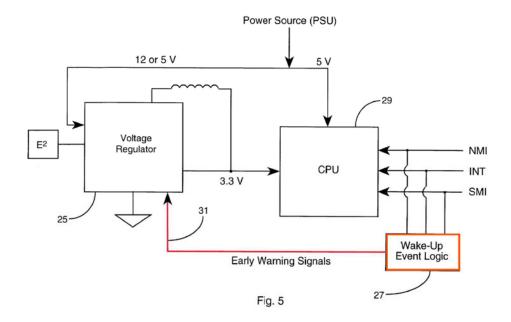

Figure 2. Conceptual Feedback Controlled Step-Down Regulator

Figure 3. A Practical Step-Down Regulator Using the LT1074

(Ex.1029 at 1 (Figure 2), 2 (Figure 3).)

72. One or more parameters of the switching, *e.g.*, the width of the switching pulses and/or the frequency of the pulses may be control the output voltage of the regulator to a desired value. (*See id.*) By convention, such a regulator is called a "switching regulator" because its passed element is switched

on and off, in order to regulate the output voltage thereof.

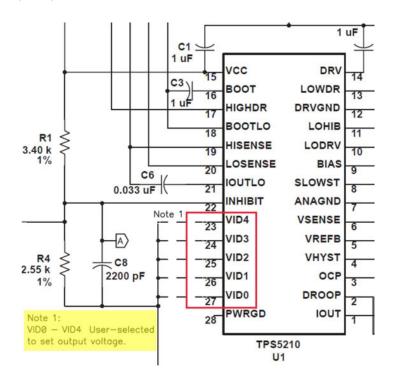

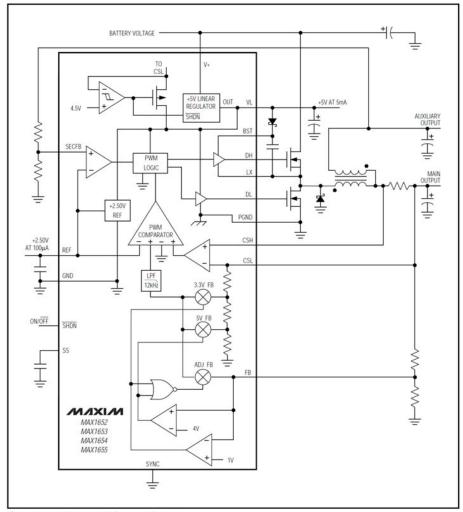

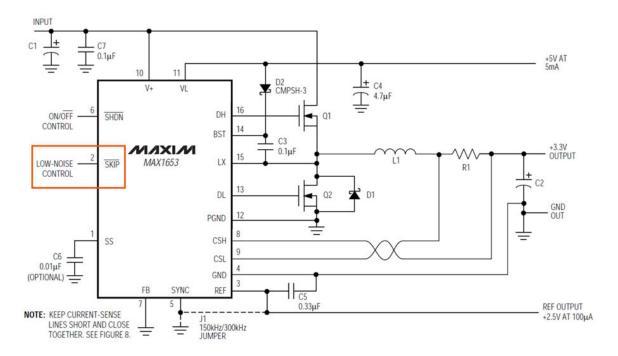

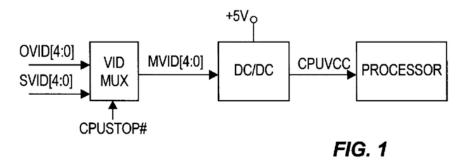

- 73. The supply voltage for a microprocessor is commonly provided by a DC-DC converter that receives power at a higher voltage level (such as about 12 V for power supply of a desktop computer or the battery of a notebook computer) and outputs a lower voltage(such as 3 V) required by the processor. The processors described above, which have dynamic voltage scaling while active and lower voltage for data retention while idle, place a number of demands on their power supply. The output voltage can vary only a limited amount, such as 5%, from a nominal target value for the processor to operate reliably. The process of *regulating* the output voltage within such limits can require different techniques for efficient operation (that is, with relatively little energy loss) when supplying high current for peak performance or low current for lower-performance or idle periods.

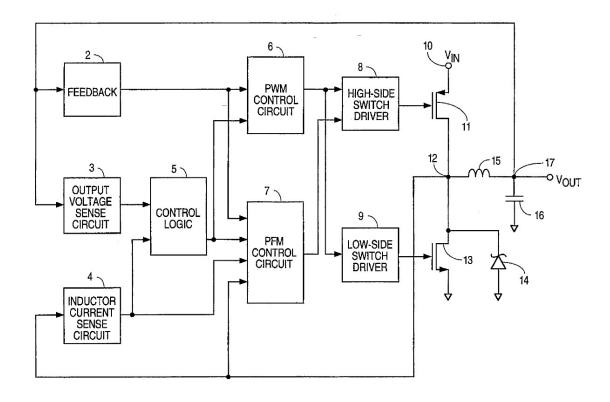

- 74. For example, U.S. Patent No. 5,568,044 ("Bittner") (Ex.1034), teaches a DC-DC converter that uses **Pulse-Width Modulation (PWM)** when supplying high current and **Pulse-Frequency Modulation (PFM)** when supplying low current. In particular, Bittner states that "the present invention achieves high efficiency over a wide range of output currents by automatically switching between PFM mode operation (when the output current is relatively small) and PWM mode operation (when the output current exceeds a predetermined level)." (Ex.1034,

5:57-61.) A block diagram of Bittner's converter is reproduced below.

(Ex.1034, FIG. 1.)

75. In Bittner's regulator, when pMOS transistor 11 (also called a high-side transistor) is switched on, the input voltage  $V_{IN}$  is coupled to node 12. The output voltage  $V_{OUT}$  is supplied from node 12 through inductor 15, which together with capacitor 16 comprises a low-pass filter to minimize the effect of high-frequency switching at node 12 on  $V_{OUT}$ . When operating in PWM mode,  $V_{OUT}$  is fed back through circuit 2 to PWM Control Unit 6, which compares  $V_{OUT}$  to a reference voltage to adjust the duty cycle of transistor 11 by controlling the width of a pulse at its gate; the bigger the voltage difference, the wider the pulse.

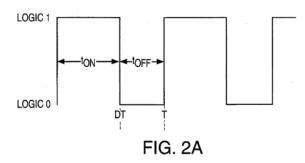

(Ex.1034, FIGS. 2A and 2B.)

- 76. When transistor 11 switches off, PWM Control Unit switches nMOS transistor 13 (also called a low-side transistor) on, which couples node 12 to ground. FIG. 2A, reproduced above, shows the PWM control signal for transistor 11. FIG. 2B, also reproduced above, shows the current through inductor 15, which is rising when transistor 11 is switched on and falling when transistor 13 is switched on. Because the inductor is conducting current throughout the converter's operation (*i.e.*, the inductor's current never goes to zero), PWM mode of operation is characterized as "continuous."

- 77. Every time transistor 11 switches on and off, some energy is

dissipated. When the supply current is high, a relatively large amount of energy is being consumed by the processor, and the energy wasted by switching is relatively small in comparison. However, when the supply current is low, the energy wasted in switching can be comparable or exceed the energy consumed by the processor. Consequently, when the current supplied is low, it is more efficient to switch transistor 11 on less frequently, in a mode called PFM.

- 78. Thus, in PFM operation pulses are skipped except when  $V_{OUT}$  has dropped by a certain margin below the reference voltage. For example, Bittner states: "This method of regulating the  $V_{OUT}$  by preventing switch 11 from turning on when  $V_{OUT}$ , exceeds its nominal value  $V_{OUT,NOM}$  is commonly referred to as "skipping cycles." (Ex.1034, 4:42-45.) Additionally, transistor 13 does not switch on; instead Zener diode 14 can provide a current path to the inductor after transistor 11 switches off. In PFM mode there are periods where the inductor current may drop to zero, and the small amount of current supplied to the processor may only be provided by capacitor 16.

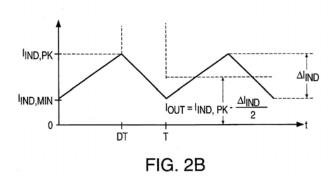

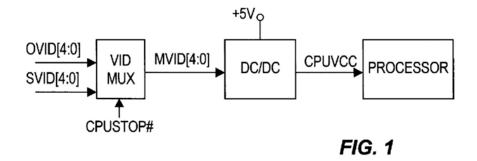

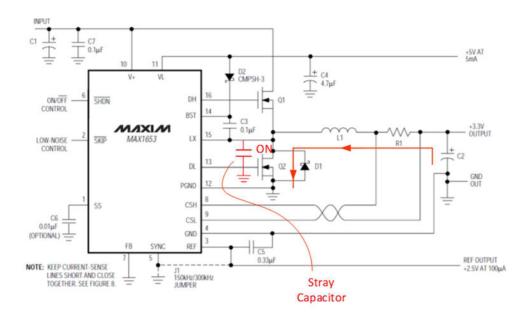

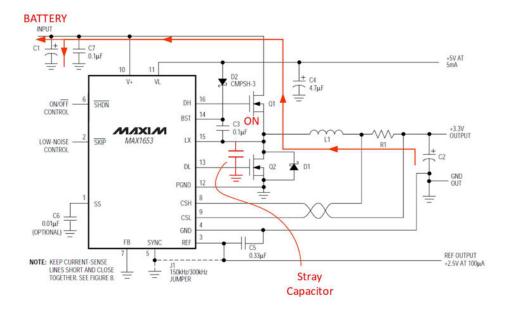

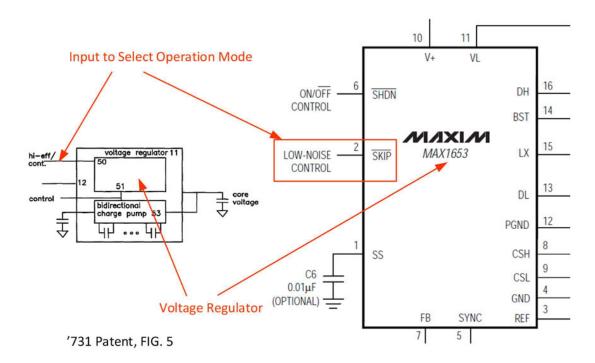

- 79. Maxim developed a DC-DC converter for notebook computer processors, MAX1711, that supported dynamically variable voltage and PWM/PFM modes selected automatically or by asserting a signal (SKIP) to force the PWM mode. (*See generally*, Ex.1035, "MAX1710/MAX1711/MAX1712

High-Speed, Digitally Adjusted Step-Down Controllers for Notebook CPUs," Maxim Integrated Products Datasheet 19-4781, Rev 0, 11/98 ("MAX171X-1998-Datasheet").) The target reference voltage is specified by a 5-bit binary code, which is input to a Digital to Analog Converter (DAC).

(*Id.* at 1.)

80. In particular, MAX171X-1998-Datasheet states that the "MAX1711 is intended for applications where the DAC code may change dynamically." (*Id.*) MAX171X-1998-Datasheet further states:

At light loads, an inherent automatic switchover to PFM takes place. This switchover is effected by a comparator that truncates the low-side switch on-time at the inductor current's zero crossing. This

mechanism causes the threshold between pulse-skipping PFM and nonskipping PWM operation to coincide with the boundary between continuous and discontinuous inductor-current operation.

(*Id.* at 13.)

81. Regarding the forced PWM made, MAX171X-1998-Datasheet states:

The low-noise, forced-PWM mode (SKIP driven high) disables the zero-crossing comparator, which controls the low-side switch on-time. This causes the low-side gatedrive waveform to become the complement of the highside gate-drive waveform. This in turn causes the inductor current to reverse at light loads, as the PWM loop strives to maintain a duty ratio of VOUT/VIN. The benefit of forced-PWM mode is to keep the switching frequency fairly constant, but it comes at a cost: the noload battery current can be as high as 40mA or more. Forced-PWM mode is most useful for reducing audio-frequency noise, improving load-transient response, providing sink-current capability for dynamic output voltage adjustment, and improving the cross-regulation of multiple-output applications that use a flyback transformer or coupled inductor.

(Id. at 14.)

82. In describing the use of the modes based on the load, MAX171X-1998-Datasheet states:

If the minimum load is very light, it may be necessary to assert forced PWM mode (via SKIP) during the transition period to guarantee some

output sink current capability. Otherwise, the output voltage won't ramp downwards until pulled down by external load current.

Using forced PWM mode repeatedly to ensure sink current capability can have side effects, however. The energy taken from the output by the synchronous rectifier isn't lost, but is instead returned to the input. If the frequency of the high-to-low output voltage transition is high enough, efficiency will be degraded by the resistive "friction" losses associated with shuttling energy between input and output capacitors. Also, if the output is being overdriven by an external source (such as an external docking-station power supply), forced PWM mode may cause the battery voltage to become pumped up, possibly overvoltaging the battery.

(*Id.* at 23, col. 1.)

83. Thus, MAX171X-1998-Datasheet teaches that the PWM mode can be forced when the voltage is being dynamically decreased, in particular when the processor load is light (*e.g.*, when the processor's clock is stopped), because the converter does not switch on the high-side transistor (such as Bitnner's transistor 11) in the PFM mode while the output voltage is above the reference voltage. By forcing PWM, the high-side transistor will turn on, sinking energy from capacitor 16 and returning it to the input, thereby decreasing the output voltage to the target reference.

- 84. It should be understood that in general, even though a switching regulator is generally more efficient than a linear regulator, the operation of a switching regulator results in some wasted power, regardless of its mode of operation. In general, less power may be wasted in the operation of the regulator in the PFM mode, due to the reduced switching activity of the high-side and low-side transistors in the PFM mode. Nevertheless, when the load is high, *e.g.*, when the processor receiving regulated voltage from a voltage regulator is in the operating state and is performing computations, it is beneficial to operate the regulator in the PWM mode because the loss of power in the regulator is relatively low compared to the power consumed by the processor, and the PWM mode offers benefits such as less noise and quicker adjustments to the output voltage than the PFM mode.

- 85. When the load is light, *e.g.*, when the processor is in the sleep state and is not performing computations, the CPU power consumption is very low and the power loss in the regulator may become comparable to or may even exceed the power consumption of a CPU in a sleep state. As such, when the load is low, the regulator is typically operated in the PFM, or the so called "high efficiency mode."

- 86. While the observations described above are generally true when the load is stable, *i.e.*, the load is settled at a high value or a low value, **a peculiar**

Declaration of Donald Alpert, Ph.D. in Support of Petition for *Inter Partes* Review of

U.S. Patent No. 7,260,731

from a high value to low value, e.g., in response to a change in the load condition from a high load to a light load. In this case, the output capacitor of the regulator already has some charge stored therein, corresponding to the high output voltage that was supplied before the transition to the low voltage commenced. The regulator cannot supply the required low voltage until this stored charged is removed from the output capacitor.

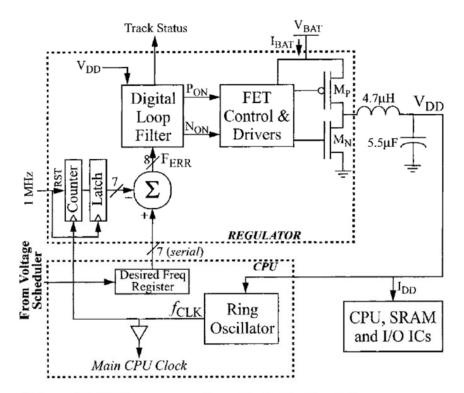

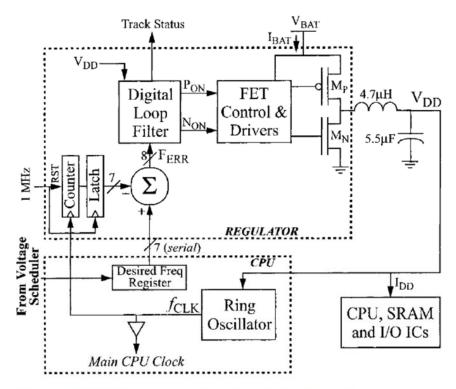

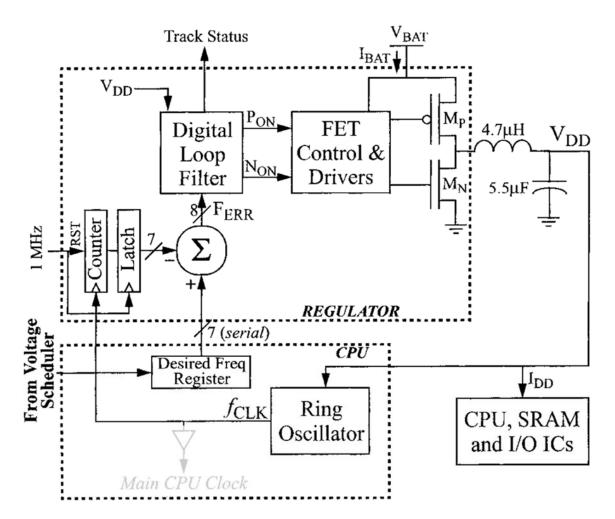

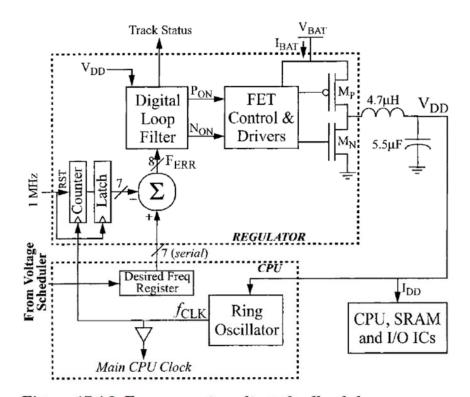

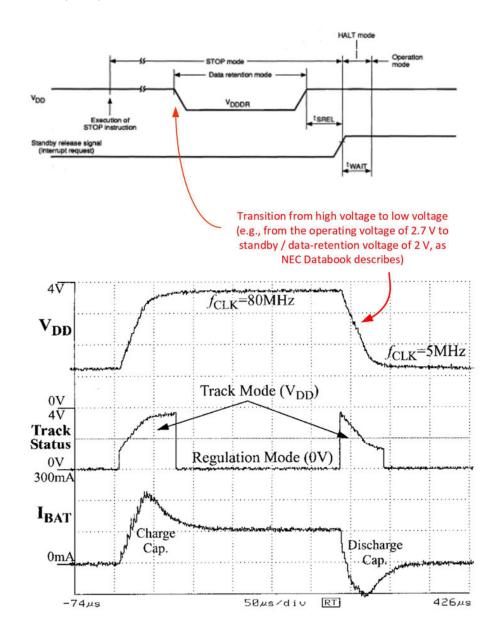

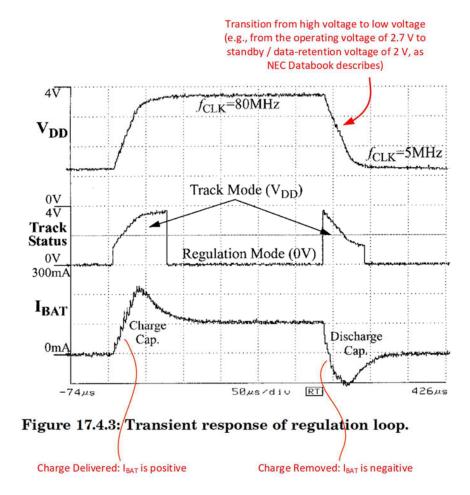

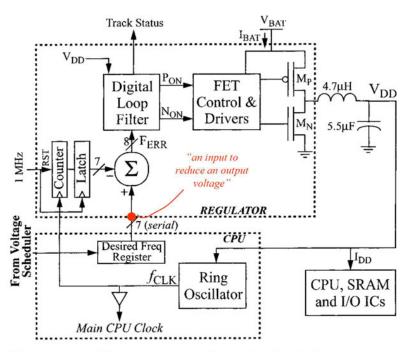

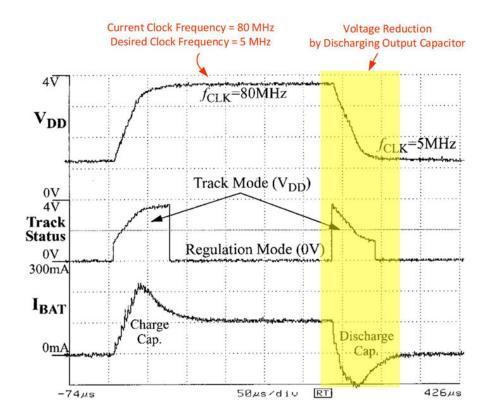

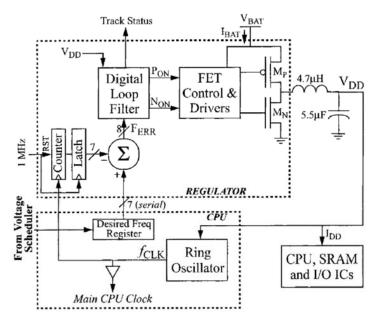

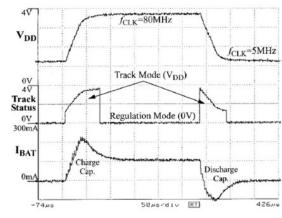

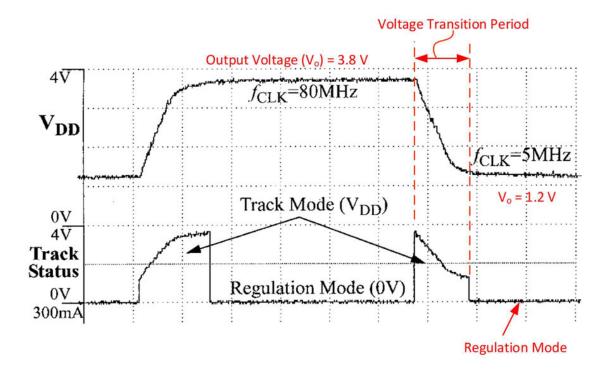

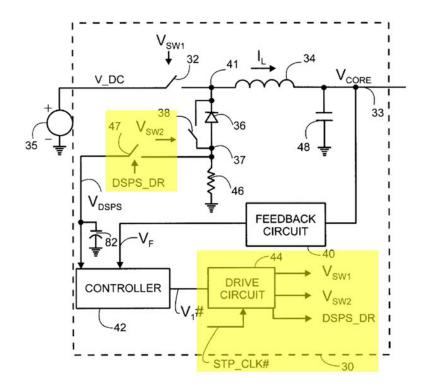

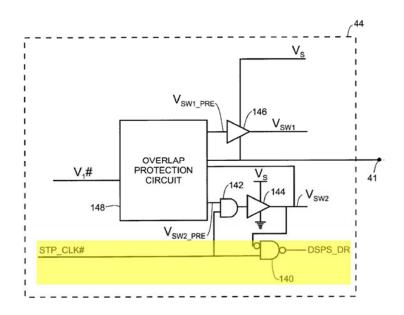

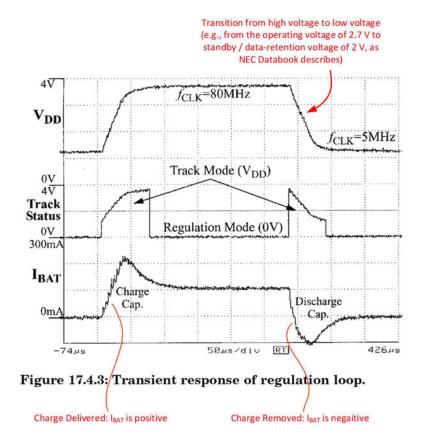

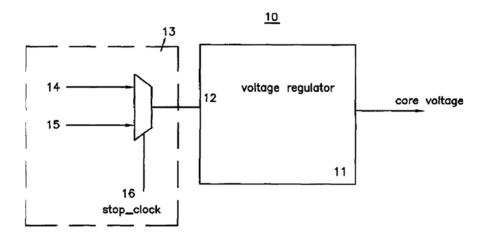

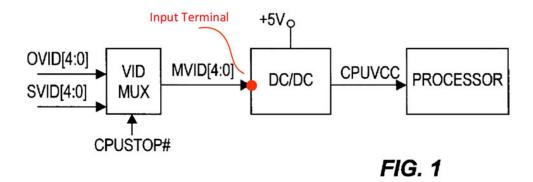

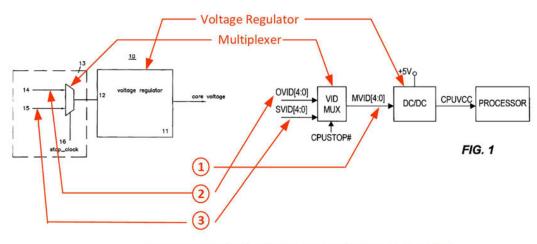

- 87. The charge from the output capacitor can be removed in two ways: either by dissipating it in the load (which may be light) or, it can be transferred to some other circuitry for storage. Dissipation of the charge in the load results in a waste of power while transferring (also called shuttling) of the charge avoids such waste, resulting in power saving. (See Ex.1035 at 23, (stating that "energy taken from the output by the synchronous rectifier isn't lost, but is instead returned to the input"); Ex.1006 at 2 (Figure 17.4.3 (depicting that the tracking mode is initiated only when the voltage is transitioning)); 1, col. 2 (describing that in the tracking mode "the converter either delivers or removes charge from the capacitor" and that in the regulation mode "only the processor circuits can remove charge").)

- 88. Shuttling the charge has an added benefit of faster voltage transition because when the load is light, dissipation of the charge in the load can take longer

Declaration of Donald Alpert, Ph.D. in Support of Petition for *Inter Partes* Review of

U.S. Patent No. 7,260,731

than the time required for shuttling. (Ex.1035 at 12 (describing that unless the PWM mode is forced, "the output voltage won't ramp downwards until pulled down by external load current"); Ex.1012 at 3, col. 2-4, col. 1 (stating that "fast [voltage] transition timing means that the regulator circuit must sink as well as source current" and that is can be accomplished by forcing "PWM mode only during [voltage] transitions").)

89. Thus, these prior art references teach that although the PFM mode is generally more efficient when the output voltage has settled to a low value, e.g., when the load is light, during the time when the voltage is changing, *e.g.*, from a high value to a low value, it is the otherwise less efficient PWM mode that can save power by shuttling the charge stored at the output capacitor to the input capacitor or the battery, and the "efficient" PFM mode can result in waste of power.

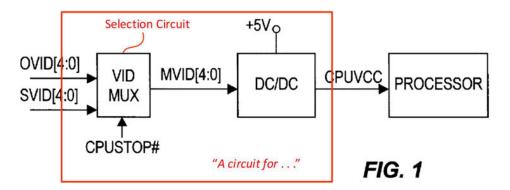

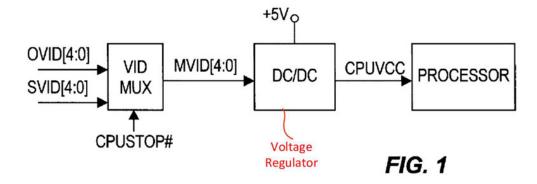

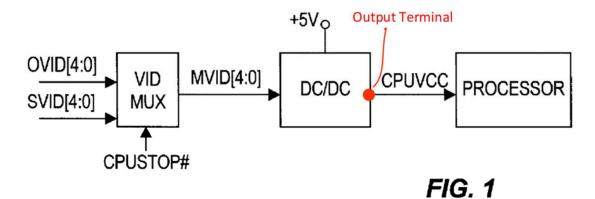

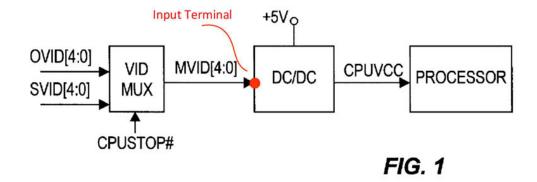

#### V. THE '731 PATENT

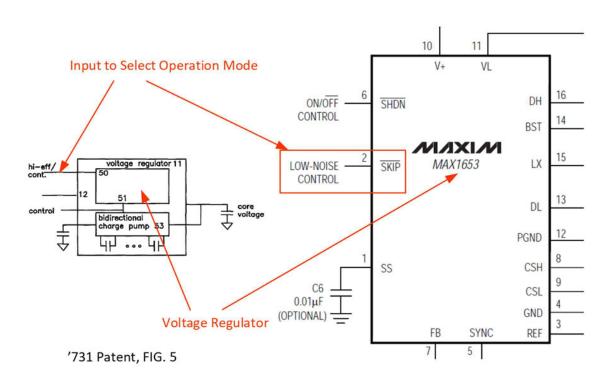

#### A. Overview of the '731 patent

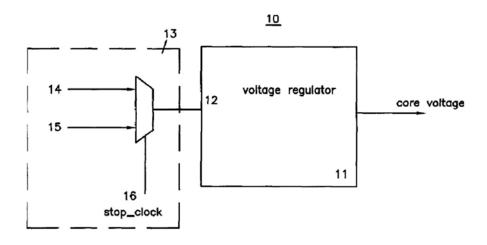

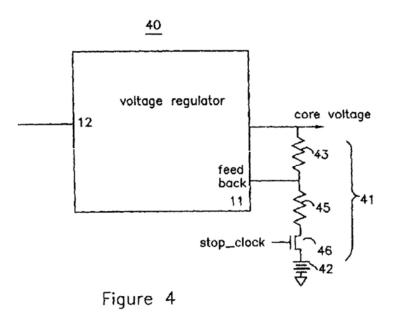

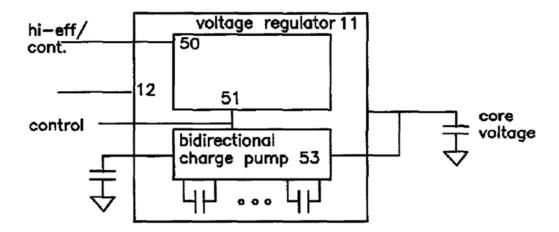

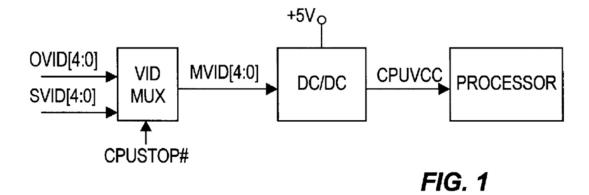

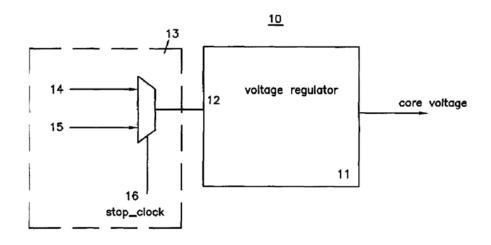

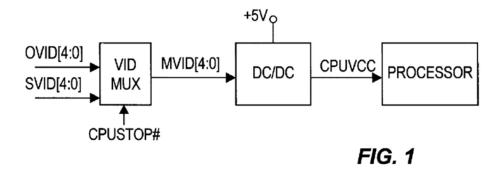

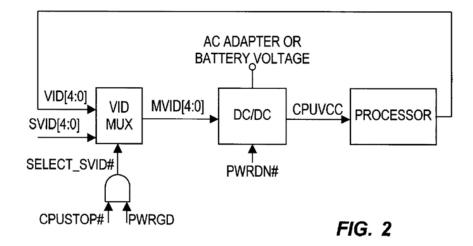

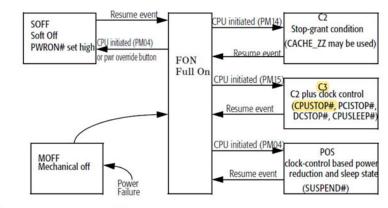

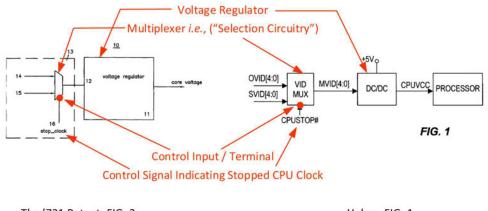

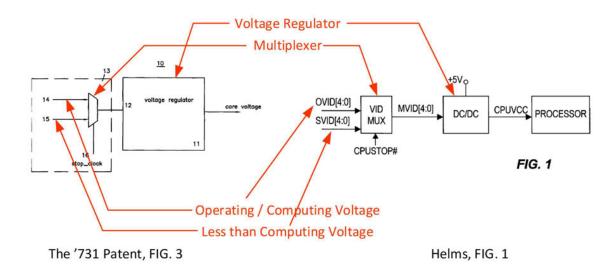

90. The '731 patent is directed, in part, to decreasing the static power consumption of a processor (when the system/processor clock is disabled) by reducing its core voltage. For example, the Abstract of the '731 patent states: "A method for reducing power utilized by a processor" includes "reducing core

voltage to the processor to a value sufficient to maintain state during the mode in which system clock is disabled." (Ex.1001, Abstract.) Since the system or processor clock is stopped, the processor's dynamic power consumption is zero. By decreasing the core voltage, static power consumption can also be reduced.

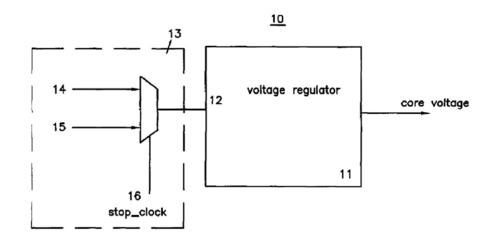

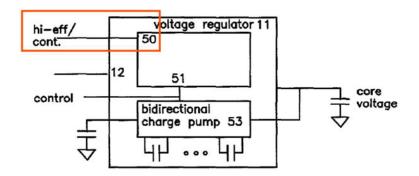

### 91. For instance, the '731 patent states:

When system clocks for a processor are disabled, the processor must remain in a state (sometimes called "deep sleep") in which it is capable of rapidly responding to interrupts. Such a state requires the application of core voltage to the various circuits. The application of this voltage generates a power dissipation referred to in this specification as "**static power**" usage because the processor is in its static state in which clocks are disabled.

(Id., 1:50-58.) (emphasis added)<sup>3</sup>.

## 92. The '731 patent further states: