# 10-Bit, 105 MSPS/125 MSPS/150 MSPS, 1.8 V Dual Analog-to-Digital Converter

AD9600

#### **FEATURES**

SNR = 60.6 dBc (61.6 dBFS) to 70 MHz at 150 MSPS SFDR = 81 dBc to 70 MHz at 150 MSPS Low power: 825 mW at 150 MSPS 1.8 V analog supply operation 1.8 V to 3.3 V CMOS output supply or 1.8 V LVDS supply Integer 1 to 8 input clock divider Intermediate frequency (IF) sampling frequencies up to 450 MHz Internal analog-to-digital converter (ADC) voltage reference **Integrated ADC sample-and-hold inputs** Flexible analog input: 1 V p-p to 2 V p-p range Differential analog inputs with 650 MHz bandwidth ADC clock duty cycle stabilizer 95 dB channel isolation/crosstalk **Serial port control** User-configurable built-in self-test (BIST) capability **Energy-saving power-down modes** Integrated receive features

#### **APPLICATIONS**

Fast detect/threshold bits

Composite signal monitor

Point-to-point radio receivers (GPSK, QAM) Diversity radio systems I/Q demodulation systems

Smart antenna systems

Digital predistortion

General-purpose software radios

Broadband data applications

Data acquisition

Nondestructive testing

#### **PRODUCT HIGHLIGHTS**

- 1. Integrated dual, 10-bit, 150 MSPS/125 MSPS/105 MSPS ADC.

- 2. Fast overrange detect and signal monitor with serial output.

- 3. Signal monitor block with dedicated serial output mode.

- 4. Proprietary differential input maintains excellent SNR performance for input frequencies up to 450 MHz.

- 5. The AD9600 operates from a single 1.8 V supply and features a separate digital output driver supply to accommodate 1.8 V to 3.3 V logic families.

- A standard serial port interface supports various product features and functions, such as data formatting (offset binary, twos complement, or gray coding), enabling the clock DCS, power-down mode, and voltage reference mode.

- 7. The AD9600 is pin compatible with the AD9627-11, AD9627, and AD9640, allowing a simple migration from 10 bits to 11 bits, 12 bits, or 14 bits.

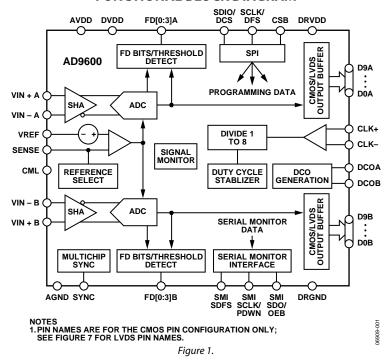

#### **FUNCTIONAL BLOCK DIAGRAM**

Rev. B Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

# AD9600

## **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| Product Highlights                          | 1  |

| Functional Block Diagram                    | 1  |

| Revision History                            | 3  |

| General Description                         | 4  |

| Specifications                              | 5  |

| DC Specifications                           | 5  |

| AC Specifications                           | 6  |

| Digital Specifications                      | 7  |

| Switching Specifications                    | 9  |

| Timing Characteristics                      | 10 |

| Timing Diagrams                             | 10 |

| Absolute Maximum Ratings                    | 12 |

| Thermal Characteristics                     | 12 |

| ESD Caution                                 | 12 |

| Pin Configuration and Function Descriptions | 13 |

| Equivalent Circuits                         | 17 |

| Typical Performance Characteristics         | 18 |

| Theory of Operation                         | 23 |

| ADC Architecture                            | 23 |

| Analog Input Considerations                 | 23 |

| Voltage Reference                           | 25 |

| Clock Input Considerations                  | 26 |

| Power Dissipation and Standby Mode          | 28 |

| Digital Outputs                             | 28 |

| Timing                                      | 29 |

| ADC Overrange and Gain Control              | 30 |

| Fast Detect Overview                        | 30 |

| ADC Fast Magnitude                          | 30 |

| ADC Overrange (OR)                          |    |

| Gain Switching                              |    |

| Signal Monitor                              |    |

| reak Detector Mode                              | ٦. |

|-------------------------------------------------|----|

| RMS/MS Magnitude Mode                           | 33 |

| Threshold Crossing Mode                         | 34 |

| Additional Control Bits                         | 34 |

| DC Correction                                   | 35 |

| Signal Monitor SPORT Output                     | 35 |

| Built-In Self-Test (BIST) and Output Test       | 36 |

| Built-In Self-Test (BIST)                       | 36 |

| Output Test Modes                               | 36 |

| Channel/Chip Synchronization                    | 37 |

| Serial Port Interface (SPI)                     | 38 |

| Configuration Using the SPI                     | 38 |

| Hardware Interface                              | 38 |

| Configuration Without the SPI                   | 39 |

| SPI Accessible Features                         | 39 |

| Memory Map                                      | 4( |

| Reading the Memory Map Table                    | 4( |

| Memory Map                                      | 41 |

| Memory Map Register Description                 | 44 |

| Applications Information                        | 47 |

| Design Guidelines                               | 47 |

| Evaluation Board                                | 48 |

| Power Supplies                                  | 48 |

| Input Signals                                   | 48 |

| Output Signals                                  | 48 |

| Default Operation and Jumper Selection Settings | 49 |

| Alternative Clock Configurations                | 49 |

| Alternative Analog Input Drive Configuration    | 5( |

| Schematics                                      | 51 |

| Evaluation Board Layouts                        | 61 |

| Bill of Materials                               | 69 |

| Outline Dimensions                              | 71 |

| Ordering Guide                                  | 72 |

# AD9600

### **REVISION HISTORY**

| 12 | /09   | Rev.   | Α                      | to | Rev.   | F |

|----|-------|--------|------------------------|----|--------|---|

| 14 | / V / | -KC V. | $\boldsymbol{\Lambda}$ | w  | IXC V. |   |

| Added new models to Specifications Section     |    |

|------------------------------------------------|----|

| Changes to Table 7                             | 12 |

| Updated Outline Dimensions                     | 71 |

| Changes to Ordering Guide                      | 72 |

| 6/09—Rev. 0 to Rev. A                          |    |

| Changes to Specifications Section              | 4  |

| Changes to Figure 3                            | 10 |

| Changes to Figure 11, Figure 12, and Figure 14 | 16 |

| Changes to Table 12                            | 28 |

| Changes to Configuration Using the SPI Section      | 37 |

|-----------------------------------------------------|----|

| Changes to Table 22                                 | 40 |

| Changes to Signal Monitor Period (Register 0x113 to |    |

| Register 0x115) Section                             | 45 |

| Added Exposed Pad Notation to Outline Dimensions    | 70 |

| -                                                   |    |

11/07—Revision 0: Initial Version

## AD9600

### **GENERAL DESCRIPTION**

The AD9600 is a dual, 10-bit, 105 MSPS/125 MSPS/150 MSPS ADC. It is designed to support communications applications where low cost, small size, and versatility are desired.

The dual ADC core features a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth, differential sample-and-hold analog input amplifiers supporting a variety of user-selectable input ranges. An integrated voltage reference eases design considerations. A duty cycle stabilizer is provided to compensate for variations in the ADC clock duty cycle, allowing the converters to maintain excellent performance.

The AD9600 has several functions that simplify the automated gain control (AGC) function in a communications receiver. For example, the fast detect feature allows fast overrange detection by outputting four bits of input level information with very short latency.

In addition, the programmable threshold detector allows monitoring the amplitude of the incoming signal with short latency, using the four fast detect bits of the ADC. If the input signal level exceeds the programmable threshold, the fine upper threshold indicator goes high. Because this threshold is set from the four MSBs, the user can quickly adjust the system gain to avoid an overrange condition.

Another AGC-related function of the AD9600 is the signal monitor. This block allows the user to monitor the composite magnitude of the incoming signal, which aids in setting the gain to optimize the dynamic range of the overall system.

The ADC output data can be routed directly to the two external 10-bit output ports. These outputs can be set from 1.8 V to 3.3 V CMOS or 1.8 V LVDS. In addition, flexible power-down options allow significant power savings.

## **SPECIFICATIONS**

#### **DC SPECIFICATIONS**

AVDD = 1.8 V, DVDD = 1.8 V, DRVDD = 3.3 V, maximum sample rate, VIN = -1.0 dBFS differential input, 1.0 V internal reference, DCS enabled, fast detect output pins disabled, signal monitor disabled, unless otherwise noted.

Table 1.

|                                                        |       | AD9600ABCPZ-105/<br>AD9600BCPZ-105 |          | AD9600ABCPZ-125/<br>AD9600BCPZ-125 |      |           | AD9600ABCPZ-150/<br>AD9600BCPZ-150 |      |           |      |         |

|--------------------------------------------------------|-------|------------------------------------|----------|------------------------------------|------|-----------|------------------------------------|------|-----------|------|---------|

| Parameter                                              | Temp  | Min                                | Тур      | Max                                | Min  | Тур       | Max                                | Min  | Тур       | Max  | Unit    |

| RESOLUTION                                             | Full  | 10                                 |          |                                    | 10   |           |                                    | 10   |           |      | Bits    |

| ACCURACY                                               |       |                                    |          |                                    |      |           |                                    |      |           |      |         |

| No Missing Codes                                       | Full  |                                    | Guarante | eed                                |      | Guarant   | eed                                |      | Guarant   | eed  |         |

| Offset Error                                           | Full  |                                    | ±0.3     | ±0.7                               |      | ±0.3      | ±0.7                               |      | ±0.3      | ±0.7 | % FSR   |

| Gain Error                                             | Full  | -3.6                               | -2.2     | -1.0                               | -4.0 | -2.5      | -1.3                               | -4.3 | -3.0      | -1.6 | % FSR   |

| Differential Nonlinearity (DNL) <sup>1</sup>           | Full  |                                    |          | ±0.2                               |      |           | ±0.2                               |      |           | ±0.2 | LSB     |

|                                                        | 25°C  |                                    | ±0.1     |                                    |      | ±0.1      |                                    |      | ±0.1      |      | LSB     |

| Integral Nonlinearity (INL) <sup>1</sup>               | Full  |                                    |          | ±0.3                               |      |           | ±0.3                               |      |           | ±0.4 | LSB     |

| , , ,                                                  | 25°C  |                                    | ±0.1     |                                    |      | ±0.1      |                                    |      | ±0.1      |      | LSB     |

| MATCHING CHARACTERISTICS                               |       |                                    |          |                                    |      |           |                                    |      |           |      |         |

| Offset Error                                           | Full  |                                    | ±0.3     | ±0.7                               |      | ±0.3      | ±0.7                               |      | ±0.2      | ±0.7 | % FSR   |

| Gain Error                                             | Full  |                                    | ±0.2     | ±0.8                               |      | ±0.3      | ±0.8                               |      | ±0.2      | ±0.8 | % FSR   |

| TEMPERATURE DRIFT                                      |       |                                    |          |                                    |      |           |                                    |      |           |      |         |

| Offset Error                                           | Full  |                                    | ±15      |                                    |      | ±15       |                                    |      | ±15       |      | ppm/°C  |

| Gain Error                                             | Full  |                                    | ±95      |                                    |      | ±95       |                                    |      | ±95       |      | ppm/°C  |

| INTERNAL VOLTAGE REFERENCE                             |       |                                    |          |                                    |      |           |                                    |      |           |      | PP      |

| Output Voltage Error (1 V Mode)                        | Full  |                                    | ±5       | ±16                                |      | ±5        | ±16                                |      | ±5        | ±16  | mV      |

| Load Regulation @ 1.0 mA                               | Full  |                                    | 7        |                                    |      | 7         |                                    |      | 7         |      | mV      |

| INPUT-REFERRED NOISE                                   |       |                                    | •        |                                    |      | •         |                                    | 1    | •         |      |         |

| VREF = 1.0 V                                           | 25°C  |                                    | 0.1      |                                    |      | 0.1       |                                    |      | 0.1       |      | LSB rms |

| ANALOG INPUT                                           |       |                                    | •••      |                                    |      |           |                                    | 1    |           |      | 200     |

| Input Span, VREF = 1.0 V                               | Full  |                                    | 2        |                                    |      | 2         |                                    |      | 2         |      | V p-p   |

| Input Capacitance <sup>2</sup>                         | Full  |                                    | 8        |                                    |      | 8         |                                    |      | 8         |      | pF      |

| VREF INPUT RESISTANCE                                  | Full  |                                    | 6        |                                    |      | 6         |                                    |      | 6         |      | kΩ      |

| POWER SUPPLIES                                         |       |                                    |          |                                    |      |           |                                    |      |           |      | 11.22   |

| Supply Voltage                                         |       |                                    |          |                                    |      |           |                                    |      |           |      |         |

| AVDD, DVDD                                             | Full  | 1.7                                | 1.8      | 1.9                                | 1.7  | 1.8       | 1.9                                | 1.7  | 1.8       | 1.9  | V       |

| DRVDD (CMOS Mode)                                      | Full  | 1.7                                | 3.3      | 3.6                                | 1.7  | 3.3       | 3.6                                | 1.7  | 3.3       | 3.6  | V       |

| Supply Current                                         | l dii | 1.,                                | 3.3      | 3.0                                | '''  | 3.3       | 5.0                                | 1.7  | 3.3       | 3.0  | *       |

| I <sub>AVDD</sub> <sup>1</sup>                         | Full  |                                    | 310      |                                    |      | 385       |                                    |      | 419       |      | mA      |

| I <sub>DVDD</sub> <sup>1</sup>                         | Full  |                                    | 34       |                                    |      | 42        |                                    |      | 50        |      | mA      |

| I <sub>AVDD</sub> and I <sub>DVDD</sub> <sup>1,3</sup> | 1 411 |                                    | 34       | 365                                |      | 72        | 455                                |      | 50        | 495  | 111/4   |

| I <sub>DRVDD</sub> (3.3 V CMOS)                        | Full  |                                    | 35       | 303                                |      | 36        | 455                                |      | 42        | 493  | mA      |

| I <sub>DRVDD</sub> (3.3 V CMOS)                        | Full  |                                    | 33<br>15 |                                    |      | 30<br>18  |                                    |      | 22        |      | mA      |

|                                                        | Full  |                                    | 15<br>42 |                                    |      |           |                                    |      | 22<br>46  |      |         |

| I <sub>DRVDD</sub> (1.8 V LVDS)                        |       |                                    | 42       |                                    |      | 44        |                                    | +    | 40        |      | mA      |

| POWER CONSUMPTION DC Input                             | Full  |                                    | 600      | 650                                |      | 750       | 900                                |      | 025       | 890  | mW      |

| •                                                      | Full  |                                    | 600      | 050                                |      | 750       | 800                                |      | 825       | 890  | TTIVV   |

| Sine Wave Input <sup>1</sup>                           | F     |                                    | 615      |                                    |      | 012       |                                    |      | 003       |      | ma\A/   |

| DRVDD = 1.8 V                                          | Full  |                                    | 645      |                                    |      | 813       |                                    |      | 892       |      | mW      |

| DRVDD = 3.3 V                                          | Full  |                                    | 740      |                                    |      | 900       |                                    |      | 990       |      | mW      |

| Standby Power <sup>3</sup>                             | Full  |                                    | 68       | _                                  |      | 77<br>2.5 |                                    |      | 77<br>2.5 | _    | mW      |

| Power-Down Power                                       | Full  |                                    | 2.5      | 6                                  |      | 2.5       | 6                                  | 1    | 2.5       | 6    | mW      |

<sup>&</sup>lt;sup>1</sup> Measured with a low input frequency, full-scale sine wave, with approximately 5 pF loading on each output bit. <sup>2</sup> Input capacitance refers to the effective capacitance between one differential input pin and AGND. Refer to Figure 8 for the equivalent analog input structure. <sup>3</sup> Standby power is measured with a dc input and the CLK+ and CLK- pins inactive )set to AVDD or AGND.

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

#### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.