## IN THE UNITED STATES DISTRICT COURT FOR THE DISTRICT OF DELAWARE

| MONTEREY RESEARCH, LLC,          | ) |     |

|----------------------------------|---|-----|

| Plaintiff,                       | ) |     |

|                                  | ) | C.A |

| V.                               | ) |     |

|                                  | ) | JUF |

| QUALCOMM INCORPORATED,           | ) |     |

| QUALCOMM TECHNOLOGIES, INC., and | ) |     |

| QUALCOMM CDMA TECHNOLOGIES       | ) |     |

| ASIA-PACIFIC PTE LTD.,           | ) |     |

|                                  |   |     |

C.A. No. 19-cv-2083-CFC

JURY TRIAL DEMANDED

Defendants.

### FIRST AMENDED COMPLAINT FOR PATENT INFRINGEMENT

Plaintiff Monterey Research, LLC ("Monterey"), for its First Amended Complaint for Patent Infringement against Defendants Qualcomm Incorporated ("Qualcomm Inc."), Qualcomm Technologies, Inc. ("QTI"), and Qualcomm CDMA Technologies Asia-Pacific Pte Ltd. ("QCTAP") (collectively, "Qualcomm" or "Qualcomm Defendants") alleges as follows:

#### **INTRODUCTION**

1. Monterey is an intellectual property and technology licensing company. Monterey's patent portfolio comprises over 2,700 active and pending patents worldwide, including approximately 2,000 active United States patents. Monterey's patent portfolio stems from technology developed from a number of leading high-technology companies, including Cypress Semiconductor Corporation, Advanced Micro Devices, Fujitsu, NVX Corporation, Ramtron, and Spansion. Those companies developed key innovations that have greatly enhanced the capabilities of computer systems, increased electronic device processing power, and reduced electronic device power consumption. Among other things, those inventions produced significant technological advances, including smaller, faster, and more efficient semiconductors and integrated circuits. 2. The Qualcomm Defendants, jointly and severally, have infringed and continue to infringe Monterey's patents. Moreover, despite Monterey notifying them of infringement, the Qualcomm Defendants have thus far refused to license those patents and, instead, have continued to make, use, sell, offer to sell, and/or import Monterey's intellectual property within the United States without Monterey's permission.

#### NATURE OF THE CASE

3. This action arises under 35 U.S.C. § 271 for Qualcomm's infringement of Monterey's United States Patent Nos. 6,459,625 ("the '625 patent"); 6,534,805 ("the '805 patent"); 6,642,573 ("the '573 patent"); 6,651,134 ("the '134 patent"); 6,680,516 ("the '516 patent"); 6,765,407 ("the '407 patent"); 7,572,727 ("the '727 patent"); and 7,977,797 ("the '797 patent") (collectively, "the Patents-in-Suit").

## THE PARTIES

4. Plaintiff Monterey is a Delaware limited liability company with offices in New Jersey and California. Monterey maintains a registered agent for service in Delaware: Intertrust Corporate Services Delaware Ltd. located at 200 Bellevue Parkway, Suite 210, Wilmington, Delaware 19808.

5. Defendant Qualcomm Inc. is a Delaware corporation with a principal place of business at 5775 Morehouse Dr., San Diego, California, 92121. Qualcomm Inc. is a publicly traded company and is the parent corporation of defendants QTI and QCTAP. Qualcomm Inc. may be served through its registered agent for service, The Prentice-Hall Corporation System, Inc., 251 Little Falls Drive, Wilmington, Delaware 19808.

6. Defendant QTI is a Delaware corporation with a principal place of business at 5775 Morehouse Dr., San Diego, California, 92121. QTI is a wholly-owned subsidiary of Qualcomm Inc. Qualcomm Inc.'s semiconductor research and engineering business is conducted wholly or

in part through the actions of QTI. Qualcomm Inc. controls and directs the actions of QTI, and therefore both directs QTI to infringe and itself infringes Monterey's patents. QTI may be served through its registered agent for service, Corporation Service Company, 251 Little Falls Drive, Wilmington, Delaware 19808.

7. Defendant QCTAP is a corporation organized under the laws of Singapore, with corporate offices at 6 Serangoon North Avenue 5, #03-04, Singapore 554910, Singapore. Defendant QCTAP is a wholly-owned subsidiary of Qualcomm Inc. QCTAP is responsible, among other things, for accepting orders and sending invoices to certain customers in the United States for Qualcomm products.

8. Qualcomm Inc. exercises control over QTI and QCTAP, and acts collectively with QTI and QCTAP to infringe Monterey's patents by making, using, selling, offering for sale, and/or importing products (including importing products made by a patented process) throughout the United States, including within this District. Qualcomm's customers incorporate those products into downstream products that are made, used, sold, offered for sale, and/or imported throughout the United States, including within this District. Those downstream products include, but are not limited to, smartphones, tablets, televisions, smartwatches, and other products that include Qualcomm semiconductor devices and integrated circuits.

## JURISDICTION AND VENUE

9. This Court has jurisdiction over the subject matter of this action under 28 U.S.C. §§ 1331 and 1338(a) at least because this action arises under the patent laws of the United States, including 35 U.S.C. § 271 *et seq*.

10. Personal jurisdiction exists over each Qualcomm Defendant.

11. Personal jurisdiction exists over Qualcomm Inc. and QTI at least because each is a Delaware corporation organized under the laws of the State of Delaware. Each also has a

registered agent for service of process in Delaware. In addition, Qualcomm Inc. and QTI have each committed, aided, abetted, contributed to and/or participated in the commission of acts of infringement giving rise to this action within the State of Delaware by, *inter alia*, directly and/or indirectly making, using, selling, offering for sale, importing products and/or practicing methods that practice one or more claims of the Patents-in-Suit. Furthermore, Qualcomm Inc. and QTI have transacted and conducted business in the State of Delaware and with Delaware residents by making, using, selling, offering to sell, and/or importing (including importing products made by a patented process) products and instrumentalities that practice one or more claims of the Patentsin-Suit. Among other things, Qualcomm Inc. and QTI, directly and/or through intermediaries, use, sell, ship, distribute, import into, offer for sale, and/or advertise or otherwise promote their products throughout the United States, including in the State of Delaware. *See, e.g.*, www.qualcomm.com. At least for those reasons, Qualcomm Inc. and QTI have the requisite minimum contacts within the forum such that the exercise of jurisdiction over Qualcomm Inc. and QTI would not offend traditional notions of fair play and substantial justice.

12. Personal jurisdiction exists over QCTAP at least because it has committed, aided, abetted, contributed to and/or participated in the commission of acts of infringement giving rise to this action within the State of Delaware by, *inter alia*, directly and/or indirectly making, using, selling, offering for sale, importing products and/or practicing methods that practice one or more claims of the Patents-in-Suit. Furthermore, QCTAP transacted and conducted business in the State of Delaware and with Delaware residents with respect to the products and instrumentalities accused of infringing the Patents-in-Suit. Among other things, QCTAP, directly and/or through intermediaries, uses, sells, ships, distributes, imports into, offers for sale, and/or advertises or otherwise promotes its products throughout the United States, including in the State of Delaware.

#### Case 1:19-cv-02083-CFC Document 16 Filed 02/14/20 Page 5 of 51 PageID #: 263

*See, e.g.*, www.qualcomm.com. For example, QCTAP develops products for sale in the United States, including in the State of Delaware, and tests and verifies products developed in the United States before selling them in the United States, including in the State of Delaware. *See, e.g.*, https://www.qualcomm.com/news/releases/2008/10/30/qualcomm-opens-asia-pacific-test-center-excellence-singapore. As an additional example, QCTAP contracts with and is responsible for accepting orders and sending invoices to customers in the United States. *See, e.g.*, *Tessera Inc. v. Motorola, Inc. et al*, No. 12-cv-692, slip op. at 3 (N.D. Ca. Aug. 7, 2013). At least for those reasons, QCTAP has the requisite minimum contacts within the forum such that the exercise of jurisdiction over QCTAP would not offend traditional notions of fair play and substantial justice.

13. Venue is proper in this Court pursuant to 28 U.S.C. §§ 1391(b) and (c) and 1400(b). Qualcomm Inc. and QTI reside in this district and have committed acts of infringement in this district. Venue is proper with respect to QCTAP at least because QCTAP is a foreign corporation, has committed acts of infringement in this district, and venue is proper in any district in which QCTAP is subject to personal jurisdiction. Venue is further proper based on the facts alleged in the preceding paragraphs, which Monterey incorporates by reference as if fully set forth herein.

#### THE PATENTS-IN-SUIT

14. Monterey incorporates by reference the preceding paragraphs as if fully set forth herein.

#### A. <u>U.S. Patent No. 6,459,625</u>

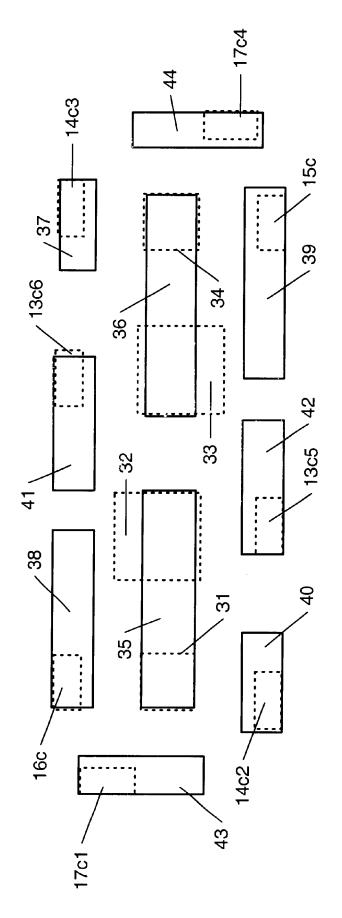

15. The '625 patent, titled "Three Metal Process for Optimizing Layout Density," was duly and properly issued by the USPTO on October 1, 2002. A true and correct copy of the '625 patent is attached hereto as Exhibit A.

16. Monterey is the owner and assignee of the '625 patent; owns all right, title, and interest in the '625 patent; and holds the right to sue for and recover damages for infringement

thereof, including past infringement.

## B. <u>U.S. Patent No. 6,534,805</u>

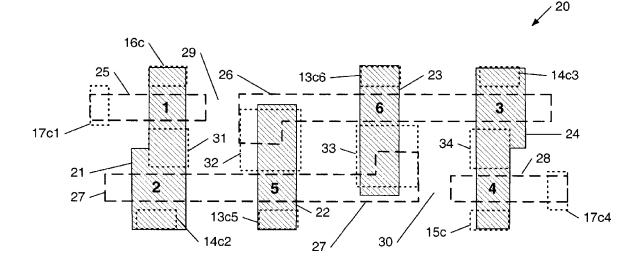

17. The '805 patent, titled "SRAM Cell Design," was duly and properly issued by the USPTO on March 18, 2003. On October 14, 2014, the USPTO issued an Ex Parte Reexamination Certificate for the '805 patent, which confirmed the patentability of the '805 patent. A true and correct copy of the '805 patent and the Ex Parte Reexamination Certificate for the '805 patent and the Ex Parte Reexamination Certificate for the '805 patent and the Ex Parte Reexamination Certificate for the '805 patent and the Ex Parte Reexamination Certificate for the '805 patent and the Ex Parte Reexamination Certificate for the '805 patent is attached hereto as Exhibit B.

18. Monterey is the owner and assignee of the '805 patent; owns all right, title, and interest in the '805 patent; and holds the right to sue and recover damages for infringement thereof, including past infringement.

# C. <u>U.S. Patent No. 6,642,573</u>

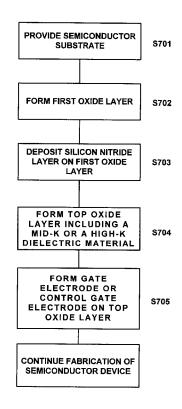

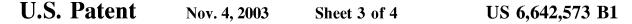

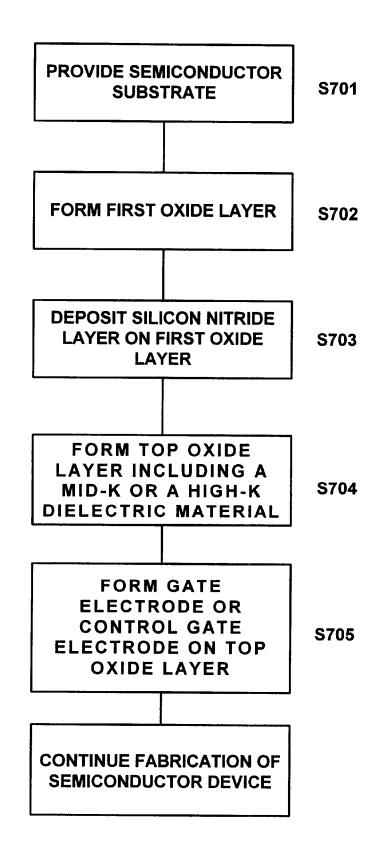

The '573 patent, titled "Use of High-K Dielectric Material in Modified ONO

Structure for Semiconductor Devices," was duly and properly issued by the USPTO on November

4, 2003. A true and correct copy of the '573 patent is attached hereto as Exhibit C.

20. Monterey is the owner and assignee of the '573 patent; owns all right, title, and interest in the '573 patent; and holds the right to sue and recover damages for infringement thereof, including past infringement.

# D. <u>U.S. Patent No. 6,651,134</u>

21. The '134 patent, titled "Memory Device with Fixed Length Non Interruptible Burst," was duly and properly issued by the USPTO on November 18, 2003. A true and correct copy of the '134 patent is attached hereto as Exhibit D.

22. Monterey is the owner and assignee of the '134 patent; owns all right, title, and interest in the '134 patent; and holds the right to sue and recover damages for infringement thereof, including past infringement.

## E. <u>U.S. Patent No. 6,680,516</u>

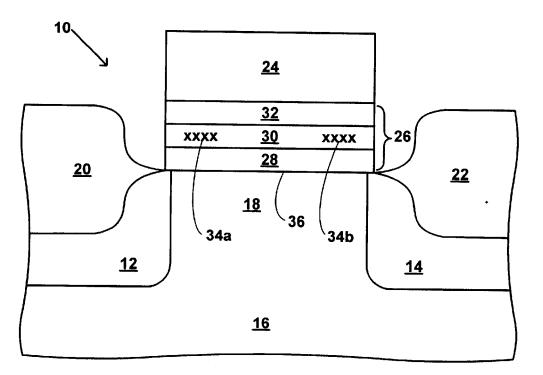

23. The '516 patent, titled "Controlled Thickness Gate Stack," was duly and properly issued by the United States Patent and Trademark Office ("USPTO") on January 20, 2004. On December 12, 2006, the USPTO issued a Certificate of Correction for the '516 patent. A true and correct copy of the '516 patent and the Certificate of Correction is attached hereto as Exhibit E.

24. Monterey is the owner and assignee of the '516 patent; owns all right, title, and interest in the '516 patent; and holds the right to sue and recover damages for infringement thereof, including past infringement.

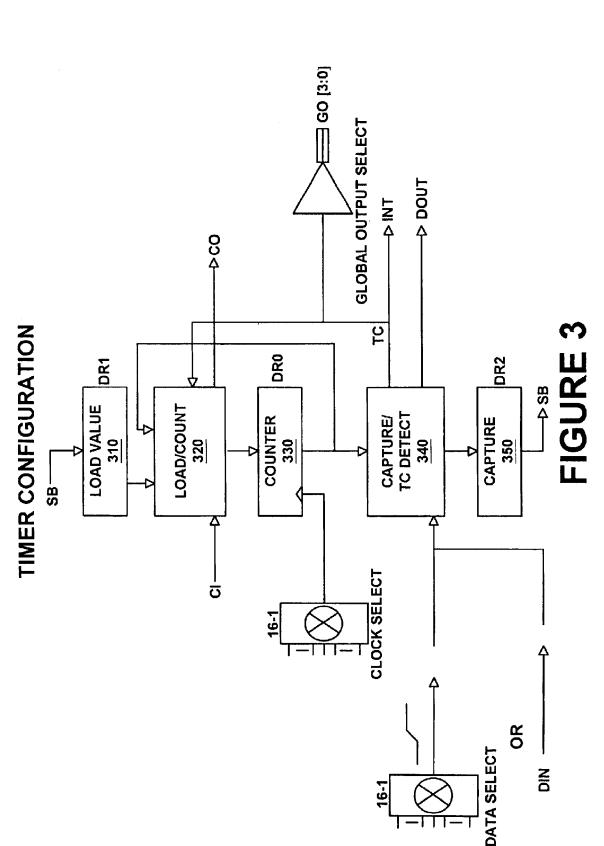

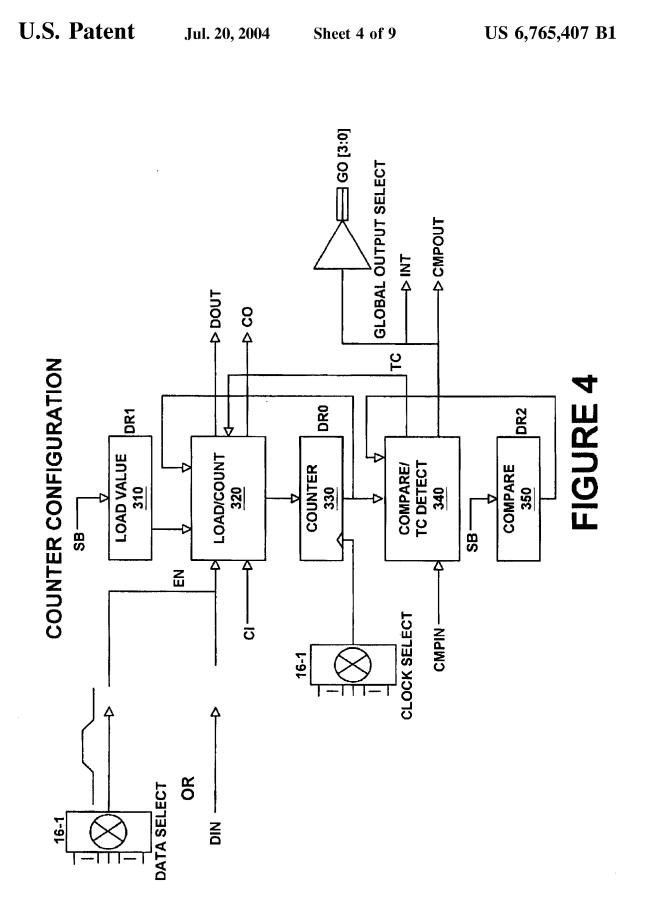

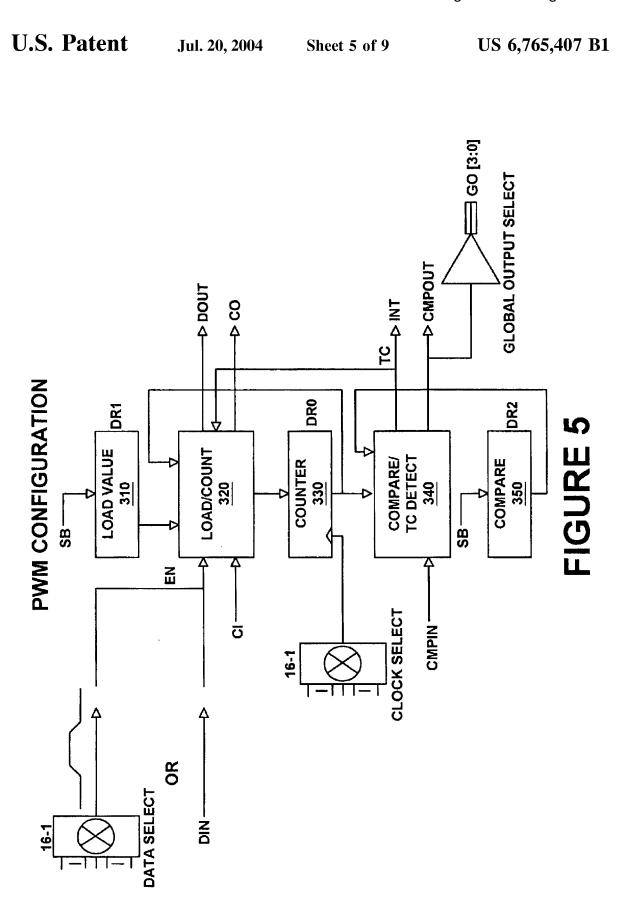

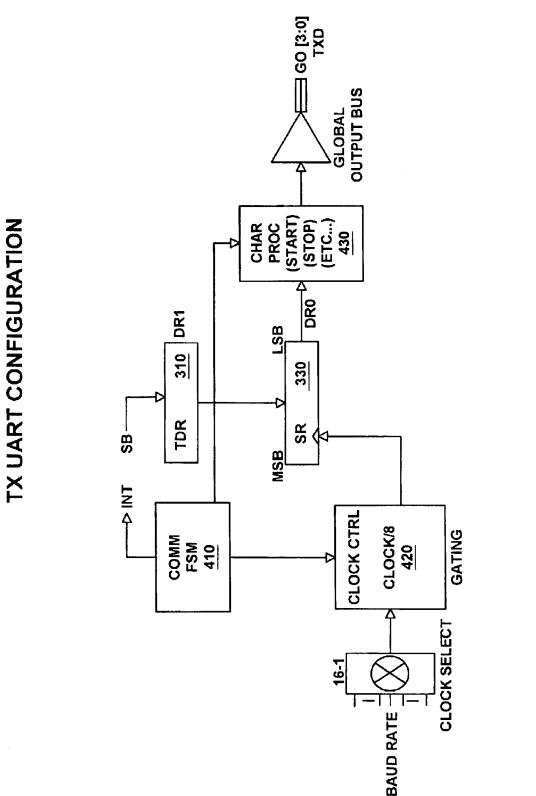

### F. <u>U.S. Patent No. 6,765,407</u>

25. The '407 patent, titled "Digital Configurable Macro Architecture," was duly and properly issued by the USPTO on July 20, 2004. A true and correct copy of the '407 patent is attached hereto as Exhibit F.

26. Monterey is the owner and assignee of the '407 patent; owns all right, title, and interest in the '407 patent; and holds the right to sue and recover damages for infringement thereof, including past infringement.

## G. <u>U.S. Patent No. 7,572,727</u>

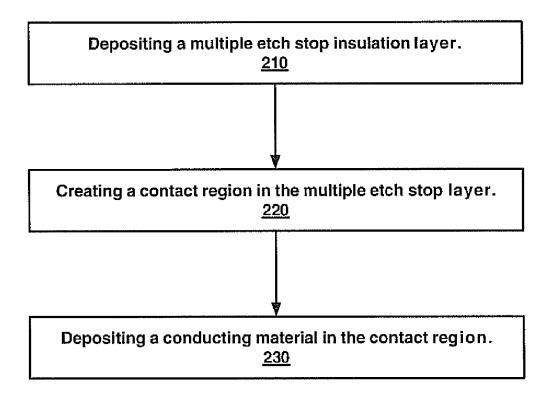

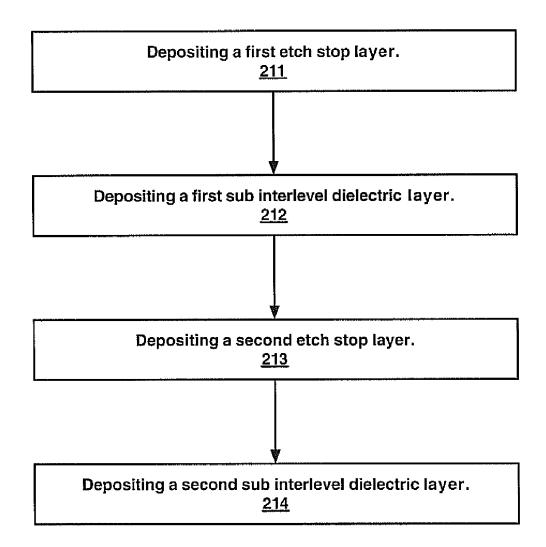

27. The '727 patent, titled "Semiconductor Formation Method that Utilizes Multiple Etch Stop Layers," was duly and properly issued by the USPTO on August 11, 2009. A true and correct copy of the '727 patent is attached hereto as Exhibit G.

28. Monterey is the owner and assignee of the '727 patent; owns all right, title, and interest in the '727 patent; and holds the right to sue and recover damages for infringement thereof, including past infringement.

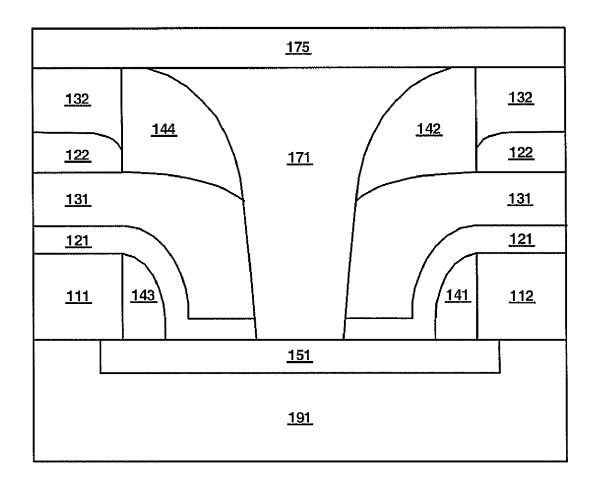

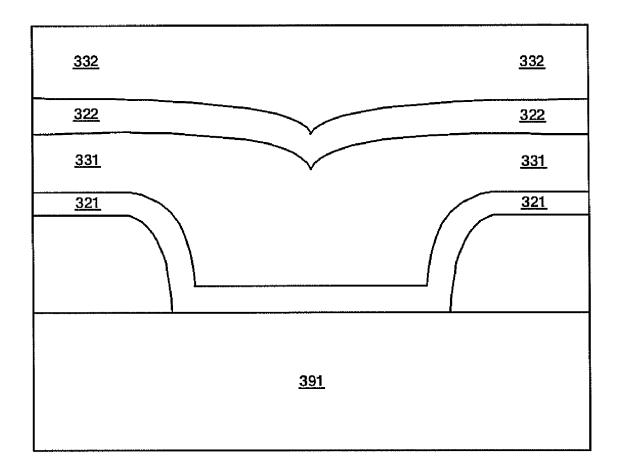

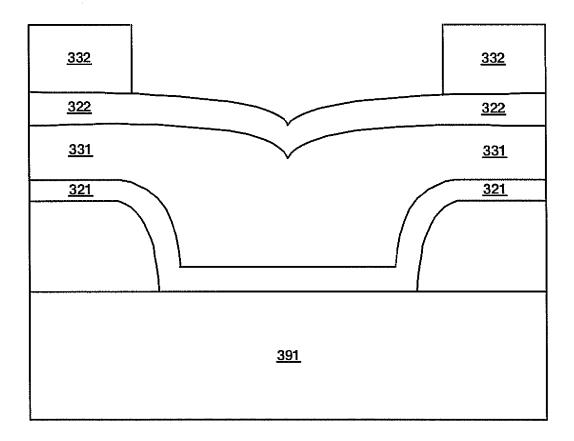

## H. <u>U.S. Patent No. 7,977,797</u>

29. The '797 patent, titled "Integrated Circuit with Contact Region and Multiple Etch

Stop Insulation Layer," was duly and properly issued by the USPTO on July 12, 2011. A true and correct copy of the '797 patent is attached hereto as Exhibit H.

30. Monterey is the owner and assignee of the '797 patent; owns all right, title, and interest in the '797 patent; and holds the right to sue and recover damages for infringement thereof, including past infringement.

## FACTUAL BACKGROUND

31. Monterey incorporates by reference the preceding paragraphs as if fully set forth herein.

32. The Patents-in-Suit stem from the research and design of innovative and proprietary technology developed by leading high-technology companies, including Cypress Semiconductor Corporation ("Cypress").<sup>1</sup> Cypress is an American multinational company and pioneer of cutting-edge semiconductor technology. Founded in 1982, Cypress has made substantial investments in researching, developing, and manufacturing high-quality semiconductor devices, integrated circuits, and products containing the same.

33. The Patents-in-Suit are directed to inventive technology relating to semiconductor devices, integrated circuits, and/or products containing the same.

34. The Qualcomm Defendants work closely with their customers, OEMs, foundry suppliers, distributors, and/or other third parties to make, use, sell, offer to sell, and/or import semiconductor devices, integrated circuits, and/or products containing the same. Among other things, the Qualcomm Defendants optimize their manufacturing process for their customers and optimize their products for integration into downstream products. The Qualcomm Defendants' affirmative acts in furtherance of the manufacture, use, sale, offer to sell, and importation of their

<sup>&</sup>lt;sup>1</sup> Other leading high-technology companies that contributed to inventions disclosed in the Patentsin-Suit include Advanced Micro Devices, Inc. ("AMD") and Spansion LLC ("Spansion").

#### Case 1:19-cv-02083-CFC Document 16 Filed 02/14/20 Page 9 of 51 PageID #: 267

products in and/or into the United States include, but are not limited to, any one or combination of: (i) designing specifications for manufacture of their products; (ii) collaborating on, encouraging, and/or funding the development of processes for the manufacture of their products; (iii) soliciting and/or sourcing the manufacture of their products; (iv) licensing, developing, and/or transferring technology and know-how to enable the manufacture of their products; (v) enabling and encouraging the use, sale, or importation of their products in the United States; and (vi) advertising their products and/or downstream products incorporating them in the United States.

35. The Qualcomm Defendants also provide marketing and/or technical support services for their products from their facilities in the United States. For example, Qualcomm maintains a website that advertises their products, including identifying the applications for which they can be used and specifications for their products. *See, e.g.*, www.qualcomm.com. Qualcomm's publicly-available website also contains user manuals, product documentation, and other materials related to their products. *See, e.g.*, www.qualcomm.com. For example, Qualcomm provides development content for specific chip products and applications; catalogs of hardware, software, and tools documentation; relevant support articles; various software code and tools; and case-specific technical assistance. *See, e.g.*, www.qualcomm.com.

### <u>QUALCOMM'S PRE-SUIT KNOWLEDGE OF MONTEREY'S PATENTS AND</u> <u>CHARGE OF INFRINGEMENT</u>

36. Before filing this action, Monterey, through its agent IPValue Management, Inc. ("IPValue"), notified Qualcomm about the Patents-in-Suit and Qualcomm's infringement thereof. Among other things, Monterey, through its agent IPValue, identified the Patents-in-Suit to Qualcomm; alleged that Qualcomm infringed the Patents-in-Suit, including identifying exemplary infringing products; and offered to license the Patents-in-Suit to Qualcomm. For example:

a. On January 31, 2018, Monterey sent a letter to Qualcomm, notifying Qualcomm of their infringement of certain Monterey patents, including the '625, '516, '805, '407, '727, and '797 patents. Among other things, Monterey identified representative Qualcomm products that utilize those patents, expressly charged that Qualcomm and their customers infringed those patents, and explained that Qualcomm required a license from Monterey. Monterey identified IPValue as Monterey's appointed agent and requested a meeting with Qualcomm.

b. On May 14, 2018, IPValue met in-person with Qualcomm and presented Qualcomm an overview of Monterey's patent portfolio. Among other things, IPValue further explained Monterey's patent portfolio's relevance to Qualcomm and further explained that Qualcomm required a license from Monterey.

c. On July 17, 2018, IPValue again met in-person with Qualcomm and presented Qualcomm with detailed infringement claim charts of certain Monterey patents. Among other things, IPValue's presentations identified specific Monterey patents including the '625, '516, '805, '407, '727, and '797 patents (as well as exemplary patent claims); identified representative Qualcomm products that utilize those patents; identified where every element of each of those exemplary patent claims was found in the representative Qualcomm products; expressly charged that Qualcomm and their customers infringed those patents; and explained that Qualcomm required a license from Monterey.

d. On July 24, 2018, IPValue, on behalf of Monterey, emailed copies of those infringement claim charts to Qualcomm.

e. On October 9, 2018, IPValue met a third time in-person with Qualcomm and presented Qualcomm with additional infringement claim charts of certain Monterey patents. Among other things, IPValue's presentation identified specific Monterey patents including the

'573 and '134 patents (as well as exemplary patent claims); identified representative Qualcomm products that utilize those patents; identified where every element of each of those exemplary patent claims was found in the representative Qualcomm products; expressly charged that Qualcomm and their customers infringed those patents; and explained that Qualcomm required a license from Monterey.

f. On October 16, 2018, IPValue, on behalf of Monterey, emailed Qualcomm copies of the '573 infringement claim chart.

g. On October 17, 2018, IPValue, on behalf of Monterey, emailed Qualcomm copies of the '134 infringement claim chart.

h. On November 13, 2018, IPValue met for a fourth time in-person with Qualcomm, and once again offered to license the Patents-in-Suit to Qualcomm.

i. Monterey continued to contact Qualcomm in the succeeding months to no avail.

j. Despite the numerous meetings and related prior and subsequent communications, at no time during any of those meetings, or at any time prior to Monterey's filing of this Complaint, did Qualcomm deny infringing any element of any claim of the Patents-in-Suit, nor did Qualcomm identify any alleged prior art to any of the Patents-in-Suit.

37. Despite Monterey's repeated efforts—which have continued for well over a year— Qualcomm still has not engaged in any meaningful discussions to end their infringement of the Patents-in-Suit and has not taken a license to them. Instead, Qualcomm continues to knowingly, intentionally, and willfully infringe Monterey's patents directly, contributorily, and by inducement, to obtain their significant benefits without a license from Monterey.

### <u>COUNT ONE</u> INFRINGEMENT OF THE '625 PATENT

38. Monterey incorporates by reference the preceding paragraphs as if fully set forth herein.

39. Monterey is the assignee and lawful owner of all right, title, and interest in and to the '625 patent.

40. The '625 patent is valid and enforceable.

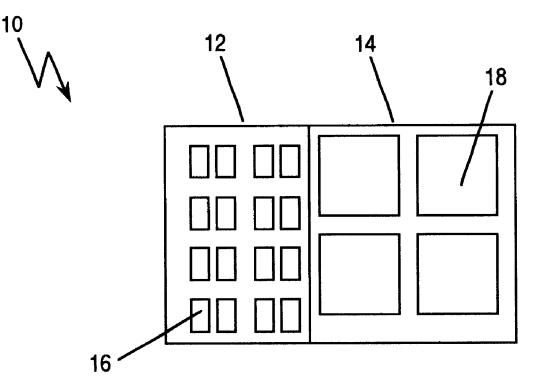

41. The '625 patent is directed to memory device layout, and particularly to systems for optimizing layout density in the periphery area of a memory device using a three-metal or more interconnect process.

42. The '625 patent explains that metallization can involve depositing a thin film of conductive metal on a memory device such that the electrical components are formed and electrically connected with the conductive metal. A periphery area of a memory device can include, for example, a plurality of electrical components such as transistors, resistors, capacitors and diodes formed in the silicon substrate during fabrication. Some types of previously known memory used a two-metal layer metallization process to electrically connect the electrical components in the periphery area of the memory. A problem with this two-metal layer metallization method was layout area consumed by the periphery area. The layout area for the traditional electrical connection systems and methods increased the size of the periphery area on the memory. The area on the memory that is not consumed by the periphery area can be, for example, reserved for the core cell area, allowing more core memory cells to be fabricated on the memory. It is therefore desirable to minimize the amount of periphery area consumed, thereby increasing the amount of information stored in the memory.

43. The '625 patent teaches, among other things, how to selectively place and electrically connect a plurality of electrical components to form sub-circuits and selectively

#### Case 1:19-cv-02083-CFC Document 16 Filed 02/14/20 Page 13 of 51 PageID #: 271

electrically connect the sub-circuits, including using three or more metal layers, resulting in, among other things, minimizing the layout area of the sub-circuits in the periphery area.

44. Qualcomm products use three or more metal layers in their memory device's periphery area. This has enabled Qualcomm to, among other things, decrease their memory device's periphery area. Memory devices containing an infringing periphery area are found integrated in Qualcomm products, including their system-on-chip semiconductor products. Specifically, at least the Qualcomm products which are manufactured with a 7 nm process node have infringing three metal layer or more metallization in their memory device's periphery area and other infringing features that use the technology of the '625 patent.

45. Qualcomm has directly infringed, and continues to directly infringe, one or more claims of the '625 patent under 35 U.S.C. § 271(a), either literally and/or under the doctrine of equivalents, by, among other things, making, using, selling, offering to sell, and/or importing in or into the United States without authorization products covered by one or more claims of the '625 patent, including, but not limited to, products that use three or more metal layers in their integrated memory device's periphery area, such as the SM8150 semiconductor device and other products in the Snapdragon 855 series product family; other Qualcomm 7 nm process node semiconductor devices, integrated circuits, and products; and all other semiconductor devices, integrated circuits, and products with similar integrated memory devices containing a periphery area which uses the infringing technology ("the Accused '625 Products").

46. As one non-limiting example, Qualcomm infringes claim 10 of the '625 patent. For example, the SM8150 Snapdragon 855 semiconductor device contains:

a. a plurality of sub-circuits in a periphery area of a memory device (e.g., subcircuits in the periphery of the SRAM of the SM8150 Snapdragon 855), wherein each sub-circuit

#### Case 1:19-cv-02083-CFC Document 16 Filed 02/14/20 Page 14 of 51 PageID #: 272

includes at least one electrical circuit with a plurality of circuit components (e.g., electrical circuit with a plurality of circuit components in the periphery of the SRAM of the SM8150 Snapdragon 855);

b. a first metal interconnect layer that partially connects the circuit components, wherein first metal layer lines are oriented in substantially one direction (e.g., metal layer connecting circuit components in the periphery of the SRAM of the SM8150 Snapdragon 855);

c. a second metal interconnect layer that completes the connection of the circuit components, and where the second metal interconnect layer lines are fabricated substantially perpendicular to the first metal layer lines (e.g., metal layer perpendicular to the first that completes the connection of the circuit components in the periphery of the SRAM of the SM8150 Snapdragon 855); and

d. a third metal interconnect layer that connects the plurality of sub-circuits, wherein the third metal interconnect layer lines are fabricated substantially parallel to the first metal layer lines (e.g., metal layer substantially parallel to the first that connects the plurality of sub-circuits in the periphery of the SRAM of the SM8150 Snapdragon 855).

47. Claim 10 of the '625 patent applies to each Accused '625 Product at least because each of those products contains the same or similar three or more metal layers in their memory device's periphery area as the Qualcomm SM8150 Snapdragon 855.

48. Monterey has complied with the requirements of 35 U.S.C. § 287(a) at least because Monterey provided Qualcomm with written notice of the infringement as discussed above.

49. Qualcomm has known of the '625 patent and their infringement of that patent since at least as early as January 31, 2018.

#### Case 1:19-cv-02083-CFC Document 16 Filed 02/14/20 Page 15 of 51 PageID #: 273

50. Qualcomm, knowing their products infringe the '625 patent and with the specific intent for others to infringe the '625 patent, has induced infringement of, and continues to induce infringement of, one or more claims of the '625 patent under 35 U.S.C. § 271(b), either literally and/or under the doctrine of equivalents, by, among other things, actively inducing others, including their customers, to make, use, sell, offer to sell, and/or import in or into the United States without authorization the Accused '625 Products, as well as products containing the same. Qualcomm knowingly and intentionally instructs their customers, OEMs, foundry suppliers, distributors, and/or other third parties to infringe at least through user manuals, product documentation, and other materials, such as those located on Qualcomm's website at www.qualcomm.com. For example, Qualcomm provides data sheets, development content, diagrams, white papers, and software instructing customers on uses of Qualcomm's products that infringe the '625 patent. https://www.qualcomm.com/support See. e.g., and https://www.qualcomm.com/system/files/document/files/prod brief qcom sd855 0.pdf. Additional non-limiting examples include the materials found on Qualcomm's website at www.qualcomm.com/products/snapdragon-855-mobile-platform.

51. Qualcomm has contributed to the infringement of, and continues to contribute to the infringement of, one or more claims of the '625 patent under 35 U.S.C. § 271(c), either literally and/or under the doctrine of equivalents, by, among other things, selling, offering to sell, and/or importing in or into the United States the Accused '625 Products, which constitute a material part of the invention of the '625 patent, knowing the Accused '625 Products to be especially made or especially adapted for use in an infringement of such patent, and not a staple article or commodity of substantial noninfringing commerce suitable for use. See, e.g., https://www.qualcomm.com/support and

https://www.qualcomm.com/system/files/document/files/prod\_brief\_qcom\_sd855\_0.pdf.

52. Monterey has sustained and is entitled to recover damages as a result of Qualcomm's past and continuing infringement.

53. Qualcomm's infringement of the '625 patent has been knowing, deliberate, and willful, since at least as early as January 31, 2018, the date of Monterey's letter to Qualcomm and therefore the date on which Qualcomm knew of the '625 patent and that their conduct constituted and resulted in infringement of the '625 patent. Monterey continued to put Qualcomm on notice of the '625 patent and Qualcomm's infringement thereof, including without limitation through communications on July 17, 2018; July 24, 2018; and yet again through this amended complaint. Qualcomm nonetheless has committed—and continues to commit—acts of direct and indirect infringement despite knowing that their actions constituted infringement of the valid and enforceable '625 patent, despite a risk of infringement that was known or so obvious that it should have been known to Qualcomm, and/or even though Qualcomm otherwise knew or should have known that their actions constituted an unjustifiably high risk of infringement of that valid and enforceable patent. Qualcomm's conduct in light of these circumstances is egregious. Qualcomm's knowing, deliberate, and willful infringement of the '625 patent entitles Monterey to increased damages under 35 U.S.C. § 284 and to attorney fees and costs incurred in prosecuting this action under 35 U.S.C. § 285.

## <u>COUNT TWO</u> INFRINGEMENT OF THE '805 PATENT

54. Monterey incorporates by reference the preceding paragraphs as if fully set forth herein.

55. Monterey is the assignee and lawful owner of all right, title, and interest in and to the '805 patent.

56. The '805 patent is valid and enforceable.

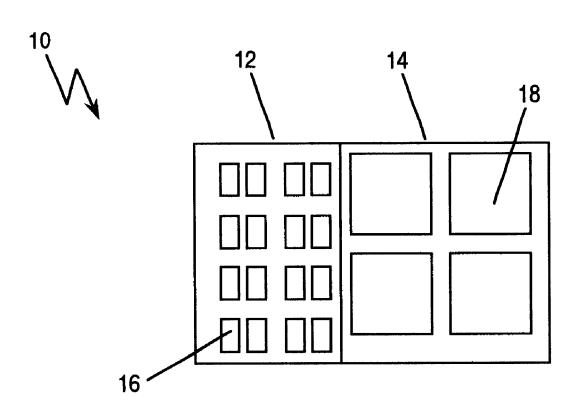

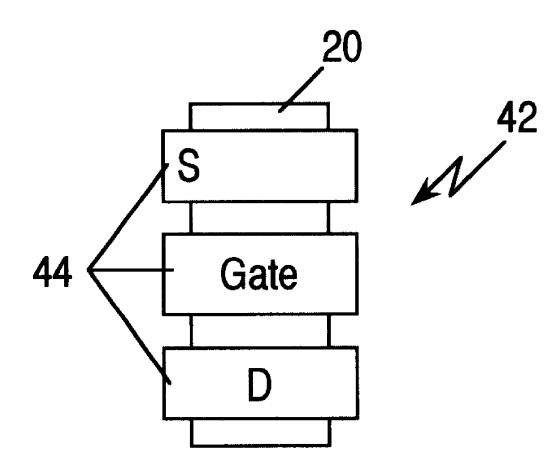

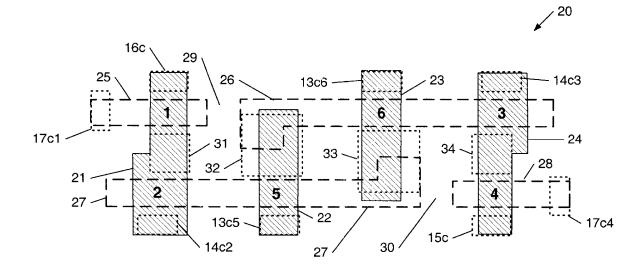

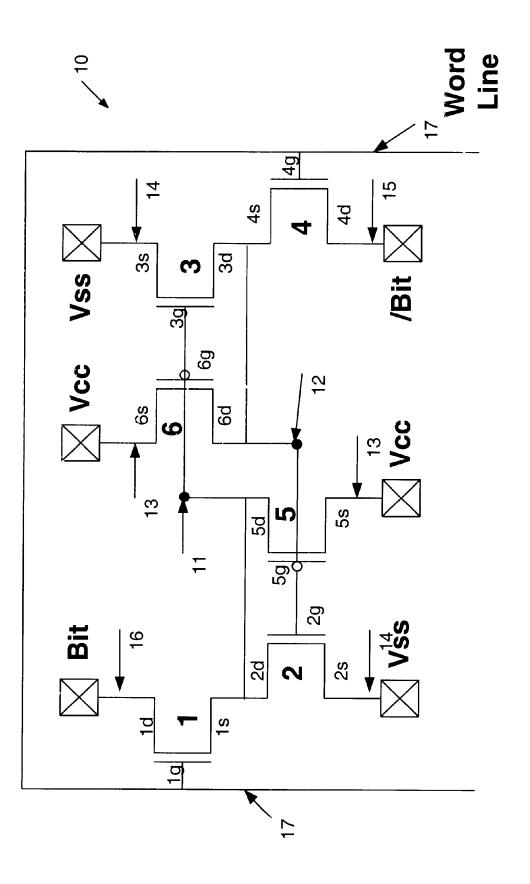

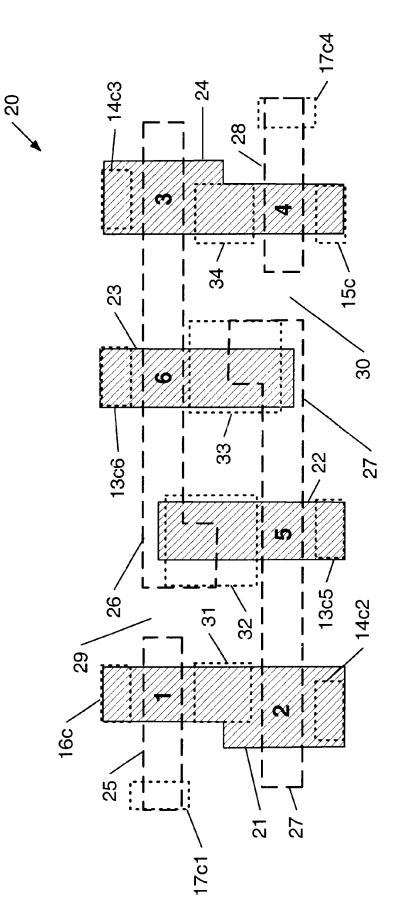

57. The '805 patent is generally directed to static random access memory ("SRAM") cell design, particularly to optimizing SRAM cell design using a simpler geometric layout.

58. As semiconductor structure size continued to shrink with time, one exemplary issue with the prior art of the '805 patent was increased difficulties in manufacturing. Specifically, the then-existing memory cells contained complex geometric designs which required numerous processing steps and larger cell sizes. Generally, more processing steps lead to increased manufacturing costs and reduced profits.

59. The '805 patent teaches, among other things, an improved memory cell layout which allows the features to be arranged in such a way as to minimize cell size. For example, the single local interconnect layer of the '805 patent allows for a thinner product and fewer processing steps.

60. Qualcomm products use SRAM with a six-transistor ("6T") and/or eight-transistor ("8T") cell design. Qualcomm's 6T and 8T SRAM contain a single local interconnect layer. This has resulted in, among other things, Qualcomm's ability to decrease the size of their SRAM area and to decrease the number of manufacturing steps.

61. Qualcomm has directly infringed, and continues to directly infringe, one or more claims of the '805 patent under 35 U.S.C. § 271(a), either literally and/or under the doctrine of equivalents, by, among other things, making, using, selling, offering to sell, and/or importing in or into the United States without authorization products covered by one or more claims of the '805 patent, including, but not limited to, all Qualcomm devices incorporating SRAM with a 6T and/or 8T cell design, such as the MSM8974 semiconductor device and other products in the Snapdragon 800, Snapdragon S4 Play, Snapdragon S4 Plus, Snapdragon S4 Pro, Snapdragon 200, Snapdragon

205, Snapdragon 208, Snapdragon 210, Snapdragon 212, Snapdragon 400, Snapdragon 410, Snapdragon 412, Snapdragon 415, Snapdragon 425, Snapdragon 427, Snapdragon 430, Snapdragon 435, Snapdragon 429, Snapdragon 439, Snapdragon 450, Snapdragon 600, Snapdragon 610, Snapdragon 615, Snapdragon 616, Snapdragon 617, Snapdragon 625, Snapdragon 626, Snapdragon 650, Snapdragon 652, Snapdragon 653, Snapdragon 630, Snapdragon 636, Snapdragon 660, Snapdragon 632, Snapdragon 670, Snapdragon 675, Snapdragon 665, Snapdragon 710, Snapdragon 712, Snapdragon 730, Snapdragon 730G, Snapdragon 801, Snapdragon 805, Snapdragon 808, Snapdragon 810, Snapdragon 820, Snapdragon 821, Snapdragon 835, Snapdragon 845, Snapdragon 850, Snapdragon 855, and Snapdragon 8cx series product families; and all other semiconductor devices, integrated circuits, and products with similar infringing technology ("the Accused '805 Products").

62. As one non-limiting example, Qualcomm infringes claim 8 of the '805 patent. For example, the MSM8974 Snapdragon 800 semiconductor device contains:

a. a memory cell (e.g., SRAM cell of the MSM8974 Snapdragon 800) comprising a plurality of substantially oblong active regions (e.g., N-type and/or P-type diffusion areas of the MSM8974 Snapdragon 800) formed in a semiconductor substrate and arranged substantially in parallel with one another, and a plurality of substantially oblong local interconnects (e.g., structures formed at the polysilicon layer on top of the substrate of the MSM8974 Snapdragon 800) above said substrate that extend only partially across the memory cell and are arranged substantially in parallel with one another and substantially perpendicular to said active regions; and

b. a single local interconnect layer (e.g., metal 1 ("M1") layer of the MSM8974 Snapdragon 800) comprising local interconnects (e.g., structures formed at the M1

layer of the MSM8974 Snapdragon 800) corresponding to bitlines (e.g., those formed at the metal 2 ("M2") layer of the MSM8974 Snapdragon 800) and a global word-line (e.g., those formed at the metal 3 ("M3") layer of the MSM8974 Snapdragon 800).

63. Claim 8 of the '805 patent applies to each Accused '805 Product at least because each of those products contain the same or similar structures as the Qualcomm MSM8974 Snapdragon 800.

64. Monterey has complied with the requirements of 35 U.S.C. § 287(a) at least because Monterey provided Qualcomm with written notice of the infringement as discussed above.

65. Qualcomm has known of the '805 patent and their infringement of that patent since at least as early as January 31, 2018.

66. Qualcomm, knowing their products infringe the '805 patent and with the specific intent for others to infringe the '805 patent, has induced infringement of, and continues to induce infringement of, one or more claims of the '805 patent under 35 U.S.C. § 271(b), either literally and/or under the doctrine of equivalents, by, among other things, actively inducing others, including their customers, to make, use, sell, offer to sell, and/or import in or into the United States without authorization the Accused '805 Products, as well as products containing the same. Qualcomm knowingly and intentionally instructs their customers, OEMs, foundry suppliers, distributors, and/or third parties to infringe at least through user manuals, product documentation, and other materials, such as those located on Qualcomm's website at www.qualcomm.com. For example, Qualcomm provides data sheets, development content, diagrams, white papers, and software instructing customers on uses of Qualcomm's products that infringe the '805 patent. *See, e.g.*, https://www.qualcomm.com/support and

https://www.qualcomm.com/media/documents/files/snapdragon-800-product-brief.pdf.

#### Case 1:19-cv-02083-CFC Document 16 Filed 02/14/20 Page 20 of 51 PageID #: 278

Additional, non-limiting examples include the materials found on Qualcomm's websites at www.qualcomm.com/products/snapdragon-processors-800.

67. Oualcomm has contributed to the infringement of, and continues to contribute to the infringement of, one or more claims of the '805 patent under 35 U.S.C. § 271(c), either literally and/or under the doctrine of equivalents, by, among other things, selling, offering to sell, and/or importing in or into the United States the Accused '805 Products, which constitute a material part of the invention of the '805 patent, knowing the Accused '805 Products to be especially made or especially adapted for use in an infringement of such patent, and not a staple article or commodity of commerce suitable for substantial noninfringing See, use. e.g., https://www.qualcomm.com/support and

https://www.qualcomm.com/media/documents/files/snapdragon-800-product-brief.pdf.

68. Monterey has sustained and is entitled to recover damages as a result of Qualcomm's past and continuing infringement.

69. Qualcomm's infringement of the '805 patent has been knowing, deliberate, and willful, since at least as early as January 31, 2018, the date of Monterey's letter to Qualcomm and therefore the date on which Qualcomm knew of the '805 patent and that their conduct constituted and resulted in infringement of the '805 patent. Monterey continued to put Qualcomm on notice of the '805 patent and Qualcomm's infringement thereof, including without limitation through communications on July 17, 2018 and July 24, 2018; through the complaint filed on November 1, 2019; and yet again through this amended complaint. Qualcomm nonetheless has committed—and continues to commit—acts of direct and indirect infringement despite knowing that their actions constituted infringement of the valid and enforceable '805 patent, despite a risk of infringement that was known or so obvious that it should have been known to Qualcomm, and/or

even though Qualcomm otherwise knew or should have known that their actions constituted an unjustifiably high risk of infringement of that valid and enforceable patent. Qualcomm's conduct in light of these circumstances is egregious. Qualcomm's knowing, deliberate, and willful infringement of the '805 patent entitles Monterey to increased damages under 35 U.S.C. § 284 and to attorney fees and costs incurred in prosecuting this action under 35 U.S.C. § 285.

## <u>COUNT THREE</u> INFRINGEMENT OF THE '573 PATENT

70. Monterey incorporates by reference the preceding paragraphs as if fully set forth herein.

71. Monterey is the assignee and lawful owner of all right, title, and interest in and to the '573 patent.

72. The '573 patent is valid and enforceable.

73. The '573 patent is generally directed to semiconductor devices including a modified oxide-nitride-oxide ("ONO") structure comprising a high-K dielectric material.

74. The '573 patent explains that as device dimensions continue to be reduced, the electrical thickness of the ONO layer must be reduced accordingly. Previously, that had been accomplished by scaling down the physical thickness of the ONO layer. However, as the ONO layer was made physically thinner, leakage current through the ONO layer could increase, and the charge trapping ability of the nitride layer could be reduced, limiting the scaling down of the total physical thickness of the ONO layer.

75. Consequently, the '573 patent describes, among other things, the use of a mid-K or a high-K dielectric material in a modified ONO structure having reduced dimensions without creation of interface states coming from contamination which could provide charge leakage paths and without sacrificing the charge trapping ability of the modified ONO structure. It thus provided

advantages such as (1) reduction of equivalent oxide thickness of ONO in next generation devices; (2) high-K film devices are expected to have improved data retention and reliability; and (3) the high-K dielectric material layer replacing one of both silicon dioxide layers allows fabrication of an ONO layer which is physically thicker, resulting in fewer charge leakage paths within the modified ONO structure.

76. Qualcomm has directly infringed, and continues to directly infringe, one or more claims of the '573 patent under 35 U.S.C. § 271(a) and/or 35 U.S.C. § 271(g), either literally and/or under the doctrine of equivalents, by, among other things, making, using, selling, offering to sell, and/or importing (including importing products made by a patented process) in or into the United States without authorization products covered by one or more claims of the '573 patent, including, but not limited to, products with high-k dielectrics, such as the MSM8994 semiconductor device and other products in the Snapdragon 810 and Snapdragon 808 series product families; other Qualcomm 20 nm process node semiconductor devices, integrated circuits, and products; and all other semiconductor devices, integrated circuits, and products with similar infringing technology ("the Accused '573 Products").

77. As one non-limiting example, Qualcomm infringes claim 1 of the '573 patent. For example, the MSM8994 Snapdragon 810 semiconductor device comprises a semiconductor device comprising a modified ONO structure:

a. wherein the modified ONO structure comprises a bottom dielectric material layer, a nitride layer on the bottom dielectric material layer, and a top dielectric material layer on the nitride layer, in which at least one of the bottom dielectric material layer and the top dielectric material layer comprises a composite dielectric material, wherein the composite dielectric material

comprises elements of at least one mid-K or high-K dielectric material (e.g., modified ONO structure of the MSM8994 Snapdragon 810);

b. wherein each mid-K or high-K dielectric material independently comprises at least one of hafnium oxide (HfO2), zirconium oxide (ZrO2), barium titanate (BaTiO3), cerium oxide (CeO2), lanthanum oxide (La2O3), lanthanum aluminum oxide (LaAlO3), lead titanate (PbTiO3), strontium titanate (SrTiO3), lead zirconate (PbZrO3), tungsten oxide (WO3), yttrium oxide (Y2O3), bismuth silicon oxide (Bi4Si2O12), barium strontium titanate (BST) (Ba1xSrxTiO3), PMN (PbMgxNb1-xO3), PZT (PbZrxTi1-xO3), PZN (PbZnxNb1-xO3), and PST (PbScxTa1-xO3) (e.g., dielectric material of the MSM8994 Snapdragon 810 comprising hafnium oxide).

78. Claim 1 of the '573 patent applies to each Accused '573 Product at least because each of those products contain the same or similar structures as the Qualcomm MSM8994 Snapdragon 810.

79. Monterey has complied with the requirements of 35 U.S.C. § 287(a) at least because Monterey provided Qualcomm with written notice of the infringement as discussed above.

80. Qualcomm has known of the '573 patent and their infringement of that patent since at least as early as October 9, 2018.

81. Qualcomm, knowing their products infringe the '573 patent and with the specific intent for others to infringe the '573 patent, has induced infringement of, and continues to induce infringement of, one or more claims of the '573 patent under 35 U.S.C. § 271(b), either literally and/or under the doctrine of equivalents, by, among other things, actively inducing others, including their customers, to make, use, sell, offer to sell, and/or import (including import products made by a patented process) in or into the United States without authorization the Accused '573

#### Case 1:19-cv-02083-CFC Document 16 Filed 02/14/20 Page 24 of 51 PageID #: 282

Products as well as products containing the same. Qualcomm knowingly and intentionally instructs their customers, OEMs, foundry suppliers, distributors, and/or other third parties to infringe at least through user manuals, product documentation, and other materials, such as those located on Qualcomm's website at www.qualcomm.com. For example, Qualcomm provides data sheets, development content, diagrams, white papers, and software instructing customers on uses of Qualcomm's products that infringe the '573 patent. See, e.g., https://www.qualcomm.com/support and

https://www.qualcomm.com/system/files/document/files/snapdragon\_product\_brief\_810\_0.pdf. Additional, non-limiting examples include the materials found on Qualcomm's websites at https://www.qualcomm.com/products/snapdragon-processors-810.

82. Qualcomm has contributed to the infringement of, and continues to contribute to the infringement of, one or more claims of the '573 patent under 35 U.S.C. § 271(c), either literally and/or under the doctrine of equivalents, by, among other things, selling, offering to sell, and/or importing in or into the United States the Accused '573 Products, which constitute a material part of the invention of the '573 patent, knowing the Accused '573 Products to be especially made or especially adapted for use in an infringement of such patent, and not a staple article or commodity of commerce suitable for substantial noninfringing use. See, e.g., https://www.qualcomm.com/support and

https://www.qualcomm.com/system/files/document/files/snapdragon\_product\_brief\_810\_0.pdf.

83. Monterey has sustained and is entitled to recover damages as a result of Qualcomm's past and continuing infringement.

84. Qualcomm's infringement of the '573 patent has been knowing, deliberate, and willful, since at least as early as October 9, 2018, the date on which Qualcomm was presented with

the '573 claim chart, knew of the '573 patent, and knew that their conduct constituted and resulted in infringement of the '573 patent. Monterey continued to put Qualcomm on notice of the '573 patent and Qualcomm's infringement thereof, including without limitation through communications on October 16, 2018; through the complaint filed on November 1, 2019; and yet again through this amended complaint. Qualcomm nonetheless has committed—and continues to commit—acts of direct and indirect infringement despite knowing that their actions constituted infringement of the valid and enforceable '573 patent, despite a risk of infringement that was known or so obvious that it should have been known to Qualcomm, and/or even though Qualcomm otherwise knew or should have known that their actions constituted an unjustifiably high risk of infringement of that valid and enforceable patent. Qualcomm's conduct in light of these circumstances is egregious. Qualcomm's knowing, deliberate, and willful infringement of the '573 patent entitles Monterey to increased damages under 35 U.S.C. § 284 and to attorney fees and costs incurred in prosecuting this action under 35 U.S.C. § 285.

## <u>COUNT FOUR</u> INFRINGEMENT OF THE '134 PATENT

85. Monterey incorporates by reference the preceding paragraphs as if fully set forth herein.

86. Monterey is the assignee and lawful owner of all right, title, and interest in and to the '134 patent.

87. The '134 patent is valid and enforceable.

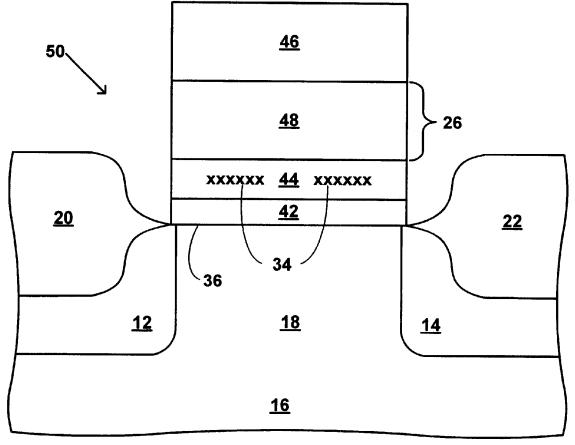

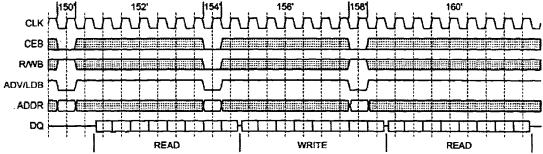

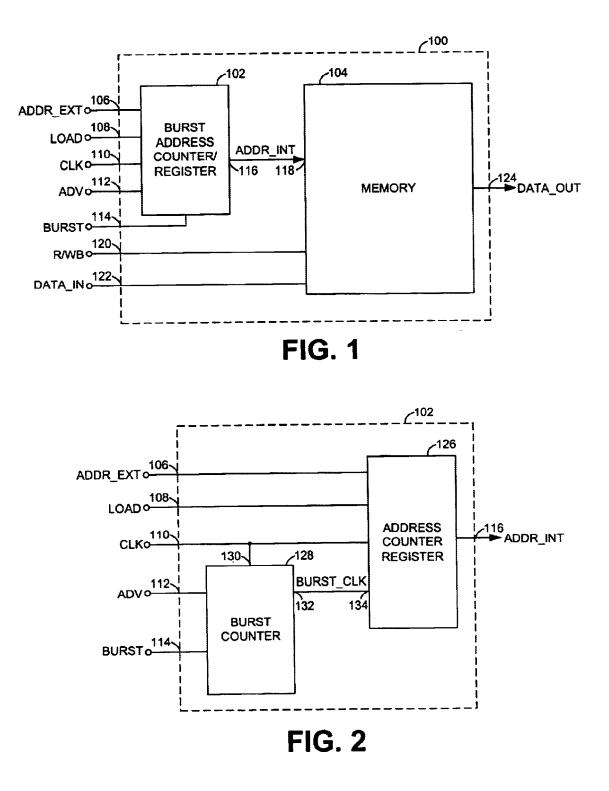

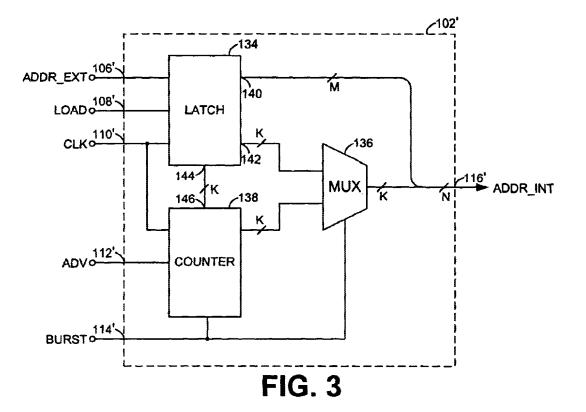

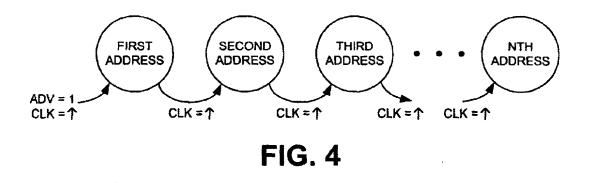

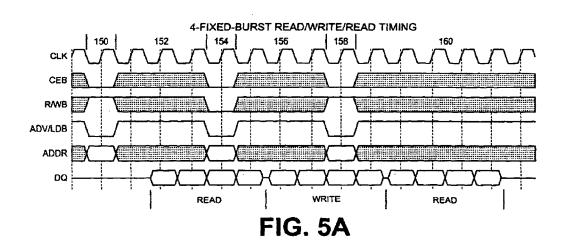

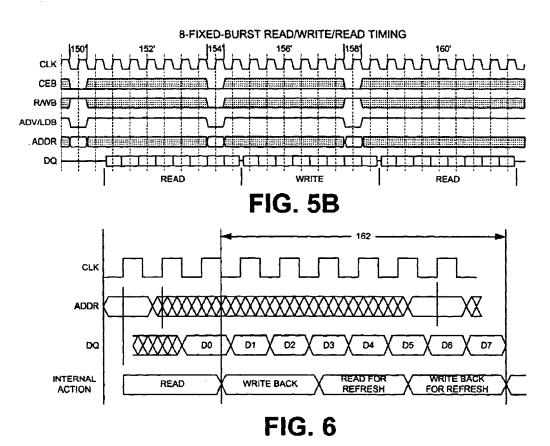

88. The '134 patent generally concerns memory devices, and is more specifically related to non-interruptible burst read and write access features, as described in JEDEC standards JESD79-3F DDR3 SDRAM, JESD79-4A DDR4 SDRAM, JESD209-3 LPDDR3, JESD209-4 LPDDR4, and similar versions of the JEDEC DDRx standards.

89. The '134 patent provides a faster and more efficient way for burst read and write access over conventional DRAM devices existing when the patent was filed in early 2000. A conventional DRAM may need an interrupt to perform data refreshes. Prior to the '134 patent, DRAM memory devices had a burst mode that had the possibility of needing to continually perform interrupts to perform data refreshes.

90. The '134 patent teaches, among other things, a fixed burst memory that can have non-interruptible bursts, hide required DRAM refreshes inside a known fixed burst length, free up the address and control busses for multiple cycles, and operate at higher frequencies without needing interrupts to perform refreshes of data.

91. Qualcomm products use memory devices that are compliant with the JEDEC standards JESD79-3F DDR3 SDRAM, JESD79-4A DDR4 SDRAM, JESD209-3 LPDDR3, JESD209-4 LPDDR4 and similar versions of the JEDEC DDRx standards that incorporate the innovations of the '134 patent's non-interruptible fixed burst length.

92. Qualcomm has directly infringed, and continues to directly infringe, one or more claims of the '134 patent under 35 U.S.C. § 271(a), either literally and/or under the doctrine of equivalents, by, among other things, making, using, selling, offering to sell, and/or importing in or into the United States without authorization products covered by one or more claims of the '134 patent, including, but not limited to, products that comply with the JEDEC standards JESD79-3F DDR3 SDRAM, JESD79-4A DDR4 SDRAM, JESD209-3 LPDDR3, JESD209-4 LPDDR4 and similar versions of the JEDEC DDRx standards that use non-interruptible burst read or write operations, such as the APQ8064E Snapragon 600E semiconductor device and other products in the Snapdragon 400, Snapdragon 410, Snapdragon 412, Snapdragon 415, Snapdragon 425, Snapdragon 427, Snapdragon 430, Snapdragon 435, Snapdragon 429, Snapdragon 439,

Snapdragon 450, Snapdragon 600, Snapdragon 600E, Snapdragon 602, Snapdragon 610, Snapdragon 615, Snapdragon 616, Snapdragon 617, Snapdragon 625, Snapdragon 626, Snapdragon 650, Snapdragon 652, Snapdragon 653, Snapdragon 630, Snapdragon 636, Snapdragon 660, Snapdragon 632, Snapdragon 670, Snapdragon 675, Snapdragon 665, Snapdragon 710, Snapdragon 712, Snapdragon 730, Snapdragon 730G, Snapdragon 800, Snapdragon 801, Snapdragon 805, Snapdragon 808, Snapdragon 810, Snapdragon 820, Snapdragon 821, Snapdragon 835, Snapdragon 845, Snapdragon 850, Snapdragon 855, Snapdragon Wear 2100 Platform, Snapdragon Wear 2500 Platform, Snapdragon Wear 3100 Platform, Smart Display Platform 200, QCS603, QCS605, Atlas VI, and Atlas 7 product families; other semiconductor devices, integrated circuits, and products that are compliant with JESD79-3F DDR3 SDRAM, JESD79-4A DDR4 SDRAM, JESD209-3 LPDDR3, JESD209-4 LPDDR4 or similar versions; and all other semiconductor devices, integrated circuits, and products with similar infringing technology ("the Accused '134 Products").

93. As one non-limiting example, Qualcomm infringes claim 1 of the '134 patent since the APQ8064E Snapdragon 600E semiconductor device contains DDR3 SDRAM memory controllers that operate in conformance with JEDEC's DDR3 SDRAM standard. For example, the APQ8064E Snapdragon 600E contains a circuit comprising:

a. a memory comprising a plurality of storage elements (e.g., banks of storage elements of the APQ8064E Snapdragon 600E);

b. each configured to read and write data in response to an internal address signal (e.g., stored bits of memory bank addressed and defined by internal addresses of the APQ8064E Snapdragon 600E);

c. a logic circuit configured to generate a predetermined number of said

internal address signals (e.g., generating addresses based on bank addresses, row addresses, and column addresses of the APQ8064E Snapdragon 600E) in response to an external address signal (e.g., read or write signals of the APQ8064E Snapdragon 600E), a clock signal (e.g., clock signal of the APQ8064E Snapdragon 600E), and one or more control signals (e.g., control signal of the APQ8064E Snapdragon 600E);

d. wherein said generation of said predetermined number of internal address signals is non-interruptible (e.g., burst reads or writes cannot be terminated or interrupted in the APQ8064E Snapdragon 600E).

94. Claim 1 of the '134 patent applies to each Accused '134 Product at least because each of those products either complies with the same JEDEC JESD79-3F DDR3 SDRAM standard, or similar versions of the JEDEC standard, including but not limited to JESD79-4A DDR4 SDRAM, JESD209-3 LPDDR3, and JESD209-4 LPDDR4, which result in infringing features (e.g., non-interruptible burst oriented read or write operations of the Accused '134 Products) found in the JESD79-3F DDR3 SDRAM standard.

95. Monterey has complied with the requirements of 35 U.S.C. § 287(a) at least because Monterey provided Qualcomm with written notice of the infringement as discussed above.

96. Qualcomm has known of the '134 patent and their infringement of that patent since at least October 9, 2018.

97. Qualcomm, knowing their products infringe the '134 patent and with the specific intent for others to infringe the '134 patent, has induced infringement of, and continues to induce infringement of, one or more claims of the '134 patent under 35 U.S.C. § 271(b), either literally and/or under the doctrine of equivalents, by, among other things, actively inducing others, including their customers, to make, use, sell, offer to sell, and/or import in or into the United States

#### Case 1:19-cv-02083-CFC Document 16 Filed 02/14/20 Page 29 of 51 PageID #: 287

without authorization the Accused '134 Products, as well as products containing the same. Qualcomm knowingly and intentionally instructs their customers, OEMs, foundry suppliers, distributors, and/or other third parties to infringe at least through user manuals, product documentation, and other materials, such as those located on Qualcomm's website at www.qualcomm.com. For example, Qualcomm provides data sheets, development content, diagrams, white papers, and software instructing customers on uses of Qualcomm's products that infringe the '134 patent. See. https://www.qualcomm.com/support e.g., and https://developer.qualcomm.com/download/sd600/snapdragon-600-device-spec.pdf. Additional non-limiting examples include the materials found on Qualcomm's website at https://www.qualcomm.com/media/documents/files/snapdragon-600e-embedded-platformproduct-brief.pdf.

98. Qualcomm has contributed to the infringement of, and continues to contribute to the infringement of, one or more claims of the '134 patent under 35 U.S.C. § 271(c), either literally and/or under the doctrine of equivalents, by, among other things, selling, offering to sell, and/or importing in or into the United States the Accused '134 Products, which constitute a material part of the invention of the '134 patent, knowing the Accused '134 Products to be especially made or especially adapted for use in an infringement of such patent, and not a staple article or commodity of substantial noninfringing suitable for See. commerce use. e.g., https://www.qualcomm.com/support and

https://developer.qualcomm.com/download/sd600/snapdragon-600-device-spec.pdf.

99. Monterey has sustained and is entitled to recover damages as a result of Qualcomm's past and continuing infringement.

100. Qualcomm's infringement of the '134 patent has been knowing, deliberate, and

willful, since at least as early as October 9, 2018, the date on which Qualcomm was presented with the '134 patent infringement claim chart, knew of the '134 patent, and knew that their conduct constituted and resulted in infringement of the '134 patent. Monterey continued to put Qualcomm on notice of the '134 patent and Qualcomm's infringement thereof, including without limitation through communications on October 17, 2018; through the complaint filed on November 1, 2019; and yet again through this amended complaint. Qualcomm nonetheless has committed—and continues to commit—acts of direct and indirect infringement despite knowing that their actions constituted infringement of the valid and enforceable '134 patent, despite a risk of infringement that was known or so obvious that it should have been known to Qualcomm, and/or even though Qualcomm otherwise knew or should have known that their actions constituted an unjustifiably high risk of infringement of that valid and enforceable patent. Qualcomm's conduct in light of these circumstances is egregious. Qualcomm's knowing, deliberate, and willful infringement of the '134 patent entitles Monterey to increased damages under 35 U.S.C. § 284 and to attorney fees and costs incurred in prosecuting this action under 35 U.S.C. § 285.

## <u>COUNT FIVE</u> INFRINGEMENT OF THE '516 PATENT

101. Monterey incorporates by reference the preceding paragraphs as if fully set forth herein.

102. Monterey is the assignee and lawful owner of all right, title, and interest in and to the '516 patent.

103. The '516 patent is valid and enforceable.

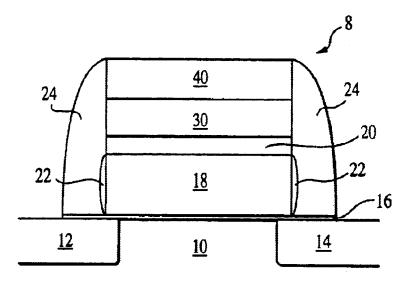

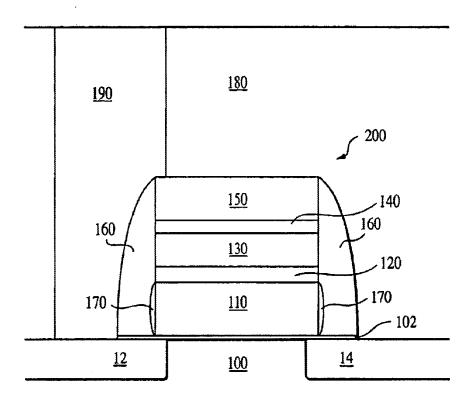

104. The '516 patent is directed to semiconductor structures, particularly to a semiconductor gate stack and related features. A gate stack can include, for example, a gate insulating layer, a gate layer, a metallic layer—which may optionally be separated from the gate

layer by a barrier layer—and an etch-stop layer.

105. The '516 patent explains that as the size of a semiconductor element is reduced, it does not necessarily follow that the thickness of specific layers that form that element can be equally reduced. By way of non-limiting example, the thickness of a nitride layer necessary for forming a self-aligned contact (type of contact) may still need to be at least 800 angstroms. This could lead to, among other things, designs for devices that require large aspect ratios for contact vias, and such vias may not be properly filled. An aspect ratio can be, for example, the ratio of the gate stack height to the via width.

106. The '516 patent teaches, among other things, a gate stack height of at most 2700 angstroms and a via width of at most 0.12 microns. A gate stack with a controlled thickness can, for example, help to avoid forming contact vias with a large aspect ratio. The '516 patent further teaches, among other things, a gate stack which can include a nitride layer that may be used for forming self-aligned contacts "SAC," which may be used in designs to significantly reduce device size.

107. Qualcomm products use a semiconductor gate stack structure having a controlled thickness, and the Qualcomm products use vias to connect to certain portions of the semiconductor structure. Specifically, at least the Qualcomm products which are manufactured with a 28 nm or smaller process node have infringing gate stacks of at most 2700 angstroms, via widths of at most 0.12 microns, and other infringing features that use the technology of the '516 patent.

108. Qualcomm has directly infringed, and continues to directly infringe, one or more claims of the '516 patent under 35 U.S.C. § 271(a), either literally and/or under the doctrine of equivalents, by, among other things, making, using, selling, offering to sell, and/or importing in or into the United States without authorization products covered by one or more claims of the '516

patent, including, but not limited to, products with a gate stack structure with a controlled thickness, such as the MSM8994 semiconductor device and other products in the Snapdragon 810, Snapdragon S4 Plus, Snapdragon S4 Pro, Snapdragon 200, Snapdragon 205, Snapdragon 208, Snapdragon 210, Snapdragon 212, Snapdragon 400, Snapdragon 410, Snapdragon 412, Snapdragon 415, Snapdragon 425, Snapdragon 427, Snapdragon 430, Snapdragon 435, Snapdragon 429, Snapdragon 439, Snapdragon 450, Snapdragon 600, Snapdragon 610, Snapdragon 615, Snapdragon 616, Snapdragon 617, Snapdragon 625, Snapdragon 626, Snapdragon 650, Snapdragon 652, Snapdragon 653, Snapdragon 630, Snapdragon 636, Snapdragon 660, Snapdragon 632, Snapdragon 670, Snapdragon 675, Snapdragon 665, Snapdragon 710, Snapdragon 712, Snapdragon 730, Snapdragon 730G, Snapdragon 800, Snapdragon 801, Snapdragon 805, Snapdragon 808, Snapdragon 820, Snapdragon 821, Snapdragon 835, Snapdragon 845, Snapdragon 850, Snapdragon 855, and Snapdragon 8cx series product families; other Qualcomm 28 nm and smaller process node semiconductor devices, integrated circuits, and products; and all other semiconductor devices, integrated circuits, and products with similar infringing technology ("the Accused '516 Products").

109. As one non-limiting example, Qualcomm infringes claim 5 of the '516 patent. For example, the MSM8994 Snapdragon 810 semiconductor device contains:

a. a semiconductor substrate (e.g., silicon substrate of the MSM8994 Snapdragon 810);

b. a gate layer, a metallic layer, an etch-stop layer, and an insulating layer (e.g., transistor gate stack of the MSM8994 Snapdragon 810);

c. a via with a via width of at most 0.12 micron (e.g., via to a portion of a transistor of the MSM8994 Snapdragon 810);

d. and a gate stack height of at most 2700 angstroms (e.g., transistor gate stack of the MSM8994 Snapdragon 810).

110. Claim 5 of the '516 patent applies to each Accused '516 Product at least because each of those products contain the same or similar structures as the Qualcomm MSM8994 Snapdragon 810.

111. Monterey has complied with the requirements of 35 U.S.C. § 287(a) at least because Monterey provided Qualcomm with written notice of the infringement as discussed above.

112. Qualcomm has known of the '516 patent and their infringement of that patent since at least as early as January 31, 2018.

Qualcomm, knowing their products infringe the '516 patent and with the specific 113. intent for others to infringe the '516 patent, has induced infringement of, and continues to induce infringement of, one or more claims of the '516 patent under 35 U.S.C. § 271(b), either literally and/or under the doctrine of equivalents, by, among other things, actively inducing others, including their customers, to make, use, sell, offer to sell, and/or import in or into the United States without authorization the Accused '516 Products, as well as products containing the same. Qualcomm knowingly and intentionally instructs their customers, OEMs, foundry suppliers, distributors, and/or other third parties to infringe at least through user manuals, product documentation, and other materials, such as those located on Qualcomm's website at www.qualcomm.com. For example, Qualcomm provides data sheets, development content, diagrams, white papers, and software instructing customers on uses of Qualcomm's products that infringe the '516 https://www.qualcomm.com/support patent. See. e.g., and https://www.qualcomm.com/system/files/document/files/snapdragon product brief 810 0.pdf. Additional, non-limiting examples include the materials found on Qualcomm's websites at

www.qualcomm.com/products/snapdragon-processors-810.

114. Qualcomm has contributed to the infringement of, and continues to contribute to the infringement of, one or more claims of the '516 patent under 35 U.S.C. § 271(c), either literally and/or under the doctrine of equivalents, by, among other things, selling, offering to sell, and/or importing in or into the United States the Accused '516 Products, which constitute a material part of the invention of the '516 patent, knowing the Accused '516 Products to be especially made or especially adapted for use in an infringement of such patent, and not a staple article or commodity substantial noninfringing of commerce suitable for See. use. e.g., https://www.qualcomm.com/support and

https://www.qualcomm.com/system/files/document/files/snapdragon\_product\_brief\_810\_0.pdf.

115. Monterey has sustained and is entitled to recover damages as a result of Qualcomm's past and continuing infringement.

116. Qualcomm's infringement of the '516 patent has been knowing, deliberate, and willful, since at least as early as January 31, 2018, the date of Monterey's letter to Qualcomm and therefore the date on which Qualcomm knew of the '516 patent and that their conduct constituted and resulted in infringement of the '516 patent. Monterey continued to put Qualcomm on notice of the '516 patent and Qualcomm's infringement thereof, including without limitation through communications on July 17, 2018; July 24, 2018; through the complaint filed on November 1, 2019; and yet again through this amended complaint. Qualcomm nonetheless has committed—and continues to commit—acts of direct and indirect infringement despite knowing that their actions constituted infringement of the valid and enforceable '516 patent, despite a risk of infringement that was known or so obvious that it should have been known to Qualcomm, and/or even though Qualcomm otherwise knew or should have known that their actions constituted and

unjustifiably high risk of infringement of that valid and enforceable patent. Qualcomm's conduct in light of these circumstances is egregious. Qualcomm's knowing, deliberate, and willful infringement of the '516 patent entitles Monterey to increased damages under 35 U.S.C. § 284 and to attorney fees and costs incurred in prosecuting this action under 35 U.S.C. § 285.

## <u>COUNT SIX</u> <u>INFRINGEMENT OF THE '407 PATENT</u>

117. Monterey incorporates by reference the preceding paragraphs as if fully set forth herein.

118. Monterey is the assignee and lawful owner of all right, title, and interest in and to the '407 patent.

119. The '407 patent is valid and enforceable.

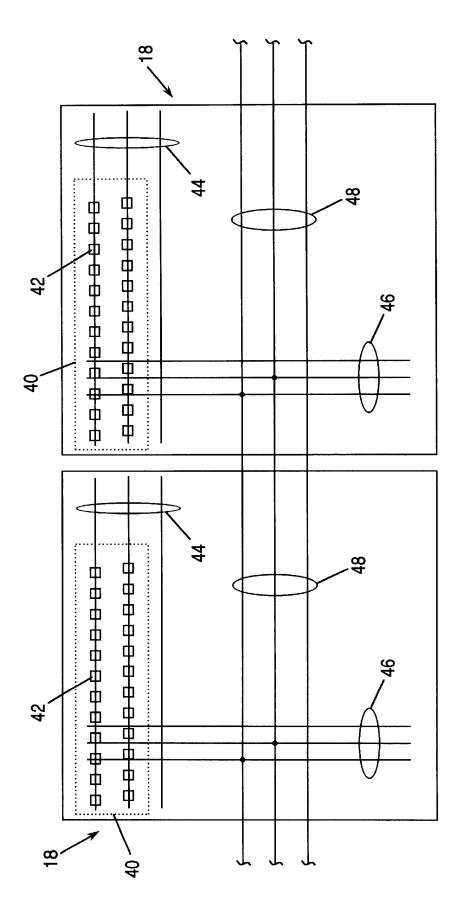

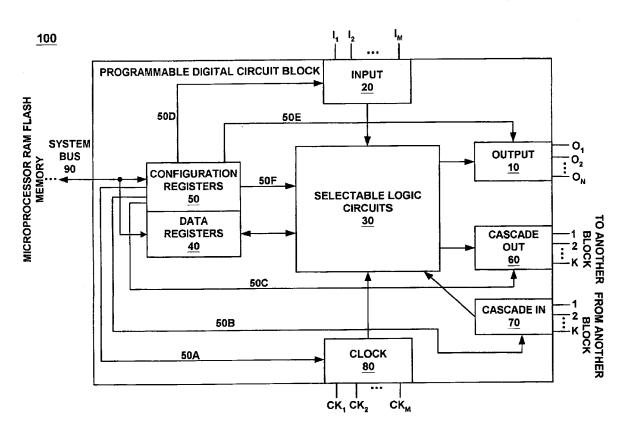

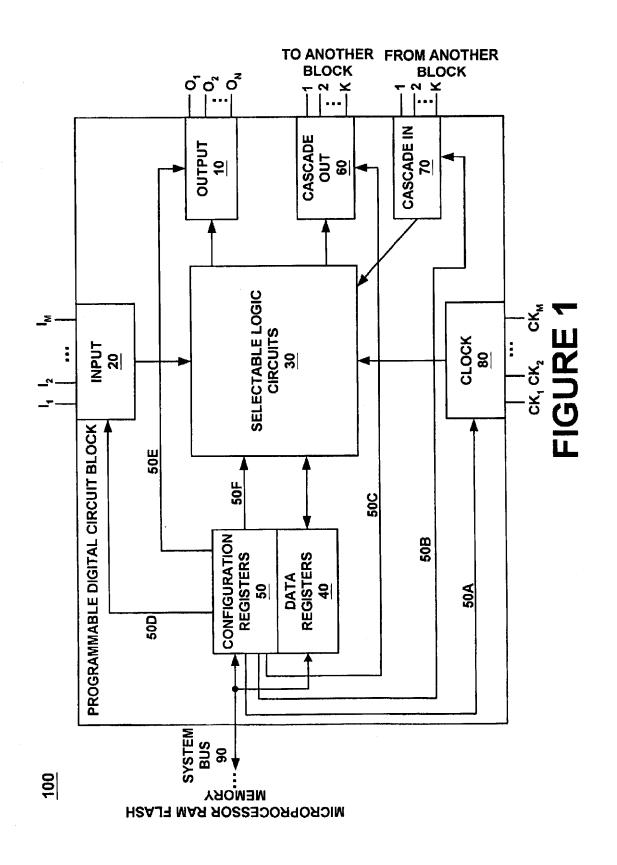

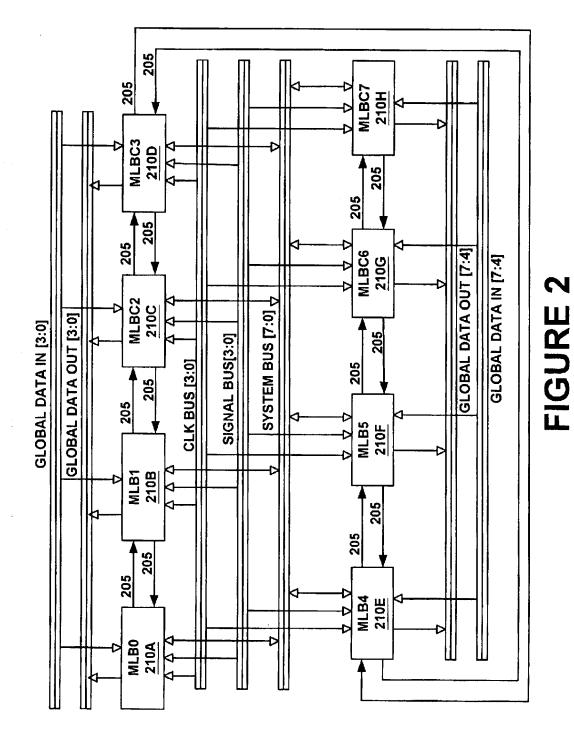

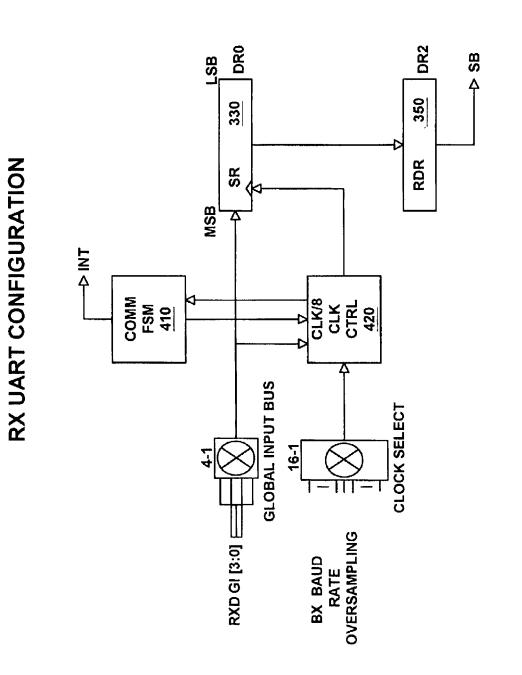

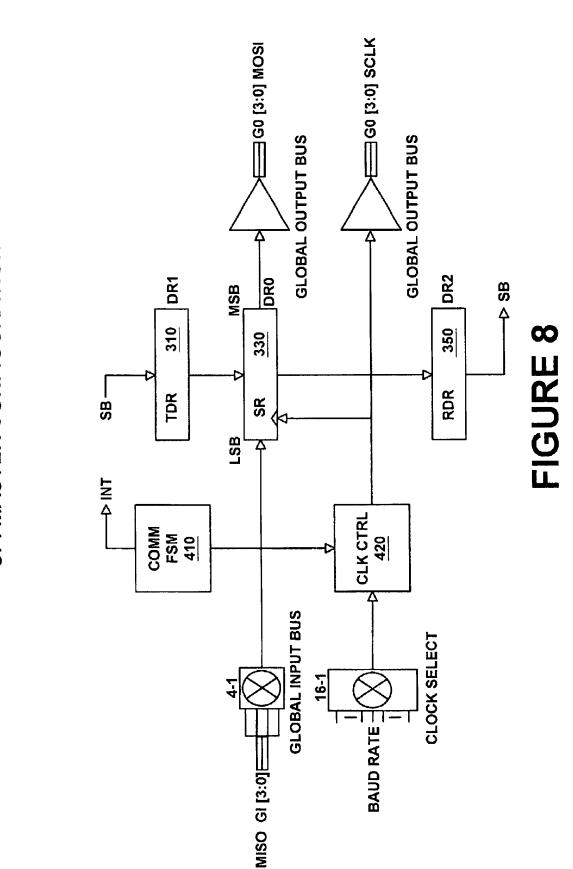

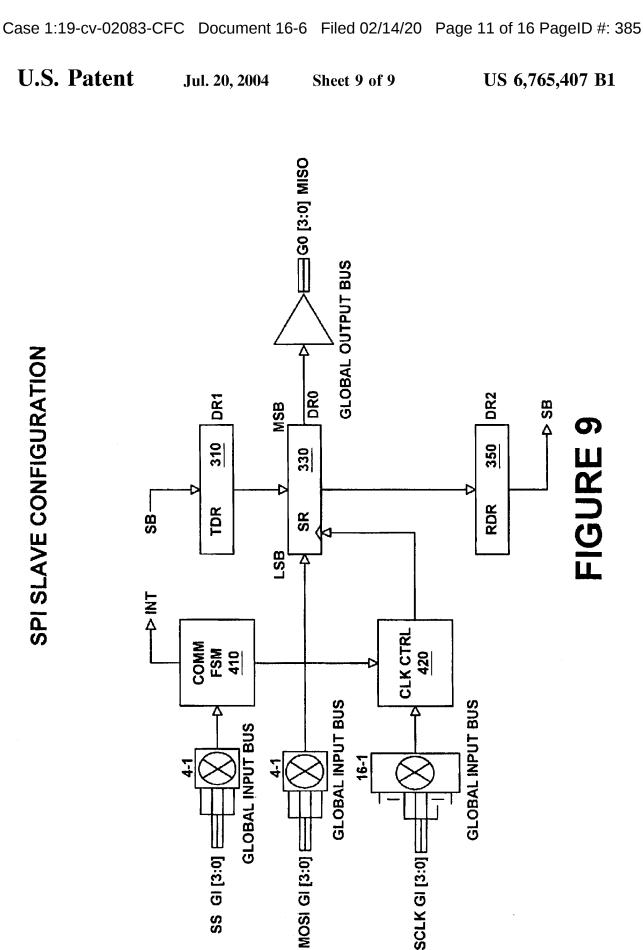

120. The '407 patent is generally directed to programmable digital circuit architecture, and particularly to programmable digital devices which are configurable to perform any one of various digital functions, by changing the contents of a register.

121. The '407 patent explains that microcontrollers or controllers have been utilized in various applications for many years. Microcontrollers are frequently found in, for example: appliances, computers and computer equipment, automobiles, environmental control, aerospace, and thousands of other uses. Prior to the '407 patent, field programmable gate arrays ("FPGA") were utilized in several microcontroller applications. FPGAs are highly inefficient with respect to chip area, increasing their cost. Moreover, FPGAs need to have their look-up tables reprogrammed in order to enable them to implement a new digital function, which is a time consuming task. FPGAs are not ideally suited for microcontroller applications, since, for example, microcontroller applications are very cost-sensitive. A FPGA is not able to realize the number of digital functions that are demanded by certain microcontroller applications within these strict cost

constraints.

122. The '407 patent teaches, among other things, a programmable digital circuit block that can be programmed to perform a variety of predetermined digital functions upon being configured with a single register write operation. This solution allows the configuration of the programmable digital circuit block to be determined by a small number of configuration registers, providing much flexibility. In particular, the configuration of the programmable digital circuit block is fast and easy since changes in configuration are accomplished by changing the contents of the configuration registers, whereas the contents are generally a small number of configuration data bits.

123. Qualcomm products use an array of programmable digital circuit blocks, such as ARM cores. For example, the ARM core can be found in a number of different Qualcomm Snapdragon products, as it functions as a processing core of the Snapdragon system-on-chip. The ARM core is programmable to perform a variety of predetermined digital functions by changing the contents of a register.

124. Qualcomm has directly infringed, and continues to directly infringe, one or more claims of the '407 patent under 35 U.S.C. § 271(a), either literally and/or under the doctrine of equivalents, by, among other things, making, using, selling, offering to sell, and/or importing in or into the United States without authorization products covered by one or more claims of the '407 patent, including, but not limited to, products with an ARM core, such as the MSM8994 semiconductor device and other products in the Snapdragon 810, Snapdragon 410, Snapdragon 412, Snapdragon 415, Snapdragon 425, Snapdragon 427, Snapdragon 430, Snapdragon 435, Snapdragon 429, Snapdragon 439, Snapdragon 450, Snapdragon 610, Snapdragon 615, Snapdragon 616, Snapdragon 617, Snapdragon 625, Snapdragon 626, Snapdragon 650,

Snapdragon 652, Snapdragon 653, Snapdragon 630, Snapdragon 636, Snapdragon 660, Snapdragon 632, Snapdragon 670, Snapdragon 675, Snapdragon 665, Snapdragon 710, Snapdragon 712, Snapdragon 730, Snapdragon 730G, Snapdragon 808, Snapdragon 835, Snapdragon 845, Snapdragon 850, Snapdragon 855, and Snapdragon 8cx series product families; other Qualcomm semiconductor devices, integrated circuits, and products containing ARM A53 and newer cores; and all other semiconductor devices, integrated circuits, and products with similar ARM or ARM-derived cores ("the Accused '407 Products").

125. As one non-limiting example, Qualcomm infringes claim 8 of the '407 patent. For example, the MSM8994 Snapdragon 810 semiconductor device contains:

a. an array of programmable digital circuit block (e.g., ARM cores of the MSM8994 Snapdragon 810);

b. where each programmable digital circuit block is configurable to perform a predetermined digital function (e.g., operating in AArch32 or AArch64 execution state in the MSM8994 Snapdragon 810);

c. upon being configured with a single register write operation (e.g., writing RMR register in the MSM8994 Snapdragon 810).

126. Claim 8 of the '407 patent applies to each Accused '407 Product at least because each of those products contain infringing ARM A53 or newer cores, and/or contain ARM or ARM-derived cores containing similar infringing functionality.

127. Monterey has complied with the requirements of 35 U.S.C. § 287(a) at least because Monterey provided Qualcomm with written notice of the infringement as discussed above.

128. Qualcomm has known of the '407 patent and their infringement of that patent since at least as early as January 31, 2018.

#### Case 1:19-cv-02083-CFC Document 16 Filed 02/14/20 Page 38 of 51 PageID #: 296

129. Qualcomm, knowing their products infringe the '407 patent and with the specific intent for others to infringe the '407 patent, has induced infringement of, and continues to induce infringement of, one or more claims of the '407 patent under 35 U.S.C. § 271(b), either literally and/or under the doctrine of equivalents, by, among other things, actively inducing others, including their customers, to make, use, sell, offer to sell, and/or import (including import products made by a patented process) in or into the United States without authorization the Accused '407 Products, as well as products containing the same. Qualcomm knowingly and intentionally instructs their customers, OEMs, foundry suppliers, distributors, and/or other third parties to infringe at least through user manuals, product documentation, and other materials, such as those located on Qualcomm's website at www.qualcomm.com. For example, Qualcomm provides data sheets, development content, diagrams, white papers, and software instructing customers on uses of Qualcomm's products that infringe the '407 patent. See. e.g., https://www.qualcomm.com/support and

https://www.qualcomm.com/system/files/document/files/snapdragon\_product\_brief\_810\_0.pdf. Additional non-limiting examples include the materials found on Qualcomm's websites at www.qualcomm.com/products/snapdragon-processors-810.

Qualcomm has contributed to the infringement of, and continues to contribute to 130. the infringement of, one or more claims of the '407 patent under 35 U.S.C. § 271(c), either literally and/or under the doctrine of equivalents, by, among other things, selling, offering to sell, and/or importing in or into the United States the Accused '407 Products, which constitute a material part of the invention of the '407 patent, knowing the Accused '407 Products to be especially made or especially adapted for use in an infringement of such patent, and not a staple article or commodity of commerce suitable for substantial noninfringing use. See, e.g.,

https://www.qualcomm.com/support

and

https://www.qualcomm.com/system/files/document/files/snapdragon\_product\_brief\_810\_0.pdf.

131. Monterey has sustained and is entitled to recover damages as a result of Qualcomm's past and continuing infringement.

132. Qualcomm's infringement of the '407 patent has been knowing, deliberate, and willful, since at least as early as January 31, 2018, the date of Monterey's letter to Qualcomm and therefore the date on which Qualcomm knew of the '407 patent and that their conduct constituted and resulted in infringement of the '407 patent. Monterey continued to put Qualcomm on notice of the '407 patent and Qualcomm's infringement thereof, including without limitation through communications on July 17, 2018; July 24, 2018; through the complaint filed on November 1, 2019; and yet again through this amended complaint. Qualcomm nonetheless has committed and continues to commit-acts of direct and indirect infringement despite knowing that their actions constituted infringement of the valid and enforceable '407 patent, despite a risk of infringement that was known or so obvious that it should have been known to Qualcomm, and/or even though Qualcomm otherwise knew or should have known that their actions constituted an unjustifiably high risk of infringement of that valid and enforceable patent. Qualcomm's conduct in light of these circumstances is egregious. Qualcomm's knowing, deliberate, and willful infringement of the '407 patent entitles Monterey to increased damages under 35 U.S.C. § 284 and to attorney fees and costs incurred in prosecuting this action under 35 U.S.C. § 285.

#### <u>COUNT SEVEN</u> INFRINGEMENT OF THE '727 PATENT

133. Monterey incorporates by reference the preceding paragraphs as if fully set forth herein.

134. Monterey is the assignee and lawful owner of all right, title, and interest in and to

the '727 patent.

135. The '727 patent is valid and enforceable.

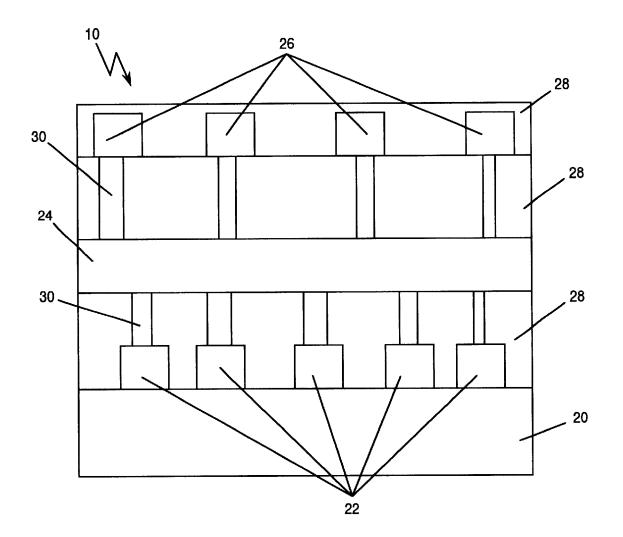

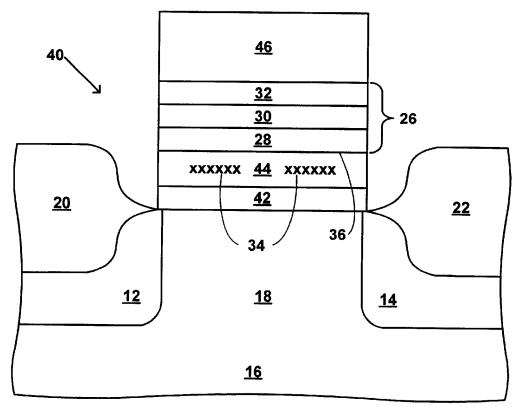

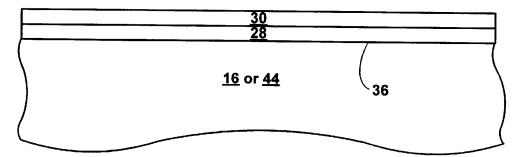

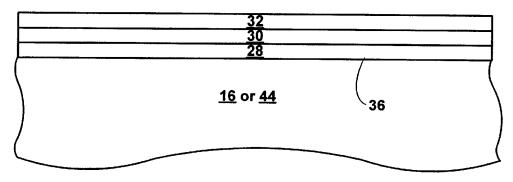

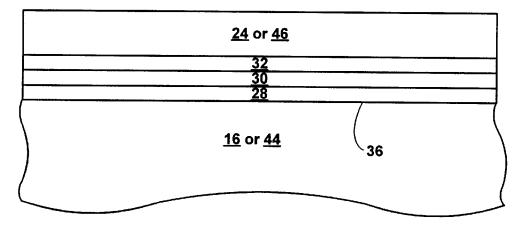

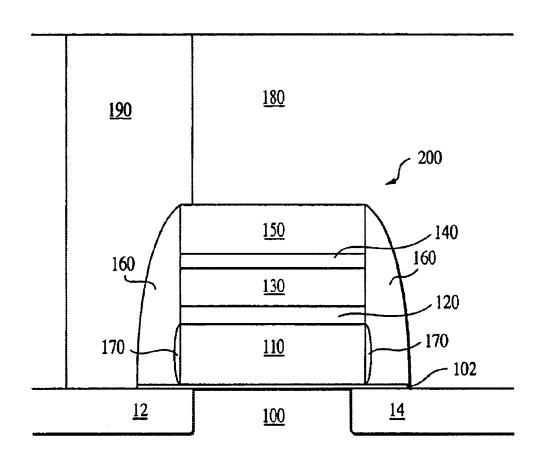

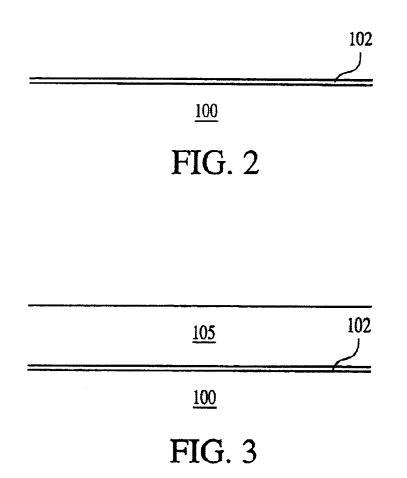

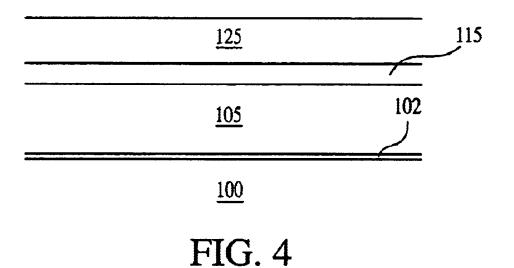

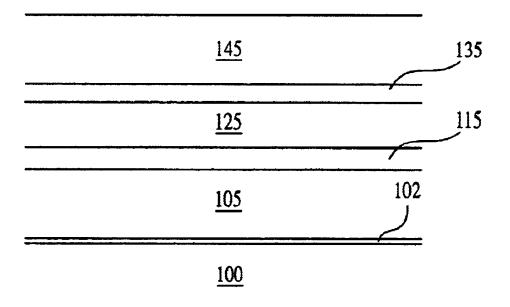

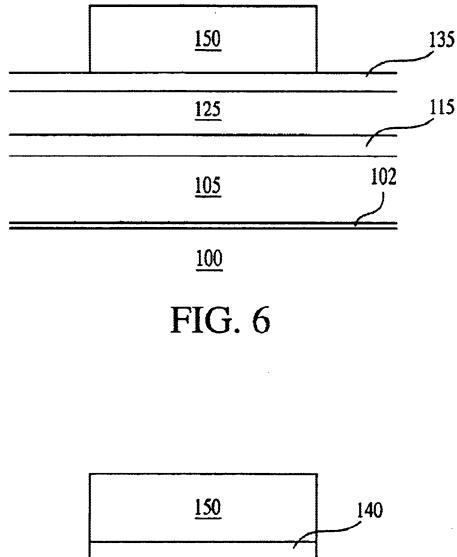

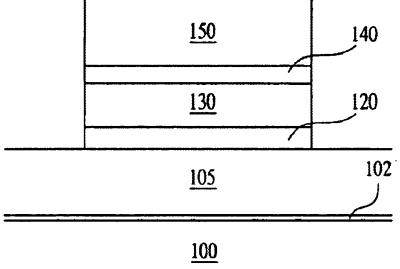

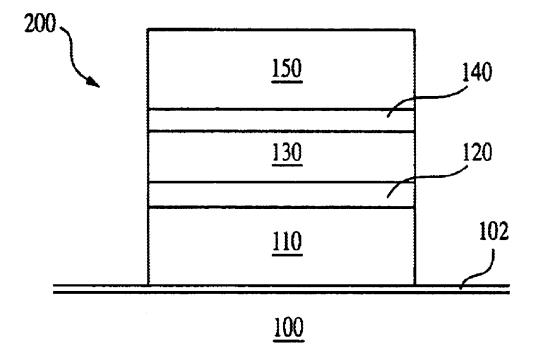

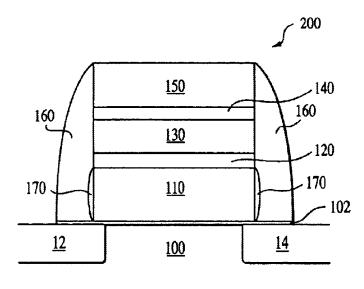

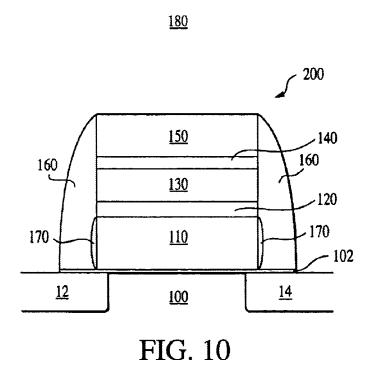

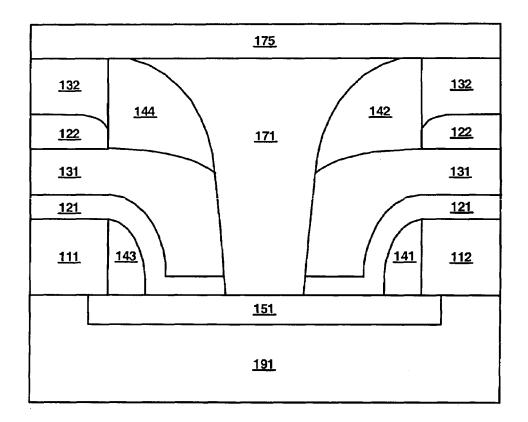

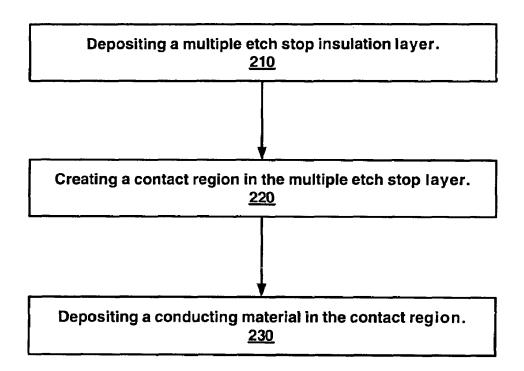

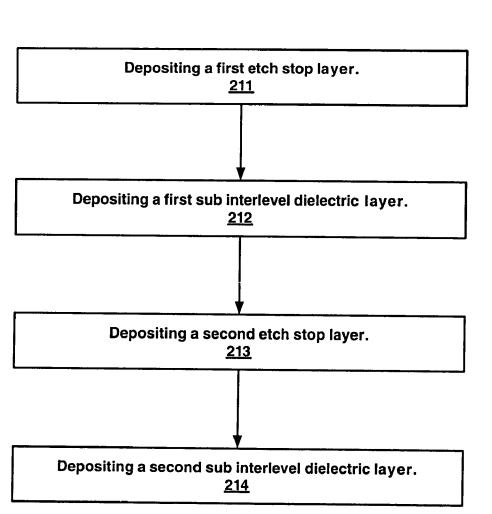

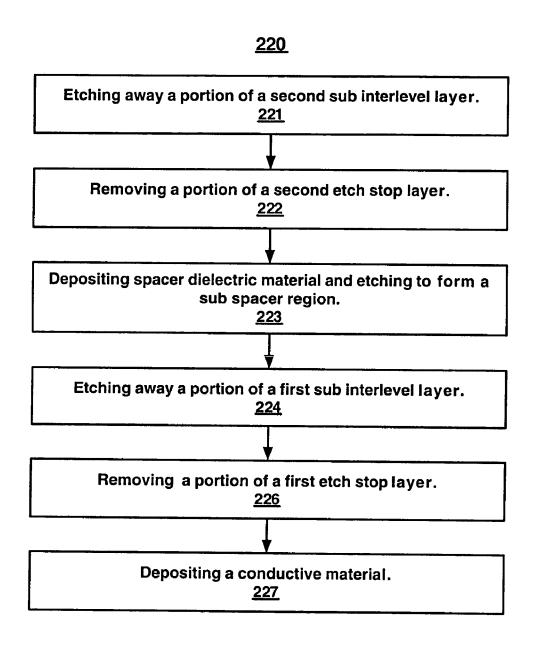

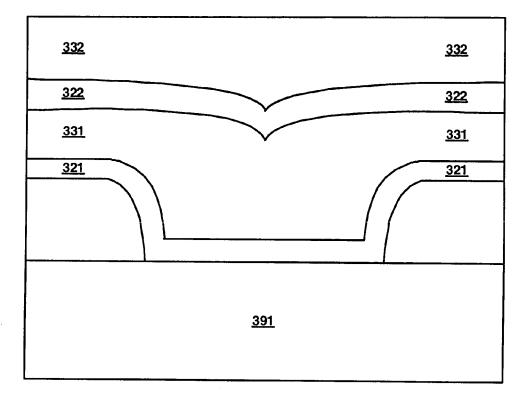

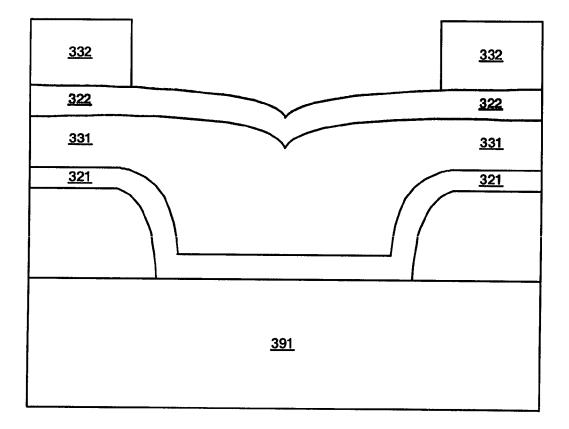

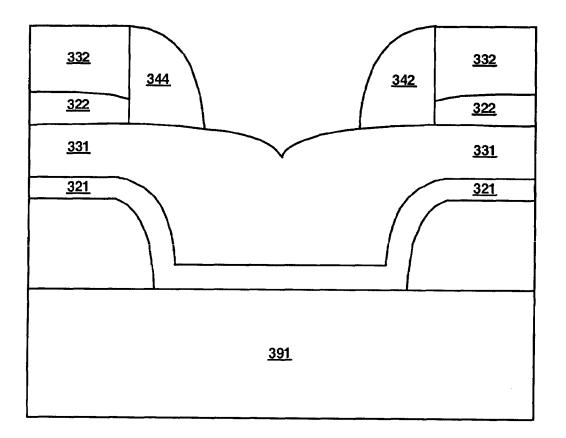

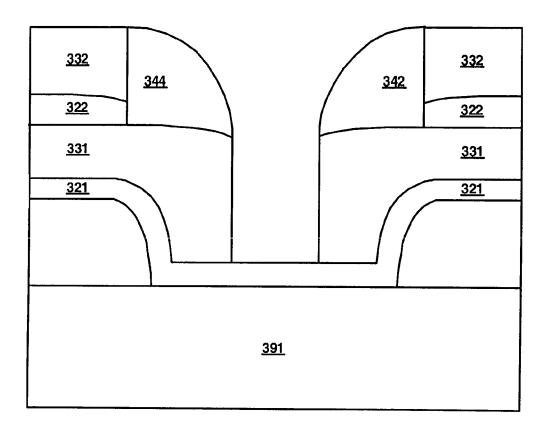

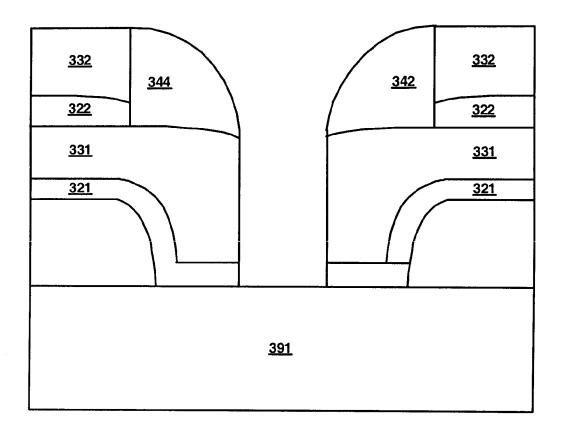

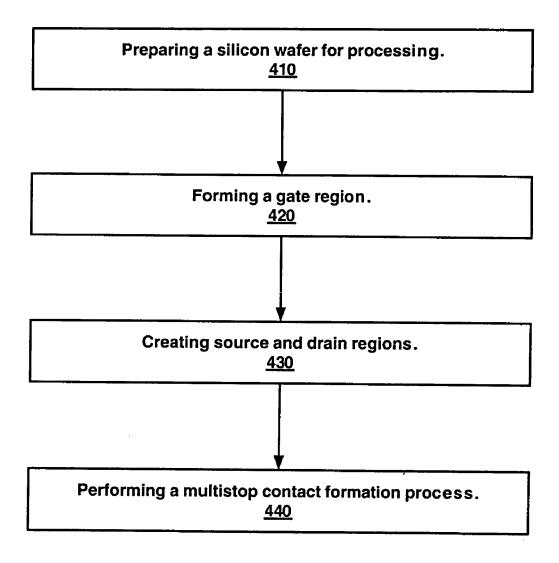

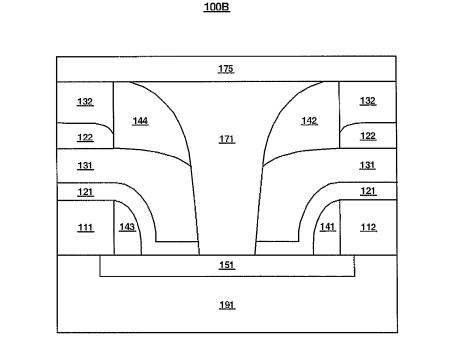

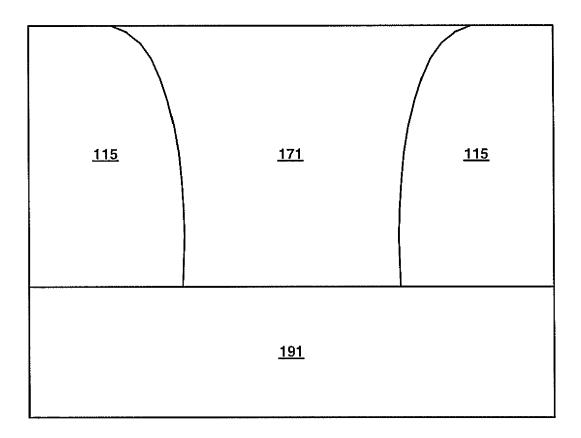

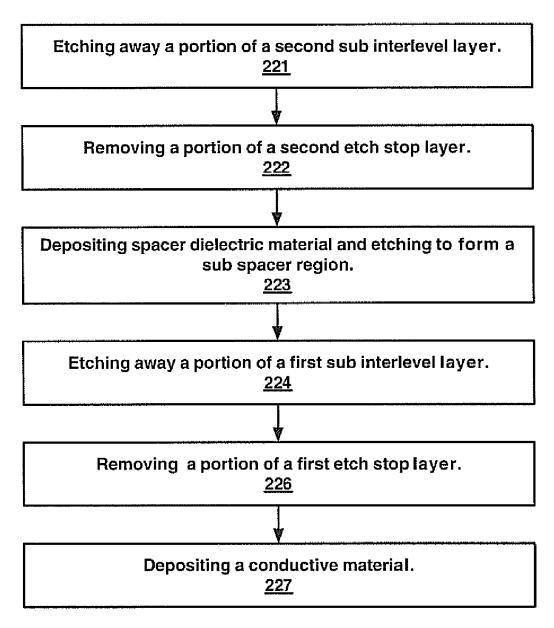

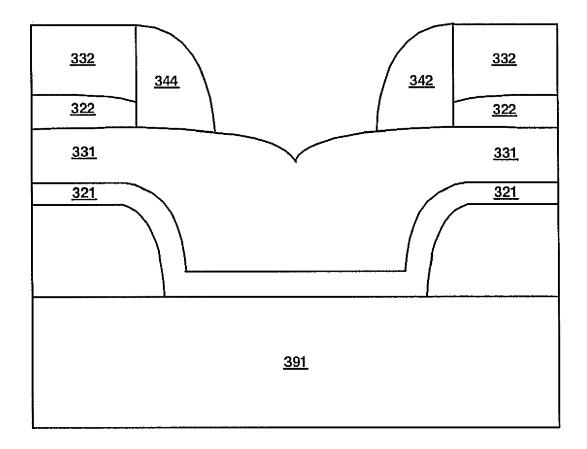

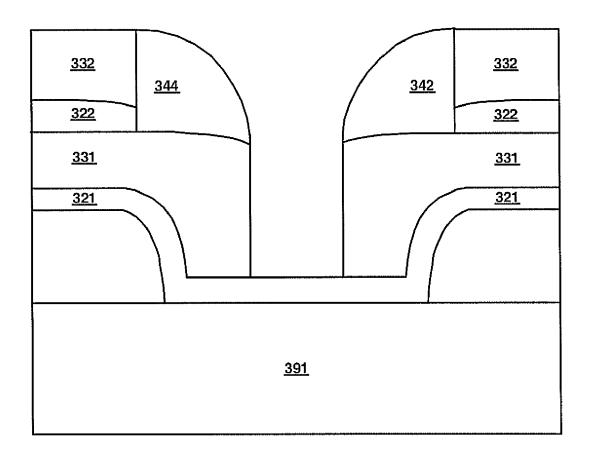

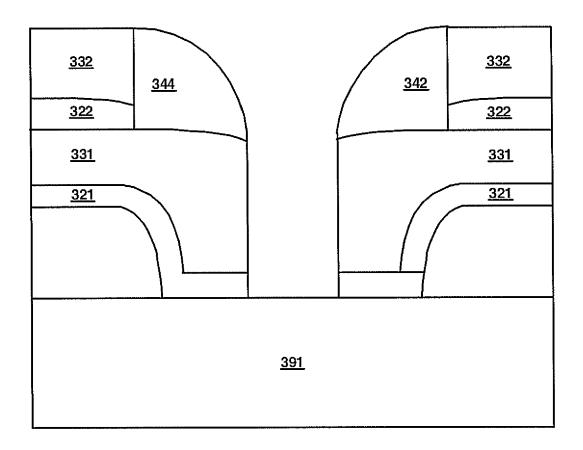

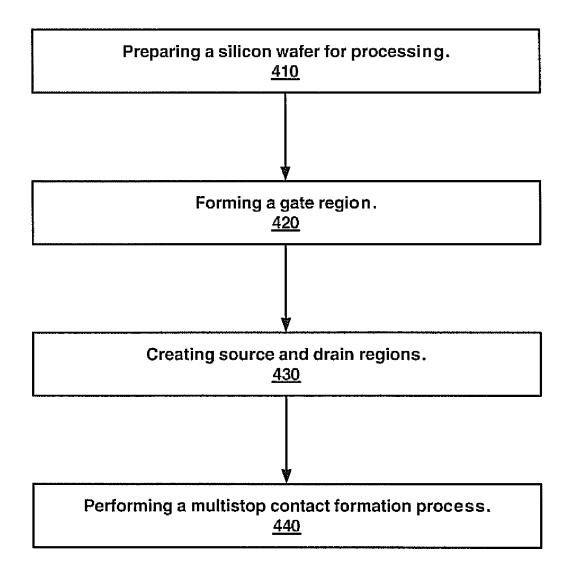

136. The '727 patent is generally directed to semiconductor formation, particularly to semiconductor contact formation using multiple etch stop layers and sub interlevel dielectric layers.

137. The '727 patent explains that semiconductor integrated circuit manufacturing efforts are usually complicated by ever increasing demands for greater functionality. Integrated circuits with more components typically provide greater functionality. One traditional focus for achieving greater densities was directed towards reducing the size of individual components (e.g., transistors). Semiconductor contact formation processes usually include the creation of a contact void for deposition of the contact layer. The smaller the contact void, the more compact the contact and the greater the possible component density. However, decreases in contact sizes can be limited by contact void creation processes (e.g., lithographic etching processes). Standard lithographic etching and removal processes traditionally had difficulty producing relatively small contact voids. Complex processes that attempted to create smaller voids were often cost prohibitive or nonfeasible.

138. The '727 patent teaches, among other things, how to use multiple etch stop sublayers and dielectric layers to form contacts which allow semiconductor devices to be densely packed. The '727 patent process allows for the ability to precisely form semiconductor contact regions in a convenient and efficient manner. One exemplary benefit of the '727 patent contact formation process is that the process facilitates the fabrication of contact regions with a relatively small substrate coupling area and relatively large metal layer coupling area. The relatively small substrate coupling area can permit multiple active regions in an integrated circuit to be arranged

#### Case 1:19-cv-02083-CFC Document 16 Filed 02/14/20 Page 41 of 51 PageID #: 299

relatively close to one another, while the relatively large metal layer coupling area facilitates avoidance of critical dimension issues. A conducting material's critical dimension may limit how small a contact can be and still operate reliably.

139. Qualcomm has directly infringed, and continues to directly infringe, one or more claims of the '727 patent under 35 U.S.C. § 271(a) and/or 35 U.S.C. § 271(g), either literally and/or under the doctrine of equivalents, by, among other things, making, using, selling, offering to sell, and/or importing (including importing products made by a patented process) in or into the United States without authorization products covered by one or more claims of the '727 patent, including, but not limited to, products such as the MSM8994 semiconductor device and other products in the Snapdragon 810 and Snapdragon 808 series product families; other Qualcomm 20 nm and smaller process node semiconductor devices, integrated circuits, and products; and all other semiconductor devices, integrated circuits, and products with similar infringing technology ("the Accused '727 Products").

140. As one non-limiting example, Qualcomm infringes claim 1 of the '727 patent. For example, the method used to produce Qualcomm's MSM8994 Snapdragon 810 semiconductor device performs the steps of:

a. forming a gate region (e.g., transistor gate of the MSM8994 Snapdragon 810) and source and drain regions (e.g., source and drain of a transistor in the MSM8994 Snapdragon 810);

b. depositing a multiple etch stop layer comprising (e.g., two layer etch stop layer comprised of silicon nitride in the MSM8994 Snapdragon 810);

c. depositing a first etch stop layer over the substrate (e.g., first silicon nitride etch stop layer in the MSM8994 Snapdragon 810);

d. depositing a sub interlevel dielectric layer over the first etch stop layer (e.g., oxide dielectric layer in the MSM8994 Snapdragon 810);

e. depositing a second etch stop layer over the dielectric layer (e.g., second silicon nitride etch stop layer in the MSM8994 Snapdragon 810) wherein said second etch stop layer has similar selectivity characteristics as the first etch stop layer (e.g., both etch stop layers being comprised of silicon nitride in the MSM8994 Snapdragon 810);

f. depositing a second sub interlevel dielectric layer over the second etch stop layer (e.g., oxide dielectric layer in the MSM8994 Snapdragon 810);