# UNITED STATES PATENT AND TRADEMARK OFFICE

\_\_\_\_\_

# BEFORE THE PATENT TRIAL AND APPEAL BOARD

INTEL CORPORATION,

Petitioner

v.

FG SRC LLC,

Patent Owner

CASE NO.: 2020-01449 PATENT NO. 7,149,867

\_\_\_\_\_

# DECLARATION OF EILEEN D. MCCARRIER

Mail Stop **PATENT BOARD**Patent Trial and Appeal Board

U.S. Patent and Trademark Office

P.O. Box 1450

Alexandria, VA 22313-1450

# I, Eileen D. McCarrier, declare as follows:

- 1. I am currently Manager of Research Services at Pillsbury Winthrop Shaw Pittman LLP, where I have worked as a reference librarian and manager of research services for 26 years.

- 2. I make this declaration based on my own personal knowledge, including my knowledge of library science practices and the evidence cited herein.

- 3. I earned a Master of Arts degree in Library Science from the University of Wisconsin-Madison in 1980, and I have worked as a law librarian for 40 years.

- 4. I have prepared this declaration in connection with the above-captioned *inter partes* review ("IPR") proceeding for which I obtained library copies of previously filed Exhibits 1003 and 1004. Each of these articles was published by the Institute of Electrical and Electronics Engineers, Inc. ("IEEE"), a widely recognized publisher of technical papers spanning a broad range of technologies including electronics, electrical engineering, telecommunications, computing, and more. The IEEE publishes thousands of conference papers every year, including by making them publicly available via its Xplore digital library. The IEEE's collection of publications is recognized within the reference library field as an authoritative source of consolidated published papers in electrical engineering, computer science, and related fields.

- 5. The primary holders of the original printed versions of IEEE conference proceedings from the 1996–2000 era are generally university libraries across the United States. However, at the time of the drafting of this declaration, safety protocols relating to COVID-19 continue to restrict the ability of members of the public to physically access many of these institutions. To accommodate these safety procedures, the library copies described below were physically located by library staff, digitally scanned, and then emailed directly to me.

# Library copies of Zhang, Exhibit 1003

- 6. X. Zhang et al., Architectural Adaptation for Application-Specific Locality Optimizations, IEEE (1997), published in the Proceedings of the International Conference on Computer Design VLSI in Computers and Processors (IEEE, October 12–15, 1997), 150–156 ("Zhang") was filed as Exhibit 1003 with the petition in the above-captioned IPR proceeding.

- 7. A true and correct copy of Zhang obtained from the Library of the Missouri University of Science and Technology, Rolla, Missouri, part of the University of Missouri system, is attached as Appendix EDM01. I personally received this copy as a pdf from the interlibrary loan department of C. L. Wilson Library.

# Library copies of Gupta, Exhibit 1004

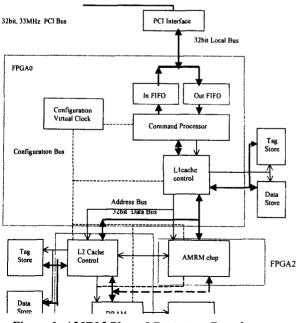

- 8. R. Gupta, Architectural Adaptation in AMRM Machines, Proceedings of the IEEE Computer Society Workshop on VLSI 2000 (IEEE, April 27–28, 2000), 75–79 ("Gupta") was filed as Exhibit 1004 with the above-captioned IPR petition.

- 9. A true and correct copy of Gupta obtained from the Georgia Tech Library, Georgia Institute of Technology is attached as Appendix EDM02. I personally received this copy as a pdf from the library's Interlibrary Loan Office.

I declare under penalty of perjury that the foregoing is true and correct.

Date: March 31, 2021

Eileen D. McCarrier

Eilea D. Milaman

# Appendix EDM01

# LIBRARY UNIVERSITY OF MISSOURI-ROLLA 1870 MINER CIRCLE ROLLA, MISSOURI 65409-0060

Intel Exhibit 1028 - 5

DEMCO

# **Proceedings**

# International Conference on Computer Design VLSI in Computers and Processors

# **Proceedings**

# International Conference on Computer Design

# **VLSI** in Computers and Processors

October 12-15, 1997

Austin, Texas

Sponsored by

IEEE Computer Society Technical Committee on Design Automation

IEEE Circuits and Systems Society

Los Alamitos, California

Washington

Brussels

Tokyo

# Copyright © 1997 by The Institute of Electrical and Electronics Engineers, Inc. All rights reserved

Copyright and Reprint Permissions: Abstracting is permitted with credit to the source. Libraries may photocopy beyond the limits of US copyright law, for private use of patrons, those articles in this volume that carry a code at the bottom of the first page, provided that the per-copy fee indicated in the code is paid through the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923.

Other copying, reprint, or republication requests should be addressed to: IEEE Copyrights Manager, IEEE Service Center, 445 Hoes Lane, P.O. Box 133, Piscataway, NJ 08855-1331.

The papers in this book comprise the proceedings of the meeting mentioned on the cover and title page. They reflect the authors' opinions and, in the interests of timely dissemination, are published as presented and without change. Their inclusion in this publication does not necessarily constitute endorsement by the editors, the IEEE Computer Society, or the Institute of Electrical and Electonics Engineers, Inc.

> IEEE Computer Society Order Number PR08026 ISBN 0-8186-8026-X ISBN 0-8186-8207-8 (case) ISBN 0-8186-8208-6 (microfiche) IEEE Order Plan Catalog Number 97CB36149 ISSN 1063-6404

### Additional copies may be ordered from:

**IEEE Computer Society** Customer Service Center 10662 Los Vaqueros Circle P.O. Box 3014 Los Alamitos, CA 90720-1314 Tel: + 1-714-821-8380

Fax: +1-714-821-4641

E-mail: cs.books@computer.org

IEEE Service Center 445 Hoes Lane P.O. Box 1331 Piscataway, NJ 08855-1331 Tel: + 1-908-981-1393

Fax: +1-908-981-9667 mis.custserv@computer.org IEEE Computer Society 13, Avenue de l'Aquilon B-1200 Brussels BELGIUM

Tel: + 32-2-770-2198 Fax: + 32-2-770-8505 euro.ofc@computer.org **IEEE Computer Society** Ooshima Building 2-19-1 Minami-Aoyama Minato-ku, Tokyo 107 **JAPAN** Tel: +81-3-3408-3118

Fax: +81-3-3408-3553 tokyo.ofc@computer.org

Editorial production by Ian Torwick Cover design by Joseph Daigle/Studio Productions Printed in the United States of America by Technical Communication Services

11-25-97

# **Table of Contents**

# ICCD '97 Conference Program

| 1997 Technical F | Program |

|------------------|---------|

|------------------|---------|

| Welcome to ICCD'97                                                                                                                        |             |

|-------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Program Committee                                                                                                                         | xvi         |

| Additional Referees                                                                                                                       | xix         |

| Session 1.1: Keynote Speech                                                                                                               |             |

| Intelligent RAM (IRAM): the Industrial Setting, Applications, and Architecture                                                            | s2          |

| D. Patterson, K. Asanovic, A. Brown, R. Fromm, J. Golbus, B. Gribstad,                                                                    |             |

| K. Keeton, C. Kozyrakis, D. Martin, S. Perissakis, R. Thomas, N. Treuhaft, and K Yelick, University of California at Berkeley, California |             |

| Session 1.2: CAD Plenary                                                                                                                  |             |

| Chair: Andreas Kuehlmann, IBM T. J. Watson Research Center                                                                                |             |

| A Brief History of the Future of Semiconductor Electronic Design Automation .                                                             | 10          |

| Ron Rohrer, TBD Consultants                                                                                                               |             |

| Concurrent Sessions 1.3                                                                                                                   |             |

| Session 1.3.1: Special Session: Industrial Applications of Formal Verific                                                                 | cation      |

| Organizer and Chair: Andreas Kuehlmann, IBM T. J. Watson Resea                                                                            | ırch Center |

| Formal Implementation Verification of the Bus Interface Unit for the Alpha 21                                                             |             |

| Microprocessor                                                                                                                            | 16          |

| G.P. Bischoff, K.S. Brace, S. Jain, and R. Razdan                                                                                         |             |

| Intertwined Development and Formal Verification of a 60x bus Model                                                                        | 25          |

| M. Kaufmann and C. Pixley                                                                                                                 |             |

| Formally Specifying and Mechanically Verifying Programs for the Motorola Co                                                               |             |

| Arithmetic Processor DSP                                                                                                                  | 31          |

| B.C. Brock and W.A. Hunt, Jr.                                                                                                             | 0.5         |

| BIST-Based Fault Diagnosis in the Presence of Embedded Memories                                                                           | 37          |

| J. Savir                                                                                                                                  | .40         |

| Built-in Self Test for Content Addressable Memories                                                                                       | 40          |

| YS. Kang, JC. Lee, and S. Kang                                                                                                            | 5.4         |

| Pseudo-Random Pattern Testing of Bridging Faults                                                                                          |             |

| N.A. Touba and E.J. McCluskey                                                                                                             |             |

| Session 1.3.3: Simulation and Power Estimation                                                                                            |             |

| Chair: Teng-Sheng Moh, Silicon Valley Research, Inc.                                                                                      |             |

| Novel Simulation of Deep-Submicron MOSFET Circuits                                                                                        | 62          |

| S. Bruma and R.H.J.M. Otten                                                                                                               |             |

| Time-Stamped Transition Density for the Estimation of Delay Dependent                                                                     |             |

| Switching Activities                                                                                                                      | 68          |

| H. Choi and S.H. Hwang                                                                                                                    |             |

| Chair: Jim Bondi, Texas Instruments                                                                       |

|-----------------------------------------------------------------------------------------------------------|

| Elastic History Buffer: A Low-Cost Method to Improve Branch Prediction Accuracy                           |

| MD. Tarlescu, K.B. Theobald, and G.R. Gao                                                                 |

| Design Optimization for High-Speed Per-address Two-level Branch Predictors                                |

| IC.K. Chen, CC. Lee, M.A. Postiff, and T.N. Mudge                                                         |

| PA-8000: A Case Study of Static and Dynamic Branch Prediction                                             |

| Concurrent Sessions 1.4                                                                                   |

| Session 1.4.1: New Techniques for Gate-Sizing and Retiming                                                |

| Chair: Derek Beatty, Motorola, Inc.                                                                       |

| Discrete Drive Selection for Continuous Sizing                                                            |

| R. Haddad, L.P.P.P. van Ginneken, and N. Shenoy                                                           |

| Continuous Retiming: Algorithms and Applications                                                          |

| Optimal Clock Period Clustering for Sequential Circuits with Retiming                                     |

| A.K. Karandikar, P. Pan, and C.L. Liu                                                                     |

| Session 1.4.2: Circuit Modeling                                                                           |

| Chair: Sandip Kundu, IBM Corp.                                                                            |

| Comparison between nMOS Pass-Transistor logic style vs. CMOS                                              |

| Complementary Cells                                                                                       |

| R. Mehrotra, M. Pedram, and X. Wu                                                                         |

| Circuit-Based Description and Modeling of Electromagnetic Noise Effects in Packaged Low-Power Electronics |

| A.C. Cangellaris, W. Pinello, and A. Ruehli                                                               |

| Transistor-Level Sizing and Timing Verification of Domino Circuits in the                                 |

| Power PC Microprocessor                                                                                   |

| A. Dharchoudhury, D. Blaauw, J. Norton, S. Pullela, and J. Dunning                                        |

| Session 1.4.3: Novel Architectures                                                                        |

| Chair: Greg Fisher, Printronix Corporation                                                                |

| Architectural Adaptation for Application-Specific Locality Optimization                                   |

| X. Zhang, A. Dasdan, M. Schulz, R.K. Gupta, and A.A. Chien                                                |

| A New Processor Architecture for Digital Signal Transport Systems                                         |

| M. Inamori, K. Ishii, A. Tsutsui, K. Shirakawa H. Nakada, and T. Miyazaki                                 |

| Short Papers                                                                                              |

| PROPHID: A Heterogeneous Multi-Processor Architecture for Multimedia                                      |

| J.A. Leijten, J.L. van Meerbergen, A.A. Timmer, and J.A.G. Jess                                           |

|                                                                                                           |

Power Compiler: A Gate-Level Power Optimization and Synthesis System......74

B. Chen and I. Nedelchev

Session 1.3.4: Branch Prediction

| Enhanced Compression Techniques to Simplify Program Decompression and Execution               |

|-----------------------------------------------------------------------------------------------|

| M. Breternitz, Jr. and R. Smith                                                               |

| Session 1.4.4: Low Power Architectures                                                        |

| Chair: Tim Brodnax, IBM                                                                       |

| A Low Power Approach to Floating Point Adder Design                                           |

| R.V.K. Pillai, D. Al-Khalili, and A.J. Al-Khalili                                             |

| Design and Implementation of Low-Power Digit-Serial Multipliers                               |

| YN. Chang, J.H. Satyanarayana, and K.K. Parhi                                                 |

| On Complexity Reduction of FIR Digital Filters Using Constrained                              |

| Least Squares Solution                                                                        |

| K. Muhammad and K. Roy                                                                        |

| Concurrent Session 1.5                                                                        |

| Session 1.5.1: Timing Optimization for Deep Submicron Technology                              |

| Chair: Masahiro Fujita, Fujitsu Laboratories of America                                       |

| An Integrated Placement and Synthesis Approach for Timing Closure of PowerPC™ Microprocessors |

| S. Hojat and P. Villarrubia                                                                   |

| Post-Layout Circuit Speed-up by Event Elimination                                             |

| H. Vaishnav, CK. Lee, and M. Pedram                                                           |

| Clustering and Load Balancing for Buffered Clock Tree Synthesis                               |

| A.D. Mehta, YP. Chen, N. Menezes, D.F. Wong, and L.T. Pileggi                                 |

| CMOS Gate Delay Models for General RLC Loading                                                |

| R. Arunachalam, F. Dartu, and L.T. Pileggi                                                    |

| Session 1.5.2: Special Session: The G4 S/390 Microprocessor                                   |

| Organizer: Andreas Kuehlmann, IBM T. J. Watson Research Center                                |

| Chair: Sumit Dasgupta, IBM                                                                    |

| Design Methodology for the High-Performance G4 S/390 Microprocessor                           |

| K.L. Shepard, S. Carey, D.K. Beece, R. Hatch, and G. Northrop                                 |

| A High-Frequency Custom CMOS S/390 Microprocessor                                             |

| C.F. Webb and J.S. Liptay                                                                     |

| High Performance CMOS Circuit Techniques for the G-4 S/390 Microprocessor24                   |

| J. Warnock, L. Sigal, B. Curran, and Y. Chan                                                  |

| A 400 MHz, 144Kb CMOS ROM MACRO for an IBM S/390-Class Microprocessor25                       |

| A. Tuminaro                                                                                   |

| Session 1.5.3: Multiprocessor Communication                                                   |

| Chair: Wai-Chi Fang, Jet Propulsion Laboratory                                                |

| A Comparative Evaluation of Hierarchical Network Architecture of the HP-Convex Exemplar25     |

| R. Castaneda, X. Zhang, and J.M. Hoover, Jr.                                                  |

| Ring based Multiprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 267 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| H. Oi and N. Ranganathan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| An Approach to Network Caching for Multimedia Objects                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 273 |

| M.A. Kozuch, W. Wolf, and A. Wolfe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| Development of a High Bandwidth Merged Logic/DRAM Multimedia Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 279 |

| W.K. Luk, Y. Katayama, W. Hwang, M. Wordeman, T. Kirihata, A. Satoh,                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| S. Munetoh, H. Wong, B. El-Kareh, P. Xio, and R. Joshi                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| Session 1.5.4: Asynchronous Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| Chair: Eric Chou, Hewlett-Packard ULSI Labs                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| TITAC-2: An asynchronous 32bit microprocessor based on Scalable -Delay-                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| Insensitive model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 288 |

| A. Takamura, M. Kuwako, M. Ima, T. Fujii, M. Ozawa, I. Fukasaku,<br>Y. Ueno, and T. Nanya                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| An Evaluation of Asynchronous and Synchronous Design for Superscalar                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 295 |

| A. Davey and D. Loyd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| Synthesis of High Speed Delay-Insensitive Combinational Iterative Tree Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                      | 301 |

| FC. Cheng                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| Asynchronous Wrapper for Heterogeneous Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 307 |

| D.S. Bormann and P.Y.K. Cheung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| Concurrent Session 1.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| Session 1.6.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| Session 1.6.1 Panel: The War of the Roses: Designers versus Tool Developers                                                                                                                                                                                                                                                                                                                                                                                                                                          | 317 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 317 |

| Panel: The War of the Roses: Designers versus Tool Developers                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 317 |

| Panel: The War of the Roses: Designers versus Tool Developers                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 317 |

| Panel: The War of the Roses: Designers versus Tool Developers                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 317 |

| Panel: The War of the Roses: Designers versus Tool Developers                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 317 |

| Panel: The War of the Roses: Designers versus Tool Developers                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 317 |

| Panel: The War of the Roses: Designers versus Tool Developers                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 317 |

| Panel: The War of the Roses: Designers versus Tool Developers  Organizer: Andreas Kuehlmann, IBM T. J. Watson Research Center  Moderator: Daniel Beece, IBM T. J. Watson Research Center  Panelists:  Barbara Chappell, Intel Corp.  Robert Damiano, Synopsys, Inc.  Charlie Malley, Hewlett-Packard                                                                                                                                                                                                                 | 317 |

| Panel: The War of the Roses: Designers versus Tool Developers  Organizer: Andreas Kuehlmann, IBM T. J. Watson Research Center  Moderator: Daniel Beece, IBM T. J. Watson Research Center  Panelists:  Barbara Chappell, Intel Corp.  Robert Damiano, Synopsys, Inc.  Charlie Malley, Hewlett-Packard  Yiannos Manoli, University of Saarland                                                                                                                                                                         | 317 |

| Panel: The War of the Roses: Designers versus Tool Developers  Organizer: Andreas Kuehlmann, IBM T. J. Watson Research Center  Moderator: Daniel Beece, IBM T. J. Watson Research Center  Panelists:  Barbara Chappell, Intel Corp.  Robert Damiano, Synopsys, Inc.  Charlie Malley, Hewlett-Packard  Yiannos Manoli, University of Saarland  David F. Reed, Advanced Micro Devices  Steven E. Schulz, Texas Instruments                                                                                             | 317 |

| Panel: The War of the Roses: Designers versus Tool Developers  Organizer: Andreas Kuehlmann, IBM T. J. Watson Research Center  Moderator: Daniel Beece, IBM T. J. Watson Research Center  Panelists:  Barbara Chappell, Intel Corp. Robert Damiano, Synopsys, Inc. Charlie Malley, Hewlett-Packard Yiannos Manoli, University of Saarland David F. Reed, Advanced Micro Devices Steven E. Schulz, Texas Instruments  Session 1.6.2                                                                                   |     |

| Panel: The War of the Roses: Designers versus Tool Developers  Organizer: Andreas Kuehlmann, IBM T. J. Watson Research Center  Moderator: Daniel Beece, IBM T. J. Watson Research Center  Panelists:  Barbara Chappell, Intel Corp.  Robert Damiano, Synopsys, Inc.  Charlie Malley, Hewlett-Packard  Yiannos Manoli, University of Saarland  David F. Reed, Advanced Micro Devices  Steven E. Schulz, Texas Instruments  Session 1.6.2  Panel: If Software is King for Systems-on-Silicon, What's New in Compilers? |     |

| Panel: The War of the Roses: Designers versus Tool Developers                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| Panel: The War of the Roses: Designers versus Tool Developers                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| Panel: The War of the Roses: Designers versus Tool Developers                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| Panel: The War of the Roses: Designers versus Tool Developers                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| Panel: The War of the Roses: Designers versus Tool Developers                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| Panel: The War of the Roses: Designers versus Tool Developers                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

Effect of Message Length and Processor Speed on the Performance of the Bidirectional

| Session 2.1 Design and Test Plenary  Chair: Magdy Abadir, Motorola, Inc.                       |     |

|------------------------------------------------------------------------------------------------|-----|

| Design and Test: The Lost World                                                                | 328 |

| W. Joyner, IBM T. J. Watson Research Center                                                    |     |

| Concurrent Sessions 2.2                                                                        |     |

| Session 2.2.1: Binary Decision Diagrams                                                        |     |

| Chair: B. Bischoff, Digital Equipment Corporation                                              |     |

| Equivalence Checking Using Abstract BDDs                                                       | 332 |

| S. Jha, Y. Lu, M. Minea, and E.M. Clarke                                                       |     |

| Speeding up Variable Reordering of OBDDs                                                       | 338 |

| C. Meinel and A. Slobodova                                                                     |     |

| Dynamic Reordering in a Breadth-First Manipulation Based BDD package: Challenges and Solutions | 344 |

| R.K. Ranjan, W. Gosti, R.K. Brayton, and A. Sangiovanni-Vincentelli                            | 011 |

| Timed Binary Decision Diagrams                                                                 | 352 |

| Z. Li, Y. Zhao, Y. Min, and R.K. Brayton                                                       | 002 |

| Session 2.2.2: Advanced Test Topics                                                            |     |

| Chair: Magdy Abadir, Motorola                                                                  |     |

| Vector Restoration Based Static Compaction of Test Sequences for Synchronous                   |     |

| Sequential Circuits                                                                            | 360 |

| I. Pomeranz and S.M. Reddy                                                                     |     |

| Nonenumerative Path Delay Fault Coverage Estimation with Optimal Algorithms                    | 366 |

| D. Kagaris, S. Tragoudas, and D. Karayiannis                                                   |     |

| Properties of the Input Pattern Fault Model                                                    | 372 |

| R.D. (Shawn) Blaton and J.P. Hayes                                                             |     |

| A new approach for Initialization Sequences Computation for Synchronous Sequential Circuits    | 381 |

| F. Corno, P. Prinetto, M. Rebaudengo, M.S. Reorda, and G. Squillero                            | 001 |

| Session 2.2.3: Embedded Software and Systems                                                   |     |

| Chair: Rolf Ernst, Technische Universitaet Braunschweig, Germany                               |     |

| Real Time Operating Systems for Embedded Computing                                             | 388 |

| Y. Li, M. Potkonjak and W. Wolf                                                                |     |

| Allocation and Data Arrival Design of Hard Real Time Systems                                   | 393 |

| D.L. Rhodes and W. Wolf                                                                        |     |

| Improving Design Turnaround Time Via Two-Levels Hw/Sw Co-Simulation                            | 400 |

| A. Allara, S. Filipponi, W. Fornaciari, F. Salice, and D. Sciuto                               |     |

| Session 2.2.4: Low Power Issues                                                                |     |

| Chair: Jose L. Cruz-Rivera, University of Puerto Rico-Mayaguez                                 |     |

| Power Constrained Design of Multiprocessor Interconnection Networks                            | 408 |

| C.S. Patel S.M. Chai S. Valamanchili and D.E. Schimmel                                         |     |

| Memory Traffic and Data Cache Behavior of an MPEG-2 Software Decoder                                     | 417 |

|----------------------------------------------------------------------------------------------------------|-----|

| Asynchronous Transpose-Matrix Architectures                                                              | 423 |

| J.A. Tierno and P. Kudva                                                                                 |     |

| A Low Power Smart Vision System Based on Active Pixel Sensor                                             |     |

| Integrated with Programmable Neural Processor                                                            | 429 |

| WC. Fang, G. Yang, B. Pain, and B.J. Sheu                                                                |     |

| Concurrent Sessions 2.3                                                                                  |     |

| Session 2.3.1: Formal Verification Methods                                                               |     |

| Chair: Warren Hunt, Jr., Computational Logic, Inc.                                                       |     |

| Formal Verification of the HAL S1 System Cache Coherence Protocol                                        | 438 |

| A.J. Hu, M. Fujita, and C. Wilson                                                                        |     |

| A Survey of Techniques for Formal Verification of Combinational Circuits                                 | 445 |

| J. Jain, A. Narayan, M. Fujita, and A. Sangiovanni-Vincentelli                                           |     |

| Checking Formal Specifications under Simulation                                                          | 455 |

| W. Canfield, E.A. Emerson, and A. Saha                                                                   |     |

| Session 2.3.2: Mixed Signal Design and Test                                                              |     |

| Chair: Yervant Zorian, Logic Vision                                                                      |     |

| Built-In Temperature Sensors for On-line Thermal Monitoring of                                           |     |

| Microelectronic Structures                                                                               | 462 |

| K. Arabi and B. Kaminska                                                                                 |     |

| Develop of Hierarchical Testability Design Methodologies for Analog/ Mixed-Signal                        | 400 |

| Integrated Circuits                                                                                      | 468 |

| CP. Wang and CL. Wey  A Novel Test Set Design for Parametric Testing of Analog and Mixed-Signal Circuits | 171 |

| J. Chen and A. Ramachandran                                                                              | 4/4 |

| o. Oleh tha A. Ramachanaran                                                                              |     |

| Session 2.3.3: FPGA Design                                                                               |     |

| Chair: Paul Franzon, North Carolina State University                                                     |     |

| On the Construction of Universal Series-Parallel Functions for Logic Module Design                       | 482 |

| F.Y. Young and D.F. Wong                                                                                 |     |

| An Universal Pezaris Array Multiplier Generator for SRAM-Based FPGAs                                     | 489 |

| J. Stohmann and E. Barke                                                                                 | 400 |

| Channel Segmentation Design for Symmetrical FPGAs                                                        | 496 |

| WK. Mak and D.F. Wong                                                                                    |     |

| Session 2.3.4: Cache Technology I                                                                        |     |

| Chair: Mauricio Breternitz, Motorola Inc.                                                                |     |

| Multi-Column Implementations for Cache Associativity                                                     | 504 |

| C. Zhang, X. Zhang, and Y. Yan                                                                           |     |

| Design and Performance Evaluation of a Cache Assist to Implement                                         |     |

| Selective Caching.                                                                                       | 510 |

| L.K. John and A. Subramanian                                                                             |     |

| J.A. Rivers, E.S. Tam, and E.S. Davidson                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------|

| Concurrent Sessions 2.4                                                                                                  |

| Session 2.4.1: Embedded Tutorial Practical Issue of Interconnect Analysis in Deep Submicron Integrated Circuits          |

| Session 2.4.2: Fault Diagnosis                                                                                           |

| Chair: Raj Raina, Motorola, Inc.                                                                                         |

| First Results of System Level Fault Tolerant Design Validation Through  Laser Fault Injection                            |

| W. A. Moreno , F.J. Falquez, J.R. Samon Jr., and T. Smith                                                                |

| Integrated Diagnostics for Embedded Memory Built-in Self Test<br>on PowerPC™ Devices                                     |

| C. Hunter                                                                                                                |

| A TSC Evalution Function for Combinatorial Circuits                                                                      |

| Session 2.4.3: Special Session: Low Power Design Issues  Chair: Sarma Vrudhula, University of Arizona                    |

| An Architectural Power Optimization Case Study Using High-level Synthesis 562                                            |

| CT. Chen and K. Kucukcakar  High-Level Design Synthesis of Low Power, VLIW Processor for the IS-54  VSELP Speech Encoder |

| R. Henning and C. Chakrabarti                                                                                            |

| Session 2.4.4: Cache Technology II                                                                                       |

| Chair: Michael Stumm, University of Toronto                                                                              |

| Fast Cache Access with Full-Map Block Directory                                                                          |

| A Data Alignment Technique for Improving Cache Performance                                                               |

| P.R. Panda, H. Nakamura, N.D. Dutt, and A. Nicolau                                                                       |

| Instruction Prefetching Using Branch Prediction Information                                                              |

| Session 3.1: Architecture & Algorithm Plenary                                                                            |

| Chair: J. Robert Jump, Rice University                                                                                   |

| Is Wireless Data Dead?60                                                                                                 |

| Panda Vata University of California at Barbeley California                                                               |

# **Concurrent Sessions 3.2**

| Session 3.2.1: Layout Partitioning and Synthesis                                           |      |

|--------------------------------------------------------------------------------------------|------|

| Chair: Georg Pelz, Gerhard-Mercator-University-GH, Duisburg, Germany                       |      |

| An Efficient Multi-Way Algorithm for Balanced Partitioning of VLSI Circuits                | 608  |

|                                                                                            | C1.4 |

| Partitioning Under Timing and Area Constraints                                             | 614  |

| A Parallel Circuit-Partitioned Algorithm for Timing Driven Standard Cell Placement         | 601  |

| J.A. Chandy, and P. Banerjee                                                               | 021  |

| Crosstalk-Constrained Maze Routing Based on Lagrangian Relaxation                          | 628  |

| H. Zhou and D.F. Wong                                                                      | 020  |

| Session 3.2.2: Design for Testability & Test Synthesis                                     |      |

| Chair: Sujit Dey, NEC                                                                      |      |

| High Level Test Synthesis Across the Boundary of Behavioral and Structural  Domains        | 636  |

| K. Lai, C.A. Papachristou, and M. Baklashov                                                |      |

| Power Driven Partial Scan                                                                  | 642  |

| JY. Jou and MC. Nien                                                                       |      |

| Synthesis of Delay Verifiable Sequential Circuits using Partial Enhanced Scan              | 648  |

| R.C. Tekumalla and P.R. Menon                                                              |      |

| Application of a Testing Framework to VHDL Descriptions at Different  Abstraction Levels   | 654  |

| M. Bacis, G. Buonanno, F. Ferrandi, F. Fummi, L. Gerli, and D. Sciuto                      |      |

| Session 3.2.3: Embedded Tutorial                                                           |      |

| Practical Advances in Asynchronous Design                                                  | 662  |

| Chair: Rob Roy, NEC, Inc.                                                                  |      |

| Presentors:                                                                                |      |

| Eric Brunvand of University of Utah                                                        |      |

| Steve Nowick of Columbia University                                                        |      |

| Kenneth Yun of University of California at San Diego                                       |      |

| Session 3.2.4: Arithmetics                                                                 |      |

| Chair: Joe Cavallaro, Rice University                                                      |      |

| Benchmarking and Analysis of Architectures for CAD Applications                            | 670  |

| A. Mehrotra, S. Qadeer, R.K. Ranjan, and R.H. Katz                                         |      |

| Fast Low-Energy VLSI Binary Addition                                                       | 676  |

| A Floating-Point Divider using Redundant Binary Circuits and an Asynchronous  Clock Scheme | 685  |

| H. Suzuki, H. Mankino, K. Mashiko, and H. Hamano                                           |      |

| Parallel-Array Implementations of A Non-Restoring Square Root Algorithm                    | 690  |

# **Concurrent Session 3.3**

| Session 3.3.1: Asynchronous Design  Chair: Daniel Saab, Case Reserve Western University                         |

|-----------------------------------------------------------------------------------------------------------------|

| Optimizing CMOS Implementations of C-element                                                                    |

| M. Shams, J.C. Ebergen, and M.I. Elmasry                                                                        |

| A Doubly-Latched Asynchronous Pipeline                                                                          |

| R. Kol and R. Ginosar                                                                                           |

| A Pulse-To-Static Conversion Latch With a Self-Timed Control Circuit                                            |

| W. Hwang, R.V. Joshi, and W.H. Henkels                                                                          |

| Session 3.3.2: Special Session: Interconnect Modeling & Repeater Methodologies  Chair: Byron Krauter, IBM Corp. |

| Fast Generation of Statistically-based Worst-Case Modeling of On-Chip Interconnect 720                          |

| N. Chang, V. Kanevsky, O.S. Nakagawa, K. Rahmat, and SY. Oh                                                     |

| A Repeater Optimization Methodology for Deep Sub-Micron, High-Performance Processor                             |

| D. Li, A. Pua, P. Srivastava, and U. Ko                                                                         |

| Critical Voltage Transition Logic: An Ultrafast CMOS Logic Family                                               |

| Session 3.3.3: Finite-State Machine and High-Level Synthesis                                                    |

| Chair: Ramin Hojati, University of California at Berkeley                                                       |

| Divide and Conquer: A Strategy for Synthesis of Low Power Finite State Machines 740                             |

| A. Dasgupta and S. Ganguly                                                                                      |

| Estimation of Maximum Power for Sequential Circuits Considering Spurious Transitions                            |

| CY. Wang and K. Roy                                                                                             |

| Dynamic Bounding of Successor Force Computations in the Force Directed  List Scheduling Algorithm               |

| S. Govindarajan and R. Vemuri                                                                                   |

| Author Index                                                                                                    |

# **Architectural Adaptation for Application-Specific Locality Optimizations**

Xingbin Zhang\* Ali Dasdan\* Martin Schulz<sup>†</sup>

\*Department of Computer Science

University of Illinois at Urbana-Champaign {zhang,dasdan,achien}@cs.uiuc.edu

Rajesh K. Gupta<sup>‡</sup> Andrew A. Chien\*

†Institut für Informatik Technische Universität München schulzm@informatik.tu-muenchen.de

†Information and Computer Science, University of California at Irvine rgupta@ics.uci.edu

### Abstract

We propose a machine architecture that integrates programmable logic into key components of the system with the goal of customizing architectural mechanisms and policies to match an application. This approach presents an improvement over traditional approach of exploiting programmable logic as a separate co-processor by preserving machine usability through software and over traditional computer architecture by providing applicationspecific hardware assists. We present two case studies of architectural customization to enhance latency tolerance and efficiently utilize network bisection on multiprocessors for sparse matrix computations. We demonstrate that application-specific hardware assists and policies can provide substantial improvements in performance on a per application basis. Based on these preliminary results, we propose that an application-driven machine customization provides a promising approach to achieve high performance and combat performance fragility.

# 1 Introduction

Technology projections for the coming decade [1] point out that system performance is going to be increasingly dominated by intra-chip interconnect delay. This presents a unique opportunity for programmable logic as the interconnect dominance reduces the contribution of per stage logic complexity on performance and the marginal costs of adding switching logic in the interconnect. However, the traditional co-processing architecture of exploiting programmable logic as a specialized functional unit to deliver a specific application suffers from the problem of machine retargetability. A system generated using this approach typically can not be retargeted to another application

without repartitioning hardware and software functionality and reimplementing the co-processing hardware. This retargetability problem is an obstacle toward exploiting programmable logic for general purpose computing.

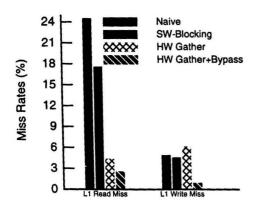

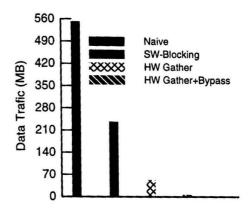

We propose a machine architecture that integrates programmable logic into key components of the system with the goal of customizing architectural mechanisms and policies to match an application. We base our design on the premise that communication is already critical and getting increasingly so [17], and flexible interconnects can be used to replace static wires at competitive performance [6, 9, 20]. Our approach presents an improvement over co-processing by preserving machine usability through software and over traditional computer architecture by providing applicationspecific hardware assists. The goal of application-specific hardware assists is to overcome the rigid architectural choices in modern computer systems that do not work well across different applications and often cause substantial performance fragility. Because performance fragility is especially apparent on memory performance on systems with deep memory hierarchies, we present two case studies of architectural customization to enhance latency tolerance and efficiently utilize network bisection on multiprocessors. Using sparse matrix computations as examples, our results show that customization for application-specific optimizations can bring significant performance improvement (10X reduction in miss rates. 100X reduction in data traffic), and that an application-driven machine customization provides a promising approach to achieve robust, high performance.

The rest of the paper is organized as follows. Section 2 presents our analyses of the technology trends. Section 3 describes our proposed architecture and the project context. We describe our case studies in Section 4 and discuss related work in Section 5. Finally, we conclude with future directions in Section 6.

# 2 Background

Technology projections for the coming decade point out a unique opportunity of programmable logic. However, the traditional co-processing approach of exploiting programmable logic suffers from the problem of machine retargetability, which limits its use for general purpose applications.

# 2.1 Key Technology Trends

The basis for architectural adaptation is in the key trends in the semiconductor technology. In particular, the difference in scaling of switching logic speed and interconnect delays points out increasing opportunities for programmable logic circuits in the coming decade. Projections by the Semiconductor Industry Association (SIA) [1] show that on-chip system performance is going to be increasingly dominated by interconnect delays. Due to these interconnect delays, the on-chip clock periods will be limited to about 1 nanosecond, which is well above the projections based on channel length scaling [1]. Meanwhile, the unit gate delay (inverter with fanout of two) scales down to 20 pico-seconds. Thus, modern day control logic consisting of 7-8 logic stages per cycle would form less than 20% of the total cycle time. This clearly challenges the fundamental design trade-off today that tries to simplify the amount of logic per stage in the interest of reducing the cycle time [14]. In addition, this points to a sharply reduced marginal cost of per stage logic complexity on the circuit-level performance.

The decreasing delay penalty for (re)programmable logic blocks compared to interconnect delays also makes the incorporation of small programmable logic blocks attractive even in custom data paths. Because the interconnect delays scale down much more slowly than transistor switching delays, in the year 2007, the delay of the average length inter-connect (assuming an average interconnect length of 1000X the pitch) would correspond to approximately three gate delays (see [5] for a detailed analysis). This is in contrast to less than half the gate delay of the average interconnect in current process technology. This implies that due to purely electrical reasons, it would be preferred to include at least one inter-connect buffer in a cycle time. This buffer gate when combined with a weak-feedback device would form the core of a storage element that presents less than 50% switching delay overhead (from 20ps to 30ps), making it performance competitive to replace static wires with flexible interconnect.

In view of these technology trends and advances in circuit modeling using hardware description languages (HDLs) such as Verilog and VHDL, the process of hardware design is increasingly a language-level activity, supported by compilation and synthesis tools [11, 12]. With

these CAD and synthesis capabilities, programmable logic circuit blocks are beginning to be used in improving system performance.

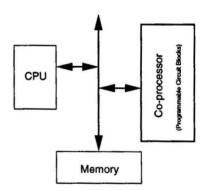

## 2.2 Co-processing

The most common architecture in embedded computing systems to exploit programmable logic can be characterized as one of co-processing, i.e., a processor working in conjunction with dedicated hardware assists to deliver a specific application. The hardware assists are built using programmable circuit blocks for easy interpretation with the predesigned CPU. Figure 1 shows the schematic of a co-processing architecture, where the co-processing hardware may be operated under direct control of the processor which stalls while the dedicated hardware is operational [10], or the co-processing may be done concurrently with software [13]. However, a system generated using this approach typically can not be retargeted to another application without repartitioning hardware and software functionality and reimplementing the co-processing hardware even if the macro-level organization of the system components remains unaffected. This presents an obstacle of exploiting programmable logic for general-purpose computing even though technology trends make it possible to do so.

Figure 1. A co-processing Architecture

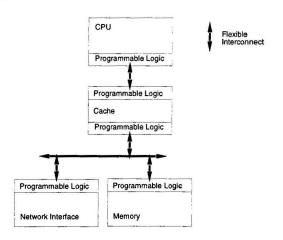

# 3 Architectural Adaptation

We propose an architecture that integrates small blocks of programmable logic into key elements of a baseline architecture, including processing elements, components of the memory hierarchy, and the scalable interconnect, to provide architectural adaptation - the customization of architectural mechanisms and policies to match an application. Figure 2 shows our architecture. Architectural adaptation can be used in the bindings, mechanisms, and policies on the interaction of processing, memory, and communication resources while keeping the macro-level organization the

same and thus preserving the programming model for developing applications. Depending upon the hardware technology used and the support available from the runtime environment, this adaptation can be done statically or at runtime.

Figure 2. An Architecture for Adaptation

Architectural adaptation provides the mechanisms for application-specific hardware assists to overcome the rigid architectural choices in modern computer systems that do not work well across different applications and often cause substantial performance fragility. In particular, the integration of programmable logic with memory components enables application-specific locality optimizations. These optimizations can be designed to overcome long latency and limited transfer bandwidth in the memory hierarchy. In addition, because the entire application remains in software while the underlying hardware is adapted for system performance, our approach improves over co-processing architectures by preserving machine usability through software. The main disadvantage of our approach is the potential increase on system design and verification time due to the addition of programmable logic. We believe that the advances in design technology will address the increase of logic complexity.

# 3.1 Project Context

Our study is in the context of the MORPH [5] project, a NSF point design study for Petaflops architectures in the year 2007 technology window. The key elements of the MORPH (MultiprocessOr with Reconfigurable Parallel Hardware) architecture consists of processing and memory elements embedded in a scalable interconnect. With a small amount of programmable logic integrated with key elements of the system, the proposed MORPH architecture aims to exploit architectural customization for a broad range of purposes such as:

- control over computing node granularity (processormemory association)

- interleaving (address-physical memory element mapping)

- cache policies (consistency model, coherence protocol, object method protocols)

- cache organization (block size or objects)

- · behavior monitoring and adaptation

As an example of its flexibility, MORPH could be used to implement either a cache-coherent machine, a non-cache coherent machine, or even clusters of cache coherent machines connected by put/get or message passing. In this paper, we focus on architectural adaptation in the memory system for locality optimizations such as latency tolerance.

### 4 Case Studies

We present two case studies of architectural adaptation for application-specific locality optimizations. On modern architectures with deep memory hierarchies, data transfer bandwidth and access latency differentials across levels of memory hierarchies can span several orders of magnitude, making locality optimizations critical for performance. Although compiler optimizations can be effective for regular applications such as dense matrix multiply, optimizations for irregular applications can greatly benefit from architectural support. However, numerous studies have shown that no fixed architectural policies or mechanisms, e.g., cache organization, work well for all applications, causing performance fragility across different applications. We present two case studies of architectural adaptation using application-specific knowledge to enhance latency tolerance and efficiently utilize network bisection on multiprocessors.

## 4.1 Experimental Methodology

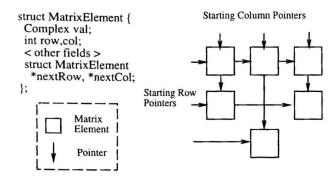

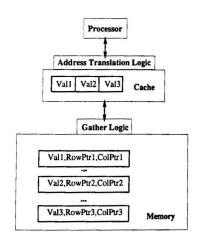

As our application examples, we use the sparse matrix library SPARSE developed by Kundert and Sangiovanni-Vincentelli (version 1.3 available from http://www.netlib.org/sparse/), and an additional sparse matrix multiply routine that we wrote. This library implements an efficient storage scheme for sparse matrices using row and column linked lists of matrix elements as shown in Figure 3. Only nonzero elements are represented, and elements in each row and column are connected by singly linked lists via the nextRow and nextCol fields. Space for elements, which is 40 bytes per matrix element, are allocated dynamically in blocks of elements for efficiency. There are also several one dimensional arrays for storing the root pointers for row and column lists.

Figure 3. Sparse Library Data Structures

We perform cycle-based system-level simulation using a program-driven simulator based on MINT [22] that interprets program binaries and models configurable logic blocks behaviorly. The details of our simulation environment are presented in [4]. Table 1 shows the simulation parameters used. We report our empirical results for current day computer technologies and then use derivative metrics (such as miss rate) to extrapolate potential benefits for future computer systems which will exhibit much higher clock rates and memory sizes. We also manually translated the C routines modeling the customizable logic blocks into HardwareC [18] to evaluate their hardware cost in terms of space and cycle delays. (However, our recent work is focused on automatic translation of these routines to synthesizable blocks [19].)

|               | L1 Cache       | L2 Cache       |

|---------------|----------------|----------------|

| Line Size     | 32B or 64B     | 32B or 64B     |

| Associativity | 1              | 2              |

| Cache Size    | 32KB           | 512KB          |

| Write         | Write back +   | Write back +   |

| Policy        | Write allocate | Write allocate |

| Replacement   |                |                |

| Policy        | Random         | Random         |

| Transfer      | (L1-L2)        | (L2-Mem)       |

| Rate          | 16B/5 cycles   | 8B/15 cycles   |

**Table 1. Simulation Parameters**

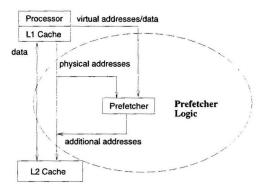

# 4.2 Architectural Adaptation for Latency Tolerance

Our first case study uses architectural adaptation for prefetching. As the gap between processor and memory speed widens, prefetching is becoming increasingly important to tolerate the memory access latency. However, oblivious prefetching can degrade a program's performance by saturating bandwidth. We show two example prefetching schemes that aggressively exploit application access pattern

information.

Figure 4 shows the prefetcher implementation using programmable logic integrated with the L1 cache. The prefetcher requires two pieces of application-specific information: the address ranges and the memory layout of the target data structures. The address range is needed to indicate memory bounds where prefetching is likely to be useful. This is application dependent, which we determined by inspecting the application program, but can easily be supplied by the compiler. The program sets up the required information and can enable or disable prefetching at any point of the program. Once the prefetcher is enabled, however, it determines what and when to prefetch by checking the virtual addresses of cache lookups to check whether a matrix element is being accessed.

Figure 4. Organizations of Prefetcher Logic

The first prefetching example targets records spanning multiple cache lines and for our example, prefetches all fields of a matrix element structure whenever some field of the element is accessed. The pseudocode of this prefetching scheme for the sparse matrix example is shown below, assuming a cache line size of 32 bytes, a matrix element padded to 64 bytes, and a single matrix storage block aligned at 64-byte boundary. Prefetching is triggered only by read misses. Because each matrix element spans two cache lines, the prefetcher generates an additional L2 cache lookup address from the given physical address (assuming a lock-up free L2 cache) that prefetches the other cache line not yet referenced.

```

/* Prefetch only if vAddr refers to the matrix */

GroupPrefetch(vAddr,pAddr,startBlock,endBlock) {

if (startBlock <= vAddr && vAddr < endBlock) {

/* Determine the prefetch address */

if (pAddr & 0x20) ptrLoc = pAddr - 0x20;

else ptrLoc = pAddr + 0x20;

<Initiate transfer of line at ptrLoc to L1 cache>

}}

```

The second prefetching example targets pointer fields that are likely to be traversed when their parent structures are accessed. For example, in a sparse matrix-vector multiply, the record pointed to by the nextRow field is accessed close in time with the current matrix element. The pseudocode below shows the prefetcher code for prefetching the row pointer, assuming a cache line size of 64 bytes. Again prefetching is triggered only by read misses, and the prefetcher generates an additional address after the initial cache miss is satisfied using the nextRow pointer value (whose offset is hardwired at setup time) embedded in the data returned by the L2 cache.<sup>1</sup>

```

/* Prefetch only if vAddr refers to the matrix */

PointerPrefetch(data,vAddr,startBlock,endBlock) {

if (startBlock <= vAddr && vAddr < endBlock) {

/* Get row pointer from returned cache line */

ptrLoc = data [24]; /* row ptr offset = 24 */

<Initiate transfer of elt at ptrLoc to L1 cache>

}}

```