Paper 13 Date: March 3, 2021

# UNITED STATES PATENT AND TRADEMARK OFFICE BEFORE THE PATENT TRIAL AND APPEAL BOARD INTEL CORPORATION, Petitioner, V. FG SRC LLC, Patent Owner. IPR2020-01449 Patent 7,149,867 B2

Before KALYAN K. DESHPANDE, GREGG I. ANDERSON, and KARA L. SZPONDOWSKI, *Administrative Patent Judges*.

${\bf SZPONDOWSKI}, \textit{Administrative Patent Judge}.$

# DECISION Granting Institution of *Inter Partes* Review 35 U.S.C. § 314

## I. INTRODUCTION

Intel Corporation ("Petitioner") filed a Petition (Paper 1, "Pet.") to institute an *inter partes* review of claims 1–19 of U.S. Patent 7,149,867 B2, issued on December 12, 2006 (Ex. 1001, "the '867 patent"). FG SRC LLC ("Patent Owner") filed a Preliminary Response (Paper 9, "Prelim. Resp.") to

the Petition. With our authorization (Paper 10), Petitioner filed a Reply to the Preliminary Response (Paper 11, "Reply") and Patent Owner filed a Sur-Reply (Paper 12, "Sur-Reply"). We have jurisdiction under 35 U.S.C. § 314.

Institution of an *inter partes* review is authorized when "the information presented in the petition . . . and any response . . . shows that there is a reasonable likelihood that the petitioner would prevail with respect to at least 1 of the claims challenged in the petition." 35 U.S.C. § 314(a).

Based on the current record, and for the reasons explained below, we determine that Petitioner has established a reasonable likelihood that it would prevail with respect to at least one challenged claim. Accordingly, we institute an *inter partes* review as to the challenged claims and grounds raised in the Petition.

# II. BACKGROUND

### A. Real Parties in Interest

Petitioner identifies Intel Corporation as the sole real party in interest. Pet. 2. Patent Owner identifies FG SRC LLC as the sole real party in interest. Paper 4, 2.

# B. Related Matters

The parties advise that the '867 patent is the subject of the following district court litigations:

FG SRC LLC v. Intel Corporation, 6:20-cv-00315-ADA (W.D. Tex.) filed April 24, 2020 ("the parallel district court litigation");

*FG SRC LLC v. Xilinx, Inc.*, 1:20-cv-00601-LPS (D. Del), filed April 30, 2020; and

SRC Labs, LLC et al., v. Amazon Web Services, Inc., et al., 2:18-cv-00317-JLR (W.D. Wash.), filed February 26, 2018.

IPR2020-01449 Patent 7,149,867 B2

Pet. 2; Paper 4, 2. Petitioner also advises that the '867 patent was the subject of IPR2019-00103 (institution denied on May 10, 2019). Pet. 2

C. The '867 Patent (Ex. 1001)

The '867 patent issued from Application No. 10/869,200 filed June 16, 2004, and claims the benefit of Provisional Application No. 60/479,339, filed June 18, 2003. Ex. 1001, codes [21], [22], [60]. The '867 patent is titled "System and Method of Enhancing Efficiency and Utilization of Memory Bandwidth in Reconfigurable Hardware" and is generally directed to "enhancing the efficiency and utilization of memory bandwidth in reconfigurable hardware" and "implementing explicit memory hierarchies in reconfigurable processors that make efficient use of off-board, on-board, on-chip storage and available algorithm locality." *Id.* at code [57], 1:15–24.

# 1. Background and Summary of the Problem

The '867 patent explains that microprocessors "have enjoyed annual performance gains averaging about 50% per year," where most of the gains were attributable to higher clock processor speeds, more memory bandwidth, and increasing utilization of instruction level parallelism ("ILP") at execution time. *Id.* at 1:26–30. However, as microprocessor speeds increased, designing memory hierarchies that could keep up became challenging. *Id.* at 1:31–33. Therefore, "there has been significant effort spent on the development of memory hierarchies that can maintain high bandwidth efficiency and utilization with faster microprocessors." *Id.* at 1:48–50.

The '867 explains that one approach to improving bandwidth efficiency and utilization in memory hierarchies is the utilization of cache memories. *Id.* at 1:51–53. In designing cache memories, there are a number of considerations to take into account, such as the width of the cache line,

cache associativity, how cache lines are replaced due to a capacity or conflict miss, the write policy for the cache, and the size and speed of the cache. *Id.* at 1:59–3:15. For example, wide cache lines are more efficient for programs that exhibit a high degree of spatial locality (i.e., it is likely that other data within the same cache line will be needed). *Id.* at 1:64–2:4. However, narrow cache lines are more efficient for programs that have low levels of spatial locality. *Id.* at 2:4–7. The '867 patent states that the various considerations and tradeoffs makes cache design challenging for a multipurpose computer that executes a wide variety of programs in that "it is very difficult to design a single cache structure that is optimized for many different programs." *Id.* at 3:28–30. Cache designers try to derive the program behavior of the "average" program, and optimize the cache for the "average" program. *Id.* at 3:32–36. As a result, the cache is sub-optimal for most programs, because most programs that actually run on the microprocessor are not "average." *Id.* at 3:36–39.

# 2. The Claimed Invention of the '867 Patent

According to the '867 patent, because of the foregoing issues, there was a growing need to develop improved memory hierarchies that limited overhead of a memory hierarchy without also reducing bandwidth efficiency and utilization. *Id.* at 3:57–60. To address this need, the '867 patent describes a system including a memory hierarchy and a reconfigurable processor that includes a data prefetch unit. *Id.* at 4:4–10, 5:60–62, 6:9–13, 7:34–48. The '867 patent states that a "Reconfigurable Processor" is "a computing device that contains reconfigurable components such as FPGAs [(field programmable gate arrays)] and can, through reconfiguration, instantiate an algorithm as hardware." *Id.* at 5:26–29. The '867 patent states that a "Data prefetch Unit" is "a functional unit [a set of logic that performs

a specific operation] that moves data between members of a memory hierarchy [a collection of memories]," where such "movement may be as simple as a copy, or as complex as an indirect indexed strided copy into a unit stride memory." *Id.* at 5:34–43.

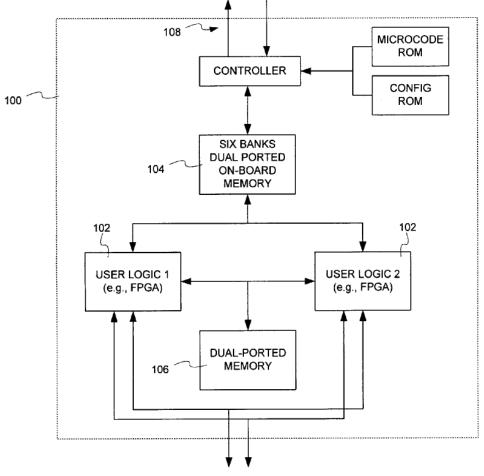

Figure 1 of the '867 patent, reproduced below, shows a reconfigurable processor (RP) 100 of the claimed invention. *Id.* at 4:38–40.

FIG. 1

Figure 1 depicts a reconfigurable processor (RP) 100. *Id.* at 4:38–40.

Figure 1 depicts reconfigurable processor 100, which "may be implemented using field programmable gate arrays (FPGAs) or other reconfigurable logic devices, that can be configured and reconfigured to

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

# API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

# **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.