#### US005764693A

## United States Patent [19]

Taylor et al.

# [11] Patent Number: 5,764,693

[45] Date of Patent: Jun. 9, 1998

#### [54] WIRELESS RADIO MODEM WITH MINIMAL INTER-DEVICE RF INTERFERENCE

[75] Inventors: Bryan Taylor; Mihal Lazaridis, both

of Waterloo; Peter Edmonson, Hamilton; Perry Jarmuszewski, Guelph; Lizhong Zhu, Waterloo; Steven Carkner, Waterloo; Matthias Wandel, Waterloo, all of Canada

[73] Assignee: Research In Motion Limited,

Waterloo, Canada

[21] Appl. No.: 488,695

[22] Filed: Jun. 8, 1995

#### Related U.S. Application Data

[63] Continuation-in-part of Ser. No. 337,841, Nov. 14, 1994, Pat. No. 5,619,531.

[51] Int. Cl.<sup>6</sup> ...... H04L 5/16; H04L 27/10

[52] U.S. Cl. ...... 375/222; 375/274; 455/73

[56] References Cited

#### U.S. PATENT DOCUMENTS

| 4,087,756 | 5/1978  | Rogers, Jr.        |

|-----------|---------|--------------------|

| 4,418,320 | 11/1983 | Guyton .           |

| 4,562,404 | 12/1985 | Futakuchi .        |

| 4,630,314 | 12/1986 | Smith .            |

| 4,646,326 | 2/1987  | Backof, Jr. et al. |

| 4,665,519 | 5/1987  | Kirchner et al     |

(List continued on next page.)

#### FOREIGN PATENT DOCUMENTS

| 0416423 | 3/1991 | European Pat. Off  |

|---------|--------|--------------------|

| 0494696 | 7/1992 | European Pat. Off  |

| 0531100 | 3/1993 | European Pat. Off  |

| 0584872 | 3/1994 | European Pat. Off. |

0599632 6/1994 European Pat. Off. . 0631398 12/1994 European Pat. Off. .

(List continued on next page.)

#### OTHER PUBLICATIONS

Electronic Design, vol. 41, No. 16, 5 Aug. 1993 pp. 45–50, Leonard 'PCMCIA-sized radio links portable WLan terminals' see figure 2.

IEICE Transactions On Communications, vol. E76-B, No. 8, Aug. 1993 pp. 990-995, Takehara 'A SAW-based spread spectrum wireless LAN system'see figures 2, 3, 7.

IEEE Transactions On Vehicular Technology, vol. 43, No. 4, 1 Nov. 1994 pp. 863–869, Mitsutaka Hilaita et al 'A wideband SAW resonator and its application to a VCO for movile radio transceivers' see abstract.

"Surface Transverse Wave Based FM Modulator/Demodulator". Reprinted from Electronics Letters 15th Mar. 1990 vol. 26 No. 6 pp. 364–365.

"A Surface Transverse Wave-Based MSK System", Ivan D. Avramov, P.J. Edmonson, Member, IEEE, Peter M. Smith, Member, IEEE IEEE Transactions On Ultrasonics, Ferroelectrics, And Frequency Control Vol. 38, No. 3, May 1991. Product Note 11729B-1 Phase Noise Characterization Of Microwave Oscillators Phase Detector Method Hewlett Packard, Aug. 1983.

Primary Examiner—Tesfaldet Bocure

Attorney, Agent, or Firm—Jones. Day, Reavis & Pogue;

Charles B. Meyer

#### [57] ABSTRACT

A wireless radio modem that may be incorporated into a host system or connected through a PCMCIA or similar port to a host system includes radio frequency modulation/demodulation circuitry employing electronic device elements that operate in a frequency range that minimizes the RF interference between the radio modem and the host system. Radio modem power conservation is maximized by 1) simplifying signal modulation processing by use of a two-point waveform transition table, thereby reducing processing requirements; and 2)incorporating a "sleep mode" feature in which all non-timer circuitry is powered-down when not in use.

#### 12 Claims, 8 Drawing Sheets

## 5,764,693

### Page 2

| U.S. PATENT DOCUMENTS |         |                |         | 5,317,707<br>5,347,304   | 317,707 5/1994 Wallace .<br>347,304 9/1994 Moura et al |                         |

|-----------------------|---------|----------------|---------|--------------------------|--------------------------------------------------------|-------------------------|

| 4,682,344             | 7/1987  | Somer .        |         | ,- ,-                    |                                                        | Durrant                 |

| 4,843,613             | 6/1989  | Crowle         | 375/295 | 0,010,200                | 0,1,,0                                                 | 241421 MINISTER 313/2/0 |

| 4,893,347             | 1/1990  | Eastmond et al |         | FOREIGN PATENT DOCUMENTS |                                                        |                         |

| 4,962,510             | 10/1990 | McDavid et al  | 375/308 |                          | 10101                                                  |                         |

| 5,020,093             | 5/1991  | Pireh .        |         | 62-292005                | 12/1987                                                | Japan .                 |

| 5,230,094             | 7/1993  | Kitching et al |         | 930577                   | 5/1982                                                 | U.S.S.R                 |

| 5,231,647             | 7/1993  | Deguchi .      |         | 2114392                  | 8/1983                                                 | United Kingdom .        |

| 5,313,211             | 5/1994  | Tokuda .       |         | 2261345                  | 5/1993                                                 | United Kingdom .        |

Fig. 4

#### WIRELESS RADIO MODEM WITH MINIMAL INTER-DEVICE RF **INTERFERENCE**

This application is a continuation-in-part of U.S. patent 5 application Ser. No. 08/337,841, filed Nov. 14, 1994 entitled Wireless Radio Modem With Minimal Interdevice RF Interference", now issued as U.S. Pat. No. 5,619,531 on Apr. 8, 1997.

#### COPYRIGHT NOTICE

Portions of the disclosure of this patent document, including the appendices, contain material that is subject to copyright protection. The copyright owner has no objection to the facsimile reproduction by anyone of the patent document or the patent disclosure as it appears in the Patent and Trademark Office patent file or records, but otherwise reserves all copyright rights whatsoever.

#### TECHNICAL FIELD OF THE INVENTION

This invention relates generally to data communication at radio frequencies in a wireless environment and, in particular, to a method of wireless data communication and to a device that can be imbedded within a host data pro- 25 cessing or communications unit (such as a PC, a laptop, a workstation, a personal digital assistant (PDA), a two-way pager or other equipment for data communications or processing) or attached directly through an external data interface, such as one that is constructed and controlled in a 30 manner that meets the standards set forth in two documents entitled "PC Card Standard," Release 2.0, and "Socket Services Interface Specification," Release 1.01, both published by the Personal Computer Memory Card International appreciated by reference to the specification that follows, although communication through a PCMCIA interface is preferable, the invention is not restricted to a particular communication interface and may be connected in any manner to a host data processing or communications unit 40 (either, a "host unit"), or integrated into such a unit. The method and device enables a host unit to transmit data to and receive data from a communication network wirelessly so that the RF interference between the host unit and the radio modem is minimized and power consumption is at a reduced 45 level. It is envisioned that in its preferred use, the invention will be used to communicate between a host unit and a remote data processing or communications device, either directly or via a network through a data transmission/ reception network station.

#### BACKGROUND OF THE INVENTION

Wireless radio modems are used to permit remotely located computers and other data communications equipment to communicate with one or more other computers or 55 equipment for data communications, usually as part of a computer network. Over the past several years, a number of efforts have been undertaken to reduce the size, weight, power consumption and portability of radio modems in order to increase their attractiveness to both the technical 60 community and the consuming public. In spite of advances in technology, most state of the art radio modem designs usually involve a flexible cable connection to the host unit and a bulky external battery pack to supply the necessary power. Previous attempts to incorporate a radio modem 65 within a host unit or to connect a radio modem through a PCMCIA interface have resulted in extremely poor operat2

ing performance predominately as a result of radio frequency interference caused by electrical noise generated by the host unit.

#### SUMMARY OF THE INVENTION

The present invention has utility in allowing a host unit to communicate with a wireless network. The present invention is a wireless radio modem that is designed to be located within a host unit, or connected to a host unit through an external port, such as a PCMCIA interface, so that the host unit can communicate with other units for data processing or communication via a wireless data network. In its preferred embodiment, the radio modem is designed to operate in a wireless data network that uses packet-switched communication such as a network that uses the Mobitex™ network protocol, the Ardis™ network protocol or the Celluar Digital Packet Data (CDPD) wireless network protocol. The radio modem design allows different network protocols to be supported by software changes only (i.e., with no substantive hardware modifications), so the scope of the invention is not limited to any specific protocol. For the preferred embodiments, however, reference is made to the Mobitex™ standard, which is a published communications standard for the Mobitex™ wireless network. The references herein to the standard shall mean the Mobitex Interface Specification, Rev. 3A, published September 1994 and available from RAM Mobile Data, 10 Woodbridge Center Drive, Woodbridge, N.J. 07095.

The radio modem is preferably designed to be built into a host unit (the OEM version) or to be directly connected to a host unit through a PCMCIA interface (the PCMCIA version), although the design may be incorporated into a stand-alone modem separate from the host unit. Both the Association (PCMCIA). in September 1991. As will be 35 size and performance of the present invention represent a significant improvement over the state of the art.

> The radio modem hardware and software of both the OEM version and the PCMCIA version are carefully designed to minimize power consumption. In the preferred embodiments, each version can be configured in one of two forms: (i) with an on-board microprocessor that provides overall control of the operation of the various subsystems of the radio modem (the "on-board processor form") or (ii) without an on-board processor, whereby the essential control functions that are performed by the microprocessor in the on-board processor form are performed by the host unit microprocessor (the "microprocessor-less form"). To reduce power consumption significantly in each version, the key power-consuming components are placed into lower power 50 modes when they are not needed and are placed in a higher power mode only when data that the radio modem is to process are detected or when a predetermined period time has elapsed from the point the components have been put into a lower power or a "sleep" mode. As one of ordinary skill in the art of digital communications equipment design will appreciate, the microprocessor is one of the key powerconsuming components in the on-board processor form. In addition to the power management circuitry, the method of operation of each version of the radio modem was optimized to reduce power consumption using low-power components and power-efficient design where possible.

Operational performance is also enhanced over the state of the art because both versions of the radio modem are designed to operate in the high electrical noise environment present within, or immediately proximate to a host unit. The major electrical noise immunity strategy employed is the use of circuitry designed to operate outside the electrically noisy

frequency bands that are present within an operating data processing unit. Among the features that enable the modem to avoid the RF interference of its host data processing unit is the implementation of frequency discrimination at an intermediate frequency (at or above 10.7 MHz) that is well 5 above the noise frequencies emanating from the operation of a host unit.

3

In order to generate the intermediate frequency at which discrimination takes place, the receiver circuitry uses a single intermediate frequency down conversion step. In the 10 preferred embodiment, the intermediate frequency is 45 MHz. After down conversion the signal is channel filtered and then demodulated and digitized. The resulting digitized signal is then conveyed to a digital signal processor ("DSP") where the data is recovered and conveyed to the host unit. 15

On the transmission side, the transmitter circuitry accepts data from the host unit, via the DSP, in a pre-modulated form. In the preferred embodiment, the data received by the transmitter is modulated using either quadrature modulation or baseband modulation, although one of ordinary skill in <sup>20</sup> the art will appreciate that various modulation techniques could be applied to modulate the signal received from the DSP.

#### Quadrature Modulation

In the implementation in which the data are quadrature modulated, the DSP presents the signal to the modulation circuitry in in-phase and quadrature phase components. The signal is then modulated directly, using quadrature modulation, and is filtered, amplified, upconverted, filtered and then amplified again before being conveyed, via a transmit/receive switch, to an antenna for propagation.

#### **Baseband Modulation**

In the implementation in which the data is baseband modulated, the DSP presents the signal to the modulation circuitry in the form of two modulation voltage signals for the Voltage Controlled Temperature Compensated Crystal Oscillator (VCTCXO) and Voltage Controlled Oscillator (VCO). The signal is then frequency modulated, using baseband modulation and is filtered and then amplified before being conveyed, via a transmit/receive switch, to an antenna for propagation.

#### Modulation Lookup Tables

The modulation scheme, in the preferred embodiment, relies upon pre-calculated wave segments that are pieced together at run time to produce smooth Gaussian Minimum Shift Keyed (GMSK) or GMSK Inphase (I) and Quadature Phase (Q) modulated waveforms. For efficiency purposes and to reduce the processing time required to modulate the signal (and thus the processing power required), a look-up 50 table stored preferably in DSP memory is employed as a part of the modulation process.

In the case of quadrature modulation, the look-up table provides precalculated waveform segments that are pieced together, taking into account the interrelationship of a digital four bit transmission stream on the waveform shape associated with the second bit of the four bit stream. Simple transforms are used to phase shift this signal by steps of 90 degrees, to compensate for the different phases that the I and Q channels may be in at the start of the segment.

In the case of baseband modulation, instead of using the I and Q channels, baseband signals are encoded. Thus, it is only necessary to have one channel instead of two, as both channels are either the same, or related by a constant multiple. The need to shift the signal by 90 degrees is no 65 longer necessary in baseband, as there is no need to use accumulated phase from previous bits.

The modulation tables, in the preferred embodiment, were generated by a program called MODTAB. MODTAB.C, the main c source file found in Appendix A, contains the mathematics to generate the modulation tables. The formulas in this code implement the modulation scheme in a simplified form and the source code is structured in such a manner that certain of its modules can be used to generate tables for quadrature phase modulation and not used when baseband modulation tables are desired.

For both types of modulation, the GMSK wave form is first calculated and used to generate a baseband modulated wave form. To FM modulate the baseband GMSK signal into I and O signals for quadrature phase modulation, a phase accumulator is used. Because frequency is a rate of phase change, the baseband values from the GMSK wave form represent the rate of change of the phase accumulator. The Sine and COSINE of value in the phase accumulator is then used to calculate the I and Q signals. Optionally, the effect of an RC filter on the I and Q signals can be compensated for by applying the inverse function of an RC filter to the I and Q signals. Thus, the output of the RC filter can be forced to correspond with the desired wave form. The math is performed in a laborious manner, using floating point evaluation. For each possible combination of four bits, all the shapes for all four bits are generated. To build the tables, the interval between the centers of bits 2 and 3 is then bracketed, extracted and placed in the table.

When generating tables for baseband code, the phase accumulator and SINE/COSINE calculation steps are skipped, and the baseband wave forms are placed in the tables directly. There is also no need to compensate for RC filter effects in the development of the baseband table. When the tables are generated and stored, modulation can be accomplished through application of the table data.

The object of the demodulation scheme is to provide a nearly optimal method for decoding bits accurately, while using as little processing power and additional hardware as possible, in order to keep power consumption and cost to a minimum. In order to eliminate the need for sophisticated hardware filters, the incoming signal is sampled at a rate that is a multiple of the bit rate. In the preferred embodiment, the sampling rate is six times the GMSK bit rate. A Finite Impulse Response (FIR) filter is applied to the signal every n samples, where n is the number of analog to digital converter (A/D) samples per GMSK bit. This implements a decimating filter, producing output samples at a rate equal to the bit rate. The FIR filter cuts off sharply after a frequency equal to half the bit rate, thus keeping to a minimum the amount of aliasing resulting from the decimation. This technique takes advantage of the Nyquist sampling theorem, fully capturing a bandwidth of half the sampling rate by taking periodic samples.

Even though the effective sampling rate is equal to the bit rate, repetitious patterns of seemingly lower bit rates, such as a GMSK Bitsync of the pattern 110011001100, can nevertheless be recognized, as such a pattern produces a wave form similar to a sinusoid at a frequency of one fourth the bit rate. A series of increasingly stringent criteria is used to determine whether the received signal is a bit sync pattern. When all the criteria are satisfied, preferably 12 samples of the bit sync are correlated to SINE and COSINE functions. Because 12 samples represent three complete periods of the sinusoid, compensating for different direct current (DC) levels is not necessary. Because the SINE and COSINE functions need only be evaluated at 90 degree intervals, this process is trivial. The SINE function, for example, takes on values of 0.1.0.-1.0.1.0.-1.0... etc.. The

two resulting correlations of the SINE and COSINE functions are then combined to form a Cartesian vector and mathematically transformed through rotations of 90 degrees to be within an angle of +/-45 degrees. A cubic function of the slope of this vector is then used to approximate the 5 arctangent of the resultant vector. The difference between the resultant angle and 45 degrees (or -45 degrees, whichever is closer), divided by 90 degrees is the fraction of a bit by which the sampling point in the decimation filter must be adjusted to be coincident with the center of the GMSK bit. 10 In the preferred embodiment, for ease of implementation, the adjustment is rounded to the nearest A/D sample. As one of ordinary skill in the art will appreciate, however, enhanced accuracy can be obtained by varying the shape of the FIR filter to accomplish shifts of less than one A/D 15 modulated waveform segment lookup table. sample. When the adjustment is performed, samples coincide with the centers of bits, so bit decoding can be done using a threshold that is a function of a DC level calculated from the 12 samples used for bit synchronization, as well as the value of the previous bit.

5

#### **OBJECTS OF THE INVENTION**

Accordingly, it is an object of the invention to provide a radio modem with modulation/ demodulation means that incorporates circuit elements that operate at frequencies 25 outside the frequency range of the RF noise associated with the host unit in which the radio modem is installed.

It is a another object of the invention to provide a radio modem in which frequency discrimination occurs at a data discrimination frequency of 10.7 MHz or higher.

It is a further object of the invention to perform FM frequency discrimination through the use of one or more piezoelectric phase-shift devices, such as surface acoustic wave ("SAW") filters, surface transverse wave ("STW") filters, surface skimming bulk wave ("SSBW") filters, leaky SAW filters or crystal filters such that the frequency discrimination takes place outside the RF noise frequencies generated by the host unit associated with the radio modem.

It is a yet further object of the invention to provide a stored waveform transition table as part of the digital signal processing circuitry to minimize processing time and power consumption during the digital signal processing phase of the operation of the radio modem.

It is another object of the invention to provide circuitry for 45 minimizing power consumption in a radio modem that permits the major power-consuming components of the radio modem to enter into an inactive or lower-powered state and to be later activated or repowered by the detection of mined period of time, whichever occurs first.

These objects as well as others appreciated by those of ordinary shill in the art will become apparent from the detailed description and in reference to the drawings that follow. The specific examples that are set forth in the 55 detailed description of the preferred embodiment should be understood to be given for illustrative purposes only and are not intended to limit the spirit and scope of the invention.

#### **BRIEF DESCRIPTION OF FIGURES**

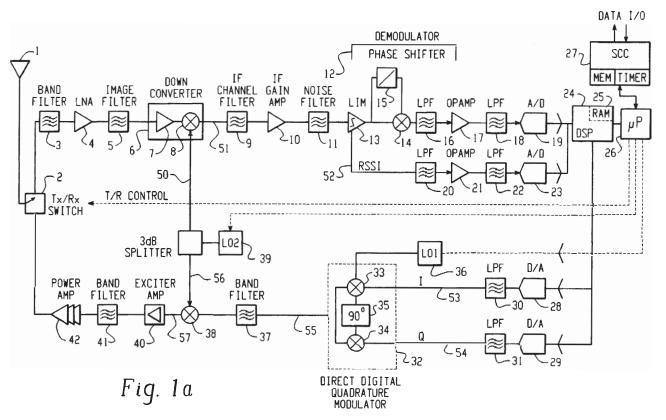

FIG. 1a is a block diagram of the hardware layout for the on-board processor form of the radio modem using quadrature modulation and two local oscillators.

FIG. 1b is a block diagram of the hardware layout for an alternative embodiment of the on-board processor form of 65 the radio modem using quadrature modulation and a single local oscillator.

6

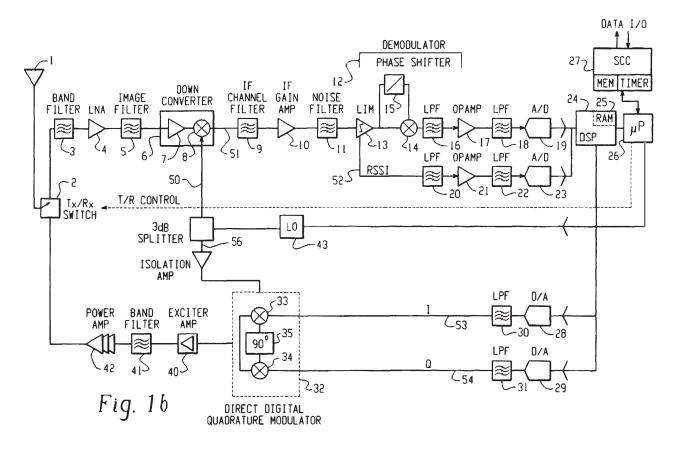

FIG. 2 is a block diagram of the hardware layout for the on-board processor form of the radio modem using baseband modulation.

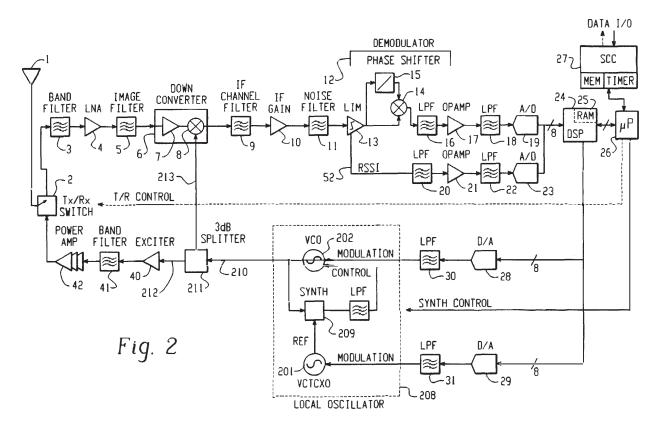

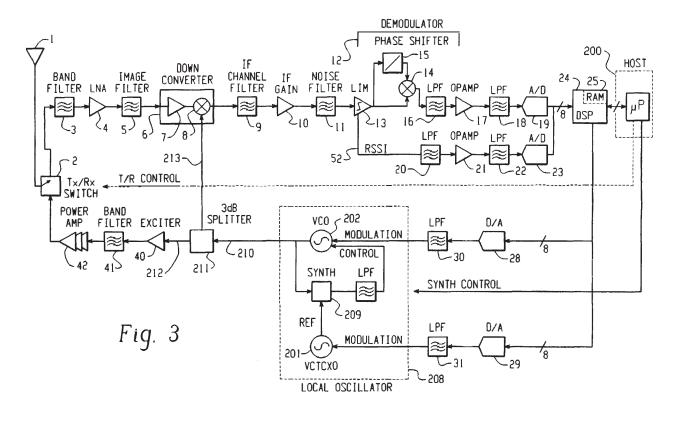

FIG. 3 is a block diagram of the hardware layout for the microprocessor-less version of the radio modem using baseband modulation and an external interface to the host unit, such as a PCMCIA interface.

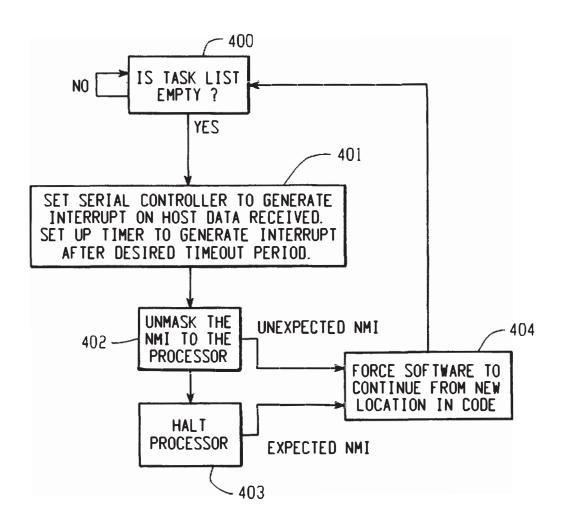

FIG. 4 is a block diagram of the operation of the interrupt handler for the power management hardware.

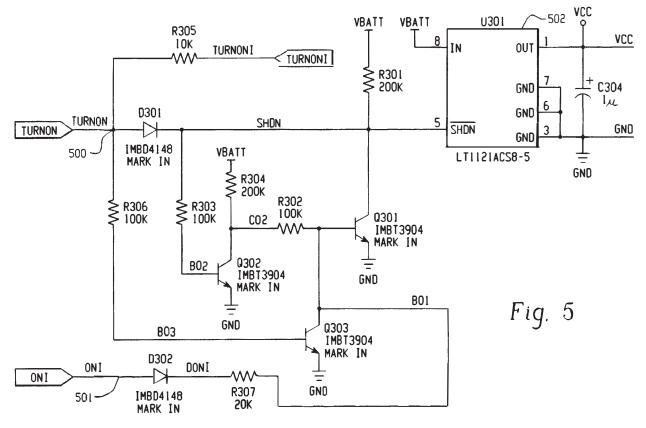

FIG. 5 is a schematic of circuitry that provides a "soft

FIG. 6 is timing diagram for the soft turn-on function.

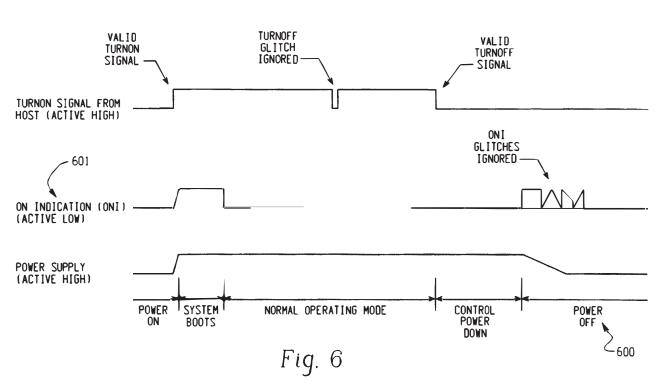

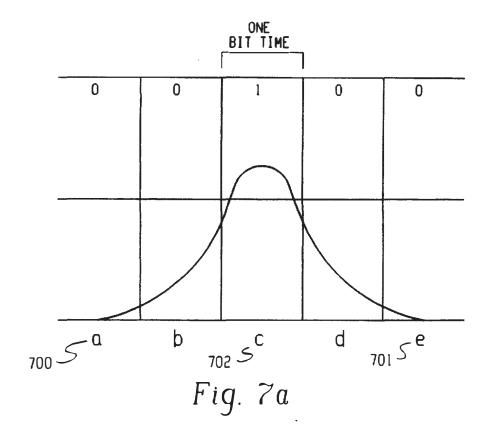

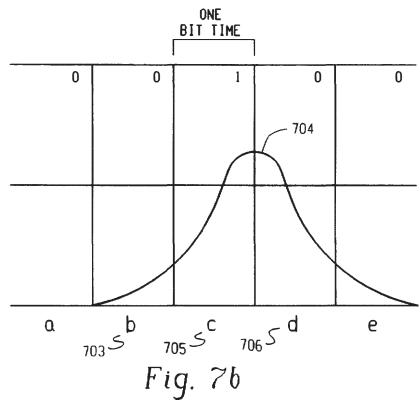

FIGS. 7a and 7b relate to the operation of the pre-

#### DESCRIPTION OF THE PREFERRED **EMBODIMENTS**

The preferred embodiments of the present invention are radio modems that can be built into the host unit or attached to a host unit through a PCMCIA or similar port. Each radio modem generally comprises transmission/reception means and a modulation/demodulation means.

With reference to FIG. 1a, the received signal is conveyed from an antenna (1) via a transmit/receive switch (2) to a bandpass filter (3), which is preferably an electronicallycoupled piezoelectric device such as an acoustic wave device and more specifically a SAW, an STW filter, an SSBW filter or what has been commonly referred to a leaky SAW filter. The filtered signal is conveyed to a low-noise amplifier (4) and image filter (5), and to the downconverter (6). In the preferred embodiments, bandpass filters (3) and (5) are SAW filters. Within the downconverter, the signal amplified by a linear amplifier (7) is mixed with a signal (50) from a local oscillator (39) at the mixer (8) to produce a signal (51) at an intermediate frequency greater than or equal to 10.7 Mhz. Signal (51) is conditioned by the intermediate frequency (IF) channel filter (9) and is amplified by the IF gain block (10) then conditioned by a noise filter (11). The resulting intermediate frequency signal is demodulated within the demodulator (12). In the preferred embodiment. the intermediate frequency is 45 MHz.

The demodulator consists of a limiting amplifier (13) to produce a signal having constant amplitude. This signal is split into two parts which are mixed in a mixer (14), with one of the parts shifted in phase relative to the other. The phase shift element (15) is preferably an electronically-coupled piezoelectric device such as surface acoustic wave filter or data communications or by the expiration of a predeter- 50 a crystal filter. The demodulated signal is conditioned and converted to a digital representation before being conveyed to a digital signal processor (DSP) (24). The digital signal processor (24) is preferably an ADSP-2171KST-133 commercially available from Analog Devices, Inc., Norwood, Mass. The conditioning and conversion to a digital representation is performed by low pass filter (16), amplified by operational amplifier (17), conditioned by anti-aliasing filter (18) and converted to a digital representation by analog to digital converter (19).

The limiting amplifier (13) produces a second signal (52) with a DC voltage proportional to the received signal strength at the input of the limiter. This signal is referred to as the Received Signal Strength Indicator (RSSI) and is conditioned by low pass filter (20), amplified by operational amplifier (21), conditioned by anti-aliasing filter (22) and converted to a digital representation by analog to digital converter (23).

In the on-board processor version, the digital data is conveyed to the host unit via the microprocessor (uP) (26), preferably an Intel SB80L188EB-8 (available from Intel Corporation. Santa Clara, Calif.), and a serial communications controller ("SCC") (27), preferably a Phillips SCC 9291 (available from Phillips Electronics North America Corporation, Sunnyvale, Calif.). In the microprocessor-less version, as seen on FIG. 3, the modem utilizes the microprocessor of the host (200), and thus there is no need to have a microprocessor resident within the externally connected modem, i.e. within the PCMCIA form factor. Additionally, because of the physical connection in the preferred embodiment through the PCMCIA port, the need for an SCC is also eliminated. One of ordinary skill in the art will appreciate that each of the aforementioned components for which particular part numbers are not referenced are well known in 15 the art.

When the radio modem is transmitting, the data to be sent is conveyed from a host data processing unit, via the serial communications controller (27) and the microprocessor (26) to the digital signal processor (24). In the case of quadrature 20 phase modulation, the digital signal processor (24) generates the appropriate in-phase and quadrature-phase modulated waveform segments, which are based on the current and previous bits to be sent, from a precalculated look-up table stored in the associated random-access memory (25). The 25 digital signals are converted to analog signals by two digital-to-analog converters (28) (29), conditioned by two low pass filters (30) (31) and are conveyed to the quadrature modulator (32). Within the quadrature modulator (32) the in-phase signal (53) is mixed in a mixer (33) with the signal 30 from L01 (36), one of two local oscillators, and the quadrature-phase signal (54) is mixed in a mixer (34) with a ninety-degree phase shifted signal from the local oscillator L01 (36) supplied via the phase shift element (35). The emerging modulated signal (55) is passed through a band- 35 pass filter (37), and input to an upconverter mixer (38), where it is mixed with a signal (56) from the local oscillator L02 (39). The resulting signal (57) is amplified by exciter amplifier (40), conditioned by a band-pass filter (41), amplified in a three-stage power amplifier (42) and transmitted 40 from the antenna (1) via the transmit/receive switch (2). As can be seen in FIG. 1b, the two local oscillators of FIG. (1a) can be replaced by a single oscillator (L0) (43) by bypassing the upconversion stage affected by the local oscillators (L01) (36), (L02) (39), the mixer (38) and the band pass filter (37). 45

As illustrated by FIGS. 2 and 3, in the case of baseband modulation, the digital signal processor (24) similarly generates, from the look-up table store in the associated RAM (25), the appropriate modulation voltage segments for the Voltage Controlled Temperature Compensated Crystal Oscillator (VCTCXO) (201) and the Voltage Controlled Oscillator (VCO) (202). The digital signals thus generated are then converted to modulation voltages by digital to analog converters (28) and (29) and are conditioned by low pass filters (30) and (31). These modulation voltages are 55 applied to the VCO (202) and VCTCXO (201) to shift the local oscillator frequency by a maximum of 2 Khz from its nominal frequency. As one of ordinary skill in the art will appreciate, a single D/A converter may perform the functions of the two converters (28) and (29). The resultant local oscillator signal (210) in the baseband modulation scheme is conveyed by splitter (211) to the exciter amplifier (40), conditioned by a band-pass filter (41), amplified in a threestage power amplifier (42) and is transmitted from the antenna (1) via the transmit/receive switch (2).

During operation in a baseband modulation configuration, in both the receive and transmit modes, the local oscillator

(L0)(208) comprising VCTCXO (201), VCO (202) and synthesizer (209) operates to pass its output signal (210) to both the receive and transmit section of the radio via splitter (211). If the radio modem is in its receive mode, the signal (212) is "ignored"—the transmit circuitry is not active because of power management and a signal is not conveyed to the antenna (1) as a result of the T/R switch (2). Correspondingly, when the radio modem is in its transmit mode, the L0 signal (213) that is transferred via splitter (211) to the receive side is "ignored"—because the receive circuitry is not active as a result of power management. It should be noted that when the radio modem is in its receive mode, the LO (208) is programmed at the reception frequency, at the beginning of the receive cycle. In the transmit mode, the L0 (208) is continuously updated by the VCO and VCTCXO modulation voltages in order to produce the desired frequency shifts required for modulation.

In greater detail, and again with reference to FIGS. 1a and 1b, 2 and 3, frequency modulation discrimination occurs through the employment of an electronically coupled piezoelectric phase shift element (15), such as a crystal filter. The use of this element represents an improvement over the prior art due to the fact that electronically coupled piezoelectric phase-shift devices have a steeper phase slope relative to changing frequency compared to the resistor inductor capacitor (RLC) tank circuits that have been used in the prior art for frequency discrimination. One advantage of the present innovation is that the discriminator can be operated at higher intermediate frequencies, which is of particular importance to this invention, and is discussed in greater detail below. A second advantage is that the steeper phase slope associated with an electronically-coupled phase-shift element makes the resulting discriminator more sensitive, thereby increasing the sensitivity and receiver performance of the radio modem. The use of a frequency modulation discriminator employing an electronically tuned phase shift element is not limited to use within a radio modem. Such means can be used to discriminate any frequency modulated signal in other systems as well. In addition, as one of ordinary skill in the art will appreciate, because of the close relationship between frequency modulation and phase modulation, the frequency modulation discriminator disclosed means could also be used with minor modifications to discriminate a phase modulated signal.

As discussed above, the discriminator disclosed in the present invention is capable of operating with superior performance at higher frequencies than known discriminator designs. An integral part of the innovation for the present invention is preclusion of electrical interference from the host data processing device, such as "software noise", which is a characteristic emission from any running computer. Typically, such noise is of significantly higher amplitude at frequencies less than 10.7 MHz. In the present invention, the received signal is down-converted in a single stage to an intermediate frequency that is above the aforementioned threshold frequency of 10.7 MHz, such as 45 MHz. By this method, the radio modem achieves greater noise immunity over known devices, permitting the radio modem to be integrated within a host data processing device without compromising performance of the radio modem.

Again with reference to FIGS. 1a and 1b, in the case of quadrature modulation, in-phase and quadrature-phase modulated waveform segments are generated by the digital signal processor (24). In the case of baseband modulation, the waveform segments generated are the VCO and VCTCXO modulation voltages. In each case, the waveform segments are based on the current bit, previous bits and

future bits to be sent, from a precalculated look-up table stored in the associated random access memory (25). The operation of this method is described below.

As discussed previously, pre-calculated waveforms can be used to eliminate the need to compute complicated formulae at run time. In the case of Gaussian Minimum Phase Shift Keying, as is specified under the Mobitex™ standard, with a bandwidth time product of 0.3, the actual waveform used to identify a bit is in excess of three bit periods long, as is shown in FIG. 7a, for the bit sequence 00100. With refer- 10 ence to FIG. 7a, the bit period a (700) and bit period e (701) are affected by the bit in period c (702). Therefore, to store all possible shapes for any bit period c (702), thirty-two different segments are required to represent all possible values for the five bit periods shown. By realizing that the 15 significant portion of the Gaussian shape is only four bit periods long, and by shifting the waveform by half of one bit, the number of table entries can be reduced by half to sixteen. The segments are centered on one interbit period (703), as shown in FIG. 7b. With reference to FIG. 7b, the  $^{20}$ bit center (704) is positioned between the bit period c (705) and the bit period d (706). Therefore the value of segment c (705) is only affected by the values of four bits, and therefore has only sixteen possible shapes.

The method described above yields baseband, but not in phase and quadrature phase signals. If baseband modulation is desired, no further calculations are needed. I and Q signals, however, for quadrature modulation, are readily calculated from the tabulated data described above, using the following approach. The in-phase and quadrature phase signals depend on the initial phase at the beginning of the bit period. This initial phase must be known when the tables are calculated. In the Mobitex™ system, the modulation is such that the frequency difference between a stream of continuous I's and a stream of continuous 0's is an even fraction of the bit rate constraining the starting phase to one of a discrete set of values. For example, in Mobitex™, the frequency deviation is 2000 Hz and the baudrate is 8000 bits/second. Thus, a 1 transmitted previously will cause a phase shift in the modulated signal of 90 degrees, whereas a 0 transmitted previously will cause a phase shift of -90 degrees. There are four multiples of 90 degree phase shifts, or four possible distinct starting phases for each wave segment for a given surrounding four bit sequence. The rotation of a Cartesian vector by steps of 90 degrees is a simple operation and can be easily calculated as required. No additional precomputed samples are required to accommodate different starting phases. In particular, only trivial trigonometric calculations or look-up tables are required.

#### Power Management

The present invention also employs innovative power management means and methods, in order to minimize power consumption. Although such power management techniques are directed to the on-board processor form of the 55 in the prior art. instant invention, one of ordinary skill in the art could recognize their applicability, albeit with potentially reduced power savings, if the techniques were incorporated into the form of the microprocessor-less form of the invention.

are the serial communications controller (27), incorporating an integrated timer and memory, and microprocessor (26), as shown in FIGS. 1a and 1b. Through implementation of the power management means, the radio modem circuitry consumes approximately one half the power of other known 65 systems. In general, maximum power savings in any situation are accomplished by completely turning the device off.

The microprocessor (26) has the ability to enter a dormant mode of operation where it consumes virtually no power. The circuit has been implemented such that the processor can also shut down other circuitry that is not in use. The processor is brought back to active mode by activating reset or providing an external non-maskable interrupt signal.

10

The present invention utilizes a system that allows the processor to shut down most of the circuitry, but remains able to power-up on one of two conditions, namely, that either a predetermined time had elapsed, or that the host system attempts to communicate. Both of these conditions are problematic, requiring innovative solutions, which are as follows:

#### Timer System

In order to "wake up" the microprocessor and, subsequently, the digital signal processor, a programmable timer circuit, external to the microprocessor, is set such that it produces an output pulse to the processor after the expiration of a selectable, predetermined time period. As seen in FIG. 4 in block (401), the timer is set when it is determined that the microprocessor does not have any tasks left to be completed in its task list therefore the microprocessor and the digital signal processor are permitted enter their lowest power mode. Although in the preferred embodiment the microprocessor when directed to shut down first shuts down the digital signal processor before shutting itself down, it would be appreciated by one of ordinary skill in the art that the digital signal processor could first determine that it is able to shut down, and then advise the microprocessor to shut down.

#### Communication System

In most applications, the host data processing system or data communication system communicates with the circuit at a very high rate, often exceeding 9600 bits per second. When the host begins communicating, the circuit has only about 1 millisecond to initialize to prevent information from being lost. By using a serial communications controller (27) with a built in memory, it is possible to store the first few characters external to the processor. This allows the processor over four times longer to initialize and respond to the host.

#### Masking the Non-Maskable Interrupt

If the external serial communications controller were 45 connected directly to the non-maskable interrupt of the processor, inefficient operation would result as an nonmaskable interrupt requires longer to service than a standard interrupt. To overcome this problem, the non-maskable interrupt is connected through standard logic gates to provide a masking operation. By enabling the processor to mask the non-maskable interrupt, faster response time, reduced processor 'on' time in a fully-powered state, and lower power consumption result. Masking a non-maskable interrupt for the purposes of power saving is previously unknown

#### Power Management Software Description

The Power Management Software contains several key components, the most important of these is the task list. As suggested by FIG. 4, if the processor or associated circuitry The major components of the power management circuit 60 is 'busy' with a task, it will be indicated by an entry in the task list. When the task list becomes empty the processor will enter the lowest power mode possible. and as seen in block (401) of FIG. 4, the serial controller is posted as a sentry to detect data communications so as to initiate an activating interrupt to the microprocessor to begin an activation cycle. Additionally, the timer associated with the serial communications controller (27) is set to initiate an

output pulse that will also serve to activate the microprocessor prior to the initiation of the activating interrupt by the serial communications controller (27). In normal operation under this power management scheme, the processor spends about 5% of its time active, and 95% in the fully idle, lowest 5 power mode.

One of the key elements in the software system is improvement to the interrupt handler. Normally, in existing systems, software would return to the instruction following the point at which the interrupt occurred. However, there is 10 a window of vulnerability when using a maskable nonmaskable interrupt as previously described. If an interrupt occurs at the instant that the interrupt is unmasked (unexpected non-maskable interrupt), and the interrupt handler was written in the manner of prior existing systems. 15 program execution would return to the instruction following where the interrupt occurred. In this case, the instruction would be a halt instruction. Therefore, the processor would be caused to halt execution by an interrupt, when what is required is an interrupt that initiates execution. As seen in 20 blocks (402), (403) and (404) of FIG. 4, the present invention incorporates modifications to the standard operation of the processor by modifying the program stack and forcing the code to execute from a specific known state that would be 'safe' after either an expected, or unexpected non- 25 maskable interrupt. The unexpected result of implementing the above power management scheme combined with the previously described circuit that includes a serial communications controller (27) to provide a masked nonmaskable interrupt, is the power consumption for continuous operation 30 of the serial communications controller (27) is dramatically less than the power requirement of the microprocessor and the digital signal processor. In the preferred embodiment, the overall system power requirement was reduced by a factor of more than 6.

#### Soft "Turn-on" Operation

The function of the soft "turn-on" circuit is to allow the host to turn the radio on and off with a minimum of extra circuitry. The soft turn-on is required to be rugged in the sense that it should not accidentally turn on or off when variations in supplied power occur. The quiescent power dissipation of the circuit must be as low as possible, especially when the circuit is in its off state. The circuit is required to operate at varying supply voltages, such as when the system battery is substantially discharged or overcharged, with the circuit most importantly maintaining

correct operation of the radio modem by keeping the radio off or on as desired. Standard off-the shelf components and circuits generally have undefined operation below a few volts making them unsuitable for this purpose.

The circuit used to achieve the above goal is shown in FIG. 5. The circuit is similar in operation to an RS flip-flop that satisfies the additional operational constraints:

- 1) When the host 'Turnon' signal (500) is active, power is supplied to the radio modem through microprocessor power supply (502) which is preferably a LT1121ACS8-5 manufactured by Linear Technology, Miltitas, Calif. As seen in the timing diagram FIG. 6, a period of time elapses from the time the Turnon signal is initiated to the time the power supply is reaches operating voltage.

- 2) When the on indication ('ONI') signal (501) is active while Turnon signal (500) goes from active to in-active, power remains supplied until both control power down functions are completed and the Turnon signal (500) is determined to be constantly active. Also, as FIG. 6 illustrates, the ONI signal (601) remains in an inactive state until the radio modem has completed its initialization cycle and remains active until the expiration of the control power down cycle.

- 3) When the host 'Turnon' signal (500) is inactive, power will only be removed from the circuit if 'ONI' is also inactive. This is illustrated as well on FIG. 6 at the point (600) where the control power down cycle ends.

- 4) A brief transition of 'ONI' from inactive to active while 'Turnon' is inactive will not cause power to be applied to the circuit as also displayed in FIG. 6.

Waveform Table Generating and DSP Software

As discussed previously, the waveform tables were generated from two software modules that can be found, in source code form in Appendix A. In Appendix B, can be found the software used to processing the received signals and to generate the transmitted signals. Although the invention is fully described in the specification without reference to the appended source code modules, the Appendices are presented to provide further insight into the advancement over the prior art.

Although the present invention has been described and illustrated in detail, the description is meant to be illustrative and not limiting the spirit or scope of the invention, which is limited and defined with particularity only by the terms of the appended claims.

#### APPENDIX A

#### WAVEFORM TABLE GENERATING SOFTWARE AND ASSOCIATED TABLES

```

1. Table-building Module (Modtab.C)

#include <std10.n>

#include <stalib h>

#include <como h>

#include <math.h>

#define TRUE I

#define FALSE 0

/ Mode variables for controlling what the program does

static int bGraphit:

static int bBaseband;

static int GaussianFullScale;

static int bBasestation;

static int correct_samples_flag.

# Graphine stutt

#define GREEN 2

#define CYAN 3

#define RED 4

#define BRWHITE 15

#define BLUE

#define WHITE

void SetGraphParameters(long MinVal. long MaxVal. int. FimeScale, int NumSamples, char Title[]).

void GraphFunction(int Functions), int color);

void Graph2Function(int Function1(), int Function2(), int color);

void TimeMark(int SamplePoint, int bBetween, int color);

void SetHiresMode(void);

void SetTextMode(void);

modtab.c -- Make I and Q Tables for

the DSP.

// Oversampling rate (samples per bit)

#define OVERSAMPLING 20

#define SAMPLING_FREQUENCY (double) 8000 * OVERSAMPLING

#define RESISTANCE idouble) 3920

#define CAPACITANCE idouble) 0 00000001011

#define CORRECTION_FACTOR 0.75

#define GAUSSLENGTH (OVERSAMPLING * 5)

// Total length of a gmsk gaussian.

// Maximu +/- value for gassian

#define GAUSSFULLSCALE 8000

waveform

# Scale factor for BT constant (guessed)

#define BTSCALE

#define IANDQFULLSCALE 0x7FFF

#1 and Q maximum value

```

#define PI

#define BITRATE 8000

// Mobitex bitrate

```

# Filter resistor

#define FILTER_R 3290

#define FILTER_C 6 8e-9

# Filter capacitro

#detine TIMECONST (FILTER_R * FILTER_C * 2 * PI)

Working arrays for generating I and Q modulation segments

int Gaussiani GAUSSLENGTHI.

int GmskShape(GAUSSLENGTH + OVERSAMPLING*41)

int (Shape(GAUSSLENGTH + OVERSAMPLING*4):

ant QShape(GAUSSLENGTH + OVERSAMPLING*4)

Storage arrays for precomputed guassian Land Q segments

int (Tubles) 2*2*2*2*OVERSAMPLING).

int QTablesi2*2*2*2*OVERSAMPLING

int IStartTable[OVERSAMPLING*3].

int QStartTable[OVERSAMPLING*3].

# Total sample space required = OVERSAMPLING * 38

struct (

int * (Pointer:

int * QPointer:

int lSign;

int QSign.

[QInit[4].

# Generates the master guassian wave shape to be used later.

static yord BuildGaussianivoid)

float power:

int a.b.

if (bGraphit))

SetGraphParameterst0.GaussianFullScale, 16*10.GAUSSLENGTH, "Natural and Modified

Gaussian shapes ).

tor (a=0):a<=5.a++)

TimeMark(OVERSAMPLING*a-1, -1, RED);

// Calculate the natural gaussian

for (a=0;a< GAUSSLENGTH;a++)

power = 1a-((float)GAUSSLENGTH-2)/2) / OVERSAMPLING.

power = -{power*power;

Gaussian(a) = (int) (((long)GaussianFullScale*2)/3) * exp(power * BTSCALE));

if (bGraphtti GraphFunction(Gaussian, GREEN).

7 Normalize the gaussian with an 8 khz rate.

for (a=0:a<0VERSAMPLING.a++){

long Sum:

Sum = 0:

```

```

for (b=0):b<GAUSSLENGTH.b+= ()VERSAMPLING){

Sum += Gaussiania+bl:

for (b=0.b<GAUSSLENGTH:b+= ()VERSAMPLING){

Gaussiania+bj = :inti(Gaussiania+b) * tlong(GaussianFullScale) / Sumi:

if tbGraphitit

GraphFunction(Gaussian, CYAN);

getch():

# Builds a GMSK waveform from four bits specified in bitstream BitArray[]

// Waveform is placed in array GinskShaper[] and is 4 bit times long.

//-------

static void BuildGMSK(int BitArray())

int a.bit;

for (a=0:a<GAUSSLENGTH + OVERSAMPLING*4:a++){

GmskShape(a) = 0

for (bit=1).bit<4.bit++ii

for (a=0.a<GAUSSLENGTH.a++)}

if (BitArrav[bit] == 1) GmskShape(bit*OVERSAMPLING + a) += Gaussian(a).

if (BitArray[bit] == ()) GmskShape[bit*OVERSAMPLING + a) -= Gaussian[a];

}

// Takes the waveform in GinskShape and I and Q modulates it into landQShape

static void landQModulatervoid)

double phase;

int a:

phase = 0.

if (bBaseband)[

// Short circuit - do not I and Q modulate for baseband testing.

for (a=0:a<GAUSSLENGTH + ()VERSAMPLING*4 a++1

IShape(a) = GmskShape(a):

QShape(a) = -GmskShape(a);

lelse

for (a=0:a<GAUSSLENGTH + OVERSAMPLING*4.a++)}

IShape(a) = (int)(IANDQFULLSCALE * sin(phase));

QShape[a] = (int)(IANDQFULLSCALE * cosiphase));

phase += GmskShape(a) * (PI / OVERSAMPLING / GaussianFullScale / 2);

}

static

void

correct_samples( void )

ınt a:

```

4.00

```

pouble k.

double temp.

double I_temp:

double Q_temp.

k = exp((double) ((double) (-1) ((double)) SAMPLING_FREQUENCY * RESISTANCE *

CAPACITANCE (1).

Lemp = IShape(0) | *CORRECTION_FACTOR;

Q_temp = QShapet 0 | *CORRECTION_FACTOR:

for( a=1, a<GAUSSLENGTH + OVERSAMPLING*4: a++ + }

temp = IShape; a |*CORRECTION_FACTOR.

IShape[a] = (int)(t temp + k * I_temp + i + 1 + k)).

I_temp = temp;

temp = QShapet a |*CORRECTION FACTOR:

QShape[a] = (int)((temp - k * Q_temp) + (1 - k)).

Q_temp = temp:

static void BuildSegments(void)

int Array[4].

int a:

int BaseIndex:

if (bGraphit)(

SetGraphParametersi-TANDQFULLSCALE, TANDQFULLSCALE, 16*10, GAUSSLENGTH

+ OVERSAMPLING*2.

"Iand Q patterms 1.

\% Based on all 16 combination of the four surrounding bits of a transition, calculate

\ell all I and Q segments for the 16 possible combinations

tor (Arrav[0] = 0, Arrav[0] < 2. Arrav[0] ++i(

for \{Array[1] = 0, Array[1] < 2, Array[1] + +ii

for (Array[2] = 0.Array[2] < 2.Array[2] ++)(

for (Array[3] = 0)Array[3] < 2:Array[3]++1{

BuildGMSK(Array);

landQModulate();

iff correct_samples_flag ) |

correct_samples();

}

if (bGraphit))

for (a=0):a<9:a++1[

TimeMark(OVERSAMPLING*a. -1 BLUE).

GraphFunction(GmskShape, RED),

GraphFunction(IShape, CYAN).

GraphFunction(QShape GREEN).

BaseIndex = (Array(3) + Array(2)^2 + Array(1)^4 + Array(0)^8) * OVERSAMPLING.

```

-

```

// Take the data from between the second and third bits, where it is

# least influenced by undetermined outside bits. These segments will

# later be used to piece tognether I and Q data for regular modulation.

for (a=t):a<OVERSAMPLING:a++if

|Tables|BaseIndex+a| = |IShape|OVERSAMPLING*3 + OVERSAMPLING/2 + a_i

QTables(BaseIndex+a) = QShaperOVERSAMPLING^*3 + OVERSAMPLING/2 + a);

if (bGraphit) geicht).

7 Now build the table for the startup sequence, based on a $10011001100 bit sync

If starting sequence. Startup is special as it is not surrounded by bits on the

If left side, which makes a slight difference in the gaussian and I and Q segments

if ibBasestation)

Arrav(0) = 1: Arrav(1) = 1.

Array(2) = 0. Arrav[3] = 0

Array(0) = 0 Array(1) = 0.

Arrav[2] = 1 Arrav[3] = 1

BuildGMSK(Array);

landQModulatec),

// Copy the segments safely away into a storage array. Segments are already

# in their proper order.

for (a=t):a<OVERSAMPLING*3;a++)(

|Start \Gamma able[a] = |Shape[a+OVERSAMPLING/2]|,

QStartTable(a) = QShape(a+OVERSAMPLING/2);

* Function to initialize the table offsets for different starting phases.

void InitPhaseIndices(void)

if (bBaseband)

[QInit[0] [Pointer = |Tables:

[QInit(0].QPointer = QTables:

[QInit(0)] | Sign = 1:

[QInit(0)].QSign = 1.

[QInit[1]. [Pointer = |Tables:

[QInit[1] QPointer = QTables:

IQInit[1].ISign = 1:

IQInit[1] QSign = 1

IQInit(2].IPointer = ITables;

|QInit(2) QPointer = QTables:

IQInit[2].ISign = 1.

IQInit(2).QSign = 1

IQInit(3).IPointer = (Tables:

IQInit(3).QPointer = QTables:

```

```

1QInin 31 ISign = i

1QIniti3| QSign = 1

eise i

IQInit(0) IPointer = (Tables.

IQInit(0).QPointer = QTables.

[QInit[0] ISign = 1:

IQIntt(0).QSign = f

[QInit[1] IPointer = QTables.

[QInit[1] QPointer = (Tables.

|Qlnit||||ISign = 1;

IQInit[1] QSign = 1

| IQInit[2] | IPointer = |Tables.

IQInit[2].QPointer = QTables:

|QInit(2).1Sign = -1

IQInit(2) QSign = 1

IQInit[3].IPointer = QTables.

[QInit[3] QPointer = [Tubles.

|Qlnit|3| |Sign = 1

[QInit[3] QSien = 1

void TestModulater)

// Modulation status variables:

int BitHistory;

// Contains history of surrounding bits used

\mathcal{I} in selecting the appropriate gaussian segment

int SamplesLett:

// Number of samples remaining in current segment

int StartingPhase.

# Cumulative phase (0 to 3) of bits no longer under

# direct consideration in BitHistory

int * IPointer, * QPointer.

#1 & Q Waveform pointers

int ISign. QSign:

#1& Q Signs (+1-1)

//-----

# Following lines for demo code only

int SourceBits[25]; // Bit pattern to modulate

static int Outputl[OVERSAMPLING*21]: // Place for storing I part of wave

static int OutputQ[OVERSAMPLING*21], # Place for storing Q part of wave

int Sample:

// Modulated sample count

int BitIndex:

// Index into SourceBits[] Array

// Generate a series of bits

tor (BitIndex=0.BitIndex<25.BitIndex++){

SourceBits[BitIndex] = i).

SourceBits[2] = 1

SourceBits[3] = 1

SourceBits(4) = 1:

SourceBits[5] = 1.

SourceBits[9] = 1

```

. . .

```

SourceBits[1]] = 1:

if Set up the starting sequence of moving from carrier to bitsync

# This is different from regular bits, as the non bits (neutral bits) have a different

if effect on the I and Q segments to be used than regular bits would. We use a special

{\it \#} Starting sequence, which assumes that the start of the modulation is 1100, the start

if of the mobile bitsvnc.

if (bBasestation))

/* Starting conditions for 11001100 - Base station **

SamplesLett = OVERSAMPLING 1/3.

iPointer = IStart Table

QPointer = QStart Table:

ISign = 1.

QSign ≈ 1.

BitHistory = 6.

StartingPhase = 1.

BitIndex = 3:

leisel

* Starting conditions for (i011)011 Mobile transmit **

SamplesLeft = OVERSAMPLING * 1

(Pointer = IStanTuble.

QPointer = QStart Fable.

ISign = 1.

QSign = 1.

BitHistory = 1.

StartingPhase = 1

BitIndex = 1

# Generate the waveform by sending out segments of the precalculated tables

for (Sample = 0:Sample<0)VERSAMPLING*21.Sample++1{

if (SamplesLett == 0){

#Take the bit no longer used for selecting I and Q segment, and

// add its phase contribution to StartingPhase

if (BitHistory & 8)}

StartingPhase = (StartingPhase + 1) & 3.

leise

StartingPhase = (StartingPhase - 1) & 3.

// Shift the bits currently under consideration to accomodate new bit.

// MSB is discarded (its phase contribution is is already accounted for).

BitHistory = ((BitHistory << 1) + SourceBits(BitIndex++|) & 15:

// Based on starting phase and surrounding bits, select the appropriate

#I and Q segments. Phase shift is in increments of 90 degrees. Use

// Tables to select the proper phase shift.

| Pointer = BitHistory * OVERSAMPLING + IQInit(StartingPhase). | Pointer:

QPointer = BitHistory * OVERSAMPLING + IQInit(StartingPhase) QPointer:

ISign = iQlnit[StartingPhase].[Sign:

QSign = IQInit(StartingPhase).QSign:

// Now have OVERSAMPLING samples before this calculation nees repetition.

```

SamplesLeft = OVERSAMPLING.

```

Crank out one sample at a time, until its time to select a new segment.

SamplesLeft = 1

Output! Sample] = *(!Pointer+++ * !Sign;

OutputQ[Sample] = *(QPointer++) * QSign:

il (bGraphiti)

int a:

SetGraphParameters(-IANDQFULLSCALE, IANDQFULLSCALE, 16*10.

OVERSAMPLING*16."Land Q segments (c)

for (a=0).a<16.a++14

TimeMark(OVERSAMPLING*a, +1, RED).

GraphFunction(Outputl, CYAN)

GraphFunction(OutputQ, GREEN)

for (a=OVERSAMPLING*16 a>0.a--n

Output[[a] = (Output[[a]-Output[[a-1]]) * (OVERSAMPLING/2).

OutputQ\{a\} = (OutputQ\{a\} \cdot OutputQ\{a-1\}) * (OVERSAMPL!NG/2).

getch().

SetGraphParameters(-IANDQFULLSCALE, IANDQFULLSCALE, 16*10.

OVERSAMPLING*16. T and Q slopes 1.

for (a=0:a<16.a++){

TimeMark(OVERSAMPLING*a -1, RED).

GraphFunction(Outputi, CYAN);

GraphFunction(OutputQ, GREEN).

getch();

# How to use program if used wrong

static void Usaget)

printif("usage of modtab program:vi"

modiab [-b] [-g]\n"

where:\m"

" -b Indicates baseband graphin"

g Indicates graphing enabled\n

t Indicates base transmitting

" i use ideal samples\n");

exittO);

// Main program

```

```

void maint int argo, char *argv() )

int a.

char * outfilename = 'moddata.h'

FILE *outfile.

7 Interpret the command line arguments.

bGraphit = FALSE:

bBaseband = FALSE:

bBasestation = FALSE.

GaussianFullScale = GAUSSFULLSCALE:

correct_samples_flag = TRUE.

tor (a = 1.a<argc:a++)|

if (argv[a][0] == f \parallel argv[a][0] == -i

switch targv[a][1]){

case 'g'

case G

printf("Graphing enabledin )

bGraphit = TRUE:

break:

case b

case B

printfi "Baseband instead of I and Q\n.).

bBaseband = TRUE.

break:

case f.

case F:

printft "Full scale baseband enabled\n" ).

GaussianFullScale = IANDQFULLSCALE;

break:

case it:

printit "Base station transmit sequencesn" );

bBasestation = TRUE.

break;

case i

case I

printf("Using ideal samples in ).

correct_samples_flag = FALSE.

break:

case o':

case O'

printf("creating output file '%s'\n",argv(a]+2);

outfilename = argv(a)+2.

goto skipcheck:

default:

Usage();

if (argv(a)[2]) Usage();

kipcheck::

else

Usage().

if (bGraphit) SetHiresModel);

```

```

Build the GMSK waveform

BuildGaussiano:

Build the 16 pairs of I and Q segments and starting segments

BuildSegments().

# Initialize phase index tables

InitPhaseIndices();

# Try out the modulation sceme

TestModulater:

SetGraphParametersi-IANDQFULLSCALE, IANDQFULLSCALE, 10*10,

OVERSAMPLING*16."Lund Q segments ');

for (a=0:a<16.a++)(

TimeMark(OVERSAMPLING*a, -1 RED);

GraphFunction(ITables, CYAN),

GraphFunction(QTables, GREEN)

getchi)

if (bGraphii) SetTextModet i.

# Generate an output file of all the segments.

outfile = topen(outfilename, "w");

ifi outfile == NULL)

printf("Failed to create '%s'\n' .outfilename).

exit(1).

tpnntt(outfile, /*\n"),

for (a=1):a<argc.a++11

fprintitoutfile,"? s ".argv(al).

fprinttioutfile. '\n *\n ');

if (bBaseband)

fprinttroutile." * This file is BASEBAND\n"i.

elset

fprintf(outfile." * This file is I and Q\n' );

fprintfroutfile." * \n\n"i;

# if (bBaseband) fprintfroutfile, "#define BASEBAND I\n"),

fprintf(outfile," INIT I_samples in ).

fort a = 0: a < 16 \text{ OVERSAMPLING}, a + = 4)

```

•

```

(printitioutrile, "htt0x%.4x00, 0x%.4x00, 0x%.4x00,

0x\%.4x00".|Tables(a),|Tables(a+1].|Tables(a+2],|Tables(a+3]);

iff a < 16*OVERSAMPLING - 4.1

fprintfroutfile.",\n");

fprintfroutfile, ",n\n');

fprintt(outrie, 'INIT Q_samples \n').

for a = 0, a < 16*OVERSAMPLING, a += 4.1

fprintfroutile."\\\t0x\% 4x00. 0x\%.4x00. 0x\\ 4x00.

0)x\%.4x00".QTables\{a\}.QTables\{a+1\}.QTables\{a+2\}.QTables\{a+3\}.);

ift a < 16*OVERSAMPLING - 4)

fprinttoutfile.",\n"):

#ifdef NEVER

int Sample:

long MaxMag.

long MinMag:

int MinSample:

int MaxSample;

long Mag:

long |Sum;

long QSum:

long lAve:

long QAvg:

MinMag = 0x7FFFFFF.

MaxMag = 11x800000000

MinSample = 0x7FFF.

MaxSample = 0x8000:

ISum = 0

tor (Sample = 0.Sample < 16*OVERSAMPLING.Sample++)

Mag = ((long)[Tables(Sample]) * ((long)[Tables(Sample])

+ ((long)QTables(Sample)) * ((long)QTables(Sample));

if (MaxMag < Mag) MaxMag = Mag:

if (MinMag > Mag) MinMag = Mag;

printft"Mag; %ld MinMag, %ld MaxMag; %ld\n", Mag, MinMag, MaxMag);

if (MaxSample < !Tables(Sample)) MaxSample = !Tables(Sample).

if (MaxSample < QTables| Sample): MaxSample = QTables|Sample]:

if (MinSample > ITables(Sample)) MinSample = ITables(Sample);

if (MinSample > QTables|Sample|) MinSample = QTables|Sample|;

[Sum = |Sum + |Tables|Sample]:

QSum = QSum + iTables(Sample):

IAvg = ISum / 16*OVERSAMPLING:

QAvg = QSum / 16*OVERSAMPLING:

```

```

printti"[Sum: %ld QSum: %ld IAvg: %ld QAvg: %ld\n".ISum.QSum.iAvg.QAvg);

printf("MagError: %f%%n".midouble)MaxMag/idouble)MinMag-1)*100));

getch();

retum

#endif

fprintfroutfile.":'n\n");

tprintif(outfile," INIT initial_l_sumples:in 'ti

fort a = 0: a < 3*OVERSAMPLING (a+= 3.)

fprintfroutfile, "\https://dx%.4x00.0x%.4x00.

()x\%.4x00".IStartTable[a].IStartTable[a+1].IStartTable[a+2]).

iff a < 3*OVERSAMPLING = 3.)

fprintttouttile." [an].

tonntttoutfile."(\n\n");

fprintfroutfile, JNIT initial_Q_samples on the

tor( a = 0; a < 3*OVERSAMPLING, a += 3)

fprintfcouttile."\t\t0x% 4xt00, 0x%.4x00,

0x% 4x00", QStart Table(a), QStart Table(a+1), QStart Table(a+21).

ife a < 3*OVERSAMPLING - 3 i

fprint(outtile,",'n').

iprintf(outfile, in );

iprinitioutfile, 'n'),

if (bBaseband)(

fprintf(outfile," INIT carrier_l_sample: 0x000000 \( \lambda n \) );

fprintf(outfile," INIT carrier_Q_sample: 0x000000:\n");

else

fprintf(outfile." INIT carner_l_sample. 0x000000:\n");

fprintfroutfile." INIT carner_Q_sample: 0x7fff00:\n");

fprintt(outfile,"\n').

exit( 0 ).

```

printft"MinSample: 57d MaxSample 57d\n".MinSample.MaxSample).

#### II. Table for Quadrature Phase Modulation

/\*

- \* oblimoddatiq.h: was created using the command line:

- \* objunodlab.exe -1 -oobj\moddatiq.h

.

- \* The data is in the 16 MSB of the 24 bit words, which

- \* are used by the DSP when getting data from program

- \* memory

- This file is I and Q

\*/

#### INIT I\_samples:

0xa91100, 0xb0b200, 0xb8d100, 0xc16000. Oxca5300, 0xd39a00, 0xdd2800, 0xe6ec00, 0xf0d800 0xfadc00, 0x04e700, 0x0eeb00. 0x18d800.0x229e00, 0x2c2d00, 0x357600. 0x3e6b00, 0x46fc00, 0x4f1e00, 0x56c200, 0xa90500, 0xb0a000, 0xb8b400, 0xc13500, 0xca1400, 0xd34000, 0xdca900, 0xeo3d00, Oxefeb00. 0xf99f00, 0x034700. 0x0cct00. 0x162500, 0x1f3600, 0x27f200, 0x304500. 0x382400, 0x3f7f00, 0x4644f00, 0x4c8500, 0x9de800, 0xa25300, 0xa69c00, 0xaaa800, ()xae5f00, 0xb1aa00, 0xb47300, 0xb6ad00. 0xb84a00, 0xb94300, 0xb99600, 0xb94700. 0xb85d00. 0xb6e700. 0xb4f300, 0xb29700, 0xafea00, 0xad0400, 0xa9fd00, 0xabee00. 0x9dde00, 0xa24300, 0xa68300, 0xaa8300, 0xae2a00.0xb15e00.0xb40a00.0xb61b00. 0xb78500, 0xb83c00, 0xb83c00, 0xb78500. 0xb61b00, 0xb40a00, 0xb15e00, 0xae2a00. ()xaa8300, 0xa68300, 0xa24300, 0x9dde00. 0xa70300, 0xaa1400, 0xad1b00, 0xb00200. 0xb2af00, 0xb50c00, 0xb70000, 0xb87700, 0xb96000, 0xb9b000, 0xb95c00, 0xb86300, 0xb6c600, 0xb48c00, 0xb1c200, 0xae7600. 0xaabt00. 0xa6b200. 0xa26800, 0x9dfc00. 0xa70f00, 0xaa2500, 0xad3500, 0xb02800. 0xb2e700, 0xb55900, 0xb76c00, 0xb90b00. 0xba2800 0xbaba00 0xbaba00 0xba2800 0xb90b00. 0xb76c00, 0xb55900, 0xb2e700. 0xb02800, 0xad3500, 0xaa2500, 0xa70f00, 0xb35600, 0xb98600, 0xc04900, 0xc79500, 0xcf5e00, 0xd79700, 0xe02d00, 0xe90e00. 0xf22500, 0xfb5e00, 0x04a200, 0x0ddb00. 0x16f200, 0x1fd300, 0x286900, 0x30a200, 0x386b00, 0x3fb700, 0x467a00, 0x4caa00. 0xb36300. 0xb99a00. 0xc06700. 0xc7c100. 0xcf9f00, 0xd7f200, 0xe0ac00, 0xe9bd00, 0xf31300, 0xfc9b00, 0x064200, 0x0ff700. 0x19a500, 0x233a00, 0x2ca300, 0x35d100. 0x3eb000, 0x473200, 0x4f4800, 0x56e400. 0x4c9d00, 0x466600, 0x3f9900, 0x383f00. 0x306100, 0x280e00, 0x1f5400, 0x164300, 0x0ced00. 0x036500, 0xf9be00. 0xt00900, 1)xe65b00, 0xdcc600, 0xd35d00, 0xca2f00. 0xc15000, 0xb8ce00, 0xb0b800, 0xa91c00, 0x4caa00, 0x467a00, 0x3fb700, 0x386b00.

#x30a200. 0x286900, 0x1fd300, 0x16f200. DxOddb00. 0x04a200. 0xfb5e00. 0xf22500, 1)xe90et)0, 0xe02d00, 0xd79700, 0xct5e00. 0xc79500, 0xc04900, 0xb98600, 0xb35600. 0x58f100, 0x55db00, 0x52cb00, 0x4fd800. 0x4d1900. 0x4aa700. 0x489400 0x46f500. 0x45d800, 0x454600, 0x454600, 0x45d800. 0x46f500, 0x489400, 0x4aa700, 0x4d1900, 0x4fd800, 0x52cb00, 0x55db00, 0x58f100, 0x58fd00, 0x55ec00, 0x52e500 0x4fe00. 0x4d5100, 0x4af400, 0x490000, 0x478900, 0x46a000, 0x465000, 0x46a400, 0x479d00, 0x493a00, 0x4b7400, 0x4e3e00, 0x518a00, 0x554100, 0x594e00, 0x5d9800, 0x620400 0x622200. 0x5dbd00, 0x597d00, 0x557d00. 0x51d600. 0x4ea200, 0x4bf600, 0x49e500, 0x487b00, 0x47c400, 0x47c400, 0x487b00, 0x49e500, 0x4bf600, 0x4ea200, 0x51d600. 0x557d00, 0x597d00, 0x5dbd00, 0x622200. 0x621800, 0x5dad00, 0x596400, 0x555800, 0x51a100, 0x4e5600, 0x4b8d00, 0x495300 9x47b600, 0x46bd00, 0x466a00, 0x46b900. 0x47a300. 0x491900. 0x4b0d00. 0x4d6900. 0x501600, 0x52fc00, 0x560300, 0x591200. 0x56fb00, 0x4f6000, 0x474c00, 0x3ecb00. 0x35ec00, 0x2cc000, 0x235700, 0x19c300, 0x101500, 0x066100, 0xfcb900, 0xf33100, 0xe9db00, 0xe0ca00, 0xd80e00, 0xcfbb00. 0xe7dc00, 0xc08100, 0xb9b300, 0xb37b00. 0x56ef00, 0x4f4e00, 0x472f00, 0x3ea000. 0x35ad00, 0x2c6600, 0x22d800, 0x191400. 0x0f2800, 0x052400, 0xfb1900, 0xf11500 Oxe72800, Oxdd6200, Oxd3d300, Oxca8a00, 0xc19500, 0xb90400, 0xb0e200, 0xa93e00,

#### INIT Q\_samples:

0xa20f00, 0x9b8900, 0x95a000, 0x905f00. 0x8bce00. 0x87f400. 0x84d700. 0x827d00. 0x80e800, 0x801c00, 0x801a00, 0x80e100, 0x827100, 0x84c700, 0x87df00, 0x8bb500, 0x904200. 0x957f00, 0x9b6300, 0xale600, 0xa21a00. 0x9b9800. 0x95b400. 0x907800. 0x8beb00, 0x881500, 0x84fb00, 0x82a000. 0x810500, 0x802a00, 0x800c00, 0x80a600. 0x81f000, 0x83df00, 0x866600, 0x897500. 0x8cfa00, 0x90de00, 0x950a00, 0x996600. 0xadc800. 0xa8c800. 0xa46500. 0xa09d00. 0x9d6a00, 0x9ac800, 0x98af00, 0x971700, 0x95fc00. 0x955400, 0x95le00. 0x955200. 0x95ee00, 0x96ef00, 0x985200, 0x9a1100, 0x9c2800, 0x9e8e00, 0xa13700, 0xa41500, 0xadd400, 0xa8d900, 0xa47d00, 0xa0be00, 0x9d9700, 0x9b0200, 0x98fc00, 0x977e00. 0x968200, 0x960500, 0x960500, 0x968200, 0x977e00, 0x98fc00, 0x9b0200, 0x9d9700, 0xa0be00.0xa47d00.0xa8d900.0xadd400. 0x5c0000. 0x5ede00. 0x618600. 0x63eb00. 0x660100, 0x67c000, 0x692200, 0x6a2300. 0x6abf00, 0x6af300, 0x6abc00, 0x6a1500,

0x68fa00. 0x676300. 0x654b00. 0x62a900. 0x5f7800, 0x5bb000, 0x574e00, 0x525000. 0x5c0b00, 0x5eee00, 0x619c00, 0x640a00, 0x662b00. 0x67f800, 0x696d00, 0x6a8600, 0x6b4200, 0x6ba000, 0x6ba000, 0x6b4200, 0x6a8600, 0x696d00, 0x67f800, 0x662b00. 0x640a00, 0x619c00, 0x5eee00, 0x5c0b00. 0x667e00, 0x6ad800, 0x6f0200, 0x72e300, 0x766500, 0x797200, 0x7bf900, 0x7dec00. 0x7f3e00. 0x7fe900. 0x7fe900. 0x7f3e00. 0x7dec00, 0x7bf900, 0x797200, 0x766500. 0x72e300, 0x6f0200, 0x6ad800, 0x667e00, 0x66880. 0x6ae500. 0x6f1300. 0x72f900, f)x767f00. 0x799000. 0x7c1a00. 0x7e0b00. 0x7f5700, 0x7ff300, 0x7fd700, 0x7eff00. 0x7d6600, 0x7b0d00, 0x77f500, 0x742100, 0x6f9700. 0x6a5d00, 0x647b00. 0x5dfb00, 0x668800, 0x6ae500, 0x6f1300, 0x72f900. 0x767f00. 0x799000. 0x7c1a00, 0x7e0b00. 0x7f5700. 0x7ff300. 0x7fd700, 0x7eff00, 0x7d6600, 0x7b0d00, 0x77f500, 0x742100. 0x6t9700. 0x6a5d00. 0x647b00. 0x5dtb00. 0x667e00, 0x6ad800, 0x6t0200, 0x72e300, 0x766500, 0x797200, 0x7bf900, 0x7dec00. 0x7f3e00, 0x7fe900, 0x7fe900, 0x7f3e00, 0x7dec00.0x7bf900.0x797200.0x766500. 0x72e300. 0x6f0200, 0x6ad800, 0x667e00, 0x5c0b00, 0x5eeei)0, 0x619c00, 0x640a00. 0x662b00, 0x67f800, 0x696d00, 0x6a8600. 0x6b4200. 0x6ba000. 0x6ba000, 0x6b4200. 0x6a8600. 0x696d00, 0x67f800, 0x662b00. 0x640a00, 0x619c00. 0x5eee00, 0x5c0b00, 0x5c0000, 0x5ede00, 0x618600, 0x63eb00 0x660100, 0x67c000, 0x692200, 0x6a2300. 0x6abt00.0x6af300.0x6abc00.0x6a1500. 0x68fa00. 0x676300, 0x654b00. 0x62a900. 0x5f7800, 0x5bb000, 0x574e00, 0x525000, 0xadd400.0xa8d900.0xa47d00.0xa0be00. 0x9d9700. 0x9b0200, 0x98fc00. 0x977e00. 0x968200. 0x960500. 0x960500, 0x968200. 0x977e00, 0x98fc00, 0x9b0200, 0x9d9700. 0xa0be00, 0xa47d00, 0xa8d900, 0xadd400. 0xadc800.0xa8c800.0xa46500.0xa09d00. 0x9d6a00, 0x9ac800, 0x98af00, 0x971700. 0x95fc00, 0x955400, 0x951e00, 0x955200. 0x95ee00, 0x96ef00, 0x985200, 0x9a1100, 0x9c2800. 0x9e8e00. 0xa13700, 0xa41500. 0xa21a00, 0x9b9800, 0x95b400, 0x907800, 0x8beb00, 0x881500, 0x84fb00, 0x82a000, 0x810500. 0x802a00. 0x800c00, 0x80a600. 0x81f000. 0x83dfQ0, 0x866600, 0x897500, 0x8cfa00, 0x90de00, 0x950a00, 0x996600. 0xa20f00, 0x9b8900, 0x95a000, 0x905f00, 0x8bceti0. 0x87f400, 0x84d700, 0x827d00. 0x80e800. 0x801c00. 0x801a00, 0x80e100. 0x827190. 0x84c700, 0x87df00, 0x8bb500, 0x904200.0x957f00.0x9b6300.0xale600;

INIT initial\_l\_samples:

```

0xfff800, 0xfff500, 0xffet@0.

0xffe800. 0xffde00. 0xffd100

Oxffbf00, Oxfta700, Oxff8900,

0xtf6200. 0xff3000, 0xtet100.

0xfea100.0xfe3e00.0xtdc300.

0xfd2c00, 0xfc7400, 0xfb9700.

0xfa8e00, 0xf95400, 0xt7e100.

0xf62f00. 0xf43600, 0xf4f100.

0xef5900 0xecb900, 0xe91c00.

0xe56e00, 0xe15f00, 0xdcef00.

0xd82100, 0xd2fb00, 0xcd8500

0xc7cb00, 0xc1db00, 0xbbc400

()xb59800, 0xaf6c00, 0xa95200.

0xa360(0), 0x9dab00, 0x984700

0x934800, 0x8ebf00, 0x8abc00.

0x874d00, 0x847e00 0x825800.

0x80e200, 0x802000, 0x801100,

0x80b400, 0x820200, 0x83f300.

0x867a00, 0x898800, 0x8d0b00,

0x90ed00 0x951700.0x997100;

```

#### INIT initial\_Q\_samples:

0x7ffe00. 0x7ffe00, 0x7ffe00. 0x7ffe00, 0x7ffe00, 0x7ffe00. 0x7ffe00, 0x7ffe00, 0x7ffe00. 0x7ffe00. 0x7ffe00. 0x7ffd00. 0x7ffd00. 0x7ffb00, 0x7ff900. 0x7ff600. 0x7ff200, 0x7feb00. 0x7fe100. 0x7fd200. 0x7fbc00. 0x7f9e00, 0x7f7300, 0x7f3800, 0x7ee800. 0x7e7c00. 0x7dee00. 0x7d3500, 0x7c4600, 0x7b1900. 0x79a000, 0x77d100, 0x759e00 0x72fe00, 0x6fe500, 0x6c4a00, 0x682500.0x637200.0x5e2d00. 0x585600, 0x51ef00, 0x4af100. 0x438c00, 0x3ba100, 0x334a00, 0x2a9600, 0x219600, 0x185b00. 0x0ef800, 0x058100, 0xfc0c00. 0xf2ab00, 0xe97400, 0xe07b00 0xd7d300, 0xct8d00, 0xc7ba(X). 0xc06700.0xb9a000.0xb36d00.

INIT carrier\_l\_sample: 0x000000; INIT carrier\_Q\_sample: 0x7fff00;

#### III. Table for Baseband Modulation

- \* obi\moddatbb.h: was created using the command line:

- \* objunodtab.exe -b -f -i -oobj\moddatbb h

- \* The data is in the 16 MSB of the 24 bit words, which

- \* are used by the DSP when getting data from program

- \* memory

- \* This file is BASEBAND

#### INIT I\_samples:

0x801e00, 0x801600, 0x801100, 0x800d00 0x800a00, 0x800700, 0x800600, 0x800500 0x800500, 0x800400, 0x800500, 0x800500. 1)x800600, 0x800700, 0x800a00, 0x800d00. 0x801100, 0x801600. 0x801e00, 0x802900. 0x808600, 0x80a400, 0x80d300, 0x811100. 0x816400. 0x81d100. 0x825e00. 0x830f00. 0x83ef00, 0x850400, 0x865b00, 0x87fb00, 0x89ee00, 0x8c4500, 0x8f0800, 0x924300, ()x960500, 0x9a5a00, 0x9f4c00, 0xa4e300. 0xab0e00, 0xb1e800. 0xb96d00, 0xc19300, 0xca5000.0xd38b00.0xdd2c00.0xe71100. 0xf11100, 0xfb0000, 0x04at00, 0x0det00. 0x169400, 0x1e6d00, 0x255800, 0x2b3300, 0x2fdd00, 0x334600, 0x355c00, 0x361700. 0xab7600, 0xb27600, 0xba2f00, 0xc29700, 0xcbaa00.0xd55500.0xdf8400.0xea1b00. 0xf4fb00, 0x000000, 0x0b0500, 0x15e500. 0x207c00. 0x2aab00, 0x345600, 0x3d6900. 0x45d100, 0x4d8a00, 0x548a00, 0x5ad100. 0x355c00, 0x334600, 0x2fdd00, 0x2b3300, 0x255800, 0x1e6d00, 0x169400, 0x0def00. 0x04af00, 0xfb0000, 0xt11100, 0xe71100. 0xdd2c00, 0xd38b00. 0xca5000, 0xc19300. 0xb96d00. 0xb1e800, 0xab0e00. 0xa4e300, 0x35c400, 0x33d400, 0x309f00, 0x2c3700. 0x26b200, 0x203700, 0x18ec00, 0x10f900. 0x089900, 0x0000000, 0x176700, 0xef0700, 0xe71400, 0xdfc900, 0xd94e00, 0xd3c900, 0xcf6100, 0xcc2c00, 0xca3c00, 0xc99d00, 0x604c00, 0x651800, 0x693900, 0x6cb900, 0x6f9e00, 0x71f100, 0x73ba00, 0x74fb00, 0x75bb00, 0x75fc00, 0x75bb00, 0x74fb00, 0x73ba00, 0x71f100, 0x6f9e00, 0x6cb900, 0x693900, 0x651800, 0x604c00, 0x5ad100, 0x60b400, 0x65a600, 0x69tb00, 0x6dbd00. 0x70f800, 0x73bb00, 0x761200, 0x780500. 0x79a500, 0x7afc00, 0x7c1100, 0x7cf100. 0x7da200, 0x7e2f00, 0x7e9c00, 0x7eet00. 0x7f2d00, 0x7f5c00, 0x7f7a00, 0x7f8b00. 0x9f4c00, 0x9a5a00, 0x960500, 0x924300, 0x8f0800, 0x8c4500, 0x89ee00, 0x87fb00, 0x865500, 0x850400, 0x83ef00. 0x830f00. 0x825e00. 0x81d100, 0x816400, 0x811100. 0x80d300, 0x80a400, 0x808600, 0x807500. 0x9fb400, 0x9ae800, 0x96c700, 0x934700,

0x906200, 0x8e0f00, 0x8c4600, 0x8b0500, 9x8a4500, 0x8a0400, 0x8a4500, 0x8b0500, 1)x8c4600. 0x8e0f00, 0x906200, 0x934700, 0x96c700, 0x9ae800, 0x9tb400, 0xa52f00, 0xca3c00, 0xcc2c00, 0xcf6100, 0xd3c900. 0xd94e00, 0xdfc900, 0xe71400, 0xef0700, 1)xf76700, 0x000000, 0x089900, 0x10f900. 1)x18ec00, 0x203700, 0x26b200, 0x2c3700. 0x309f00,0x33d400,0x35c400,0x366300. 0xcaa400, 0xccba00, 0xd02300, 0xd4cd00, 0xdaa800, 0xe19300, 0xe96c00, 0xt21100, 0xfb5100. 0x050000, 0x0eef00, 0x18ef00. 0x22d400, 0x2c7500, 0x35b000, 0x3e6d00. 0x469300, 0x4e1800, 0x54f200, 0x5b1d00, 0x548a00, 0x4d8a00, 0x45d100, 0x3d6900. 0x345600, 0x2aab00, 0x207c00, 0x15e500. 0x0b0500, 0x0000000, 0xf4fb00, 0xea1b00. 0xdf8400. 0xd55500, 0xcbaa00, 0xc29700. 0xba2f00, 0xb27600, 0xab7600, 0xa52f00. 0x54f200, 0x4e1800, 0x469300, 0x3e6d00 0x35b000. 0x2c7500. 0x22d400. 0x18ef00. 0x0cet00, 0x050000, 0xtb5100, 0xt21100, 0xe96c00, 0xe19300, 0xdaa800, 0xd4cd00, Oxd02300, 0xccba00, 0xcaa400, 0xc9e900 0x7f7a00, 0x7f5c00, 0x7f2d00, 0x7eet00. 0x7e9c00, 0x7e2f00, 0x7da200, 0x7cf100. 0x7c1100, 0x7afc00, 0x79a500, 0x780500 0x761200, 0x73bb00, 0x70f800, 0x6dbd00. 0x69fb00, 0x65a600, 0x60b400, 0x5b1d00. 0x7fe200, 0x7fea00, 0x7fef00, 0x7ff300, 0x7ff600, 0x7ff900, 0x7ffa00, 0x7ffb00, 0x7ffb00, 0x7ffc00, 0x7ffb00, 0x7ffb00, 0x7ffa00.0x7ff900.0x7ff600,0x7ff300, 0x7(ef00, 0x7(ea00, 0x7(e200, 0x7(d700;

47

#### INIT Q\_samples:

0x7fe200. 0x7fea00, 0x7fef00. 0x7ff300, 0x7ff600, 0x7ff900, 0x7ffa00, 0x7ffb00. 0x7ffb00, 0x7ffc00, 0x7ffb00, 0x7ffb00, 0x7ffa00. 0x7ff900, 0x7ff600, 0x7ff300, 0x7fef00, 0x7fea00, 0x7fe200, 0x7fd700, 0x7f7a00, 0x7f5c00, 0x7f2d00, 0x7eei00. 0x7e9c00, 0x7e2f00, 0x7da200, 0x7cf100, 0x7c1100, 0x7afc00, 0x79a500, 0x780500. 0x761200, 0x73bb00, 0x70f800, 0x6dbd00. 0x69fb00. 0x65a600, 0x60b400, 0x5b1d00, 0x54f200, 0x4e1800, 0x469300, 0x3e6d00. 0x35b000. 0x2c7500, 0x22d400, 0x18ef00. 0x0eef00.0x050000, 0xfb5100, 0xf21100, 0xe96c00, 0xe19300, 0xdaa800. 0xd4cd00. 0xd02300, 0xccba00. 0xcaa400. 0xc9e900. 0x548a00, 0x4d8a00, 0x45d100, 0x3d6900. 0x345600, 0x2aab00, 0x207c00, 0x15e500, 0x0b0500, 0x0000000, 0xf4fb00, 0xea1b00, 0xdf8400. 0xd55500. 0xcbaa00. 0xc29700. 0xba2f00. 0xb27600, 0xab7600. 0xa52f00, 0xcaa400, 0xccba00, 0xd02300, 0xd4cd00, 0xdaa800.0xe19300.0xe96c00.0xf21100. 0xfb5100, 0x050000, 0x0eet00, 0x18ef00,