This book is in the Addison-Wesley VLSI Systems Series.

Lynn Conway and Charles Seitz, Consulting Editors

#### The VLSI Systems Series

Circuits, Interconnections, and Packaging for VLSI by H. B. Bakoglu

Analog VLSI and Neural Systems by Carver Mead

The CMOS3 Cell Library edited by Dennis Heinbuch

Computer Aids for VLSI Design by Steven Rubin

The Design and Analysis of VLSI Circuits by Lance Glasser and Daniel Dobberpuhl

Principles of CMOS VLSI Design by Neil H. E. Weste and Kamran Eshraghian

Also from Addison-Wesley:

An Introduction to VLSI Systems by Carver Mead and Lynn Conway

# PRINCIPLES OF CMOS VLSI DESIGN A Systems Perspective

Second Edition

Neil H. E. Weste

TLW, Inc.

Kamran Eshraghian

University of Adelaide

#### ADDISON-WESLEY PUBLISHING COMPANY

Reading, Massachusetts • Menlo Park, California • New York Don Mills, Ontario • Wokingham, England • Amsterdam • Bonn Sydney • Singapore • Tokyo • Madrid • San Juan • Milan • Paris Sponsoring Editor: Peter S. Gordon Production Supervisor: Peggy McMahon

Marketing Manager: Bob Donegan Manufacturing Supervisor: Roy Logan

Cover Designer: Eileen Hoff Composition Services: Mike Wile

Technical Art Supervisor: Joseph K. Vetere Technical Art Consultant: Loretta Bailey Technical Art Coordinator: Alena B. Konecny

### Library of Congress Cataloging-in-Publication Data Weste, Neil H. E.

Principles of CMOS VLSI design: a systems perspective / Neil Weste, Kamran Eshraghian -- 2nd ed.

p. cm.

Includes bibliographical references and index.

ISBN 0-201-53376-6

Intergrated circuits--Very large scale integration--design and construction

Metal oxide semiconductors, Complementary.

I. Eshraghian, Kamran. . II. Title.

TK7874.W46 1992

621.3'95--dc20

92-16564

Cover Photo: Dick Morton Cover Art: Neil Weste

Photo Credit: Plates 5, 12, and 13, Melgar Photography, Inc., Santa Clara, CA

Copyright © 1993 by AT&T

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher. Printed in the United States of America.

1 2 3 4 5 6 7 8 9 10-MA-96959493

To Avril, Melissa, Tammy and Nicky and Shohreh, Michelle, Kylie, Natasha and Jason

## **ABOUT THE AUTHORS**

Neil Weste is President of TLW, Inc., a VLSI engineering company in Burlington, Massachusetts. Before cofounding TLW, he was Director of VLSI Systems at Symbolics, Inc., where he led the team that developed the Ivory Lisp microprocessor and the NS design system. Prior to joining Symbolics, Inc., Weste spent six years at AT&T Bell Labs in Holmdel, New Jersey. He worked one year at the Microelectronics Center of North Carolina, with teaching duties at Duke University and the University of North Carolina, Chapel Hill. Weste received his B. Sc., B.E., and Ph.D. from the University of Adelaide, South Australia.

Kamran Eshraghian is an Associate Professor in Electrical Engineering and Director of the Center for Gallium Arsenide VLS1 Technology at The University of Adelaide, South Australia. His research interests include very high performance circuits, systems and architectures with applications in digital signal processing. Eshraghian received his B.Tech., B.E., and Ph.D. from the University of Adelaide. Prior to teaching, Eshraghian was with Philips Ltd. as an IC designer.

vi

## **PREFACE**

In the eight years since this book was first published, CMOS technology has steadily moved to occupy a central position in modern electronic system design. Whether digital systems are high speed, high density, low power, or low cost, CMOS technology finds ubiquitous use in the majority of leading-edge commercial applications. CMOS processes have shrunk, and more automated design tools have become commonplace, leading to far more complex chips operating at much higher speeds than a decade ago. While the basic theory of CMOS design remains unchanged, the emphasis and approach to design have changed. With smaller processes and higher speeds comes an increased emphasis on clocking and power distribution, while with complex chip designs and short time-to-market constraints, less emphasis is now placed on die size and the physical details of chip design. The requirement for higher-quality CMOS chips has also increased the need for good approaches to testing.

This edition was updated with these changes in mind. All chapters have undergone extensive revision, and a new chapter on testing replaces one on symbolic layout. Sections on emerging technologies such as BiCMOS, logic synthesis, and parallel scan testing have been added. The overall emphasis has been to include as much as possible of the engineering (and to some extent, the economic) side of CMOS-system design. The artwork has been completely redone and many new figures have been added. All figures were captured on a CMOS VLSI design system. Thus, where possible, diagrams were checked via simulation or net comparison. The tendency has been to include figures where possible ("a picture is worth a thousand words") to trigger the reader's thinking.

vii

As a text, this book provides students with the necessary background to complete CMOS designs and assess which particular design style to use on a given design, from Field Programmable Gate Arrays to full custom design. For the practicing designer, the book provides an extensive source of reference material that covers contemporary CMOS logic, circuit, design, and processing technology.

In common with the first edition, the text is divided into three main sections. The first deals with basic CMOS logic and circuit design and CMOS processing technology. This includes design issues such as speed, power dissipation, and clocking and subsystem design. The second section deals with design approaches and testing. The final section describes three examples of CMOS module/chip designs to provide working examples of the material presented in the first two parts of the book.

In the eighties, designers struggled with tools, circuit techniques, and technology to build CMOS digital systems that could frequently be mastered by one person. The design issues, for example, related to whether a simulation for a circuit could be done and, if so, how accurately. Or perhaps the success of a project depended on a router or a design-rule checker that could deal with large databases. Today, the technology has moved to a point where, to a first order, the technology always works. Failures in design relate to incomplete specifications, inadequate testing, poor communication between designers in a team, or other issues that are somewhat removed from the detailed engineering that still has to take place. That engineering is supported by well-developed design tools. A significant task to be mastered in today's world (once the basics have been learnt) is to take a specification, turn it into a design, enter the design into a CAD system, test it, have it manufactured, and then be able to ship the product.

Increasingly, CMOS VLSI design is being seen as an ideal medium in which to teach the general digital (and analog) system design principles required in such a design process by introducing such issues as structured design and testing. Coupled with education-based Field Programmable Logic Array tools and prototyping kits, courses can be crafted around the basic principles of CMOS design, such as logic design and delay estimation, and coupled with more advanced topics such as simulation, timing analysis, placement and routing, and testing. With reprogrammable hardware, the concept-to-reality delay is reduced to minutes, and the education dynamics of almost-real-time feedback can only help in the education of tomorrow's system designers. The principles used in these laboratory systems are then applicable, with suitable modifications and information, to real-world products, whether such products employ gate-array, standard-cell, or full-custom CMOS design techniques.

Burlington, Mass.

N. H. E. W.

Technical Note: The text was revised using Microsoft Word 4/5 on an Apple Mac II (8Mb RAM, 1.2Gb disk) from a scanned OCR'ed version of the first-edition text. The figures were captured by the author using the TLW NS VLSI design software (developed at Symbolics) with custom Lisp code for specialized EPS output and for capturing SPICE simulation results. The NS design system was run under the Genera operating system on the Mac II, using a Symbolics MacIvory 2 board (2.6 Mwords physical memory, 400Mb of paging space), and a Symbolics XL 1200 Lisp machine. All design work (symbolic layout and schematic capture, net comparison, SPICE, timing and switch simulation, compaction, and timing analysis) dealt with in the book was completed on these machines. In fact, an interesting example of "the wheel of reincarnation" applies: the first edition of the book was used in part to create the Ivory Lisp microprocessor, while the processor was used in turn to create the second edition of the text.

#### **ACKNOWLEDGMENTS**

Bruce Edwards, Chris Terman, Jud Leonard, and Brian Ogilvie of TLW, Inc. supplied a number of the circuit designs used in this edition. They also provided comments and encouragement during the rewrite. Kurt Keutzer provided material on logic synthesis. Tom Knight, André DeHon, and Thomas Simon provided material on high-performance CMOS pads. Jim Cherry provided material on timing analyzers. Fred Rosenberger helped with metastability and provided corrections to the first edition. Don MacLennan provided feedback on the section on design economics. The author would like to acknowledge the support of Amihai Miron and that of Philips Laboratories for permission to include the ghost canceller system example in Chapter 9. Analog Devices provided the means to fabricate and test the A/D described in Chapter 9. Diane DeCastro was of assistance in the early stages of this rewrite with OCR support for the capture of the previous text. Bryan Ackland and Ismail Eldumiati of AT&T Bell Labs also provided assistance.

A number of reviewers were instrumental in determining the direction of this revision, and their detailed comments on the first drafts were much appreciated. In particular, the author would like to thank Don Trotter for sharing his course notes and his detailed comments on the first draft. Lex A. Akers, Jonathan Allen, Andreas Andreou, James H. Aylor, Prithvraj Banaerjee, Hans van den Biggelaar, Ray Chen, Willhelm Eggimann, Joseph Ku, Ronald K. Lomax, and John Uyemura also provided valuable feedback.

Finally, the author would like to thank his family—Avril, Melissa, Tammy, and Nicky—for their continued support and their work on the book through the long period it took to complete this revision.

Burlington, Mass.

N. H. E. W.

#### x PREFACE

#### KEY TO SCHEMATICS USED IN THIS BOOK

| P             | RIMITIVES                                                                                         |                      |                                  |                |                       | •                       |

|---------------|---------------------------------------------------------------------------------------------------|----------------------|----------------------------------|----------------|-----------------------|-------------------------|

| ଐ୕ୢ           | n-channel onhancement MOS transistor                                                              | <u> </u>             | capacitor                        | (1)            | gonesal v             | olago sourco            |

| -[[*          | p-channel enhancement MOS transactor                                                              | \$W                  | resistor                         | ٥              | pulso voli            | lago sourte             |

| ٠ <b>١</b> ١, | n-channel depletion MOS trensistar                                                                | ำแร                  | Inductor                         | ¢              | piocews.              | s linear voltage source |

| ښن<br>وړه     | junction diade                                                                                    | 7                    | VDO supply voltage               | $\diamondsuit$ | current se            | DUFCS                   |

| •             | non bipolar transistor                                                                            |                      |                                  |                |                       |                         |

| ٠[-           | prop bipolar transistor                                                                           | ~. <mark>\$</mark> ? | VSS supply voltage 🚚             | Ī              |                       | ansmission line         |

| 8             | usses                                                                                             |                      |                                  |                |                       |                         |

|               | 3                                                                                                 |                      | i≊∕* input port                  |                | <b>8</b> +(1)         | open dram port          |

|               |                                                                                                   |                      | • 🕾 output port                  |                | <b>ল</b> ্ট্র         | bidirectional port      |

|               | bus ripper taus for                                                                               | nt/join              | * '© tristate port               |                | *4.3                  | ынсео рогі              |

| n Barre       | o bus width<br>s width specifies the width of the bus and the b                                   |                      | anno as ba a da data'a anno ite. |                |                       |                         |

|               | u angulation of the pria are extracted from the pr                                                |                      | FOO                              | 4              | - A,B,C,              | D                       |

|               | nopper can extract erbitrary fields per connect<br>a bus fort/join extracts one signat per connec |                      | a bus ca<br>names o              | en be na       |                       | ncatenating             |

| 1             | 1 D                                                                                               |                      | Here the                         | abus FO        | O<3:0> is<br>• FOO<3> | made up of the signois  |

|               | 1 × A four bit bus with A<                                                                        | :0>:1                | A-to-y A-2>== A-3>=w             | IND WILL       | (FCORJ)               |                         |

| INS           | 7 11 35                                                                                           |                      |                                  |                |                       |                         |

|               | 15.12 CMD<br>11.8 WA A 16 bit bus callo<br>74 PA INST<3.0> FB                                     |                      |                                  |                |                       |                         |

| RE            | EPLICATION                                                                                        |                      |                                  |                |                       |                         |

|               | replication is indicated by a small x and a num                                                   | nber o               | n a schematic icon               |                |                       |                         |

|               | in shorter librated an investor librated                                                          | 6 bmc                | 9\$                              |                |                       |                         |

| Dŧ            | EVICE/GATE SIZES                                                                                  |                      |                                  |                |                       |                         |

|               | an nkiOS transistor with Width < 2 a * - 2/1 the units are in terms of minimum de                 | nd La                | ngth « !<br>andth cond temperate |                |                       |                         |

|               | i.e in a process where Wmin • Zµ a                                                                | nd La                | in ~0.8p. W+4p and L=0.8p        | lb.            |                       |                         |

|               | an inventor with p transis<br>4/2 and n transistor violing                                        |                      |                                  |                |                       |                         |

# **CONTENTS**

| PART<br>I <b>NT</b> | 1 RODUCTION TO CMOS TECHNOLOGY     |               |

|---------------------|------------------------------------|---------------|

| 1                   |                                    |               |

| INTE                | RODUCTION TO CMOS CIRCUITS         | 3             |

| 1.1                 | A Brief History                    | 3             |

| 1.2                 | Book Summary                       | 4             |

| 1.3                 | MOS Transistors                    | 5             |

| 1.4                 | MOS Transistor Switches            | 7             |

| 1.5                 | CMOS Logic                         | 9             |

|                     | 1.5.1 The Inverter                 | 9             |

|                     | 1.5.2 Combinational Logic          | 10            |

|                     | 1.5.3 The NAND Gate                | Series Series |

|                     | 1.5.4 The NOR Gate                 | 13            |

|                     | 1.5.5 Compound Gates               | 15            |

|                     | 1.5.6 Multiplexers                 | 17            |

|                     | 1.5.7 Memory—Latches and Registers | 19            |

| 1.6                 | Circuit and System Representations | 21            |

|                     | 1.6.1 Behavioral Representation    | 22            |

|                     | 1.6.2 Structural Representation    | 24            |

|                     | 1.6.3 Physical Representation      | 28            |

|                     |                                    |               |

| 26 10 |                    |    |

|-------|--------------------|----|

| ¥ iš  | CONTENT            | rc |

|       | 1.34 1191 1 = 1791 |    |

| 1.7  | An Ex    | ample                                         | 30 |

|------|----------|-----------------------------------------------|----|

|      | 1,7.1    | Specification                                 | 31 |

|      | 1.7.2    |                                               | 31 |

|      | 1.7.3    |                                               | 32 |

|      | 1.7.4    |                                               | 35 |

|      | 1.7.5    |                                               | 37 |

| 1.8  | CMO5     | Scorecard                                     | 38 |

| 1.9  | Summ     |                                               | 39 |

| 1.10 | Refere   |                                               | 39 |

| 2    |          |                                               |    |

| MOS  | TRANSI   | STOR THEORY                                   | 41 |

| 2.1  | Introdu  | ection                                        | 41 |

|      | 2.1.1    | nMOS Enhancement Transistor                   | 43 |

|      | 2.1.2    | pMOS Enhancement Transistor                   | 47 |

|      | 2.1.3    | Threshold Voltage                             | 47 |

|      |          | 2.1.3.1 Threshold Voltage Equations           | 48 |

|      | 2.1.4    | Body Effect                                   | 51 |

| 2.2  | MOS I    | Device Design Equations                       | 51 |

|      | 2.2.1    | Basic DC Equations                            | 51 |

|      | 2.2.2    | Second Order Effects                          | 53 |

|      |          | 2.2.2.1 Threshold Voltage—Body Effect         | 54 |

|      |          | 2.2.2.2 Subthreshold Region                   | 55 |

|      |          | 2.2.2.3 Channel-length Modulation             | 55 |

|      |          | 2.2.2.4 Mobility Variation                    | 56 |

|      |          | 2.2.2.5 Fowler-Nordheim Tunneling             | 57 |

|      |          | 2.2.2.6 Drain Punchthrough                    | 57 |

|      |          | 2.2.2.7 Impact Ionization—Hot Electrons       | 57 |

|      | 2.2.3    | MOS Models                                    | 58 |

|      | 2.2.4    |                                               | 59 |

| 2.3  | The Co   | amplementary CMOS Inverter—DC Characteristics | 61 |

|      | 2.3.1    | $\beta_n/\beta_p$ Ratio                       | 68 |

|      | 2.3.2    | Noise Margin                                  | 69 |

|      | 2.3.3    | The CMOS Inverter as an Amplifier             | 71 |

| 2.4  | Static I | Load MOS Inverters                            | 72 |

|      | 2.4.1    | The Pseudo-nMOS Inverter                      | 73 |

|      | 2.4.2    |                                               | 77 |

|      | 2.4.3    | Saturated Load Inverters                      | 78 |

|      | 2.4.4    | The Cascode Inverter                          | 80 |

|      | 2.4.5    | TTL Interface Inverter                        | 80 |

| 2.5  |          | fferential Inverter                           | 81 |

| 2.6  | The Tr   | ansmission Gate                               | 86 |

| 2.7  | The Tr   | istate Inverter                               | 91 |

| 2.8  | Bipolar   | Devices                                              | 91  |

|------|-----------|------------------------------------------------------|-----|

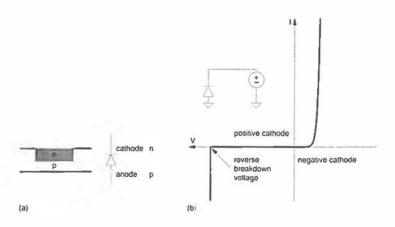

|      |           | Diodes                                               | 91  |

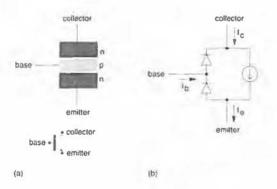

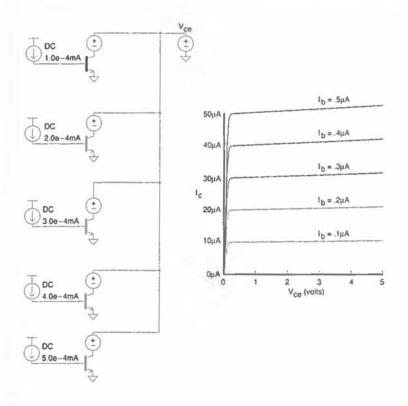

|      | 2.8.2     | Bipolar Transistors                                  | 93  |

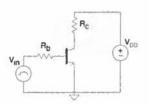

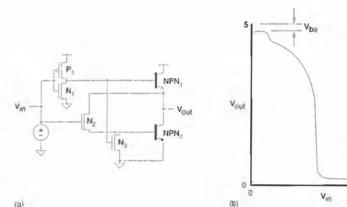

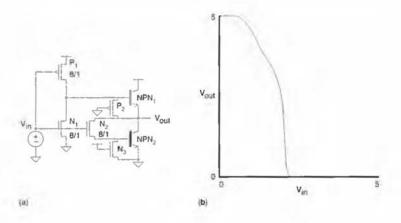

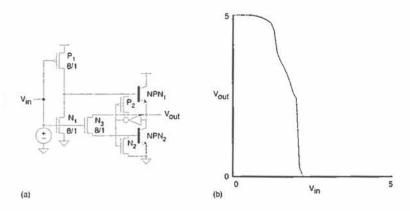

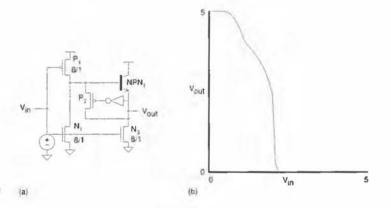

|      | 2.8.3     | BiCMOS Inverters                                     | 96  |

| 2.9  | Summai    | ry                                                   | 98  |

| 2.10 | Exercise  |                                                      | 98  |

| 2.11 | Append:   | ix—SPICE Level 3 Model                               | 99  |

| 2.12 | Referen   | çes                                                  | 106 |

|      |           |                                                      |     |

| 3    |           |                                                      |     |

| CMOS |           | SSING TECHNOLOGY                                     | 109 |

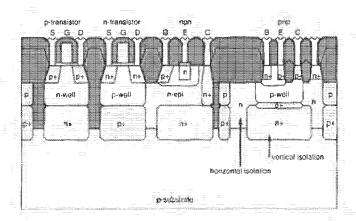

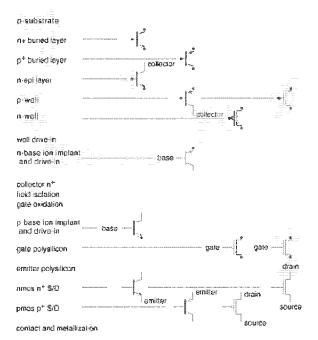

| 3.1  | Silicon S | Semiconductor Technology: An Overview                | 109 |

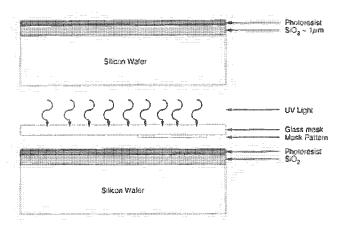

|      | 3.1.1     | Wafer Processing                                     | 110 |

|      | 3.1.2     | Oxidation                                            | 111 |

|      | 3.1.3     | Epitaxy, Deposition, Ion Implantation, and Diffusion | 111 |

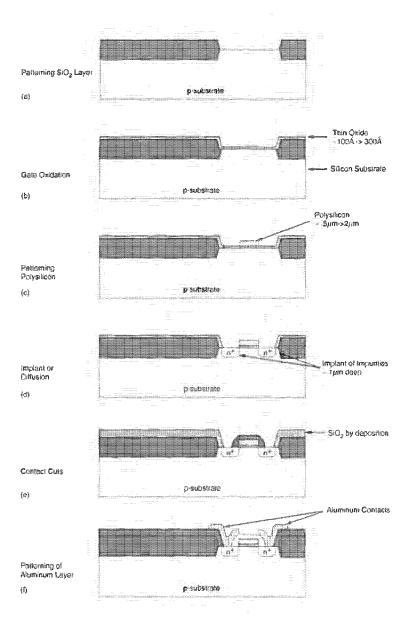

|      |           | The Silicon Gate Process                             | 113 |

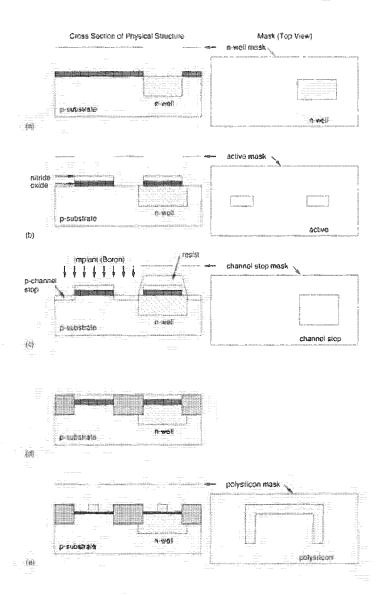

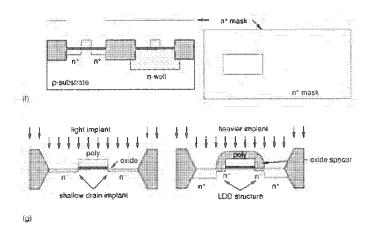

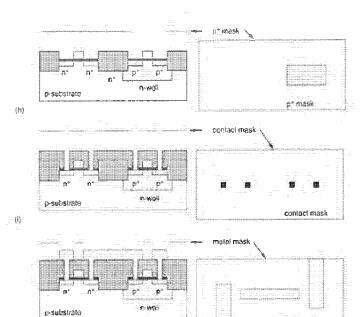

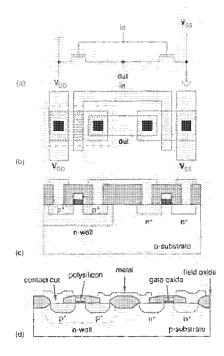

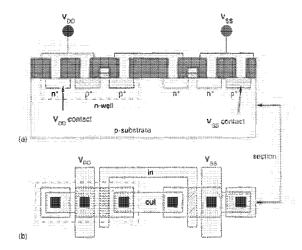

| 3.2  |           | MOS Technology                                       | 117 |

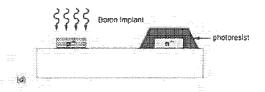

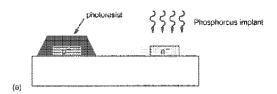

|      |           | A basic newell CMOS Process                          | 117 |

|      | 3.2.2     | The p-well Process                                   | 123 |

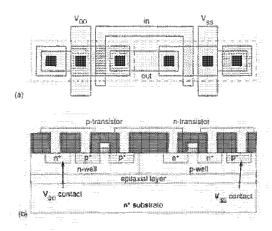

|      | 3.2.3     | Twin-Tub Processes                                   | 124 |

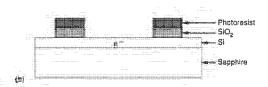

|      | 3.2.4     | Silicon On Insulator                                 | 125 |

| 3.3  | CMOS I    | Process Enhancements                                 | 130 |

|      | 3.3.1     | Interconnect                                         | 130 |

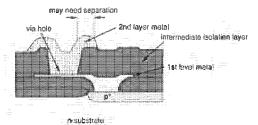

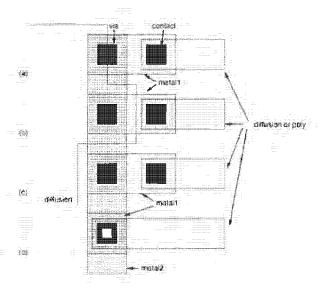

|      |           | 3.3.1.1 Metal Interconnect                           | 130 |

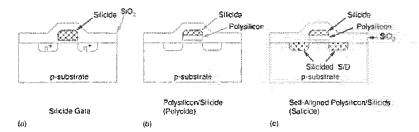

|      |           | 3.3.1.2 Polysilicon/Refractory Metal Interconnect    | 132 |

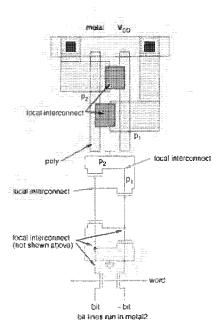

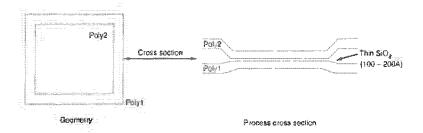

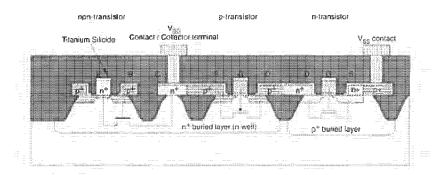

|      |           | 33.1.3 Local Interconnect                            | 133 |

|      | 3.3.2     | Circuit Elements                                     | 134 |

|      |           | 3.3.2.1 Resistors                                    | 134 |

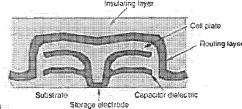

|      |           | 3.3.2.2 Capacitors.                                  | 134 |

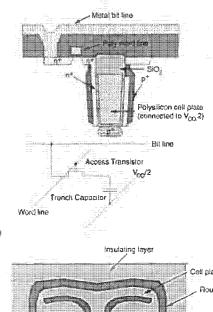

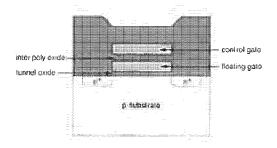

|      |           | 3.3.2.3 Electrically Alterable ROM                   | 136 |

|      |           | 3.3.2.4 Bipolar Transistors                          | 136 |

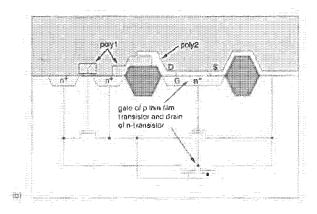

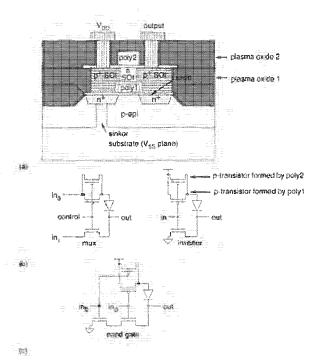

|      |           | 3.3.2.5 Thin-film Transistors                        | 139 |

|      | 3.3.3     | 3-D CMOS                                             | 140 |

|      | 3.3.4     | Summary                                              | 141 |

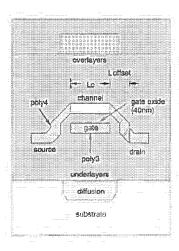

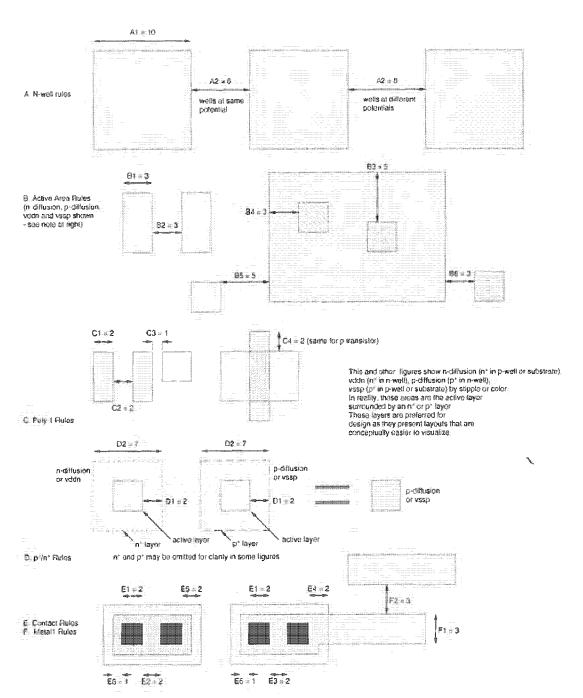

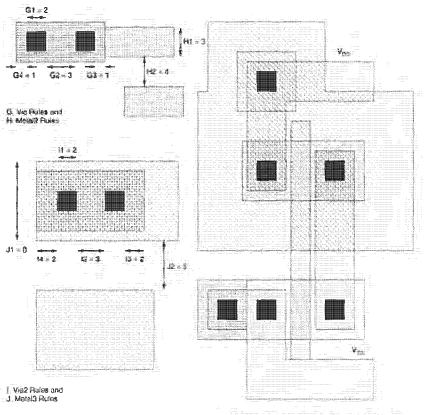

| 3.4  | Layout l  | Design Rules                                         | 142 |

|      | 3.4.1     | Layer Representations                                | 143 |

|      | 3.4.2     | CMOS n-well Rules                                    | 144 |

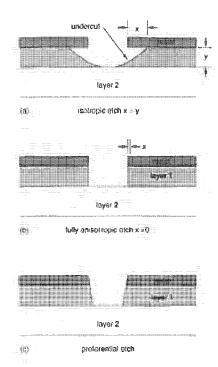

|      | 3.4.3     | Design Rule Backgrounder                             | 150 |

|      | 3.4.4     | Scribe Line                                          | 155 |

|      | 3.4.5     | Layer Assignments                                    | 155 |

|      | 3.4.6     | SOI Rules                                            | 156 |

|      | 3.4.7     | Design Rules—Summary                                 | 156 |

| 3.5  | Latchup   | ······································               | 156 |

|     | ATT ATT A ADDROUGH A NAME | - 4- |

|-----|---------------------------|------|

| XIV | CONTENT                   | 15   |

| 3.6        | 3.6.1<br>3.6.2     | The Physical Origin of Latchup Latchup Triggering Latchup Prevention Internal Latchup Prevention Techniques I/O Latchup Prevention ogy-related CAD Issues DRC—Spacing and Dimension Checks Circuit Extraction | 156<br>158<br>160<br>161<br>162<br>163<br>164<br>166 |

|------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 3.7<br>3.8 | Summar<br>Exercise | -                                                                                                                                                                                                             | 167                                                  |

| 3.9        |                    |                                                                                                                                                                                                               | 168                                                  |

|            |                    | ix—An n-well CMOS Technology Process Flow                                                                                                                                                                     | 172                                                  |

| 3.10       | Referen            | ces                                                                                                                                                                                                           | 172                                                  |

| 4          |                    |                                                                                                                                                                                                               |                                                      |

|            |                    | RACTERIZATION<br>MANCE ESTIMATION                                                                                                                                                                             | 175                                                  |

| 4.1        | Introduc           |                                                                                                                                                                                                               | 175                                                  |

| 4.2        |                    | ice Estimation                                                                                                                                                                                                | 176                                                  |

| 4.2        | 4.2.1              | Resistance of Nonrectangular Regions                                                                                                                                                                          | 178                                                  |

|            | 4.2.1              | Contact and Via Resistance                                                                                                                                                                                    | 179                                                  |

| 4.3        |                    | unce Estimation                                                                                                                                                                                               | 180                                                  |

| 4.3        | 4.3.1              |                                                                                                                                                                                                               | 180                                                  |

|            |                    | MOS-Capacitor Characteristics                                                                                                                                                                                 | 183                                                  |

|            | 4.3.2              | MOS Device Capacitances                                                                                                                                                                                       |                                                      |

|            | 4.3.3              | Diffusion (source/drain) Capacitance                                                                                                                                                                          | 186                                                  |

|            | 4.3.4              | SPICE Modeling of MOS Capacitances                                                                                                                                                                            | 188                                                  |

|            | 4.3.5              | Routing Capacitance                                                                                                                                                                                           | 191                                                  |

|            |                    | 4.3.5.1 Single Wire Capacitance                                                                                                                                                                               | 191                                                  |

|            |                    | 4.3.5.2 Multiple Conductor Capacitances                                                                                                                                                                       | 192                                                  |

|            | 4.3.6              | Distributed RC Effects                                                                                                                                                                                        | 198                                                  |

|            | 4.3.7              | Capacitance Design Guide                                                                                                                                                                                      | 202                                                  |

|            | 4.3.8              | Wire Length Design Guide                                                                                                                                                                                      | 204                                                  |

| 4.4        | Inductar           |                                                                                                                                                                                                               | 205                                                  |

| 4.5        |                    | ng Characteristics                                                                                                                                                                                            | 207                                                  |

|            | 4.5.1              | Analytic Delay Models                                                                                                                                                                                         | 208                                                  |

|            |                    | 4.5.1.1 Fall Time                                                                                                                                                                                             | 208                                                  |

|            |                    | 4.5.1.2 Rise Time                                                                                                                                                                                             | 210                                                  |

|            |                    | 4.5.1.3 Delay Time                                                                                                                                                                                            | 211                                                  |

|            | 4.5.2              | Empirical Delay Models                                                                                                                                                                                        | 213                                                  |

|            | 4.5.3              | Gate Delays                                                                                                                                                                                                   | 214                                                  |

|            | 4.5.4              | Further Delay Topics                                                                                                                                                                                          | 216                                                  |

|            |                    | 4.5.4.1 Input Waveform Slope                                                                                                                                                                                  | 216                                                  |

|            |                    | 4.5.4.2 Input Capacitance                                                                                                                                                                                     | 217                                                  |

|            |                    | 4.5.4.3 Switch-Level RC Models                                                                                                                                                                                | 218                                                  |

XV

|      |         | 4.5;4.4 Macromodeling                         | 221 |

|------|---------|-----------------------------------------------|-----|

|      |         | 4.5.4.5 Body Effect                           | 223 |

|      | 4.5.5   | Summary                                       | 225 |

| 4.6  | CMOS:   | -Gate Transistor Sizing                       | 226 |

|      |         | Cascaded Complimentary Inverters              | 226 |

|      | 4.6.2   | Cascaded Pseudo-nMOS Inverters                | 228 |

|      | 4.6.3   | Stage Ratio                                   | 229 |

| 4.7  |         | Dissipation                                   | 231 |

|      | 4.7.1   | Static Dissipation                            | 231 |

|      | 4.7.2   | Dynamic Dissipation Short-Circuit Dissipation | 233 |

|      |         |                                               | 235 |

|      | 4.7.4   | Total Power Dissipation                       | 236 |

|      |         | Power Economy                                 | 237 |

| 4.8  | Sizing  | Routing Conductors                            | 238 |

|      | 4.8.1   | Power and Ground Bounce                       | 239 |

|      |         | Contact Replication                           | 240 |

|      | Charge  |                                               | 240 |

| 4.10 |         | Margining                                     | 243 |

|      | 4.10.1  | Temperature                                   | 243 |

|      |         | Supply Voltage                                | 244 |

|      | 4.10.3  | Process Variation                             | 245 |

|      |         | Design Corners                                | 246 |

|      | 4.10.5  | Packaging Issues                              | 247 |

|      | 4.10.6  | Power and Clock Conductor Sizing              | 248 |

|      | 4.10.7  | Summary                                       | 248 |

| 4.11 | Yield   |                                               | 248 |

| 4.12 | Reliabi |                                               | 250 |

| 4.13 | Scaling | of MOS Transistor Dimensions                  | 250 |

|      | 4.13.1  | Scaling Principles                            | 251 |

|      | 4.13.2  | Interconnect-Layer Scaling                    | 253 |

|      | 4.13.3  | Scaling in Practice                           | 255 |

| 4.14 | Summa   | nry                                           | 255 |

| 4.15 | Exercis | es                                            | 256 |

| 4.16 | Referer | ices.                                         | 257 |

| 5    |         |                                               |     |

| _    | CIRCU   | IT AND LOGIC DESIGN                           | 261 |

| 5.1  | Introdu | ection                                        | 261 |

|      | CMOS    | Logic Gate Design                             | 262 |

|      |         | Fan-in and Fan-out                            | 264 |

|      |         | Typical CMOS NAND and NOR Delays              | 267 |

|      |         | Transistor Sizing                             | 271 |

|      | 5.2.4   | Summary                                       | 272 |

|      |         |                                               |     |

#### xvi CONTENTS

| 5.3        | Basic F | Physical Design of Simple Logic Gates      | 273  |

|------------|---------|--------------------------------------------|------|

|            | 5.3.1   | The Inverter                               | 273  |

|            | 5.3.2   | NAND and NOR gates                         | 278  |

|            | 5.3.3   | Complex Logic Gates Layout                 | 279  |

|            | 5.3.4   | CMOS Standard Cell Design                  | 283  |

|            | 5.3.5   | Gate Array Layout                          | 285  |

|            | 5.3.6   | Sea-of-Gates Layout                        | 286  |

|            | 5.3.7   | General CMOS Logic-Gate Layout Guidelines  | 287  |

|            | 5.3.8   | Layout Optimization for Performance        | 290  |

|            | 5.3.9   | Transmission-gate Layout Considerations    | 291  |

|            | 5.3.10  | 2-input Multiplexer                        | 294  |

| 5.4        |         | Logic Structures                           | 295  |

|            | 5.4.1   | CMOS Complementary Logic                   | 295  |

|            | 5.4.2   | BiCMOS Logic                               | 297  |

|            | 5.4.3   | Pseudo-nMOS Logic                          | 298  |

|            | 5.4.4   | Dynamic CMOS Logic                         | 301  |

|            | 5,4.5   | Clocked CMOS Logic (C <sup>2</sup> MOS)    | 302  |

|            | 5.4.6   | Pass-transistor Logic                      | 304  |

|            | 5.4.7   | CMOS Domino Logic                          | 308  |

|            | 5.4.8   | NP Domino Logic (Zipper CMOS)              | 310  |

|            | 5.4.9   | Cascade Voltage Switch Logic (CVSL)        | 311  |

|            | 5.4.10  | SFPL Logic                                 | 314  |

|            | 5.4.11  | Summary                                    | 315  |

| 5.5        |         | ng Strategies                              | 317  |

| and friend | 5.5.1   | Clocked Systems                            | 3.17 |

|            | 5.5.2   | Latches and Registers                      | 318  |

|            | 5.5.3   | System Timing                              | 322  |

|            | 5.5.4   | Setup and Hold Time                        | 323  |

|            | 5.5.5   | Single-phase Memory Structures             | 325  |

|            | 5.5.6   | Phase Locked Loop Clock Techniques         | 334  |

|            | 5.5.7   | Metastability and Synchronization Failures | 337  |

|            | 5.5.8   | Single-phase Logic Structures              | 340  |

|            | 5.5.9   | Two-phase Clocking                         | 344  |

|            | 5.5.10  | Two-phase Memory Structures                | 346  |

|            | 5.5.11  | Two-phase Logic Structures                 | 350  |

|            | 5.5.12  | Four-phase Clocking                        | 351  |

|            | 5.5.13  | Four-phase Memory Structures               | 352  |

|            | 5.5.14  | Four-phase Logic Structures                | 353  |

|            | 5.5.15  |                                            | 355  |

|            | 5.5.16  | Clock Distribution                         | 356  |

| 5.6        | I/O Str | * · · · · · · · · · · · · · · · · · · ·    | 357  |

| 51 (K)     | 5.6.1   | Overall Organization                       | 357  |

|            | 5.6.2   | $V_{DD}$ and $V_{SS}$ Pads                 | 360  |

|            | 5.6.3   | Outrout Pade                               | 360  |

|            |         |                                            |      |

|       |             |                                            |      | CONTENTS |

|-------|-------------|--------------------------------------------|------|----------|

|       | 5.6.4       | Input Pady                                 | 361  |          |

|       | 5.6.5       | •                                          | 364  |          |

|       | 5.6.6       |                                            | 365  |          |

|       | 5.6.7       |                                            | 367  |          |

| 5,7   |             | ower Design                                | 368  |          |

| 5.8   | Summ        |                                            | 370  |          |

| 5.9   | Exerci      | •                                          | 370  |          |

| 5:40  | Refere      | nces                                       | 372  |          |

| PART  | 9           |                                            |      |          |

| SYS   | Z<br>TEMS ( | DESIGN AND DESIGN METHODS                  | 379  |          |

| Ô     |             |                                            |      |          |

| ·1000 | S DESIG     | IN METHODS                                 | 381  |          |

| 6.1   | Introdu     | uction                                     | 381  |          |

| 6.2   |             | Strategics                                 | 382  |          |

|       | 6.2.1       | = ""                                       | 382  |          |

|       | 6.2.2       |                                            | 383  |          |

|       |             | Hierarchy                                  | 384  |          |

|       | 6.2.4       |                                            | 387  |          |

|       | 6.2.5       | •                                          | 387  |          |

|       | 6.2,6       |                                            | 389  |          |

|       | 6.2.7       |                                            | 39 i |          |

| 6.3   |             | Chip Design Options                        | 391  |          |

|       | 6.3.1       |                                            | 391  |          |

|       | 6.3.2       | Programmable Logic Structures              | 392  |          |

|       | 6.3.3       | Programmable Interconnect                  | 395  |          |

|       | 6.3.4       | Reprogrammable Gate Arrays                 | 400  |          |

|       |             | 6.3.4.1 The XILINX Programmable Gate Array | 400  |          |

|       |             | 6.3,4.2 Algotronix                         | 403  |          |

|       |             | 6.3.4.3 Concurrent Logic                   | 406  |          |

|       | 6.3.5       | Sea-of-Gate and Gate Array Design          | 407  |          |

|       | 6.3.6       | Standard-cell Design                       | 413  |          |

|       |             | 6.3.6.1 A Typical Standard-cell Library    | 414  |          |

|       | 6.3.7       | Full-custom Mask Design                    | 417  |          |

|       | 6.3.8       | Symbolic Layout                            | 417  |          |

|       |             | 6.3.8.1 Coarse-grid Symbolic Layout        | 417  |          |

|       |             | 6.3.8.2 Gate-matrix Layout                 | 418  |          |

|       |             | 6.3.8.3 Sticks Layout and Compaction       | 420  |          |

|       |             | 6.3.8.4 Virtual-grid Symbolic Layout       | 421  |          |

|       | 630         | Process Migration—Retargetting Designs     | 423  |          |

XVII

#### xviii CONTENTS

| 6.4 | Design | n Methods                              | 424  |

|-----|--------|----------------------------------------|------|

| *   | 6.4.1  | Behavioral Synthesis                   | 424  |

|     | 6.4.2  | RTL Synthesis                          | 425  |

|     | 6.4.3  | Logic Optimization                     | 427  |

|     | 6.4.4  |                                        | 431  |

|     |        | 6.4.4.1 Placement                      | 431  |

|     |        | 6.4.4.2 Routing                        | 431  |

|     |        | 6.4.4.3 An Automatic Placement Example | 432  |

|     | 6.4.5  | Layout Synthesis                       | 434  |

| 6.5 | Design | n-capture Tools                        | 437  |

|     | 6.5.1  | HDL Design                             | 437  |

|     | 6.5.2  | -                                      | 438  |

|     | 6.5.3  |                                        | 438  |

|     | 6.5.4  | Floorplanning                          | 438  |

|     | 6.5.5  | Chip Composition                       | 439  |

| 6.6 | Design | n Verification Tools                   | 44() |

|     | 6.6.1  | Simulation                             | 441  |

|     |        | 6.6.1.1 Circuit-level Simulation       | 441  |

|     |        | 6.6.1.2 Timing Simulation              | 442  |

|     |        | 6.6.1.3 Logic level Simulation         | 443  |

|     |        | 6.6.1.4 Switch-level Simulation        | 444  |

|     |        | 6.6.1.5 Mixed-mode Simulators          | 444  |

|     |        | 6.6.1.6 Summary                        | 445  |

|     | 6.6.2  | Timing Verifiers                       | 445  |

|     | 6.6.3  | Network Isomorphism                    | 446  |

|     | 6.6.4  | Netfist comparison                     | 447  |

|     | 6.6.5  | Layout Extraction                      | 448  |

|     | 6.6.6  | Back-Annotation                        | 448  |

|     | 6.6.7  | Design-rule Verification               | 448  |

|     | 6.6.8  | Pattern Generation                     | 448  |

| 6.7 | Design | n Economics                            | 449  |

|     | 6.7.1  | Nonrecurring Engineering Costs (NREs)  | 450  |

|     |        | 6.7.1.1 Engineering Costs              | 450  |

|     |        | 6.7.1.2 Prototype Manufacturing Costs  | 451  |

|     | 6.7.2  | Recurring Costs                        | 452  |

|     | 6.7.3  | Fixed Costs                            | 452  |

|     | 6.7.4  | Schedule                               | 453  |

|     | 6.7.5  | Personpower                            | 454  |

|     | 6.7.6  | An Example—Gate-array Productivity     | 454  |

| 6.8 | Data S |                                        | 456  |

|     | 6.8.1  | The Summary                            | 456  |

|     | 6.8.2  | Pinout                                 | 456  |

|     | 6.8.3  | Description of Operation               | 457  |

|     | 6.8.4  | DC Specifications                      | 457  |

|      | 6.8.5   | AC Specifications                             | 457 |

|------|---------|-----------------------------------------------|-----|

|      | 6.8.6   | Package Diagram                               | 458 |

| 6.9  | Summa   | •                                             | 458 |

| 6.10 | Exercis |                                               | 458 |

| 6.11 | Referei | nces"                                         | 459 |

| 7    |         |                                               |     |

| 100  |         |                                               |     |

| CMOS | TESTI   | NG                                            | 465 |

| 7.1  | The Ne  | ed for Testing                                | 465 |

|      | 7.1.1   | *                                             | 466 |

|      | 7.1.2   | Manufacturing Tests                           | 468 |

|      | 7.1.3   | A Walk Through the Test Process               | 456 |

| 7.2  | Manufa  | acturing Test Principles                      | 471 |

|      | 7.2.1   | Fault models                                  | 472 |

|      |         | 7.2.1.1 Stuck-At Faults                       | 472 |

|      |         | 7.2.1.2 Short-Circuit and Open-Circuit Faults | 473 |

|      | 7.2.2   | Observability                                 | 474 |

|      | 7.2.3   | Controllability                               | 475 |

|      | 7.2.4   |                                               | 475 |

|      | 7.2.5   | Automatic Test Pattern Generation (ATPG)      | 476 |

|      | 7.2.6   | Fault Grading and Fault Simulation            | 481 |

|      | 7,2.7   | Delay Fault Testing                           | 482 |

|      | 7.2.8   | Statistical Fault Analysis                    | 483 |

|      | 7.2.9   | Fault Sampling                                | 484 |

| 7.3  | Design  | Strategies for Test                           | 485 |

|      | 7.3.1   | Design for Testability                        | 485 |

|      | 7.3.2   | Ad-Hoc Testing                                | 485 |

|      | 7.3.3   | Scan-Based Test Techniques                    | 489 |

|      |         | 7.3.3.1 Level Sensitive Sean Design (LSSD)    | 489 |

|      |         | 7.3.3.1 Serial Scan                           | 490 |

|      |         | 7.3,3.2 Partial Serial Scan                   | 493 |

|      |         | 7.3.3.3 Parallel Scan                         | 493 |

|      | 7.3.4   | Self-Test Techniques                          | 495 |

|      |         | 7.3.4.1 Signature Analysis and BILBO          | 495 |

|      |         | 7.3.4.2 Memory Self-Test                      | 497 |

|      |         | 7.3.4.3 Iterative Logic Array Testing         | 498 |

|      | 7.3.5   | IDDQ Testing                                  | 498 |

| 7,4  | Chip-L  | evel Test Techniques                          | 498 |

|      | 7.4.1   | Regular Logic Arrays                          | 499 |

|      | 7.4.2   | Memories                                      | 500 |

|      | 7.4.3   | Random logic                                  | 500 |

| 7.5  | System  | -Level Test Techniques                        | 500 |

|      | 7.5.1   | Boundary Scan                                 | 500 |

#### XX CONTENTS

|     |                 |                    | Introduction                            | 500 |  |

|-----|-----------------|--------------------|-----------------------------------------|-----|--|

|     |                 | 7.5.1.2            | The Test Access Port (TAP)              | 501 |  |

|     |                 |                    | The Test Architecture                   | 502 |  |

|     |                 | 7.5.1.4            | The Tap Controller                      | 502 |  |

|     |                 | 7.5.1.5            | The Instruction Register (IR)           | 503 |  |

|     |                 | 7.5.1.6            | Test-Data Registers (DRs)               | 504 |  |

|     |                 | 7.5.1.7            | Boundary Scan Registers                 | 504 |  |

|     | 7.5.3           | Summa              | ry                                      | 506 |  |

| 7.6 | Layout          | Design fo          | or Improved Testability                 | 506 |  |

| 7.7 | Summa           | mmary              |                                         |     |  |

| 7.8 | Exercis         | ercises            |                                         |     |  |

| 7.9 | Referer         | nces               |                                         | 508 |  |

| 8   |                 |                    |                                         |     |  |

| · · | SUBSY           | STEM C             | ESIGN                                   | 513 |  |

| 8.1 | Introdu         | ction              |                                         | 513 |  |

| 8.2 | Datpath         | ı Operatio         | ons                                     | 513 |  |

|     | 8.2.1           | Addition           | n/Subtraction                           | 515 |  |

|     |                 | 8.2.1.1            | Single-Bit Adders                       | 515 |  |

|     |                 | 8.2.1.2            | Bit-Parallel Adder                      | 517 |  |

|     |                 | 8.2.1.3            | Bit Serial Adders, Carry-save Addition, |     |  |

|     |                 |                    | and Pipelining                          | 520 |  |

|     |                 | 8.2.1.4            | Transmission-Gate Adder                 | 524 |  |

|     |                 | 8.2.1.5            | Carry-Lookahead Adders                  | 526 |  |

|     |                 | 8.2.1.6            | Carry-Select Adder                      | 532 |  |

|     |                 | 8.2.1.7            | Conditional-Sum Adder                   | 532 |  |

|     |                 | 8.2.1.8            | Very Wide Adders                        | 534 |  |

|     |                 |                    | Summary                                 | 536 |  |

|     | 8.2.2           |                    | ienerators                              | 537 |  |

|     | 8.2.3           | Comparators        |                                         | 537 |  |

|     | 8.2.4           | Zero/One Detectors |                                         | 537 |  |

|     | 8.2.5           | Binary (           | Counters                                | 539 |  |

|     |                 | 8.2.5.1            | Asynchronous Counters                   | 539 |  |

|     |                 | 8.2.5.2            | Synchronous Counters                    | 539 |  |

|     | 8.2.6           |                    | Operations—ALUs                         | 541 |  |

|     | 8.2.7           |                    | Multiplication                          |     |  |

|     |                 |                    | Array Multiplication                    | 545 |  |

|     |                 |                    | Radix-n Multiplication                  | 547 |  |

|     |                 |                    | Wallace Tree Multiplication             | 554 |  |

|     |                 |                    | Serial Multiplication                   | 557 |  |

|     | 8.2.8           | Shifters           | •                                       | 560 |  |

| 3,3 | Memory Elements |                    |                                         | 563 |  |

| -   |                 | •                  | rite Memory                             | 564 |  |

|             |         |                                          |            | CONTENTS | XX |

|-------------|---------|------------------------------------------|------------|----------|----|

|             |         |                                          |            |          |    |

|             |         | 8.3.1.1 RAM                              | 564        |          |    |

|             |         | 8.3.1.2 Register Files                   | 580        |          |    |

|             |         | 8.3.1.3 FIFOs, LIFOs, SIPOs              | 582        |          |    |

|             |         | 8.3.1.4 Serial-Access Memory             | 583        |          |    |

|             | 8.3.2   | Read Only Memory                         | 585<br>500 |          |    |

|             | 8.3.3   | Content-Addressable Memory               | 589        |          |    |

| 8.4         | Contro  |                                          | 590        |          |    |

|             | 8.4.1   | Finite-State Machines                    | 591        |          |    |

|             |         | 8.4.1.1 FSM Design Procedure             | 59 i       |          |    |

|             | 8.4.2   | Control Logic Implementation             | 595        |          |    |

|             |         | 8.4.2.1 PLA Control Implementation       | 595        |          |    |

|             |         | 8.4.2.2 ROM Control Implementation       | 602        |          |    |

|             |         | 8.4.2.3 Multilevel Logic                 | 604        |          |    |

|             |         | 8.4.2.4 An Example of Control            | 701        |          |    |

|             |         | Logic Implementation                     | 604        |          |    |

| 8.5         | Summ    | -                                        | 620        |          |    |

| 8.6         | Exerci  |                                          | 621<br>622 |          |    |

| 8.7         | Refere  | ices                                     | 044        |          |    |

| PART<br>CM( | _       | TEM CASE STUDIES                         | 625        |          |    |

| 9           |         |                                          |            |          |    |

| CMC         | S SYSTE | M DESIGN EXAMPLES                        | 627        |          |    |

| 9.1         | Introde | ction                                    | 627        |          |    |

| 9.2         | A Core  | RISC Microcontroller                     | 628        |          |    |

|             | 9.2.1   | Instruction Set                          | 629        |          |    |

|             |         | 9.2.1.1 Address Architecture             | 629        |          |    |

|             |         | 9.2.1.2 ALU Class Instructions           | 631        |          |    |

|             |         | 9.2.1.3 Control Transfer Instructions    | 633        |          |    |

|             | 9.2.2   | Pipeline Architecture                    | 634        |          |    |

|             |         | 9.2.2.1 Bypassing, Result Forwarding, or |            |          |    |

|             |         | Pass-around                              | 637        |          |    |

|             |         | 9.2.2.2 Conditional Branching            | 638        |          |    |

|             |         | 9.2.2.3 Subroutine Call and Return       | 639        |          |    |

|             |         | 9.2.2.4 I/O Architecture                 | 639        |          |    |

|             | 9.2.3   | •                                        |            |          |    |

|             |         | 9.2.3.1 ALU_DP                           | 640        |          |    |

|             |         | 9.2.3.2 Register File                    | 651        |          |    |

|             |         | 9.2.3.3 PC Datapath (PC_DP)              | 654        |          |    |

|             |         | 9.2.3.4 Instruction Memory               | 656        |          |    |

#### xxII CONTENTS

|     |                     | 9.2.3.5 Instruction Pipe                        | 656        |

|-----|---------------------|-------------------------------------------------|------------|

|     |                     | 9.2.3.6 Control Logic                           | 658        |

|     | 9.2.4               | Layout                                          | 663        |

|     |                     | 9.2.4.1 Datapath Floorplans:                    | 666        |

|     | 9.2.5               | Functional Verification and Testing             | 669        |

| 9.3 | A TV Echo Canceller |                                                 | 672        |

|     | 9.3.1               | Ghost Cancellation                              |            |

|     | 9.3.2               | FIR and IIR filters                             |            |

|     | 9.3.3               | -3                                              |            |

|     | 9.3.4               | Chip Architecture                               |            |

|     |                     | 9.3.4.1 Filter Considerations                   | 677        |

|     |                     | 9.3.4.2 Chip Overview                           | 678        |

|     | 9.3.5               | Submodules                                      | 680        |

|     |                     | 9.3.5.1 Filter Taps                             | 680        |

|     |                     | 9.3.5.2 Delay Lines                             | 685        |

|     |                     | 9.3.5.3 Phase-locked Loop- and Clock-generation | 685        |

|     |                     | 9.3.5.4 Peripheral Processing                   | 689<br>689 |

|     | 9.3.6               | Power Distribution                              |            |

|     | 9.3.7               | Chip Floorplan                                  |            |

|     | 9.3.8               | Testing and Verification                        |            |

|     | 9.3.9               | Summary                                         |            |

| 9.4 | A 6-bit Flash A/D   |                                                 | 694        |

|     | 9.4.1               | Introduction                                    | 694        |

|     | 9.4.2               |                                                 | 695<br>696 |

|     | 9.4.3               | Resistor String                                 |            |

|     | 9.4.4               | The Comparator                                  |            |

|     | 9.4.5               |                                                 |            |

|     | 9.4.6               | Floorplan and Layout                            |            |

|     | 9.4.7               | Summary                                         | 701        |

| 9.5 | Summa               | -                                               | 701        |

| 9.6 | Exercis             | ses                                             | 701<br>702 |

| 9.7 | References          |                                                 |            |

|     | INDEX               | (                                               | 703        |

# MOS TRANSISTOR THEORY

#### 2.1 Introduction

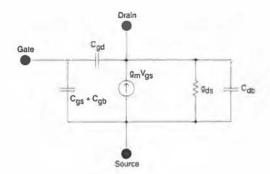

In Chapter 1 the MOS transistor was introduced in terms of its operation as an ideal switch. In this chapter we will examine the characteristics of MOS transistors in more detail to lay the foundation for predicting the performance of the switches, which is less than ideal. Figure 2.1 shows some of the symbols that are commonly used for MOS transistors. The symbols in Fig. 2.1(a) will be used where it is necessary only to indicate the switch logic required to build a function. If the substrate connection needs to be shown, the symbols in Fig. 2.1(b) will be used. Figure 2.1(c) shows an example of the many symbols that may be encountered in the literature.

This chapter will concentrate on the static or DC operation of MOS transistors. This is the first design goal that must be satisfied to ensure that logic gates operate as logic gates. All circuits are analog in nature and the digital abstraction only remains an abstraction as long as certain design goals are met. Design for timing constraints is covered in Chapter 4.

An MOS transistor is termed a majority-carrier device, in which the current in a conducting channel between the source and the drain is modulated by a voltage applied to the gate. In an n-type MOS transistor (i.e., nMOS), the majority characters are electrons. A positive voltage applied on the gate with respect to the substrate enhances the number of electrons in the channel

FIGURE 2.1 MOS transistor symbols

(the region immediately under the gate) and hence increases the conductivity of the channel. For gate voltages less than a threshold value denoted by  $V_l$ , the channel is cut off, thus causing a very low drain-to-source current. The operation of a p-type transistor (i.e., pMOS) is analogous to the nMOS transistor, with the exception that the majority carriers are holes and the voltages are negative with respect to the substrate.

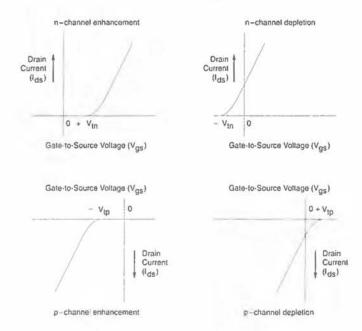

The first parameter of interest that characterizes the switching behavior of an MOS device is the threshold voltage, V<sub>t</sub>. This is defined as the voltage at which an MOS device begins to conduct ("turn on"). We can graph the relative conduction against the difference in gate-to-source voltage in terms of the source-to-drain current  $(I_{ds})$  and the gate-to-source voltage  $(V_{gs})$ . These graphs for a fixed drain-source voltage,  $V_{ds}$ , are shown in Fig. 2.2. It is possible to make n-devices that conduct when the gate voltage is equal to the source voltage, while others require a positive difference between gate and source voltages to bring about conduction (negative for p-devices). Those devices that are normally cut off (i.e., nonconducting) with zero gate bias (gate voltage-source voltage) are further classed as enhancement-mode devices, whereas those devices that conduct with zero gate bias are called depletion-mode devices. The n-channel transistors and p-channel transistors are the duals of each other; that is, the voltage polarities required for correct operation are the opposite. The threshold voltages for n-channel and p-channel devices are denoted by  $V_{tn}$  and  $V_{tp}$ , respectively.

FIGURE 2.2 Conduction characteristics for enhancement and depletion mode MOS transistors (assuming fixed  $V_{ds}$ )

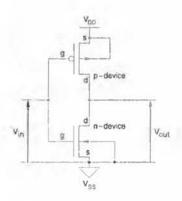

In CMOS technologies both n-channel and p-channel transistors are fabricated on the same chip. Furthermore, most CMOS integrated circuits, at present, use transistors of the enhancement type.

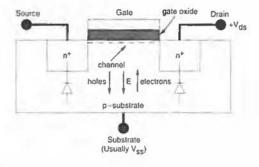

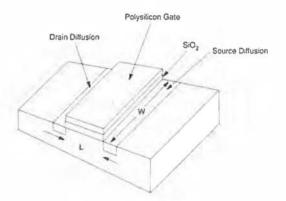

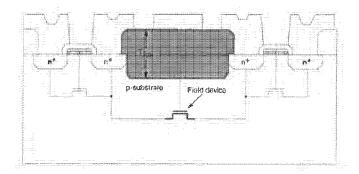

#### 2.1.1 nMOS Enhancement Transistor

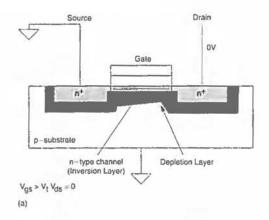

The structure for an n-channel enhancement-type transistor, shown in Fig. 2.3, consists of a moderately doped p-type silicon substrate into which two heavily doped  $n^+$  regions, the *source* and the *drain*, are diffused. Between these two regions there is a narrow region of p-type substrate called the *channel*, which is covered by a thin insulating layer of silicon dioxide (SiO<sub>2</sub>) called *gate oxide*. Over this oxide layer is a polycrystalline silicon (polysilicon) electrode, referred to as the *gate*. Polycrystalline silicon is silicon that is not composed of a single crystal. Since the oxide layer is an insulator, the DC current from the gate to channel is essentially zero. Because of the inherent symmetry of the structure, there is no physical distinction between the drain and source regions. Since SiO<sub>2</sub> has relatively low loss and high dielectric strength, the application of high gate fields is feasible.

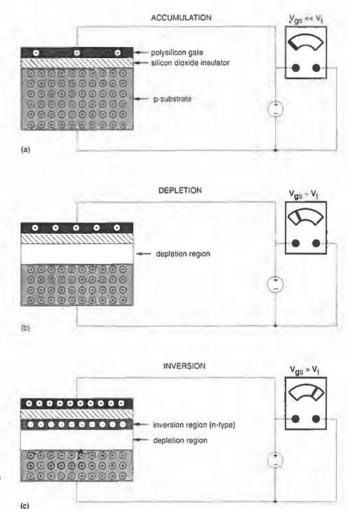

In operation, a positive voltage is applied between the source and the drain  $(V_{ds})$ . With zero gate bias  $(V_{gs}=0)$ , no current flows from source to drain because they are effectively insulated from each other by the two reversed biased pn junctions shown in Fig. 2.3 (indicated by the diode symbols). However, a voltage applied to the gate, which is positive with respect to the source and the substrate, produces an electric field E across the substrate, which attracts electrons toward the gate and repels holes. If the gate voltage is sufficiently large, the region under the gate changes from p-type to n-type (due to accumulation of attracted electrons) and provides a conduction path between the source and the drain. Under such a condition, the surface of the underlying p-type silicon is said to be *inverted*. The term *n-channel* is applied to the structure. This concept is further illustrated by Fig. 2.4(a), which shows the initial distribution of mobile positive holes in a p-type silicon substrate of an MOS structure for a voltage,  $V_{gs}$ , much less than a voltage,  $V_{f}$ , which is

FIGURE 2.3 Physical structure of an nMOS transistor

#### 44 CHAPTER 2 MOS TRANSISTOR THEORY

FIGURE 2.4 Accumulation, Depletion and Inversion modes in an MOS structure.

the threshold voltage. This is termed the accumulation mode. As  $V_{gs}$  is raised above  $V_t$  in potential, the holes are repelled causing a depletion region under the gate. Now the structure is in the depletion mode (Fig. 2.4b). Raising  $V_{gs}$  further above  $V_t$  results in electrons being attracted to the region of the substrate under the gate. A conductive layer of electrons in the p substrate gives rise to the name inversion mode (Fig. 2.4c).

The difference between a pn junction that exists in a bipolar transistor or diode (or between the source or drain and substrate) and the inversion layer

substrate junction is that in the pn junction, the n-type conductivity is brought about by a metallurgical process; that is, the electrons are introduced into the semiconductor by the introduction of donor ions. In an inversion layer substrate junction, the n-type layer is induced by the electric field E applied to the gate. Thus, this junction, instead of being a metallurgical junction, is a field-induced junction.

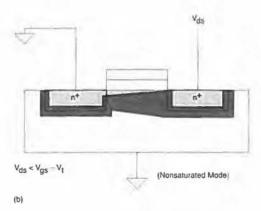

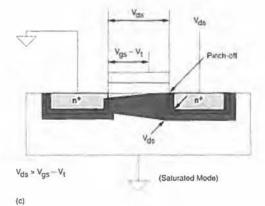

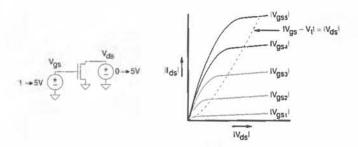

Electrically, an MOS device therefore acts as a voltage-controlled switch that conducts initially when the gate-to-source voltage,  $V_{ys}$ , is equal to the threshold voltage,  $V_t$ . When a voltage  $V_{ds}$  is applied between source and drain, with  $V_{gs} = V_f$ , the horizontal and vertical components of the electrical field due to the source-drain voltage and gate-to-substrate voltage interact, causing conduction to occur along the channel. The horizontal component of the electric field associated with the drain-to-source voltage (i.e.,  $V_{ds} > 0$ ) is responsible for sweeping the electrons in the channel from the source toward the drain. As the voltage from drain to source is increased, the resistive drop along the channel begins to change the shape of the channel characteristic. This behavior is shown in Fig. 2.5. At the source end of the channel, the full gate voltage is effective in inverting the channel. However, at the drain end of the channel, only the difference between the gate and drain voltages is effective. When the effective gate voltage  $(V_{ys} - V_t)$  is greater than the drain voltage, the channel becomes deeper as  $V_{es}$  is increased. This is termed the "linear," "resistive," "nonsaturated," or "unsaturated" region, where the channel current  $I_{ds}$  is a function of both gate and drain voltages. If  $V_{ds} > V_{gs} - V_t$ , then  $V_{gd} < V_t$  ( $V_{gd}$  is the gate to drain voltage), and the channel becomes pinched off—the channel no longer reaches the drain. This is illustrated in Fig. 2.5(c). However, in this case, conduction is brought about by a drift mechanism of electrons under the influence of the positive drain voltage. As the electrons leave the channel, they are injected into the drain depletion region and are subsequently accelerated toward the drain. The voltage across the pinched-off channel tends to remain fixed at  $(V_{ps} - V_I)$ . This condition is the "saturated" state in which the channel current is controlled by the gate voltage and is almost independent of the drain voltage. For fixed drain-to-source voltage and fixed gate voltage, the factors that influence the level of drain current,  $I_{ds}$ , flowing between source and drain (for a given substrate resistivity) are:

- · the distance between source and drain

- · the channel width

- the threshold voltage V<sub>I</sub>

- · the thickness of the gate-insulating oxide layer

- · the dielectric constant of the gate insulator

- the carrier (electron or hole) mobility, μ.

#### 46 CHAPTER 2 MOS TRANSISTOR THEORY

FIGURE 2.5 nMOS device behavior under the influence of different terminal voltages

The normal conduction characteristics of an MOS transistor can be categorized as follows:

- "Cut-off" region: where the current flow is essentially zero (accumulation region).

- "Nonsaturated" region: weak inversion region where the drain current is dependent on the gate and the drain voltage (with respect to the substrate).

- "Saturated" region: channel is strongly inverted and the drain current flow is ideally independent of the drain-source voltage (strong inversion region).

An abnormal conduction condition called avalanche breakdown or punch-through can occur if very high voltages are applied to the drain. Under these circumstances, the gate has no control over the drain current.

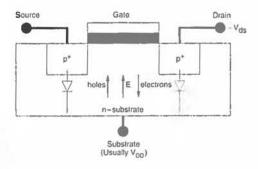

#### 2.1.2 pMOS Enhancement Transistor

So far, our discussions have been primarily directed toward nMOS; however, a reversal of n-type and p-type regions yields a p-channel MOS transistor. This is illustrated by Fig. 2.6. Application of a negative gate voltage (w.r.t. source) draws holes into the region below the gate, resulting in the channel changing from n-type to p-type. Thus, similar to nMOS, a conduction path is created between the source and the drain. In this instance, however, conduction results from the movement of holes (versus electrons) in the channel. A negative drain voltage sweeps holes from the source through the channel to the drain.

#### 2.1.3 Threshold Voltage

The threshold voltage,  $V_t$ , for an MOS transistor can be defined as the voltage applied between the gate and the source of an MOS device below which the drain-to-source current  $I_{ds}$  effectively drops to zero. The word "effectively drops" to zero.

FIGURE 2.6 Physical structure of a pMOS transistor

tively" is used because the drain current never really is zero but drops to a very small value that may be deemed insignificant for the current application (i.e., fast digital CMOS circuits). In general, the threshold voltage is a function of a number of parameters including the following:

- · Gate conductor material.

- · Gate insulation material.

- · Gate insulator thickness-channel doping.

- · Impurities at the silicon-insulator interface.

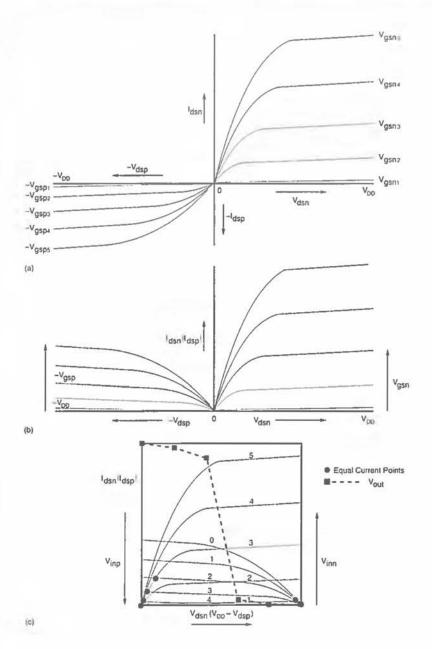

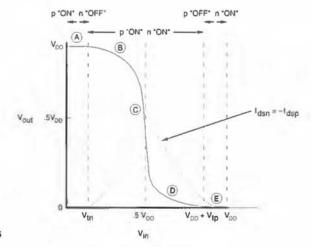

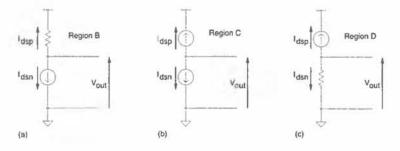

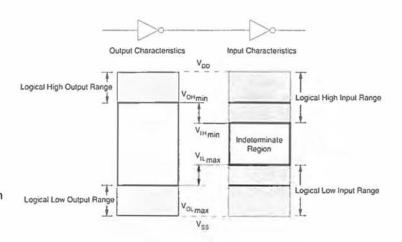

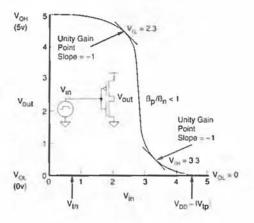

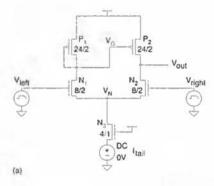

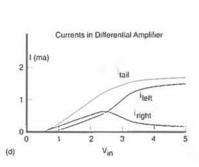

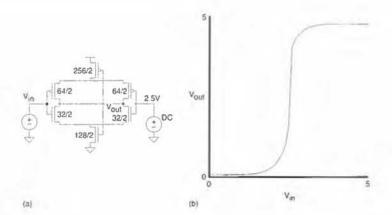

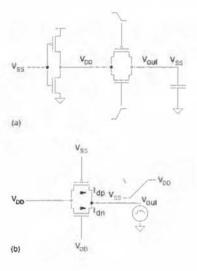

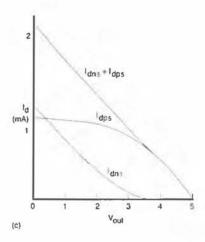

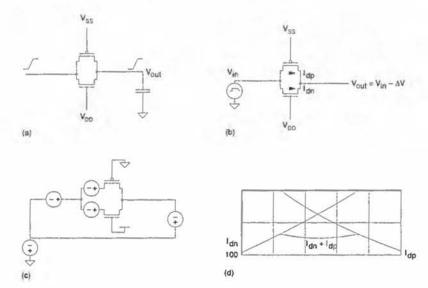

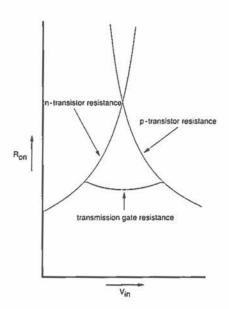

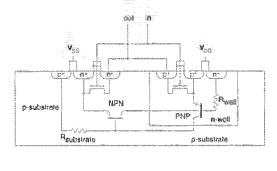

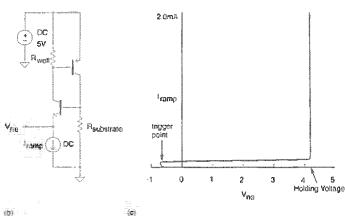

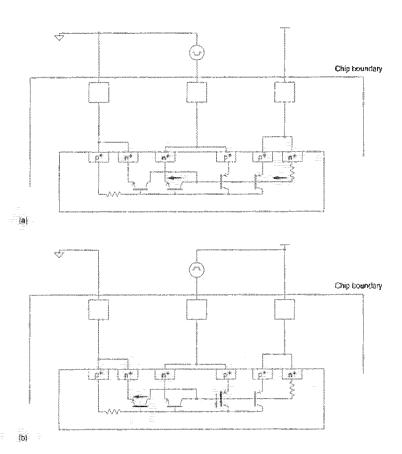

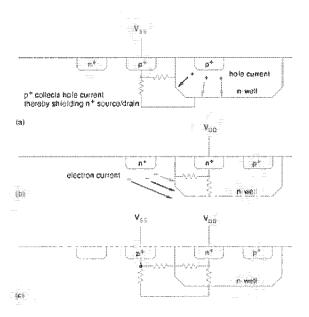

- Voltage between the source and the substrate, V<sub>sb</sub>.