# PETITIONER'S DEMONSTRATIVE EXHIBIT 1016

# Advanced Micro Devices, Inc. et al. v. Monterey Research LLC

Petitioners' Presentation For IPR2020-00985 U.S. Patent No. 6,651,134 September 1, 2021

Demonstrative Exhibit 1016, 0001

# **Overview**

- Alleged Invention

- "Non-Interruptible" Limitation

- **-**Wada

- -Wada + Barrett

- Patent Owner Fails To Distinguish Prior Art

- "Predetermined Number" Limitation

- No Objective Indicia of Non-Obviousness

# **Overview**

## Alleged Invention

• "Non-Interruptible" Limitation

**-**Wada

-Wada + Barrett

- Patent Owner Fails To Distinguish Prior Art

• "Predetermined Number" Limitation

• No Objective Indicia of Non-Obviousness

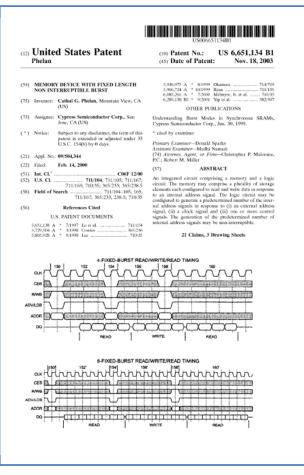

#### '134 Patent – Non-Interruptible Burst Memory

| (12) United States Patent<br>Phelan                                                                                            | (10) Patent No.: US 6,651,134 B1<br>(45) Date of Patent: Nov. 18, 2003                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (54) MEMORY DEVICE WITH FIXED LENGTH<br>NON INTERRUPTIBLE BURST                                                                | 5.936,975 A * 8/1999 Okanaora                                                                                                                                                                                                                |

| (75) Inventor: Cathal G. Phelan, Mountain View, CA<br>(US)                                                                     | 6,289,138 B1 * 9/2001 Yip et al                                                                                                                                                                                                              |

| (73) Assignce: Cypress Semiconductor Corp., San<br>Jose, CA (US)                                                               | Understanding Burst Modes in Synchronous SRAMs<br>Cypress Semiconductor Corp., Jun. 30, 1999.                                                                                                                                                |

| (*) Notice: Subject to any disclaimer, the term of this<br>patent is extended or adjusted under 35<br>U.S.C. 154(b) by 0 days. | * cited by examiner<br>Prinury Examiner—Dotald Sparfes<br>Assistant Examiner—Mellii Namazi<br>(24) Attornes, Agent, or Firm—Christopher P. Maiceant                                                                                          |

| (21) Appl. No.: 09/504,344                                                                                                     | P.C.; Robert M. Miller                                                                                                                                                                                                                       |

| (22) Filed: Feb. 14, 2000                                                                                                      | (57) ABSTRACT                                                                                                                                                                                                                                |

| (51) Int. CL <sup>7</sup>                                                                                                      | An integrated circuit comprising a memory and a logi                                                                                                                                                                                         |

| (52) U.S. CL                                                                                                                   | circuit. The memory may comprise a plurality of storag<br>elements each configured to read and write data in respons<br>to an internal address signal. The logic circuit may b<br>configured to generate a predetermined number of the intel |

| (56) References Cited                                                                                                          | nal address signals in response to (i) an external address<br>signal, (ii) a clock signal and (iii) one or more control                                                                                                                      |

| U.S. PATENT DOCUMENTS                                                                                                          | signals. The generation of the predetermined number of                                                                                                                                                                                       |

| \$,651,138         *         7/1997         Le et al.                                                                          | internal address signals may be non-interruptible.<br>21 Claims, 3 Drawing Sheets                                                                                                                                                            |

| ADVALDB<br>200<br>                                                                                                             |                                                                                                                                                                                                                                              |

|                                                                                                                                |                                                                                                                                                                                                                                              |

- 1. A circuit comprising:

- a memory comprising a plurality of storage elements each configured to read and write data in response to an internal address signal; and

- a logic circuit configured to generate a predetermined number of said internal address signals in response to (i) an external address signal, (ii) a clock signal and (iii) one or more control signals, wherein said generation of said predetermined number of internal address signals is non-interruptible.

'134 Patent (Ex-1001) at Cover, claim 1

## **Grounds Presented In Petition**

| Ground | Prior Art and Claims                                            |  |

|--------|-----------------------------------------------------------------|--|

| 1      | Wada anticipates claims 1-3, 8, 12-13, 16, and 17               |  |

| 2      | Wada renders obvious claims 1-4, 8, 12-14, 16, and 17           |  |

| 2a     | Wada + Barrett renders obvious claims 1-4, 8, 12-14, 16, and 17 |  |

| 3      | Wada + Fujioka renders obvious claims 4-7 and 18-20             |  |

| 3a     | Wada + Barrett + Fujioka renders obvious claims 4-7 and 18-20   |  |

| 4      | Wada + Reeves renders obvious claims 9-10, 14, and 21           |  |

| 4a     | Wada + Barrett + Reeves renders obvious claims 9-10, 14, and 21 |  |

| 5      | Wada + Lysinger renders obvious claims 11 and 15                |  |

| 5a     | Wada + Barrett + Lysinger renders obvious claims 11 and 15      |  |

Petition (Paper 1) at 5

# **Overview**

- Alleged Invention

- "Non-Interruptible" Limitation

- **-**Wada

- -Wada + Barrett

- Patent Owner Fails To Distinguish Prior Art

- "Predetermined Number" Limitation

- No Objective Indicia of Non-Obviousness

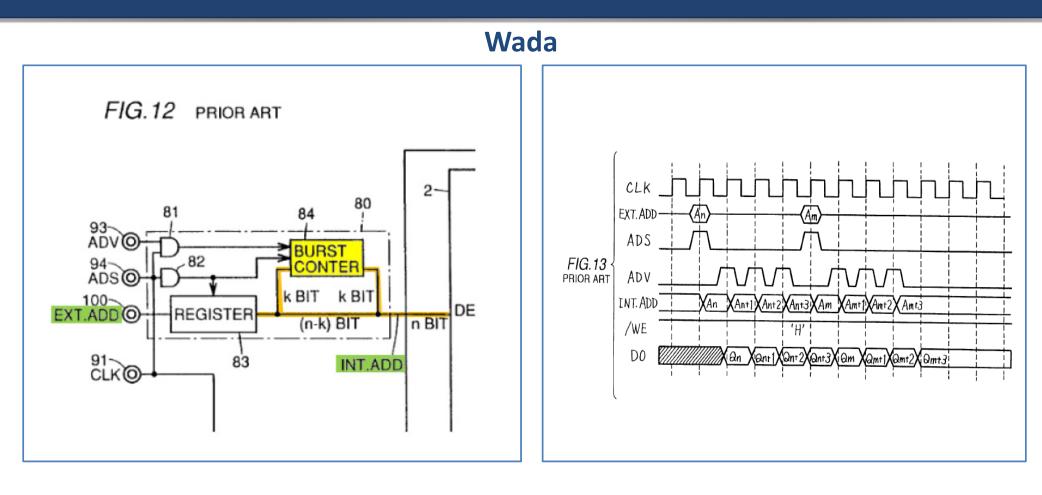

## U.S. 6,115,280 ("Wada")

|              |                           | l                                                                                                      |                       |                         | USC                        | 06115280A                     |                                                     |

|--------------|---------------------------|--------------------------------------------------------------------------------------------------------|-----------------------|-------------------------|----------------------------|-------------------------------|-----------------------------------------------------|

| Un           | ited S                    | States Patent [19]                                                                                     | [11]                  | Pa                      |                            | umber:                        | 6,115,280                                           |

| Wae          | la                        |                                                                                                        | [45]                  | Da                      | ate of I                   | Patent:                       | *Sep. 5, 2000                                       |

| [54]         |                           | NDUCTOR MEMORY CAPABLE OF<br>PPERATION                                                                 | 5,46                  | 0,529<br>3,591<br>5,172 | 10/1995                    | Aimoto et al                  | 365/78 X<br>                                        |

| [75]         | Inventor:                 | Tomohisa Wada, Hyogo, Japan                                                                            | 5,56                  | 1,633                   | 10/1996                    | Yamano                        |                                                     |

| [73]         | Assignee:                 | Mitsubishi Denki Kabushiki Kaisha,                                                                     |                       |                         |                            | PATENT DOG                    | UMENTS                                              |

| [*]          | Notice:                   | Tokyo, Japan                                                                                           | 3.7                   | 8386<br>6094<br>4791    | 3/1991<br>4/1991<br>7/1992 | Japan .<br>Japan .<br>Japan . |                                                     |

| 1.1          | Nonce:                    | This patent issued on a continued pros-<br>ecution application filed under 37 CFR                      |                       | 4259                    | 6/1993                     | Japan .                       |                                                     |

|              |                           | <ol> <li>1.53(d), and is subject to the twenty year<br/>patent term provisions of 35 U.S.C.</li> </ol> |                       |                         |                            | R PUBLICAT                    |                                                     |

|              |                           | 154(a)(2).                                                                                             | "IBM Pr<br>6, 1994,   |                         |                            | SRAM Entries                  | ," Electric News, Jun.                              |

| [21]         | Appl. No.                 | 08/833,178                                                                                             | Child, "              | RISC                    | and Pent                   |                               | nand for SRAMs that                                 |

| [22]         | Filed:                    | Apr. 4, 1997                                                                                           | 47-48.                | SU OF U                 | ne tasi, x                 | .omputer Des                  | ign, Mar. 28, 1994, pp.                             |

|              |                           | ated U.S. Application Data                                                                             |                       |                         |                            | Zarabian<br>m—McDermo         | tt, Will & Emery                                    |

| [63]         | Continuatio<br>abandoned. | n of application No. 08/547,341, Oct. 24, 1995,                                                        | [57]                  |                         |                            | ABSTRACT                      |                                                     |

| [30]         | Fore                      | gn Application Priority Data                                                                           | A semie               | onduc                   | tor memo                   | ry for operati                | ng in burst mode. The                               |

| No           | s. 1, 1994                | [JP] Japan 6-268925                                                                                    | memory                | block                   | cs, a plura                | lity of (e.g., 2              | ided into a plurality of<br>) output registers each |

| [51]<br>[52] |                           |                                                                                                        |                       |                         |                            |                               | etaining blocks corre-<br>ks, and a burst counter   |

|              |                           | 365/230.03                                                                                             | unit. The             | outp                    | ut register                | is alternately r              | eceive data transferred<br>lance with the result of |

| [58]         | Field of S                | earch                                                                                                  | counting              | by t                    | he burst e                 | ounter unit, th               | se data retained in the                             |

| [56]         |                           | References Cited                                                                                       |                       |                         |                            |                               | in bursts, whereby the<br>e memory is boosted       |

| 10.01        | U.                        | S. PATENT DOCUMENTS                                                                                    | regardles<br>therein. | ss of                   | the operation              | ting speed of                 | the memory cell array                               |

|              | ,899,310 2                | 2/1990 Baba et al                                                                                      |                       |                         |                            |                               |                                                     |

| 5            | ,200,925 4                | /1993 Morooka                                                                                          |                       |                         | 12 Claim                   | s, 16 Drawin                  | g Sheets                                            |

|              |                           |                                                                                                        | 11 BIT LINE P         | яесн                    | ARGING                     | а                             |                                                     |

|              |                           | 2                                                                                                      |                       | T                       | TL                         |                               |                                                     |

|              |                           | 20                                                                                                     | -                     |                         |                            |                               |                                                     |

|              |                           | MADD Q                                                                                                 | <u>M0</u> <u>M1</u>   | M                       | MB                         |                               |                                                     |

|              |                           | DOATH <sup>de</sup>                                                                                    |                       | 1111                    |                            |                               |                                                     |

|              |                           | L                                                                                                      | 7 <del>7</del> -      | ÷                       | ÷-                         | 41                            |                                                     |

|              |                           |                                                                                                        | 7299T.C               | 2280 г.                 | 72917 73817                |                               |                                                     |

|              |                           | 72                                                                                                     | 1 1                   | 1                       |                            |                               |                                                     |

|              |                           | 71                                                                                                     |                       |                         | 2 49                       | 54                            |                                                     |

|              |                           |                                                                                                        | B0 B1                 | B2                      |                            | 58.                           |                                                     |

|              |                           |                                                                                                        |                       |                         | 1.1                        |                               |                                                     |

|              |                           | 91 SELA.SELB                                                                                           | 60 / 61 / L           | 바막                      | x MUX                      |                               |                                                     |

|              |                           | SELA,SELB                                                                                              |                       | MUX                     | 5-7                        |                               |                                                     |

|              |                           | EXT.CHA                                                                                                | R INT.CHA             |                         |                            |                               |                                                     |

|              |                           | ADV 0 -94<br>ADS 0 -94                                                                                 |                       | \$-                     | 9                          |                               |                                                     |

|              |                           | à                                                                                                      | _                     | 00                      |                            |                               |                                                     |

|              |                           |                                                                                                        |                       |                         |                            |                               |                                                     |

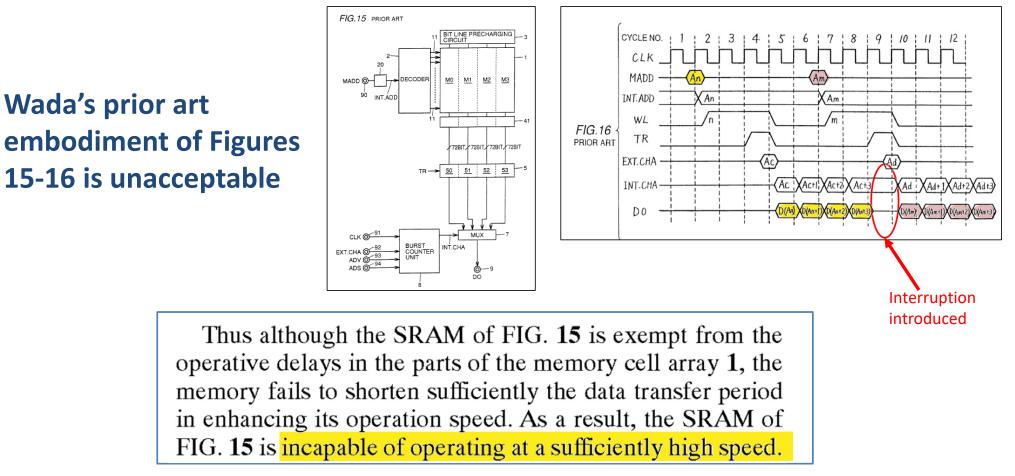

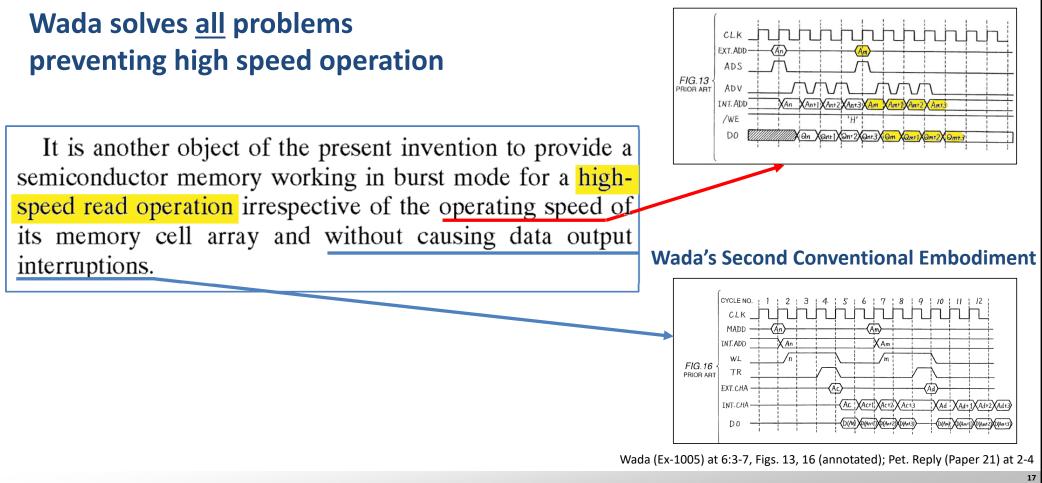

It is another object of the present invention to provide a semiconductor memory working in burst mode for a highspeed read operation irrespective of the operating speed of its memory cell array and without causing data output interruptions.

three or more output registers. This constitution provides one advantage identical to that of the first embodiment, i.e., the ability to execute data burst output in uninterrupted fashion.

Wada (Ex-1005) at 6:3-8, 16:12-15; Petition (Paper 1) at 23, 47; Pet. Reply (Paper 21) at 4

Demonstrative Exhibit 1016, 0007

#### An Interruption Anywhere Defeats Wada's Goals

Wada (Ex-1005) at 5:59-63, Figs. 15, 16; Pet. Reply (Paper 21) at 2-4

Demonstrative Exhibit 1016, 0008

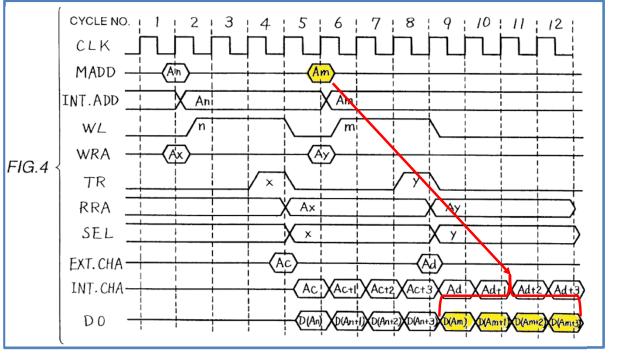

#### Wada's Bursts Are Not Interruptible

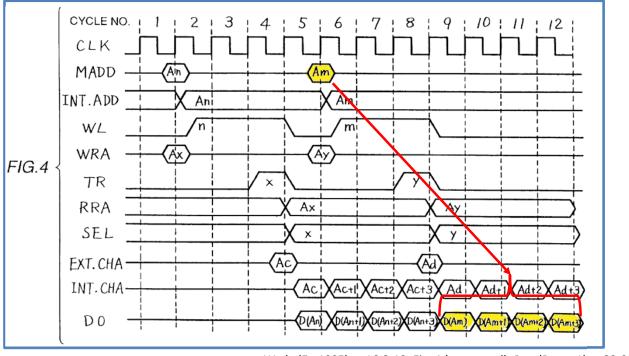

Wada's second embodiment (Figs. 3-4) eliminates interruptions in burst addresses generated corresponding to external address Am. described actions are carried out continuously. This allows the data corresponding to the address Am to be output uninterrupted in burst mode.

Wada (Ex-1005) at 16:8-10, Fig. 4; Pet. (Paper 1) at 22-23; Pet. Reply (Paper 21) at 5.

#### **Patent Owner's Expert Agrees**

Patent Owner's expert agrees "data corresponding to the address Am" is one burst. described actions are carried out continuously. This allows the data corresponding to the address Am to be output uninterrupted in burst mode.

Wada at 16:8-10

10

Q. And so the D(Am) to D(Am+3), that's one burst that corresponds to address Am; is that correct?

• • •

A. In this case, if the signals are maintained to not interrupt a burst in this embodiment of Wada, then those four transactions Dm—I'm sorry, D(Am) onward *would be the burst for the address Am* in clock cycle 6.

Brogioli Dep. at 211:23-212:7 (emphasis added)

Wada (Ex-1005) at 16:8-10; Brogioli Dep. (Ex-1015) at 211:23-212:7; Pet. Reply (Paper 21) at 5

#### **Board Concurrence Recognized Wada's Overall Goal**

Institution Decision, APJ Horvath, concurring Although I agree with the majority that Wada's primary concern is eliminating data output interruptions *between* bursts, I disagree that a person skilled in the art would not read Wada to also teach or suggest eliminating data output interruptions *within* bursts. Indeed, an express object of Wada's invention is a memory circuit that operates in burst mode "without causing data output interruptions," not to operate in burst mode without causing data output interruptions only *between* bursts. Ex. 1005, 6:3–8. As shown in

uninterrupted in burst mode." Id. at 16:7–10. That is, Wada teaches its Second Embodiment has not only eliminated data output interruptions *between* bursts, but should be operated in a manner having no data output interruptions *within* bursts. *Id.*, Fig. 4.

Institution Decision (APJ. Horvath, concurring) (Paper 13) at 28.

## U.S. 5,584,033 ("Barrett")

#### United States Patent [19]

#### Barrett et al.

- [54] APPARATUS AND METHOD FOR BURST DATA TRANSFER EMPLOYING A PAUSE AT FIXED DATA INTERVALS

- [75] Inventors: Wayne M. Barrett, Rochester; Bruce L. Beukema, Hayfield; William E. Hammer; Daniel F. Moertl, both of Rochester, all of Minn.

- [73] Assignce: International Business Machines Corporation, Armonk, N.Y.

- [21] Appl. No.: 335,228

- [22] Filed: Nov. 7, 1994

#### Related U.S. Application Data

| [63] | Continuation of Ser. No. 760,426, Sep. 16, 1991, abando | ned  |

|------|---------------------------------------------------------|------|

| [51] | Int. Cl.6                                               | 5/28 |

| [52] | U.S. Cl                                                 | 1.5  |

|      | 364/260.1; 364/DIG. 1; 395/                             |      |

| [58] | Field of Search 395/800,                                | 868  |

#### [56] References Cited

| U.S | . PATENT | DOCUMENTS |

|-----|----------|-----------|

|     |          |           |

| Rc.34,282 | 6/1993  | Suzuki                   |

|-----------|---------|--------------------------|

| 4,275,440 | 6/1981  | Adams                    |

| 4,558,429 | 12/1985 | Barlow                   |

| 4,644,463 | 2/1987  | Hotchkin 395/250         |

| 4,703,478 | 10/1987 | Haselton 370/94          |

| 4,712,176 | 12/1987 | Fredericks et al 364/200 |

| 4,799,199 | 1/1989  | Scales, III et al        |

| 4,807,109 | 2/1989  | Farrell et al 364/200    |

| 4,816,947 | 3/1989  | Scales                   |

| 5,029,124 | 7/1991  | Leahy et al              |

| 5,073,969 | 12/1991 | Shoemaker 395/307        |

| 5,140,680 | 8/1992  | Best                     |

| [45] I      | Date of Patent:                                           | Dec. 10, 1996        |

|-------------|-----------------------------------------------------------|----------------------|

|             | 2 10/1992 Salmon                                          |                      |

| 5,276,81    | 8 1/1994 Okazawa                                          |                      |

|             | OTHER PUBLICA                                             | TIONS                |

|             | cal Disclosure Bulletin<br>434 "Swinging Buffer           |                      |

| Attorney, A | aminer-Eric Coleman<br>gent, or Firm-Roy V<br>runa Ojanen | W. Truelson; Owen J. |

| [57]        | ABSTRACT                                                  |                      |

5,584,033

Patent Number:

#### ABSTRACT

A plurality of devices attached to a communications bus observe a burst transfer protocol which allows pausing only at pre-determined, fixed intervals of n data words, where a word is the width of the bus. In accordance with this protocol, once burst transfer is initialized the sending device transmits an uninterrupted stream of n data words over the communications bus, after which either the sender or receiver may cause transmission to pause. The sender may need to wait for more data, or the receiver may need to finish processing the data just received. The pause lasts as long as needed until both devices are ready to proceed. This cycle is repeated until the data transmission is complete. The sending and receiving devices do not relinquish control of the bus during a nause, and therefore are not required to re-initialize communications. In the preferred embediment, after n data words have been transmitted, the sender and receiver toggle interlocking signals that accomplish a handshaking between the two devices. The sender de-activates its signal when it is ready to send more, and the receiver de-activates its signal when it is ready to receive more. Both devices are equipped with buffers large enough to hold n data words, but the buffers need not be as large as the longest possible burst

#### 30 Claims, 5 Drawing Sheets

The essential feature of burst communication is that the data transfer takes place at high speed and without interruption. This feature places certain constraints on the design of

devices to handle the pauses. In effect, allowing a pause at any point defeats the purpose of burst transmission, which is to send data a rapidly as possible in an uninterrupted stream.

Barrett (Ex-1010) at 1:64-67, 2:39-41; Petition (Paper 1) at 50-51, Pet. Reply (Paper 21) at 17

12

Demonstrative Exhibit 1016, 0012

#### **Board Agreed Wada + Barrett Teaches Non-Interruptible Burst**

#### **Institution Decision**

We conclude that, in light of Barrett's teaching that "allowing a pause at any point defeats the purpose of burst transmission, which is to send data a[s] rapidly as possible in an uninterrupted stream" (Ex. 1010, 2:39–41), skilled artisans had reason to modify Wada's conventional embodiment or Second Embodiment to remove the ability to interrupt burst-generation via external signals. Thus, the modified conventional embodiment and Second Embodiment would generate internal address or internal chunk addresses, respectively, such that their generation "cannot be stopped or terminated once initiated until the fixed number of internal addresses has been generated." *See* Pet. 12 (claim construction).

Institution Decision (Paper 13) at 21

# **Overview**

- Alleged Invention

- "Non-Interruptible" Limitation

- **-**Wada

- -Wada + Barrett

- Patent Owner Fails To Distinguish Prior Art

- "Predetermined Number" Limitation

- No Objective Indicia of Non-Obviousness

#### **Patent Owner Fails To Distinguish Prior Art**

- Wada's teachings not limited to eliminating interruptions only *between* bursts

- Wada's control signals make it no more "interruptible" than those of the '134 Patent

- Wada and Barrett are not directed to opposing goals

Pet. Reply (Paper 21) at 2-3, 8-12, 17; Petition (Paper 1) at 8, 51-53

#### **Patent Owner Fails To Distinguish Prior Art**

# Wada's teachings not limited to eliminating interruptions only *between* bursts

- Wada's control signals make it no more "interruptible" than those of the '134 Patent

- Wada and Barrett are not directed to opposing goals

Pet. Reply (Paper 21) at 2-3, 8-12, 17; Petition (Paper 1) at 8, 51-53

#### Wada Eliminates Interruptions Between And Within Bursts

#### Wada's First Conventional Embodiment

Demonstrative Exhibit 1016, 0017

#### Wada Eliminates Interruptions Between And Within Bursts

Wada's second embodiment expressly teaches eliminating interruptions in the burst addresses corresponding to external address Am. described actions are carried out continuously. This allows the data corresponding to the address Am to be output uninterrupted in burst mode.

Wada (Ex-1005) at 16:8-10, Fig. 4 (annotated); Pet. (Paper 1) at 22-23

#### **Patent Owner Fails To Distinguish Prior Art**

- Wada's teachings not limited to eliminating interruptions only *between* bursts

- Wada's control signals make it no more "interruptible" than those of the '134 Patent

- Wada and Barrett are not directed to opposing goals

Pet. Reply (Paper 21) at 2-3, 8-12, 17; Petition (Paper 1) at 8, 51-53

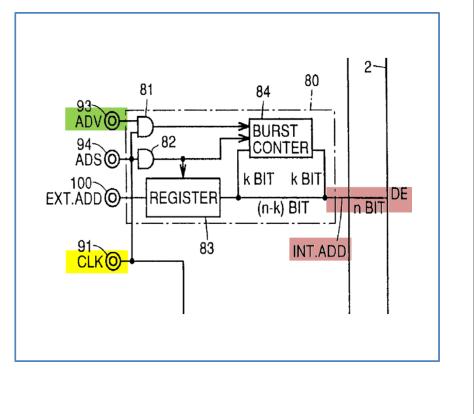

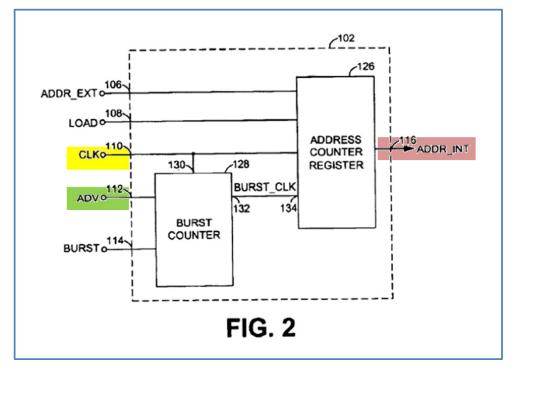

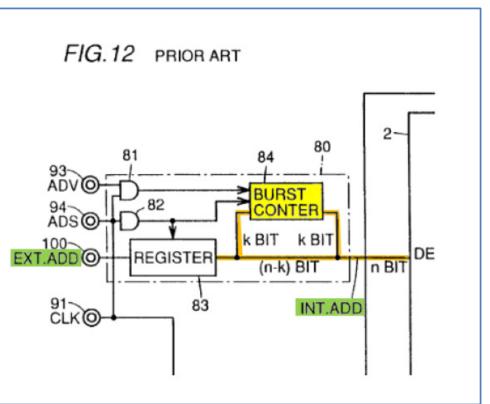

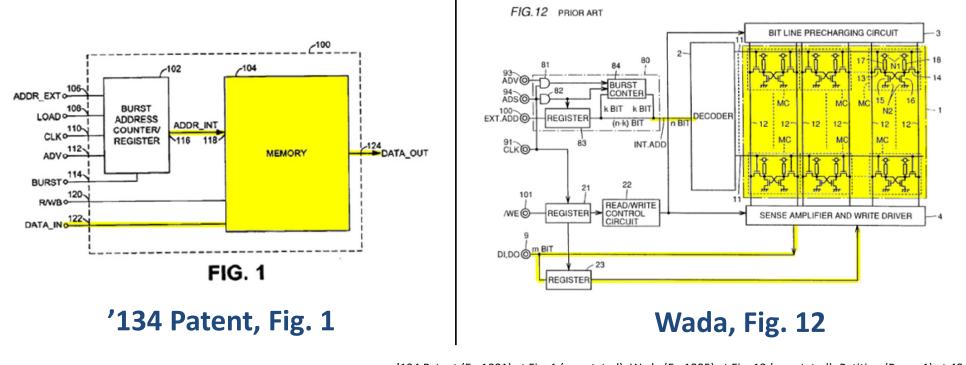

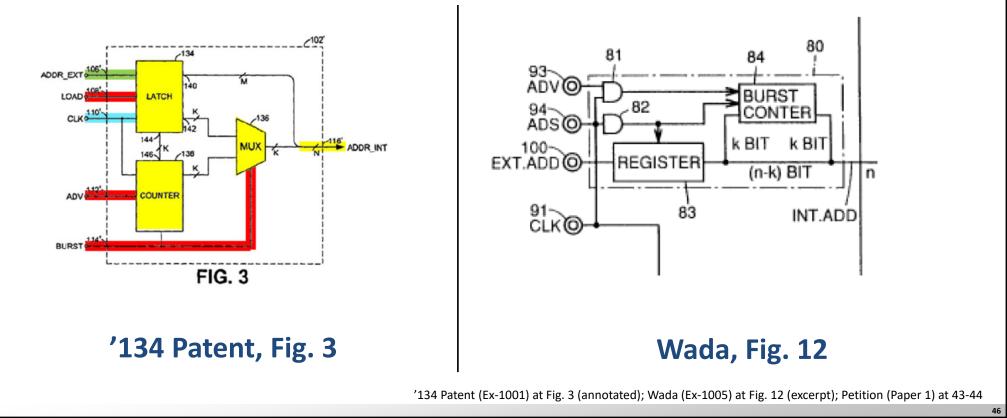

#### Wada, Fig. 12 (excerpt)

#### '134 Patent, Fig. 2

Wada (Ex-1005) at Fig. 12 (annotated); '134 Patent (Ex-1001) at Fig. 2 (annotated); Pet. Reply (Paper 21) at 8-9; Petition (Paper 1) at 8

The signals ADV and LOAD may be, in one example, a single signal (e.g., ADV/LDb). The signal ADV/LDb may be a control signal that may be in a first state or a second state. When the signal ADV/LDb is in the first state, the circuit 102 will generally load an address presented by the signal ADDR\_EXT as an initial address. When the signal ADV/LDb is in the second state, the circuit 102 may be configured to generate the signal ADDR\_INT as a fixed number of addresses in response to the signal CLK. The

#### When '134 Patent's ADV/LDB signal goes low, next burst is generated

#### Patent Owner's expert agrees that ADV low starts the burst over:

Q. So if the bursts started and the signal ADV/LDb were driven to the first state, wouldn't that load in a new starting address?

A. Let me reread the paragraph. I don't know that that paragraph explicitly states that. It says in that when the signal ADV/LDb is in a first state, the circuit will generally load an address presented by the ADDR\_EXT as an initial address. And then the second state happens for ADV/LDb and then you have a non-interruptible burst. I don't know that it says -- *I guess at some point, down the road if you replace or you reset ADV/LDb back to the first state, you would -- you know, I think that would be part of starting the process over, for example.*

Brogioli Dep. (Ex-1015) at 116:6-24 (emphasis added); Pet. Reply (Paper 21) at 11-12

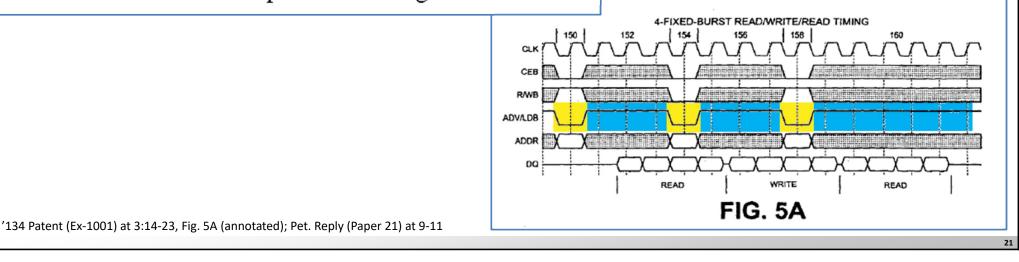

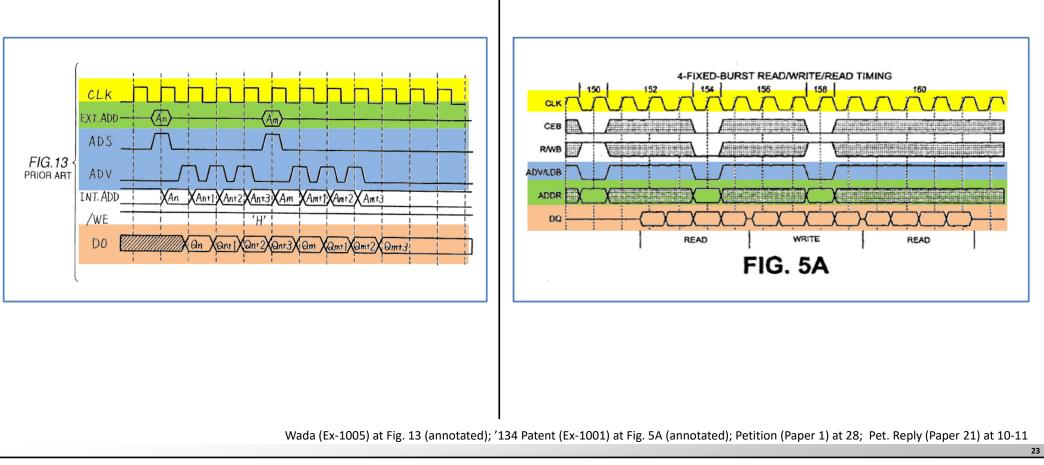

Wada, Fig. 13

#### '134 Patent, Fig. 5A

#### **Patent Owner Fails To Distinguish Prior Art**

- Wada's teachings not limited to eliminating interruptions only *between* bursts

- •Wada's control signals make it no more "interruptible" than those of the '134 Patent

- Wada and Barrett are not directed to opposing goals

Pet. Reply (Paper 21) at 2-3, 8-12, 17; Petition (Paper 1) at 8, 51-53

#### Wada and Barrett's Goals Not Opposed

#### Barrett and Wada are in similar fields:

<u>Wada</u>

"[T]he present invention [] provide[s] semiconductor memory working in burst mode for a high-speed read operation..." Wada at 6:3-7. **Barrett**

"multiple CPUs and memory units communicating with other units via system I/O bus..." Barrett at 4:46-48

#### Barrett and Wada share goal of high-speed uninterrupted burst data transfer:

<u>Wada</u>

"allows the data corresponding to address Am to be output uninterrupted in burst mode." Wada at 16:8-10

"a semiconductor memory operating in burst mode at a sufficiently high speed irrespective of the operating speed of its memory cell array." Wada at 5:67-6:2.

#### <u>Barrett</u>

"a burst data transmission comprised of a plurality of uninterruptible streams of n data transfer cycles." Barrett at claim 1.

"allowing a pause at any point defeats the purpose of burst transmission, which is to send data as rapidly as possible in an uninterrupted stream." Barrett at 2:39-41.

25

Wada (Ex-1005) at 5:67-6:7, 16:8-10; Barrett (Ex-1010) at 2:39-41, 4:46-48, claim 1; Petition (Paper 1) at 51-52; Pet. Reply (Paper 21) at 17

#### Wada and Barrett's Goals Not Opposed

#### **Patent Owner argues:**

Instead, AMD ignores the complication of changing the control circuitry that sets or resets the ADV signal and also ignores the consequences of its proposed modification, e.g., how to handle overflows of data when the burst output produces more data than can be consumed by the receiving device.

Barrett, on the other hand, is explicitly directed towards ensuring pauses in between burst data transfers between I/O devices within a computing system precisely the opposite of Wada's goal. *See, e.g.*, Ex-1010, Abstract, 3:12-22; Ex-

P.O. Sur-Reply (Paper 22) at 13-14

#### Wada And Barrett Do Not Defeat Each Other's Goals

#### Barrett

Because the sending device transmits an uninterrupted stream of n data transfer cycles, it can guarantee that sufficient space will be available in its buffer for the next data transfer cycles stream within a specific time period. As a result, it can overlap the action of obtaining more data (refilling the buffer) with the action of transmitting the current data (emptying the buffer). Furthermore, allowing pauses only at specific intervals simplifies the bus interface circuitry because the number of potential cases (or scenarios) involving pauses is drastically reduced.

Barrett (Ex-1010) at 3:52-61; Pet Rep. (Paper 21) at 19

# **Overview**

- Alleged Invention

- "Non-Interruptible" Limitation

- **-**Wada

- -Wada + Barrett

- Patent Owner Fails To Distinguish Prior Art

- "Predetermined Number" Limitation

- No Objective Indicia of Non-Obviousness

#### '134 Patent

#### 1. A circuit comprising:

a memory comprising a plurality of storage elements each configured to read and write data in response to an internal address signal; and

a logic circuit configured to generate a predetermined number of said internal address signals in response to (i) an external address signal, (ii) a clock signal and (iii) one or more control signals, wherein said generation of said predetermined number of internal address signals is non-interruptible.

'134 Patent (Ex-1001) at claim 1

#### Wada

#### Wada's burst counter is configured to generate 2<sup>k</sup> internal addresses

Wada (Ex-1005) at Fig. 12 (annotated excerpt); Pet. Reply (Paper 21) at 7

#### Patent Owner's expert agrees that k bits represent 2<sup>k</sup> states:

Q. I'm asking how many different states can be represented in k-bits?

A. States, let's say if you had one bit and it's a binary system, you could have two states. You have two bits, it would be four states, that kind of thing.

Q. In general, k-bits can represent two to the k states; is that correct?

A. If you're talking about a set of bits in a binary system, you could have two—two to k states, states that could be represented at any one instance in time.

Brogioli Dep. (Ex-1015) at 193:16-194:5; Pet. Reply (Paper 21) at 7

#### **Institution Decision**

of internal addresses. Indeed, Patent Owner's argument discussed above, that deasserting the ADV signal would interrupt a burst (*see supra* at 16), could not apply upon modifying Wada's system such that continued generation of address signals in a burst is not interruptible by external signals. Accordingly, we do not agree with Patent Owner that, once modified, Wada's system fails to disclose the "predetermined number" limitation.

Institution Decision (Paper 13) at 21

## **Patent Owner's Argument Fails**

Wada (Ex-1005) at Figs. 12 (annotated excerpt), 13; Pet. Reply (Paper 21) at 7-8

# **Overview**

- Alleged Invention

- "Non-Interruptible" Limitation

- **-**Wada

- -Wada + Barrett

- Patent Owner Fails To Distinguish Prior Art

- "Predetermined Number" Limitation

- No Objective Indicia of Non-Obviousness

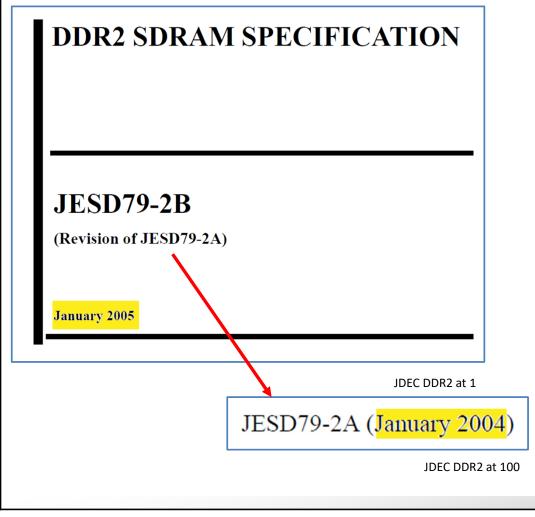

### No Objective Indicia of Non-Obviousness

Alleged long-felt need to mitigate DRAM/SDRAM refresh requirement fails to show non-obviousness

- No nexus: '134 Patent claims encompass SRAM, which has no need of refresh

- '134 Patent does not eliminate need to refresh DRAM

- Mitigation for DRAM refresh had already been solved in the prior art

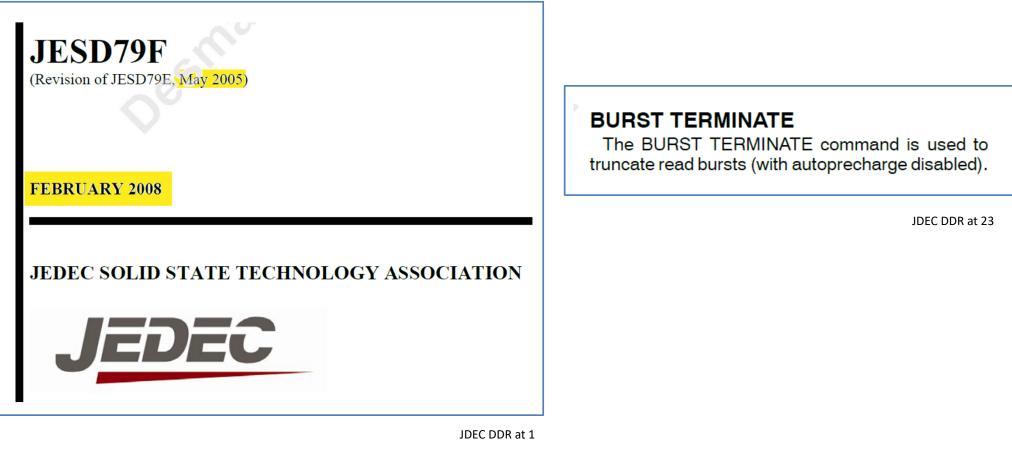

- Timeline of JDEC specification publications shows opposite of what Patent Owner claims

### No Nexus Between Claims And Alleged Long-Felt Need

Patent Owner's alleged "long-felt need" is to mitigate need to refresh DRAM/SDRAM

#### **Patent Owner Response:**

The claimed invention of the '134 Patent solves a long-felt need, specifically the need to improve read/write rates and efficiency of DRAMs. (Ex-2004, ¶219.) Before the invention of the '134 Patent. DRAM and SDRAM suffered from a susceptibility to interruptions, necessitated by the need to refresh DRAM cells. (See, e.g., Ex-1001, 1:20-25; Ex-2006, 65:11-21; Ex-2003, 19 ("The dynamic nature of DRAM requires that the memory be refreshed periodically so as not to lose the contents of the memory cells."); Ex-2004, ¶219.) Even as the industry transitioned into greater use of SDRAM, and DDR SDRAM, the need to refresh remained. (Ex-2006, 65:22-66:8; Ex-2004, ¶219.)

P.O. Resp. (Paper 19) at 64; Pet. Reply (Paper 21) at 21

### **No Nexus: Claims Encompass SRAM**

### '134 Patent

- 1. A circuit comprising:

- a memory comprising a plurality of storage elements each configured to read and write data in response to an internal address signal; and

- a logic circuit configured to generate a predetermined number of said internal address signals in response to (i) an external address signal, (ii) a clock signal and (iii) one or more control signals, wherein said generation of said predetermined number of internal address signals is non-interruptible.

8. The circuit according to claim 1, wherein said memory comprises a static random access memory.

'134 Patent (Ex-1001) at claims 1, 8; Petition (Paper 1) at 33; Pet. Reply (Paper 21) at 13-14, 24

### No Nexus: '134 Patent Does Not Eliminate Refresh

### Patent Owner's expert admits no teaching in '134 Patent:

Q. So sitting here today, you are not aware of any teaching about how to eliminate the need to refresh DRAM?

A. In the confines of the patent, I—I don't recall if it says that from memory. I don't remember. Maybe there's a section you can point me to, but I don't recall that.

Brogioli Dep. (Ex-1015) at 27:12-19; Pet. Rep. (Paper 21) at 14

### Mitigation For DRAM Refresh Was Already Known

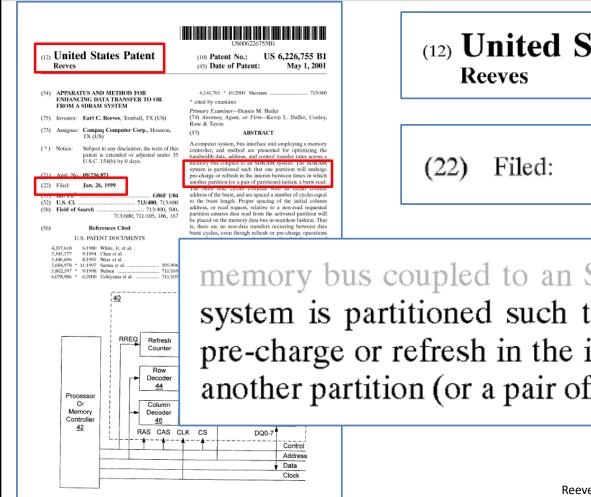

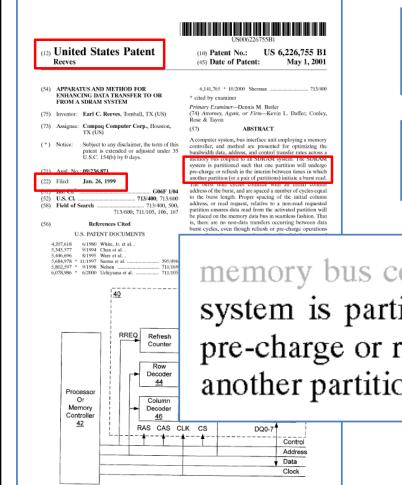

(12) United States Patent Reeves

Jan. 26, 1999

memory bus coupled to an SDRAM system. The SDRAM system is partitioned such that one partition will undergo pre-charge or refresh in the interim between times in which another partition (or a pair of partitions) initiate a burst read.

Reeves (Ex-1008) at Abstract; Petition (Paper 1) at 60-65; Pet. Reply (Paper 21) at 14-15, 21

### Solved Problem Cannot Demonstrate Long Felt Need

Nike's arguments and evidence on long-felt need focused solely on Nishida and its response to the problem in the art of making cutting waste less expensive, but ignored the teachings of other asserted prior art references. . . . 'any alleged, long-felt need was met by the teachings of at least Schuessler I, namely, knitting textile elements 'without requiring cutting'

Nike, Inc. v. Adidas AG, 955 F.3d 45, 55 (Fed. Cir. 2020)

Pet. Reply (Paper 21) at 21

### **Patent Owner's Sur-Reply**

### **Patent Owner Argues in Sur-Reply:**

issued.. But this solution does not address the '134 Patent's solution to the issue,

which doesn't need to partition the DRAM in order to achieve non-interruptible

*bursts*. The '134 Patent meets a long felt need by providing uninterrupted bursts—

which also addresses the refresh problem for DRAM—without requiring partitions.

P.O. Sur-Reply (Paper 22) at 16

### JEDEC Specification Timeline Does Not Show Long Felt Need

JDEC DDR (Ex-2010) at 1, 23; Pet. Reply (Paper 21) at 22

Demonstrative Exhibit 1016, 0042

### DDR2 Specification In 2004 and 2005 Still Specifies Interrupts

However, in case of BL=8 setting, two cases of interrupt by a new burst access are allowed, one reads interrupted by a read, the other writes interrupted by a write with 4 bit burst boundary respectively.

JDEC DDR 2 at 29-30

43

JDEC DDR2 (Ex-2011) at 1, 29-30, 100; Pet. Reply (Paper 21) at 22-23

# Back-up / Rebuttal Slides

44

Demonstrative Exhibit 1016, 0044

### **Claim 16 Means Plus Function Structure Mapping**

# 16[a]: means for reading data from and writing data to a plurality of storage elements in response to a plurality of internal address signals

'134 Patent (Ex-1001) at Fig. 1 (annotated); Wada (Ex-1005) at Fig. 12 (annotated); Petition (Paper 1) at 40-41

### **Claim 16 Means Plus Function Structure Mapping**

16[b]: means for generating a predetermined number of said internal address signals in response to (i) an external address signal, (ii) a clock signal and (iii) one or more control signals, wherein said generation of said predetermined number of internal address signals is non-interruptible

- Alleged problem of interrupted bursts <u>did not exist</u> for SRAM

- '134 Patent's references to refresh cycles apply only to DRAM, not SRAM

'134 Patent:

refreshes. Using a DRAM in a burst application is difficult because of the need to refresh. Completely hiding refresh

## Yet '134 Patent claims cover both SRAM and DRAM/SDRAM

Pet. Reply (Paper 21), 13-14

### (12) United States Patent Reeves

(22) Filed:

Jan. 26, 1999

memory bus coupled to an SDRAM system. The SDRAM system is partitioned such that one partition will undergo pre-charge or refresh in the interim between times in which another partition (or a pair of partitions) initiate a burst read.

Reeves (Ex-1008) at Abstract; Petition (Paper 1) at 60-65; Pet. Rep. (Paper 21) at 14-15, 21

### **Patent Owner's Sur-Reply**

### **Patent Owner Argues in Sur-Reply:**

different advantages. AMD points to U.S. Patent No. 6,226,755 ("Reeves" ("Ex-1008")), which addresses the problem by *partitioning, such that one partition is pre-charged while the other bursts*. But this solution is the same as the solution disclosed in U.S. Patent No. 5,729,504 to Cowles ("Ex-2001"), which was identified in the '134 Patent's prosecution history. Cowles's—and therefore Reeves's proposed solution does not address the '134 Patent's solution to the issue, which *does not need to partition the memory to achieve non-interruptible bursts*.

P.O. Sur-Reply (Paper 22) at 10

### File History, '134 Patent

| <b>sign</b><br>edge | cerminate a continuous burst read operation, the WE*<br>al merely has to transition high prior to a falling<br>of the CAS* signal." (Col. 8, 11. 33-36 of Cowles;<br>asis added.) |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ther                | efore, even if we assume for the sake of argument                                                                                                                                 |

| that OE* does       | not affect the generation of internal addresses,                                                                                                                                  |

| there is still      | one condition under which the memories of Cowles                                                                                                                                  |

| will interrup       | t (or prematurely terminate) an access: <u>WE*</u>                                                                                                                                |

| transitioning.      | Cowles rather explicitly teaches how such a                                                                                                                                       |

| premature term      | ination can take place.                                                                                                                                                           |

'134 File Hist. (Ex-1004) at 112; Pet. Prelim. Reply (Paper 10) at 1-2

50

Demonstrative Exhibit 1016, 0050

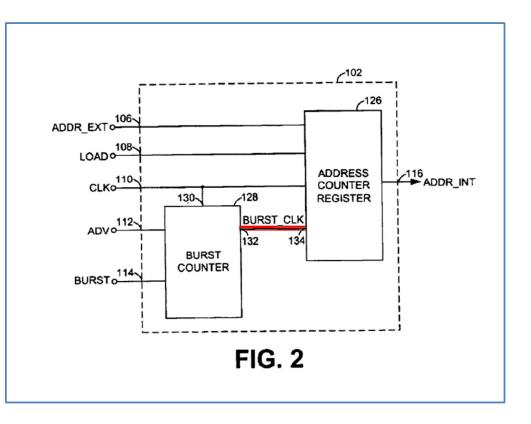

Patent Owner incorrectly argues "The '134 Patent discloses a mechanism to achieve a noninterruptible burst."

PO Resp. (Paper 19) at 31; '134 Patent (Ex-1001) at Fig. 2; Pet. Reply (Paper 21) at 15-16

### **Patent Owner's expert agrees**

Q. Okay. And the patent doesn't describe a particular circuit that will take in a number such as four and generate four pulses in any detail; is that correct?

A. Yeah, I don't recall that the patent sort of talks about pulse circuit design. That's something that, you know, the reader would understand and, you know, depending on the use case probably, you know, there'd be different design tradeoffs. But I don't recall—maybe you can point me to a section if it does, but going from memory, I don't recall it talking about pulse circuit design. That's just something a person of skill would understand.

Brogioli Dep. (Ex-1015) at 153:24-154:17; Pet. Reply (Paper 21) at 15-16