#### 4. Memory access or R-type instruction completion step

During this step, a load or store instruction accesses memory and an arithmetic-logical instruction writes its result. When a value is retrieved from memory it is stored into the memory data register (MDR), where it must be used on the next clock cycle.

#### Memory reference:

MDR = Memory [ALUOut];

#### or

```

Memory [ALUOut] = B;

```

*Operation:* If the instruction is a load, a data word is retrieved from memory and is written into the MDR. If the instruction is a store, then the data is written into memory. In either case, the address used is the one computed during the previous step and stored in ALUOut. For a store, the source operand is saved in B. (B is actually read twice, once in step 2 and once in step 3. Luckily, the same value is read both times, since the register number—which is stored in IR and used to read from the register file—does not change.) The signal MemRead (for a load) or MemWrite (for store) will need to be asserted. In addition, for loads and stores, the signal IorD is set to 1 to force the memory address to come from the ALU, rather than the PC. Since MDR is written on every clock cycle, no explicit control signal need be asserted.

#### *Arithmetic-logical instruction (R-type):*

Reg[IR[15-11]] = ALUOut;

*Operation:* Place the contents of ALUOut, which corresponds to the output of the ALU operation in the previous cycle, into the Result register. The signal RegDst must be set to 1 (to force the rd (bits 15–11) field to be used to select the register file entry to write). RegWrite must be asserted, and MemtoReg must be set to 0 (so that the output of the ALU is written, as opposed to the memory data output).

#### 5. Memory read completion step

During this step, loads complete by writing back the value from memory.

Load:

#### Reg[IR[20-16]] = MDR;

*Operation:* Write the load data, which was stored into MDR in the previous cycle, into the register file. To do this, we set MemtoReg = 1 (to write the result from memory), assert RegWrite (to cause a write), and we make RegDst = 0 to choose the rt (bits 20-16) field as the register number.

| Step name                                                     | Action for R-type<br>instructions                                                         | Action for memory-<br>reference instructions | Action for<br>branches | Action for<br>jumps                |  |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------|------------------------|------------------------------------|--|

| Instruction fetch                                             |                                                                                           | IR = Memory[PC] $PC = PC + 4$                |                        |                                    |  |

| Instruction<br>decode/register fetch                          | A = Reg [IR[25-21]]<br>B = Reg [IR[20-16]]<br>ALUOut = PC + (sign-extend (IR[15-0]) << 2) |                                              |                        |                                    |  |

| Execution, address<br>computation, branch/<br>jump completion | ALUOut = A op B                                                                           |                                              |                        | PC = PC [31-28]  <br>(IR[25-0]<<2) |  |

| Memory access or R-type<br>completion                         | Reg [IR[15-11]] = Load: MDR = Memory[ALUOut]<br>ALUOut or<br>Store: Memory [ALUOut] = B   |                                              |                        |                                    |  |

| Memory read completion                                        |                                                                                           | Load: Reg[IR[20-16]] = MDR                   |                        |                                    |  |

**FIGURE 5.35 Summary of the steps taken to execute any instruction class.** Instructions take from three to five execution steps. The first two steps are independent of the instruction class. After these steps, an instruction takes from one to three more cycles to complete, depending on the instruction class. The empty entries for the Memory access step or the Memory read completion step indicate that the particular instruction class takes fewer cycles. In a multicycle implementation, a new instruction will be started as soon as the current instruction completes, so these cycles are not idle or wasted. As mentioned earlier, the register file actually reads every cycle, but as long as the IR does not change, the values read from the register file are identical. In particular, the value read into register B during the Instruction decode stage, for a branch or R-type instruction, is the same as the value stored into B during the Execution stage and then used in the Memory access stage for a store word instruction.

This five-step sequence is summarized in Figure 5.35. From this sequence we can determine what the control must do on each clock cycle.

#### **Defining the Control**

Now that we have determined what the control signals are and when they must be asserted, we can implement the control unit. To design the control unit for the single-cycle datapath, we used a set of truth tables that specified the setting of the control signals based on the instruction class. For the multicycle datapath, the control is more complex because the instruction is executed in a series of steps. The control for the multicycle datapath must specify both the signals to be set in any step and the next step in the sequence.

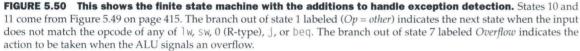

In this subsection and in section 5.5, we will look at two different techniques to specify the control. The first technique is based on finite state machines that are usually represented graphically. The second technique, called *microprogramming*, uses a programming representation for control. Both of these techniques represent the control in a form that allows the detailed implementation—using gates, ROMs, or PLAs—to be synthesized by a CAD system. In this chapter, we will focus on the design of the control and its representation in these two forms. If you are interested in how these control specifications are

translated into actual hardware, Appendix C continues the development of this chapter, translating the multicycle control unit to a detailed hardware implementation. The key ideas of control can be grasped from this chapter without examining the material in Appendix C. However, if you want to get down to the bits, Appendix C can show you how to do it!

The first method we use to specify the multicycle control is a *finite state machine*. A finite state machine consists of a set of states and directions on how to change states. The directions are defined by a *next-state function*, which maps the current state and the inputs to a new state. When we use a finite state machine for control, each state also specifies a set of outputs that are asserted when the machine is in that state. The implementation of a finite state machine usually assumes that all outputs that are not explicitly asserted are deasserted. The correct operation of the datapath depends on the fact that a signal that is not explicitly asserted is deasserted, rather than acting as a don't care. For example, the RegWrite signal should be asserted only when a register file entry is to be written; when it is not explicitly asserted, it must be deasserted.

Multiplexor controls are slightly different, since they select one of the inputs whether they are 0 or 1. Thus, in the finite state machine, we always specify the setting of all the multiplexor controls that we care about. When we implement the finite state machine with logic, setting a control to 0 may be the default and thus may not require any gates. A simple example of a finite state machine appears in Appendix B, and if you are unfamiliar with the concept of a finite state machine, you may want to examine Appendix B before proceeding.

The finite state control essentially corresponds to the five steps of execution shown on pages 385 through 388; each state in the finite state machine will take 1 clock cycle. The finite state machine will consist of several parts. Since the first two steps of execution are identical for every instruction, the initial two states of the finite state machine will be common for all instructions. Steps 3 through 5 differ, depending on the opcode. After the execution of the last step for a particular instruction class, the finite state machine will return to the initial state to begin fetching the next instruction.

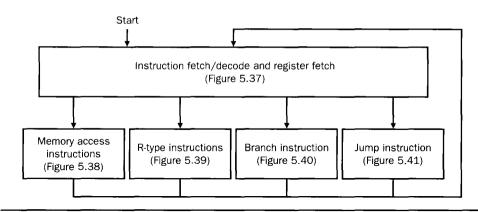

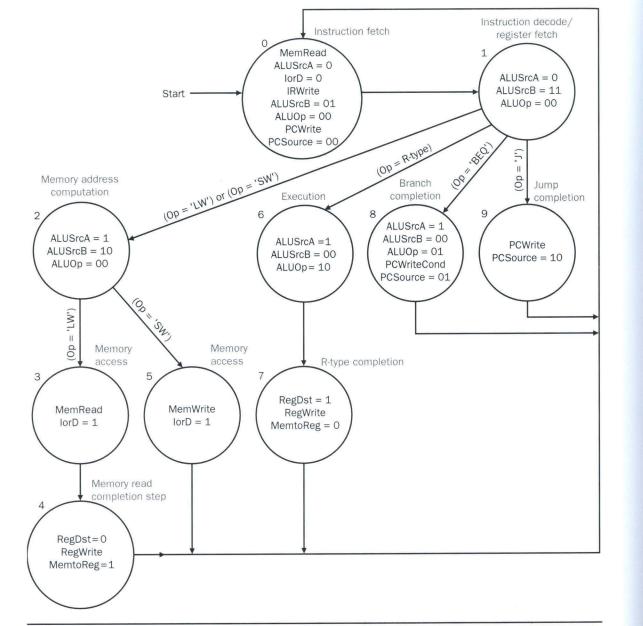

Figure 5.36 shows this abstracted representation of the finite state machine. To fill in the details of the finite state machine, we will first expand the instruction fetch and decode portion, then we will show the states (and actions) for the different instruction classes.

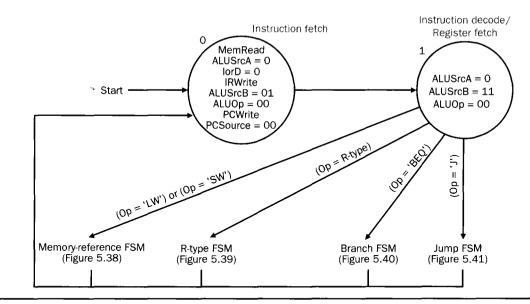

We show the first two states of the finite state machine in Figure 5.37 using a traditional graphic representation. We number the states to simplify the explanation, though the numbers are arbitrary. State 0, corresponding to step 1, is the starting state of the machine.

The signals that are asserted in each state are shown within the circle representing the state. The arcs between states define the next state and are labeled

**FIGURE 5.36** The high-level view of the finite state machine control. The first steps are independent of the instruction class; then a series of sequences that depend on the instruction opcode are used to complete each instruction class. After completing the actions needed for that instruction class, the control returns to fetch a new instruction. Each box in this figure may represent one to several states. The arc labeled *Start* marks the state in which to begin when the first instruction is to be fetched.

**FIGURE 5.37** The instruction fetch and decode portion of every instruction is identical. These states correspond to the top box in the abstract finite state machine in Figure 5.36. In the first state we assert two signals to cause the memory to read an instruction and write it into the Instruction register (MemRead and IRWrite), and we set IorD to 0 to choose the PC as the address source. The signals ALUSrcA, ALUSrcB, ALUOp, PCWrite, and PCSource are set to compute PC + 4 and store it into the PC. (It will also be stored into ALUOut, but never used from there.). In the next state, we compute the branch target address by setting ALUSrcB to 11 (causing the shifted and sign-extended lower 16 bits of the IR to be sent to the ALU), setting ALUSrcA to 0 and ALUOp to 00; we store the result in the ALUOut register, which is written on every cycle. There are four next states that depend on the class of the instruction, which is known during this state. The control unit input, called Op, is used to determine which of these arcs to follow.

with conditions that select a specific next state when multiple next states are possible. After state 1, the signals asserted depend on the class of instruction. Thus, the finite state machine has four arcs exiting state 1, corresponding to the four instruction classes: memory reference, R-type, branch on equal, and jump. This process of branching to different states depending on the instruction is called *decoding*, since the choice of the next state, and hence the actions that follow, depend on the instruction class.

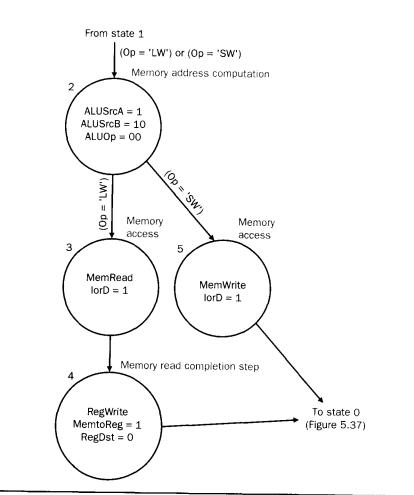

Figure 5.38 shows the portion of the finite state machine needed to implement the memory-reference instructions. For the memory-reference instructions, the first state after fetching the instruction and registers computes the memory address (state 2). To compute the memory address, the ALU input multiplexors must be set so that the first input is the A register, while the second input is the sign-extended displacement field; the result is written into the ALUOut register. After the memory address calculation, the memory should be read or written; this requires two different states. If the instruction opcode is 1w, then state 3 (corresponding to the step Memory access) does the memory read (MemRead is asserted). The output of the memory is always written into MDR. If it is sw, state 5 does a memory write (MemWrite is asserted). In states 3 and 5, the signal IorD is set to 1 to force the memory address to come from the ALU. After performing a write, the instruction sw has completed execution, and the next state is state 0. If the instruction is a load, however, another state (state 4) is needed to write the result from the memory into the register file. Setting the multiplexor controls MemtoReg = 1 and RegDst = 0 will send the loaded value in the MDR to be written into the register file, using rt as the register number. After this state, corresponding to the Memory read completion step, the next state is state 0.

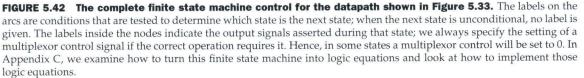

To implement the R-type instructions requires two states corresponding to steps 3 (Execute) and 4 (R-type completion). Figure 5.39 shows this two-state portion of the finite state machine. State 6 asserts ALUSrcA and sets the ALUSrcB signals to 00; this forces the two registers that were read from the register file to be used as inputs to the ALU. Setting ALUOp to 10 causes the ALU control unit to use the function field to set the ALU control signals. In state 7, Reg-Write is asserted to cause the register file to write, RegDst is asserted to cause the rd field to be used as the register number of the destination, and MemtoReg is deasserted to select ALUOut as the source of the value to write into the register file.

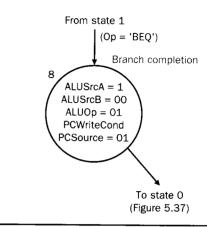

For branches, only a single additional state is necessary, because they complete execution during the third step of instruction execution. During this state, the control signals that cause the ALU to compare the contents of registers A and B must be set, and the signals that cause the PC to be written conditionally with the address in the ALUOut register are also set. To perform the

comparison requires that we assert ALUSrcA and set ALUSrcB to 00, and set the ALUOp value to 01 (forcing a subtract). (We use only the Zero output of the ALU, not the result of the subtraction.) To control the writing of the PC, we assert PCWriteCond and set PCSource = 01, which will cause the value in the

394

**FIGURE 5.39 R-type instructions can be implemented with a simple two-state finite state machine.** These states correspond to the box labeled "R-type instructions" in Figure 5.36. The first state causes the ALU operation to occur, while the second state causes the ALU result (which is in ALUOut) to be written in the register file. The three signals asserted during state 7 cause the contents of ALUOut to be written into the register file in the entry specified by the rd field of the Instruction register.

ALUOut register (containing the branch address calculated in state 1, Figure 5.37 on page 391) to be written into the PC if the Zero bit out of the ALU is asserted. Figure 5.40 shows this single state.

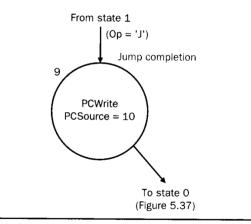

The last instruction class is jump; like branch, it requires only a single state (shown in Figure 5.41) to complete its execution. In this state, the signal PCWrite is asserted to cause the PC to be written. By setting PCSource to 10, the value supplied for writing will be the lower 26 bits of the Instruction register with  $00_{two}$  added as the low-order bits concatenated with the upper 4 bits of the PC.

We can now put these pieces of the finite state machine together to form a specification for the control unit, as shown in Figure 5.42. In each state, the signals that are asserted are shown. The next state depends on the opcode bits of the instruction, so we label the arcs with a comparison for the corresponding instruction opcodes.

**FIGURE 5.40** The branch instruction requires a single state. The first three outputs that are asserted cause the ALU to compare the registers (ALUSrcA, ALUSrcB, and ALUOp), while the signals PCSource and PCWriteCond perform the conditional write if the branch condition is true. Notice that we do not use the value written into ALUOut; instead, we use only the Zero output of the ALU. The branch target address is read from ALUOut, where it was saved at the end of state 1.

FIGURE 5.41 The jump instruction requires a single state that asserts two control signais to write the PC with the lower 26 bits of the Instruction register shifted left 2 bits and concatenated to the upper 4 bits of the PC of this instruction.

Given this implementation, and the knowledge that each state requires 1 clock cycle, we can find the CPI for a typical instruction mix.

396

### **CPI in a Multicycle CPU** Example Using the control shown in Figure 5.42 and the gcc instruction mix shown in Figure 4.54 on page 311, what is the CPI, assuming that each state requires 1 clock cycle? Answer The mix is 23% loads (1% load byte + 1% load halfword + 21% load word), 13% stores (1% store byte + 12% store word), 19% branches (9% BEQ, 8% BNE, 1% BLTZ, 1% BGEZ), 2% jumps (1% jal + 1% jr), and 43% ALU (all the rest of the mix). From Figure 5.42, the number of clock cycles for each instruction class is the following: ■ Loads: 5 ■ Stores: 4 ■ ALU instructions: 4 Branches: 3 ■ Jumps: 3 The CPI is given by the following: $CPI = \frac{CPU \text{ clock cycles}}{Instruction \text{ count}} = \frac{\sum Instruction \text{ count}_i \times CPI_i}{Instruction \text{ count}}$ $= \sum \frac{\text{Instruction count}_i}{\text{Instruction count}} \times \text{CPI}_i$ The ratio Instruction count, Instruction count is simply the instruction frequency for the instruction class *i*. We can therefore substitute to obtain $CPI = 0.23 \times 5 + 0.13 \times 4 + 0.43 \times 4 + 0.19 \times 3 + 0.02 \times 3 = 4.02$ This CPI is better than the worst-case CPI would have been if all the in-

structions took the same number of clock cycles (5).

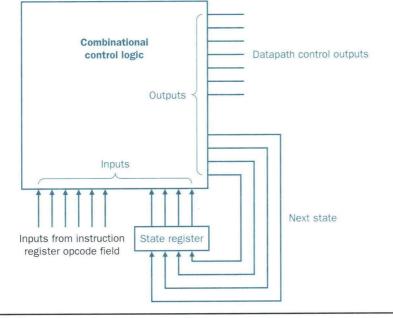

**FIGURE 5.43** Finite state machine controllers are typically implemented using a block of combinational logic and a register to hold the current state. The outputs of the combinational logic are the next-state number and the control signals to be asserted for the current state. The inputs to the combinational logic are the current state and any inputs used to determine the next state. In this case, the inputs are the instruction register opcode bits. Notice that in the finite state machine used in this chapter, the outputs depend only on the current state, not on the inputs. The following elaboration explains this in more detail.

A finite state machine can be implemented with a temporary register that holds the current state and a block of combinational logic that determines both the datapath signals to be asserted as well as the next state. Figure 5.43 shows how such an implementation might look. Appendix C describes in detail how the finite state machine is implemented using this structure. In section C.3, the combinational control logic for the finite state machine of Figure 5.42 is implemented both with a ROM (read-only memory) and a PLA (programmable logic array). (Also see Appendix B for a description of these logic elements.) In the next section of this chapter, we consider another way to represent control. Both of these techniques are simply different representations of the same control information.

**Elaboration:** The style of finite state machine in Figure 5.43 is called a Moore machine, after Edward Moore. Its identifying characteristic is that the output depends only on the current state. For a Moore machine, the box labeled combinational control logic can be split into two pieces. One piece has the control output and only the state input, while the other has only the next-state output.

An alternative style of machine is a Mealy machine, named after George Mealy. The Mealy machine allows both the input and the current state to be used to determine the output. Moore machines have potential implementation advantages in speed and size of the control unit. The speed advantages arise because the control outputs, which are needed early in the clock cycle, do not depend on the inputs, but only on the current state. In Appendix C, when the implementation of this finite state machine is taken down to logic gates, the size advantage can be clearly seen. The potential disadvantage of a Moore machine is that it may require additional states. For example, in situations where there is a one-state difference between two sequences of states, the Mealy machine may unify the states by making the outputs depend on the inputs.

### Microprogramming: Simplifying Control Design

5.5

For the control of our simple MIPS subset, a graphical representation of the finite state machine, as in Figure 5.42, is certainly adequate. We can draw such a diagram on a single page and translate it into equations (see Appendix C) without generating too many errors. Consider instead an implementation of the full MIPS instruction set, which contains over 100 instructions (see Appendix A). In one implementation, instructions take from 1 clock cycle to over 20 clock cycles. Clearly, the control function will be much more complex. Or consider an instruction set with more instructions of widely varying classes: The control unit could easily require thousands of states with hundreds of different sequences. For example, the Intel 80x86 instruction set has many more addressing mode combinations, as well as a much larger set of opcodes.

In such cases, specifying the control unit with a graphical representation will be cumbersome, since the finite state machine can contain hundreds to thousands of states, and even more arcs! The graphical representation—although useful for a small finite state machine—will not fit on a page, let alone be understandable, when it becomes very large. Programmers know this phenomenon quite well: As programs become large, additional structuring techniques (for example, procedures and modules) are needed to keep the programs comprehensible. Of course, specifying complex control functions directly as equations, without making any mistakes, becomes essentially impossible.

Can we use some of the ideas from programming to help create a method of specifying the control that will make it easier to understand as well as to design? Suppose we think of the set of control signals that must be asserted in a state as an instruction to be executed by the datapath. To avoid confusing the instructions of the MIPS instruction set with these low-level control instructions, the latter are called *microinstructions*. Each microinstruction defines the

400

set of datapath control signals that must be asserted in a given state. Executing a microinstruction has the effect of asserting the control signals specified by the microinstruction.

In addition to defining which control signals must be asserted, we must also specify the sequencing—what microinstruction should be executed next? In the finite state machine shown in Figure 5.42 on page 396, the next state is determined in one of two different ways. Sometimes a single next state follows the current state unconditionally. For example, state 1 always follows state 0, and the only way to reach state 1 is via state 0. In other cases, the choice of the next state depends on the input. This is true in state 1, which has four different successor states.

When we write programs, we also have an analogous situation. Sometimes a group of instructions should be executed sequentially, and sometimes we need to branch. In programming, the default is sequential execution, while branching must be indicated explicitly. In describing the control as a program, we also assume that microinstructions written sequentially are executed in sequence, while branching must be indicated explicitly. The default sequencing mechanism can still be implemented using a structure like the one in Figure 5.43 on page 398; however, it is often more efficient to implement the default sequential state using a counter. We will see how such an implementation looks at the end of this section.

Designing the control as a program that implements the machine instructions in terms of simpler microinstructions is called *microprogramming*. The key idea is to represent the asserted values on the control lines symbolically, so that the microprogram is a representation of the microinstructions, just as assembly language is a representation of the machine instructions. In choosing a syntax for an assembly language, we usually represent the machine instructions as a series of fields (opcode, registers, and offset or immediate field); likewise, we will represent a microinstruction syntactically as a sequence of fields whose functions are related.

### **Defining a Microinstruction Format**

The microprogram is a symbolic representation of the control that will be translated by a program to control logic. In this way, we can choose how many fields a microinstruction should have and what control signals are affected by each field. The format of the microinstruction should be chosen so as to simplify the representation, making it easier to write and understand the microprogram. For example, it is useful to have one field that controls the ALU and a set of three fields that determine the two sources for the ALU operation as well as the destination of the ALU result. In addition to readability, we would also like the microprogram format to make it difficult or impossible to write inconsistent microinstructions. A microinstruction is inconsistent if it requires that a given control signal be set to two different values. We will see an example of how this could happen shortly.

To avoid a format that allows inconsistent microinstructions, we can make each field of the microinstruction responsible for specifying a nonoverlapping set of control signals. To choose how to make this partition of the control signals for this implementation into microinstruction fields, it is useful to reexamine two previous figures:

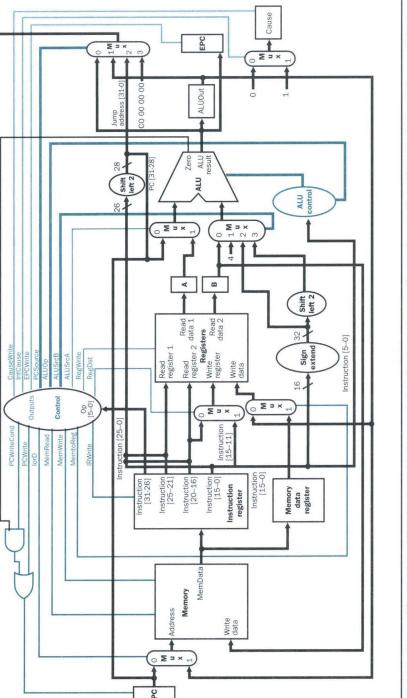

- Figure 5.33, on page 383, which shows all the control signals and how they affect the datapath

- Figure 5.34, on page 384, which shows the function of each datapath control signal

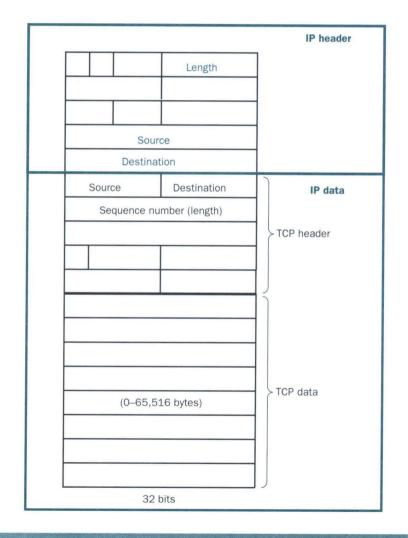

Signals that are never asserted simultaneously may share the same field. Figure 5.44 shows how the microinstruction can be broken into seven fields and defines the general function of each field. The first six fields of the micro-instruction control the datapath, while the Sequencing field (the seventh field) specifies how to select the next microinstruction.

Microinstructions are usually placed in a ROM or a PLA (both described in Appendix B and used to implement control in Appendix C), so we can assign addresses to the microinstructions. The addresses are usually given out sequentially, in the same way that we chose sequential numbers for the states in the finite state machine. Three different methods are available to choose the next microinstruction to be executed:

1. Increment the address of the current microinstruction to obtain the address of the next microinstruction. This sequential behavior is indicated in the microprogram by putting Seq in the Sequencing field. Since sequential execution of instructions is encountered often, many microprogramming systems make this the default.

| Field name       | Function of field                                                                                      |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------|--|--|--|

| ALU control      | Specify the operation being done by the ALU during this clock; the result is always written in ALUOut. |  |  |  |

| SRC1             | Specify the source for the first ALU operand.                                                          |  |  |  |

| SRC2             | Specify the source for the second ALU operand.                                                         |  |  |  |

| Register control | Specify read or write for the register file, and the source of the value for a write.                  |  |  |  |

| Memory           | Specify read or write, and the source for the memory. For a read, specify the destination register.    |  |  |  |

| PCWrite control  | Specify the writing of the PC.                                                                         |  |  |  |

| Sequencing       | Specify how to choose the next microinstruction to be executed.                                        |  |  |  |

**FIGURE 5.44** Each microinstruction contains these seven fields. The values for each field are shown in Figure 5.45.

- 2. Branch to the microinstruction that begins execution of the next MIPS instruction. We will label this initial microinstruction (corresponding to state 0) as Fetch and place the indicator Fetch in the Sequencing field to indicate this action.

- 3. Choose the next microinstruction based on the control unit input. Choosing the next microinstruction on the basis of some input is called a *dispatch*. Dispatch operations are usually implemented by creating a table containing the addresses of the target microinstructions. This table is indexed by the control unit input and may be implemented in a ROM or in a PLA. There are often multiple dispatch tables; for this implementation, we will need two dispatch tables, one to dispatch from state 1 and one to dispatch from state 2. We indicate that the next microinstruction should be chosen by a dispatch operation by placing Dispatch i, where i is the dispatch table number, in the Sequencing field.

Figure 5.45 gives a description of the values allowed for each field of the microinstruction and the effect of the different field values. Remember that the microprogram is a symbolic representation. This microinstruction format is just one example of many potential formats.

**Elaboration:** The basic microinstruction format may allow combinations that cannot be supported within the datapath. Typically, a microassembler will perform checks on the microinstruction fields to ensure that such inconsistencies are flagged as errors and corrected. An alternative is to structure the microinstruction format to avoid this, but this might make the microinstruction harder to read. Most microprogramming systems choose readability and require the microcode assembler to detect inconsistencies.

#### **Creating the Microprogram**

Now let's create the microprogram for the control unit. We will label the instructions in the microprogram with symbolic labels, which can be used to specify the contents of the dispatch tables (see section C.5 in Appendix C for a discussion of how the dispatch tables are defined and assembled). In writing the microprogram, there are two situations in which we may want to leave a field of the microinstruction blank. When a field that controls a functional unit or that causes state to be written (such as the Memory field or the ALU dest field) is blank, no control signals should be asserted. When a field *only* specifies the control of a multiplexor that determines the input to a functional unit, such as the SRC1 field, leaving it blank means that we do not care about the input to the functional unit (or the output of the multiplexor).

| Field name       | Values for field | Function of field with specific value                                                                                                                                                                                                                                                                                                                                                               |

|------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Label            | Any string       | Used to specify labels to control microcode sequencing. Labels that end in a 1 o 2 are used for dispatching with a jump table that is indexed based on the opcode Other labels are used as direct targets in the microinstruction sequencing. Labels do not generate control signals directly but are used to define the contents of dispatch tables and generate control for the Sequencing field. |

|                  | Add              | Cause the ALU to add.                                                                                                                                                                                                                                                                                                                                                                               |

| ALU control      | Subt             | Cause the ALU to subtract; this implements the compare for branches.                                                                                                                                                                                                                                                                                                                                |

|                  | Func code        | Use the instruction's funct field to determine ALU control.                                                                                                                                                                                                                                                                                                                                         |

| SRC1             | PC               | Use the PC as the first ALU input.                                                                                                                                                                                                                                                                                                                                                                  |

| SHOT             | A                | Register A is the first ALU input.                                                                                                                                                                                                                                                                                                                                                                  |

|                  | В                | Register B is the second ALU input.                                                                                                                                                                                                                                                                                                                                                                 |

| SRC2             | 4                | Use 4 for the second ALU input.                                                                                                                                                                                                                                                                                                                                                                     |

| SRU2             | Extend           | Use output of the sign extension unit as the second ALU input.                                                                                                                                                                                                                                                                                                                                      |

|                  | Extshft          | Use the output of the shift-by-two unit as the second ALU input.                                                                                                                                                                                                                                                                                                                                    |

|                  | Read             | Read two registers using the rs and rt fields of the IR as the register numbers, putting the data into registers A and B.                                                                                                                                                                                                                                                                           |

| Register control | Write ALU        | Write the register file using the rd field of the IR as the register number and the contents of ALUOut as the data.                                                                                                                                                                                                                                                                                 |

|                  | Write MDR        | Write the register file using the rt field of the IR as the register number and the contents of the MDR as the data.                                                                                                                                                                                                                                                                                |

|                  | Read PC          | Read memory using the PC as address; write result into IR (and the MDR).                                                                                                                                                                                                                                                                                                                            |

| Memory           | Read ALU         | Read memory using ALUOut as address; write result into MDR.                                                                                                                                                                                                                                                                                                                                         |

|                  | Write ALU        | Write memory using the ALUOut as address; contents of B as the data.                                                                                                                                                                                                                                                                                                                                |

|                  | ALU              | Write the output of the ALU into the PC.                                                                                                                                                                                                                                                                                                                                                            |

| PCWrite control  | ALUOut-cond      | If the Zero output of the ALU is active, write the PC with the contents of the register ALUOut.                                                                                                                                                                                                                                                                                                     |

|                  | Jump address     | Write the PC with the jump address from the instruction.                                                                                                                                                                                                                                                                                                                                            |

|                  | Seq              | Choose the next microinstruction sequentially.                                                                                                                                                                                                                                                                                                                                                      |

| Sequencing       | Fetch            | Go to the first microinstruction to begin a new instruction.                                                                                                                                                                                                                                                                                                                                        |

|                  | Dispatch i       | Dispatch using the ROM specified by i (1 or 2).                                                                                                                                                                                                                                                                                                                                                     |

**FIGURE 5.45 Each field of the microinstruction has a number of values that it can take on.** The second column gives the possible values that are legal for the field, and the third column defines the effect of that value. Each field value, other than the label field, is mapped to a particular setting of the datapath control lines; this mapping is described in Appendix C, section C.5. That section also shows how the label field is used to generate the dispatch tables. As we will see, the microcode implementation will differ slightly from the finite state machine control, but only in ways that do not affect instruction semantics.

The easiest way to understand the microprogram is to break it into pieces that deal with each component of instruction execution, just as we did when we designed the finite state machine. The first component of every instruction execution is to fetch the instructions, decode them, and compute both the sequential PC and branch target PC. These actions correspond directly to the first two steps of execution described on pages 385 through 388. The two microinstructions needed for these first two steps are shown below:

| Label | ALU<br>control | SRC1 |         | Register<br>control |         | PCWrite<br>control | Sequencing |

|-------|----------------|------|---------|---------------------|---------|--------------------|------------|

| Fetch | Add            | PC   | 4       |                     | Read PC | ALU                | Seq        |

|       | Add            | PC   | Extshft | Read                |         |                    | Dispatch 1 |

To understand what each microinstruction does, it is easiest to look at the effect of a group of fields. In the first microinstruction, the fields asserted and their effects are the following:

| Fields                  | Effect                                                                                            |

|-------------------------|---------------------------------------------------------------------------------------------------|

| ALU control, SRC1, SRC2 | Compute PC + 4. (The value is also written into ALUOut, though it will never be read from there.) |

| Memory                  | Fetch instruction into IR.                                                                        |

| PCWrite control         | Causes the output of the ALU to be written into the PC.                                           |

| Sequencing              | Go to the next microinstruction.                                                                  |

The label field, containing the label Fetch, will be used in the Sequencing field when the microprogram wants to start the execution of the next instruction.

For the second microinstruction, the operations controlled by the microinstruction are the following:

| Fields                  | Effect                                                                      |

|-------------------------|-----------------------------------------------------------------------------|

| ALU control, SRC1, SRC2 | Store PC + sign extension (IR[15–0]) << 2 into ALUOut.                      |

| Register control        | Use the rs and rt fields to read the registers placing the data in A and B. |

| Sequencing              | Use dispatch table 1 to choose the next microinstruction address.           |

We can think of the dispatch operation as a *case* or *switch* statement with the opcode field and the dispatch table 1 used to select one of four different microinstruction sequences with one of four different labels (all ending in "1"):

- Mem1 for memory-reference instructions

- Rformat1 for R-type instructions

- BEQ1 for the branch equal instruction

- JUMP1 for the jump instruction

The microprogram for memory-reference instructions has four microinstructions, as shown below. The first instruction does the memory address calculation. A two-instruction sequence is needed to complete a load (memory read followed by register file write), while the store requires only one microinstruction after the memory address calculation:

| Label | ALU<br>control | SRC1 | SRC2   | Register<br>control | Memory                                                                                                         | PCWrite<br>control | Sequencing |

|-------|----------------|------|--------|---------------------|----------------------------------------------------------------------------------------------------------------|--------------------|------------|

| Mem1  | Add            | А    | Extend |                     | Construction of the second |                    | Dispatch 2 |

| LW2   |                |      |        |                     | Read ALU                                                                                                       |                    | Seq        |

|       |                |      |        | Write MDR           |                                                                                                                |                    | Fetch      |

| SW2   |                |      |        |                     | Write ALU                                                                                                      |                    | Fetch      |

### Let's look at the fields of the first microinstruction in this sequence:

| Fields                     | Effect                                                                                              |

|----------------------------|-----------------------------------------------------------------------------------------------------|

| ALU control,<br>SRC1, SRC2 | Compute the memory address: Register (rs) + sign-extend (IR[15–0]), writing the result into ALUOut. |

| Sequencing                 | Use the second dispatch table to jump to the microinstruction labeled either LW2 or SW2.            |

The first microinstruction in the sequence specific to 1w is labeled LW2, since it is reached by a dispatch through table 2. This microinstruction has the following effect:

| Fields     | Effect                                                                         |

|------------|--------------------------------------------------------------------------------|

| Memory     | Read memory using the ALUOut as the address and writing the data into the MDR. |

| Sequencing | Go to the next microinstruction.                                               |

The next microinstruction completes execution with a microinstruction that has the following effects:

| Fields           | Effect                                                                      |

|------------------|-----------------------------------------------------------------------------|

| Register control | Write the contents of the MDR into the register file entry specified by rt. |

| Sequencing       | Go to the microinstruction labeled Fetch.                                   |

The store microinstruction, labeled SW2, operates similarly to the load micro-instruction labeled LW2:

| Fields     | Effect                                                                                   |  |  |

|------------|------------------------------------------------------------------------------------------|--|--|

| Memory     | Write memory using contents of ALUOut as the address and the contents of B as the value. |  |  |

| Sequencing | Go to the microinstruction labeled Fetch.                                                |  |  |

The microprogram sequence for R-type instructions consists of two microinstructions: the first does the ALU operation (and is labeled Rformat1 for dispatch purposes), while the second writes the result into the register file:

| Label    | ALU<br>control | SRC1 | SRC2 | Register<br>control | Memory | PCWrite<br>control |       |

|----------|----------------|------|------|---------------------|--------|--------------------|-------|

| Rformat1 | Func code      | A    | В    |                     |        |                    | Seq   |

|          |                |      |      | Write ALU           |        |                    | Fetch |

You might think that because the fields of these two microinstructions do not conflict (i.e., each uses different fields), you could combine them into one. Indeed, microcode optimizers perform such operations when compiling microcode. In this case, however, the result of the ALU instruction is written into the register ALUOut, and the written value cannot be read until the next clock cycle; hence we cannot combine them into one microinstruction. (If you did combine them, you'd end up writing the wrong thing into the register file!) You could try to remove the ALUOut register to allow the two microinstructions to be combined, but this would require lengthening the clock cycle to allow the register file write to occur in the same clock cycle as the ALU operation.

The first microinstruction initiates the ALU operation:

| Fields                     | Effect                                                                                                            |

|----------------------------|-------------------------------------------------------------------------------------------------------------------|

| ALU control,<br>SRC1, SRC2 | The ALU operates on the contents of the A and B registers, using the function field to specify the ALU operation. |

| Sequencing                 | Go to the next microinstruction.                                                                                  |

The second microinstruction causes the ALU output to be written in the register file:

| Fields           | Effect                                                                                 |  |  |

|------------------|----------------------------------------------------------------------------------------|--|--|

| Register control | The value in ALUOut is written into the register file entry specified by the rd field. |  |  |

| Sequencing       | Go to the microinstruction labeled Fetch.                                              |  |  |

Because the immediately previously executed microinstruction computed the branch target address, the microprogram sequence for branch, labeled with BEQ, requires just one microinstruction:

| Label | ALU<br>control | SRC1 |   | Register<br>control | PCWrite<br>control | Sequencing |

|-------|----------------|------|---|---------------------|--------------------|------------|

| BEQ1  | Subt           | А    | В |                     | ALUOut-cond        | Fetch      |

#### The asserted fields of this microinstruction are the following:

| Fields                     | Effect                                                                                                |

|----------------------------|-------------------------------------------------------------------------------------------------------|

| ALU control,<br>SRC1, SRC2 | The ALU subtracts the operands in A and B to generate the Zero output.                                |

| PCWrite control            | Causes the PC to be written using the value already in ALUOut, if the Zero output of the ALU is true. |

| Sequencing                 | Go to the microinstruction labeled Fetch.                                                             |

The jump microcode sequence also consists of one microinstruction:

| Label | ALU<br>control | SRC1 | Register<br>control | PCWrite<br>control | Sequencing |

|-------|----------------|------|---------------------|--------------------|------------|

| JUMP1 |                |      |                     | Jump address       | Fetch      |

Only two fields of this microinstruction are asserted:

| Fields          | Effect                                                     |  |  |

|-----------------|------------------------------------------------------------|--|--|

| PCWrite control | Causes the PC to be written using the jump target address. |  |  |

| Sequencing      | Go to the microinstruction labeled Fetch.                  |  |  |

The entire microprogram appears in Figure 5.46. It consists of the 10 microinstructions appearing above. This microprogram matches the 10-state finite state machine we designed earlier, since they were both derived from the same five-step execution sequence for the instructions. In more complex machines, the microprogram sequence might consist of hundreds or thousands of microinstructions and would be the representation of choice for the control. Datapaths of more complex machines typically require additional scratch registers used for holding intermediate results when implementing complex multicycle instructions. Registers A and B are like such scratch registers, but datapaths for more complex instruction sets often have a larger number of such registers

INTEL - 1012

| Label        | ALU<br>control | SRC1 | SRC2                | Register<br>control | Memory    | PCWrite<br>control | Sequencing |

|--------------|----------------|------|---------------------|---------------------|-----------|--------------------|------------|

| Fetch        | Add            | PC   | 4                   |                     | Read PC   | ALU                | Seq        |

| recen        | Add            | PC   | Extshf              | Read                |           |                    | Dispatch 1 |

| Mem1         | Add            | A    | Extend              |                     |           |                    | Dispatch 2 |

| LW2          | Maa            |      | Search Schercharter |                     | Read ALU  |                    | Seq        |

| LWC          |                |      |                     | Write MDR           |           |                    | Fetch      |

| SW2          |                |      |                     |                     | Write ALU |                    | Fetch      |

| Rformat<br>1 | Func code      | A    | В                   |                     |           |                    | Seq        |

|              |                |      |                     | Write ALU           |           |                    | Fetch      |

| BE01         | Subt           | A    | В                   |                     |           | ALUOut-cond        | Fetch      |

| JUMP1        | 5400           | 13   | 5                   |                     |           | Jump address       | Fetch      |

**FIGURE 5.46** The microprogram for the control unit. Recall that the labels are used to determine the targets for the dispatch operations. Dispatch 1 does a jump based on the IR to a label ending with a 1, while Dispatch 2 does a jump based on the IR to a label ending with 2.

with a richer set of interconnections to other datapath elements. These registers are available to the microprogrammer and make the analogy of implementing the control as a programming task even stronger.

### **Implementing the Microprogram**

Translating a microprogram into hardware involves two aspects: deciding how to implement the sequencing function and choosing a method of storing the main control function. The microprogram can be thought of as a text representation of a finite state machine, and implemented in exactly the same way we would implement a finite state machine: using a PLA to encode both the sequencing function as well as the main control (see Figure 5.43 on page 398). Often, however, both the implementation of the sequencing function, as well as the implementation of the main control function, are done differently, especially for large microprograms.

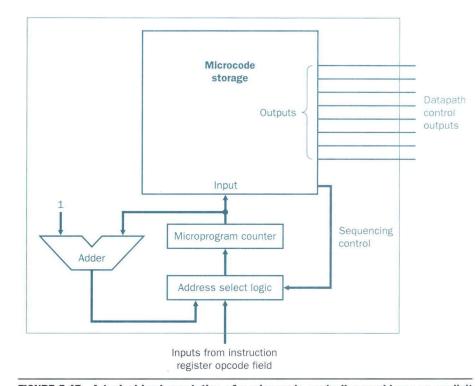

The alternative form of implementation involves storing the control function in a read-only memory (ROM) and implementing the sequencing function separately. Figure 5.47 shows this different way to implement the sequencing function: using an incrementer to choose the next microinstruction. In this type of implementation, the microcode storage would determine the values of the datapath control lines, as well as *how to select* the next state (as opposed to *specifying* the next state, as in our finite state machine implementation). The address select logic would contain the dispatch tables, implemented in ROMs or PLAs, and would, under the control of the address select outputs, determine the next microinstruction to execute. The advantage of this implementation of the sequencing function is that it removes the logic to implement normal

**FIGURE 5.47** A typical implementation of a microcode controller would use an explicit incrementer to compute the default sequential next state and would place the microcode in a read-only memory. The microinstructions, used to set the datapath control, are assembled directly from the microprogram. The microprogram counter, which replaces the state register of a finite state machine controller, determines how the next microinstruction is chosen. The address select logic contains the dispatch tables as well as the logic to select from among the alternative next states; the selection of the next microinstruction is controlled by the sequencing control outputs from the control logic. The combination of the current microprogram counter, incrementer, dispatch tables, and address select logic forms a sequencer that selects the next microinstruction. The microcode storage may consist either of read-only memory (ROM) or may be implemented by a PLA. PLAs may be more efficient in VLSI implementations, while ROMs may be easier to change. Further discussions of the advantages of these two alternatives can be found in section 5.9 and in Appendix C.

sequencing of microinstructions, implementing such sequencing with a counter. Thus, in cases where there are long sequences of microinstructions, the explicit sequencer can result in less logic in the microcode controller.

In Figure 5.47, the main control function could be implemented in ROM, rather than implemented in a PLA. With a ROM implementation, the microprogram is assembled and stored in microcode storage and is addressed by the microprogram counter, in much the same way as a normal program is stored in program memory and the next instruction is chosen by the program counter. This analogy with programming is both the origin of the terminology (microcode, microprogramming, etc.) and the initial method by which microprograms were implemented (see section 5.10).

Although the type of sequencer shown in Figure 5.47 is typically used to implement a microprogram control specification, it can also be used to implement a finite state specification. Section C.4 of Appendix C describes how to generate such a sequencer in more detail. Section C.5 describes how a microprogram can be translated to such an implementation. Similarly, Appendix C shows how the control function can be implemented in either a ROM or a PLA and discusses the trade-offs. In total, Appendix C shows how to go from the symbolic representations of finite state machines or microprograms shown in this chapter to either bits in a memory or entries in a PLA. If you are interested in detailed implementation or the translation process, you may want to proceed to Appendix C.

The choice of which way to represent the control (finite state diagram versus microprogram) and how to implement control (PLA versus ROM and encoded state versus explicit sequencer) are independent decisions, affected by both the structure of the control function and the technology used to implement the control. We return to these issues briefly in section 5.9, but before we do that we need to look at one of the hardest aspects of control: exceptions.

### **5.6** Exceptions

Control is the most challenging aspect of processor design: it is both the hardest part to get right and the hardest part to make fast. One of the hardest parts of control is implementing *exceptions* and *interrupts*—events other than branches or jumps that change the normal flow of instruction execution. An exception is an unexpected event from within the processor; arithmetic overflow is an example of an exception. An interrupt is an event that also causes an unexpected change in control flow but comes from outside of the processor. Interrupts are used by I/O devices to communicate with the processor, as we will see in Chapter 8.

Many architectures and authors do not distinguish between interrupts and exceptions, often using the older name *interrupt* to refer to both types of events. We follow the MIPS convention, using the term *exception* to refer to *any* unexpected change in control flow without distinguishing whether the cause is internal or external; we use the term *interrupt* only when the event is externally caused. The Intel 80x86 architecture uses the word *interrupt* for all these events, while the PowerPC architecture uses the word *exception* to indicate that an unusual event has occurred and *interrupt* to indicate the change in control flow.

Interrupts were initially created to handle unexpected events like arithmetic overflow and to signal requests for service from I/O devices. The same basic mechanism was extended to handle internally generated exceptions as well. Here are some examples showing whether the situation is generated internally by the processor or externally generated:

| Type of event                                 | From where? | MIPS terminology       |

|-----------------------------------------------|-------------|------------------------|

| I/O device request                            | External    | Interrupt              |

| Invoke the operating system from user program | Internal    | Exception              |

| Arithmetic overflow                           | Internal    | Exception              |

| Using an undefined instruction                | Internal    | Exception              |

| Hardware malfunctions                         | Either      | Exception or interrupt |

Many of the requirements to support exceptions come from the specific situation that causes an exception to occur. Accordingly, we will return to this topic in Chapter 7, when we discuss memory hierarchies, and in Chapter 8, when we discuss I/O, and we better understand the motivation for additional capabilities in the exception mechanism. In this section, we deal with the control implementation for detecting two types of exceptions that arise from the portions of the instruction set and implementation that we have already discussed.

Detecting exceptional conditions and taking the appropriate action is often on the critical timing path of a machine, which determines the clock cycle time and thus performance. Without proper attention to exceptions during design of the control unit, attempts to add exceptions to a complicated implementation can significantly reduce performance, as well as complicate the task of getting the design correct.

### **How Exceptions Are Handled**

The two types of exceptions that our current implementation can generate are execution of an undefined instruction and an arithmetic overflow. The basic action that the machine must perform when an exception occurs is to save the address of the offending instruction in the exception program counter (EPC) and then transfer control to the operating system at some specified address.

The operating system can then take the appropriate action, which may involve providing some service to the user program, taking some predefined action in response to an overflow, or stopping the execution of the program and reporting an error. After performing whatever action is required because of the exception, the operating system can terminate the program or may continue its execution, using the EPC to determine where to restart the execution of the program. In Chapter 7, we will look more closely at the issue of restarting the execution. For the operating system to handle the exception, it must know the reason for the exception, in addition to the instruction that caused it. There are two main methods used to communicate the reason for an exception. The method used in the MIPS architecture is to include a status register (called the *Cause register*), which holds a field that indicates the reason for the exception.

A second method is to use *vectored interrupts*. In a vectored interrupt, the address to which control is transferred is determined by the cause of the exception. For example, to accommodate the two exception types listed above, we might define the following:

| Exception type        | Exception vector address (in hex) |  |  |

|-----------------------|-----------------------------------|--|--|

| Undefined instruction | C0 00 00 00 <sub>hex</sub>        |  |  |

| Arithmetic overflow   | C0 00 00 20 <sub>hex</sub>        |  |  |

The operating system knows the reason for the exception by the address at which it is initiated. The addresses are separated by 32 bytes or 8 instructions, and the operating system must record the reason for the exception and may perform some limited processing in this sequence. When the exception is not vectored, a single entry point for all exceptions can be used, and the operating system decodes the status register to find the cause.

We can perform the processing required for exceptions by adding a few extra registers and control signals to our basic implementation and by slightly extending the finite state machine. Let's assume that we are implementing the exception system used in the MIPS architecture. (Implementing vectored exceptions is no more difficult.) We will need to add two additional registers to the datapath:

- *EPC*: A 32-bit register used to hold the address of the affected instruction. (Such a register is needed even when exceptions are vectored.)

- *Cause:* A register used to record the cause of the exception. In the MIPS architecture, this register is 32 bits, although some bits are currently unused. Assume that the low-order bit of this register encodes the two possible exception sources mentioned above: undefined instruction = 0 and arithmetic overflow = 1.

We will need to add two control signals to cause the EPC and Cause registers to be written; call these *EPCWrite* and *CauseWrite*. In addition, we will need a 1-bit control signal to set the low-order bit of the Cause register appropriately; call this signal *IntCause*. Finally, we will need to be able to write the *exception address*, which is the operating system entry point for exception handling, into the PC; let's assume that this address is C0000000<sub>hex</sub>. Currently, the PC is fed from the output of a three-way multiplexor, which is controlled by the signal

PCSource (see Figure 5.33 on page 383). We can change this to a four-way multiplexor, with additional input wired to the constant value  $C0000000_{hex}$ . Then PCSource can be set to  $11_{two}$  to select this value to be written into the PC.

Because the PC is incremented during the first cycle of every instruction, we cannot just write the value of the PC into the EPC, since the value in the PC will be the instruction address plus four. However, we can use the ALU to subtract four from the PC and write the output into the EPC. This requires no additional control signals or paths, since we can use the ALU to subtract, and the constant 4 is already a selectable ALU input. The data write port of the EPC, therefore, is connected to the ALU output. Figure 5.48 shows the multicycle datapath with these additions needed for implementing exceptions.

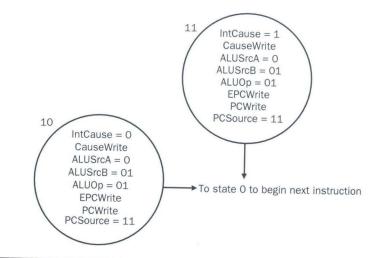

Using the datapath of Figure 5.48, the action to be taken for each different type of exception can be handled in one state apiece. In each case, the state sets the Cause register, computes and saves the original PC into the EPC, and writes the exception address into the PC. Thus, to handle the two exception types we are considering, we will need to add only the two states shown in Figure 5.49.

To connect this finite state machine to the finite state machine of the main control unit, we must determine how to detect exceptions and add arcs that transfer control from the main execution machine to this exception-handling finite state machine.

### **How Control Checks for Exceptions**

Now we have to design a method to detect these exceptions and to transfer control to the appropriate state in the exception states shown in Figure 5.49. Each of the two possible exceptions is detected differently:

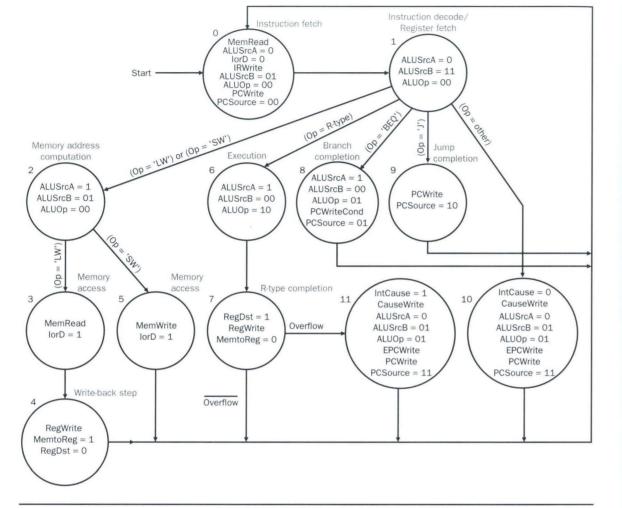

- Undefined instruction: This is detected when no next state is defined from state 1 for the op value. We handle this exception by defining the next-state value for all op values other than 1w, sw, 0 (R-type), j, and beq as state 10. We show this by symbolically using other to indicate that the op field does not match any of the opcodes that label arcs out of state 1. A modified finite state diagram is shown in Figure 5.50.

- Arithmetic overflow: Chapter 4 included logic in the ALU to detect overflow, and a signal called Overflow is provided as an output from the ALU. This signal is used in the modified finite state machine to specify an additional possible next state for state 7, as shown in Figure 5.50.

Figure 5.50 represents a complete specification of the control for this MIPS subset with two types of exceptions. Remember that the challenge in designing the control of a real machine is to handle the variety of different interactions between instructions and other exception-causing events in such a way that

**FIGURE 5.49** This pair of states handles the necessary actions for the two different exceptions we are considering. Each state provides control for three actions: setting the Cause register, getting the address of the offending instruction into the EPC, and setting the PC to the exception vector address. Both state 10 and state 11 represent the starting point for an exception. Control is transferred to one of these two states when an exception occurs. After either state 10 or state 11 is completed, control is transferred to state 0, and a new instruction is fetched.

the control logic remains both small and fast. The complex interactions that are possible are what make the control unit the most challenging aspect of hard-ware design.

**Elaboration:** If you examine the finite state machine in Figure 5.50 closely, you can see that some problems could occur in the way the exceptions are handled. For example, in the case of arithmetic overflow, the instruction causing the overflow completes writing its result because the overflow branch is in the state when the write completes. However, it's possible that the architecture defines the instruction as having no effect if the instruction causes an exception; this is what the MIPS instruction set architecture specifies. In Chapter 7, we will see that certain classes of exceptions require us to prevent the instruction from changing the machine state, and that this aspect of handling exceptions becomes complex and potentially limits performance.

### Real Stuff: The Pentium Pro Implementation

5.7

The techniques described in this chapter for building datapaths and control units are at the heart of every computer. All recent computers, however, go beyond the techniques of this chapter and use pipelining. *Pipelining*, which is the subject of the next chapter, improves performance by overlapping the execution of multiple instructions, achieving throughput close to one instruction per clock cycle (like our single-cycle implementation) with a clock cycle time determined by the delay of individual functional units rather than the entire execution path of an instruction (like our multicycle design). The last Intel 80x86 processor without pipelining was the 80386 introduced in 1985; the very first MIPS processor, the R2000, also introduced in 1985, was pipelined.

5.7 Real Stuff: The Pentium Pro Implementation

Recent Intel 80x86 processors (the 80486, Pentium, and Pentium Pro) employ successively more sophisticated pipelining approaches. These processors, however, are still faced with the challenge of implementing control for the complex 80x86 instruction set, described in Chapter 3. The basic functional units and datapaths in use in modern processors, while significantly more complex than those described in this chapter, have the same basic functionality and similar types of control signals. Thus the task of designing a control unit builds on the same principles used in this chapter.

### **Challenges Implementing More Complex Architectures**

Unlike the MIPS architecture, the 80x86 architecture contains instructions that are very complex and can take tens, if not hundreds, of cycles to execute. For example, the string move instruction (MOVS) requires calculating and updating two different memory addresses as well as loading and storing a byte of the string. The larger number and greater complexity of addressing modes in the 80x86 architecture complicates implementation of even simple instructions similar to those on MIPS. Fortunately, a multicycle datapath is well structured to adapt to variations in the amount of work required per instruction that are inherent in 80x86 instructions. This adaptability comes from two capabilities:

- 1. A multicycle datapath allows instructions to take varying numbers of clock cycles. Simple 80x86 instructions that are similar to those in the MIPS architecture can execute in three or four clock cycles, while more complex instructions can take tens of cycles.

- 2. A multicycle datapath can use the datapath components more than once per instruction. This is critical to handling more complex addressing modes, as well as implementing more complex operations, both of which are present in the 80x86 architecture. Without this capability the datapath would need to be extended to handle the demands of the more complex instructions without reusing components, which would be completely impractical. For example, a single-cycle datapath, which doesn't reuse components, for the 80x86 would require several data memories and a very large number of ALUs.

Using the multicycle datapath and a microprogrammed controller provides a framework for implementing the 80x86 instruction set. The challenging task, however, is creating a high-performance implementation, which requires dealing with the diversity of the requirements arising from different instructions. Simply put, a high-performance implementation needs to ensure that the simple instructions execute quickly, and that the burden of the complexities of the instruction set penalize primarily the complex, less frequently used, instructions.

To accomplish this goal, every Intel implementation of the 80x86 architecture since the 486 has used a combination of hardwired control to handle simple instructions, and microcoded control to handle the more complex instructions. For those instructions that can be executed in a single pass through the datapath (i.e., those with complexity similar to a MIPS instruction), the hardwired control generates the control information and executes the instruction in one pass through the datapath that takes a small number of clock cycles. Those instructions that require multiple datapath passes and complex sequencing are handled by the microcoded controller that takes a larger number of cycles and multiple passes through the datapath to complete the execution of the instruction. The benefit of this approach is that it enables the designer to achieve low cycle counts for the simple instructions without having to build the enormously complex datapath that would be required to handle the full generality of the most complex instructions.

### The Structure of the Pentium Pro Implementation

Both the Pentium and Pentium Pro processors are capable of executing more than one instruction per clock, using an advanced pipelining technique, called *superscalar*. We describe how a superscalar processor works in the next chapter. The important thing to understand here is that executing more than one instruction per clock requires duplicating the datapath resources. The simplest way to think about this is that the processor has multiple datapaths, though these are tailored to handle one class of instructions: say, loads and stores, ALU operations, or branches. In this way, the processor is able to execute a load or store in the same clock cycle that it is also executing a branch and an ALU operation. The Pentium allows up to two such instructions to be executed in a clock cycle, while the Pentium Pro allows up to four.