11 Publication number:

**0 071 727** A1

12

### **EUROPEAN PATENT APPLICATION**

Application number: 82105491.3

f) Int. Cl.3: G 06 F 15/06

② Date of filing: 23.06.82

③ Priority: 24.07.81 US 286426 24.07.81 US 286424 24.07.81 US 286425 Applicant: TEXAS INSTRUMENTS INCORPORATED, 13500 North Central Expressway, Dallas Texas 75265 (US)

- Date of publication of application: 16.02.83

Bulletin 83/7

- (7) Inventor: Budzinski, Robert L., 1106 Edgewood Drive, Richardson Texas 75081 (US) Inventor: Thatte, Satish M., 1304 Elk Grove, Richardson Texas 75081 (US)

- M Designated Contracting States: DE FR GB NL

- Representative: Leiser, Gottfried, Dipl.-Ing. et al, Patentanwälte Prinz, Bunke & Partner Ernsberger Strasse 19, D-8000 München 60 (DE)

(54) Restructurable integrated circuit.

A restructurable integrated circuit, including four 16-bit processors PR0, PR1, PR2, PR3, data and control memories 66 and 78, and external interfaces 72, 73, 74, 75, 76 all mounted on a chip. The processors include reconfigurable connections through a status bus 52, microprogramming capability with dynamic logic array interpretation, and a multi-level flexible interrupt management system, so that the processors PR0-PR3 may be reconfigured programmably to operate independently, in lockstep, or as pipelined processors. All processors PR0-PR3 are connected to data, control, and status busses 56, 14, and 52. In addition, external control, data, and status interfaces 72-76 are also provided, connected through the respective corresponding busses 56, 14, and 52 to each of the processors PR0-PR3. These external interfaces are connected to all of the interconnections which permit reconfigurability among the processors on a chip, and these external interfaces permit coordination of the processors on more than one RIC chip.

0 071

#### RESTRUCTURABLE INTEGRATED CIRCUIT

#### SPECIFICATION

# Background of the Invention

This invention relates to a restructurable integrated circuit which includes multiple 16-bit processors all accessing a common memory, with the interconnections between the processors being alterable in software so that the restructurable IC may be operated in a variety of different computing configurations.

A major difficulty in taking advantage of the possible economies offered by VLSI technology is that few prospective VLSI parts can be produced in sufficient quantity to bring the price down to an attractive level.

In particular, since many applications impose their own particular constraints on processor function, special processors for such applications have been custom-designed, at a necessarily high cost.

It is a particular object of the present invention to satisfy the peculiar processing requirements of many different applications by one common IC chip design, which can therefore be manufactured in large quantities economically.

In addition to a main processor, it is often advantageous to use a dedicated processor for controlling I/O functions (such as CRT display), for memory management, or for specialized arithmetic processing. However, as noted above, the high cost of custom VLSI design has prevented optimal exploitation of the advantages provided by such dedicated processors.

It is a further object of the present invention to provide means for easily configuring a dedicated special-purpose processor by means of a unspecialized common IC.

It is often particularly advantageous, in implementing such dedicated processors, to integrate them on a single chip with a general-purpose processor. However, such structures require further specialization of the design, and are therefore subject to cost disadvantages as discussed above.

It is a further object of the present invention to permit integration of a general-purpose processor with one or more special-purpose processors on a single chip, by means of a general-purpose reconfigurable IC which can 5 easily be manufactured in quantity.

A further disadvantage of custom VLSI design is that, together with cost, yield, and reliability of the finished part normally improve as the manufacturing history of the part proceeds along the "learning curve". However, custom 10 special-purpose designs are normally not manufactured in large enough numbers over a large enough period of time to permit exploitation of the progressive improvement of cost and reliability.

A further object of the present invention is 15 therefore to provide a general purpose part which can be manufactured in large quantity over a long period of time, to permit exploitation of cost yield, and reliability improvements obtained by progress along the "learning curve".

20 Expensive as custom VLSI designs are, they often have the further disadvantage that the gate density is relatively low. This is because, for a part which will be produced in small quantities, it is not economical to spend the additional time and money to optimize the 25 packing density.

Thus, it is a further object of the present invention to provide an integrated circuit which can satisfy the requirements of a custom integrated circuit while retaining a high gate density.

Gate arrays provide an extremely flexible LSI or VLSI part, and gate arrays do satisfy some special functions (such as a high speed multiplier or a cross bar switch) efficiently. However, gate arrays are not very well adapted to supporting programmable systems, and the gate density of a gate array is normally not as high as that of a processor.

Thus, it is a further object of the present invention to provide a restructurable integrated circuit which has a higher gate density than a gate array, and is better adapted to supporting a programmable system.

Where relatively large and complicated systems must be mathematically modelled, it is frequently desirable to have a large array processor, where, even though the data throughput capacity of each processor is relatively low, the total data throughput is extremely high, due to the large degree of parallelism. However, such array processors have to date been relatively expensive, since they were usually constructed as special-purpose systems.

Similarly, it is sometimes desirable to perform a long series of computations on an extremely wide multiple-precision word (e.g., where a complex orbital system must be modeled over a very long period of time.) In this case also, adaptation of existing systems has normally imposed disadvantages of high cost, low speed, or both.

Thus, it is a further object of the present invention to provide a processor in an integrated circuit, such that a number of these integrated circuits can be combined to provide array processing and/or multiple-precision processing cheaply, without custom hardware design.

A further crucial disadvantage of custom VLSI designs is that the design cycle time is unavoidably long, since redesign and testing of hardware is required.

Thus, it is a further object of the present invention to provide an integrated circuit which can be reconfigured for custom applications solely by changes to software and/or firmware.

Additional background references on multiple 30 processing systems, dynamic architecture, and microprocessor architecture generally, include the following: Multiprocessors and Parallel Processing (ed. P. Enslow, Jr. 1974); A. Abd-Alla & A. Meltzer, Principles of Digital Computer Design (1976); C. Mead & L. Conway, Introduction 35 to VLSI Systems (1980); R. Krutz, Microprocessors and Logic Design (1980); G. Myers, Advances in Computer Architecture (1978); Baer, Multiprocessing Systems, 25 IEEE Transactions on Computers 1271 (1976); Thurber & Wald, Associative and Parallel Processors, 7 Computing

Surveys 215 (1975); Kartashev & Kartashev, Dynamic Architectures: Problems and Solutions, Computer Magazine, 26; Kartashev & Kartashev, A Multicomputer July '78, System with Dynamic Architecture, 28 IEEE Transactions on 5 Computers 704 (1979); Kartashev & Kartashev, Super Systems for the 80's, Computer Magazine, November 1980, at 11; and Vick, Adaptable Architectures for Super Systems, Computer Magazine, November 1980 at 17; all of which are hereby incorporated by reference.

It is often advantageous, particularly where unsophisticated users are involved, to design a very high level application language which is tailored to a specific job. However, such application languages, if embodied in software, are normally very slow, and if embodied in 15 hardware, are normally very expensive.

10

30

35

It is thus a further object of the present invention to provide means for economically providing VLSI processors which are adapted to interpret any desired application language.

The many advantages of multi-processor systems have 20 seldom been efficiently exploited, partly because it has always been difficult to train programmers to adapt their programming so as to be optimal on a multi-processor rather than a uniprocessor system. Thus, it is a further 25 object of the present invention to provide a system which is easily reconfigurable between a multiprocessing and a uniprocessing system, so that programmers may gradually accustom themselves to the advantages and requirements of multiprocessor programming.

A further difficulty with the exploitation of multiprocessing systems has been the problem of inflexible hardware structures. Since much of the behavor of a multiprocessor system is determined by its hardware structure, and since all hardware structures yet suggested appear to be optimized for one type of problem but not for another, no multiprocessor hardware structure has yet been achieved which appears to be a truly general-purpose system.

Thus it is a further object of the present invention

to provide a multi-processor hardware structure which is reconfigurable, and which thereby provides a truly general-purpose multiprocessor hardware structure.

A further difficulty which has arisen in many multiprocessor systems is the problem of interprocessor interference, which occurs when more than one processor attempts to access the same area of memory. It is possible to restrict the area of memory which may be accessed by any one processor, but, while this avoids the problems of interprocessor interference, it sacrifices much of the advantage of a multiprocessor system.

Thus, it is a further object of the present invention to provide a multiprocessor architecture which, while permitting every processor to access any area of memory, protects data integrity.

Emulation of microprocessor languages and architectures, and of micro- and minicomputer systems, is at present relatively expensive. If emulation could be made cheaper, e.g. based on a single processing chip, then the cheaper development and testing possible would permit wider use of custom designed application systems, and faster adoption of new innovations.

A further object of the present invention is to provide a single-chip processor capable of versatile and 25 efficient emulation.

It would also be desirable to provide a microprocessor architecture which would permit graceful degradation in the event of failure. Thus, both reliability and yield could be greatly improved, since the 30 first major hardware fault would not prevent function of a chip, but would simply degrade its preformance marginally.

It is a further object of the present invention to provide a microprocessing architecture which provides graceful degradation, rather than catastrophic failure, in the event of hardware fault.

35

Only minor exploration of the advantages of multiprocessor systems including large numbers of processors has betherto been undertaken, because of the expense of multiple processors, the difficulty of

interconnecting them, and the extreme difficulty of specifying appropriate protocols for the interface between processors in a large system.

Thus, it is a further object of the present invention to provide processors which can easily be combined into a multi-processor system including any desired number of processors.

A further difficulty, if IC processors are to be made capable of combination into multi-processor systems, is 10 the provision of additional hardware on chip for interface with external processors. I/O communication, receipt and routing of externally generated interrupts, and interprocessor communication with external processors are functions which will require excess hardware if implemented separately.

Thus, it is a further object of the present invention to provide an external interface which can both handle I/O communications inmediate interprocessor communication.

15

30

It is a further object of the present invention to 20 provide an interrupt managing structure, in each processor, such that interrupts can be used both to govern interprocessor communication and to transmit externally generated interrupts.

When a change in operating function or structure of a 25 processor system is required, logic redesign is not only expensive and difficult, but also time consuming.

Thus it is a further object of the present invention to permit ready alteration of processor operation, at any level, by reprogramming rather than by logic redesign.

It would be highly desirable to have a processor hardware system to which an "architecture compiler" could be applied. Such a compiler would permit programming of the effective architecture of the system, in addition to the other changes normally possible by programming.

35 However, to support such a compiler it is necessary to have hardware which permits selective and programmable reconfiguration of functional interconnections.

Thus, it is a further object of the present invention to provide a processor architecture having the necessary alterable functional structure to support an architecture compiler.

## Summary of the Invention

5 present invention provides for four microprogrammable 16-bit microprocessors on a single Microprogramming capability is provided by a large PLA which is included in each processor. Each of the processors is connected to each of three main buses, 10 namely the status bus, the data bus, and the control bus. Each processor is connected to the status bus by a respective status bus multiplexer, which operates as a programmable interconnect. In accordance with the various configurations of the status bus connections which are 15 thus possible, the processors may be operated independently (e.g. as four 16-bit processors), in lockstep (e.g. as one 64-bit processor), or pipelined. Thus, two major sources of programming flexibility are provided: the microprogramming flexibility provided by 20 PLA interpretation, and the processor reconfiguration flexibility which is provided by the use of the programmable status bus connections and by controlling the instruction streams interpreted by each processor.

To exploit this flexibility in processor control, 25 each chip level instruction is directed to one or more specific processors. Thus, when it is desired to operate the processors in a pipeline mode (where separate processors sequentially perform different operations on a single data stream), each processor is respectively 30 instructed to perform the operation appropriate to its position in the pipeline sequence. In lockstep processing, one processor is designated as the master processor (to control sequencing etc.), and the other lockstepped processors are all controlled simultaneously. 35 These modes of reconfiguration may also be combined, so that, e.g., a chip might be reconfigured to contain four independent 16-bit processors, two pipelined 32-bit processors, one 48-bit processor (three lockstepped 16-bit processors) and one independent 16-bit processor, etc.

Since the control bus may be segmented to carry plural unrelated sequences of instructions, a multilevel interrupt hierarchy is used, arbitrated by a single control store manager, to arbitrate access to the control bus. The external interface controls (including an external interrupt manager, two external status ports and two external data ports) also permit processors on more than one RIC chip to be linked together in the various modes discussed above. In addition, the external interface controls also control access to external memory, I/O's, etc.

A substantial amount of on-chip RAM is provided, which may be accessed by any of the processors. However, each processor also has direct access to a primary 15 allocation of the on-chip RAM. All processors may directly access their respective primary allocations of RAM in parallel, but, to access other portions of RAM, a processor must use the data bus, and therefore such accesses must be arbitrated. Two design expedients 20 prevent hangups and deadlocks: first, 256 priority levels are used coincidence of priority is thereby reduced. Second, all interrupts are sent, and acknowledged, in parallel. Third, any processor which is unable to acquire all resources needed to proceed with execution releases 25 all previously acquired resources while it is waiting for the necessary resources to become available.

In addition to these crucial elements, numerous conventional elements are also used to fully implement the design. For example, each processor includes an ALU, a 30 barrel shifter, a memory mapper, a microsequencer, etc.

The advantages of the present invention include all objects of the invention discussed above, and others which will be obvious to those skilled in the art. For example, the hardware layout time of the RIC chip is reduced by a 35 factor of almost four, since much of the structure (e.g., all four processors) is replicated.

Of course, the processors need not be 16-bit processors but may alternatively be 32-bit, 8-bit, etc. Similarly, the number of processors on a chip may not be

exactly four, but may be three, or any number larger than four. In fact, the maximum number of processors is constrained simply by manufacturing technology, as smaller geometries become practicable, it might be very desirable to include large numbers of processors on a chip. In such case, the interconnections, busses, and protocols would remain the same. Of course, if the processors were other than 16-bit, the width of the respective busses would have to be changed correspondingly.

According to the present invention, there is provided a restructurable integrated circuit, comprising a monolithic substrate having: a plurality of processors; a plurality of busses, each connected to all of said processors; and means, connected to each of said processors, for reconfiguring said processors selectively so that said processors are operable in lockstep or independently.

According to the present invention, there is provided a restructurable integrated circuit, comprising a 20 monolithic substrate having: a plurality of processors; a plurality of busses, each connected to all of said processors; said busses comprising a status bus including a plurality of lines said lines of said status bus including synchronization and arithmetic linkage lines; 25 each said processor comprising a respective status bus multiplexer connected to said respective processor and to said status bus, said respective status bus multiplexer selectively and programmably connecting or interrupting selected lines of said status bus and selectively 30 connecting said respective processor to said status bus, thereby selectively and programmably connecting said respective processor through said status bus to adjacent ones of said processors.

According to the present invention, there is provided a restructurable integrated circuit, comprising a monolithic substrate having: a plurality of processors; a plurality of busses, each connected to all said processors; each said processor comprising a dynamic logic array (DLA) connected to receive commands provided to

35

said respective processor said DLA comprising: an AND matrix; an OR matrix; intermediate lines connecting said AND matrix to said OR matrix; a plurality of input lines, connected to a first one of the AND and OR matrices; and a 5 plurality of output lines connected to the other one of said AND and OR matrices; at least one of said AND and OR matrices of said DLA being arranged in rows and columns to define partitions within said respective matrix; each said partition being selectively arranged to contain a selected 10 number of active elements disposed to implement a desired logical function; and a plurality of control lines, each said control line being connected to selectively enable or disable said active devices in one or more of said partitions, so that said DLA implements a selected logical 15 function in accordance with a state of said control lines; whereby said DLA interprets commands provided to said respective processor selectively in accordance with the state of said control lines.

According to the present invention, there is provided a restructurable integrated circuit, comprising a monolithic substrate having: a plurality of processors; a plurality of busses, each connected to all of said processors; a RAM memory, said RAM memory comprising a plurality of RAM memory modules; said busses comprising a data bus including a plurality of lines; and a plurality of bus control units, each said bus control unit being connected to one of said processors, to one of said RAM memory modules, and to said data bus, said bus control unit selectively connecting said processor to said data bus or directly to said corresponding RAM memory module.

According to the present invention, there is provided a restructurable integrated circuit, comprising a monolithic substrate having: a plurality of processors; a plurality of busses, each connected to all of said processors; and means for reconfiguring each said processor, so that each said processor selectively and programmably is operated in lockstep with or independently of one or more others of said processors on the same restructurable integrated circuit or on another similar

restructurable integrated circuit.

According to the present invention, there is provided a restructurable integrated circuit, comprising a monolithic substrate having: a plurality of processors; a 5 plurality of busses, each connected to all of said processors; said busses comprising a control bus, said control bus comprising lines for transmitting commands, and also lines for transmitting interrupt signals, each said interrupt signal including bits indicating a priority 10 and an interruptee processor among said processors, wherein one of said interrupt signals initiates each sequence of said commands; wherein each said processor contains an interrupt manager, connected to said control bus, to receive said interrupt signals, and wherein said 15 interrupt manager tests each successive one of said interrupt signals to determine whether said respective processor which includes said interrupt manager is designated by said successive interrupt signal as an interruptee, wherein said interrupt manager stores the 20 priority of the one of said interrupt signals which initiated whichever respective sequence of commands is currently being executed by said processor, and wherein said interrupt manager compares the priority of each successive one of said interrupt signals which is 25 addressed to said respective processor with the priority of said respective interrupt signal which initiated whichever respective sequence of commands is currently being executed by said processor and provides a corresponding context switch output; and wherein each said 30 respective processor also contains a scheduler, connected to said context switch line of said interrupt manager, said scheduler displacing a sequence of said commands currently being executed by said corresponding processor whenever said context switch line indicates that a newly 35 received interrupt signal includes a higher priority level.

## Brief Description of the Drawings

15

20

25

35

The present invention will now be described more specifically with reference to the accompanying drawings wherein:

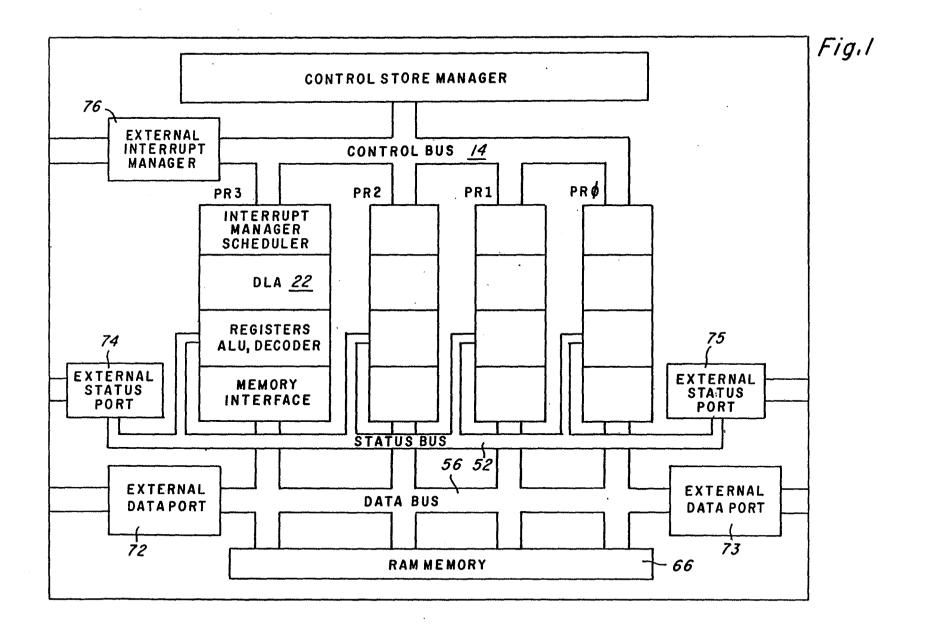

Figure 1 shows a general overview of the restructurable IC according to the present invention;

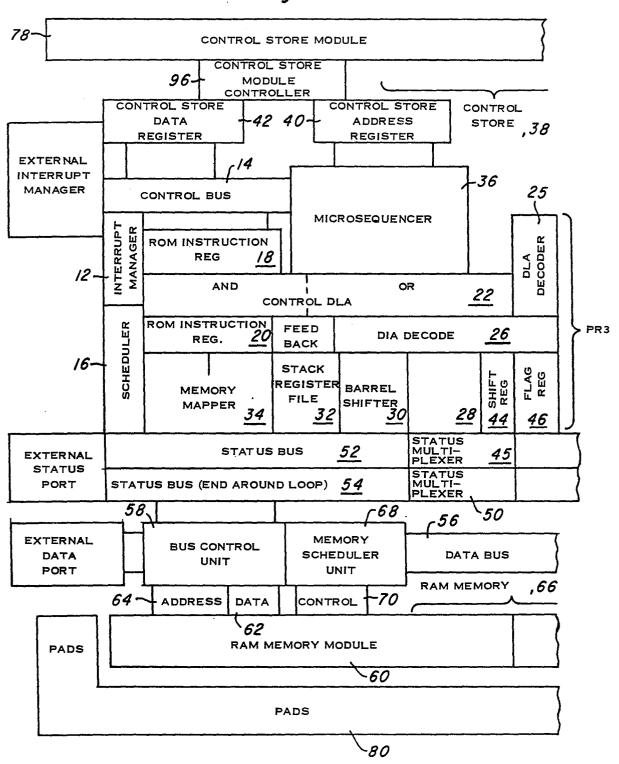

Figure 2 shows a floor plan of a portion of the RIC, including one processor in its entirety and one of each kind of the external interfaces;

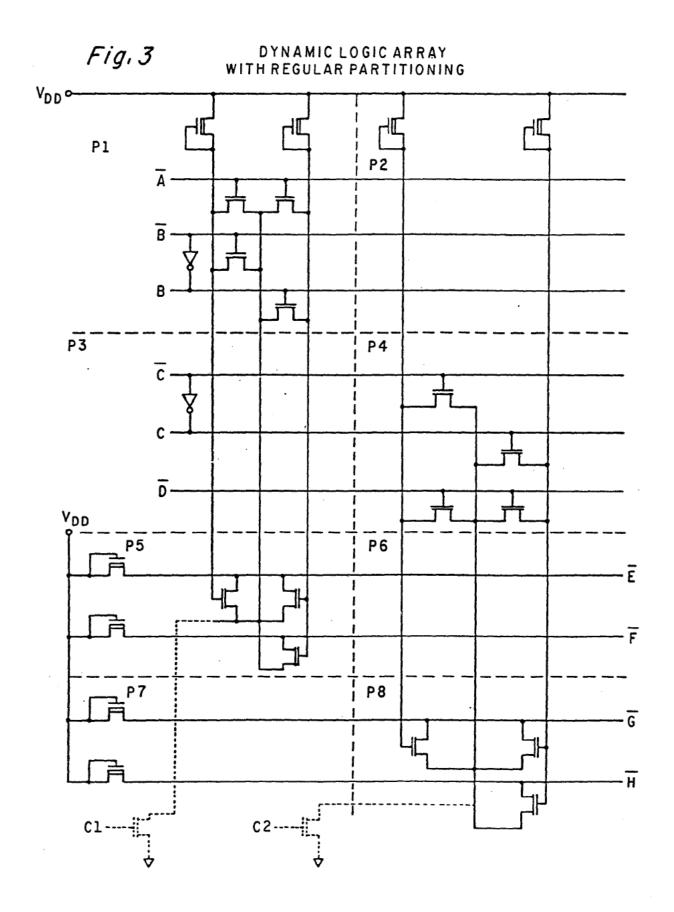

10 Figure 3 shows portions of the AND and OR portions of a DLA, embodied in a NOR gate implementation;

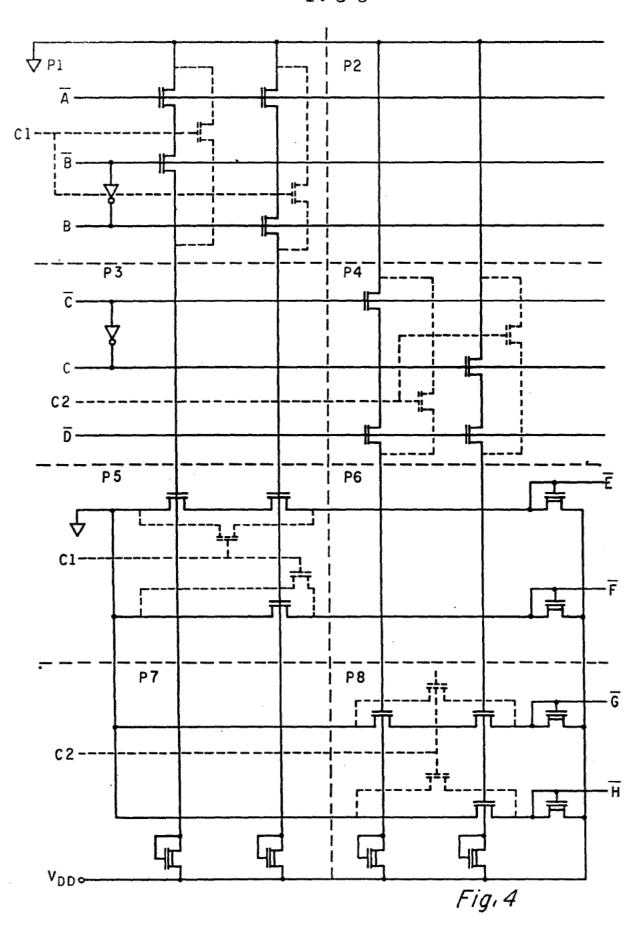

Figure 4 shows portions of the AND and OR matrixes of a DLA embodied in a named gate implementation;

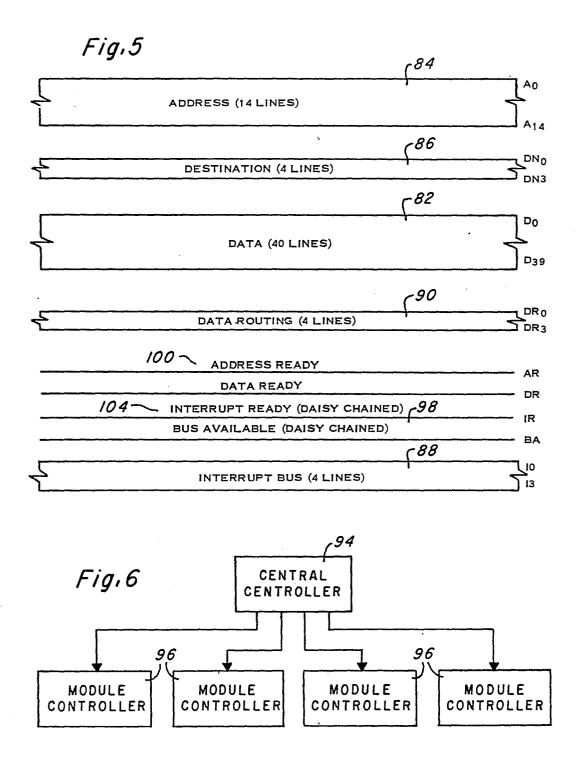

Figure 5 shows the structure of the control bus;

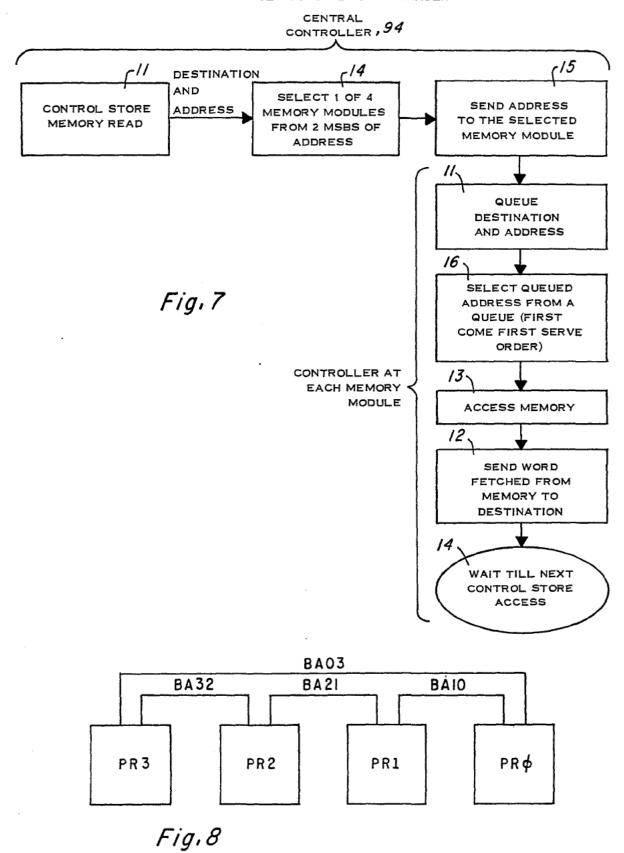

Figure 6 shows the relation between the central control store controller and the four module controllers;

Figure 7 is a flowchart illustrating the operation of the central control store controller and of the respective module controller, where the control store is being accessed;

Figure 8 shows the connection of the daisy chained bus available line;

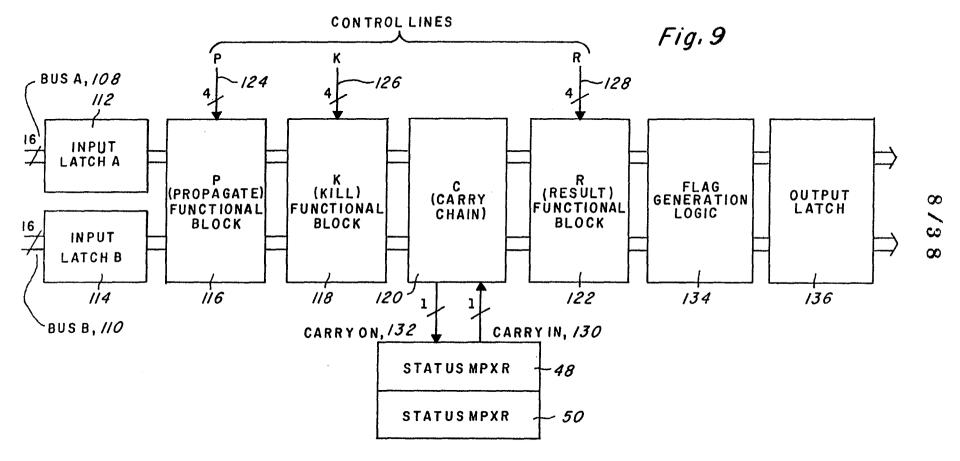

Figure 9 is a schematic diagram of major portions of the ALU within each processor;

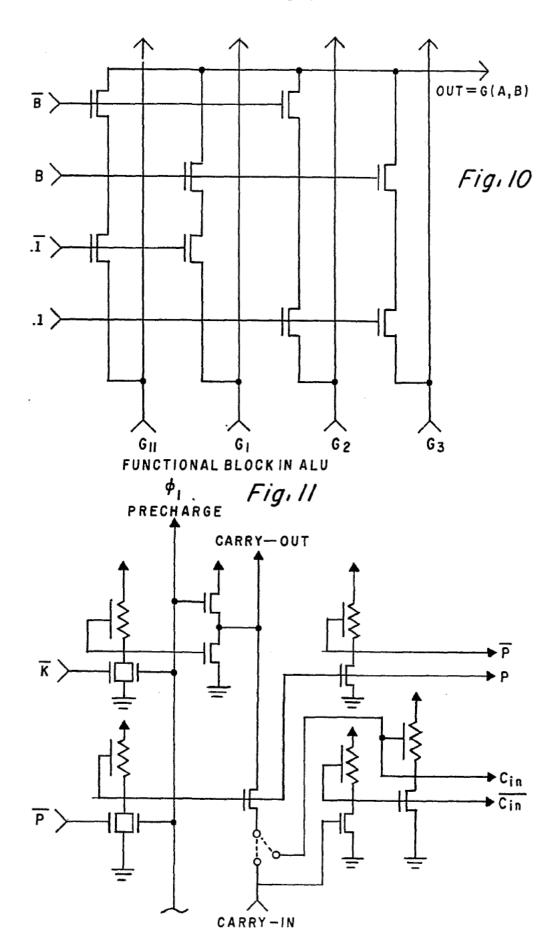

Figures 10 and 11 respectively provide circuit diagrams of portions of functional and carry chain blocks within the ALU in each processor;

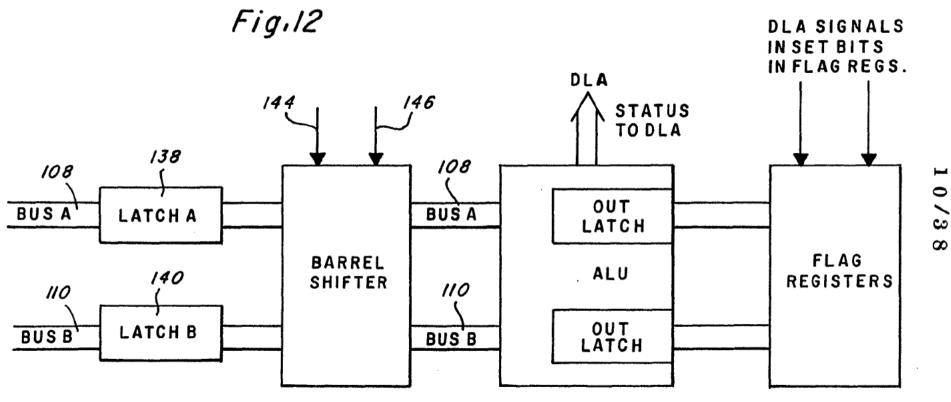

Figure 12 is a flow chart illustrating the structure of the barrel shifter within each processor;

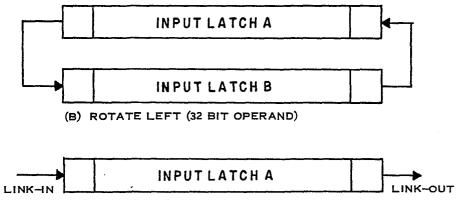

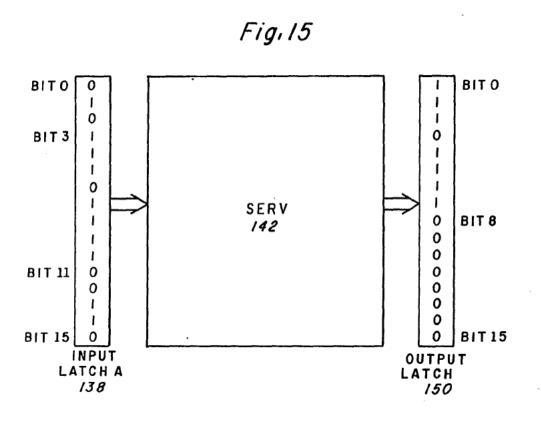

Figures 13, 14(a), 14(b) and 14(c) show examples of shift and/or rotate operations performed by the barrel shifter within each processor;

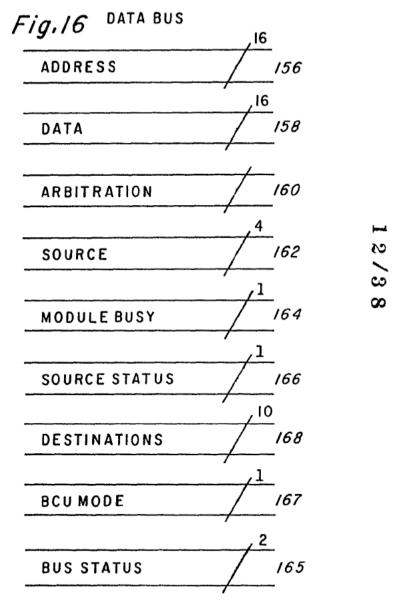

Figure 16 shows the structure of the data bus;

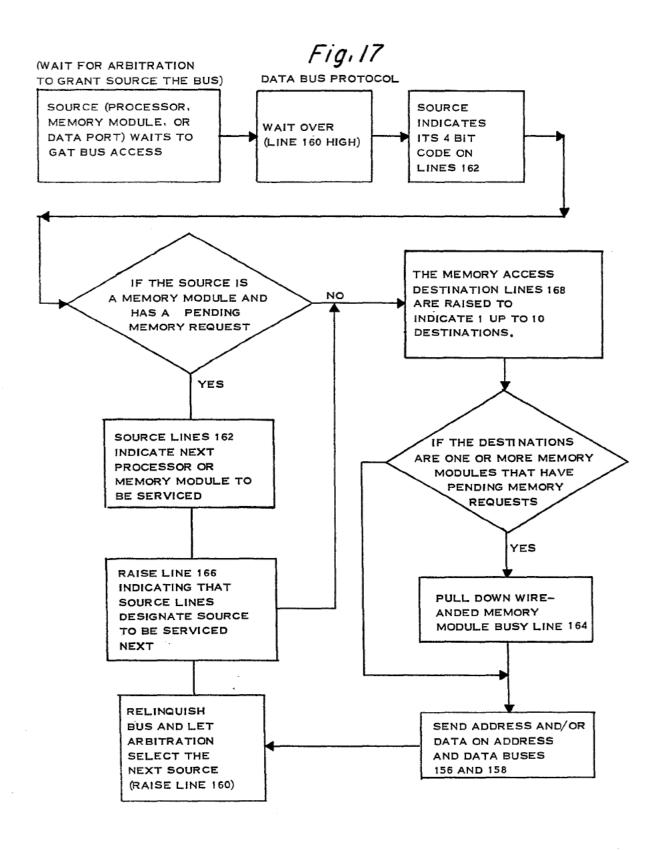

Figure 17 shows the protocol of the data bus;

Figure 18 provides a block diagram of the data path within each processor;

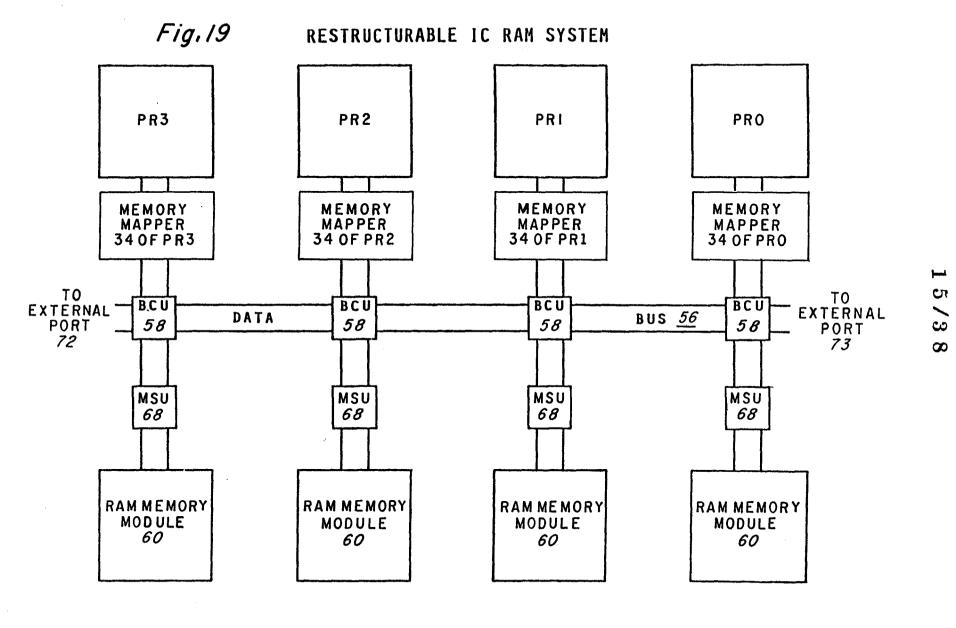

Figure 19 illustrates schematically the internal RAM system of the RIC;

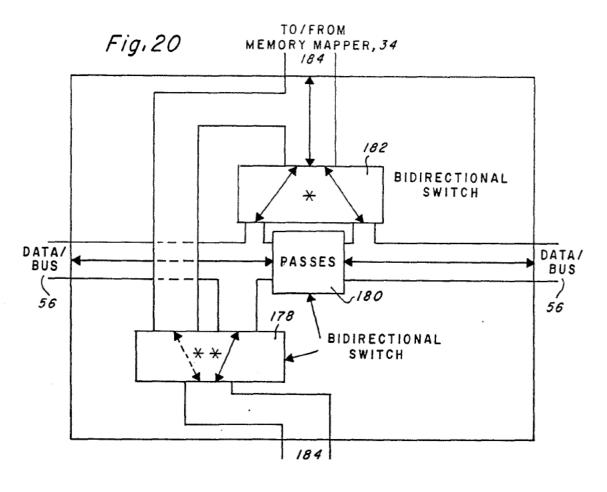

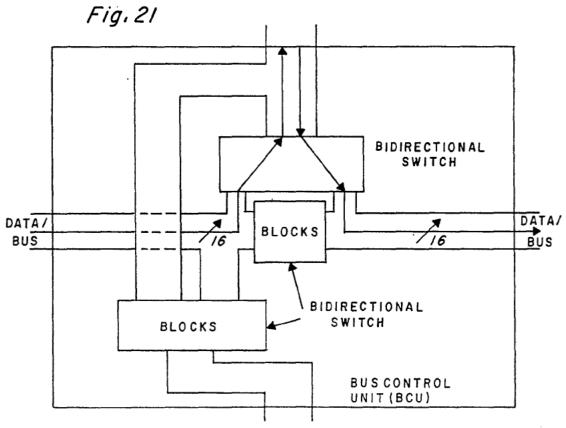

Figures 20 and 21 show the structure and operation of

the respective bus control units;

5

10

15

20

25

35

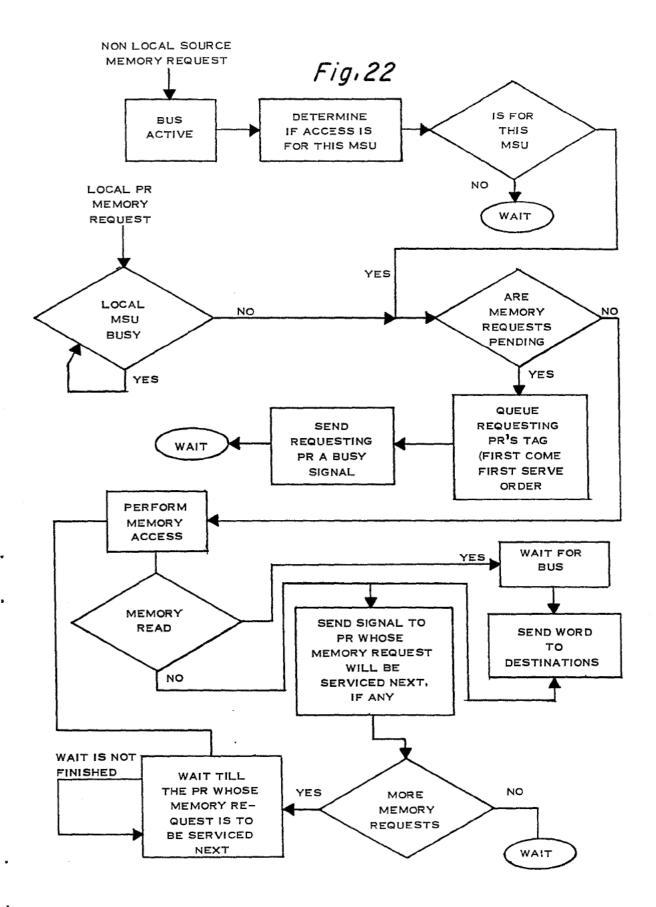

Figure 22 is a flowchart showing the operation of the memory scheduling unit;

Figures 23-25 show the interconnections of the status bus, as effected by the status bus multiplexer, corresponding to different modes of reconfiguration of adjacent processors;

Figures 26, 27 and 28 show schematically the data and command instruction flows within the RIC, in the independent mode, internal lockstep mode, in pipeline mode, respectively;

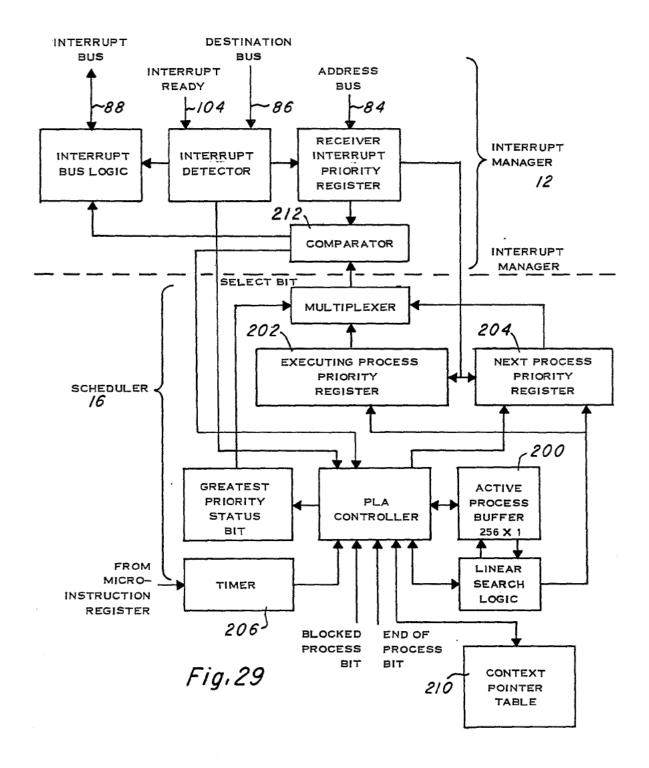

Figure 29 is a block diagram of the scheduler and interrupt manager within each processor;

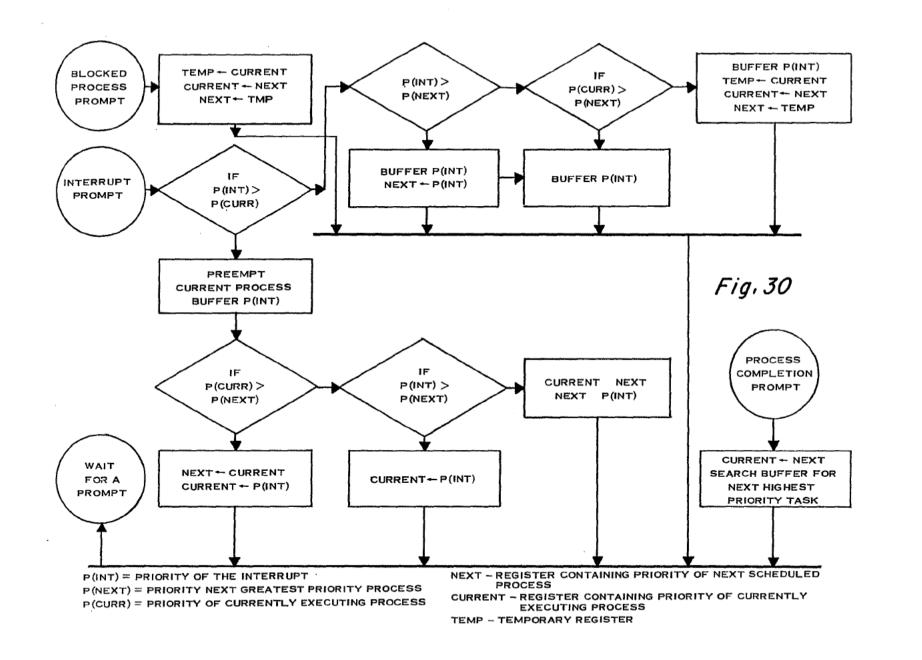

Figure 30 is a flowchart of the operation of the scheduler within each processor;

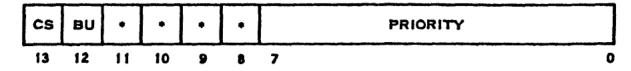

Figure 31 shows the format of the interrupt control word;

Figure 32 shows the format of the control store address lines, when an interrupt is being sent;

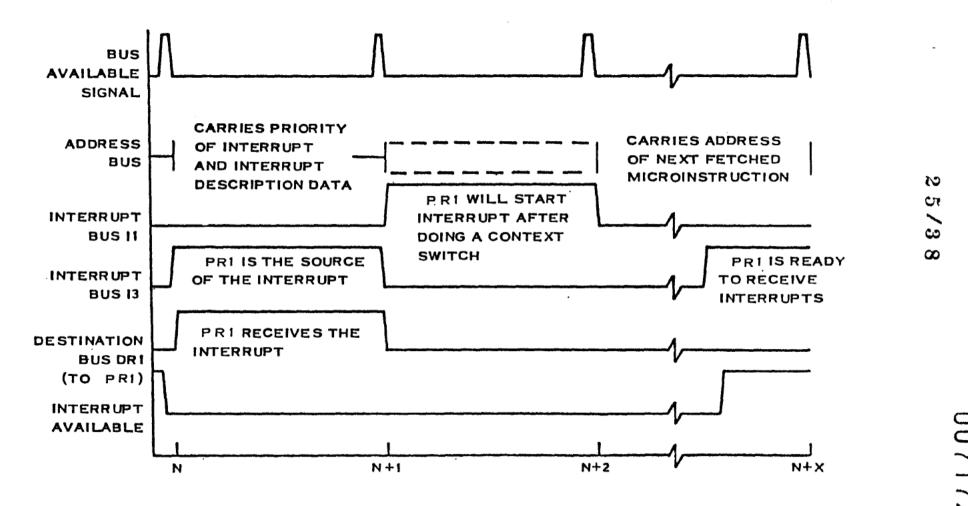

Figure 33 provides an example of interrupt timing, when processor PR3 is interrupting processor PR1;

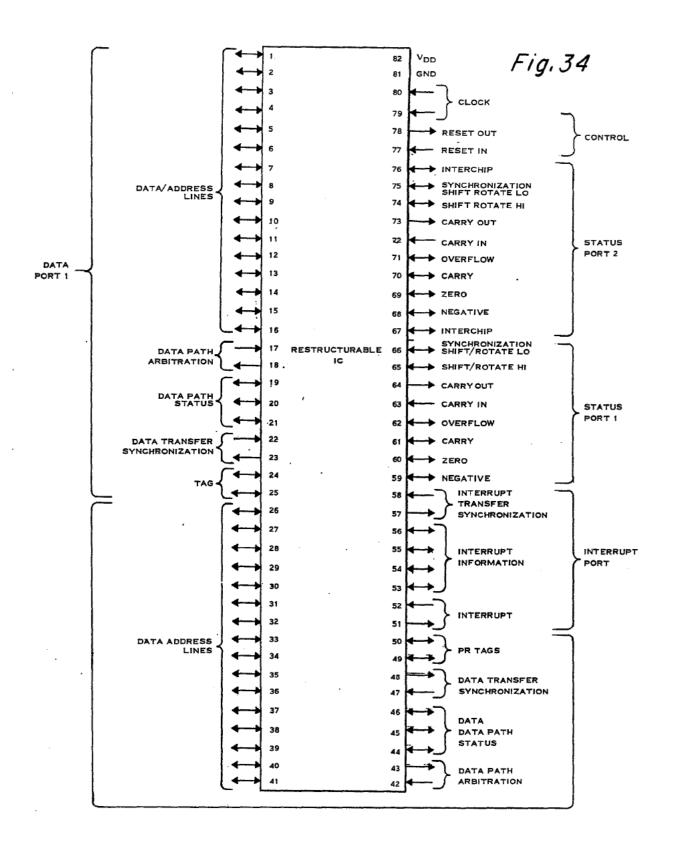

Figure 34 provides a pin diagram of the RIC;

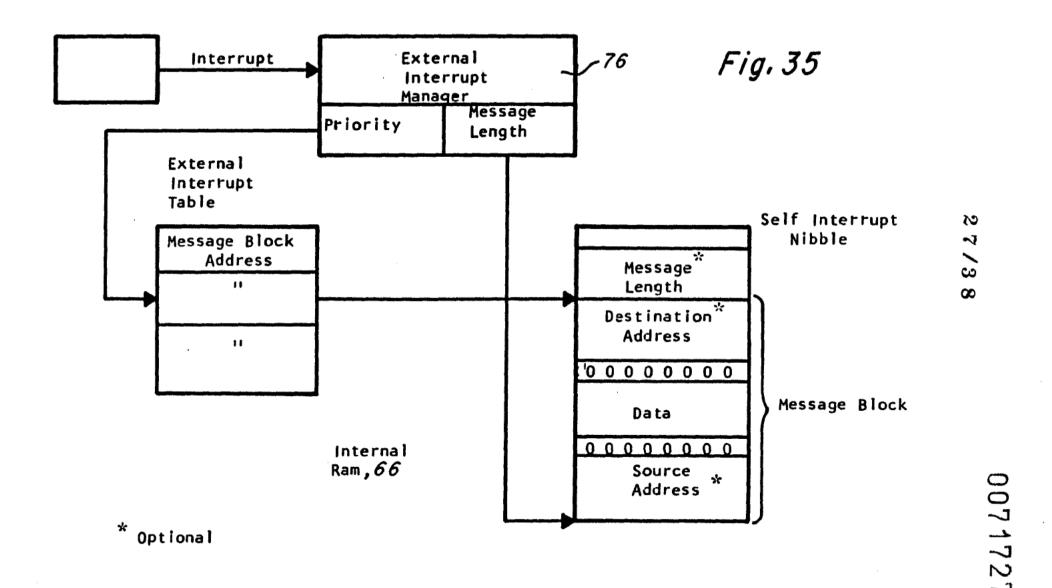

Figure 35 shows generally the internal interrupt data structure;

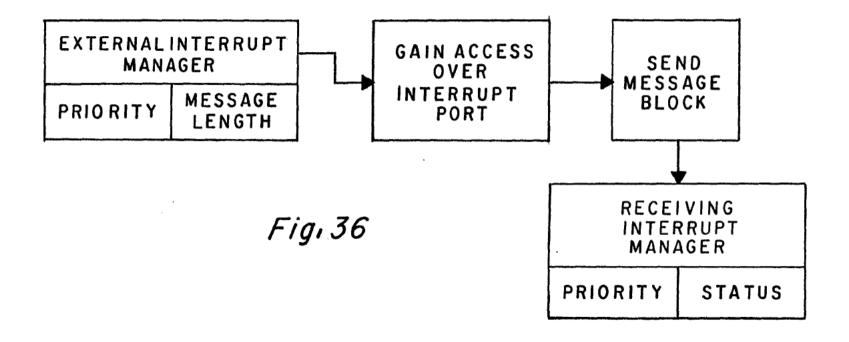

Figure 36 shows the operation of an external interrupt manager, while an interrupt is being sent;

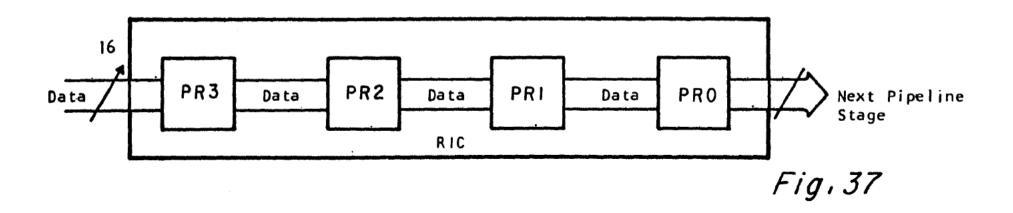

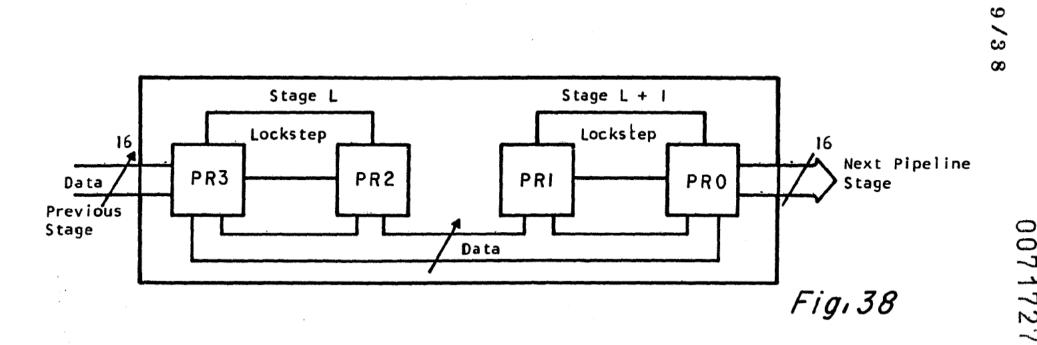

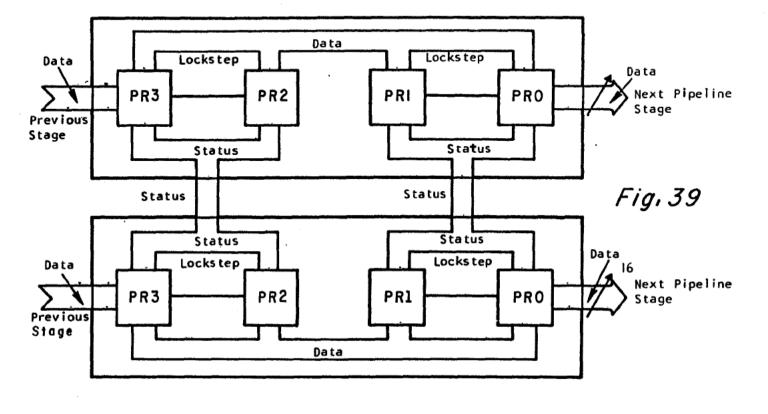

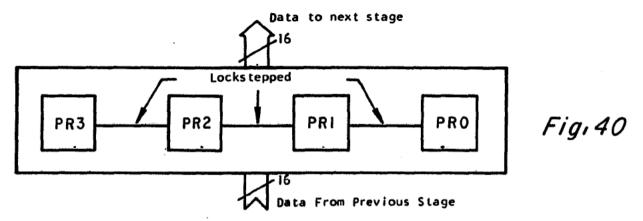

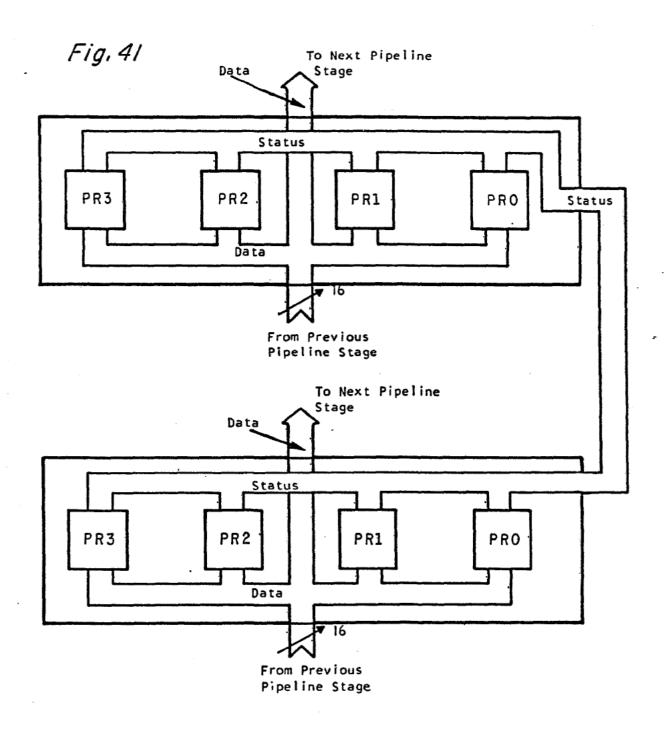

Figures 37-41 illustrate examples of configurations which are attained by linking processors on more than one RIC chip;

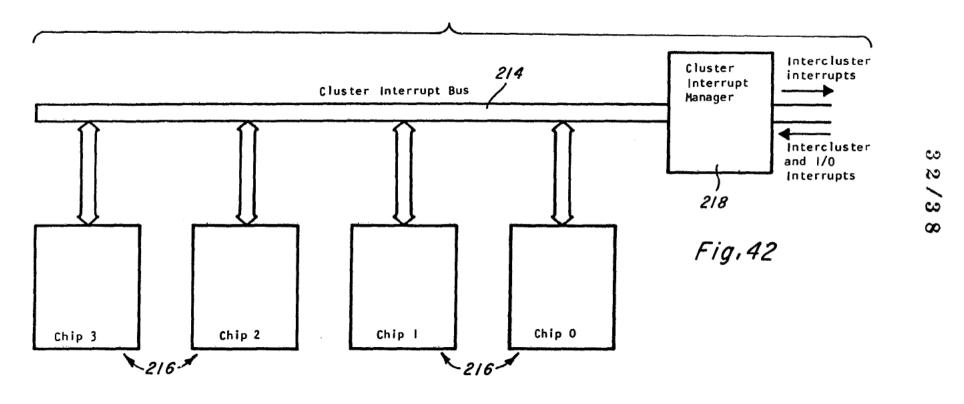

Figure 42 shows the organization of four RIC chips into a cluster;

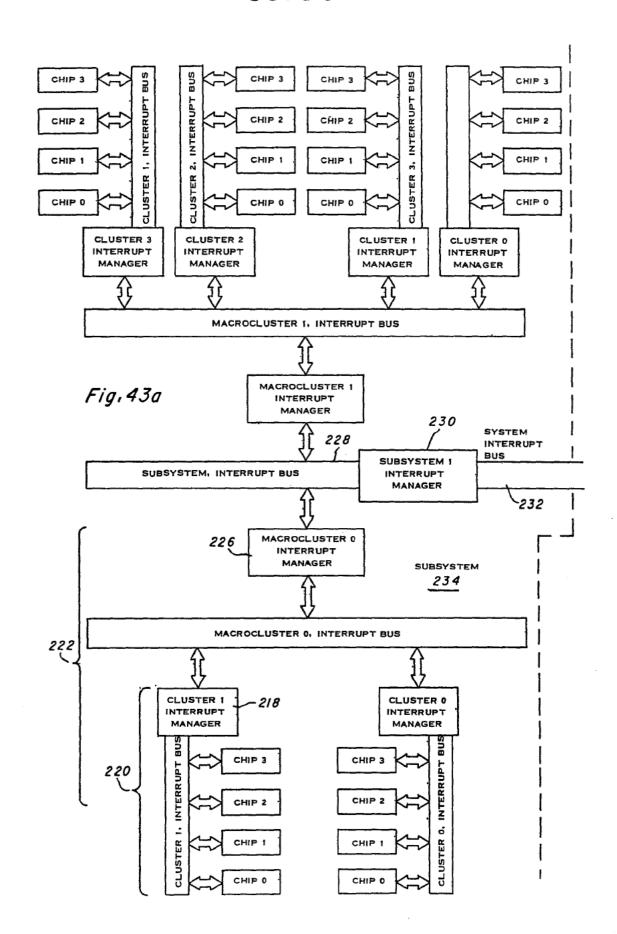

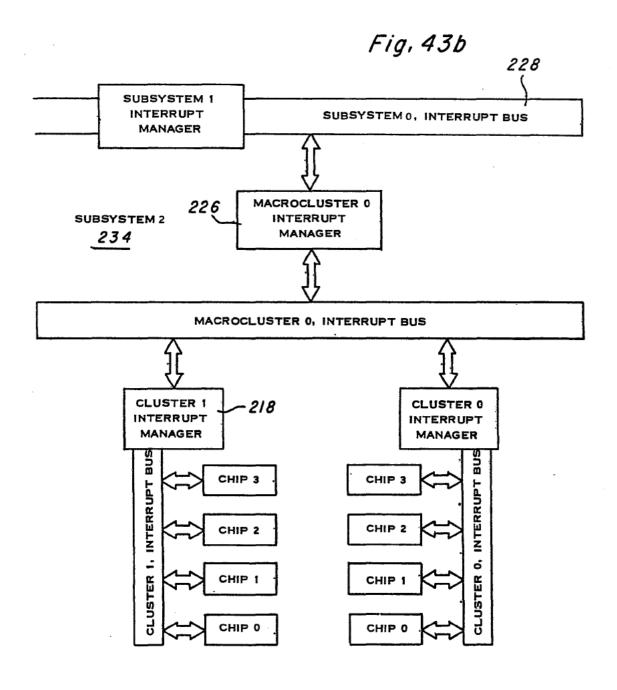

Figure 43 shows a hierarchical system, whereby many RIC chips are combined;

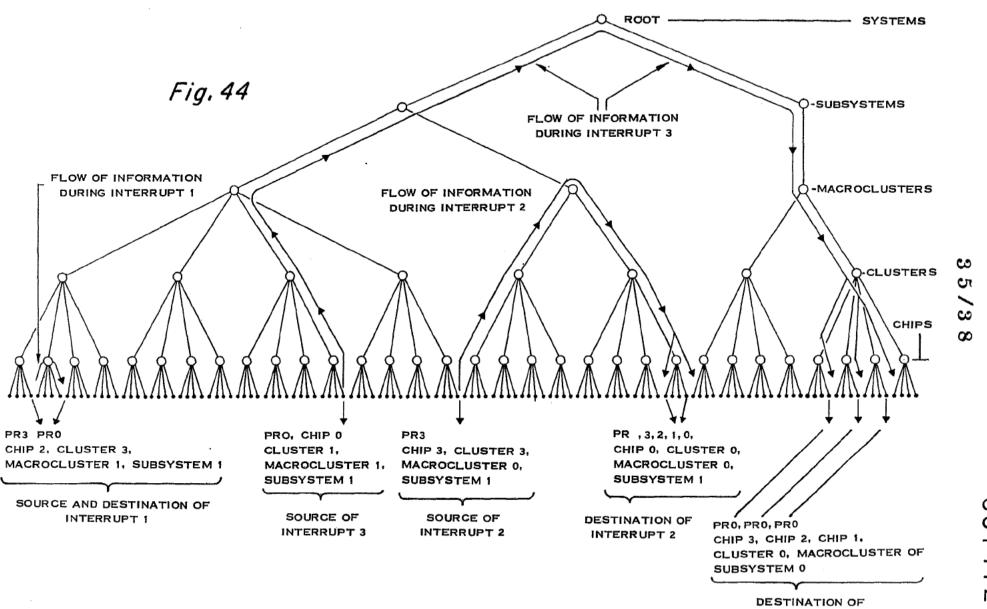

Figure 44 is a true representation corresponding to the multi-chip organization shown in Figure 43;

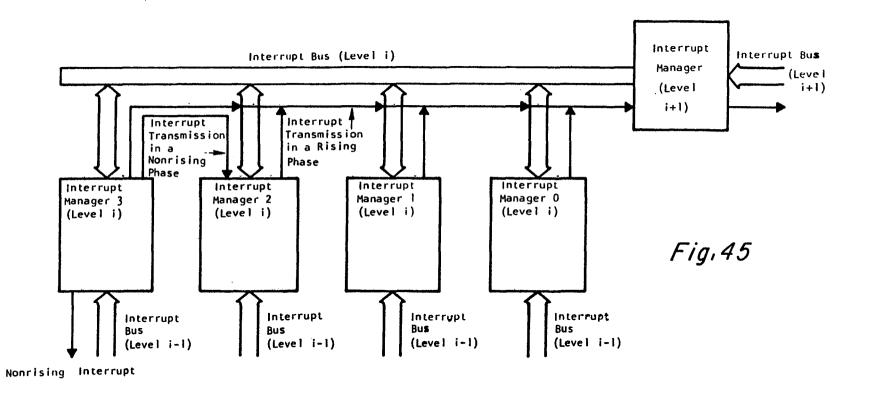

Figure 45 shows generally the operation of an interrupt level manager and busses, at an unspecified level within a hierarchy such as that shown in Figures 43 and 44;

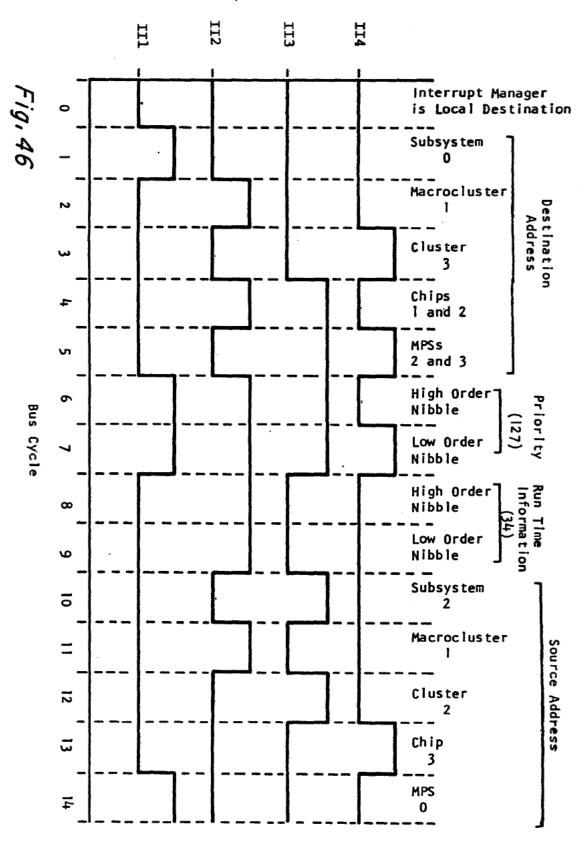

Figure 46 is a timing chart showing the information protocol when an interrupt is in the rising phase, in a multi-chip hierarchy such as that as of Figures 43 and 44; and

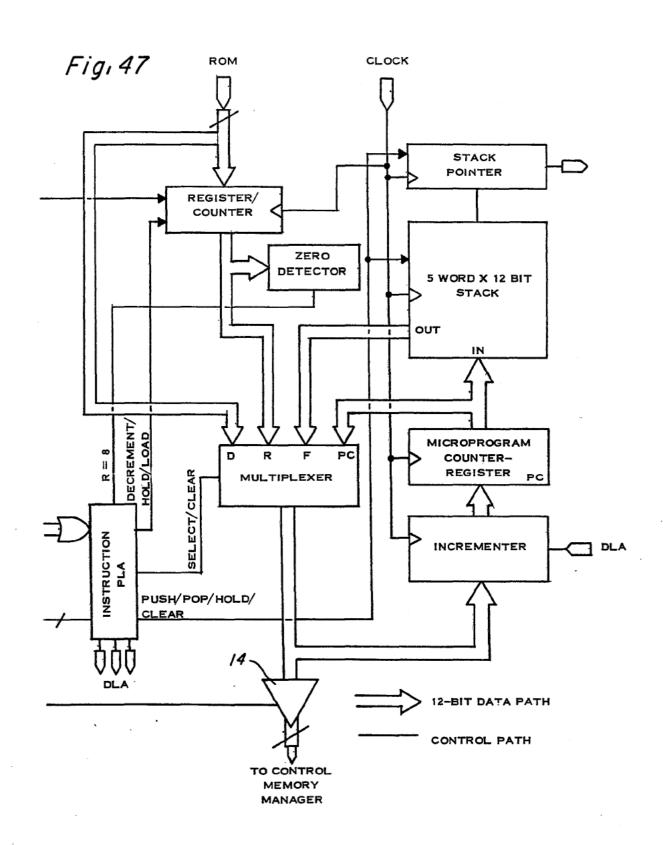

Figure 47 is a block diagram of the microsequencer contained in each processor.

## Description of the Preferred Embodiments

Figure 1 shows a block diagram of the restructurable IC(RIC). Four microprocessors PRO through PR3 are provided on a single chip, and three busses 14, 52 and 56 are 5 provided to interconnect all of the processors. External interfaces 76, 74 and 75, and 72 and 73 are is provided for each of the respective busses, and on-chip RAM memory 66 and control store 38 are also provided. detailed topographic view is provided in Figure 2, which shows a floor plan of a portion of the restructurable IC, 10 including one processor (PR3) in its entirety, one of each type of the external interfaces, and portions of the bus lines and on-chip memories. The interrupt manager 12 of each processor constantly monitors the interrupts which appear on the control bus 14. Only interrupts which are 15 addressed to processor PR3 are recognized by the interrupt manager 12 in PR3. Such interrupts are then successively compared, by the scheduler 16 in PR3, to see whether their priority level is higher than that of the sequence of instructions currently being executed by processor PR3. 20 If this is the case, it is necessary to begin execution of the stream of instructions which the new interrupt has introduced (such a stream of instructions is called a "process"). The scheduler 16 then provides a corresponding output to the DLA 22, which then enables the ROM instruction register 18 or the RAM instruction register 20, so that the control DLA 22 begins to receive the sequence of instructions contained in the "process". The control DLA 22 functions analogously to a PLA, except that 30 its improved structure permits greater packing density, as will be discussed below. Thus the control DLA generates a substantial number of minterms in an AND matrix, and an OR matrix then converts these minterms into selected logical-sum outputs. Adjacent to the control DLA 22 is a feedback block 24, through which a few of the outputs of 35 control DLA 22 are fed back to provide inputs to the DLA. By this means finite state machine capability is provided for the DLA 22, so that the DLA 22 can, e.g., translate one high-level instruction into a sequence of lower-level

instructions. The DLA 22 is connected todecoder sections 25 and 26, which selects outputs of the DLA 22 as hardware commands for the ALU 28, barrel shifter 30, register file 32, memory mapper 34, etc. Outputs of the DLA 22 are also 5 connected to a microsequencer 36, which controls access to the control bus 14 and to the control store 38. The microsequencer 36 can send appropriate signals on the control bus 14 to access the control store 38 through a control store address register 40. Data which is called 10 from the control store 38 is output through a control store data register 42 to the control bus 14, and then input into the ROM instruction register 18 (if the register 18 has been enabled by the interrupt manager 12), and provided as an input to the AND section of the control 15 DLA 22. Operation of the memory mapper 34, register file 32, the barrel shifter 30, the ALU 28, the shift register 44, and the flag register 46 proceeds according to conventional principles of operation well known in the microprocessor art.

A status bus 52, including an end around loop 54, is also provided on the chip. The status bus is connected to each processor through status multiplexers 48 and 50. Each such pair of status multiplexers operates as a programmable interconnect. The lines of the status bus 52 25 and 54 are used to provide synchronization of adjacent processors in the pipeline mode, or to provide complete linkage of adjacent processors in the lockstep mode. the independent mode no such linkage is required. pair of status multiplexers 48 and 50 is programmed to provide the appropriate status bus interconnections each time a new mode is entered.

20

The processor PR3 accesses the RAM memory 66 by way of memory mapper 34. Lines from the memory mapper 34 cross the status bus 52 and 54, and interface with the data bus 56 at a bus control unit 58. The bus control unit 58 operates selectively and programmably, so that the output from memory mapper 34 is either connected directly to the RAM memory module 60 to which processor PR3 has preferred access, through data register 62 and address

register 64, or else is connected through data bus 56 to some other area of on-chip or off-chip memory. If it is necessary to access one of the other three modules (not shown) of the RAM memory 66, the access will be communicated through data bus 56 to the appropriate one of the other three memory scheduler units 68. Each memory scheduler unit 68 schedules memory access requests according to first-come-first-serve, and controls access to the corresponding memory module through a control register 70. In addition, the data bus 56 is connected to external data ports 72 and 73, through which each processor can access off-chip memory.

Similarly, the status bus 52 and 54 is connected to external status ports 74 and 75, so that off-chip processors may be synchronized for multi-chip lockstep and pipeline operations, and control bus 14 is provided with an external interrupt manager 76, so that commands may be sent to and received from off-chip processors.

The control store 38 is divided into modules 78, 20 controlled by respective control store module controllers 96, analogously with the division of the RAM memory 66 into modules 60. Finally, a plurality of pads contact areas 80 are provided at the periphery of the chip, for bonding of external contacts. An 84 pin package is 25 preferred.

The foregoing has provided a summary overview of the function and structure of the restructurable integrated circuit. A more detailed description of the chip, together with suggestions of some possible applications, 30 will now be provided.

The first aspect of the restructurable integrated circuit (RIC) which will be described in greater detail is the control path. A crucial part in the control path is played by the control DLA 22, and the structure and operation of this DLA will be described first. The PLA used in each processor is necessarily large. The preferred embodiment requires a PLA of 40 by 400 by 120. In present production technology, a PLA of this complexity would have an area on the order of 10,000 square mils, which is

uneconomically large. However, process improvements reduce the required area greatly. In addition, considerable size improvement is also obtained by using a DLA (dynamic logic array) in place of the conventional PLA, as discussed 5 above. Preferably mask-programmed DLA's would be used for large-quantity applications, but field programmable (or even electrically alterable) DLA's would also be used for initial development work and to maximize customer flexibility. The exact maximum limit on density depends on 10 the minterm (or maxterm) products desired, but since a typical PLA only has 10% transistor density, improvement by a factor of four in a DLA realization is easily attained through "folding" minterms. A dynamic logic array (DLA) may be thought of simply as a PLA which has 15 been improved to utilize area more efficiently. Alternatively, the DLA may be considered as a PLA which has been made restructurable at the circuit level. allows multiple functions to be embodied in a PLA, subject to the constraint that only one function can be utilized 20 at a time. The DLA improves utilization of area by a factor of 2 to 5. Also, the DLA (with associated multiplexers) allows the inputs and outputs of a PLA to be used for multiple functions instead of only one. The DLA does this by isolating partitions of a PLA in such a way 25 that the circuitry performing only one function is enabled, while the circuitry performing the other functions is not. Selection of an active partition within the DLA 22 is performed by the two decoders 25 and 26. accordance with the activation of the DLA's control lines 30 by these two decoders, the DLA is activated to form a selected logical function. Of course, some partitions of the DLA will not be controlled by these control lines. This concept can be applied to both NOR gate implementations of PLAs and to NAND gate implementations.

As shown in Figure 3, in the NOR gate implementation of a PLA using NMOS technology, the transistors forming gates in the AND matrix along with the transistors forming gates in the OR matrix have all sources common to ground. If the sources for the transistors implementing a

35

particular function are floated, the circuit behaves as if these transistors had been removed, so that the function The basic idea behind the NOR gate DLA is to connect all the transistors implementing a function to a 5 control line, which is grounded when the function is to be performed and is floated when the function is to be disabled. To implement multiple functions in a DLA, the sources of the transistors for each function are connected to a separate control line corresponding to that function. 10 Figure 3 illustrates a typical NOR gate DLA. The ordinary PLA circuitry is drawn in solid lines, and the additional circuitry to implement a DLA is drawn with dotted lines. The DLA is partitioned as shown by the dashed lines, and the various partitions are labelled Pl through P8. 15 control line C1 is at logical 1, the circuitry in partitions Pl and P5 is activated, and the outputs E and F become functions of the inputs A, B, and B. control line Cl was at a 0 level, the E and F outputs would not be controlled as a function of any inputs. 20 Additional circuitry could also be added to the P3 and P7 partitions, in order to implement another function which controlled outputs E and F as functions of inputs A, B and В.

Similarly, the control line C2 in Figure 3 can 25 activate or neutralize circuitry in partitions P4 and P8, and additional circuitry, to provide additional output functions, could be added in partitions P2 and P6.

This circuit can be generalized to any number of partitions, and the partitions can be of varying sizes.

30 Also, the AND matrix can be separately controlled from the OR matrix.

Although Figure 3 shows the DLA as an improvement based on a static gate PLA, for clarity, the above discussion also applies to a DLA which is based on a 35 dynamic gate PLA. The additional peripheral control circuitry required to implement a dynamic gate DLA requires only a very small increase in chip area, particularly where the PLA is large.

Figure 4 shows an NAND gate DLA. The concept of

partitioning a PLA for implementing a selected one of multiple possible functions remains the same. changes is the method of isolating the gates that implement the desired function. For NOR gate 5 implementations, voltage control (of the common sources) is used. The NAND gate DLA is the current dual to the voltage-controlled NOR gate DLA. In the NAND gate DLA, all transistors except those implementing the desired function are shunted by a current bypass, which is 10 controlled by a control line. Only the transistors which implement the desired function are not so shunted. also possible to configure a DLA which generates maxterm rather than minterm products, but the area economies remain the same.

Use of a DLA for interpretation permits the interpretation system of each processor to be rapidly reconfigured, by selecting one of the modes of operation of the DLA. The DLA 22 will preferably be mask-programmed, although more expensive field-programmable structures are also useful for user development.

Thus, the use of the control DLA 22 has provided the sophisticated microprogramming capability which is required in each processor. The path by which macro-instructions are provided to the DLA as inputs will now be traced.

25

35

The DLA 22 can also be used to provide real-time capability, simply by connecting a real-time input to one of the input lines of the DLA, and ANDing that input with 30 the appropriate outputs of the DLA.

The structure of the control store and control bus, and the interrupt control system used, will now be described.

In one embodiment, the central control store is accessible to and can be shared by all four processors. The currently preferred alternative is to allocate the control store 38 among the processors, like the allocation of the data storage among the processors, while still permitting each processor to access any portion of control

The four microsequencers 36 do not permit store 38. parallel access, but simply permit a low average access Of course, the microsequencers 36 can also be constructed (like the bus control units 38) to permit 5 parallel access, but this would impose additional circuit complexity without corresponding advantages. and sharable control store provides the following advantages: the memory space is more efficiently utilized, since code used by multiple processors is not 10 replicated; the amount of control store assigned to each processor can be better tailored to its needs; and field programming is practical because of memory centralization. Of course, to prevent the single channel of access to the central control storage from becoming a system bottleneck, 15 the level of instructions stored in control storage should be sufficiently high that, on the average, each processor requires four or more complete clock cycles to execute each single instruction received from control storage. Since, in current microprocessor software structures, one 20 assembly-language instruction will typically require, on the average, five to ten cycles, the above constraint on the level of instructions should be very easily satisfied.

The microsequencer 36 is an address sequencer intended for controlling the sequence of execution of microinstructions stored in the ROM memory. Besides the capability of sequential access, it provides conditional branching to any microinstruction within its 14-bit range or 16K word range. It also provides the last in and first out stack which provides microsubroutine return linkage and looping capability. There are 4 to 8 levels of microsubroutines. It also has a microinstruction loop counter within the address range. Other details of the preferred embodiment of the microsequencer 36 will be obvious to those skilled in the art, and are shown in greater detail in Figure 47.

The central control store structure implies a central shared control bus. The control bus 14 arbitrates the use of the control store 38 among the four processors PRO-PR3, carries addresses from the processors, and carries

microinstructions from the control store 38 to the processors. The control bus 14 includes 73 lines, which run nearly the length of the chip. Thus, the bus is an expensive resource, and it is desirable to fully use the bandwidth of the bus. That is, the bandwidth of the control bus is approximately matched to the throughput of the control store 38 and the microstore access rate of the processors.

The structure of the control bus 14, according to the 10 currently preferred embodiment, is shown in Figure 5. control bus 14 includes a control data bus 82, an address bus 84, a destination bus 86, an interrupt bus 88, and a data routing bus 90. A control data bus 82 carries microinstructions fetched from the control store 38 to the 15 processors PRO-PR3. This bus is 40 lines wide. The address bus 84 carries addresses generated by the microsequencers 36 in the respective processors to the control store 38, to fetch microinstructions. explained below, the address bus 84 also carries priority 20 information during interrupts. This bus is 14 lines wide, allowing 16K words of address space in the control store The destination bus 86 is used, whenever a processor accesses the control store 38, to indicate which one or more of the processors PRO-PR3 and the external interrupt 25 manager 76 are to receive the data which is stored at the address in control store 38 which is concurrently being accessed. The destination bus 86 is also used during interrupts, to identify which of the processors PRO-PR3 and the interrupt manager 76 are to receive the current 30 interrupt (i.e., the interruptees). The destination bus 86 is 5 lines wide. The interrupt bus 88 is used to transmit It is also used for the source of an interrupt. interruptee processors to signal whether the interrupt is the highest priority task they have on hand, i.e. to signal whether the interruptee processor will accept the interrupt or not. This form of reply is needed to quickly establish (or postpone) processes which require pipelined or lockstep operation. Interrupt bus 88 is 5 lines wide. The data routing bus 90 is controlled by the control store

manager 92, and is used to indicate which processor or processors PRO-PR3 are to receive the microinstruction currently being transmitted on the control data bus 82. The data routing bus 90 is 5 lines wide. Lines DRO-DR3 5 are used to designate the corresponding processor(s) PRO-PR3 as destinations of words fetched from ROM or for interrupts. Line DR4 is used to designate the external interrupt manager as the destination of a fetched ROM word or interrupt.

As shown in Figure 6, the control store manager 92 is 10 organized as a central controller 94 and four control store module controllers 96. Figure 7 is a flow chart showing the operation of the control store manager 92. When the control store manager 92 is activated, it 15 receives the destination and control address information from the buses 86 and 84 respectively. It then selects one of the four control store modules 78 within the control store 38, in accordance with the two most significant bits of the address information which it 20 receives on the address bus 84. The address is then sent to the appropriate module controller 96. The preceding functions in the flow chart of Figure 7 have been performed by the central controller 94, and the remainder of the functions shown are then performed by the 25 appropriate module controller 96. The module controller 96 now queues the address and destination for the requested access, and reads out the control words which have been requested in FIFO order.

Arbitration of the control bus 14 is achieved by 30 means of the bus available line 98, which is daisy chained among the processors PRO-PR3. When one processor gains control of the control bus 14, it uses the control bus for only one full cycle. (One phase to send an address, and a second phase, not necessarily consecutive, to receive the data). During the first phase, the processor which has control of the bus 14 holds the bus available line 98 down. After the address is sent, that processor raises the bus available line 98. Since the line is daisy chained, the high state of the bus available line 98 is immediately INTEL - 1006

35

received by only one processor, which then either accesses the control memory or raises the next link of the daisy chain of the bus available line 98. In the case where one processor is utilizing the control bus and the bus 5 available line is circulated back to it during the cycle, (i.e., no other processor wants to use the control bus) the processor utilizing the bus will trap the signals and reissue it to maintain proper synchronization of the Thus round-robin arbitration of control bus control bus. 10 access is provided. In similarly conventional fashion, the address ready line 100 and the data ready line 102 are used to synchronize communications between an active processors and/or the control store manager 92. Othe data ready line and address ready line are used to disseminate 15 between addresses and data during interrupt transmission.)

Finally, the control bus 14 also contains an interrupt ready line 104, which is also daisy chained. The daisy chaining permits round-robin arbitration among processors seeking to send an interrupt. When a processor 20 gains control of the control bus 14 to initiate an interrupt immediately, it sends a zero down the daisy chained interrupt ready line 104. A processor sending an interrupt can take over the interrupt bus 88 before gaining the control address bus 84. When an interrupting 25 processor gains control of the destination bus 86, it raises the lines within the destination bus 86 that correspond to the processors on the external interrupt manager 76 which are the destinations of the interrupt being originated. After issuing the interrupt, the 30 originating processor signals that it is the source of the interrupt on the interrupt bus 88.

After an interrupt is initiated, other interrupts are inhibited for at least two bus cycles: one for the interrupt to be sent, and one for the replies from the receiving processors (the interruptees) to be received by the originating processor (the interruptor). If only buffering of the interrupt is required, the interruptee's interrupt manager will be able to process the interrupt and be ready to receive another interrupt after one to

four additional bus cycles. If the receivers of the interrupt are to become engaged in a lockstep or pipeline process, i.e., if a context switch is necessary, the interrupt bus 88 is blocked for the time it takes to 5 perform the necessary context switch. The length of the context switch depends on how much context (i.e., register contents ALU status, etc.) within the interrupted processor is to be retained. As will be discussed below, some context switches may require an essentially complete 10 change of processor context, while others may require only a minimal change. The shortest context switch will normally require three or more bus cycles. This delay does limit the bandwidth of interrupt signals, but this approach seems reasonable because interrupts are not 15 expected to take up the full available bandwidth. delay serves the purpose of smoothing out bursty interrupt occurrences without reducing the average rate of the interrupt traffic over the long run.

An interrupt is used to commence each sequence of 20 instructions (each "process"). As discussed above, the interrupt specifies a priority level, and also contains a four bit code conveyed on the data routing bus 90 specifying which processors it is addressed to. If all of the processors addressed by the interrupt are available 25 (that is, have no higher-priority tasks on hand), execution of the sequence of instructions within the process begins. If the instructions to be executed are located in control store 38, they are sequentially read out by the appropriate microsequencer 36. 30 instructions to be executed are located in RAM memory 66, they are sequentially read out by the appropriate memory scheduler unit 68 and bus control unit 58 from RAM memory, and the memory mapper 34 within each affected processor transmits these instructions, through the RAM instruction 35 register 20, to the DLA 22. The DLA 22 can translate these RAM instructions into ROM addresses, and these ROM addresses are then accessed via the microsequencer. Also, the RAM instructions can be directly decoded by the DLA The control words stored in ROM do not contain

processor specification fields, but are merely short bit strings (preferably 32-bit), of which the only fixed format portion is an op code. When the control word which has been called from ROM is returned to the processor's 5 DLA 22, the control word, together with any constants or operands which may have been specified by the instruction received from RAM, is interpreted by the DLA 22. The DLA interprets the remainder of the control word field in accordance with the opcode and the control word as, e.g., 10 an operand field, a constant field, a microsequencer command, a memory interface instruction, a status bus command, destination and priority data (if the command is an interrupt), commands for control of the interrupt manager, the scheduler, the barrel shifter, etc. 15 appropriate portions of the command word are then decoded and provided directly to the appropriate hardware, by the DLA as controlled by decoders 25 and 26.

Of course, this microprogramming interpretation structure also permits use of further stages of interpretation before hardware execution. For example, a command read out from the control store 38 may be interpreted to require execution of another series of instructions from control store 38 or from RAM 66. Moreover, off-chip memory may also be used for instructions. For example, if a single command in an application language is to represent a very lengthy 10 subroutine, the corresponding control word in the control store 38 might be interpreted to command loading of the subroutine in a specified block of RAM memory 66, and subsequently executing the instructions of that subroutine sequentially. Of course, instructions stored in off-chip storage can be fetched and executed through the external interrupt manager 76 and/or the external data ports 72 and 73, as will be discussed in greater detail below.

Further information regarding the interrupt protocols will be provided below, where reconfiguration of the RIC into different modes of operation is discussed in connection with the status bus operation. At this point, further details regarding the structure of each processor PRO-PR3 will be provided.

As seen in Figure 2, each processor includes, in 25 addition to the DLA 22 and associated decoders 25 and 26, feedback lines 24, and instruction registers 18 and 20, an interrupt manager 12, a scheduler 16, a memory mapper 34, a stack/register file 32, a barrel shifter 30, an ALU 28, a shift register 44 and a flag register 46. 30 latter elements are conventional, but will be discussed in greater detail for convenience and clarity. For example, Figure 9 shows greater detail of the ALU 28. Two busses 108 and 110 are provided as inputs from other blocks of the processor, e.g. barrel shifter 30. The busses are connected via input latches 112 and 114 respectively, to a P (propagate) functional block 116, a K (kill) functional block 118, a C (carry chain) block 120, and an R (result) functional block 122 successively. The propagate block is controlled by P control lines 124, the kill block is

controlled by K control lines 126, and the result block is controlled by R control lines 128. These control lines are provided to the ALU 28 from the DLA 22. In addition, a carry in line 130 and a carry-out line 132 are provided, 5 to connect the C block 120 to the status multiplexers 48 and 50 (the operation of the status multiplexers 48 and 50 is discussed in greater detail below in connection with the status bus protocol). The output of the R block 122 is a dual bus, which is provided through a flag generation 10 logic 134, to an output latch 136. The flag generation logic 134 computes status and error information to provide a program status word through the DLA. The flag generation logic 134 (in the DLA 22) is connected to the flag register 46, and the output latch 136 is connected to 15 the shift register 44. The shift register 44 is, in turn, connected through busses A and B (108 and 110) to the register file 32 or, through memory mapper 32, to the bus control unit 58, so that the output of the ALU may be transmitted on the data bus 56, or stored for future 20 operation within the processor.

Figure 10 shows the component-level architecture of one portion of one of the functional blocks 116, 118, or 122 within the ALU 28. Figure 11 shows the structure of one portion of the carry chain block 120 within the ALU 28. Further references on microprocessor architecture include, for example, Osborne and Associates, which is hereby incorporated by reference.

Figure 12 shows a schematic diagram of the data path. Input signals are provided on busses 108 and 110, to which are connected respective input latches 138 and 140. These latches provide input to a barrel shifter 30. The barrel shifter 30 is controlled by control lines 144, and parameter inputs 146, which are both supplied by the DLA 22. The parameter inputs 146 provide values for, e.g., shift count and for extraction boundaries. The barrel shifter 30 provides outputs, to bus A and bus B. The ALU generates arithmetic status signals such as carry, overflow, negative and/or zero. The ALU also generates other trap signals such as integer overflow, decimal

digit carry etc. These signals are sent to the DLA which performs logical operations upon them to generate signals which set bits in the flag register. This mechanism generates the setting of status signals for the 5 circulation of a computer architecture for example.

Figure 13 illustrates the terminology of shift operations formed by the barrel shifter 30. Conventionally, a shift left is used to designate a shift toward the most significant bit; i.e., the most significant bit is the leading bit for a shift left. Similarly, the least significant bit is the trailing bit for a shift left, and is the leading bit for a shift right. Figures 14a,b, and c illustrate some further examples of shift operations. Figure 14a shows a shift left, where the trailing bit is filled with a zero, and the leading bit is discarded.

Figure 14b illustrates a rotate left operation, the significant bit of input latch A (138) is mapped into the least significant bit of input latch B (140), the most significant bit of input latch B (140) is mapped into the least significant bit of input latch A (138), and the other bits are shifted accordingly. Figure 14b illustrates a one-bit rotate operation, but a rotate operation may move up to 16 bits, right or left, within one clock cycle in the barrel shifter.

Figure 14c shows a shift and link operation, where the input latch 138 is shifted right, a link-in line 152 provides the new contents of the trailing bit, and the contents of the leading bit are output over the link-out line 154. In the preferred embodiment, the link-in and link-out lines 152 and 154 are provided by input latch B (140), so that multi-bit shift-and-link operations may be performed, but separate link-in and link-out lines may alternatively be provided.

Figure 15 illustrates the extraction operation which is performed by the barrel shifter 30. In the illustrated operation, the barrel shifter 30 has been commanded to extract bits 3-11 of the input, and these bits are then provided as the leading bits at output latch

35

150. The circuitry required for an barrel shifter 30 to perform these functions as well known, and is illustrated, for example, in Mead and Conway, Introduction to VLSI Systems, previously incorporated by reference.

The memory mapper 34 is merely a familiar structure which forms a function familiar in processor architecture. A virtual address received by the memory mapper 34 is compared in parallel, by an associative memory operation, with 16 stored virtual addresses. If the virtual address 10 received matches one of the stored virtual addresses, the corresponding local address is used to fetch the desired word from local memory. If there is no match, the virtual address will be translated through a table lookup (such as a page table lookup) to determine the real address, and 15 can optionally be loaded into one of the register files. By this means the memory mapper 34 distinguishes between memory units stored internally and memory units stored The memory mapper 34 thus permits hashing externally. table searches, and the hashing function used to select a 20 location in the hash table is firmware programmable. hashing table is implemented as a multiway set associative The output of the hashing function points to multiple locations to be searched in parallel. desired address does not match the comparison made at the 25 multiple locations in the hash table, no other probes are necessary since the desired address is (by design) not in the table. Thus this mapping function maps memory units of varying size. If the hashing function is used to support a cache, the hash table entries will point to memory units 30 of tens of bytes. If the hashing function supports a virtual memory translation lookaside buffer, the memory units will be 512 bytes to 2,048 bytes typically. appropriate structure for the memory mapper would be that contained in National Semiconductor chip No. 16082.

The interrupt manager 12 directly receives all interrupts transmitted over the control bus 14. (The interrupt protocol is discussed in greater detail below.) The interrupt manager tests the appropriate destination bit in each interrupt, to see whether its own processor is

35

an interruptee, and, if the address is appropriate, compares the priority of the new interrupt with the priority of the process currently being executed. If the new process has higher priority, the interrupt manager accepts the interrupt, and otherwise the interrupt manager 12 rejects the interrupt by pulling down the wire-ANDED line.

The scheduler 16 buffers interrupts by priority in a 256 bit shift register. When a process is active, the 10 scheduler 16 scans through the shift register to find the process with the next highest priority. When the current process is finished or is timed out, the scheduler 16 uses the priority of the next highest priority process to access a table which contains a pointer to that process's context. The appropriate context is then recalled from a stack/register file 32, from RAM memory 66, or from external memory.

Figure 18 provides a general overview of the data path discussed above. Busses A and B (108 and 110) flank 20 the principal components of the data path, namely the stack/register file 32, the barrel shifter 30, the ALU 28, and the flag and shift register sets 44 and 46. addition, the left port 170 is provided at the input and output ends of the data path. Although not in the 25 preferred embodiment, there is alternative provision for a right port 172. This right port of one processor can be used to connect to a left port of an adjacent processor. For example, the right port of processor PR3 can be connected to the left port of processor PR2. A literal 30 register 174 is also provided for generating constants. Input is provided to the left port 170 from the memory mapper 34, and the output from the right port 172 is also routed through the memory mapper 34.

The stack/register file 32 must be a dual port 35 register file, in order to adequately utilize the two busses 108 and 110. Otherwise the register file 32 is completely conventional.

The organization of the data bus 56 will now be described, together with the operation and structure of the RAM memory 66, the bus control unit 58, and the memory scheduler unit 68.

Figure 16 indicates the structure of data bus 56. The data bus 56 includes 16 address lines 156, 16 data lines 158, a round robin arbitration line 160, 4 source lines 162, a module busy line 164, a source status 166 and a BCU mode line 167. The separate address and data 10 lines 156 and 158 permit a data access operation to take place within one single bus cycle, at least where the speed of memory access permits this, as where the on-chip RAM memory 66 is being accessed. Alternatively, the address and data lines 156 and 158 could be multiplexed to A round robin arbitration line 160 is daisy 15 save space. chained among the four processors PRO-PR3, the four memory modules 60, and the external data ports 72 and 73, so that access to the data bus 56 is efficiently arbitrated. four source lines 162 specify the processor, module, or 20 data port which is the source of the memory access request currently being conveyed. Alternatively, in accordance with the status of control line 164, the source lines 163 may be used to indicate which memory module 60 is going to be serviced next by the memory module. 25 10 destination lines 168 indicate which processor, module, or port will receive the data. The source status line 166 shows (if low) that the source lines 162 indicate the processor, module, or data port whose memory request will be serviced next. The high state of source status line 30 166 simply shows that source lines indicate the current source. There are also two bus status lines 165 to indicate if the bus is idle, used for reading memory or used for writing memory.

The flowchart of Figure 17 provides further clarification of the utilization of the lines within the data bus 56. Once any source (a processor PRO-PR3, a RAM memory module 60, or a data port 72 or 73) receives access to the data bus (i.e., once that source receives a high signal on the daisy-chained line 160), the source

35

indicates its four bit code on lines 162. If the source is a RAM memory module 60, and if the corresponding memory scheduler unit 68 has a memory request pending, the source lines 162 are driven to indicate which processor or memory module will be serviced next, and line 166 is raised. After this, or in any case if the source was not a memory module subject to a pending memory request, the memory access destination lines 168 will be raised to indicate any combination of 10 destinations for the data to be read out. An interlock is also provided to protect data integrity: if the destinations include one or more RAM memory modules 60 which have pending memory requests, the busy line 164, which is wire-ANDED, is raised to avoid concurrent reading and writing in the same memory space.

Figure 19 provides a general overview of the organization of the RAM system in the RIC. Each processor PRO-PR3 is connected, via its memory mapper 34, to a bus control unit (BCU) 58, which provides interface with the data bus 56. Each BCU 58 is also connected to a corresponding memory scheduler unit (MSU) 68, and each BCU 58 and MSU 68 are both connected to a corresponding RAM memory module 60.

When a processor accesses its own memory module 60, the processor is directly connected through its BCU 58 to The MSU 68 indicates whether there are 25 its MSU 68. pending memory requests. If there are no pending memory request, the access occurs immediately. If accesses are pending, the MSU 68 queues a tag indicating which processor or data port first requested memory service. 30 An MSU 68 queues the request according to a first come first served scheduling discipline. When a particular request reaches the head of the queue, the MSU 68 signals this to the processor or data port. The processor or data port then reissues its request, and the memory access is 35 performed immediately. When a processor accesses a memory module other than its own, the bus control units 58 must be configured to permit communication via the data bus 56. Thus, for example, if processor PR3 is to access the memory module 60 corresponding to processor PR1, the bus INTEL - 1006

control unit 58 corresponding to PR3 must be configured to connect processor PR3 to the data bus 56, the BCU 58 corresponding to processor PR2 must be configured to transmit communications along the data bus 56, the BCU 58 5 corresponding to the processor PRI must be configured to connect the data bus 56 (in the direction of processor PR3) to the RAM memory module 60 which corresponds to the As discussed above, the processor must processor PR1. first wait for access to the shared data bus 56, which is 10 scheduled in round robin order. After a processor gains access to the bus, it transmits the memory information and a destination tag indicating the destination memory module. Any memory module can have at most six requests pending, since each processor or data port can have only 15 one memory request pending at a time. The memory interface of each processor contains circuitry to monitor the memory control signals which are communicated over the data bus 56. This function is performed by the memory mapper 34.

20 The internal RAM memory of the RIC is preferably 16K bytes of dynamic RAM, in an NMOS RIC (using CMOS realization of high-power components such as bus drivers) with a minimum geometry feature of one micron (lambda = .5 microns).

25 Thus, the BCUs 58 play a crucial role in permitting all processors to access the respective adjacent memory module 60, while also permitting each processor to access any other remote memory module over the data bus 56. structure of a BCU is shown in Figures 20 and 21. 30 BCU includes three bidirectional switches 178, 180, and A short bus 184 is connected from the BCU 58 to the memory mapper 34 of the respective corresponding processor, and a second short bus 186 is connected to the address and data registers 62 and 64 of the corresponding 35 module 60. The bidirectional switch 178 is connected to both of these short busses, so that, in one position, the bidirectional switch 178 simply serves to connect the memory mapper 34 directly to the registers 62 and 64, so that each processor can access its corresponding memory

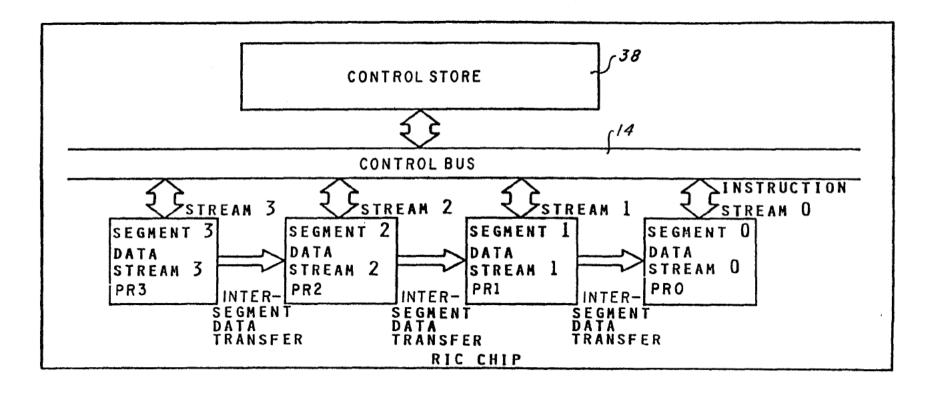

module 60, in parallel. The other position of bidirectional switch 178 serves to connect the MSU 68 (via short bus 186) to the data bus 56. Similarly, bidirectional switch 182 either blocks data flow (when the 5 corresponding processor is accessing its own corresponding memory module), or simply connects the short bus 184 directly to the data bus 156, or directionally connects the short bus 184 to the two setments of data bus 56 which are isolated when bidirectional switch 180 is in the 10 blocking mode. This mode of operation is shown in Figure 21, and permits operation of the RIC in the pipeline mode, where each processor receives a data stream from an earlier stage of operation, and contemporaneously provides an output stream of data to the following stage of Thus, the pipeline mode requires parallel 15 operation. transmission of different streams of data between respective pairs of adjacent processors, and this capability is provided by the blocking mode of bidirectional switch 180 and by the directional connection 20 provided by directional switch 182.

When a processor accesses a remote memory module, three different configurations of the BCUs may be necessary. For example, if processor PR3 accesses the memory module 60 corresponding to processor PRO, the BCU 25 58 at PR3 must connect PR3 to the data bus 56, the BCU 58 corresponding to processor PRO must connect the data bus 56 to the corresponding registers 62 and 64, and the intermediate BCUs 58 must simply permit clear operation of the data bus 56. In the presently preferred embodiment, 30 the necessary coordination of BCUs 58 is accomplished by BCU mode control line 167 in the data bus 56. When any processor has taken control of the data bus, that processor can then control all BCUs, using the BCU mode line 167. When the arbitration lines 160 indicate that a 35 processor has taken control of the data bus 56, the only necessary conditions which must be imposed on all BCUs 58 are that the bidirectional switches 180 must not block the data bus 56. In addition, the bidirectional switches 178 in each BCU 58 are operated to connect the data bus 56 to the registers 62 and 64. Thus, each address register 64 receives the requested address, and the appropriate MSU 68 then operates the control register 70 of its memory module 60 to provide the data requested.

5

15

25

While the above system for controlling the BCUs 58 is not the most efficient possible, it does avoid interprocessor interference at a minimum requirement in additional control lines. Preferably, each MSU 68 is directly connected to Bus status lines 165 of the data 10 bus, to receive the read/write and enable bits needed for RAM control register 70. Each MSU 68 is also provided with two direct lines to its corresponding processor, to provide RAM control data for local accesses without using data bus 56.

The memory scheduling unit (MSU) 68 operates as shown in Figure 22. Whenever the data bus 56 is active and the BCU mode control line 167 has been activated, the MSU looks at the leading bits of the address lines 156 to determine whether the access is for the memory module 60 20 which this MSU controls. If so, the next decision is whether memory requests are already pending. If so, the number of the latest requesting processor or data port it queued in first come first serve order. Since at most six sources (four processors and two data ports) will need to be queued, a small shift register will accomplish this. Similarly, a memory access requested by the local processor is deferred, and a busy signal returned, if other memory requests are already pending. When a memory read is performed, it is necessary to wait for the data 30 bus 56 to become available, and then to send the data word to the destinations which have been designated over the ten destination lines 168. If a write is performed, no return signal is required. In either case, the MSU 68 simply pulls the next pending memory request off the queue 35 register, and sends a signal to that source to notify it that memory access is now available. The MSU 68 now waits until the next source reissues its request, and then enables the appropriate memory access, as noted above.

As will be obvious to those skilled in the art, an

address register 64, a data register 62, and a control register 70 are provided as interfaces between the MSU 68 and the corresponding memory module 60.

In the presently preferred embodiment, each memory 5 module is addressed with a 16 bit address. This allows for eventual growth of up to 64K bytes of directly addressable space foe each of four processors. However, a processor supports two types of addresses: 16 and 32 bits. Sixteen bit addrsses are used to directly access a 10 processor's own memory module. Thirty-two bit addresses are used to access external memory. In the case of accessing other memory modules, the processor sends a 16 bit address and indicates the memory module by asserting the destination signal associated with the desired 15 internal memory module. A 32 bit address can either be an external address, or a mapped address, depending upon processor control. If the address is designated to be an external address, it is sent to the external memory interface for processing. Otherwise, it is sent to the 20 memory mapper. The memory mapper uses an associative search to determine if the address is internal or external. If it is internal the associated internal address is sent to the external memory interface.

The status bus 52 (including the end around loop 54 of the status bus) interconnects the four processors PRO-PR3, and the external status ports 74 and 75. status bus 52 includes only seven lines, namely a carry 5 status line 190, a carry IN/OUT line 191 an overflow line 192, a negative line 194, a zero line 196, and a processor synchronization line 198, and shift rotate line 199. Thus, including the end around loop 54, the status bus is only Each processor includes a corresponding 14 lines wide. 10 pair of status multiplexers 48 or 50, which are programmable switches. These switches serve to selectively and programmably connect the status output and input lines of each ALU 28 to the status bus lines, both of the status bus 52 and of the end around loop 54, in either direction. Figures 23-25 provide several examples of the status bus connections selected by the status multiplexers 48 and 50. When the processors are operating independently, as shown in Figure 23, there is no need for status line interconnections, and the status multiplexers 48 and 50 20 simply create open circuits in the status bus 52 and 54. When adjacent processors are operating in a pipeline configuration, where the data output of (e.g., PR3 is provided as an input to PR2, only the processor synchronization line 198 needs to be connected. Finally, when processors PR3 and PR2 are operating in a lockstep 25 configuration, as part of a 32 bit or wider processor, the status outputs of processor PR2 are all provided as status inputs to processor PR3. The processor synchronization line is used in the lockstep mode to ensure that a new 30 operation is not started before the current is completed. For example, all processors may not receive their memory access at the same time due to pending memory requests from other sources being unevenly distributed across the memory modules being accessed by lockstepped processors. The status of the programmable interconnects in the status 35 multiplexer 48 and 50 is governed by control lines provided from the DLA 22. The status lines 190 through 196 are connected to status inputs and outputs from the ALU 28 and the flag register 46, the shift/rotate line 199

is connctd to link-in and link-out bits of the barrel shifter 30, and the processor synchronization line 198 is connected to the DLA 22. The external status ports 74 and 75 also contain similar programmable interconnect circuitry.

The manner in which the above structural features cooperate to provide the reconfigurable multiprocessor capability of the present invention will now be discussed in further detail.

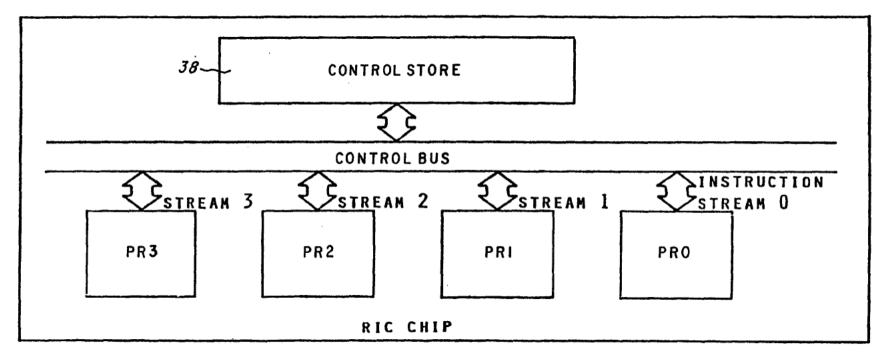

Figures 26, 27, and 28 illustrate the three principle modes of operation of the restructurable integrated circuit according to the present invention. Figure 26 shows generally the organization of the independent mode, where processors PRO-PR3 function as, in effect, four independent processors which happen to be located on a single chip. Four separate instruction streams are provided to the separate processor PRO-PR3, and the only interface required between the separate processors is that accessitated by the control bus and data bus protocols.

20 The same configuration also supports array processing operations. In array processing, the interconnections of the processors are the same as for the independent mode; the difference is that, in array processing, each processor receives the same instruction stream. Of course, array processing may also be based on lockstepped subcombinations of processors (e.g., two 32-bit processors).

Figure 27 shows an example of the RIC operating in the internal lockstep mode. In this example, all four processors have been reconfigured to operate as a single 64-bit processor. In this configuration, the control bus 14 carries a single common instruction stream, which is received by all processors. The necessary synchronization carry and status bits are communicated over the status bus 52 and 54, as discussed above. In addition, shift and rotate linkage is provided, so any desired bit or rotate operation may be performed on a 64-bit word, via the data bus 56. (For this linkage, the data bus 56 is configured as discussed above for the pipeline mode.) One-bit

shifts and rotations are performed over shift/rotate line 199. Accurate programming for this mode of the RIC permits 64-bit access to the RAM memory 66 in a single clock cycle, since each processor reads or writes its 16-bit segment of the 64-bit word, and all processors do this in corresponding locations of the four RAM memory modules 60 simultaneously.