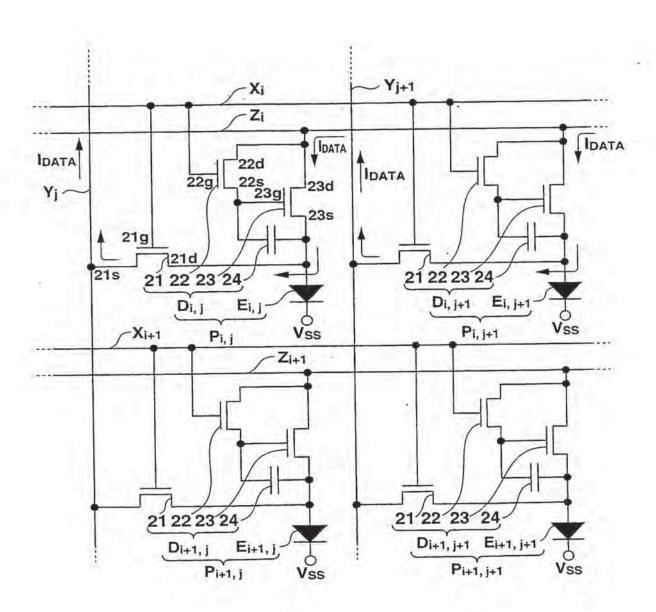

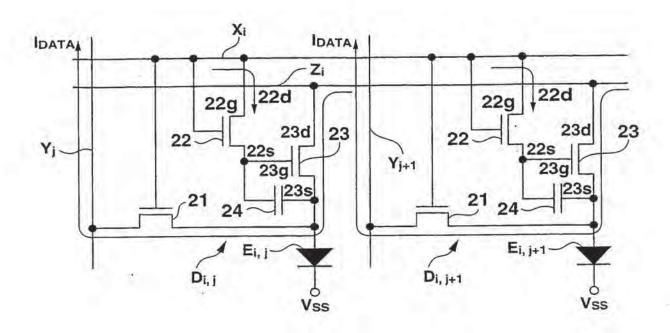

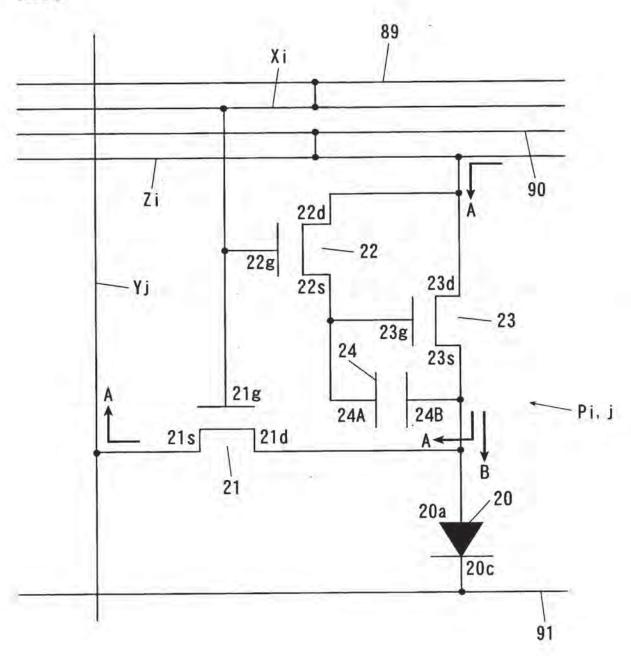

light-emitting elements  $E_{i,1}$  to  $E_{i,n}$  of the ith row. Hence, in all the pixel circuits  $D_{i,1}$  to  $D_{i,n}$  of the ith row, a driving current equal to the gray level designation current  $I_{DATA}$  flows from the common signal supply line  $Z_i$  to the light-emitting elements  $E_{i,1}$  to  $E_{i,n}$  of the ith row through the drains 23s and sources 23s of the third transistors 23. Hence, the light-emitting elements  $E_{i,1}$  to  $E_{i,n}$  emit light.

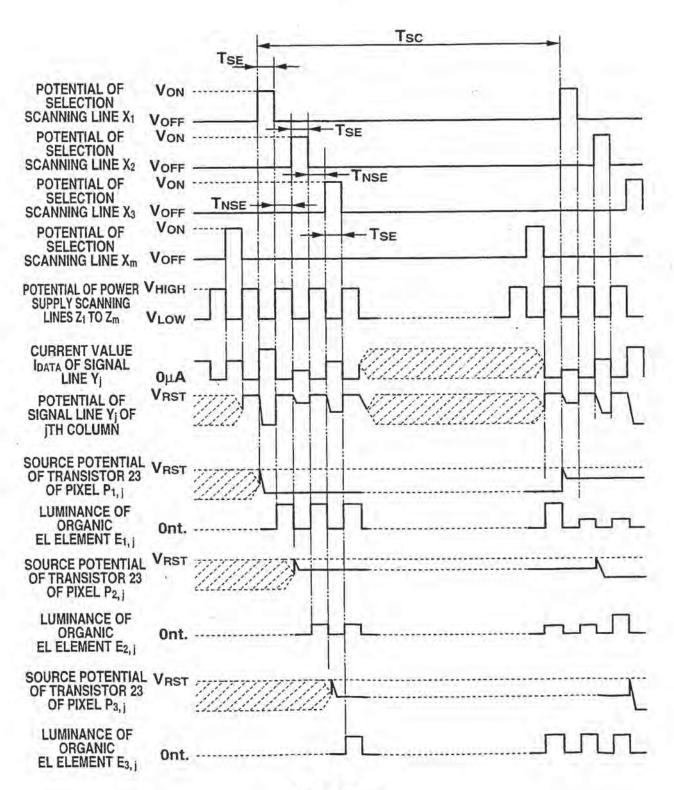

More specifically, in each of the pixel circuits Di,1 to Di,n during the non-selection period TNSE, the first transistor 21 functions to electrically disconnect the corresponding signal line Yi from the third transistor 23 such that the gray level designation current IDATA flowing to the signal line Yi does not flow to the third transistor 23. The second transistor 22 functions to hold the voltage between the gate 23g and the source 23s of the third transistor 23, which is converted during the selection period TSE, by confining the charges in the capacitor 24. In all the pixel circuits Di,1 to Di,n of the ith row, when the common signal is set to the voltage VHIGH during the non-selection period TNSE, the third transistor 23 functions to supply a driving current of a level corresponding to the held gate-source voltage level to the light-emitting element Ei, j.

Hence, the light-emitting elements  $E_{\text{i,1}}$  to  $E_{\text{i,n}}$  of the ith row do not emit light during each of the

5

15

selection periods TSE of the first to mth rows. The light-emitting elements  $E_{i,1}$  to  $E_{i,n}$  emit light during each of the  $\underline{m}$  non-selection periods  $T_{\mbox{\scriptsize NSE}}$  in one scanning period TSC. The current value of the driving current that flows to the light-emitting elements  $E_{i,1}$ to Ei,n when the common signal is at VHIGH is the same as that of the current flowing to the third transistor 23 of each of the pixel circuits Di,1 to Di,n. is, the current value is equal to that of the gray level designation current IDATA that flows to the third transistor 23 of each of the pixel circuits  $D_{i,1}$  to Di,n during the selection period TSE of the ith row. During the selection period TSE of the ith row, when the current value that flows to the third transistor 23 of each of the pixel circuits Di, 1 to Di, n of the ith row is set, the driving current of each of the light-emitting elements Ei,1 to Ei,n has a desired current value. Hence, the light-emitting elements Ei,1 to Ei,n emit light at a desired gray level luminance.

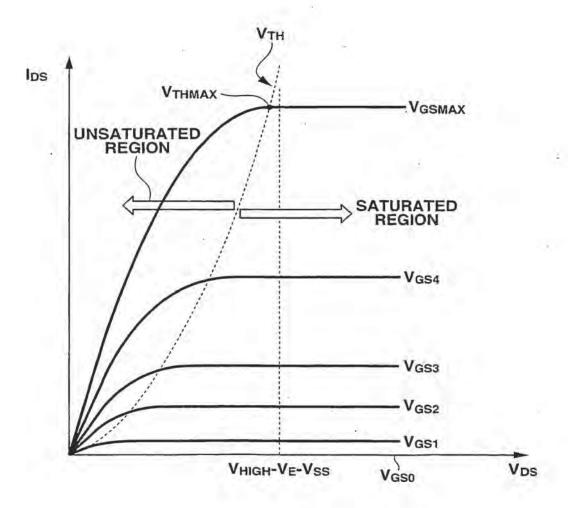

20 As described above, in this embodiment, even when the current vs. voltage characteristic of the third transistor 23 changes between the pixel circuits D<sub>1,1</sub> to D<sub>m,n</sub>, the gray level designation current I<sub>DATA</sub> having a predetermined current value is forcibly supplied between the source 23s and the drain 23d of the third transistor 23 during the selection period T<sub>SE</sub>. In addition, when the voltage between the source

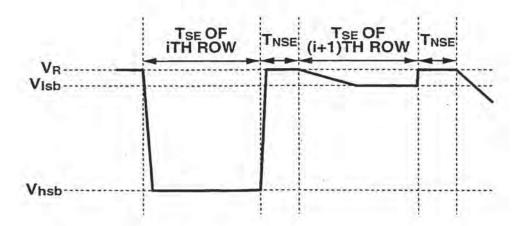

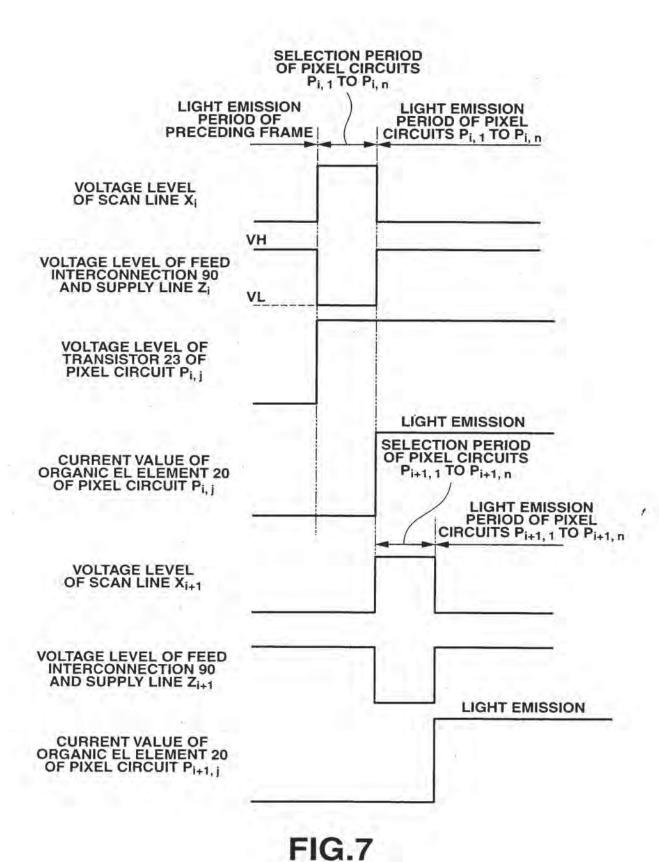

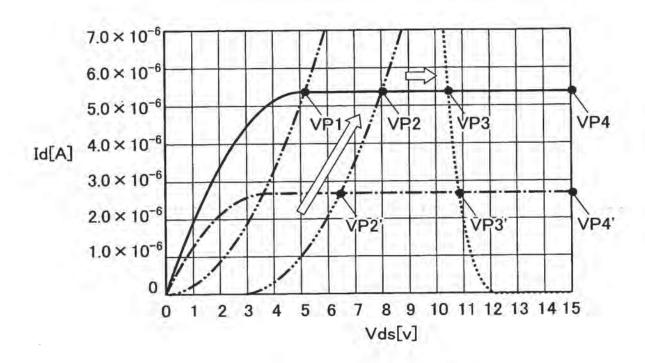

23s and the drain 23d of the third transistor 23 is always saturated, as shown in FIG. 7, the common signal of the voltage  $V_{\rm HIGH}$  is output to the common signal supply lines  $Z_1$  to  $Z_m$  during the non-selection period .  $T_{\rm NSE}$ . Accordingly, a driving current having a current value equal to the gray level designation current  $I_{\rm DATA}$  is supplied between the source 23s and the drain 23d of the third transistor 23. For this reason, the luminance does not vary between the light-emitting elements  $E_{1,1}$  to  $E_m$ , n of the pixels. That is, in this embodiment, even when a luminance gray level signal having the same voltage level is output to pixels, any in-plane variation in luminance between the pixels can be suppressed. Hence, the organic EL display 1 of this embodiment can display a high-quality image.

During the non-selection period  $T_{\rm NSE}$ , the common signal changes to  $V_{\rm HIGH}$  m times. The light emission duty of the light-emitting element  $E_{\rm i,j}$  is about 50%. To the contrary, in a simple matrix driving display having m light-emitting elements arrayed in the vertical direction and n light-emitting elements arrayed in the horizontal direction, the light emission duty is 1/m. In the simple matrix driving display, as the resolution becomes high, the light emission duty of the light-emitting element decreases. In the organic EL display 1 of this embodiment, however, even when the resolution becomes high, the light emission duty of the

15

20

light-emitting element  $E_{i,j}$  does not decrease. The organic EL display 1 can display an image at a high luminance, high contrast, and high resolution.

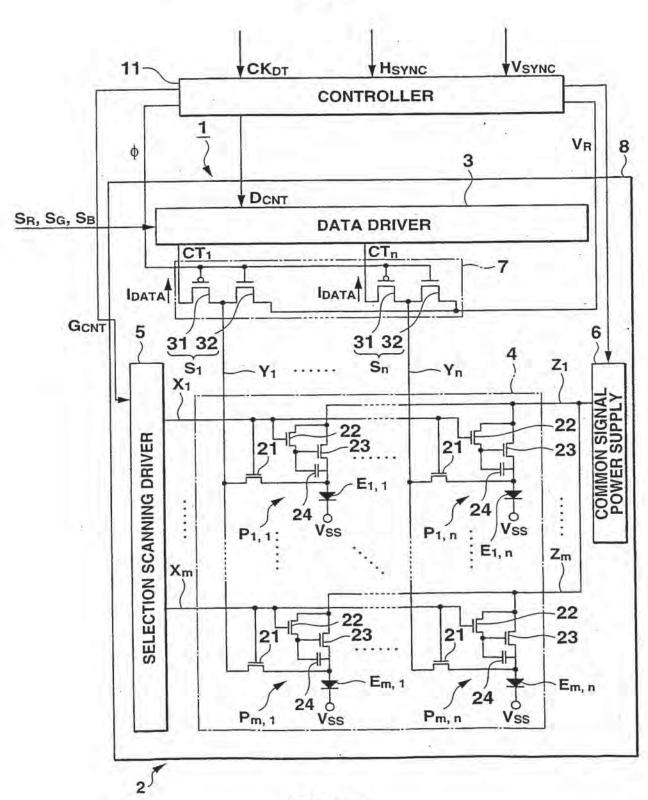

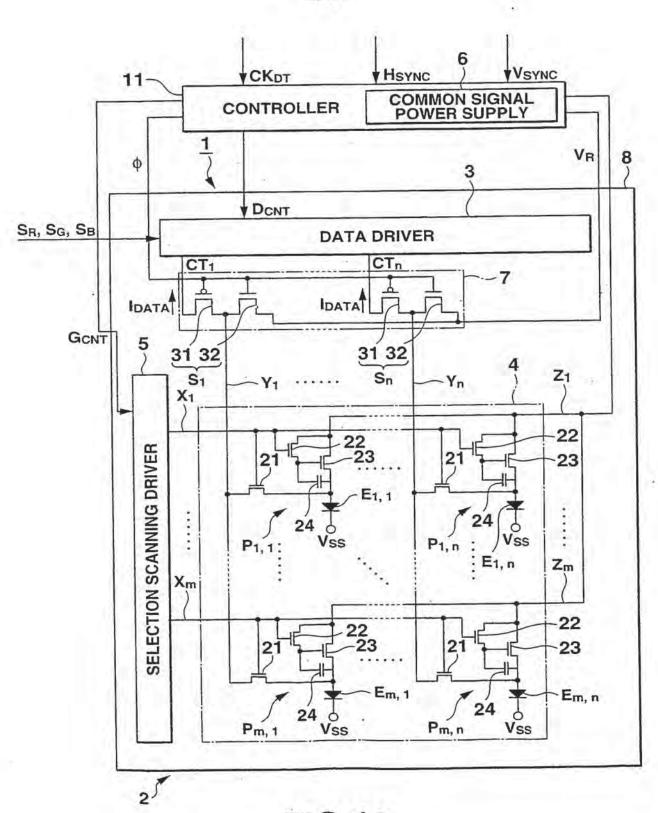

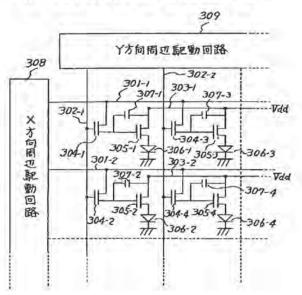

One selection scanning line Xi and one common signal supply line Zi are arranged in each row. Not a signal for scanning but a common signal is simply output from the common signal power supply 6 to the common signal supply line Zi. The only shift register for scanning, which is arranged in the organic EL display 1, is the selection scanning driver 5. A shift register is generally formed from m flip-flop circuits. The common signal power supply 6 only needs to output signals having the same waveform to all the common signal supply lines  $\mathbf{Z}_1$  to  $\mathbf{Z}_{\mathbf{m}}$  and therefore can have a simplified circuit structure. For this reason, in the common signal power supply 6, the mounting area is smaller, the structure is simpler, and the number of elements is smaller than a shift register. As compared to a conventional organic EL display having two shift registers serving as drivers, the organic EL display 1 of this embodiment can reduce the manufacturing cost and increase the yield.

[Second Embodiment]

15

20

25

An organic EL display according to the second embodiment will be described next.

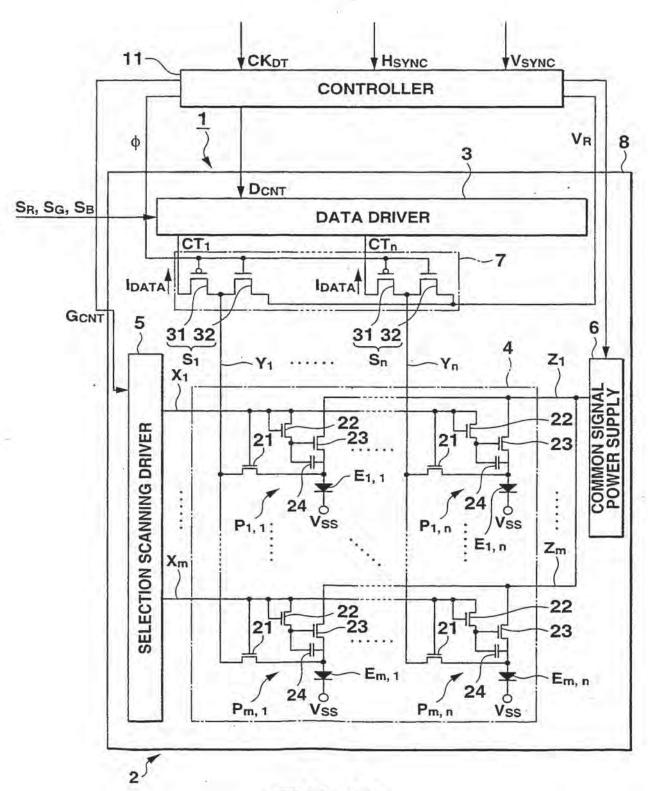

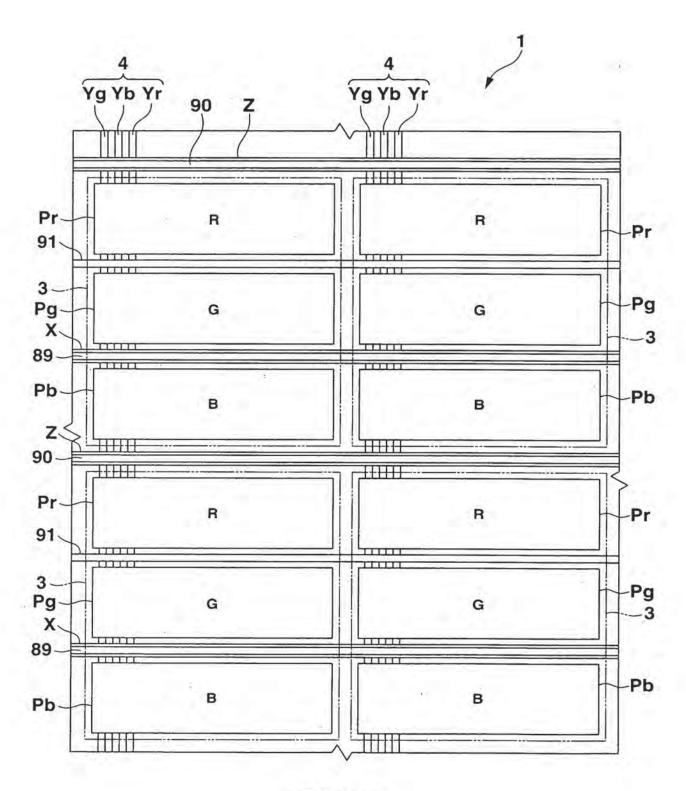

Even in the second embodiment, the organic EL display comprises an organic EL display panel 2, data

driver 3, and selection scanning driver 5, like the organic EL display 1 according to the first embodiment shown in FIG. 1. The data driver 3, a display section 4, the selection scanning driver 5, pixel circuits  $D_{1,1}$  to  $D_{m,n}$ , and light-emitting elements  $E_{1,1}$  to  $E_{m,n}$  have the same structures as those in the organic EL display 1 of the first embodiment, and a detailed description thereof will be omitted in the second embodiment.

In the second embodiment, a common signal power supply 6 is arranged in a controller 11 connected to the organic EL display 1, as shown in FIG. 10. For this reason, the ratio of the occupied area of the pixels on the substrate of the organic EL display 1 can be increased.

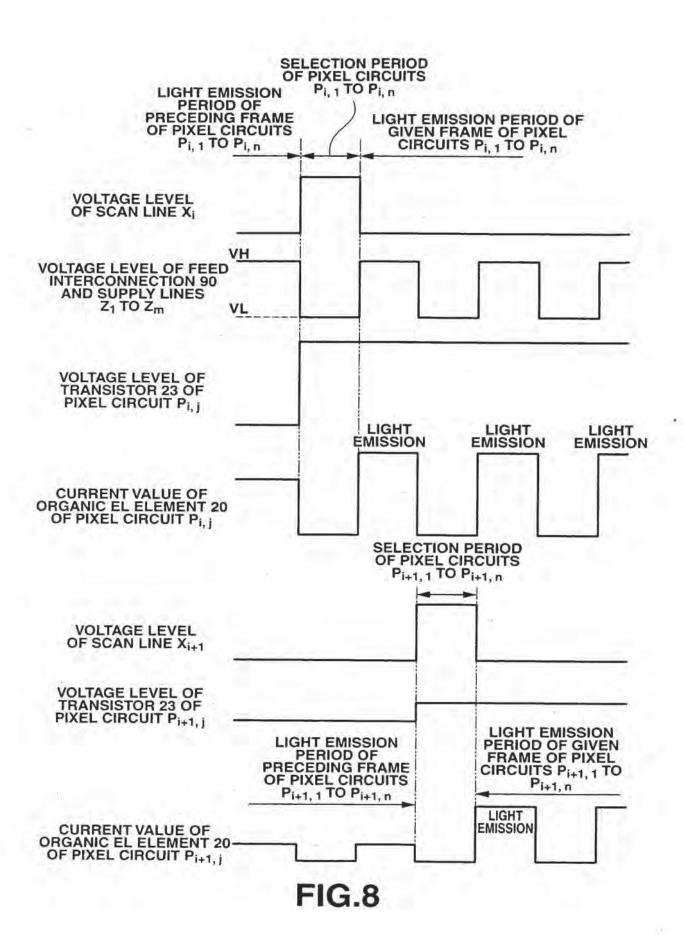

The organic EL display 1 according to the second embodiment can operate in accordance with the waveform chart shown in FIG. 8, as in the first embodiment.

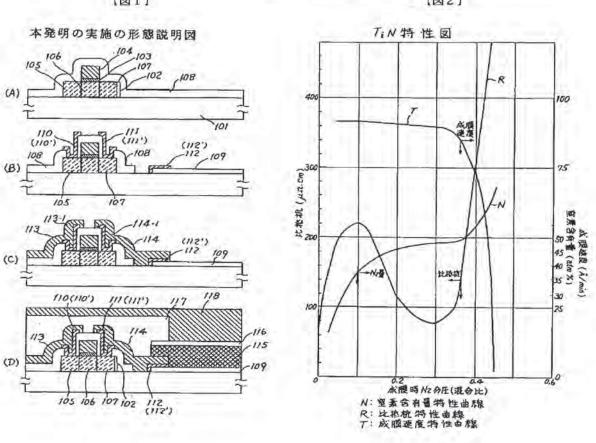

[Third Embodiment]

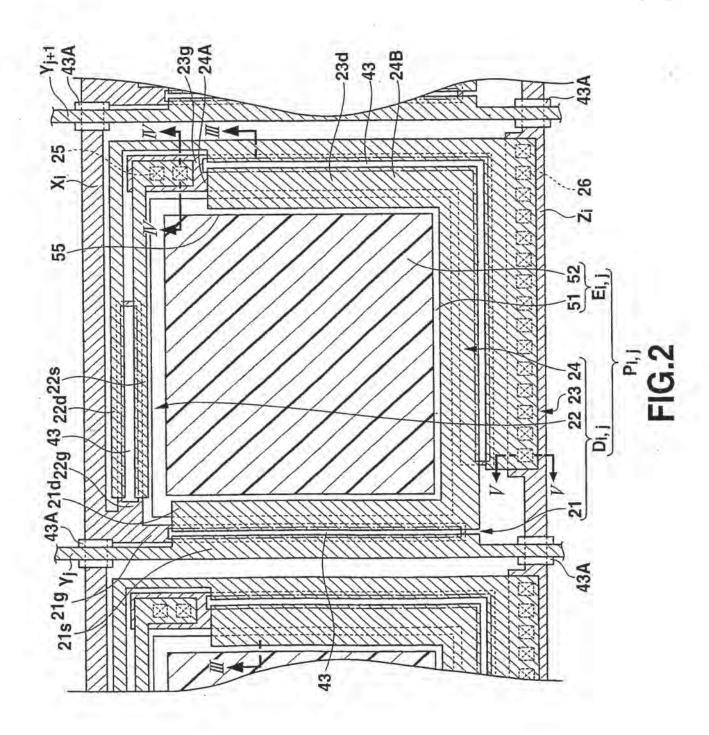

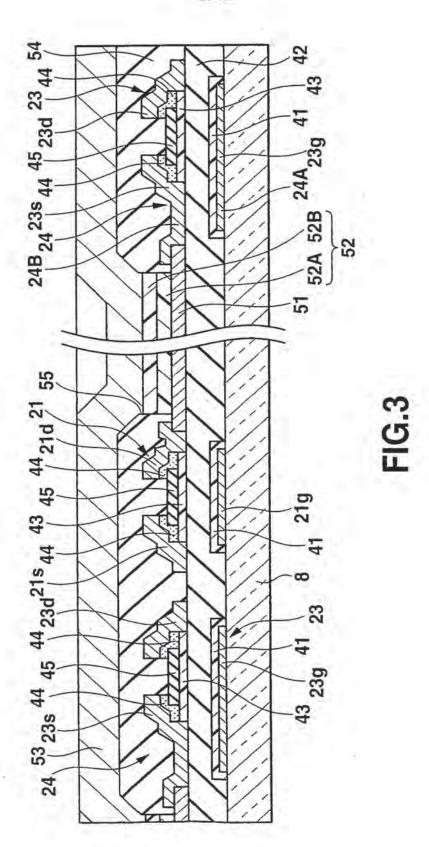

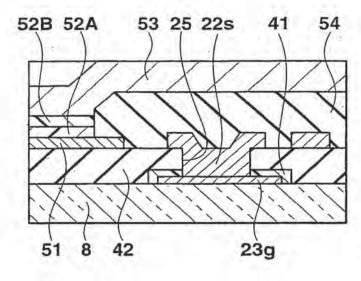

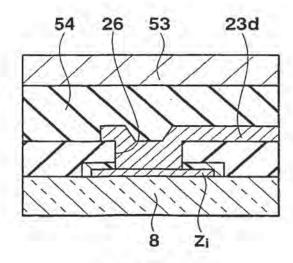

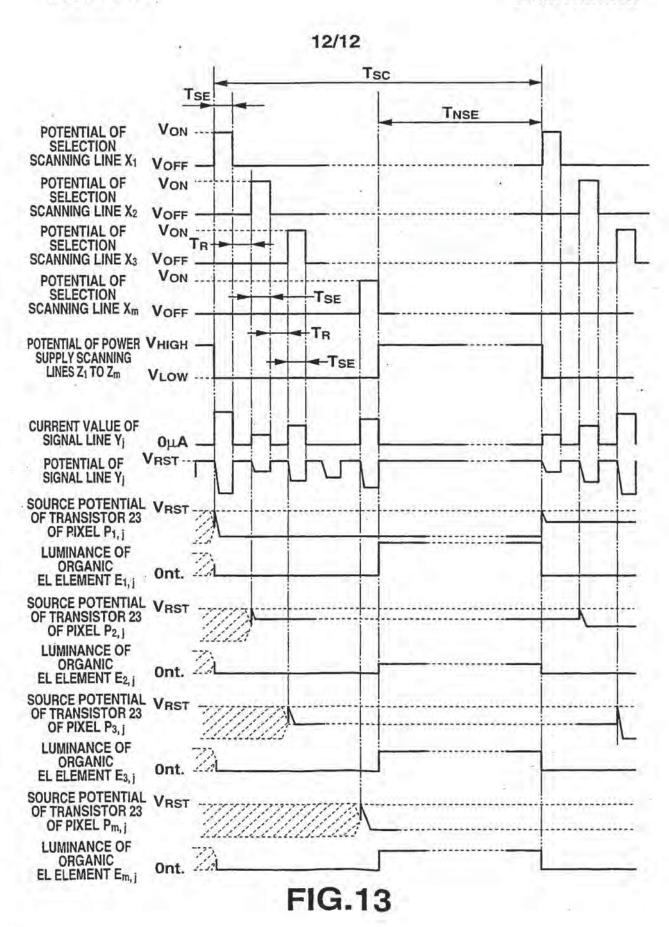

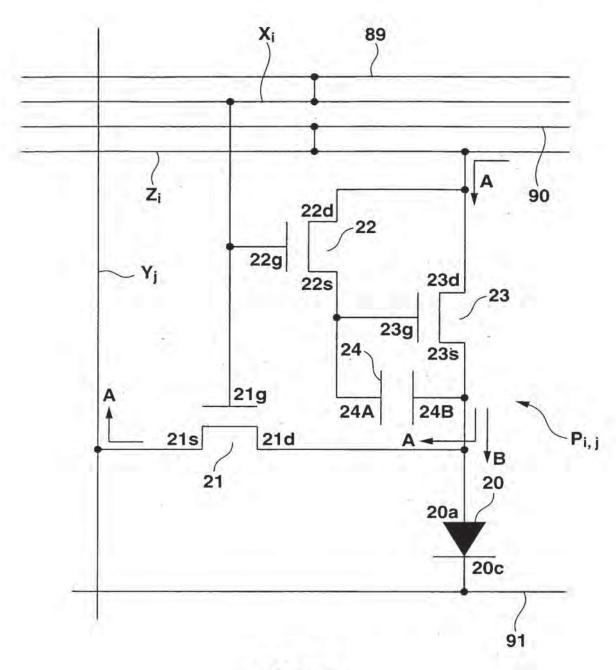

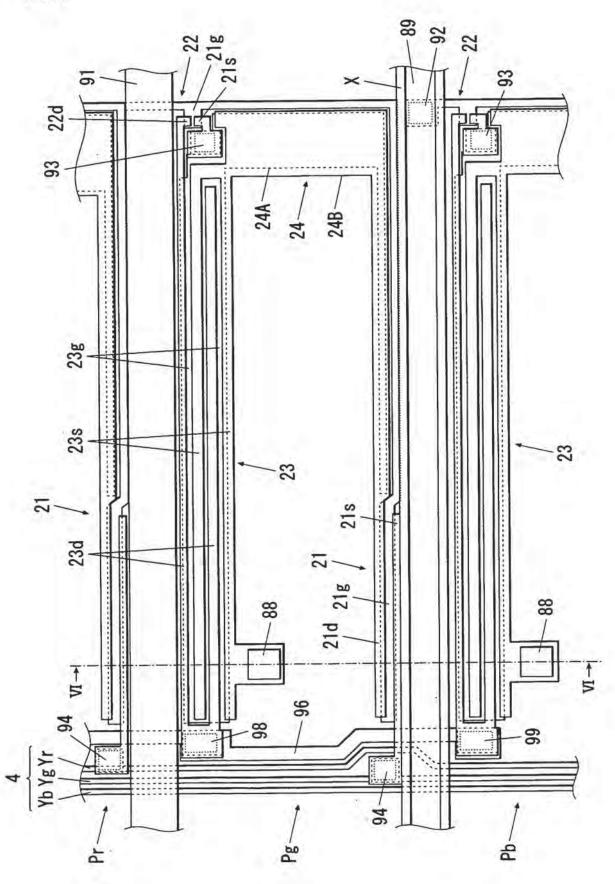

The third embodiment will be described next. This embodiment is the same as the first embodiment except that a drain 22d of a second transistor 22 of a pixel circuit  $D_{i,j}$  of each pixel  $P_{i,j}$  is not connected to a common signal supply line  $Z_i$  but to a selection scanning line  $X_i$ , as shown in FIG. 11. The same reference numerals as in the first embodiment denote the same parts in the third embodiment, and a detailed description thereof will be omitted.

25

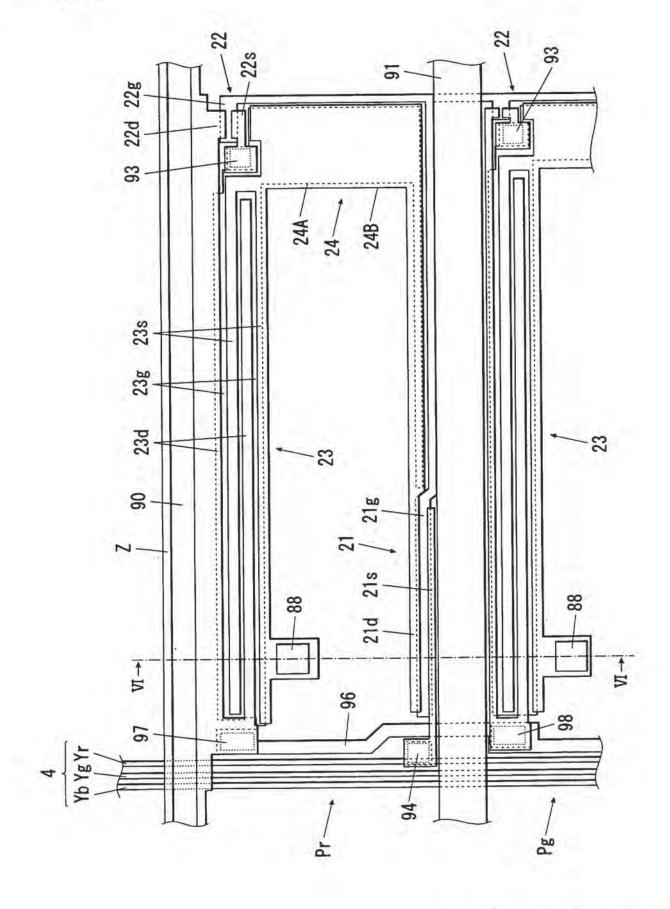

In the transistor 22, the drain electrode 22d and gate electrode 22g are connected to the selection scanning line  $X_i$ . A source electrode 22s is connected to a gate electrode 23g of a third transistor 23. The transistor 22 is an N-channel amorphous silicon thin film transistor, like a first transistor 21 and the transistor 23.

5

10

15

20

The transistor 22 operates upon receiving the voltage shown in the waveform chart in FIG. 8. is, as shown in FIG. 12A, during a selection period TSE, the transistor 22 of each of pixels Pi,1 to Pi,n is turned on by a scanning signal of an ON-level (high-level) voltage  $V_{\mbox{ON}}$  from the selection scanning line Xi so that the voltage from the selection scanning line  $X_1$  is applied to the gate of the transistor 23. Simultaneously, the transistor 21 of each of the pixels P<sub>i,1</sub> to P<sub>i,n</sub> is turned on. In addition, the transistor 23 of each of the pixels Pi,1 to Pi,n is turned on by the gate voltage applied by the transistor 22 during the selection period TSE. Hence, the data driver 3 supplies a gray level designation current IDATA to the paths between the drains 23d and the sources 23s of the transistors 23 of the pixels Pi,1 to Pi,n and signal lines  $Y_1$  to  $Y_n$  in the direction indicated by the arrow in FIG. 12A. The current value of the gray level designation current IDATA at this time corresponds to the gray level of a red digital gray level image signal

SR, green digital gray level image signal SG, and blue digital gray level image signal SB input to the data driver 3. Charges corresponding to the current value of the gray level designation current IDATA are stored in capacitors 24 connected to the paths between the gates 23g and the sources 23s of the transistors 23 of the pixels Pi,1 to Pi,n during the selection period TSE .

During a non-selection period T<sub>NSE</sub>, the transistor 21 and transistor 22 of each of the pixels Pi,1 to Pi,n 10 are turned off by a scanning signal of an OFF-level voltage VOFF supplied to the selection scanning line Xi. A voltage VHIGH is applied to all common signal supply lines Z<sub>1</sub> to Z<sub>m</sub>. For this reason, the voltages between the sources 23s and the drains 23d of all the transistors 23 are saturated. The voltages between the gates 23g and the sources 23s of all the transistors 23 have a voltage value corresponding to the charges stored in the capacitors 24 during the selection period TSE. As shown in FIG. 12B, a driving current having a current value equal to the gray level designation current IDATA flows between the sources 23s and the drains 23d of all the transistors 23. Since the voltage VHIGH is much higher than a reference voltage VSS, the driving current flows in the direction indicated by the arrow in FIG. 12A to cause light-emitting elements  $E_{1,1}$  to  $E_{m,n}$  to emit light.

15

20

20

The present invention is not limited to the above embodiments. Various changes and modifications of design may be done without departing from the spirit and scope of the invention.

For example, in the above embodiments, all the first transistor 21, second transistor 22, and third transistor 23 of the pixel circuit  $D_{i,j}$  are N-channel transistors. However, all the transistors may be formed from P-channel transistors, and the anode and cathode of the light-emitting element  $E_{i,j}$  may be connected in the reverse direction. At this time, the waveforms shown in FIG. 8 are inverted.

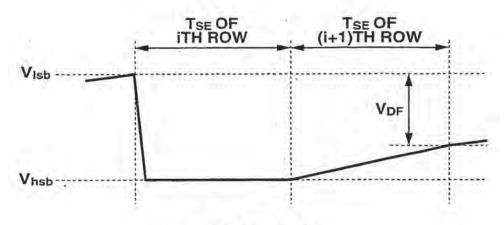

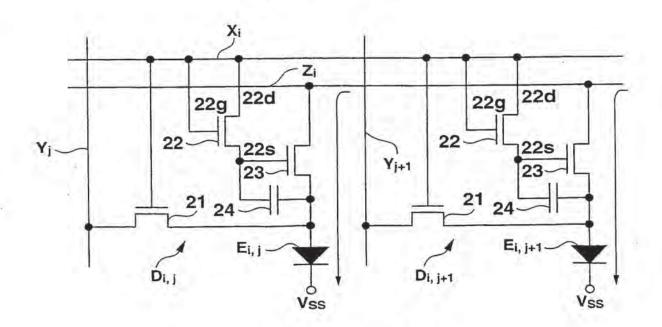

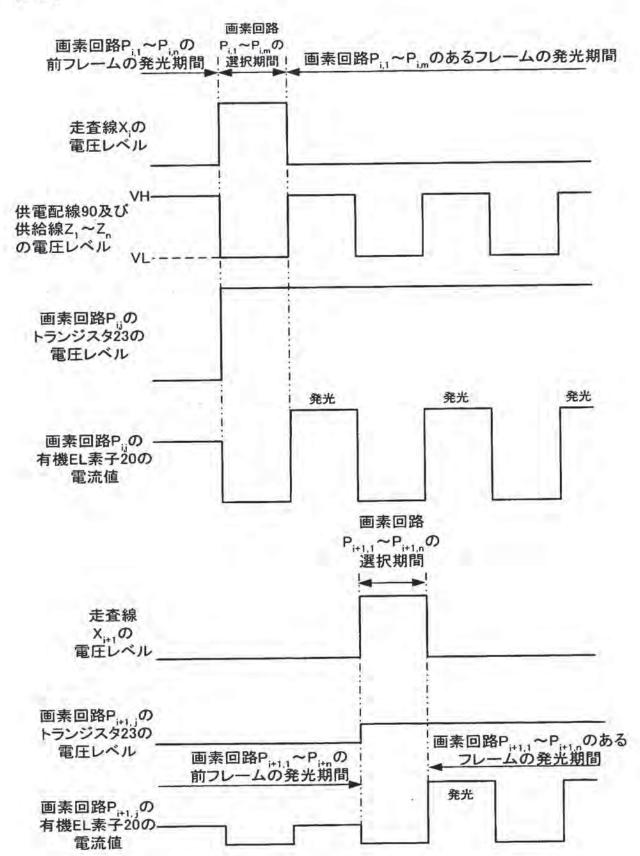

In the embodiments, the light-emitting period of the light-emitting elements  $E_{1,1}$  to  $E_{m,n}$  is the non-selection period  $T_{\rm NSE}$  between the selection periods  $T_{\rm SE}$ . the light-emitting period of the light-emitting element  $E_{i,j}$  is the <u>m</u> discontinuous non-selection periods  $T_{\rm NSE}$  between the selection period  $T_{\rm SE}$  of the ith row and the selection period  $T_{\rm SE}$  of the next ith row. As shown in FIG. 13, all the light-emitting elements  $E_{1,1}$  to  $E_{m,n}$  may be simultaneously caused to emit light during the non-selection period  $T_{\rm NSE}$  after charges by the gray level designation current  $I_{\rm DATA}$  are written in the capacitors 24 of all the light-emitting elements  $E_{1,1}$  to  $E_{m,n}$ . At this time, when at least one of the selection period  $T_{\rm SE}$  during one scanning period  $T_{\rm SC}$  and (m-1) reset periods  $T_{\rm R}$  when the reset voltage

10

15

20

$V_{RST}$  is applied to the signal lines  $Y_1$  to  $Y_n$  is set to be short, the non-selection period  $T_{NSE}$ , i.e., the light-emitting period of the light-emitting elements  $E_{1,1}$  to  $E_{m,n}$  can be made relatively long. Referring to FIG. 13, after the selection scanning line  $X_m$  is selected, to return the charges stored in the parasitic capacitances of the signal lines  $Y_1$  to  $Y_n$  in the write mode of the pixels  $P_{m,1}$  to  $P_{m,n}$  of the selection scanning line  $X_m$ , the reset voltage  $V_{RST}$  may be applied to increase the number of reset periods  $T_R$  during one scanning period  $T_{SC}$  to  $\underline{m}$ .

In the above embodiments, an organic EL element is used. However, any other light-emitting element having rectification properties may be used. That is, the light-emitting element may be an element which flows no current when a reverse bias voltage is applied but flows a current when a forward bias voltage is applied, and also emits light at a luminance correspondence with the magnitude of the flowing current. An example of a light-emitting element having rectification properties is an LED (Light Emitting Diode) element.

In the above embodiments, the data driver 3 and selection scanning driver 5 operate on the basis of a clock signal input from the controller 11. However, the clock signal CK3 that is output from the common signal power supply 6 and used as a common signal may be input to the selection scanning driver 5 as the

10

15

20

25

clock signal CK2.

In the above embodiments, the number of times the common signal output from the common signal power supply 6 changes to low level, i.e., the gray level designation current  $I_{\mathrm{DATA}}$  is supplied is one per selection period  $T_{\mathrm{SE}}$ . However, the number of times may be two or more per selection period  $T_{\mathrm{SE}}$ .

According to the present invention, when a driving current flows to the light-emitting element, the light-emitting element emits light. The current value of the driving current corresponds to the voltage held between the gates 23g and the source 23s of the transistor 23 of the pixel circuit. The voltage value is obtained by converting the current value of the designation current. For these reasons, the current value of the driving current coincides with the current value of the designation current. The light-emitting element emits light at a luminance depending on the current value of the designation current. That is, the light-emitting element emits light at a luminance set by the current value of the designation current. Hence, if the current value of the designation current does not change between pixels, the luminance does not vary between the plurality of light-emitting elements, and a high-quality image can be displayed.

It is only the scanning driver 5 that supplies a selection signal to each scanning line. No drivers for

scanning are arranged at all. In addition, the common signal power supply 6 has a smaller number of elements than that of the scanning driver and therefore has a simple arrangement. Hence, the mounting area of the driver is small.

SAMSUNG EX. 1002 - 717/899

## CLAIMS

- 1. A display device comprising:

- a plurality of scanning lines;

- a plurality of signal lines;

10

15

20

25

a scanning driver which sequentially supplies to the scanning lines selection signals that select the scanning lines;

a data driver which supplies a designation current to said plurality of signal lines within a selection period when the scanning lines are being selected;

a plurality of pixel circuits which supplies a driving current corresponding to a current value of the designation current that flows to the signal lines;

a plurality of optical elements which emit light in accordance with the driving current supplied by said plurality of pixel circuits; and

a power supply which outputs to said plurality of pixel circuits a driving current reference voltage to supply the driving current.

- 2. A display device according to claim 1, wherein the power supply outputs the driving current reference voltage to said plurality of pixel circuits within a non-selection period.

- 3. A display device according to claim 2, wherein the non-selection period is a period when none of said plurality of optical elements are selected.

- 4. A display device according to claim 2, wherein

10

15

20

25

a reset voltage is output to said plurality of signal lines within the non-selection period.

- 5. A display device according to claim 1, wherein the power supply selectively outputs the driving current reference voltage and a designation current reference voltage to supply the designation current.

- 6. A display device according to claim 5, wherein the designation current reference voltage is lower than the driving current reference voltage.

- 7. A display device according to claim 5, wherein the power supply outputs the designation current reference voltage within the selection period.

- 8. A display device according to claim 1, wherein the power supply alternately outputs a designation current reference voltage to supply the designation current and the driving current reference voltage.

- 9. A display device according to claim 1, wherein the data driver supplies the designation current to the signal lines and the pixel circuits on the basis of a designation current reference voltage output from the power supply within the selection period, and

each of the pixel circuits stores the current value of the designation current and supplies the driving current that is equal to the current value of the designation current on the basis of the driving current reference voltage output from the power supply.

10. A display device according to claim 1, wherein

15

20

25

each of the pixel circuits comprises a driving transistor and a capacitor which is connected between a gate and a source of the driving transistor,

the data driver supplies the designation current to the signal lines and the driving transistors of the pixel circuits on the basis of a designation current reference voltage output from the power supply within the selection period, and

the capacitor stores charges corresponding to the designation current between the gate and the source, and when the driving current reference voltage is input from the power supply, the driving transistor supplies the driving current corresponding to the charges stored between the gate and the source.

11. A display device according to claim 1, wherein each of the pixel circuits comprises

a first transistor in which a gate is connected to the scanning line and one of a drain and a source is connected to the signal line,

a second transistor in which a gate is connected to the scanning line and a designation current reference voltage and the driving current reference voltage are selectively input to one of a drain and a source, and

a driving transistor in which a gate is connected to the other of the drain and the source of the second transistor, one of a drain and a source is connected to

one of the drain and the source of the second transistor, and the other of the drain and the source is connected to the other of the drain and the source of the first transistor and the optical element.

- 5 12. A display device according to claim 11, wherein the scanning driver selects the first transistor and the second transistor, which are connected to a predetermined scanning line, within the selection period.

- 13. A display device according to claim 1, wherein each of the pixel circuits comprises

- a first transistor in which a gate is connected to the scanning line and one of a drain and a source is connected to the signal line,

- a second transistor in which a gate is connected to the scanning line and one of a drain and a source is connected to the scanning line, and

- a driving transistor in which a gate is connected to the other of the drain and the source of the second transistor, one of a drain and a source is connected to the power supply, and the other of the drain and the source is connected to the other of the drain and the source of the first transistor and the optical element.

- 14. A display device according to claim 13,

wherein the scanning driver selects the first

transistor and the second transistor, which are

connected to a predetermined scanning line, within the

10

15

15

20

25

selection period.

- 15. A display device according to claim 1, wherein the power supply outputs the driving current reference voltage from the end of the selection period of a predetermined scanning line till the beginning of the selection period of a next scanning line.

- 16. A display device according to claim 1, wherein the optical element has a first electrode connected to the power supply through the pixel circuit and a second electrode to which a reference voltage is applied.

- 17. A display device according to claim 16, wherein

the power supply selectively outputs the driving current reference voltage and a designation current reference voltage to supply the designation current, and

the driving current reference voltage is not less than the reference voltage, and the designation current reference voltage is not more than the reference voltage.

- 18. A display device according to claim 1, wherein the optical element is an organic EL element.

- 19. A display device comprising:

a scanning line group having a scanning line of a first row and a scanning line of a second row;

an optical element group having a first optical element which is connected to the scanning line of the

10

15

20

25

first row and emits light in accordance with a current value of a first driving current supplied, and a second optical element which is connected to the scanning line of the second row and emits light in accordance with a current value of a second driving current supplied;

a pixel circuit group having a first pixel circuit which is connected to the first optical element and supplies the first driving current equal to a current value of a first designation current supplied, and a second pixel circuit which is connected to the second optical element and supplies the second driving current equal to a current value of a second designation current supplied; and

a power supply which applies a driving current reference voltage to supply the first driving current to the first optical element through the first pixel circuit and applies the driving current reference voltage to supply the second driving current to the second optical element through the second pixel circuit between a selection period of the scanning line of the first row and a selection period of the scanning line of the second row.

- 20. A display device according to claim 19, wherein the power supply outputs the driving current reference voltage to the optical element group within a non-selection period.

- 21. A display device according to claim 20,

wherein the non-selection period is a period when none of the optical elements of the optical element group are selected.

- 22. A display device according to claim 20, wherein a reset voltage is output to said plurality of signal lines within the non-selection period.

- 23. A display device according to claim 19, wherein the power supply selectively outputs the driving current reference voltage and a designation current reference voltage to supply the first and second designation currents to the first and second pixel circuits.

10

- 24. A display device according to claim 23, wherein the designation current reference voltage is lower than the driving current reference voltage.

- 25. A display device according to claim 23, wherein the power supply outputs the designation current reference voltage within the selection period.

- 26. A display device according to claim 19,

wherein the power supply alternately outputs a

designation current reference voltage to supply the

first and second designation currents and the driving

current reference voltage.

- 27. A display device according to claim 19,

25 further comprising a data driver which supplies the

first and second designation currents to the first and

second pixel circuits on the basis of a designation

10

15 .

20

current reference voltage output from the power supply within the selection period.

- 28. A display device according to claim 27, further comprising a signal line which connects the data driver to the pixel circuits.

- 29. A display device according to claim 19, wherein each of the pixel circuits stores the current value of the designation current supplied within the selection period and supplies the driving current that is equal to the current value of the designation current on the basis of the driving current reference voltage output from the power supply after the selection period.

- 30. A display device according to claim 19, wherein

each of the pixel circuits comprises a driving transistor and a capacitor which is connected between a gate and a source of the driving transistor,

the data driver supplies the designation current to the driving transistors of the pixel circuits on the basis of a designation current reference voltage output from the power supply within the selection period, and

the capacitor stores charges corresponding to the designation current between the gate and the source, and when the driving current reference voltage is input from the power supply, the driving transistor supplies the driving current corresponding to the charges stored

10

15

20

between the gate and the source.

31. A display device according to claim 19, wherein each of the pixel circuits comprises

a first transistor in which a gate is connected to one scanning line of the scanning line group and one of a drain and a source is connected to the data driver,

a second transistor in which a gate is connected to the scanning line and a designation current reference voltage and the driving current reference voltage are selectively input to one of a drain and a source, and

a driving transistor in which a gate is connected to the other of the drain and the source of the second transistor, one of a drain and a source is connected to one of the drain and the source of the second transistor, and the other of the drain and the source is connected to the other of the drain and the source of the first transistor and one optical element of the optical element group.

- 32. A display device according to claim 31, further comprising a selection scanning driver which selects the first transistor and the second transistor, which are connected to the predetermined scanning line of the scanning line group within the selection period.

- 25 33. A display device according to claim 19,

wherein each of the pixel circuits comprises

a first transistor in which a gate is connected to

one scanning line of the scanning line group and one of a drain and a source is connected to the data driver,

a second transistor in which a gate is connected to the scanning line and one of a drain and a source is connected to the scanning line, and

a driving transistor in which a gate is connected to the other of the drain and the source of the second transistor, one of a drain and a source is connected to the power supply, and the other of the drain and the source is connected to the other of the drain and the source of the first transistor and one optical element of the optical element group.

- 34. A display device according to claim 33, further comprising a selection scanning driver which selects the first transistor and the second transistor, which are connected to the predetermined scanning line of the scanning line group within the selection period.

- 35. A display device according to claim 19, wherein the power supply outputs the driving current reference voltage within a non-selection period between the selection period of a predetermined scanning line and the selection period of a next scanning line.

- 36. A display device according to claim 19, wherein the optical element has a first electrode connected to the power supply through the pixel circuit and a second electrode to which a reference voltage is applied.

10

15

10

15

20

25

37. A display device according to claim 36, wherein

the power supply selectively outputs the driving current reference voltage and the designation current reference voltage to supply the first and second designation currents, and

the driving current reference voltage is not less than the reference voltage, and the designation current reference voltage is not more than the reference voltage.

- 38. A display device according to claim 19, wherein the optical element is an organic EL element.

- 39. A display device comprising:

- a plurality of scanning lines;

a scanning driver which sequentially supplies to the scanning lines selection signals that select one of said plurality of scanning lines;

a plurality of pixel circuits each of which is connected to a corresponding one of said plurality of scanning lines and supplies a driving current corresponding to a current value of the designation current;

a plurality of optical elements each of which emits light in accordance with the driving current supplied by a corresponding one of said plurality of pixel circuits;

a data driver which supplies the designation currents to the pixel circuits within a selection

10

15

20

period when the scanning lines are selected; and

a common voltage output circuit which outputs to the selected pixel circuit a designation current reference voltage to supply the designation currents within the selection period of the scanning lines and outputs to said plurality of pixel circuits a driving current reference voltage to supply the driving currents within a non-selection period.

- 40. A display device according to claim 39, wherein the common voltage output circuit outputs the driving current reference voltage to all the pixel circuits within the non-selection period.

- 41. A display device according to claim 39, wherein the designation current reference voltage is lower than the driving current reference voltage.

- 42. A display device driving method comprising:

a first designation current step of supplying a first designation current to a first driving transistor within a first selection period to store charges corresponding to a current value of the first designation current between a gate and a source of the first driving transistor;

a second designation current step of supplying a second designation current to a second driving transistor within a second selection period to store charges corresponding to a current value of the second designation current between a gate and a source of the

15

second driving transistor; and

a driving current reference voltage output step

of, from the end of the first selection period till the

beginning of the second selection period, outputting a

driving current reference voltage to the first driving

transistor and a first optical element which is

connected in series with the first driving transistor

and outputting the driving current reference voltage to

the second driving transistor and a second optical

element which is connected in series with the second

driving transistor.

- 43. A display device driving method according to claim 42, wherein the driving current reference voltage is a voltage at which a source-drain voltage of the first driving transistor and a source-drain voltage of the second driving transistor are set in a saturated state.

- 44. A display device driving method comprising:

- a first designation current step of supplying a

first designation current to a first driving transistor

within a first selection period to store charges

corresponding to a current value of the first

designation current between a gate and a source of the

first driving transistor;

- a second designation current step of supplying a second designation current to a second driving transistor within a second selection period after the

10

15

first designation current step to store charges corresponding to a current value of the second designation current between a gate and a source of the second driving transistor; and

a driving current reference voltage output step

of, after the second designation current step,

outputting a driving current reference voltage to the

first driving transistor and a first optical element

which is connected in series with the first driving

transistor and outputting the driving current reference

voltage to the second driving transistor and a second

optical element which is connected in series with the

second driving transistor.

45. A display device driving method according to claim 44, wherein the driving current reference voltage is a voltage at which a source-drain voltage of the first driving transistor and a source-drain voltage of the second driving transistor are set in a saturated state.

1/12

FIG.1

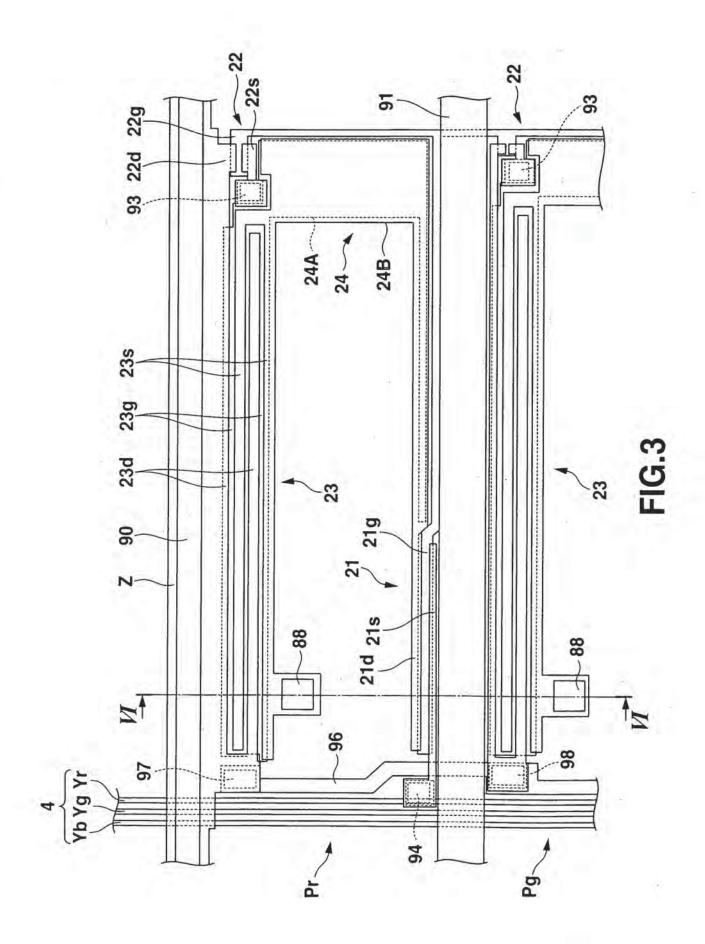

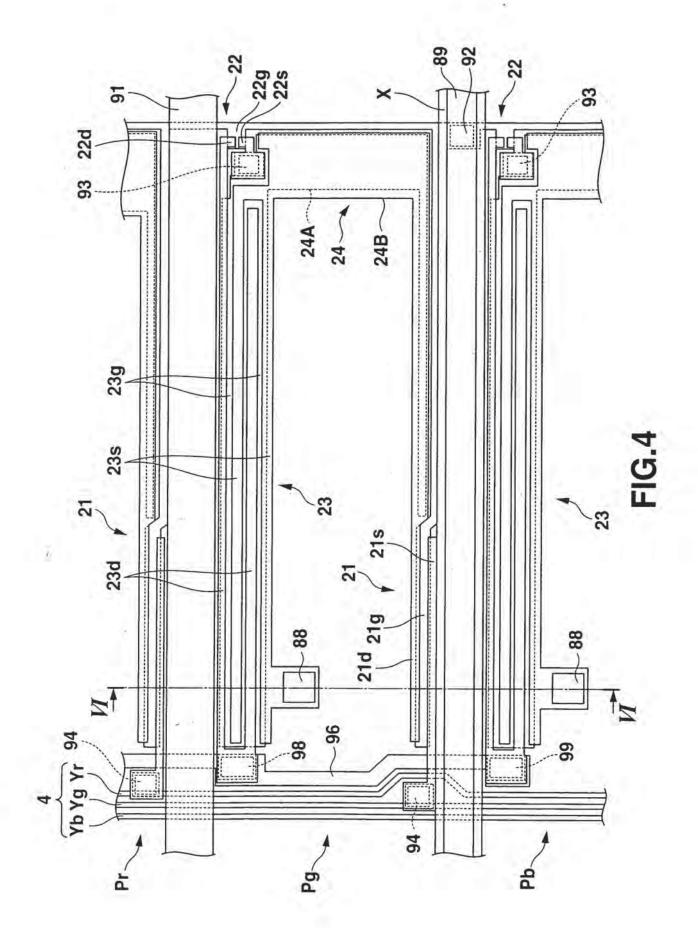

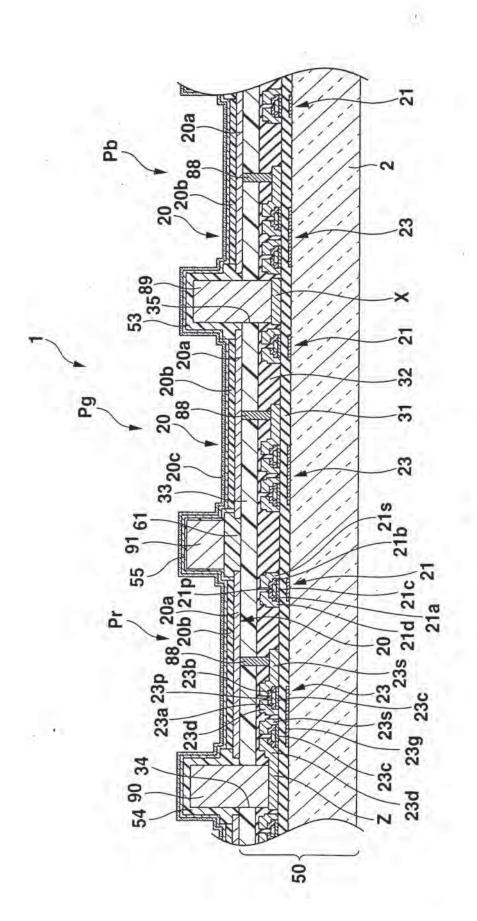

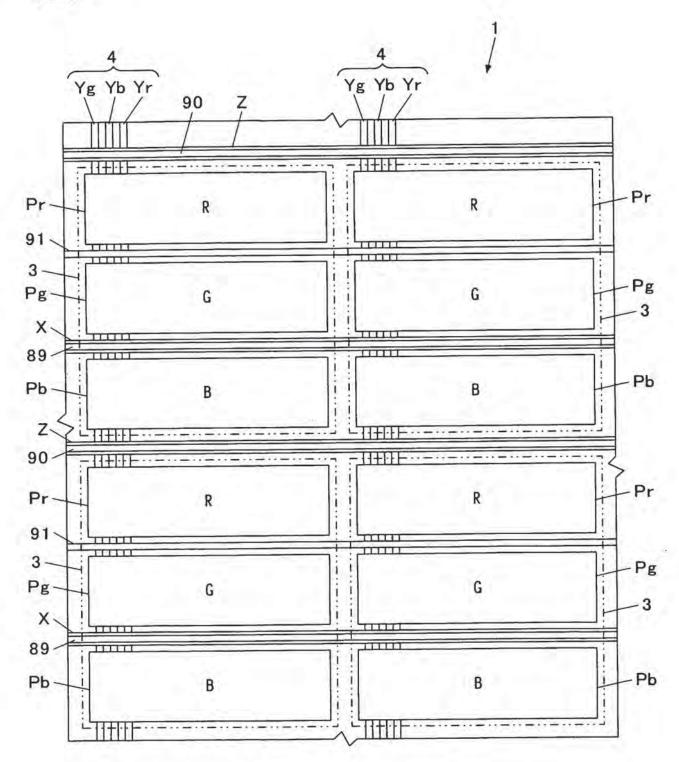

FIG.4

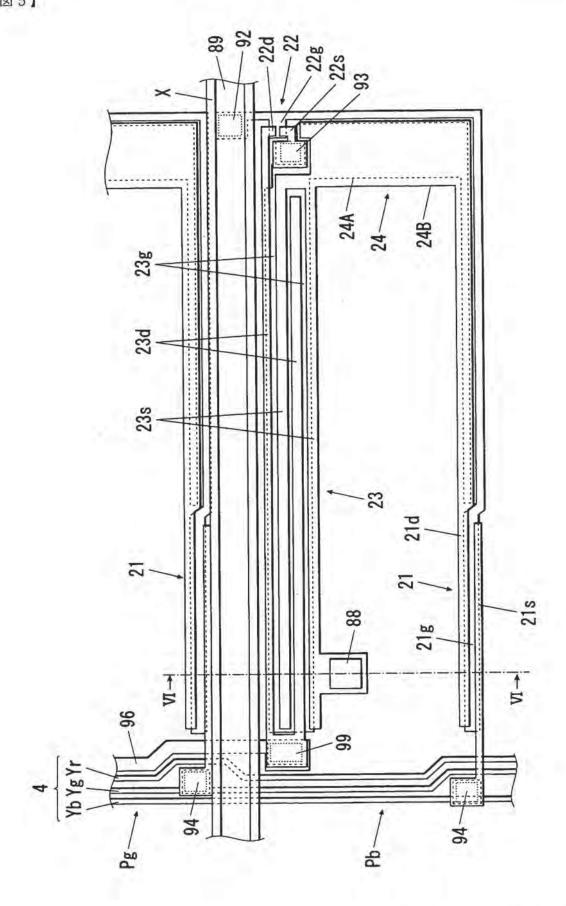

FIG.5

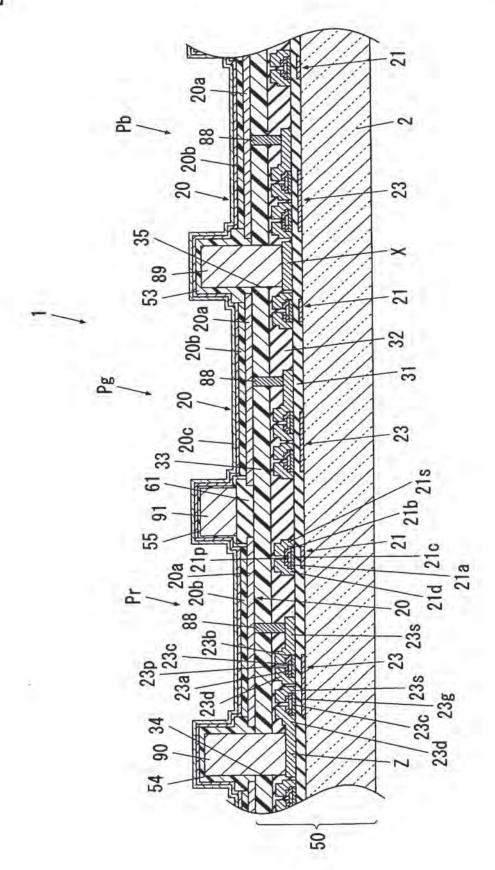

FIG.6

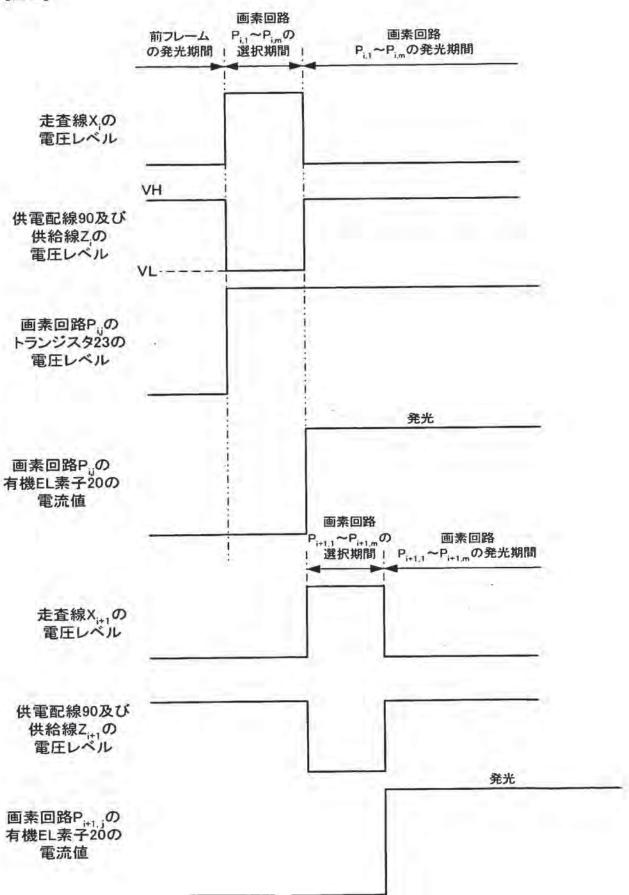

FIG.7

7/12

FIG.8

FIG.9A

FIG.9B

**FIG.10**

10/12

**FIG.11**

## 11/12

FIG.12A

FIG.12B

# INTERNATIONAL SEARCH REPORT

PCT/JP 03/10644

| IPC 7                                                                              | G09G3/32                                                                                                                                                                | 180                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                          |

|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| According to                                                                       | International Patent Classification (IPC) or to both national cla                                                                                                       | ssification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                          |

|                                                                                    | SEARCHED                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                          |

|                                                                                    | cumentation searched (classification system followed by class $6096$                                                                                                    | ification symbols)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                          |

| Documentat                                                                         | ion searched other than minimum documentation to the extent                                                                                                             | that such documents are included in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | e fields searched                                                                                                                                        |

| Instronia d                                                                        | ala base consulted during the international search (name of da                                                                                                          | ata base and, where practical, search ter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | rms used)                                                                                                                                                |

|                                                                                    | ternal, PAJ                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V                                                                                                                                                        |

| C. DOCUM                                                                           | ENTS CONSIDERED TO BE RELEVANT                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                          |

| Category *                                                                         | Cliation of document, with indication, where appropriate, of t                                                                                                          | he relevant passages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Relevant to daim No.                                                                                                                                     |

| P,X                                                                                | WO 03 058328 A (CASIO COMP CO<br>REIJI (JP); YAMADA HIROYASU (C<br>17 July 2003 (2003-07-17)<br>figures 1,7,9                                                           | LTD ;HATTORI JP); SHIRA) -/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1,2,<br>5-20,<br>23-39,<br>41-44                                                                                                                         |

| V Fur                                                                              | ther documents are listed in the continuation of box C.                                                                                                                 | X Patent family members                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | are listed in annex.                                                                                                                                     |

| * Special c  *A' docum cons  *E' earlier filing  *L' docum which cliati  *O' docum | alegories of cited documents :  nent defining the general state of the art which is not idered to be of particular relevance of the international                       | 'T' later document published after or priority date and not in concided to understand the print invention  'X' document of particular relevations an inventive step with the considered to inventive step with the considered to inventive step with the comment is combined with document is combined with the combined with | onflict with the application but ciple or theory underlying the ance; the claimed invention i or cannot be considered to hen the document is taken alone |

| *P* docum                                                                          | r means ment published prior to the International filling date but than the priority date claimed                                                                       | In the art.  '&' document member of the sa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                          |

|                                                                                    | e actual completion of the international search  2 January 2004                                                                                                         | Date of mailing of the intern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ational search report                                                                                                                                    |

|                                                                                    | d malling address of the ISA  European Patent Office, P.B. 5818 Patentlaan 2  NL - 2280 HV Rijswijk  Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,  Fax: (+31-70) 340-3016 | Authorized officer  Gundlach, H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                          |

Form PCT/ISA/210 (second sheet) (July 1992)

# INTERNATIONAL SEARCH REPORT

PCT/JP 03/10644

| .(Continu | ation) DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                  |      | +                     |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|

| tegory °  | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                          |      | Relevant to claim No. |

|           | WO 99 65011 A (KONINKL PHILIPS ELECTRONICS NV; PHILIPS SVENSKA AB (SE)) 16 December 1999 (1999-12-16) page 8, line 5 - line 6; figure 1 page 8, line 9 - line 10 page 8, line 15 - line 18 page 10, line 5 - line 16 page 11, line 25 -page 12, line 14 page 12, line 3 - line 8 page 12, line 31 -page 13, line 16; figure |      | 1-10,<br>15-45        |

|           | page 13, line 2 - line 25<br>page 14, line 26 -page 15, line 7                                                                                                                                                                                                                                                              |      |                       |

|           | EP 1 170 718 A (SEIKO EPSON CORP) 9 January 2002 (2002-01-09) figure 5                                                                                                                                                                                                                                                      |      | 1                     |

| r.        | JP 2002.215095 A (PIONEER ELECTRONIC CORP) 31 July 2002 (2002-07-31) figures 1-8 -& US 2002/135309 A1 (PIONEER ELECTRONIC CORP) 26 September 2002 (2002-09-26)                                                                                                                                                              |      | 11,13                 |

|           |                                                                                                                                                                                                                                                                                                                             | 9 44 |                       |

|           |                                                                                                                                                                                                                                                                                                                             |      |                       |

|           |                                                                                                                                                                                                                                                                                                                             |      |                       |

|           |                                                                                                                                                                                                                                                                                                                             |      |                       |

|           |                                                                                                                                                                                                                                                                                                                             |      |                       |

|           |                                                                                                                                                                                                                                                                                                                             |      |                       |

|           |                                                                                                                                                                                                                                                                                                                             |      |                       |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

PCT/JP 03/10644

| Patent document<br>cited in search report |   | Publication date |                      | Patent family<br>member(s)                             | Publication date           |

|-------------------------------------------|---|------------------|----------------------|--------------------------------------------------------|----------------------------|

| WO 03058328                               | Α | 17-07-2003       | JP<br>WO             | 2003195810 A<br>03058328 A                             | 09-07-2003<br>1 17-07-2003 |

| WO 9965011                                | Α | 16-12-1999       | EP<br>WO<br>JP<br>US | 1034530 A2<br>9965011 A2<br>2002517806 T<br>6373454 B3 | 2 16-12-1999<br>18-06-2002 |

| EP 1170718                                | Α | 09-01-2002       | CN<br>EP<br>WO<br>US | 1388951 T<br>1170718 A<br>0205254 A<br>2002033718 A    | 1 17-01-2002               |

| JP 2002215095                             | A | 31-07-2002       | us                   | 2002135309 A                                           | 1 26-09-2002               |

220 FIFTH AVENUE, NEW YORK, N.Y. 10001-7708

THENAKA HOLTZ MARSHALL I. CHICK RICHARD S. BARTH DOUGLAS HOLTZ ROBERT P. MICHAL TELEPHONE: (212) 319-4900 FACSIMILE: (212) 319-5101

Commissioner for Patents P.O. Box 1450, Alexandria, VA 22313-1450

Express Mail Mailing Label No.: EV 720 476 985 US

Date of Deposit: September 26, 2005

I hereby certify that this paper is being deposited with the United States Postal Service "Express Mail Post Office to Addressee" service under 37 CFR 1.10 on the date indicated above and is addressed to the Commissioner for Patents,

> 'n SIC 7

Box 1450, Alexandria, VA

22313-1450

Bárbara

Attorney Docket No. 05644/LH

CUSTOMER NO. 01933

Pursuant to 37 CFR 1.53(b), transmitted herewith for filing is the patent application of

Tomoyuki SHIRASAKI of Higashiyamato-shi, Japan Tsuyoshi OZAKI of Fuchu-shi, Japan Inventor(s):

Jun OGURA of Fussa-shi, Japan

Title: "DISPLAY PANEL"

Priority Claim (35 U.S.C. 119) is made, based upon:

No. 2004-283824 filed September 29, 2004

ASSIGNMENT INFORMATION FOR PUBLICATION:

Casio Computer Co., Ltd. Tokyo, Japan

Enclosed herewith are:

- Specification (Description, Claims, Abstract): Pages 1 75; Number of claims 1 23

- IX I Declaration and Power of Attorney

- IX1 13 Sheets of drawings, Figures 1 - 13 | X | Formal | | Informal

- Assignment and Recordation Form Cover Sheet (PTO-1595) AND \$40. RECORDATION FEE. IX1

- IXI Certified copy of priority document identified above