#### UNITED STATES PATENT AND TRADEMARK OFFICE

Commissioner for Patents United States Patent and Trademark Office P.O. Box 1450 Alexandria, VA 22313-1450 www.uspto.gov

Konda Technologies, Inc 6278 GRAND OAK WAY SAN JOSE CA 95135 In re Application of : KONDA, Venkat : Application No.: 12/601,275 : PCT No.: PCT/US08/64605 : Int. Filing Date: 22 May 2008 : Priority Date: 25 May 2007 : Att. Doc. No.: V-0045US : For: VLSI LAYOUTS OF FULLY : CONNECTED GENERALIZED : NETWORKS : MAILED

AUG 192019

INTERNATIONAL PATENT LEGAL ADM.

DECISION

Applicant's Petition To Accept Late Payment of the Basic National Fee Under 37 CFR 1.137(a), filed in the above-captioned application on 08 August 2019 is **GRANTED**.

Applicant states that the entire delay in filing the required reply from the due date for the required reply until the filing of a grantable petition was unintentional. The proper response was previously filed on 22 December 2009. The petition fee has been furnished. A terminal disclaimer is not required as the application was filed on or after 08 June 1995. Accordingly, all requirements under 37 CFR 1.137(a) have been satisfied.

/Erin P. Thomson/ Erin P. Thomson Attorney Advisor International Patent Legal Administration 571-272-3292 Application Number: 12/601,275

Art Unit: 2819

Communication Dated: August 8, 2019

### In The United States Patent And Trademark Office

Application Number: 12/601,275

Application Filed: 11/22/2009

Applicant(s): Venkat Konda

Patent No. 8,269,523

5 Title: VLSI Layouts of Fully Connected Generalized Networks Confirmation No: 6372

Examiner/Art Unit: Vibol Tan / 2819

Priority Date: 5/25/2007

San Jose, 2019 August 8

### PETITION TO ACCPET LATE PAYMENT OF THE BASIC NATIONAL FEE UNDER 37 CFR 1.137

Attn: Richard Cole Office of PCT Legal Mail Stop PCT

10

15 Commissioner for PatentsP.O. Box 1450Alexandria, Virginia, 22313-1450

Dear Sir/Madam:

20 For the above referenced application, please accept the payment of the basic national fee as being unintentionally delayed. The entire delay in filing the basic national fee from the due date for the fee until the filing of a grantable petition under 37 CFR 1.137 was unintentional. A check of \$1000, the small entity fee, for this petition is enclosed.

- 25 Very respectfully, /Venkat Konda/

Venkat Konda

6278 Grand Oak Way

San Jose, CA 95135

- 30 Phone: 408-472-3273

| Electronic Patent Application Fee Transmittal        |                                                      |             |          |        |                         |  |

|------------------------------------------------------|------------------------------------------------------|-------------|----------|--------|-------------------------|--|

| Application Number:                                  | 12                                                   | 12601275    |          |        |                         |  |

| Filing Date:                                         | 31-                                                  | 31-May-2010 |          |        |                         |  |

| Title of Invention:                                  | VLSI LAYOUTS OF FULLY CONNECTED GENERALIZED NETWORKS |             |          |        |                         |  |

| First Named Inventor/Applicant Name:                 | Venkat Konda                                         |             |          |        |                         |  |

| Filer:                                               | Venkat Konda                                         |             |          |        |                         |  |

| Attorney Docket Number:                              | V-(                                                  | 0045US      |          |        |                         |  |

| Filed as Small Entity                                |                                                      |             |          |        |                         |  |

| Filing Fees for U.S. National Stage under 35 USC 371 |                                                      |             |          |        |                         |  |

| Description                                          |                                                      | Fee Code    | Quantity | Amount | Sub-Total in<br>USD(\$) |  |

| Basic Filing:                                        |                                                      |             |          |        |                         |  |

| Pages:                                               |                                                      |             |          |        |                         |  |

| Claims:                                              |                                                      |             |          |        |                         |  |

| Miscellaneous-Filing:                                |                                                      |             |          |        |                         |  |

| Petition:                                            |                                                      |             |          |        |                         |  |

| PET. REVIVE ABANDON APP, DELAY PYMT-RESP             |                                                      | 2453        | 1        | 1000   | 1000                    |  |

| Patent-Appeals-and-Interference:                     |                                                      |             |          |        |                         |  |

| Post-Allowance-and-Post-Issuance:                    |                                                      |             |          |        |                         |  |

| Description        | Fee Code | Quantity  | Amount | Sub-Total in<br>USD(\$) |

|--------------------|----------|-----------|--------|-------------------------|

| Extension-of-Time: |          |           |        |                         |

| Miscellaneous:     |          |           |        |                         |

|                    | Tot      | al in USD | (\$)   | 1000                    |

|                    |          |           |        |                         |

| Electronic Ac                        | knowledgement Receipt                                |

|--------------------------------------|------------------------------------------------------|

| EFS ID:                              | 36825423                                             |

| Application Number:                  | 12601275                                             |

| International Application Number:    |                                                      |

| Confirmation Number:                 | 6372                                                 |

| Title of Invention:                  | VLSI LAYOUTS OF FULLY CONNECTED GENERALIZED NETWORKS |

| First Named Inventor/Applicant Name: | Venkat Konda                                         |

| Customer Number:                     | 38139                                                |

| Filer:                               | Venkat Konda                                         |

| Filer Authorized By:                 |                                                      |

| Attorney Docket Number:              | V-0045US                                             |

| Receipt Date:                        | 08-AUG-2019                                          |

| Filing Date:                         | 31-MAY-2010                                          |

| Time Stamp:                          | 16:32:33                                             |

| Application Type:                    | U.S. National Stage under 35 USC 371                 |

## Payment information:

| Submitted with Payment                                                                                         | yes              |  |  |

|----------------------------------------------------------------------------------------------------------------|------------------|--|--|

| Payment Type                                                                                                   | CARD             |  |  |

| Payment was successfully received in RAM                                                                       | \$1000           |  |  |

| RAM confirmation Number                                                                                        | E201988G34075103 |  |  |

| Deposit Account                                                                                                |                  |  |  |

| Authorized User                                                                                                |                  |  |  |

| The Director of the USPTO is hereby authorized to charge indicated fees and credit any overnayment as follows: |                  |  |  |

The Director of the USPTO is hereby authorized to charge indicated fees and credit any overpayment as follows:

### File Listing:

|                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                  |                                                                                                                                          |                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Document<br>Number                                                                                                                                                                                                                                                | <b>Document Description</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | File Name                                                                                                                                                                                                                                                                                                                                                                                              | File Size(Bytes)/<br>Message Digest                                                                                                                                                                                              | Multi<br>Part /.zip                                                                                                                      | Pages<br>(if appl.)                                                                   |

| 1                                                                                                                                                                                                                                                                 | Petition for review by the PCT legal<br>office                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PetUnintDelay-V0045US.pdf                                                                                                                                                                                                                                                                                                                                                                              | 75026<br>dc16c6a0f247024d21c0f54128af4f7c5e1ee<br>3a0                                                                                                                                                                            | no                                                                                                                                       | 1                                                                                     |

| Warnings:                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                  |                                                                                                                                          |                                                                                       |

| Information:                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                  |                                                                                                                                          |                                                                                       |

|                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                        | 30076                                                                                                                                                                                                                            |                                                                                                                                          |                                                                                       |

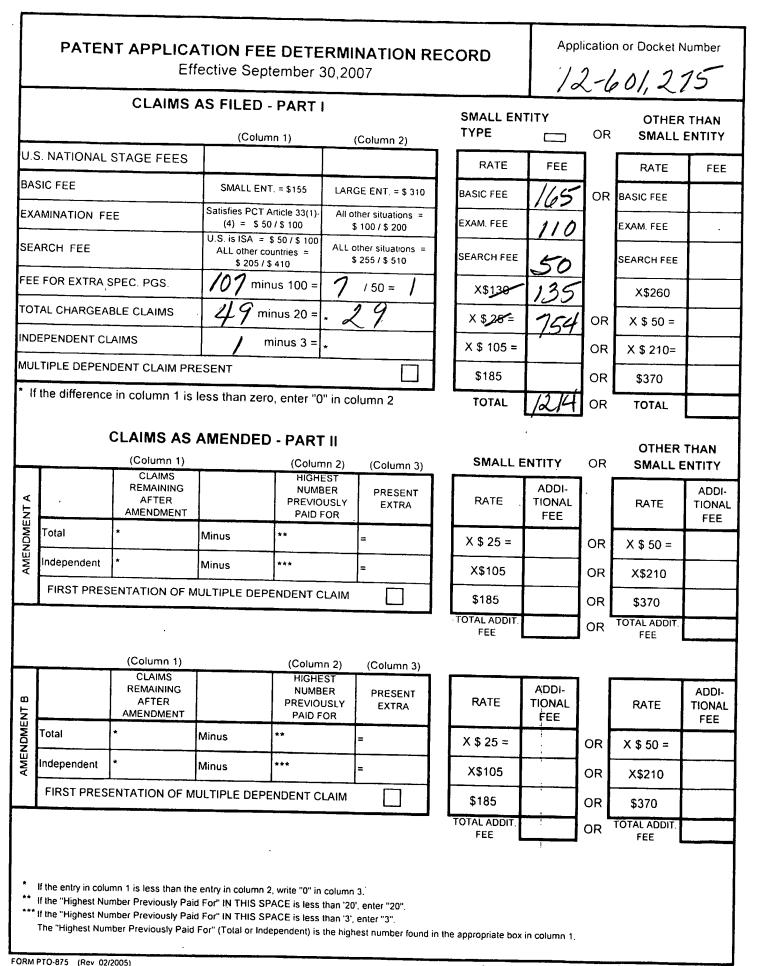

| 2                                                                                                                                                                                                                                                                 | Fee Worksheet (SB06)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | fee-info.pdf                                                                                                                                                                                                                                                                                                                                                                                           | f6cb27709e04fa0fb586944ee8732dc11110<br>b06f                                                                                                                                                                                     | no                                                                                                                                       | 2                                                                                     |

| Warnings:                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                  |                                                                                                                                          |                                                                                       |

| Information:                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                  |                                                                                                                                          |                                                                                       |

|                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Total Files Size (in bytes)                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                | 05102                                                                                                                                    |                                                                                       |

| characterized<br>Post Card, as<br><u>New Applicat</u><br>If a new appli<br>1.53(b)-(d) an<br>Acknowledge<br><u>National Stac</u><br>If a timely sul<br>U.S.C. 371 an<br>national stag<br><u>New Internat</u><br>If a new inter<br>an internatio<br>and of the Int | ledgement Receipt evidences receip<br>d by the applicant, and including pay<br>described in MPEP 503.<br>tions Under 35 U.S.C. 111<br>ication is being filed and the applica<br>of MPEP 506), a Filing Receipt (37 CF<br>ement Receipt will establish the filin<br>ge of an International Application un<br>bmission to enter the national stage<br>d other applicable requirements a F<br>ie submission under 35 U.S.C. 371 with<br>ional Application Filed with the USP<br>national application is being filed an<br>nal filing date (see PCT Article 11 an<br>ternational Filing Date (Form PCT/Re<br>urity, and the date shown on this Ack<br>on. | ge counts, where applicable.<br>tion includes the necessary of<br>R 1.54) will be issued in due<br>g date of the application.<br><u>Inder 35 U.S.C. 371</u><br>of an international applicati<br>orm PCT/DO/EO/903 indicati<br>ill be issued in addition to the<br><u>PTO as a Receiving Office</u><br>and the international applicat<br>d MPEP 1810), a Notification<br>D/105) will be issued in due c | It serves as evidence<br>components for a filir<br>course and the date s<br>ion is compliant with<br>ing acceptance of the<br>e Filing Receipt, in du<br>ion includes the nece<br>of the International<br>ourse, subject to pres | of receipt s<br>ing date (see<br>shown on th<br>the condition<br>application<br>e course.<br>essary comp<br>Application<br>scriptions co | imilar to a<br>37 CFR<br>is<br>ons of 35<br>as a<br>onents for<br>Number<br>oncerning |

Application Number: 12/601,275

Art Unit: 2819

Communication Dated: August 8, 2019

### In The United States Patent And Trademark Office

Application Number: 12/601,275

Application Filed: 11/22/2009

Applicant(s): Venkat Konda

Patent No. 8,269,523

5 Title: VLSI Layouts of Fully Connected Generalized Networks Confirmation No: 6372

Examiner/Art Unit: Vibol Tan / 2819

Priority Date: 5/25/2007

San Jose, 2019 August 8

### PETITION TO ACCPET LATE PAYMENT OF THE BASIC NATIONAL FEE UNDER 37 CFR 1.137

Attn: Richard Cole Office of PCT Legal Mail Stop PCT

10

15 Commissioner for PatentsP.O. Box 1450Alexandria, Virginia, 22313-1450

Dear Sir/Madam:

20 For the above referenced application, please accept the payment of the basic national fee as being unintentionally delayed. The entire delay in filing the basic national fee from the due date for the fee until the filing of a grantable petition under 37 CFR 1.137 was unintentional. A check of \$1000, the small entity fee, for this petition is enclosed.

- 25 Very respectfully, /Venkat Konda/

Venkat Konda

6278 Grand Oak Way

San Jose, CA 95135

- 30 Phone: 408-472-3273

| Electronic Patent Application Fee Transmittal        |                                                      |             |          |        |                         |  |

|------------------------------------------------------|------------------------------------------------------|-------------|----------|--------|-------------------------|--|

| Application Number:                                  | 12                                                   | 12601275    |          |        |                         |  |

| Filing Date:                                         | 31-                                                  | 31-May-2010 |          |        |                         |  |

| Title of Invention:                                  | VLSI LAYOUTS OF FULLY CONNECTED GENERALIZED NETWORKS |             |          |        |                         |  |

| First Named Inventor/Applicant Name:                 | Venkat Konda                                         |             |          |        |                         |  |

| Filer:                                               | Venkat Konda                                         |             |          |        |                         |  |

| Attorney Docket Number:                              | V-(                                                  | 0045US      |          |        |                         |  |

| Filed as Small Entity                                |                                                      |             |          |        |                         |  |

| Filing Fees for U.S. National Stage under 35 USC 371 |                                                      |             |          |        |                         |  |

| Description                                          |                                                      | Fee Code    | Quantity | Amount | Sub-Total in<br>USD(\$) |  |

| Basic Filing:                                        |                                                      |             |          |        |                         |  |

| Pages:                                               |                                                      |             |          |        |                         |  |

| Claims:                                              |                                                      |             |          |        |                         |  |

| Miscellaneous-Filing:                                |                                                      |             |          |        |                         |  |

| Petition:                                            |                                                      |             |          |        |                         |  |

| PET. REVIVE ABANDON APP, DELAY PYMT-RESP             |                                                      | 2453        | 1        | 1000   | 1000                    |  |

| Patent-Appeals-and-Interference:                     |                                                      |             |          |        |                         |  |

| Post-Allowance-and-Post-Issuance:                    |                                                      |             |          |        |                         |  |

| Description        | Fee Code | Quantity  | Amount | Sub-Total in<br>USD(\$) |

|--------------------|----------|-----------|--------|-------------------------|

| Extension-of-Time: |          |           |        |                         |

| Miscellaneous:     |          |           |        |                         |

|                    | Tot      | al in USD | (\$)   | 1000                    |

|                    |          |           |        |                         |

| Electronic Ac                        | knowledgement Receipt                                |

|--------------------------------------|------------------------------------------------------|

| EFS ID:                              | 36824269                                             |

| Application Number:                  | 12601275                                             |

| International Application Number:    |                                                      |

| Confirmation Number:                 | 6372                                                 |

| Title of Invention:                  | VLSI LAYOUTS OF FULLY CONNECTED GENERALIZED NETWORKS |

| First Named Inventor/Applicant Name: | Venkat Konda                                         |

| Customer Number:                     | 38139                                                |

| Filer:                               | Venkat Konda                                         |

| Filer Authorized By:                 |                                                      |

| Attorney Docket Number:              | V-0045US                                             |

| Receipt Date:                        | 08-AUG-2019                                          |

| Filing Date:                         | 31-MAY-2010                                          |

| Time Stamp:                          | 15:45:01                                             |

| Application Type:                    | U.S. National Stage under 35 USC 371                 |

# Payment information:

| Submitted with Payment                         |                                              |                           | no        |                                     |                     |                     |  |

|------------------------------------------------|----------------------------------------------|---------------------------|-----------|-------------------------------------|---------------------|---------------------|--|

| File Listing                                   | g:                                           |                           |           |                                     |                     |                     |  |

| Document<br>Number                             | <b>Document Description</b>                  |                           | File Name | File Size(Bytes)/<br>Message Digest | Multi<br>Part /.zip | Pages<br>(if appl.) |  |

|                                                |                                              | PetUnintDelay-V0045US.pdf |           | 75026                               |                     |                     |  |

| Petition for review by the PCT legal<br>office | dc16c6a0f247024d21c0f54128af4f7c5e1ee<br>3a0 |                           |           | no                                  | 1                   |                     |  |

| Warnings:                                      |                                              |                           |           | ł                                   | ľ                   |                     |  |

| 30076                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                             |

| 2 Fee Worksheet (SB06) fee-info.pdf no 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2                                                                                                                                           |

| Warnings:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ngs:                                                                                                                                        |

| Information:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nation:                                                                                                                                     |

| Total Files Size (in bytes): 105102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                             |

| characterized by the applicant, and including page counts, where applicable. It serves as evidence of receipt similar t<br>Post Card, as described in MPEP 503.<br><u>New Applications Under 35 U.S.C. 111</u><br>If a new application is being filed and the application includes the necessary components for a filing date (see 37 CFR<br>1.53(b)-(d) and MPEP 506), a Filing Receipt (37 CFR 1.54) will be issued in due course and the date shown on this<br>Acknowledgement Receipt will establish the filing date of the application.<br><u>National Stage of an International Application under 35 U.S.C. 371</u><br>If a timely submission to enter the national stage of an international application is compliant with the conditions of 3<br>U.S.C. 371 and other applicable requirements a Form PCT/DO/EO/903 indicating acceptance of the application as a<br>national stage submission under 35 U.S.C. 371 will be issued in addition to the Filing Receipt, in due course.<br><u>New International Application Filed with the USPTO as a Receiving Office</u><br>If a new international application is being filed and the international application includes the necessary components<br>an international filing date (see PCT Article 11 and MPEP 1810), a Notification of the International Application Numbu<br>and of the International Filing Date (Form PCT/RO/105) will be issued in due course, subject to prescriptions concernin<br>national security, and the date shown on this Acknowledgement Receipt will establish the international filing date of<br>the shown on this Acknowledgement Receipt will establish the international filing date of<br>the shown on this Acknowledgement Receipt will establish the international filing date of<br>the shown on this Acknowledgement Receipt will establish the international filing date of<br>the shown on this Acknowledgement Receipt will establish the international filing date of<br>the shown on this Acknowledgement Receipt will establish the international filing date of<br>the shown on this Acknowledgement Receipt will establish the international filing date of | ard, as d<br>pplication<br>w applic<br>b)-(d) and<br>bwledger<br>nal Stage<br>nely sub-<br>al stage<br>nternation<br>ernation<br>f the Inte |

# 505428057 04/15/2019

### PATENT ASSIGNMENT COVER SHEET

Electronic Version v1.1 Stylesheet Version v1.2 EPAS ID: PAT5474857

| SUBMISSION TYPE:                                                                       |          | NE                         | W ASSIGNMENT                           |           |                           |

|----------------------------------------------------------------------------------------|----------|----------------------------|----------------------------------------|-----------|---------------------------|

| NATURE OF CONVEYANCE:                                                                  |          |                            | SIGNMENT                               |           |                           |

| CONVEYING PARTY D                                                                      | ΑΤΑ      | <b>I</b>                   |                                        |           |                           |

|                                                                                        |          | Nai                        | me                                     |           | Execution Date            |

| KONDA TECHNOLOGIE                                                                      | ES INC.  |                            |                                        |           | 04/15/2019                |

| RECEIVING PARTY DA                                                                     |          |                            |                                        |           |                           |

| Name:                                                                                  |          |                            | A                                      |           |                           |

| Street Address:                                                                        |          | ARAND O                    |                                        |           |                           |

| City:                                                                                  | SAN JO   |                            |                                        |           |                           |

| State/Country:                                                                         | CALIFO   |                            |                                        |           |                           |

| Postal Code:                                                                           | 95135    |                            |                                        |           |                           |

|                                                                                        |          |                            |                                        |           |                           |

| PROPERTY NUMBERS                                                                       | Total: 2 | 2                          |                                        |           |                           |

| Property Type                                                                          |          |                            | Number                                 |           |                           |

| Patent Number: 8269                                                                    |          | 8269523                    |                                        |           |                           |

| Application Number: 16202067                                                           |          |                            |                                        |           |                           |

|                                                                                        |          |                            |                                        |           |                           |

| Fax Number:                                                                            |          | (408)238                   | -2478                                  |           |                           |

|                                                                                        |          | . ,                        | ail address first; if that             | is unsud  | cessful, it will be sent  |

| using a fax number, if                                                                 | providea | d; if that i               | is unsuccessful, it will l             |           |                           |

| Phone:                                                                                 |          | 4084723                    |                                        |           |                           |

| Email:                                                                                 |          |                            | kondatech.com                          |           |                           |

| Correspondent Name: KONDA TECHNOLOGIES INC.                                            |          |                            |                                        |           |                           |

| •                                                                                      |          |                            |                                        |           |                           |

| Address Line 1:<br>Address Line 4:                                                     |          |                            | SE, CALIFORNIA 95135                   |           |                           |

| Address Line 1:<br>Address Line 4:                                                     |          | SAN JOS                    |                                        |           |                           |

| Address Line 1:<br>Address Line 4:<br>NAME OF SUBMITTER:                               |          | SAN JOS                    | ENKAT KONDA                            |           |                           |

| Address Line 1:<br>Address Line 4:<br>NAME OF SUBMITTER:<br>SIGNATURE:                 |          | SAN JOS<br>VE<br>/ve       | ENKAT KONDA<br>enkat Konda/            |           |                           |

| Address Line 1:<br>Address Line 4:<br>NAME OF SUBMITTER:<br>SIGNATURE:                 |          | SAN JOS<br>VE<br>/ve<br>04 | NKAT KONDA<br>enkat Konda/<br>/15/2019 |           | $\sim$                    |

| Address Line 1:<br>Address Line 4:<br>NAME OF SUBMITTER:<br>SIGNATURE:<br>DATE SIGNED: |          | SAN JOS<br>VE<br>/ve<br>04 | NKAT KONDA<br>enkat Konda/<br>/15/2019 | n Oath/De | eclaration (37 CFR 1.63). |

| Address Line 1:<br>Address Line 4:<br>NAME OF SUBMITTER:<br>SIGNATURE:                 |          | SAN JOS<br>VE<br>/ve<br>04 | NKAT KONDA<br>enkat Konda/<br>/15/2019 | n Oath/De | eclaration (37 CFR 1.63). |

#### ASSIGNMENT OF PATENTS

WHEREAS, Konda Technologies, Inc., a California corporation, located at 6278 Grand Oak Way, San Jose, CA 95135, hereinafter referred to as "Assignor," is the record owner of the patents described as

- Title: VLSI Layouts of Fully Connected Generalized Networks US Patent No.: 8,269,523 Patent Issue Date: September 18, 2012;

- Title: VLSI Layouts of Fully Connected Generalized Networks US Patent Application No.: 16/202,067 Patent Filing Date: November 27, 2018;

WHEREAS, Konda, Venkat of San Jose, California, having a residence at 6278 Grand Oak Way, San Jose, CA, hereinafter referred to as "ASSIGNEE," wishes to acquire all right, title and interest to and under the patents described above owned by Assignor and in and to any and all improvements to said applications and in any Letters Patent and Registrations which may be granted on the same in the United States or any country throughout the world;

For good and valuable consideration, receipt of which is hereby acknowledged by Assignor, effective 15<sup>th</sup> day of April, 2019, has assigned, and by these presents does assign to Assignee all right, title and interest for the United States and all foreign countries, in and to any and all improvements for the applications described above and in and to said applications and to all utility divisional continuing, substitute, renewal, reissue, and all other patent applications which have been or shall be filed in the United States and all foreign counterparts (including patent, utility model and industrial designs), and in and to any Letters Patent and Registrations which may hereafter be granted on the same in the United States and all countries throughout the world, and to claim the priority from the application as provided by the Paris Convention. The right, title and interest is to be held and enjoyed by Assignee and Assignee's successors and assigns as fully and exclusively as it would have been held and enjoyed by Assignor had this Assignment not been made, for the full term of any Letters Patent and Registrations which may be granted thereon, or of any division, renewal, continuation in whole or in part, substitution, conversion, reissue, prolongation or extension thereof.

Assignor further agrees that they will, without charge to Assignee, but at Assignee's expense, (a) cooperate with Assignee in the prosecution of U.S. Patent applications and foreign counterparts on the applications and any improvements, (b) execute, verify, acknowledge and deliver all such further papers, including patent applications and instruments of transfer, and (c) perform such other acts as Assignee lawfully may request to obtain or maintain Letters Patent and Registrations for the applications and improvements in any and all countries, and to vest title thereto in Assignee, or Assignee's successors and assigns. Page 2

IN TESTIMONY WHEREOF, Assignor has signed on the date indicated.

Date: 4/15/2019 By: Vanka

- 1(r Venkat Konda (Founder/CEO)

Venkat Konda (Founder/CEC Konda Technologies Inc. 6278 Grand Oak Way San Jose, CA 95135

UNITED STATES PATENT AND TRADEMARK OFFICE

| UNITED STATES DEPARTMENT OF COMMERCE<br>United States Patent and Trademark Office |

|-----------------------------------------------------------------------------------|

| Address: COMMISSIONER FOR PATENTS                                                 |

| P.O. Box 1450                                                                     |

| Alexandria, Virginia 22313-1450                                                   |

| www.uspto.gov                                                                     |

| APPLICATION NO. | ISSUE DATE     | PATENT NO. | ATTORNEY DOCKET NO. | CONFIRMATION NO. |

|-----------------|----------------|------------|---------------------|------------------|

| 12/601,275      | 09/18/2012     | 8269523    | V-0045US            | 6372             |

| 38139 7         | 590 08/29/2012 |            |                     |                  |

Konda Technologies, Inc 6278 GRAND OAK WAY SAN JOSE, CA 95135

### **ISSUE NOTIFICATION**

The projected patent number and issue date are specified above.

### Determination of Patent Term Adjustment under 35 U.S.C. 154 (b)

(application filed on or after May 29, 2000)

The Patent Term Adjustment is 183 day(s). Any patent to issue from the above-identified application will include an indication of the adjustment on the front page.

If a Continued Prosecution Application (CPA) was filed in the above-identified application, the filing date that determines Patent Term Adjustment is the filing date of the most recent CPA.

Applicant will be able to obtain more detailed information by accessing the Patent Application Information Retrieval (PAIR) WEB site (http://pair.uspto.gov).

Any questions regarding the Patent Term Extension or Adjustment determination should be directed to the Office of Patent Legal Administration at (571)-272-7702. Questions relating to issue and publication fee payments should be directed to the Application Assistance Unit (AAU) of the Office of Data Management (ODM) at (571)-272-4200.

APPLICANT(s) (Please see PAIR WEB site http://pair.uspto.gov for additional applicants):

Venkat Konda, San Jose, CA;

The United States represents the largest, most dynamic marketplace in the world and is an unparalleled location for business investment, innovation, and commercialization of new technologies. The USA offers tremendous resources and advantages for those who invest and manufacture goods here. Through SelectUSA, our nation works to encourage and facilitate business investment. To learn more about why the USA is the best country in the world to develop technology, manufacture products, and grow your business, visit <u>SelectUSA.gov</u>.

5

10

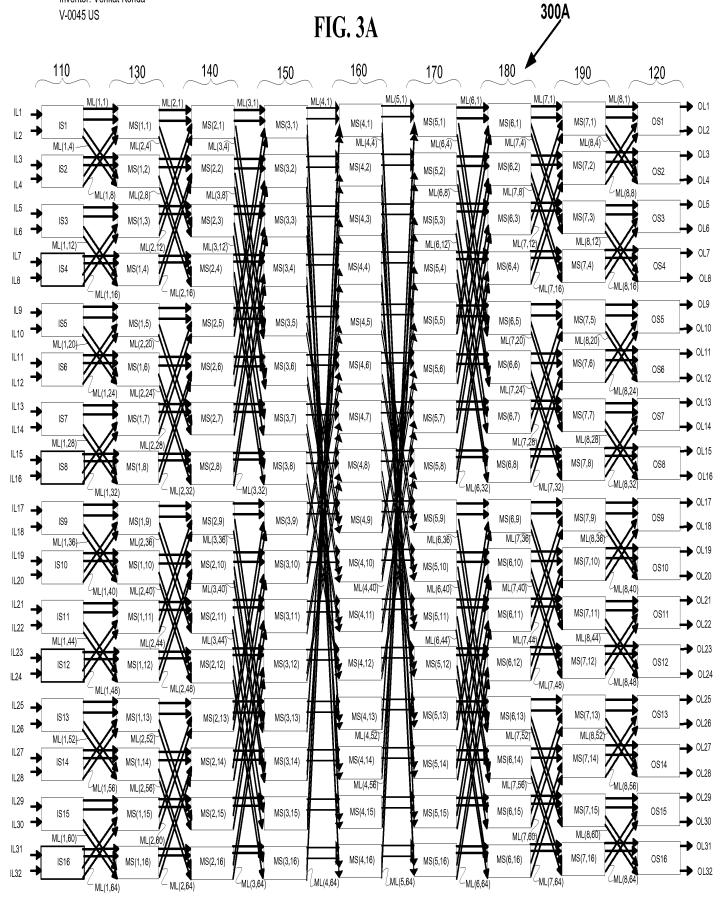

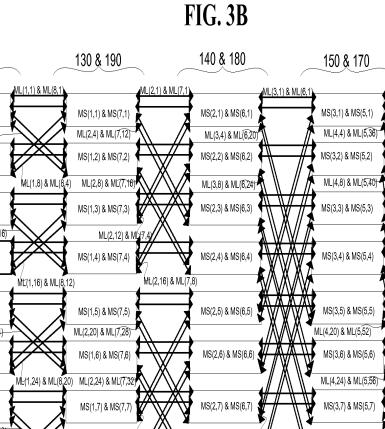

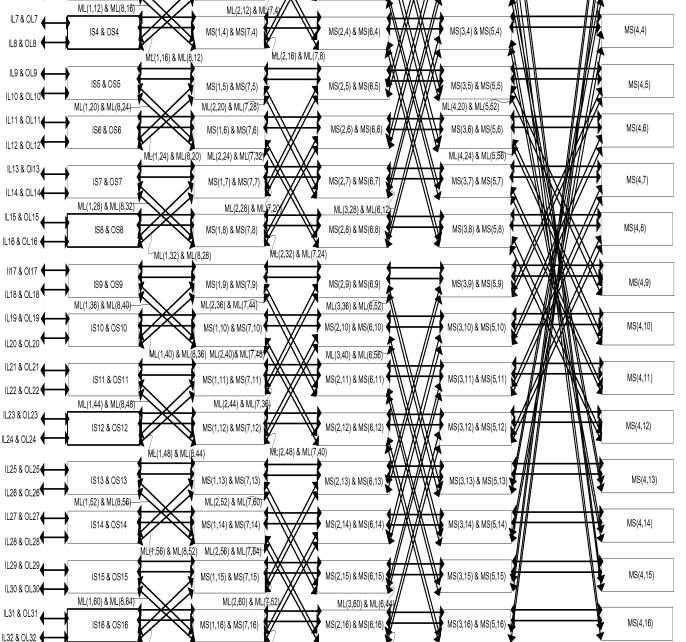

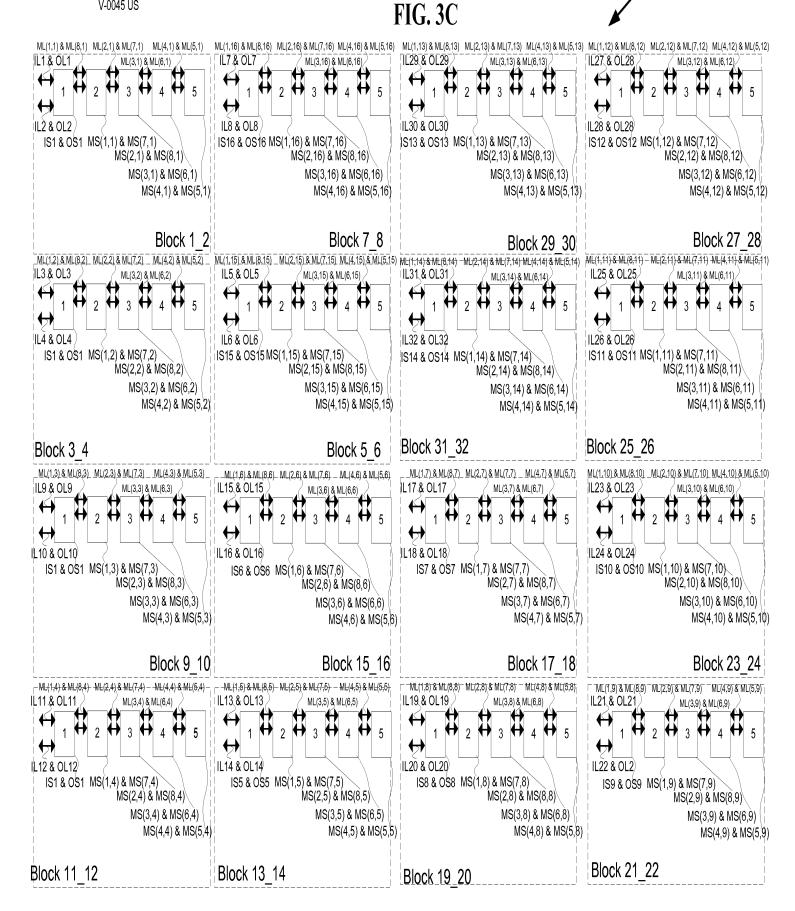

Change(s) applied to document, /D.H.P./ 6/29/2012 This application is related to and incorporates by reference in its entirety the US 12/601273 Patent Application Docket No. V-0038US entitled "FULLY CONNECTED GENERALIZED BUTTERFLY FAT TREE NETWORKS" by Venkat Konda assigned to the same assignee as the current application filed concurrently, the PCT Application Serial No. PCT/US08/64603 entitled "FULLY CONNECTED GENERALIZED BUTTERFLY FAT TREE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 22, 2008, the U.S. Provisional Patent Application Serial No. 60/940, 387 entitled "FULLY CONNECTED GENERALIZED BUTTERFLY FAT TREE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007, and the U.S. Provisional Patent Application Serial No. 60/940, 390 entitled "FULLY CONNECTED GENERALIZED BUTTERFLY FAT TREE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007, and the U.S. Provisional Patent Application Serial No. 60/940, 390 entitled "FULLY CONNECTED GENERALIZED MULTI-LINK BUTTERFLY FAT TREE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007.

This application is related to and incorporates by reference in its entirety the US 12/601274

- 15 Patent Application Doeket No. V-0039US entitled "FULLY CONNECTED GENERALIZED MULTI-LINK MULTI-STAGE NETWORKS" by Venkat Konda assigned to the same assignee as the current application filed concurrently, the PCT Application Serial No. PCT/US08/64604 entitled "FULLY CONNECTED GENERALIZED MULTI-LINK MULTI-STAGE NETWORKS" by Venkat Konda

- 20 assigned to the same assignee as the current application, filed May 22, 2008, the U.S. Provisional Patent Application Serial No. 60/940, 389 entitled "FULLY CONNECTED GENERALIZED REARRANGEABLY NONBLOCKING MULTI-LINK MULTI-STAGE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007, the U.S. Provisional Patent Application Serial No.

- 25 60/940, 391 entitled "FULLY CONNECTED GENERALIZED FOLDED MULTI-STAGE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007 and the U.S. Provisional Patent Application Serial No. 60/940, 392 entitled "FULLY CONNECTED GENERALIZED STRICTLY NONBLOCKING MULTI-LINK MULTI-STAGE NETWORKS" by Venkat Konda

- 30 assigned to the same assignee as the current application, filed May 25, 2007.

#### PART B - FEE(S) TRANSMITTAL

#### Complete and send this form, together with applicable fee(s), to: Mail Mail Stop ISSUE FEE

#### **Commissioner** for Patents P.O. Box 1450 Alexandria, Virginia 22313-1450 or Fax (571) 273-2885

INSTRUCTIONS: This form should be used for transmitting the ISSUE FEE and PUBLICATION FEE (if required). Blocks 1 through 5 should be completed where appropriate. All further correspondence including the Patent, advance orders and notification of maintenance fees will be mailed to the current correspondence address as indicated unless corrected below or directed otherwise in Block 1, by (a) specifying a new correspondence address; and/or (b) indicating a separate "FEE ADDRESS" for maintenance fees will be mailed to the current correspondence of the second maintenance fee notifications

CURRENT CORRESPONDENCE ADDRESS (Note: Use Block 1 for any change of address)

Note: A certificate of mailing can only be used for domestic mailings of the Fee(s) Transmittal. This certificate cannot be used for any other accompanying papers. Each additional paper, such as an assignment or formal drawing, must have its own certificate of mailing or transmission.

#### **Certificate of Mailing or Transmission**

I hereby certify that this Fee(s) Transmittal is being deposited with the United States Postal Service with sufficient postage for first class mail m an envelope addressed to the Mail Stop ISSUE FEE address above, or being facsimile transmitted to the USPTO (571) 273-2885, on the date indicated below.

|                   | VEC          | ¢970         | ¢200            | ¢1170               | 8/17/0010          |

|-------------------|--------------|--------------|-----------------|---------------------|--------------------|

| APPLN. TYPE       | SMALL ENTITY | ISSUE FEE    | PUBLICATION FEE | TOTAL FEE(S) DUE    | DATE DUE           |

| ILE OF INVENTION: |              |              |                 |                     |                    |

| 12/601,275        | 5/31/2010    | Venkat Konda |                 | V-0045US            | 6372               |

| APPLICATION NO.   | FILING DATE  | FIRST NAM    | IED INVENTOR    | ATTORNEY DOCKET NO. | CONFIRMATION NO.   |

|                   |              |              |                 |                     | (Date)             |

|                   |              |              |                 |                     | (Signature)        |

|                   |              |              |                 |                     | (Depositor's name) |

|   | nonprovisional                            | YES                      | \$870           |                              | \$300                                                  | \$117       | 0 | 8/17/2012 |  |

|---|-------------------------------------------|--------------------------|-----------------|------------------------------|--------------------------------------------------------|-------------|---|-----------|--|

|   | EXAMINER                                  |                          | ART UN          | IT                           | CLASS-SUBCLASS                                         |             |   |           |  |

|   |                                           |                          |                 |                              |                                                        |             |   |           |  |

|   | 1. Change of correspondence addre         | ess or indication of "Fe | ee Address" (37 | 2. For prir                  | ting on the patent front page, list                    |             |   |           |  |

| ę | CFR 1.363).<br>Change of correspondence a | ddress (or Change of     | Correspondence  | (1) the nation of agents (1) | mes of up to 3 registered patent<br>DR, alternatively, | attorneys 1 |   |           |  |

|   | Address form PTO/SB/122) atta             | ached.                   |                 | (2) the nor                  | ne of a single firm (having as a r                     | nembera 2   |   |           |  |

| Address form P1O/SB/122) attached.<br>"Fee Address" indication (or "Fee Address" Indication form<br>PTO/SB/47; Rev 03-02 or more recent) attached. Use of a Customer<br>Number is required. | (2) the name of a single firm (having as a member a registered attorney or agent) and the names of up to 2 registered patent attorneys or agents. If no name is listed, no name will be printed. | 2<br>3 |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|

3. ASSIGNEE NAME AND RESIDENCE DATA TO BE PRINTED ON THE PATENT (print or type)

PLEASE NOTE: Unless an assignee is identified below, no assignee data will appear on the patent. If an assignee is identified below, the document has been filed for recordation as set forth in 37 CFR 3.11. Completion of this form is NOT a substitute for filing an assignment.

| (A) NAME OF ASSIGNEE    | (B) RESIDENCE: (CITY and STATE OR COUNTRY) |

|-------------------------|--------------------------------------------|

| Konda Technologies Inc. | San Jose, CA                               |

| Please check the appropriate assignee category or ca | ategories (will not be printed on the patent) : Individ | ual Corporation or other private group entity Government |

|------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------|

| 4a. The following fee(s) are enclosed:               | 4b. Payment of Fee(s):                                  |                                                          |

| 🗹 Issue Fee                                          | A check in the amount of the t                          | fee(s) is enclosed.                                      |

| Publication Fee (No small entity discount permitted)     | Payment by credit card. Form PTO-2038 is attached.                                                                    |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Advance Order - # of Copies _                            | The Director is hereby authorized to charge the required fee(s), or credit any overpayment, to Deposit Account Number |

| 5. Change in Entity Status (from status indicated above) |                                                                                                                       |

a. Applicant claims SMALL ENTITY status. See 37 CFR 1.27. b. Applicant is no longer claiming SMALL ENTITY status. See 37 CFR 1.27(g)(2).