#### **VENKAT KONDA EXHIBIT 2005**

UNITED STATES PATENT AND TRADEMARK OFFICE

Commissioner for Patents United States Patent and Trademark Office P.O. Box 1450 Alexandria, VA 22313-1450 www.uspto.gov

#### Konda Technologies, Inc 6278 GRAND OAK WAY SAN JOSE CA 95135

# MAILED

NOV 27 2019

INTERNATIONAL PATENT LEGAL ADM.

| In re Application of          | : |          |

|-------------------------------|---|----------|

| Konda Technologies Inc.       | : |          |

| Application No.: 16/202,067   | : | DECISION |

| Filing Date: 27 November 2018 | : |          |

| Attorney Docket No.: V-0070US | : |          |

This Decision is in response to the filing of "Petition To Withdraw the Prior Filed Petition on 11/27/2018 To Accept The Unintentionally Delayed Claim Under 35 U.S.C. 119(e)," in the United States Patent and Trademark Office on 17 September 2019.

This application does not contain a delayed claim of benefit. A petition for the unintentionally delayed payment of the basic national fee under 37 CFR 1.137(a) was accepted in 12/601,275.

Applicant's request to withdraw the petition and refund the petition fee is **GRANTED**.

/Erin P. Thomson/ Erin P. Thomson Attorney Advisor International Patent Legal Administration 571-272-3292

| Electronic Acknowledgement Receipt   |                                                      |  |  |  |  |

|--------------------------------------|------------------------------------------------------|--|--|--|--|

| EFS ID:                              | 37235943                                             |  |  |  |  |

| Application Number:                  | 16202067                                             |  |  |  |  |

| International Application Number:    |                                                      |  |  |  |  |

| Confirmation Number:                 | 8134                                                 |  |  |  |  |

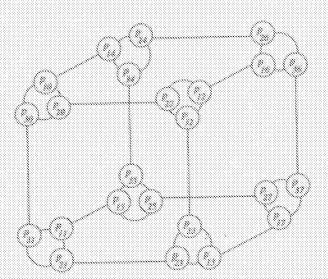

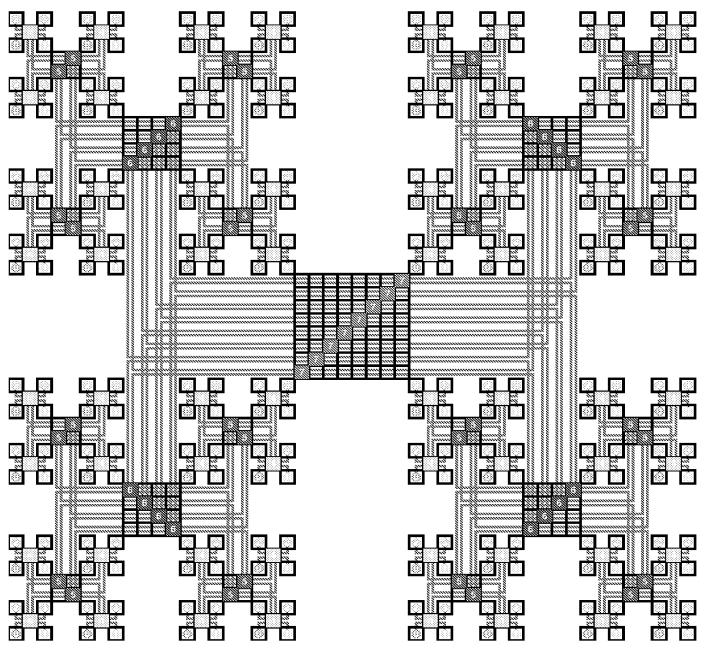

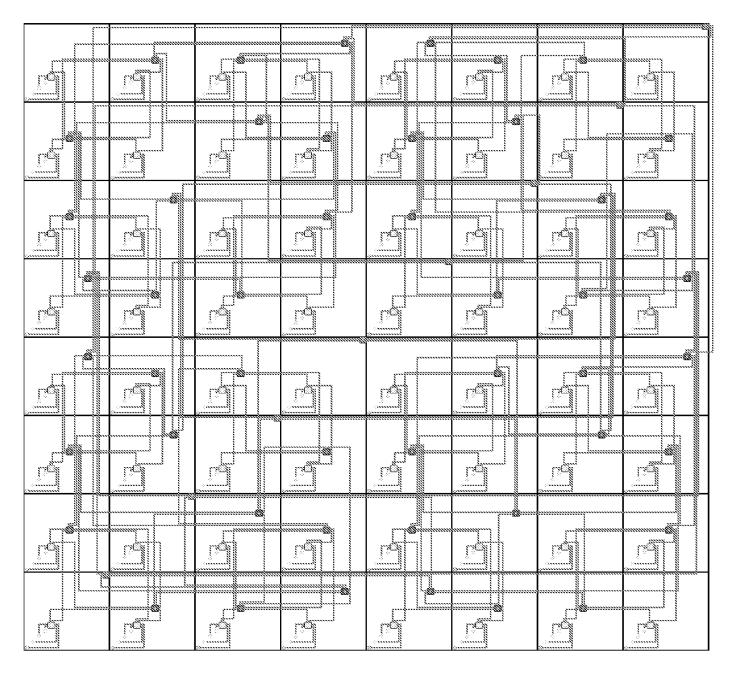

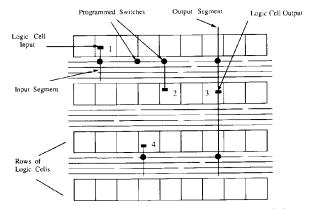

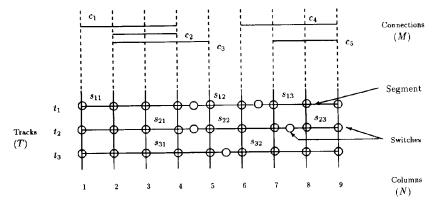

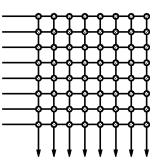

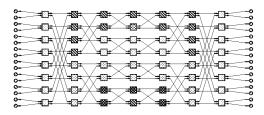

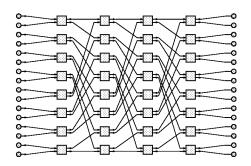

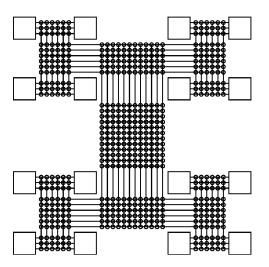

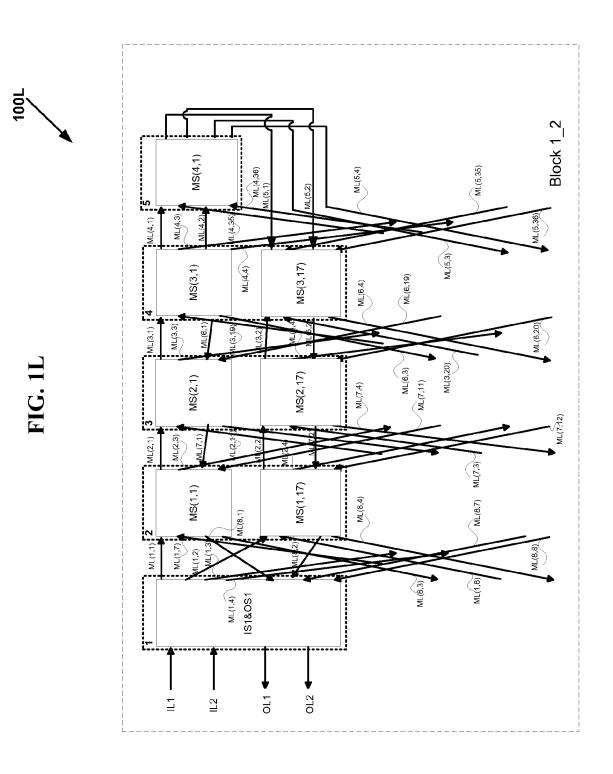

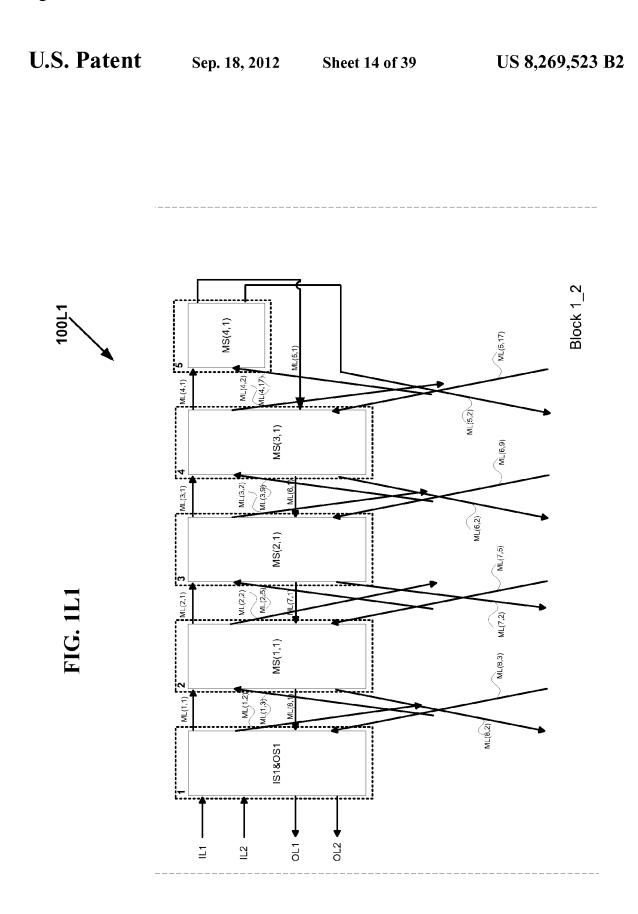

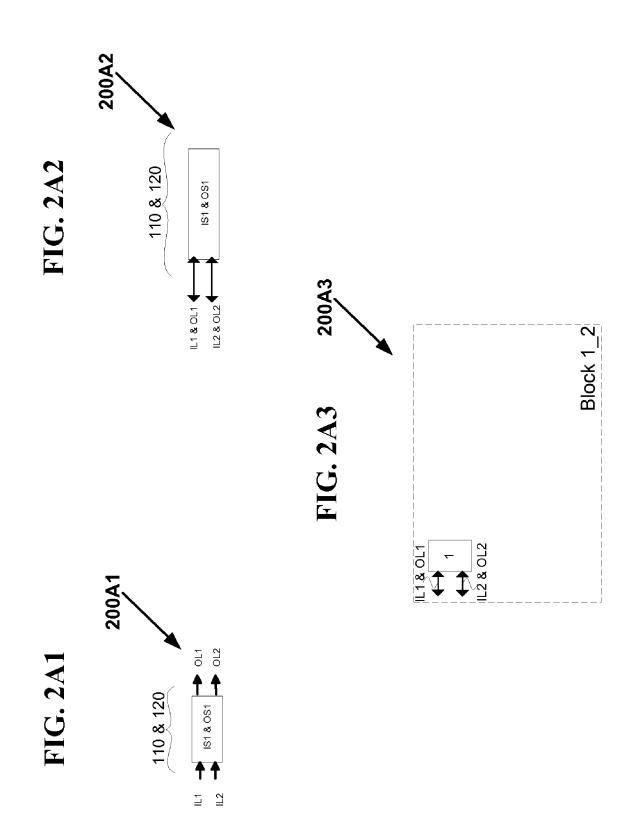

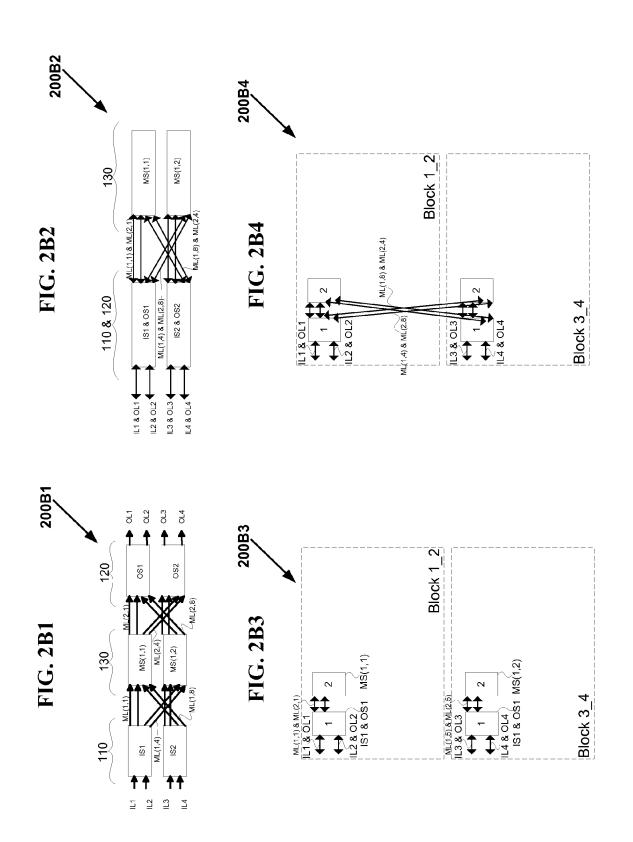

| Title of Invention:                  | VLSI Layouts of Fully Connected Generalized Networks |  |  |  |  |

| First Named Inventor/Applicant Name: | Venkat Konda                                         |  |  |  |  |

| Customer Number:                     | 38139                                                |  |  |  |  |

| Filer:                               | Venkat Konda                                         |  |  |  |  |

| Filer Authorized By:                 |                                                      |  |  |  |  |

| Attorney Docket Number:              | V-0070US                                             |  |  |  |  |

| Receipt Date:                        | 23-SEP-2019                                          |  |  |  |  |

| Filing Date:                         | 27-NOV-2018                                          |  |  |  |  |

| Time Stamp:                          | 01:08:04                                             |  |  |  |  |

| Application Type:                    | Utility under 35 USC 111(a)                          |  |  |  |  |

# Payment information:

| Submitted with Payment |                                                   |  | no                  |                                                        |                     |                     |  |  |

|------------------------|---------------------------------------------------|--|---------------------|--------------------------------------------------------|---------------------|---------------------|--|--|

| File Listing:          |                                                   |  |                     |                                                        |                     |                     |  |  |

| Document<br>Number     | Document Description                              |  | File Name           | File Size(Bytes)/<br>Message Digest                    | Multi<br>Part /.zip | Pages<br>(if appl.) |  |  |

| 1                      | Reissue dec filed in accordance with<br>MPEP 1414 |  | V0070US-aia0005.pdf | 218167<br>eb6d66b02b0eb8f341153179cc12222cd75<br>0b95d | no                  | 3                   |  |  |

| Warnings:              |                                                   |  |                     | ļ                                                      |                     |                     |  |  |

Page 3 of 626 IPR2020-00261

### VENKAT KONDA EXHIBIT 2005

| Information: |  |

|--------------|--|

| mormation.   |  |

| 2                                                                                                                                                                                                                                                       | Preliminary Amendment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 238878<br>4e11df3fe54386626c1600c646245d906699<br>7be9                                                                                                                                                                                                                                                                                                                                                      | no                                                                                                                                                                                                                                      | 26                                                                                                                                    |                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Warnings:                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                         |                                                                                                                                       |                                                                                         |

| Information                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                         |                                                                                                                                       |                                                                                         |

|                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Total Files Size (in bytes):                                                                                                                                                                                                                                                                                                                                                                                | 4                                                                                                                                                                                                                                       | 57045                                                                                                                                 |                                                                                         |

| characterize<br>Post Card, as<br><u>New Applica</u><br>If a new appl<br>1.53(b)-(d) a<br>Acknowledg<br><u>National Sta</u><br>If a timely su<br>U.S.C. 371 ar<br>national stag<br><u>New Interna</u><br>If a new international<br>an international stag | ledgement Receipt evidences receip<br>d by the applicant, and including page<br>described in MPEP 503.<br><u>tions Under 35 U.S.C. 111</u><br>lication is being filed and the applican<br>nd MPEP 506), a Filing Receipt (37 CF<br>ement Receipt will establish the filin<br>ge of an International Application ur<br>bmission to enter the national stage<br>of other applicable requirements a F<br>ge submission under 35 U.S.C. 371 with<br>tional Application Filed with the USP<br>rnational application is being filed an<br>onal filing date (see PCT Article 11 an<br>ternational Filing Date (Form PCT/Re<br>urity, and the date shown on this Ack<br>on. | ge counts, where applicable.<br>tion includes the necessary of<br>R 1.54) will be issued in due of<br>g date of the application.<br><u>Inder 35 U.S.C. 371</u><br>of an international applicati<br>orm PCT/DO/EO/903 indicati<br>ill be issued in addition to the<br><u>PTO as a Receiving Office</u><br>and the international applicati<br>d MPEP 1810), a Notification<br>D/105) will be issued in due co | It serves as evidence<br>components for a filin<br>course and the date s<br>on is compliant with<br>ng acceptance of the<br>e Filing Receipt, in du<br>ion includes the nece<br>of the International <i>i</i><br>ourse, subject to pres | of receipt s<br>og date (see<br>hown on th<br>the condition<br>application<br>e course.<br>ssary comp<br>Application<br>scriptions co | imilar to a<br>37 CFR<br>is<br>ons of 35<br>n as a<br>onents for<br>Number<br>oncerning |

| Page 4 of 626 I                                                      | PR2020-00261                                                           | VE                                      | NKAT KONDA EXHIBIT 2005                                                                                     |

|----------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Doc Code: REIS.DECL                                                  |                                                                        |                                         |                                                                                                             |

| Document Description: Reissu                                         | e Declaration Filed In Accordance                                      | e With MPEP 1                           | FT0/AM03 (00-12)                                                                                            |

|                                                                      |                                                                        |                                         | Approved for use through 01/31/2020. OMB 0651-0033<br>ent and Trademark Office; U.S. DEPARTMENT OF COMMERCE |

| Under the Paperwork Reduction                                        | in Act of 1995, no persons are required to                             | respond to a collec                     | tion of information unless it displays a valid OMB control number.<br>Docket Number (Optional)              |

| REISSUE APPLICATION                                                  | DECLARATION BY THE IN                                                  | VENTOR                                  | V-0070US                                                                                                    |

|                                                                      |                                                                        | 000000000000000000000000000000000000000 |                                                                                                             |

| I hereby declare that:                                               |                                                                        |                                         |                                                                                                             |

|                                                                      | nd mailing address are stated bel                                      | ow next to their                        | name.                                                                                                       |

| I believe I am the original inv<br>in patent number <u>8,269,523</u> | entor or an original joint inventor                                    | of the subject r                        | natter which is described and claimed                                                                       |

| reissue patent is sought on t                                        | ne invention titled VLSI Layouts of F                                  | Fully Connected Gener                   | and for which a alized Networks                                                                             |

|                                                                      |                                                                        |                                         |                                                                                                             |

| the specification of which                                           |                                                                        |                                         |                                                                                                             |

| is attached hereto.                                                  |                                                                        |                                         |                                                                                                             |

| ↓ was filed on 11/27/2                                               | 018 as reissue a                                                       | application pur                         | har 16/202.067                                                                                              |

|                                                                      | as reissue a                                                           | application nun                         | 1001 <u></u> .                                                                                              |

|                                                                      |                                                                        |                                         |                                                                                                             |

|                                                                      |                                                                        |                                         |                                                                                                             |

| The above-identified applica                                         | tion was made or authorized to b                                       | e made by me                            |                                                                                                             |

|                                                                      |                                                                        | o maao oy mor                           |                                                                                                             |

| I hereby acknowledge that a                                          | iny willful false statement made i                                     | n this declaratio                       | n is punishable under 18 U.S.C. 1001 by fine                                                                |

| or imprisonment of not more                                          | than five (5) years, or both.                                          |                                         |                                                                                                             |

|                                                                      |                                                                        |                                         |                                                                                                             |

| I believe the original patent t<br>below. (Check all boxes that      | o be wholly or partly inoperative of apply.)                           | or invalid, for th                      | e reasons described                                                                                         |

| below. (Oneck all boxes that                                         | appiy.)                                                                |                                         |                                                                                                             |

| by reason of a defective                                             | e specification or drawing.                                            |                                         |                                                                                                             |

|                                                                      |                                                                        |                                         |                                                                                                             |

| by reason of the patent                                              | ee claiming more or less than he                                       | had the right to                        | o claim in the patent.                                                                                      |

|                                                                      |                                                                        |                                         |                                                                                                             |

| by reason of other error                                             | S.                                                                     |                                         |                                                                                                             |

|                                                                      |                                                                        |                                         |                                                                                                             |

|                                                                      | h reissue is based is described b<br>lication seeks to broaden must be |                                         | ssue is a broadening                                                                                        |

|                                                                      |                                                                        |                                         | the electronic that UC Determs No.                                                                          |

|                                                                      |                                                                        |                                         | t to claim in the US Patent No.<br>by incorporating limitations of claim 3                                  |

|                                                                      |                                                                        |                                         | and 50 also do not broaden the                                                                              |

| scope of original clair                                              |                                                                        |                                         |                                                                                                             |

|                                                                      |                                                                        |                                         |                                                                                                             |

|                                                                      |                                                                        |                                         |                                                                                                             |

|                                                                      |                                                                        |                                         |                                                                                                             |

#### [Page 1 of 2]

This collection of information is required by 37 CFR 1.175. The information is required to obtain or retain a benefit by the public which is to file (and by the USPTO to process) an application. Confidentiality is governed by 35 U.S.C. 122 and 37 CFR 1.11 and 1.14. This collection is estimated to take 30 minutes to complete, including gathering, preparing, and submitting the completed application form to the USPTO. Time will vary depending upon the individual case. Any comments on the amount of time you require to complete this form and/or suggestions for reducing this burden, should be sent to the Chief Information Officer, U.S. Patent and Trademark Office, U.S. Department of Commerce, P.O. Box 1450, Alexandria, VA 22313-1450. DO NOT SEND FEES OR COMPLETED FORMS TO THIS ADDRESS. SEND TO: Commissioner for Patents, P.O. Box 1450, Alexandria, VA 22313-1450.

## Page 5 of 626 IPR2020-00261

#### VENKAT KONDA EXHIBIT 2005

| Under the Paperwork Reduction Act                                                                                                                                                                                                                                                                                                                           | of 1995, no persons are required to re                                                                                                                                                                                                                                   |                                                                   |                                                                                                 | l Traden                                                                         | oved for use thre<br>hark Office; U.S<br>ion unless it dis                                                                 | DEPAR                                                                         | 31/2020. OMB<br>TMENT OF C                                                                           | OMMERCE                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| (REISSUE APPLICATION DECL                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                          |                                                                   |                                                                                                 |                                                                                  | *********************                                                                                                      | cket N                                                                        | umber (Opt                                                                                           |                                                                                             |

| Note: To appoint a power of attorney, use form PTO/AIA/81.<br>Correspondence Address: Direct all communications about the application to:                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                          |                                                                   |                                                                                                 |                                                                                  |                                                                                                                            |                                                                               |                                                                                                      |                                                                                             |

| The address associated v     OR                                                                                                                                                                                                                                                                                                                             | with Customer Number: 381                                                                                                                                                                                                                                                | 39                                                                |                                                                                                 |                                                                                  |                                                                                                                            |                                                                               |                                                                                                      |                                                                                             |

| Firm or<br>Individual Name                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                          |                                                                   |                                                                                                 |                                                                                  |                                                                                                                            |                                                                               | ****                                                                                                 |                                                                                             |

| Address                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                          |                                                                   |                                                                                                 |                                                                                  |                                                                                                                            |                                                                               |                                                                                                      |                                                                                             |

| City                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                          | State                                                             |                                                                                                 |                                                                                  |                                                                                                                            | Zip                                                                           |                                                                                                      |                                                                                             |

| Country                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                          |                                                                   | ~~~~~~                                                                                          | ~~~~~                                                                            |                                                                                                                            | *******                                                                       |                                                                                                      |                                                                                             |

| Telephone                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                          |                                                                   | Email                                                                                           |                                                                                  |                                                                                                                            |                                                                               |                                                                                                      |                                                                                             |

| contribute to identity theft. Pers<br>numbers (other than a check or cl<br>the USPTO to support a petition<br>the USPTO, petitioners/applicants<br>them to the USPTO. Petitioner/<br>publication of the application (unle<br>or issuance of a patent. Further<br>application is referenced in a p<br>authorization forms PTO-2038 su<br>publicly available. | redit card authorization form P<br>or an application. If this type<br>is should consider redacting su<br>applicant is advised that the<br>ess a non-publication request<br>more, the record from an ab-<br>published application or an i<br>ubmitted for payment purpose | TO-2038<br>of perso<br>incompl<br>andoned<br>ssued p<br>is are no | 3 submitte<br>onal inforr<br>of a pater<br>iance with<br>application<br>atent (se<br>t retained | d for p<br>nation<br>nation<br>1 appl<br>1 37 CF<br>on may<br>e 37 (<br>I in the | ayment purp<br>is included i<br>from the do<br>ication is av<br>FR 1.213(a)<br>y also be av<br>CFR 1.14).<br>e application | ooses)<br>n docu<br>cumen<br>/ailable<br>is mad<br>ailable<br>Cheo<br>file ar | is never red<br>iments sub<br>ts before su<br>to the put<br>to the put<br>ks and cre<br>nd therefore | quired by<br>mitted to<br>ubmitting<br>blic after<br>plication)<br>blic if the<br>edit card |

| Legal name of sole or first inventor Venkat Konda                                                                                                                                                                                                                                                                                                           | or ( <i>E.g.</i> , Given Name (first and                                                                                                                                                                                                                                 | a midale                                                          | (ir any) ar                                                                                     | io Fam                                                                           | illy Name or                                                                                                               | Sumar                                                                         | ne)                                                                                                  |                                                                                             |

| Inventor's Signature                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                          | Date (0                                                           | Optional)                                                                                       | ******                                                                           |                                                                                                                            | *******                                                                       |                                                                                                      | 000000000000000000000000000000000000000                                                     |

| /Venkat Konda/                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                          | Septe                                                             | mber 2                                                                                          | 3, 20                                                                            | 19                                                                                                                         |                                                                               |                                                                                                      |                                                                                             |

| Residence: City<br>San Jose                                                                                                                                                                                                                                                                                                                                 | State<br>CA                                                                                                                                                                                                                                                              | Counti<br>USA                                                     | У                                                                                               | ******                                                                           |                                                                                                                            | ******                                                                        |                                                                                                      |                                                                                             |

| Mailing Address                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                          | U3A                                                               |                                                                                                 |                                                                                  |                                                                                                                            |                                                                               |                                                                                                      |                                                                                             |

| 6278 Grand Oak Way                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                          |                                                                   |                                                                                                 |                                                                                  |                                                                                                                            |                                                                               |                                                                                                      |                                                                                             |

| city<br>San Jose                                                                                                                                                                                                                                                                                                                                            | State<br>CA                                                                                                                                                                                                                                                              | <sup>Zip</sup><br>9513                                            | 35                                                                                              |                                                                                  |                                                                                                                            | Country<br>JSA                                                                | ý                                                                                                    |                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                          |                                                                   |                                                                                                 | 000000000000000000000000000000000000000                                          |                                                                                                                            | 000000000000000000000000000000000000000                                       |                                                                                                      |                                                                                             |

| Additional joint inv                                                                                                                                                                                                                                                                                                                                        | entors are named on the supp                                                                                                                                                                                                                                             | lemental s                                                        | neet(s) PTO                                                                                     | AIA/10 a                                                                         | ittached hereto.                                                                                                           |                                                                               | ****                                                                                                 | ****                                                                                        |

#### Privacy Act Statement

The **Privacy Act of 1974 (P.L. 93-579)** requires that you be given certain information in connection with your submission of the attached form related to a patent application or patent. Accordingly, pursuant to the requirements of the Act, please be advised that: (1) the general authority for the collection of this information is 35 U.S.C. 2(b)(2); (2) furnishing of the information solicited is voluntary; and (3) the principal purpose for which the information is used by the U.S. Patent and Trademark Office is to process and/or examine your submission related to a patent application or patent. If you do not furnish the requested information, the U.S. Patent and Trademark Office may not be able to process and/or examine your submission, which may result in termination of proceedings or abandonment of the application or expiration of the patent.

The information provided by you in this form will be subject to the following routine uses:

- 1. The information on this form will be treated confidentially to the extent allowed under the Freedom of Information Act (5 U.S.C. 552) and the Privacy Act (5 U.S.C 552a). Records from this system of records may be disclosed to the Department of Justice to determine whether disclosure of these records is required by the Freedom of Information Act.

- 2. A record from this system of records may be disclosed, as a routine use, in the course of presenting evidence to a court, magistrate, or administrative tribunal, including disclosures to opposing counsel in the course of settlement negotiations.

- 3. A record in this system of records may be disclosed, as a routine use, to a Member of Congress submitting a request involving an individual, to whom the record pertains, when the individual has requested assistance from the Member with respect to the subject matter of the record.

- 4. A record in this system of records may be disclosed, as a routine use, to a contractor of the Agency having need for the information in order to perform a contract. Recipients of information shall be required to comply with the requirements of the Privacy Act of 1974, as amended, pursuant to 5 U.S.C. 552a(m).

- 5. A record related to an International Application filed under the Patent Cooperation Treaty in this system of records may be disclosed, as a routine use, to the International Bureau of the World Intellectual Property Organization, pursuant to the Patent Cooperation Treaty.

- 6. A record in this system of records may be disclosed, as a routine use, to another federal agency for purposes of National Security review (35 U.S.C. 181) and for review pursuant to the Atomic Energy Act (42 U.S.C. 218(c)).

- 7. A record from this system of records may be disclosed, as a routine use, to the Administrator, General Services, or his/her designee, during an inspection of records conducted by GSA as part of that agency's responsibility to recommend improvements in records management practices and programs, under authority of 44 U.S.C. 2904 and 2906. Such disclosure shall be made in accordance with the GSA regulations governing inspection of records for this purpose, and any other relevant (*i.e.*, GSA or Commerce) directive. Such disclosure shall not be used to make determinations about individuals.

- 8. A record from this system of records may be disclosed, as a routine use, to the public after either publication of the application pursuant to 35 U.S.C. 122(b) or issuance of a patent pursuant to 35 U.S.C. 151. Further, a record may be disclosed, subject to the limitations of 37 CFR 1.14, as a routine use, to the public if the record was filed in an application which became abandoned or in which the proceedings were terminated and which application is referenced by either a published application, an application open to public inspection or an issued patent.

- 9. A record from this system of records may be disclosed, as a routine use, to a Federal, State, or local law enforcement agency, if the USPTO becomes aware of a violation or potential violation of law or regulation.

5

Reissue Application No. 16/202,067 Reissue Application Filed: 11/27/18 Attorney Docket No. V-0070US

# In The United States Patent And Trademark Office

| Filed: November 27, 2018   |

|----------------------------|

| Issued: September 18, 2012 |

| Filed: May 31, 2010        |

| Group Art Unit: 3992       |

| Filed: November 27, 2018   |

|                            |

Title: VLSI Layouts of Fully Connected Generalized Networks

San Jose, 2019 Sept 23, Mon

# 10 AMENDMENT ACCOMPANYING REISSUE APPLICATION RESUBMITTED PURSUANT TO 37 C.F.R. §1.173(B)

Mail Stop Reissue Commissioner for Patents

15 P.O. Box 1450Alexandria, VA 22313-1450

Dear Sir/Madam:

- For the above above-referenced reissue patent application, in view of the petition granted on August 19, 2019 that was filed in the parent Patent No. 8,269,523 for the entire delay in filing the basic national fee from the due date for the fee until the filing of a grantable petition under 37 CFR 1.137 was unintentional, applicant is now submitting a new "the reissue application declaration by the inventor". Furthermore the Amendment

- 25 submitted for the above-referenced reissue patent application filed on November 27, 2018 which supposed to set forth applicant's requested amendments to U.S. Patent No.

Attorney Docket No. V-0070US

8,269,523 is non-compliant with 37 C.F.R. §1.173(B) at least since the submitted claims are not identified with correct format.

Accordingly applicant respectfully requests to disregard the amendment submitted on November 27, 2018 and consider this amendment. This Amendment accompanies the

5 reissue patent application filed on November 27, 2018, and sets forth applicant's requested amendments to U.S. Patent No. 8,269,523.

Amendment to Specification is set forth on page 4.

Amendments to the claims are set forth in the *Listing of the Claims*, which begins on

- Page 5. Originally issued claims 1, 2, 4, 7, 11, 16, 22, 24, 28, 33, 36, 39, 43 are amended.

Originally issued claims 3, 5, 6, 8 10, 12 14, 15, 17 21, 23, 25 27, 29 32, 34 35, 37 38, 40 42, 44 48 are now cancelled. Originally issued claims are amended perfecting the claim language. But no new matter is added. Furthermore:

Incorporated limitations of Claim 3 into Claim 1 and cancelled claim 3.

- Incorporated limitations of Claims 5 6 into Claim 4 and cancelled claims 5 6.

Incorporated limitations of Claims 8 10 into Claim 7 and cancelled claims 8 10.

Incorporated limitations of Claims 12 14 into Claim 11 and cancelled claims 12 14.

Incorporated limitations of Claims 18, 19, 21, 22, and 47 into Claim 16 and cancelled claims 18, 19, 21, 22, and 47.

- 20 Incorporated limitations of Claims 25 27 into Claim 24 and cancelled claims 25 27. Incorporated limitations of Claims 29 – 32 into Claim 28 and cancelled claims 29 – 32. Incorporated limitations of Claims 34 – 35 into Claim 33 and cancelled claims 34 – 35. Incorporated limitations of Claims 37 – 38 into Claim 36 and cancelled claims 37 – 38. Incorporated limitations of Claims 40 – 42 into Claim 39 and cancelled claims 40 – 42.

- 25 Incorporated limitations of Claims 44 46 into Claim 43 and cancelled claims 44 46.

Attorney Docket No. V-0070US

New claims 49 and 50 are added both narrowing the original Claim 1 in different ways.

Therefore, the claims 1, 2, 4, 7, 11, 16, 22, 24, 28, 33, 36, 39, 43, 49, 50 are pending in this reissue application following entry of this amendment.

*Remarks* are set forth on page 25.

5

#### VENKAT KONDA EXHIBIT 2005

Reissue Application No. 16/202,067 Reissue Application Filed: 11/27/18 Attorney Docket No. V-0070US

#### Amendments to the Specification

Amendments to the specification are indicated below wherein matter to added is indicated by <u>underlining</u> and matter to be deleted is indicated in [brackets].

5

Please replace the paragraph at column 1, lines 7-15, following the heading "CROSS REFERENCE TO RELATED APPLICATIONS" with the following:

This application [is related to and] is an application for reissue of U.S. Patent No.

- 8,269,523 which claims priority of the PCT Application Serial No. PCT/US08/64605

entitled "VLSI LAYOUTS OF FULLY CONNECTED GENERALIZED NETWORKS"

by Venkat Konda assigned to the same assignee as the current application, filed May 22,

2008, [and] which in turn claims priority of the U.S. Provisional Patent Application Serial

No. 60/940, 394 entitled "VLSI LAYOUTS OF FULLY CONNECTED

- 15 GENERALIZED NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007.

Attorney Docket No. V-0070US

#### LISTING OF THE CLAIMS

This Claim listing sets forth all the claims that will be pending in this reissue application following entry of the present amendment.

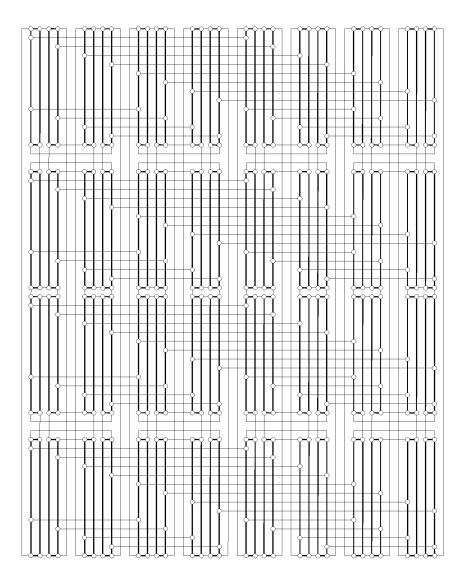

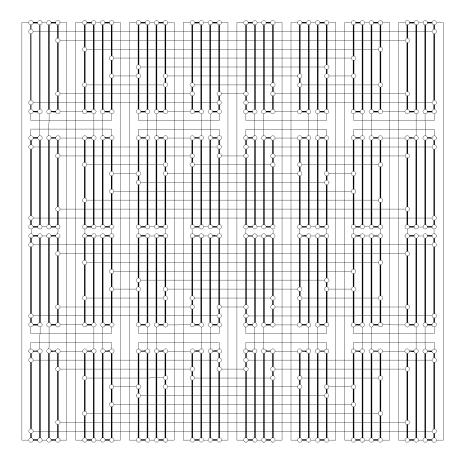

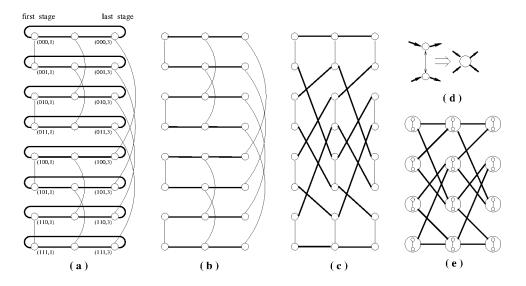

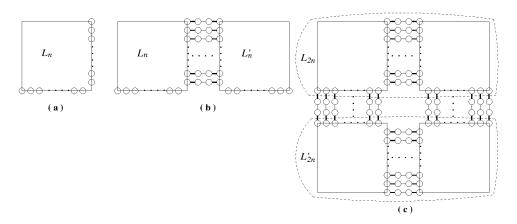

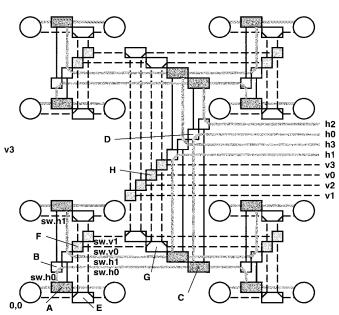

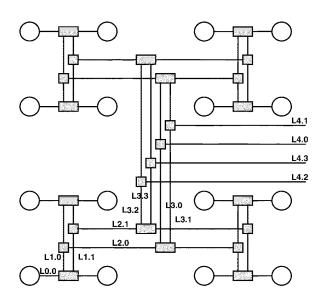

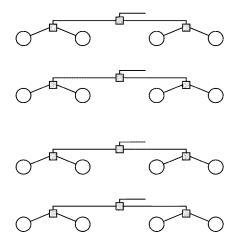

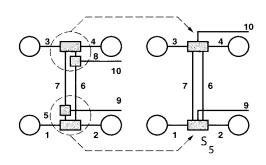

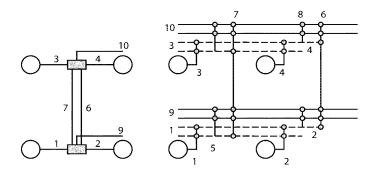

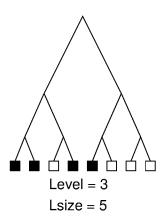

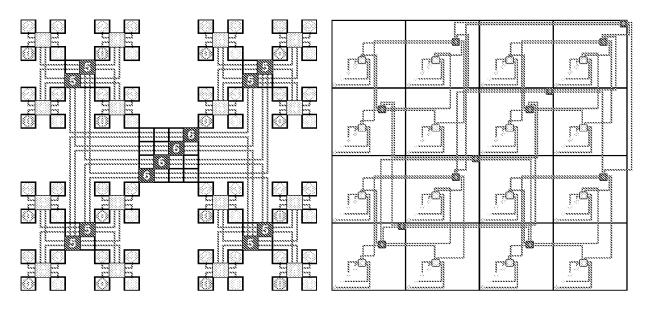

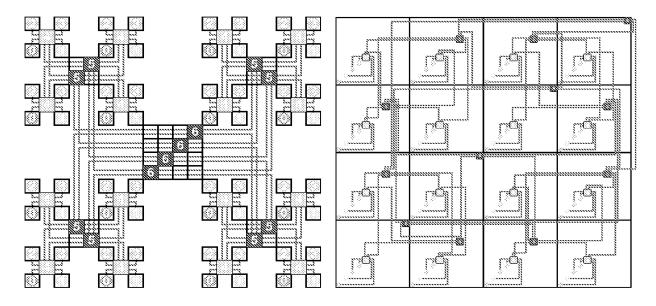

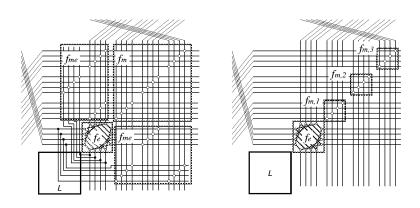

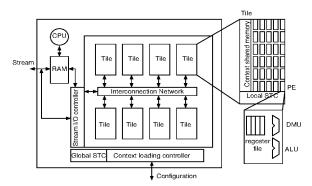

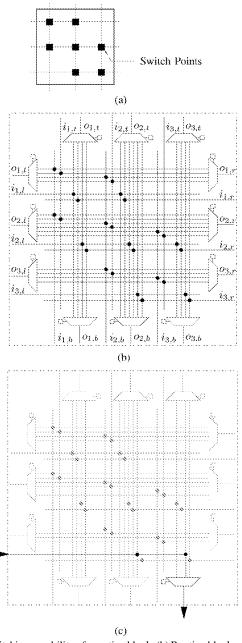

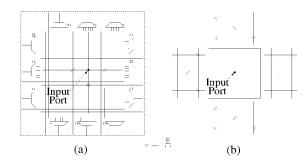

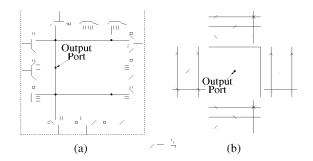

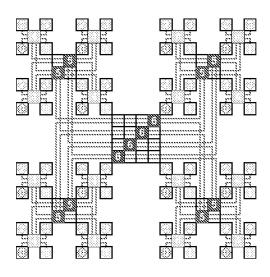

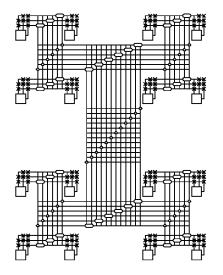

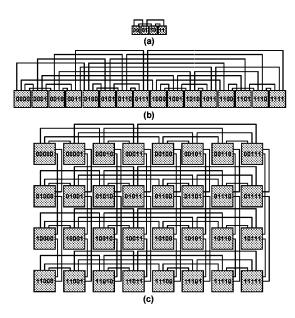

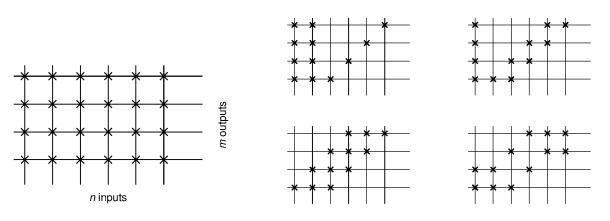

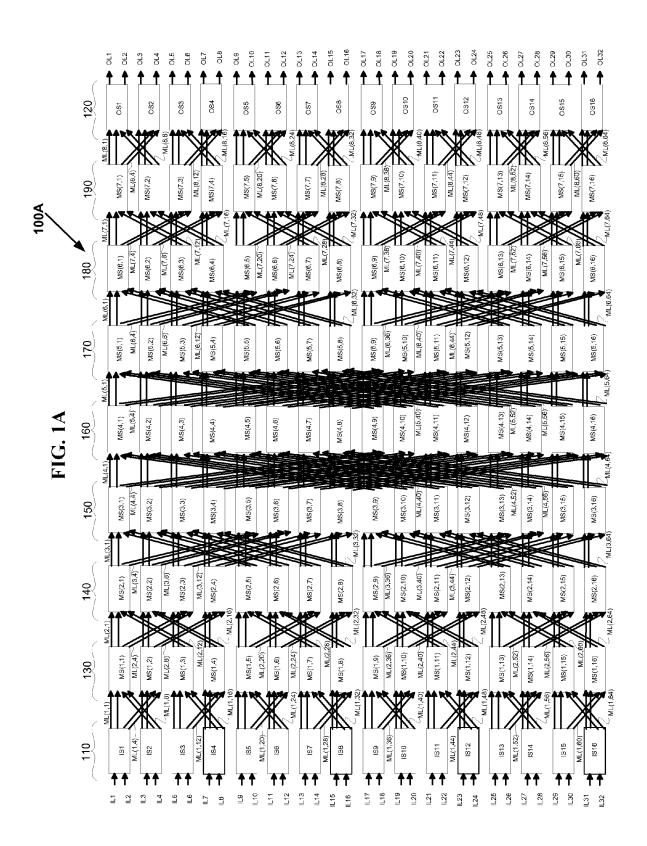

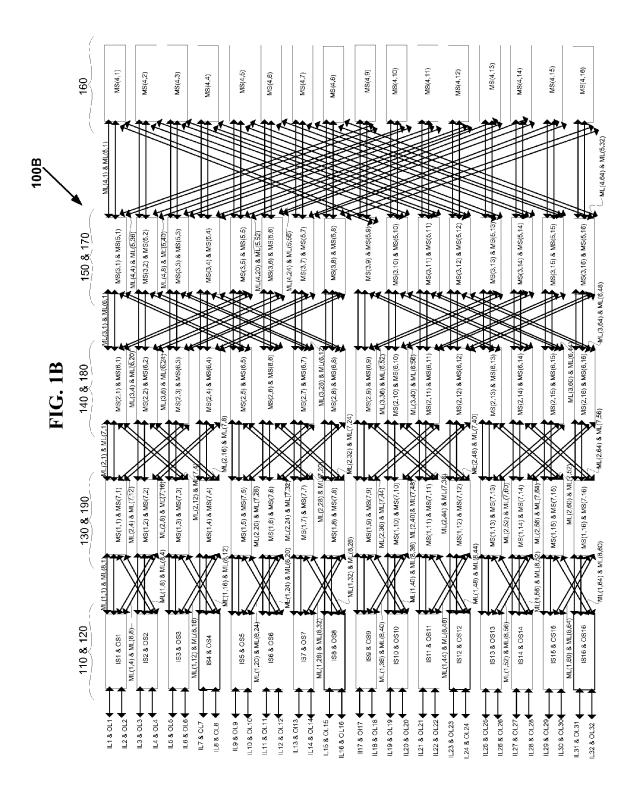

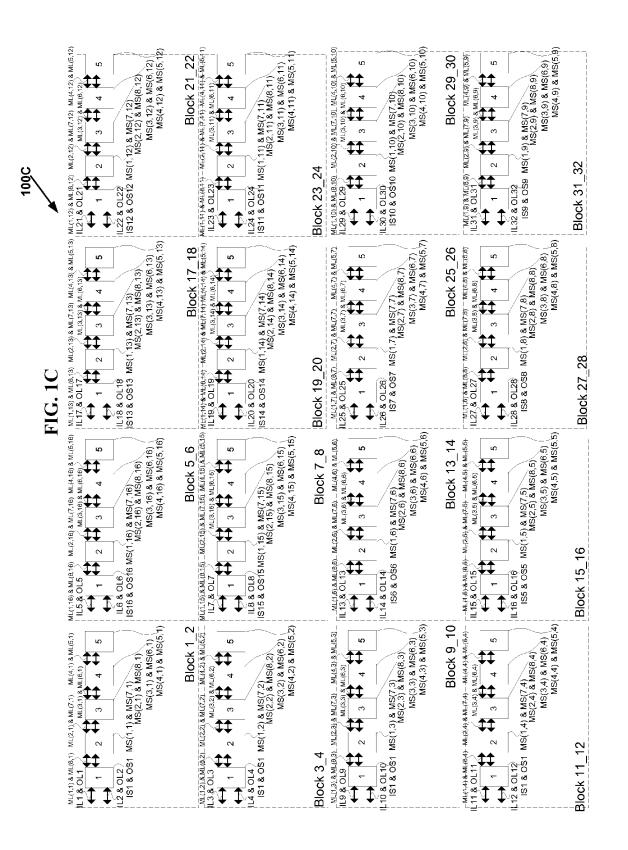

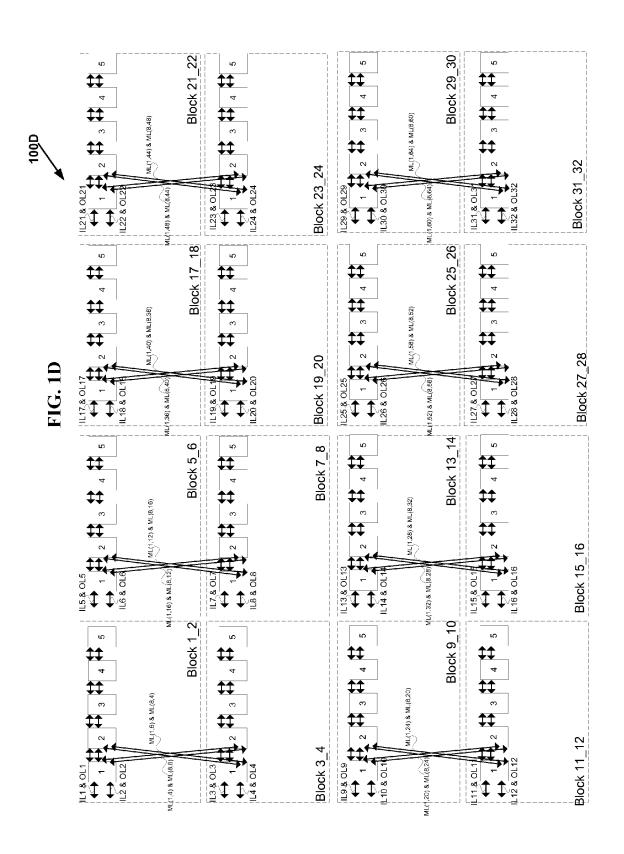

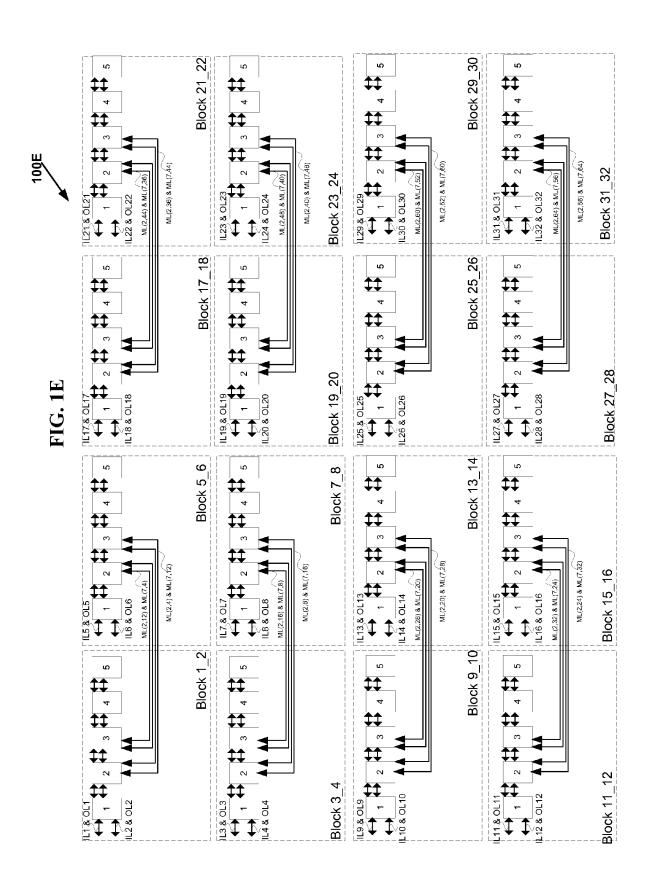

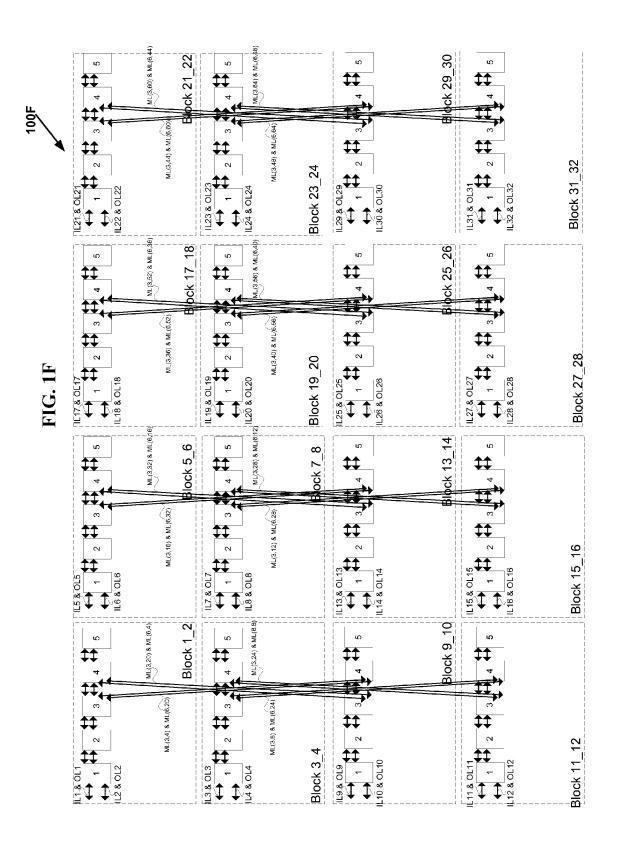

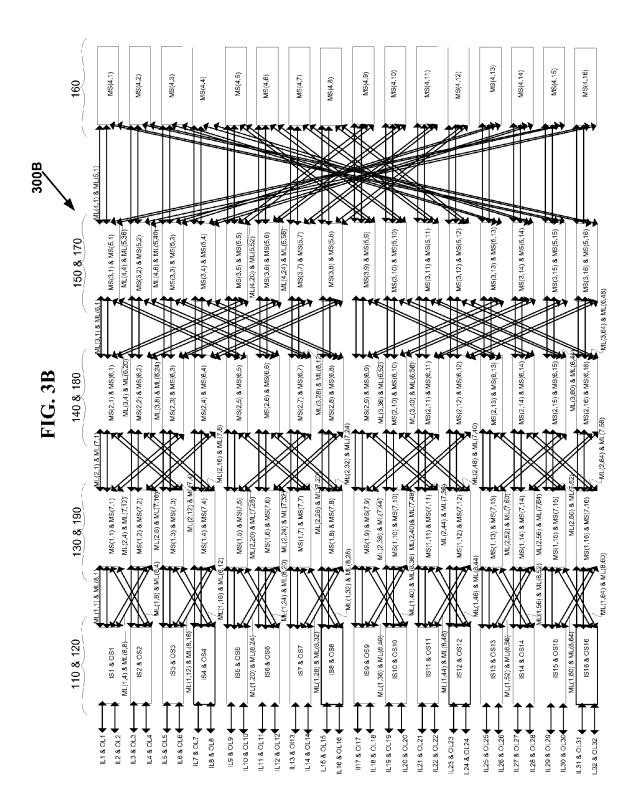

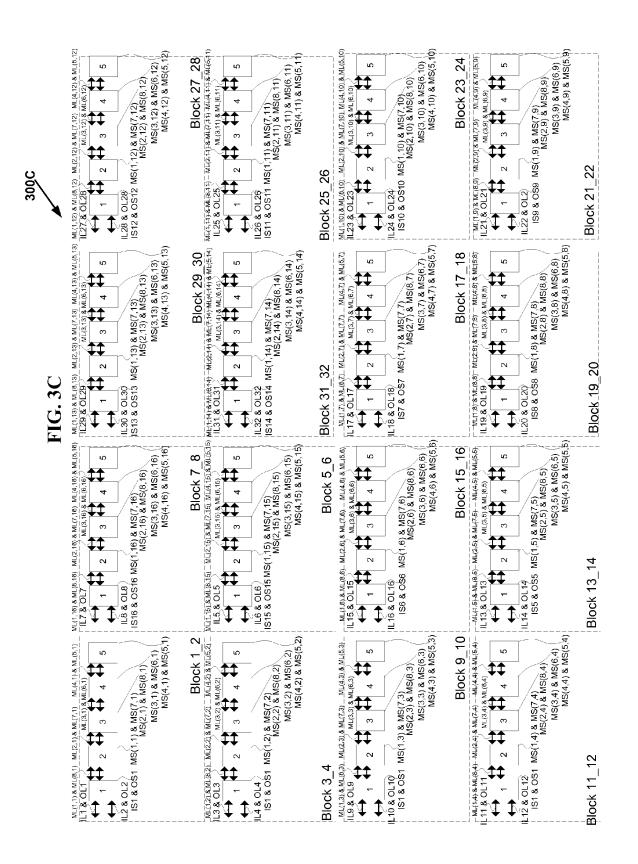

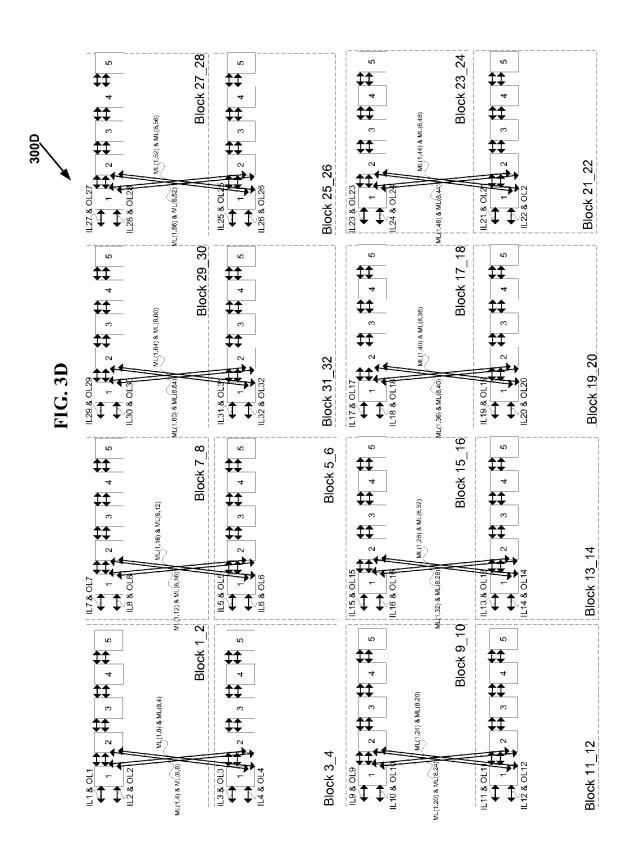

5 1. (Amended): An integrated circuit [device] comprising a plurality of subintegrated circuit blocks and a [routing network] <u>multi-stage network</u>, and

[Said] each <u>sub-integrated circuit block of said</u> plurality of sub-integrated circuit blocks comprising a plurality of inlet links and a plurality of outlet links; and

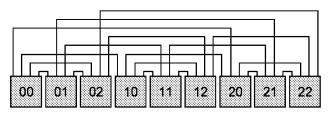

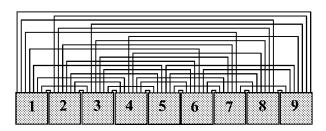

[Said] <u>said</u> [routing network] <u>multi-stage network</u> comprising [of] a plurality of

10 stages y [in] corresponding to each [said] sub-integrated circuit block of said plurality of sub-integrated circuit blocks, starting from [the lowest] stage [of] 1 to [the highest] stage [of] y, where  $y \ge 1$ ; and

[Said routing network comprising] each stage of said plurality of stages y comprising a plurality of switches of size  $d \times d$ , where  $d \ge 2$  [, in each said

15 stage] and each [said] switch <u>of said plurality of switches</u> of size  $d \times d$  having d inlet links and d outlet links; and

[Said] <u>said</u> plurality of outlet links of [said] each sub-integrated circuit block <u>of</u> <u>said plurality of sub-integrated circuit blocks</u> are directly connected to said <u>plurality of</u> inlet links of said <u>plurality of</u> switches <u>of size</u>  $d \times d$  of its corresponding said [lowest]

stage [of] 1 of said plurality of stages y, and said plurality of inlet links of [said] each sub-integrated circuit block of said plurality of sub-integrated circuit blocks are directly connected from said plurality of outlet links of said plurality of switches of size  $d \times d$  of [its corresponding] said [lowest] stage [of] 1 of said plurality of stages y; and

[said] each sub-integrated circuit block <u>of said plurality of sub-integrated circuit</u>

25 <u>blocks</u> comprising a plurality of forward connecting links connecting from <u>said plurality</u> <u>of switches in [a lower] each stage of said plurality of stages y to said plurality of</u>

#### Page 12 of 626 IPR2020-00261

#### **VENKAT KONDA EXHIBIT 2005**

Reissue Application No. 16/202,067 Reissue Application Filed: 11/27/18 Attorney Docket No. V-0070US

switches in [its] <u>an</u> immediate succeeding [higher] stage <u>of said plurality of stages y</u>, and also comprising a plurality of backward connecting links connecting from <u>said plurality</u> <u>of switches in [a higher] each stage of said plurality of stages y to <u>said plurality of</u> switches in [its] <u>an</u> immediate [succeeding lower] preceding stage <u>of said plurality of</u></u>

5 stages y; and

[Said each sub-integrated circuit block comprising a plurality straight links in said forward connecting links from switches in said each lower stage to switches in its immediate succeeding higher stage and a plurality cross links in said forward connecting links from switches in said each lower stage to switches in its immediate succeeding

- 10 higher stage, and further comprising a plurality of straight links in said backward connecting links from switches in said each higher stage to switches in its immediate preceding lower stage and a plurality of cross links in said backward connecting links from switches in said each higher stage to switches in its immediate preceding lower stage,]

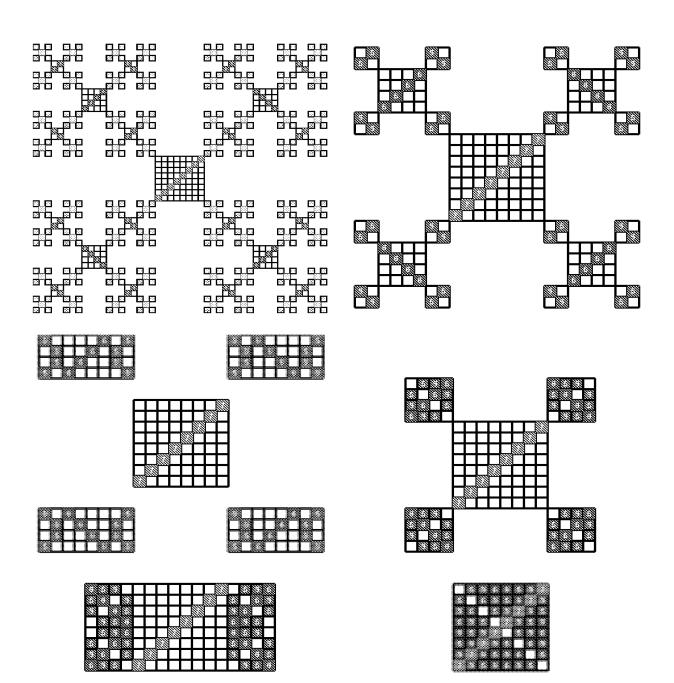

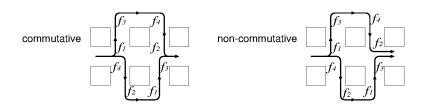

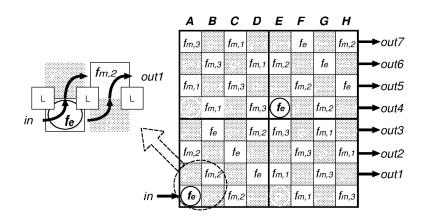

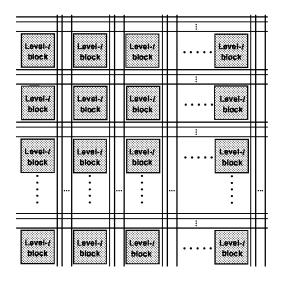

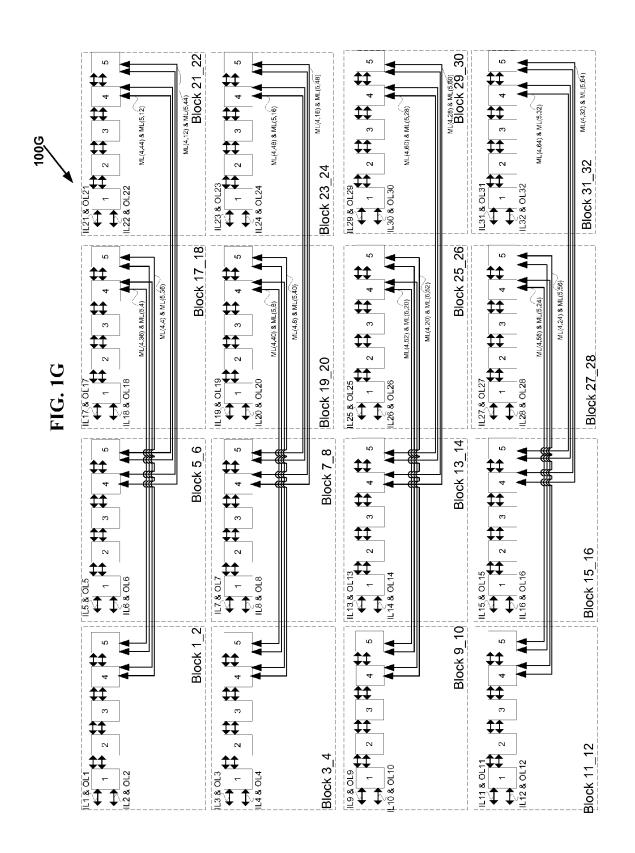

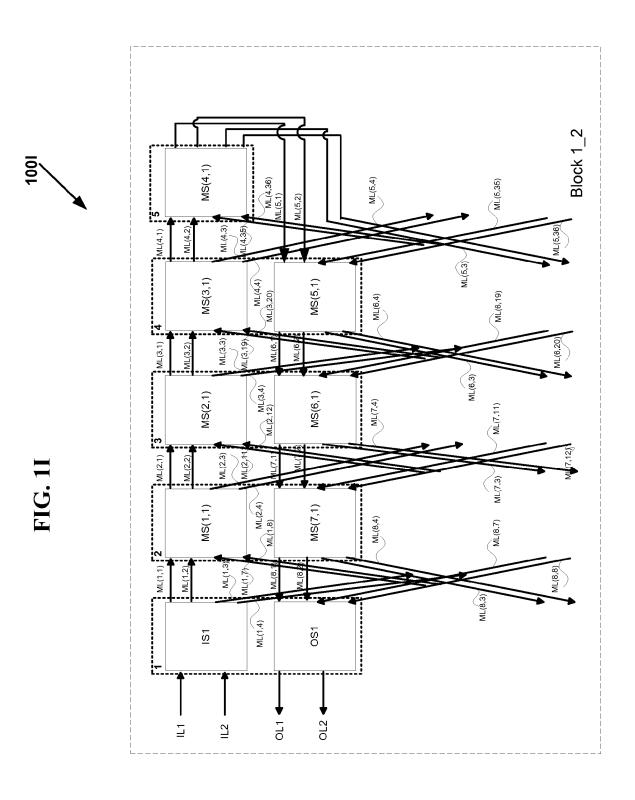

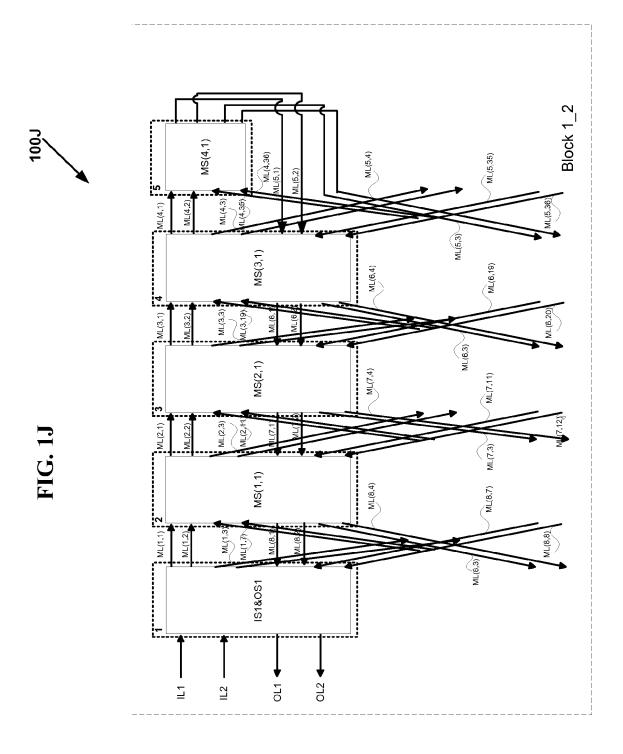

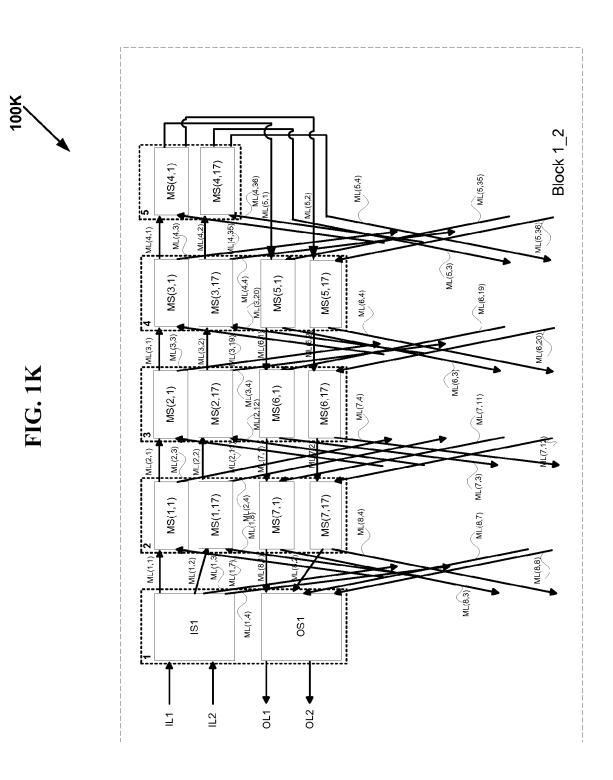

- 15 said plurality of sub-integrated circuit blocks arranged in a two-dimensional grid of <u>a plurality of</u> rows and <u>a plurality of</u> columns, and

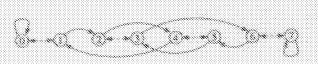

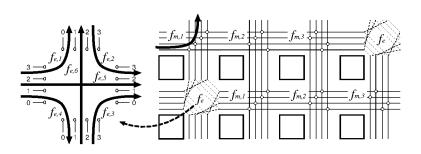

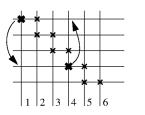

said plurality of forward connecting links and said plurality of backward connecting links comprise[s] a plurality of [said all] straight middle links [are] connecting from said plurality of switches of a first stage of said plurality of stages y in [each said] a

20 <u>first</u> sub-integrated circuit block <u>of said plurality of sub-integrated circuit blocks</u> [are connecting] to <u>said plurality of</u> switches <u>of an immediate succeeding or an immediate</u> <u>preceding stage of said first stage of said plurality of stages y</u> in [the same] said first sub-integrated circuit block <u>of said plurality of sub-integrated circuit blocks</u>; and

<u>said plurality of forward connecting links and said plurality of backward</u>

<u>connecting links comprise[s] a plurality of [said all] cross middle links [are] connecting</u>

[as either vertical or horizontal links between switches in two different said sub-

Attorney Docket No. V-0070US

integrated circuit blocks which are either placed vertically above or below, or placed horizontally to the left or to the right,] from switches of said plurality of switches in a stage of said plurality of stages y in a first sub-integrated circuit block of said plurality of switches in a succeeding

5 <u>stage or a preceding stage a first sub-integrated circuit block of said plurality of sub-</u> <u>integrated circuit blocks wherein said plurality of cross middle links are either vertical</u> <u>tracks or horizontal tracks</u>, and

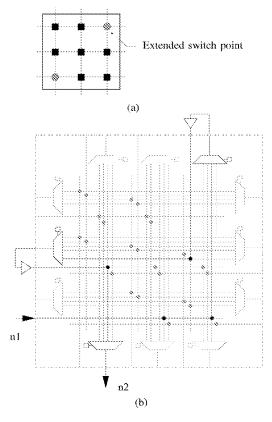

a plurality of said plurality of cross middle links in succeeding stages of said plurality of stages y are connected alternately as vertical tracks and horizontal tracks

10 (hereinafter "hypercube topology"), and

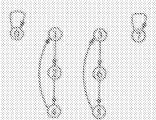

[each said plurality of sub-integrated circuit blocks comprising same number of said stages and] each sub-integrated circuit block of said plurality of sub-integrated circuit blocks connected with said plurality of switches of size  $d \times d$  of said plurality of stages y [said switches in each said stage,] regardless of the size of said plurality of rows

- 15 <u>and size of said plurality of columns of said two-dimensional grid [so that] wherein each</u> <u>sub-integrated circuit block of said plurality of sub-integrated circuit [block with its</u> corresponding said stages and said switches in each stage] <u>blocks connected with said</u> <u>plurality of switches of size  $d \times d$  of said plurality of stages y is replicable in both</u> vertical direction or horizontal direction of said two-dimensional grid.

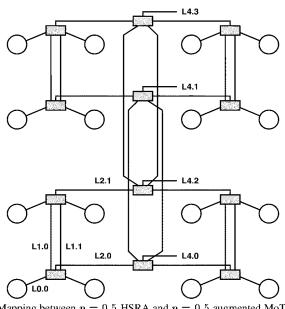

- 20 2. (Amended): The integrated circuit [device] of claim 1, said two-dimensional grid of said <u>plurality of sub-integrated circuit blocks connected</u> with [their corresponding] said <u>plurality of stages y</u> [and said switches in each stage] is scalable by any power of 2, and,

for each multiplication of 2 of [the] size of total said <u>plurality of sub-integrated</u>

circuit blocks, by adding one more stage [of switches] to said <u>plurality of stages</u> and said

hypercube [layout] topology is <u>extended and placed in said</u> hypercube topology [format]

and [also] the cross <u>middle</u> links between said one more stage to said plurality of stages y

Attorney Docket No. V-0070US

of switches <u>of said plurality of switches</u> are connected in <u>said hypercube topology</u> [format].

- 3. (Cancel claim 3)

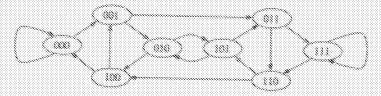

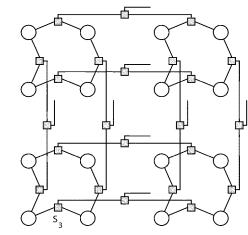

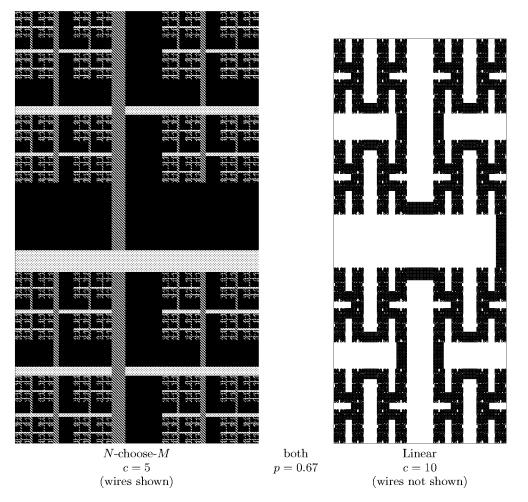

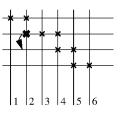

- 4. (Amended): The integrated circuit [device] of claim [3] 1, wherein [said cross

5 links from switches in a stage said stages in one of said sub-integrated circuit blocks are connecting to switches in the succeeding stage in another of said sub-integrated circuit blocks so that said cross links are either vertical links or horizontal and vice versa, and hereinafter such cross links are "shuffle exchange links").] said plurality of cross middle links between switches in any two same succeeding stages of said plurality of stages *y* are

- 10 substantially of equal length in said integrated circuit, and the shortest cross middle links of said plurality of cross middle links are connected at stage 1 of said plurality of stages y and between switches of said plurality of switches in two nearest neighboring said plurality of sub-integrated circuit blocks, and length of the cross middle links is doubled in each succeeding stage of said plurality of

15 <u>stages y in either said vertical tracks or said horizontal tracks.</u>

sub-integrated circuit blocks,], and wherein d = 2 and either

- 5. (Cancel claim 5)

- 6. (Cancel claim 6)

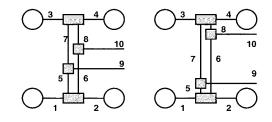

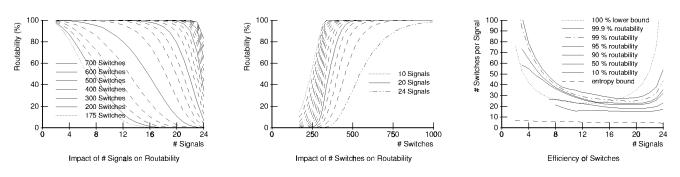

7. (Amended): The integrated circuit [device] of claim [6] <u>4</u>, wherein  $y \ge (\log_2 N)$ , where N > 1, [so that] wherein [the] length or width of the [horizontal] plurality of cross 20 middle links [shuffle exchange links] in [the highest] stage <u>y</u> is equal to half the [size] length or width [of the horizontal size] of said two dimensional grid of said plurality of sub-integrated circuit blocks [and the length of the vertical shuffle exchange links in the highest stage is equal to half the size of the vertical size of said two dimensional grid of

Attorney Docket No. V-0070US

each stage of said plurality of stages in each sub-integrated circuit block of said plurality of sub-integrated circuit blocks comprises only one switch of said plurality of switches connecting said plurality of forward connecting links and each stage of said plurality of stages in each sub-integrated circuit block of said plurality of sub-integrated

5 circuit blocks comprises only one switch of said plurality of switches connecting said plurality of backward connecting links and said multi-stage network is rearrangeably nonblocking for unicast Benes network, or

each stage of said plurality of stages in each sub-integrated circuit block of said plurality of sub-integrated circuit blocks comprises at least two switches of said plurality

- 10 of switches connecting said plurality of forward connecting links and each stage of said plurality of stages in each sub-integrated circuit block of said plurality of sub-integrated circuit blocks comprises at least two switches of said plurality of switches connecting said plurality of backward connecting links and said multi-stage network is strictly nonblocking for unicast Benes network and is rearrangeably nonblocking for arbitrary

- 15 fan-out multicast Benes network, or

each stage of said plurality of stages in each sub-integrated circuit block of said plurality of sub-integrated circuit blocks comprises at least three switches of said plurality of switches connecting said plurality of forward connecting links and each stage of said plurality of stages in each sub-integrated circuit block of said plurality of sub-integrated

- 20 circuit blocks comprises at least three switches of said plurality of switches connecting said plurality of backward connecting links and said multi-stage network is strictly nonblocking for arbitrary fan-out multicast Benes network.

- 8. (Cancel claim 8)

- 25 9. (Cancel claim 9)

- 10. (Cancel claim 10)

Attorney Docket No. V-0070US

11. (Amended): The integrated circuit [device] of claim [6]  $\underline{4}$ , wherein  $y \ge (\log_2 N)$ , where N > 1, [so that] wherein [the] length or width of the [horizontal] plurality of cross middle links [shuffle exchange links] in [the highest] stage  $\underline{y}$  is equal to half the [size] length or width [of the horizontal size] of said two dimensional grid of said plurality of

5 sub-integrated circuit blocks [and the length of the vertical shuffle exchange links in the highest stage is equal to half the size of the vertical size of said two dimensional grid of sub-integrated circuit blocks,]. and

[said] each sub-integrated circuit block <u>of said plurality of sub-integrated circuit</u> <u>blocks</u> further comprising a plurality of U-turn links within switches <u>of said plurality of</u>

10 <u>switches</u> in each <u>stage</u> of said <u>plurality</u> of stages in each of said <u>plurality</u> of sub-integrated circuit blocks[.], and wherein d = 2 and either

each stage of said plurality of stages in each sub-integrated circuit block of said plurality of sub-integrated circuit blocks comprises only one switch of said plurality of switches connecting said plurality of forward connecting links and each stage of said

15 plurality of stages in each sub-integrated circuit block of said plurality of sub-integrated circuit blocks comprises only one switch of said plurality of switches connecting said plurality of backward connecting links and said multi-stage network is rearrangeably nonblocking for unicast butterfly fat tree network, or

each stage of said plurality of stages in each sub-integrated circuit block of said

- 20 plurality of sub-integrated circuit blocks comprises at least two switches of said plurality of switches connecting said plurality of forward connecting links and each stage of said plurality of stages in each sub-integrated circuit block of said plurality of sub-integrated circuit blocks comprises at least two switches of said plurality of switches connecting said plurality of backward connecting links and said multi-stage network is strictly

- 25 <u>nonblocking for unicast butterfly fat tree network and rearrangeably nonblocking for</u> <u>arbitrary fan-out multicast butterfly fat tree network, or</u>

each stage of said plurality of stages in each sub-integrated circuit block of said plurality of sub-integrated circuit blocks comprises at least three switches of said plurality

Attorney Docket No. V-0070US

of switches connecting said plurality of forward connecting links and each stage of said plurality of stages in each sub-integrated circuit block of said plurality of sub-integrated circuit blocks comprises at least three switches of said plurality of switches connecting said plurality of backward connecting links and said multi-stage network is strictly

- 5 <u>nonblocking for arbitrary fan-out multicast butterfly fat tree network.</u>

- 12. (Cancel claim 12)

- 13. (Cancel claim 13)

- 14. (Cancel claim 14)

- 15. (Cancel claim 15)

- 10 16. (Amended): The integrated circuit [device] of claim 1, wherein said <u>plurality of</u> switches comprising [active and] <u>a plurality of</u> reprogrammable cross points and said <u>plurality of</u> [each] <u>reprogrammable</u> cross point is programmable by SRAM cells or Flash Cells[.], or

said integrated circuit is a a field programmable gate array (FPGA) or a

15 programmable logic device (PLD) or an anti-fuse based programmable integrated circuit device or a mask programmable structured ASIC device, or an Application Specific Integrated Circuit (ASIC) embedded with programmable logic circuit or 3D-FPGA, or

said plurality of forward connecting links use a plurality of buffers to amplify signals driven through them and said plurality of backward connecting links use a

- 20 plurality of buffers to amplify signals driven through them; and said plurality of buffers are either inverting or non-inverting buffers.

- 17. (Cancel claim 17)

Attorney Docket No. V-0070US

- 18. (Cancel claim 18)

- 19. (Cancel claim 19)

- 20. (Cancel claim 20)

- 21. (Cancel claim 21)

- 5 22. (Amended) The integrated circuit [device] of claim 1, wherein said <u>plurality of</u> switches comprising passive cross points or just connection of two links or not and said integrated circuit [device] is [a] <u>an</u> Application Specific Integrated Circuit (ASIC) device.

- 23. (Cancel claim 23)

- 24. (Amended): The integrated circuit [device] of claim [4] <u>1</u>, wherein said [all

horizontal] <u>plurality of cross middle links</u> [shuffle exchange links] between switches <u>of</u>

<u>said plurality of switches</u> in any two corresponding [said] succeeding stages <u>of said</u>

<u>plurality of stages</u> are of different length and said [vertical] <u>plurality of cross middle links</u>

[shuffle exchange links] between switches <u>of said plurality of switches</u> in any two

corresponding [said] succeeding stages <u>of said plurality of stages</u> are of different [length]

- 15 width and y≥ (log<sub>2</sub> N), where N > 1[.], and wherein d = 2 and either each stage of said plurality of stages in each sub-integrated circuit block of said plurality of sub-integrated circuit blocks comprises only one switch of said plurality of switches connecting said plurality of forward connecting links and each stage of said plurality of stages in each sub-integrated circuit block of said plurality of sub-integrated

- 20 circuit blocks comprises only one switch of said plurality of switches connecting said plurality of backward connecting links and said multi-stage network is rearrangeably nonblocking for unicast generalized multi-stage network, or

each stage of said plurality of stages in each sub-integrated circuit block of said plurality of sub-integrated circuit blocks comprises at least two switches of said plurality

25 of switches connecting said plurality of forward connecting links and each stage of said

#### Page 19 of 626 IPR2020-00261

#### VENKAT KONDA EXHIBIT 2005