|                                        | Page 1 of 708 IPR2020-00261 19CV3458<br>Santa Clara –                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                        |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5                  | VENKAT KONDA<br>6278 Grand Oak Way<br>San Jose, California 95135<br>Telephone: (408) 472-3273<br>Email: vkonda@gmail.com<br>Plaintiff <i>Pro se</i>                                                                                                                                                                                                                               | Electronically Filed<br>by Superior Court of CA,<br>County of Santa Clara,<br>on 3/22/2021 11:34 PM<br>Reviewed By: F. Miller<br>Case #19CV345846<br>Envelope: 6087286 |

| 6<br>7                                 | SUPERIOR COURT OF CALIFORNIA - COUNTY OF SANTA CLARA<br>UNLIMITED JURISDICTION                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                        |

| 8<br>9                                 | VENKAT KONDA, Ph.D., an individual,                                                                                                                                                                                                                                                                                                                                               | CASE NO. 19CV345846                                                                                                                                                    |

| 10<br>11<br>12                         | Plaintiff,<br>v.                                                                                                                                                                                                                                                                                                                                                                  | EXHIBITS A - E IN DECLARATION OF<br>VIPIN CHAUDHARY, Ph.D. IN SUPPORT<br>OF PLAINTIFF'S FOURTH AMENDED<br>COMPLAINT                                                    |

| 12<br>13<br>14<br>15<br>16<br>17<br>18 | DEJAN MARKOVIC, Ph.D., an individual;<br>CHENG C. WANG, Ph.D., an individual;<br>FLEX LOGIX TECHNOLOGIES, INC., a<br>Delaware Corporation; THE REGENTS OF<br>THE UNIVERSITY OF CALIFORNIA;<br>GEOFFREY TATE, an individual; PIERRE<br>LAMOND, an individual; PETER HEBERT,<br>an individual; LESLIE M. LACKMAN, Ph.D.,<br>an individual; and DOES 1-20, inclusive,<br>Defendants. | Department: 2<br>Before: Honorable Drew C. Takaichi<br>Date Complaint Filed: April 3, 2019<br>Trial Date: None                                                         |

| 19<br>20                               |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                        |

| 21<br>22                               |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                        |

| 23                                     |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                        |

| 24                                     |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                        |

| 25<br>26                               |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                        |

| 20                                     |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                        |

| 28                                     |                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                        |

|                                        | Vipin Chaudhary Ph.D. Declaration 1                                                                                                                                                                                                                                                                                                                                               | Case No: 19CV345846                                                                                                                                                    |

# **EXHIBIT A**

#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization International Bureau

(43) International Publication Date

12 September 2008 (12.09.2008)

PCT

(51) International Patent Classification: H04Q 3/00 (2006.01)

(21) International Application Number: PCT/US2008/056064

(22) International Filing Date: 6 March 2008 (06.03.2008)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data: 60/905,526 6 March 2007 (06.03.2007) US 60/940,383 25 May 2007 (25.05.2007) US

#### (71) Applicant and

- (72) Inventor: KONDA, Venkat [US/US]; 6278, Grand Oak Way, San Jose, CA 95135 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM,

## (10) International Publication Number

#### (10) International Publication Number WO 2008/109756 A1

AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, NO, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

with international search report

100E **FIG. 1B** 110 130  $130 + 10 * (Log_{d}N)$ -2) 130+10\*(2\*Log MS(Log,N MS(2×Log\_N - 3,1) (L(2,1) MS(1,1) ML2,d)  $\mathsf{VL}(2,(\mathsf{d+1})) \xrightarrow{MS(Log_N-1,2)}$  $MS(2 \times Log_{d}N)$ MS(1,2)  $ML(2 \times Log_{d}N - 2,1)$ . L(2,2d) IL1 OL1 IS1 ML(1,2"d+1) OS1 IL(d) OL(d)  $\frac{ML(2 \times Log_d N - 2, 2 \times d)}{-+OL(d+1)}$ ML(1,2\*d) MS(2×Log\_N VIL(2,N-d) IL(d+1) MS(1,N/d) 1S2 ML(2\_N) 0.52 IL(2d) OL(2d ML(1,4\*č  $ML(2 \times Log_d N - 2, 4 \times d)$  $MS(Log_{d}N-1)$ +1)  $MS(2 \times Log_{J}N -$ 1ML(2.N+1) MS(1,N/d+1) ML2,N+d) L(2×Log<sub>d</sub>N  $-2,2\times(N-d)$ VL(2,N+d+1)) + - 2) IL(N-d) MS(2×Loc.) +OL(N-d) IS(N/d) OS(N/d) N/d+2) IL(N) OL(N) ML(2,N+2d  $ML(2 \times Log_d N - 2, 2 \times N)$ ML(1,2N) MS(2×Log\_1 MS(1,2N/d)  $\overline{ML(Log_N + 1, 2 \times N)}$

(54) Title: FULLY CONNECTED GENERALIZED MULTI-STAGE NETWORKS

(57) Abstract: A multi-stage network comprising  $(2x \log_d N)$  - I stages is operated in strictly nonblocking manner for unicast includes an input stage having N / d switches with each of them having d inlet links and 2x d outgoing links connecting to second stage switches, an output stage having N / d switches with each of them having d outlet links and 2 xd incoming links connecting from switches in the penultimate stage. The network also has  $(2x \log_d N)$ - 3 middle stages with each middle stage having 2 x N / d switches, and each switch in the middle stage has d incoming links connecting from the switches in its immediate preceding stage, and d outgoing links connecting to the switches in its immediate succeeding stage. Also the same multi-stage network is operated in rearrangeably nonblocking manner for arbitrary fan-out multicast and each multicast connection is set up by use

**Provide the system of at most two outgoing links from the input stage switch.** A multi-stage network comprising  $(2x \log_d N) - 1$  stages is operated in strictly nonblocking manner for multicast includes an input stage having N / d switches with each of them having d outlet links and 3 x d incoming links connecting from switches, and d outgoing links connecting from switches, and each switch in the middle stage having N / d switches with each of them having d outlet links and 3 x d incoming links connecting from strictly nonblocking manner for switches, and d outgoing links connecting from switches in the penultimate stage. The network also has  $(2x \log_d N) - 3$  middle stage switches, and d outgoing links connecting from switches in the switches in its immediate succeeding stage.

20

25

#### PCT/US2008/056064

## FULLY CONNECTED GENERALIZED MULTI-STAGE NETWORKS

1

#### Venkat Konda

#### 5 CROSS REFERENCE TO RELATED APPLICATIONS

This application is Continuation In Part PCT Application to and incorporates by reference in its entirety the U.S. Provisional Patent Application Serial No. 60/905,526 entitled "LARGE SCALE CROSSPOINT REDUCTION WITH NONBLOCKING UNICAST & MULTICAST IN ARBITRARILY LARGE MULTI-STAGE

10 NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed March 6, 2007.

This application is Continuation In Part PCT Application to and incorporates by reference in its entirety the U.S. Provisional Patent Application Serial No. 60/940, 383 entitled "FULLY CONNECTED GENERALIZED MULTI-STAGE NETWORKS" by Verket Konda assigned to the same assignee as the current application filed May 25

15 Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007.

This application is related to and incorporates by reference in its entirety the U.S. Provisional Patent Application Serial No. 60/940, 387 entitled "FULLY CONNECTED GENERALIZED BUTTERFLY FAT TREE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007.

This application is related to and incorporates by reference in its entirety the U.S. Provisional Patent Application Serial No. 60/940, 389 entitled "FULLY CONNECTED GENERALIZED REARRANGEABLY NONBLOCKING MULTI-LINK MULTI-STAGE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007.

25

#### 2

PCT/US2008/056064

This application is related to and incorporates by reference in its entirety the U.S. Provisional Patent Application Serial No. 60/940, 390 entitled "FULLY CONNECTED GENERALIZED MULTI-LINK BUTTERFLY FAT TREE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007.

- 5 This application is related to and incorporates by reference in its entirety the U.S. Provisional Patent Application Serial No. 60/940, 391 entitled "FULLY CONNECTED GENERALIZED FOLDED MULTI-STAGE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007.

- This application is related to and incorporates by reference in its entirety the U.S.

Provisional Patent Application Serial No. 60/940, 392 entitled "FULLY CONNECTED GENERALIZED STRICTLY NONBLOCKING MULTI-LINK MULTI-STAGE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007.

- This application is related to and incorporates by reference in its entirety the U.S.

Provisional Patent Application Serial No. 60/940, 394 entitled "VLSI LAYOUTS OF FULLY CONNECTED GENERALIZED NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007.

This application is related to and incorporates by reference in its entirety the U.S.

Provisional Patent Application Serial No. 60/984, 724 entitled "VLSI LAYOUTS OF

FULLY CONNECTED NETWORKS WITH LOCALITY EXPLOITATION" by Venkat Konda assigned to the same assignee as the current application, filed November 2, 2007.

This application is related to and incorporates by reference in its entirety the U.S. Provisional Patent Application Serial No. 61/018, 494 entitled "VLSI LAYOUTS OF FULLY CONNECTED GENERALIZED AND PYRAMID NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed January 1, 2008.

#### WO 2008/109756

requests.

5

#### PCT/US2008/056064

3

#### **BACKGROUND OF INVENTION**

Clos switching network, Benes switching network, and Cantor switching network are a network of switches configured as a multi-stage network so that fewer switching points are necessary to implement connections between its inlet links (also called "inputs") and outlet links (also called "outputs") than would be required by a single stage (e.g. crossbar) switch having the same number of inputs and outputs. Clos and Benes networks are very popularly used in digital crossconnects, switch fabrics and parallel

computer systems. However Clos and Benes networks may block some of the connection

- 10 There are generally three types of nonblocking networks: strictly nonblocking; wide sense nonblocking; and rearrangeably nonblocking (See V.E. Benes, "Mathematical Theory of Connecting Networks and Telephone Traffic" Academic Press, 1965 that is incorporated by reference, as background). In a rearrangeably nonblocking network, a connection path is guaranteed as a result of the network's ability to rearrange prior

- 15 connections as new incoming calls are received. In strictly nonblocking network, for any connection request from an inlet link to some set of outlet links, it is always possible to provide a connection path through the network to satisfy the request without disturbing other existing connections, and if more than one such path is available, any path can be selected without being concerned about realization of future potential connection

- 20 requests. In wide-sense nonblocking networks, it is also always possible to provide a connection path through the network to satisfy the request without disturbing other existing connections, but in this case the path used to satisfy the connection request must be carefully selected so as to maintain the nonblocking connecting capability for future potential connection requests.

- 25 Butterfly Networks, Banyan Networks, Batcher-Banyan Networks, Baseline Networks, Delta Networks, Omega Networks and Flip networks have been widely studied particularly for self routing packet switching applications. Also Benes Networks with radix of two have been widely studied and it is known that Benes Networks of radix two are shown to be built with back to back baseline networks which are rearrangeably 30 nonblocking for unicast connections.

PCT/US2008/056064

#### WO 2008/109756

#### 4

U.S. Patent 5,451,936 entitled "Non-blocking Broadcast Network" granted to Yang et al. is incorporated by reference herein as background of the invention. This patent describes a number of well known nonblocking multi-stage switching network designs in the background section at column 1, line 22 to column 3, 59. An article by Y.

5 Yang, and G.M., Masson entitled, "Non-blocking Broadcast Switching Networks" IEEE Transactions on Computers, Vol. 40, No. 9, September 1991 that is incorporated by reference as background indicates that if the number of switches in the middle stage, m, of a three-stage network satisfies the relation  $m \ge \min((n-1)(x+r^{1/x}))$  where

$1 \le x \le \min(n-1,r)$ , the resulting network is nonblocking for multicast assignments. In

10 the relation, r is the number of switches in the input stage, and n is the number of inlet links in each input switch.

U.S. Patent 6,885,669 entitled "Rearrangeably Nonblocking Multicast Multi-stage Networks" by Konda showed that three-stage Clos network is rearrangeably nonblocking for arbitrary fan-out multicast connections when m ≥ 2×n. And U.S. Patent 6,868,084

entitled "Strictly Nonblocking Multicast Multi-stage Networks" by Konda showed that three-stage Clos network is strictly nonblocking for arbitrary fan-out multicast connections when m ≥ 3×n-1.

In general multi-stage networks for stages of more than three and radix of more than two are not well studied. An article by Charles Clos entitled "A Study of Non-

- 20 Blocking Switching Networks" The Bell Systems Technical Journal, Volume XXXII, Jan. 1953, No.1, pp. 406-424 showed a way of constructing large multi-stage networks by recursive substitution with a crosspoint complexity of  $d^2 \times N \times (\log_d N)^{2.58}$  for strictly nonblocking unicast network. Similarly U.S. Patent 6,885,669 entitled "Rearrangeably Nonblocking Multicast Multi-stage Networks" by Konda showed a way of constructing

- 25 large multi-stage networks by recursive substitution for rearrangeably nonblocking multicast network. An article by D. G. Cantor entitled "On Non-Blocking Switching Networks" 1: pp. 367-377, 1972 by John Wiley and Sons, Inc., showed a way of constructing large multi-stage networks with a crosspoint complexity of  $d^2 \times N \times (\log_d N)^2$  for strictly nonblocking unicast, (by using  $\log_d N$  number of Benes

30 Networks for d = 2) and without counting the crosspoints in multiplexers and

#### WO 2008/109756

#### 5

#### PCT/US2008/056064

demultiplexers. Jonathan Turner studied the cascaded Benes Networks with radices larger than two, for nonblocking multicast with 10 times the crosspoint complexity of that of nonblocking unicast for a network of size N=256.

The crosspoint complexity of all these networks is prohibitively large to 5 implement the interconnect for multicast connections particularly in field programmable gate array (FPGA) devices, programmable logic devices (PLDs), field programmable interconnect Chips (FPICs), digital crossconnects, switch fabrics and parallel computer systems.

#### 10 SUMMARY OF INVENTION

A multi-stage network comprising  $(2 \times \log_d N) - 1$  stages is operated in strictly nonblocking manner for unicast includes an input stage having  $\frac{N}{d}$  switches with each of them having *d* inlet links and  $2 \times d$  outgoing links connecting to second stage switches, an output stage having  $\frac{N}{d}$  switches with each of them having *d* outlet links and  $2 \times d$ 15 incoming links connecting from switches in the penultimate stage. The network also has  $(2 \times \log_d N) - 3$  middle stages with each middle stage having  $\frac{2 \times N}{d}$  switches, and each switch in the middle stage has *d* incoming links connecting from the switches in its immediate preceding stage, and *d* outgoing links connecting to the switches in its immediate succeeding stage. Also the same multi-stage network is operated in

20 rearrangeably nonblocking manner for arbitrary fan-out multicast and each multicast connection is set up by use of at most two outgoing links from the input stage switch.

A multi-stage network comprising  $(2 \times \log_d N) - 1$  stages is operated in strictly nonblocking manner for multicast includes an input stage having  $\frac{N}{d}$  switches with each of them having d inlet links and  $3 \times d$  outgoing links connecting to second stage

#### 6

PCT/US2008/056064

switches, an output stage having  $\frac{N}{d}$  switches with each of them having d outlet links and  $3 \times d$  incoming links connecting from switches in the penultimate stage. The network also has  $(2 \times \log_d N) - 3$  middle stages with each middle stage having  $\frac{3 \times N}{d}$ switches, and each switch in the middle stage has d incoming links connecting from the

5 switches in its immediate preceding stage, and *d* outgoing links connecting to the switches in its immediate succeeding stage.

#### **BRIEF DESCRIPTION OF DRAWINGS**

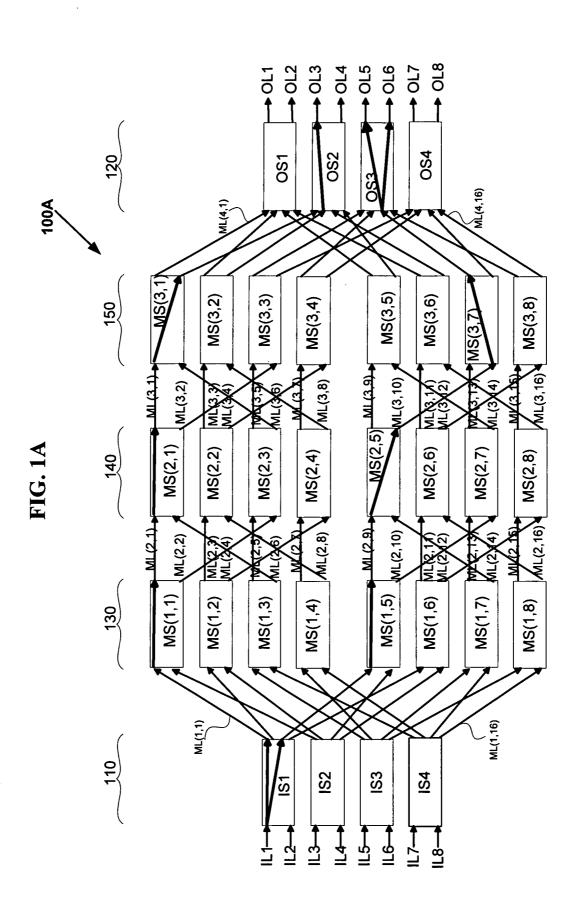

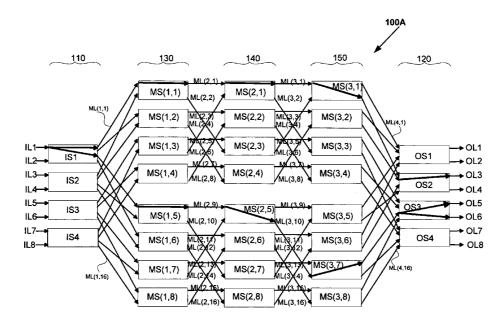

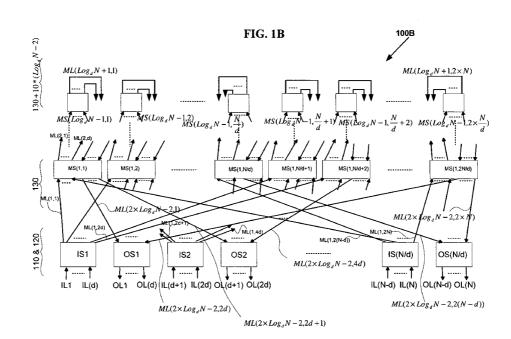

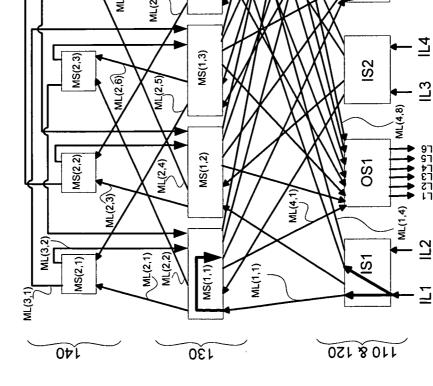

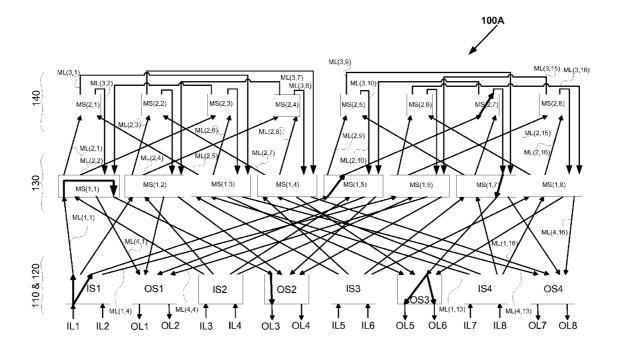

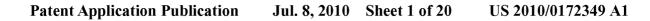

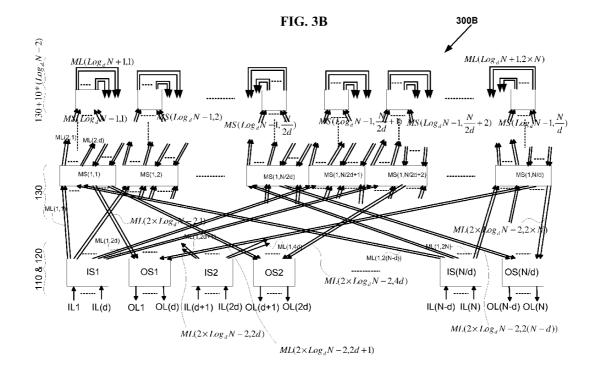

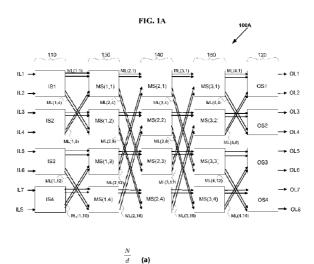

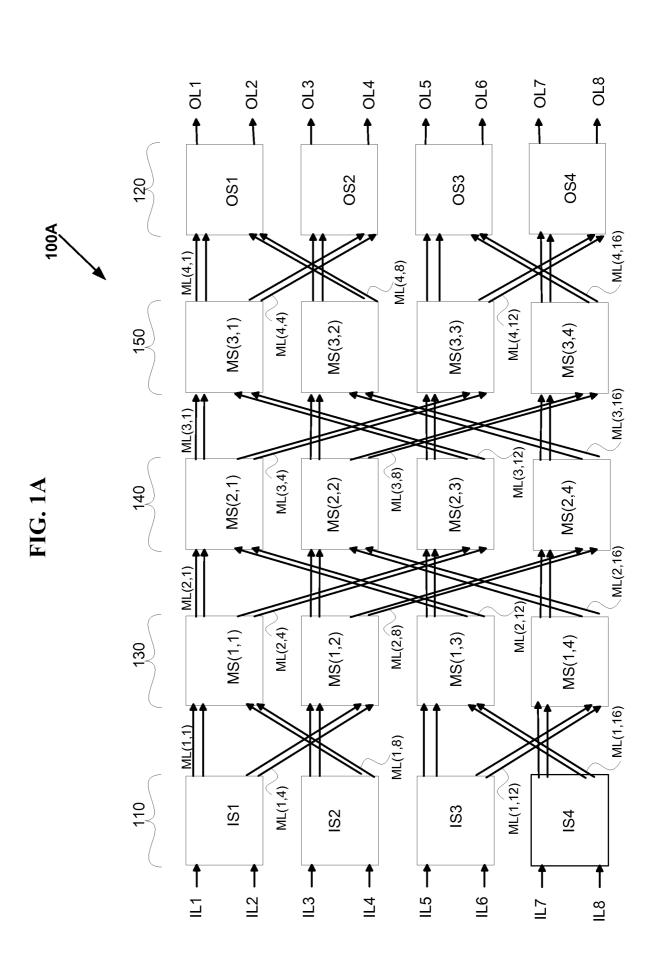

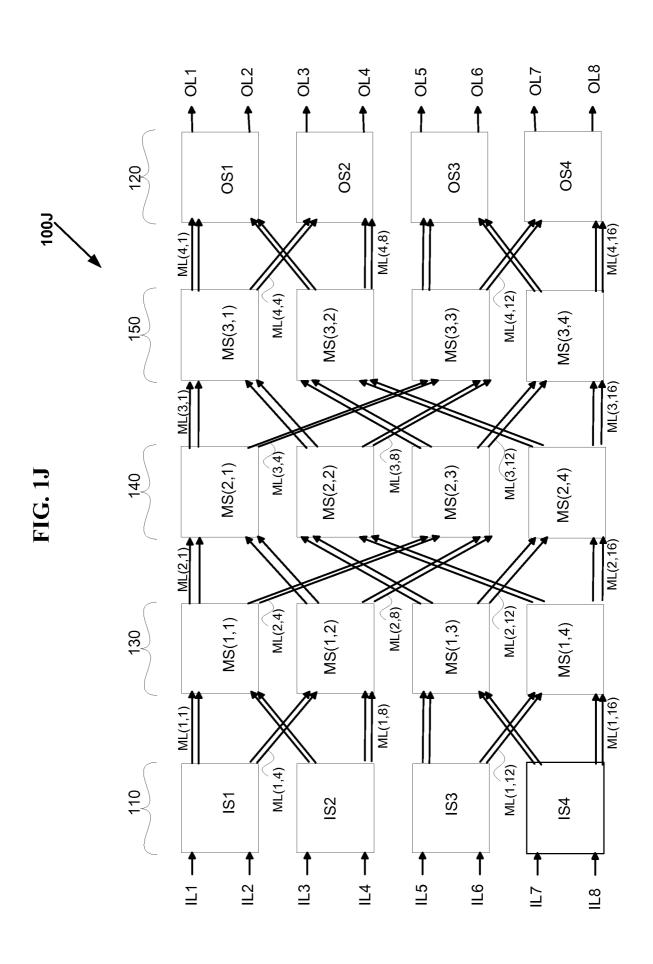

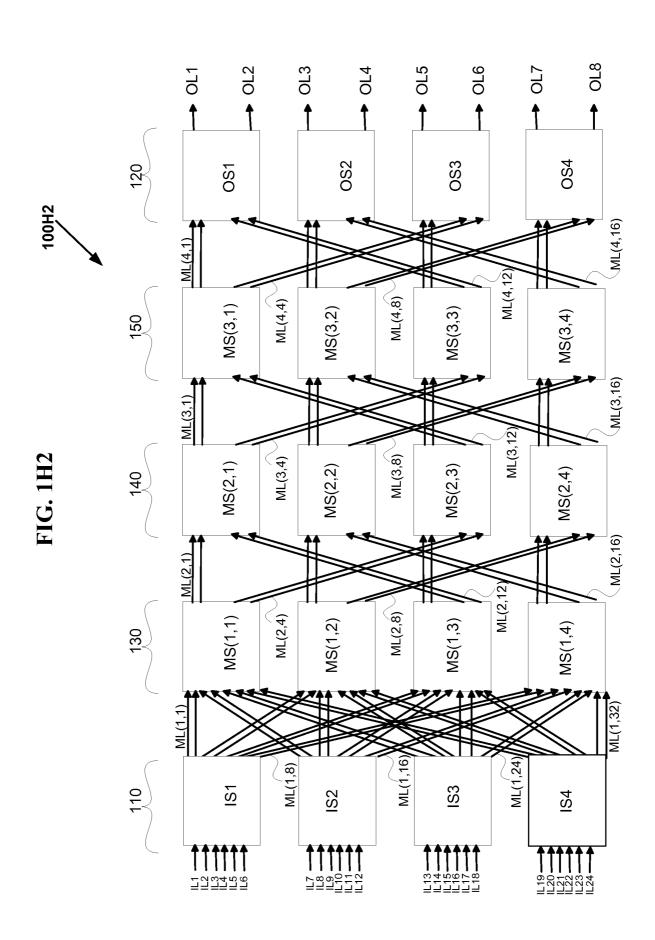

- FIG. 1A is a diagram 100A of an exemplary symmetrical multi-stage network 10 V(N,d,s) having inverse Benes connection topology of five stages with N = 8, d = 2 and s=2 with exemplary multicast connections, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

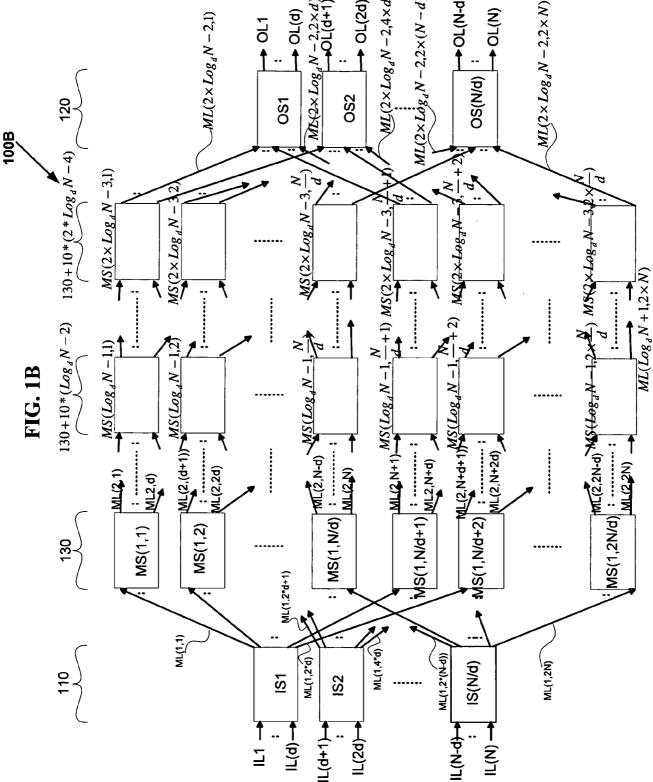

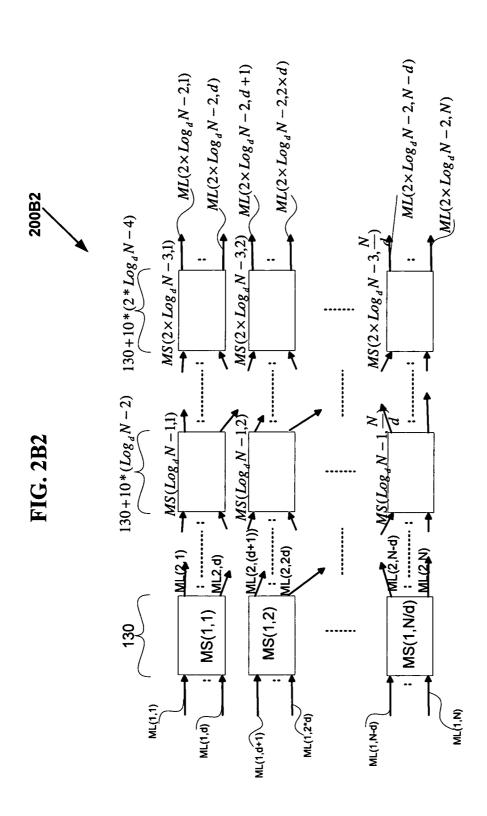

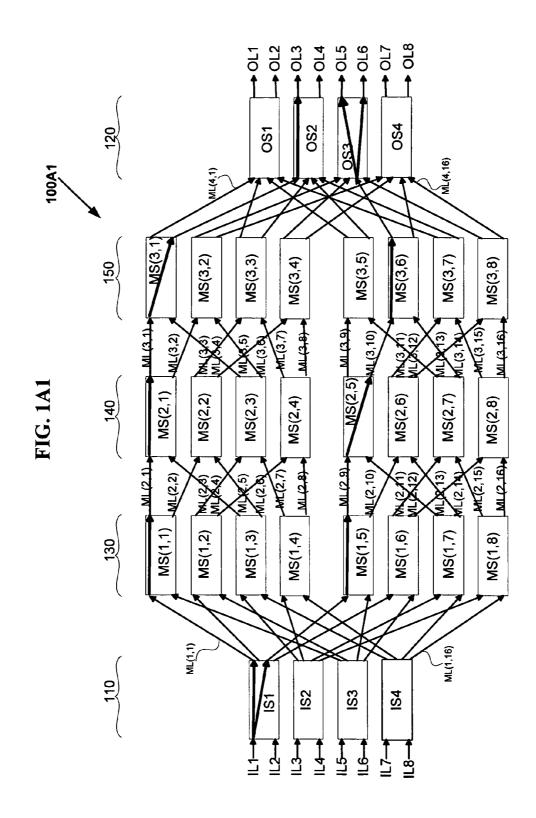

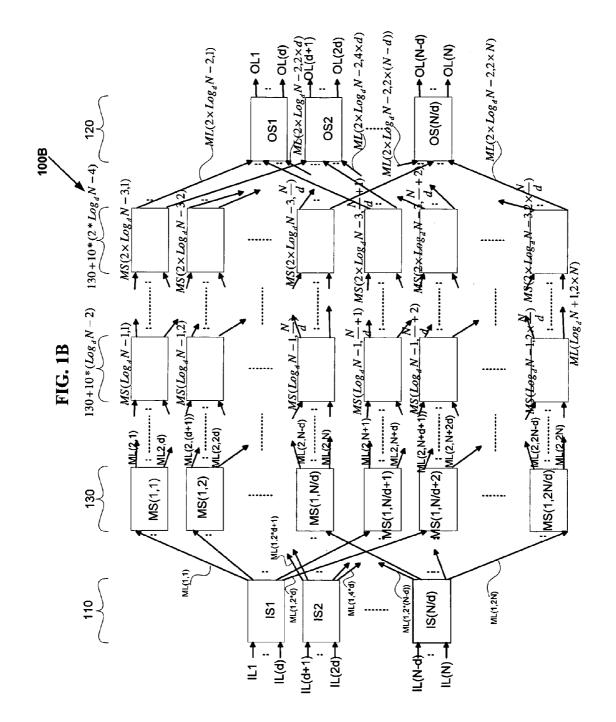

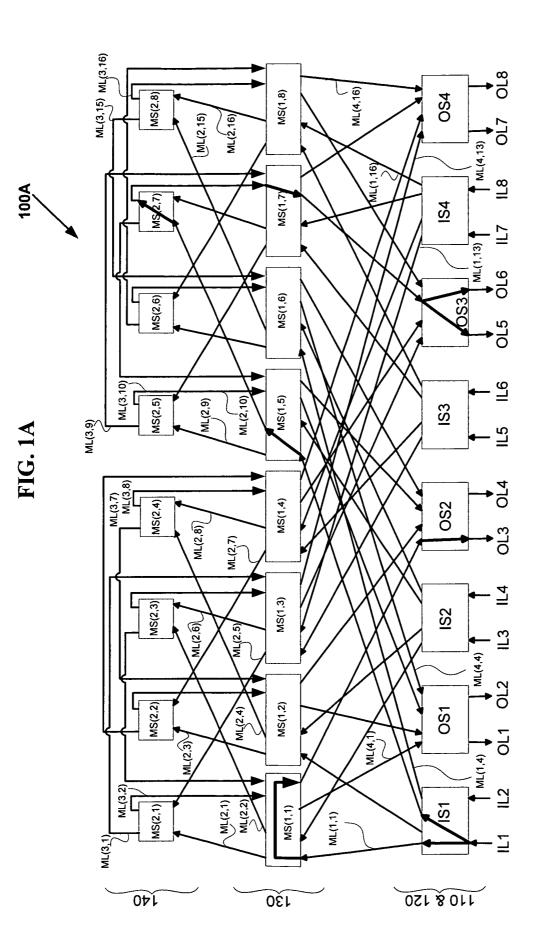

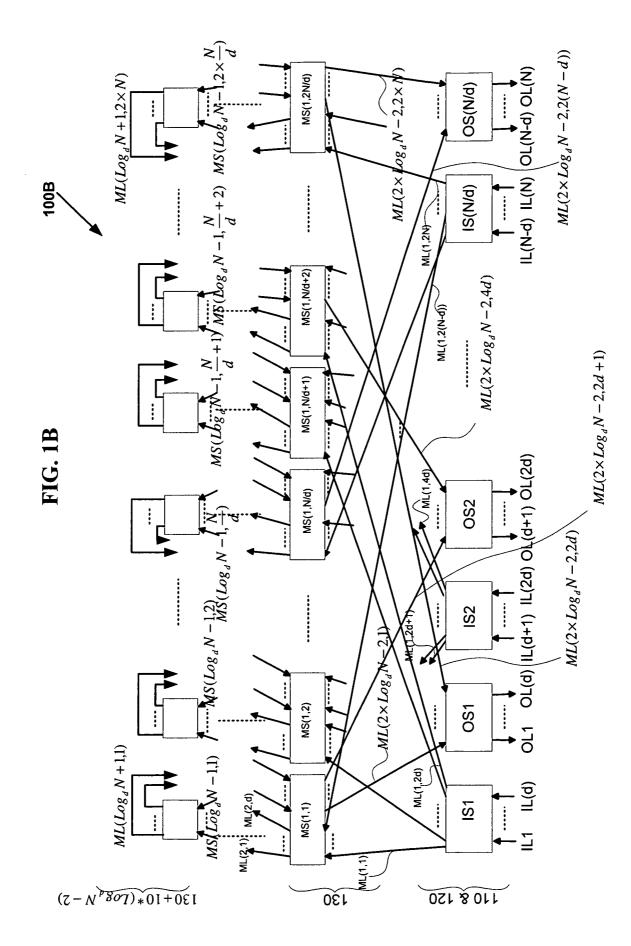

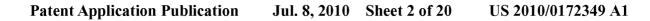

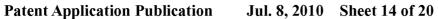

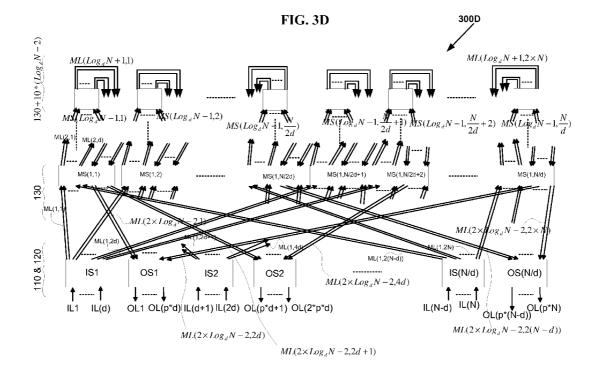

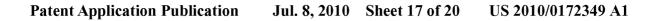

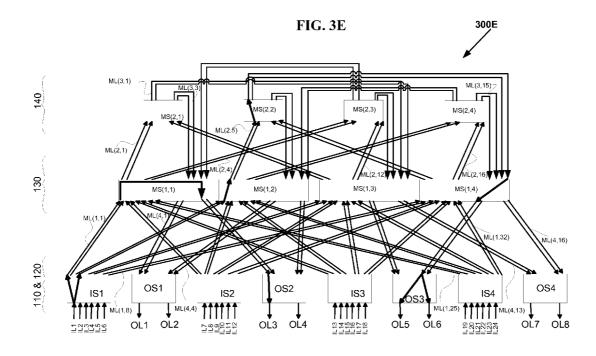

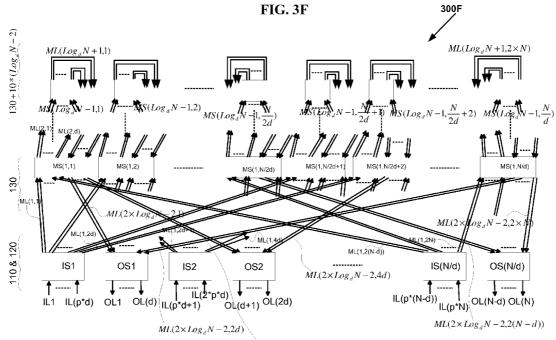

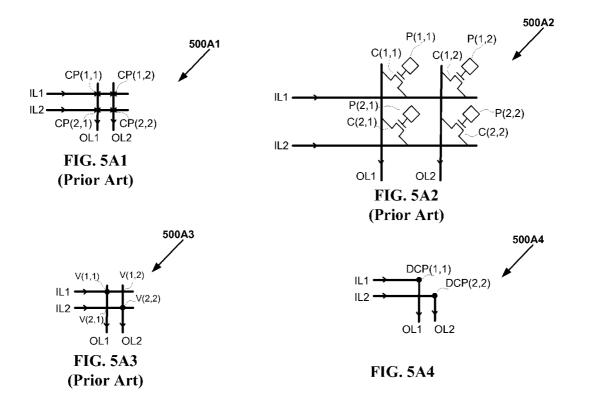

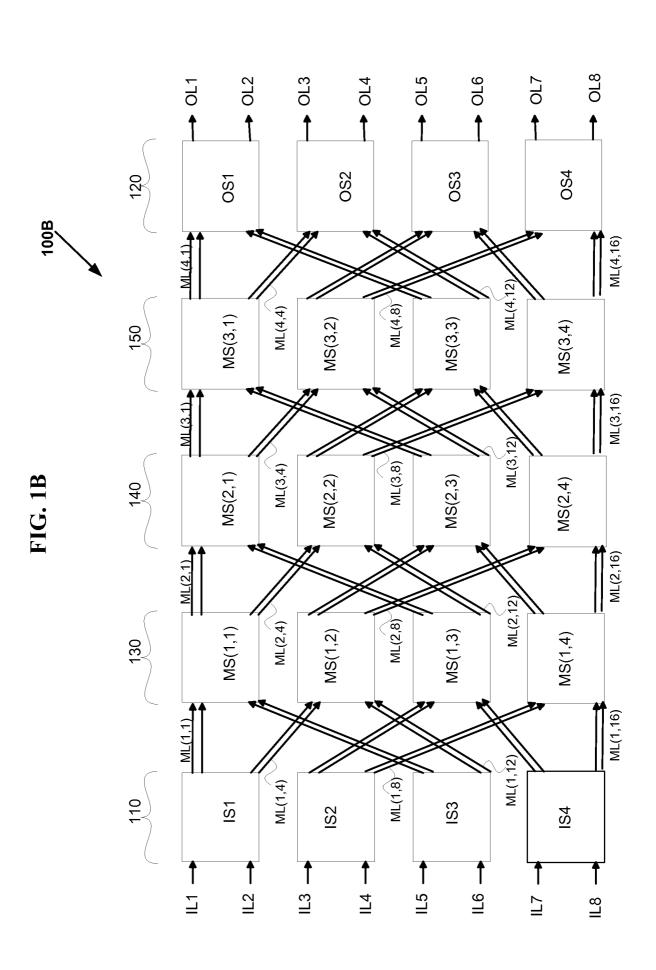

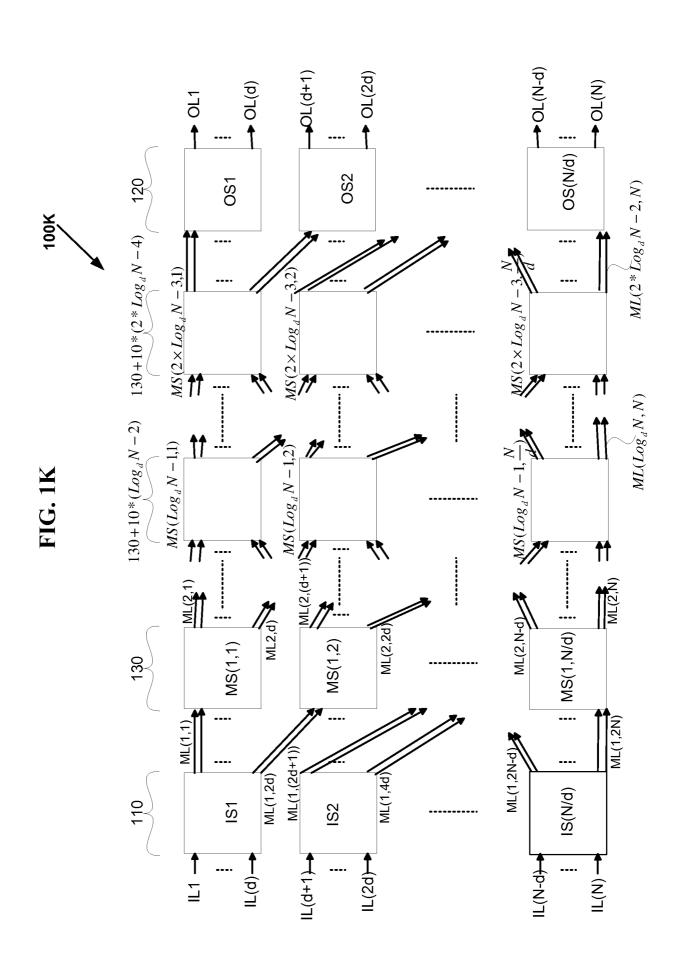

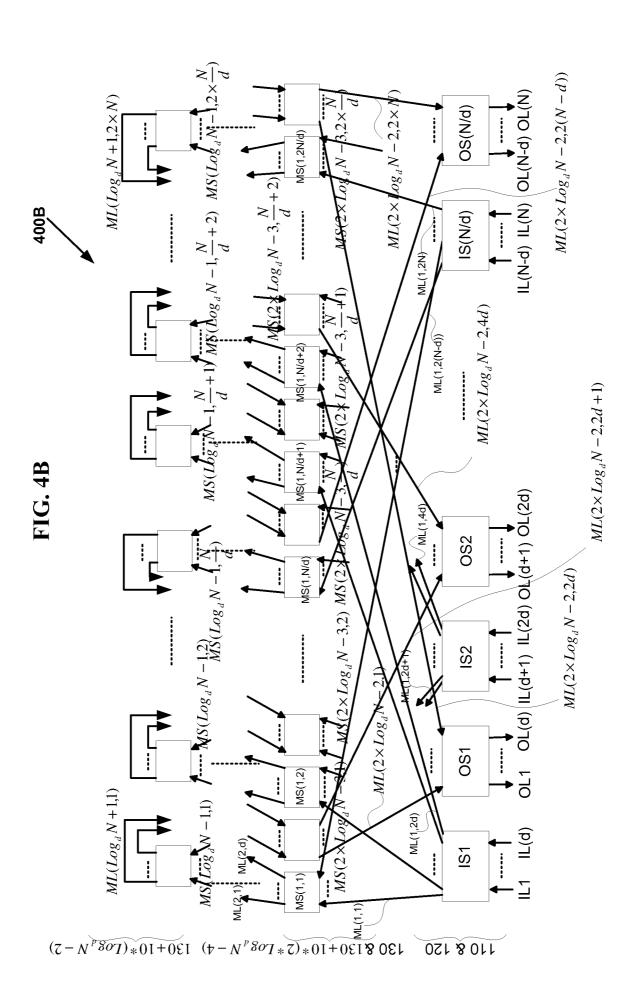

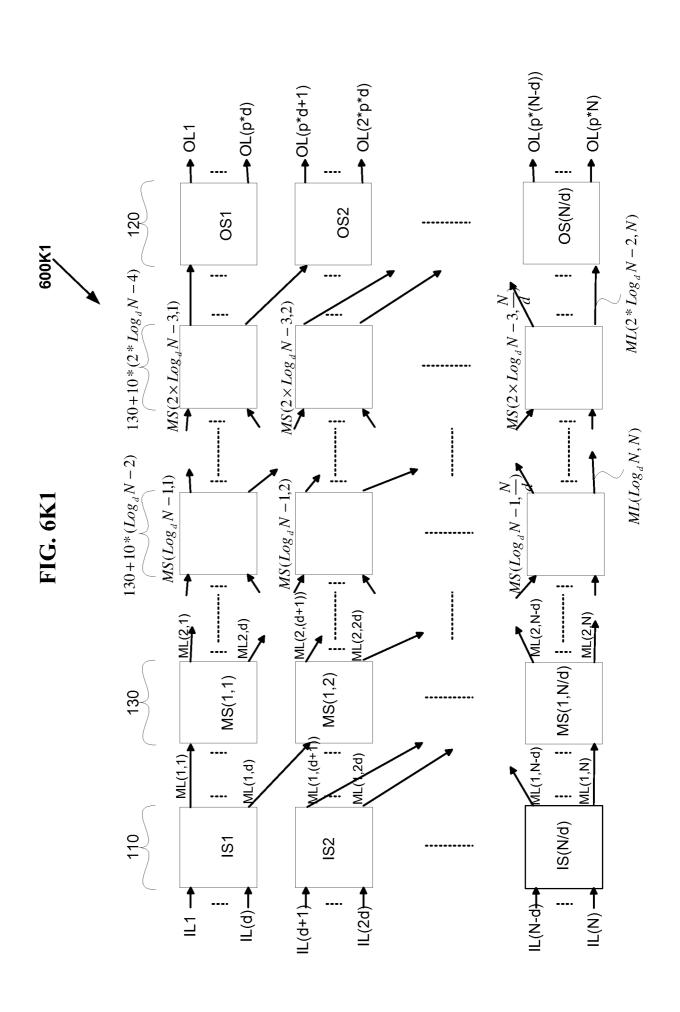

- FIG. 1B is a diagram 100B of a general symmetrical multi-stage network 15 V(N,d,2) with  $(2 \times \log_d N) - 1$  stages strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections in accordance with the invention.

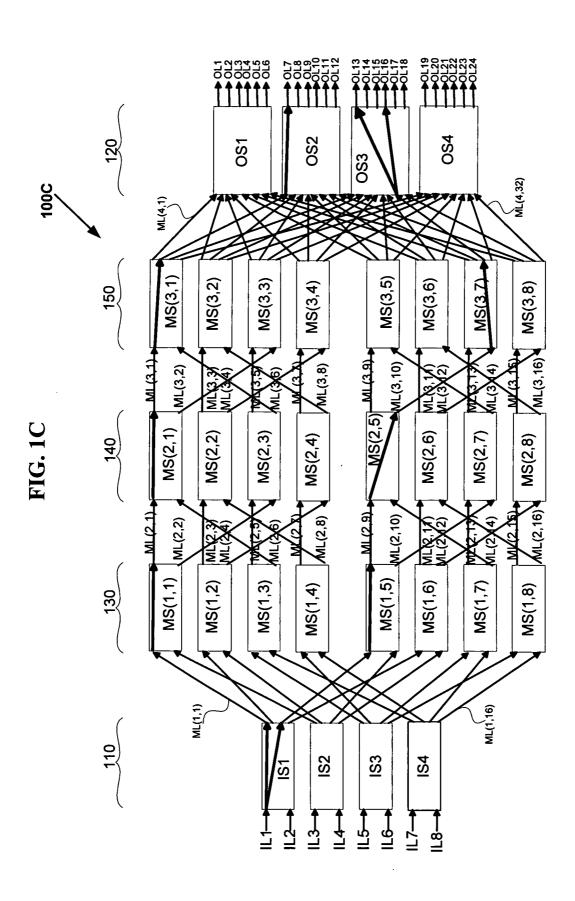

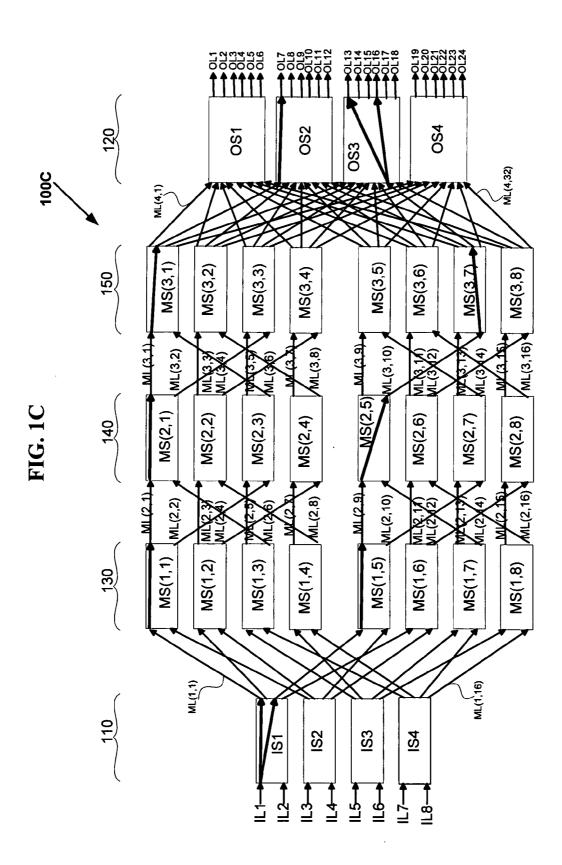

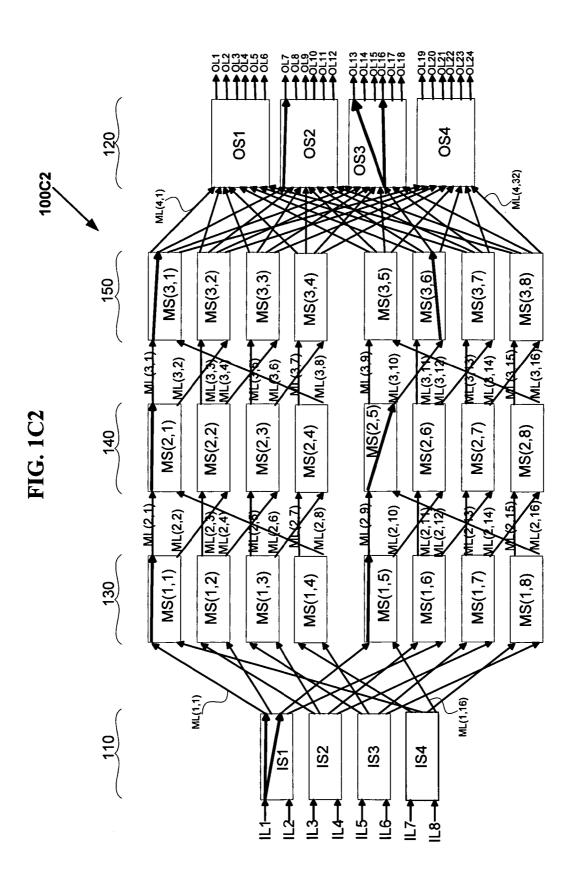

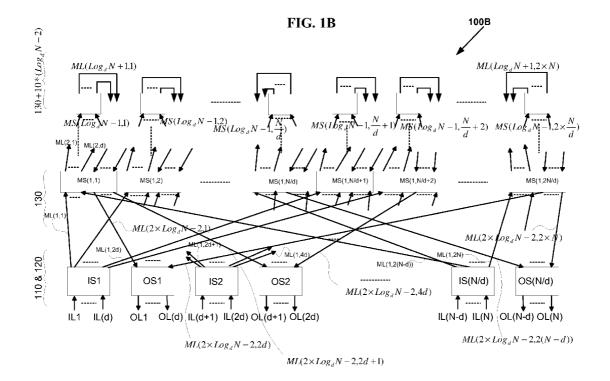

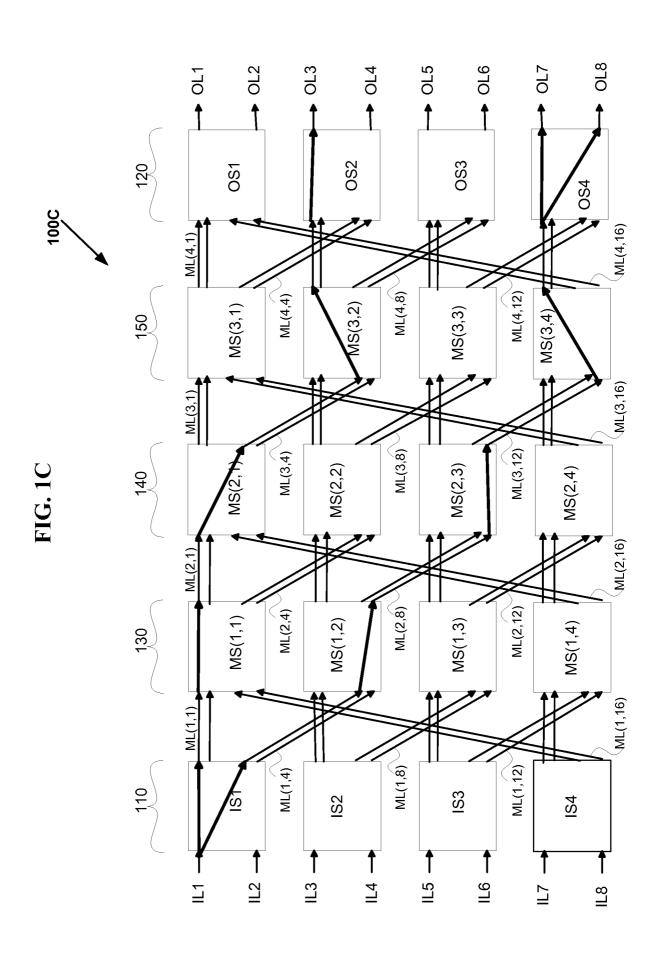

FIG. 1C is a diagram 100C of an exemplary asymmetrical multi-stage network  $V(N_1, N_2, d, 2)$  having inverse Benes connection topology of five stages with N<sub>1</sub> = 8, N2 20 = p\* N<sub>1</sub> = 24 where p = 3, and d = 2 with exemplary multicast connections, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

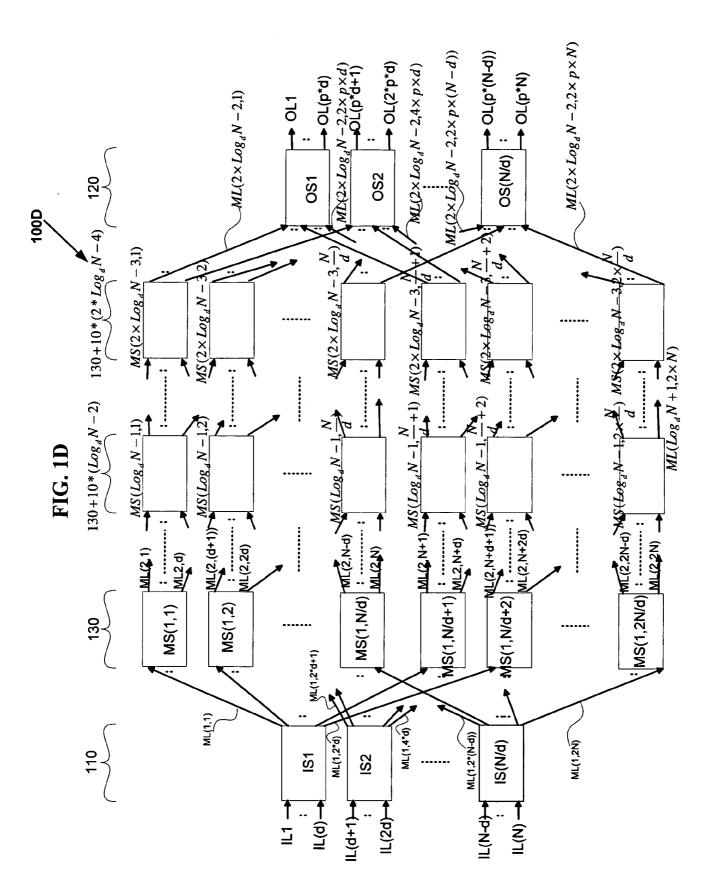

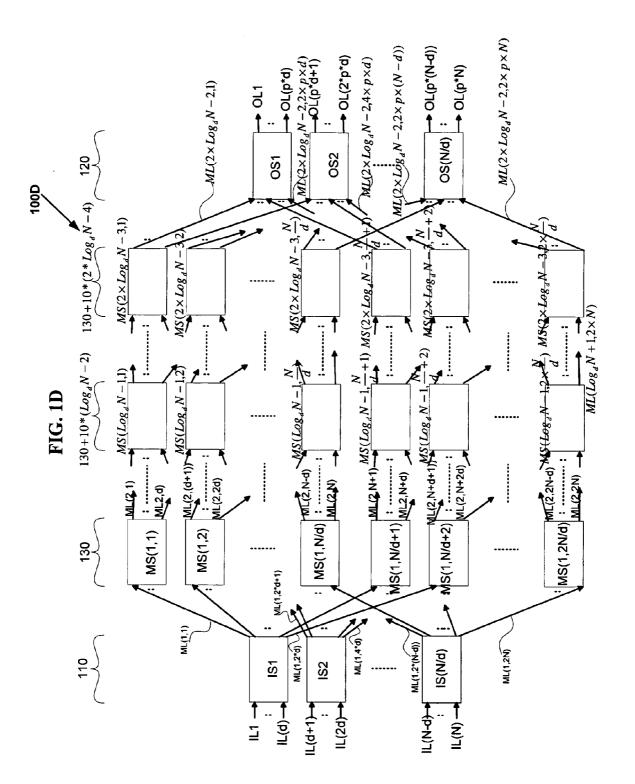

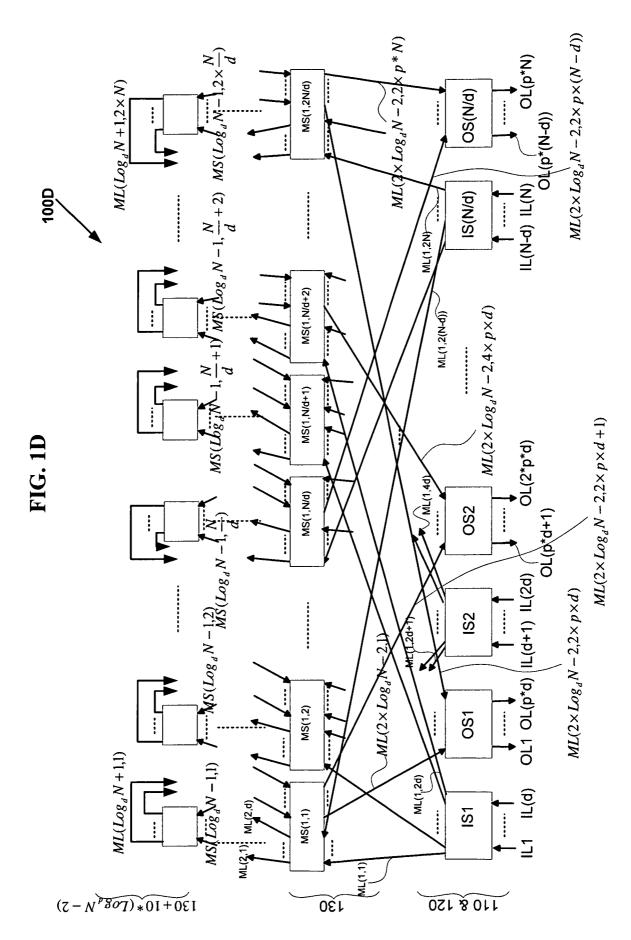

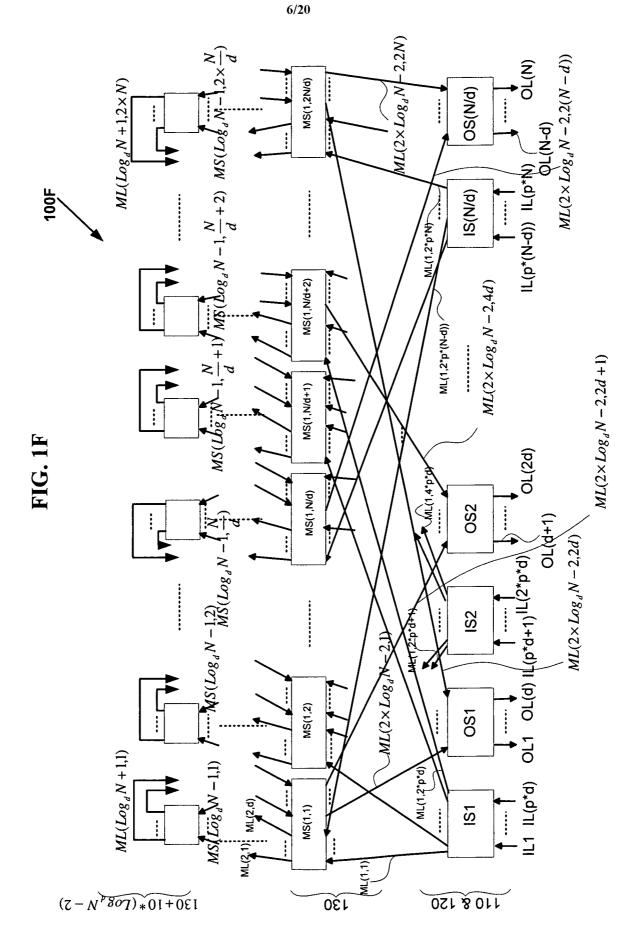

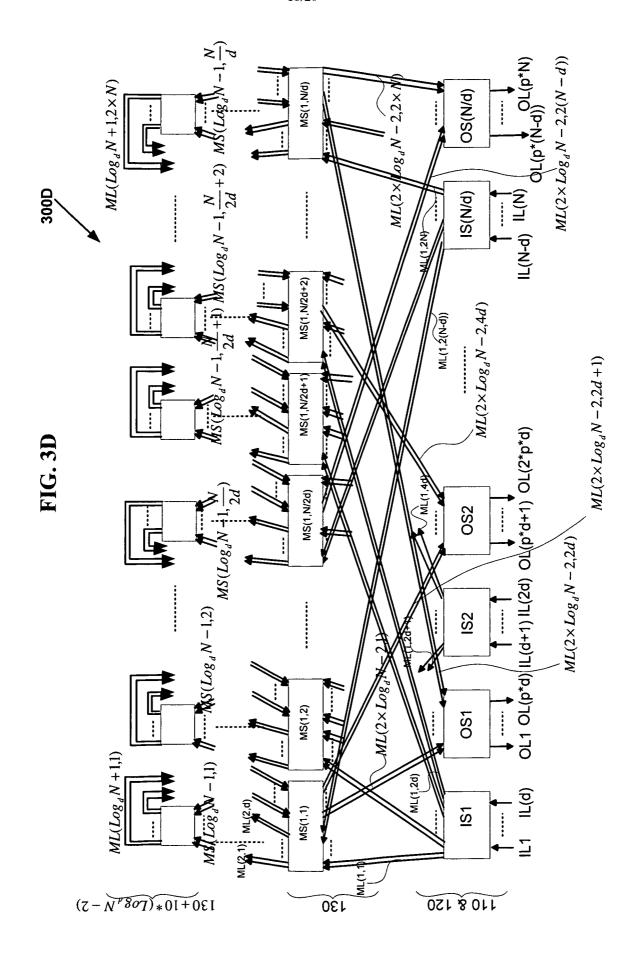

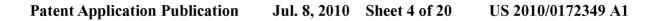

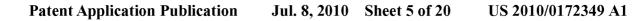

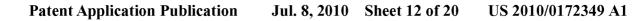

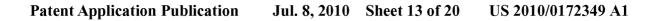

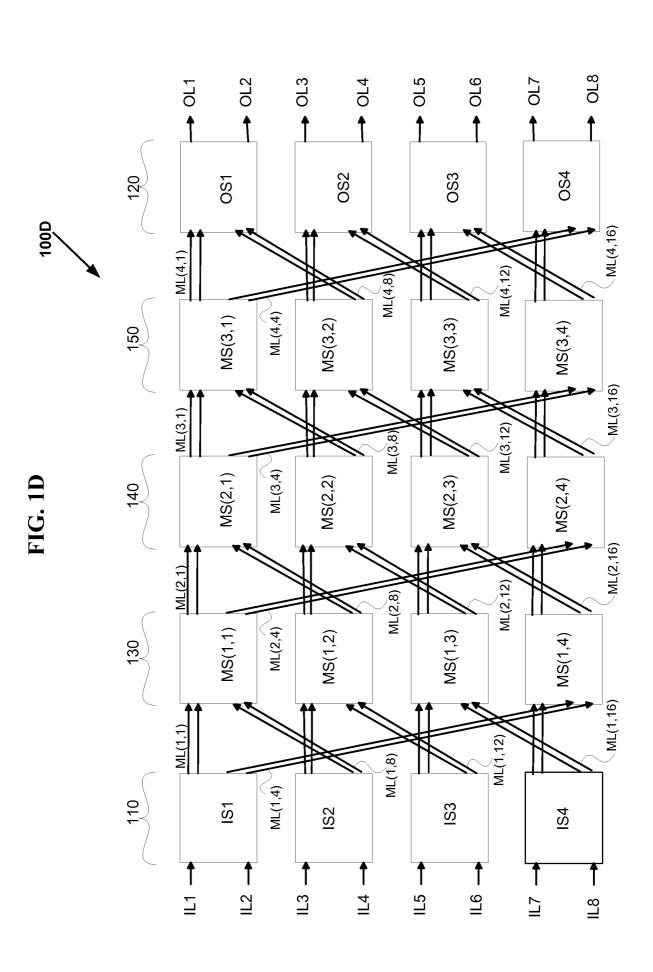

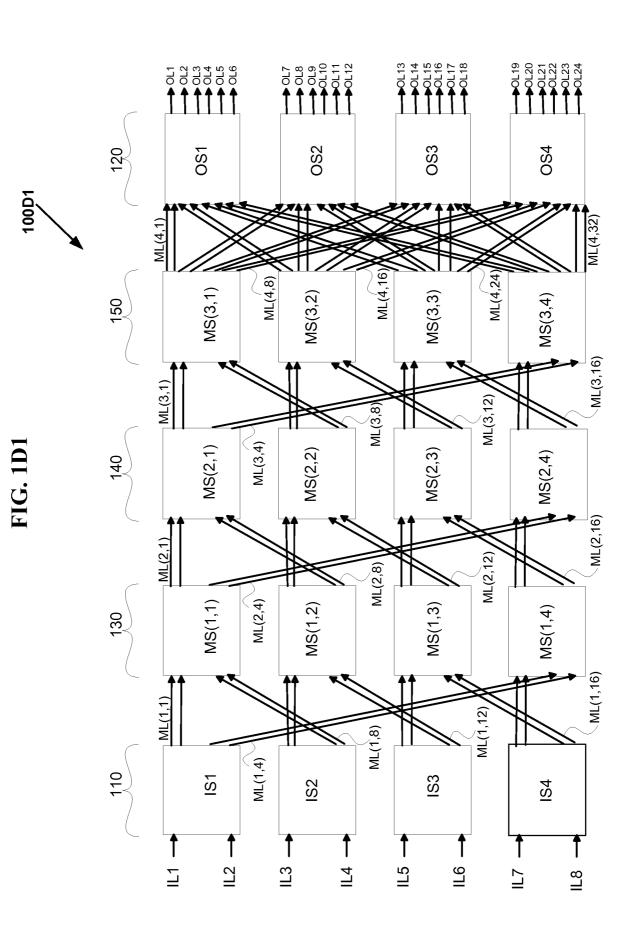

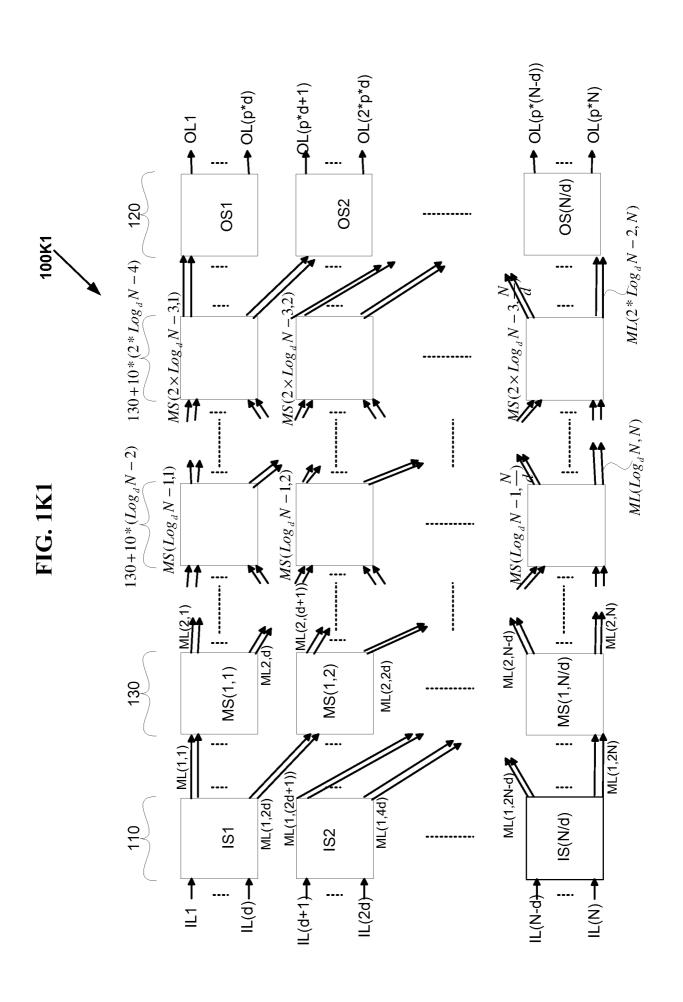

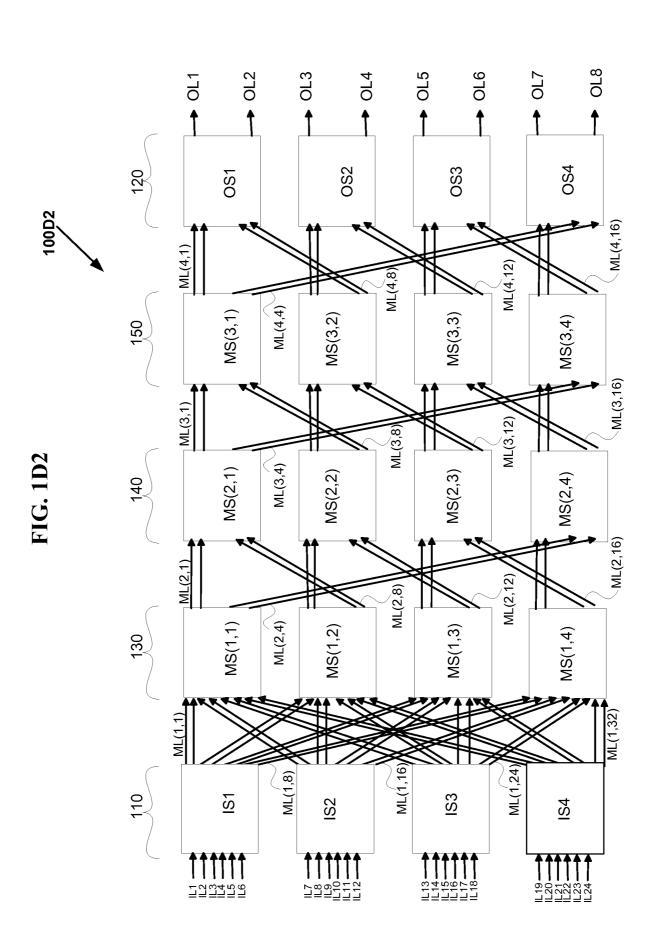

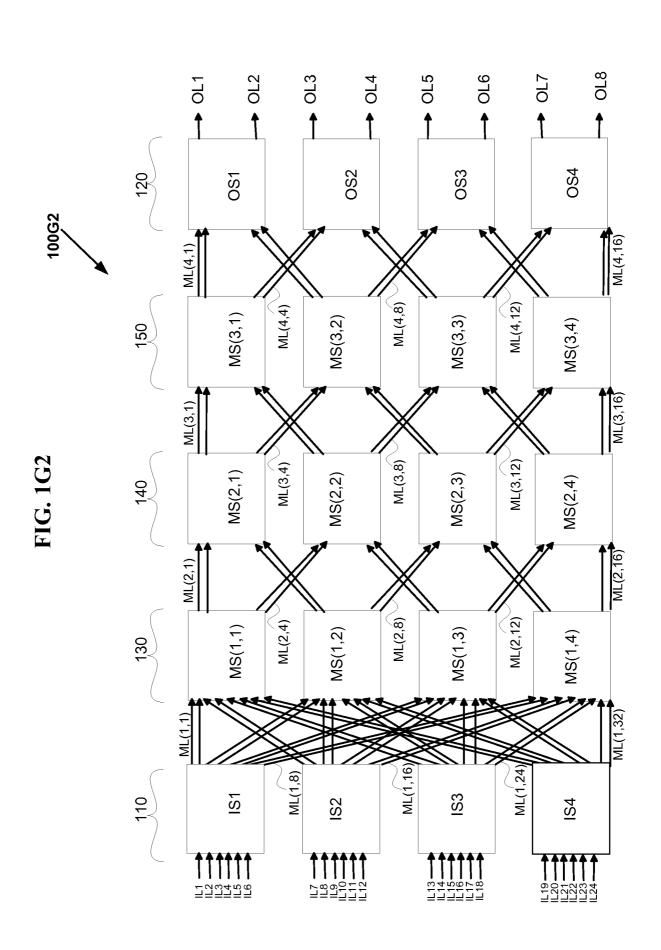

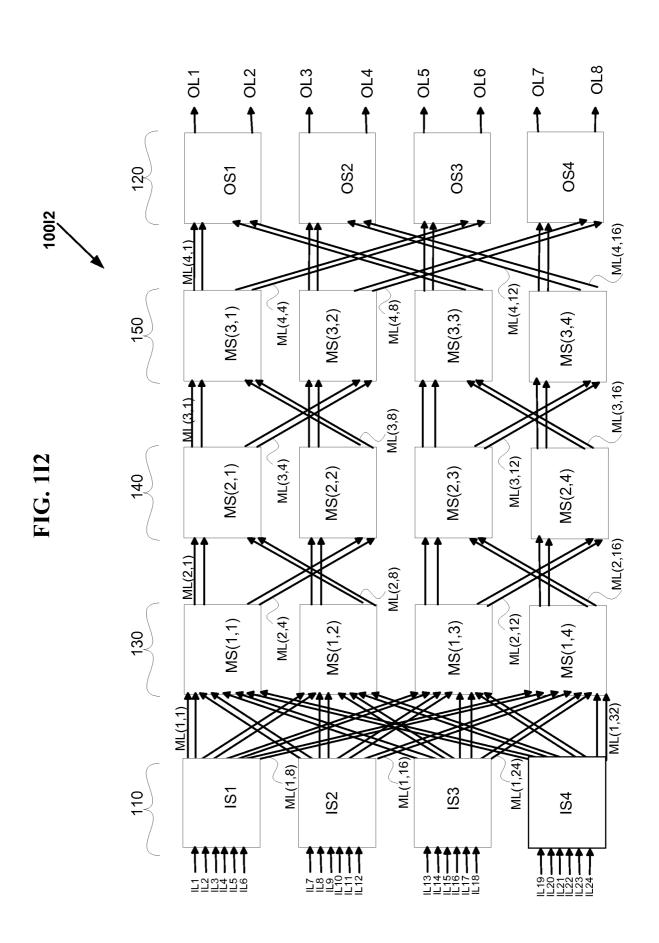

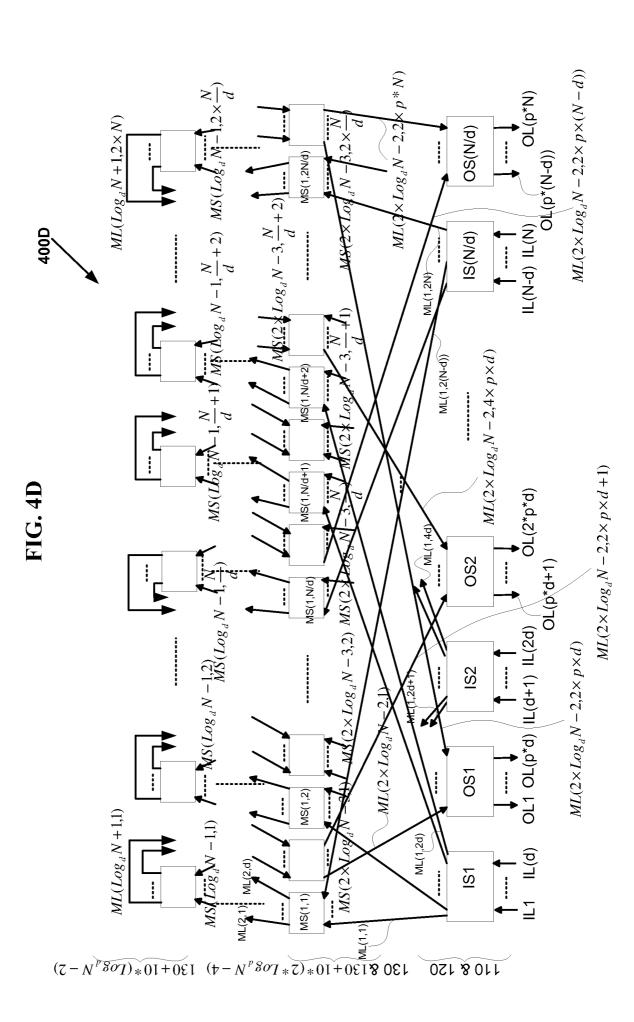

FIG. 1D is a diagram 100D of a general asymmetrical multi-stage network  $V(N_1, N_2, d, 2)$  with  $N_2 = p^* N_1$  and with  $(2 \times \log_d N) - 1$  stages strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fanout multicast connections in accordance with the invention.

#### 7

PCT/US2008/056064

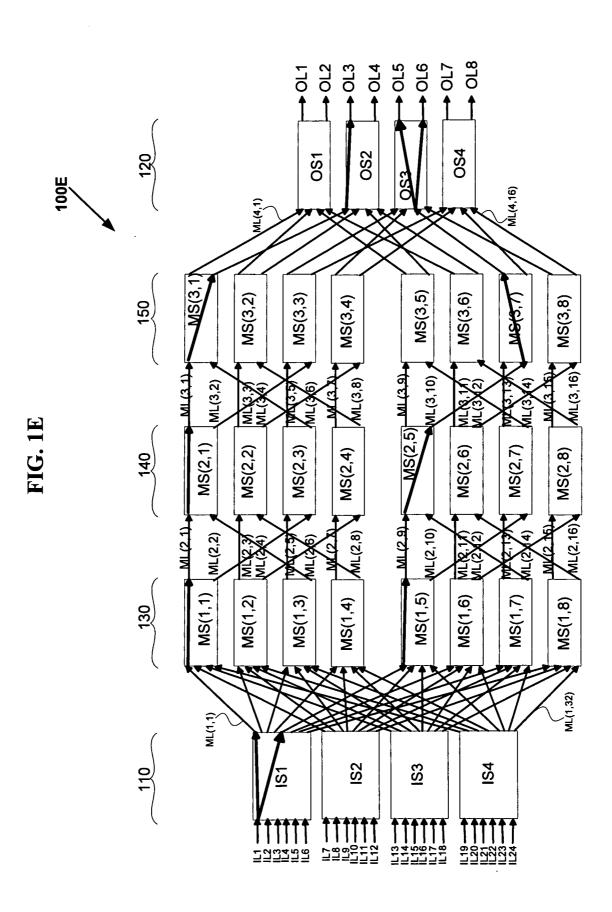

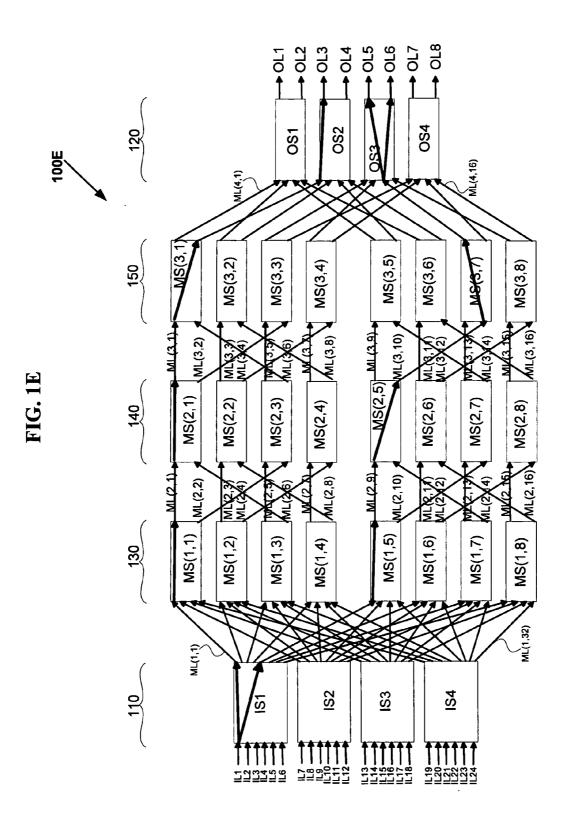

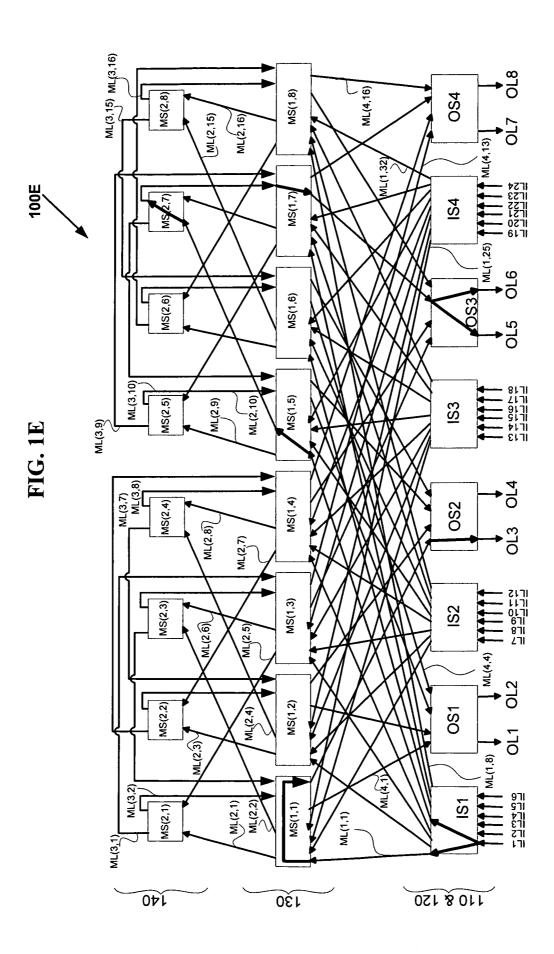

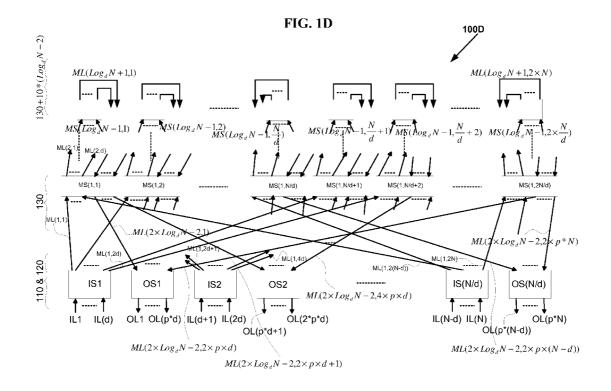

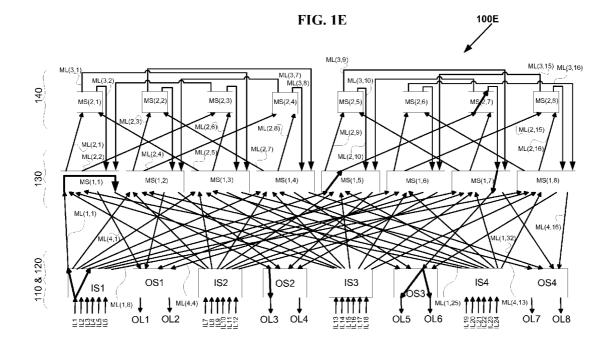

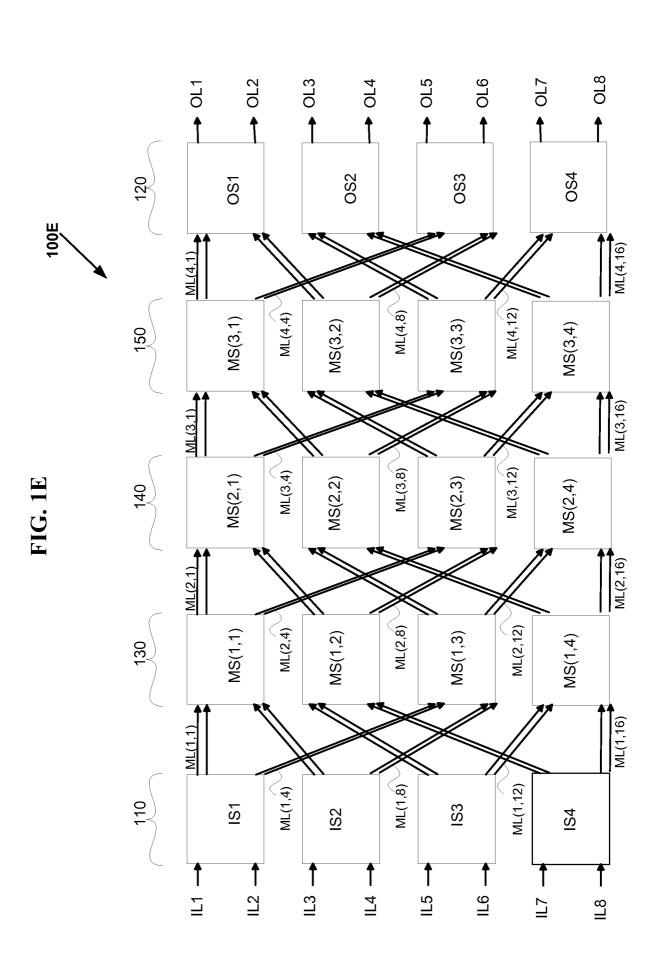

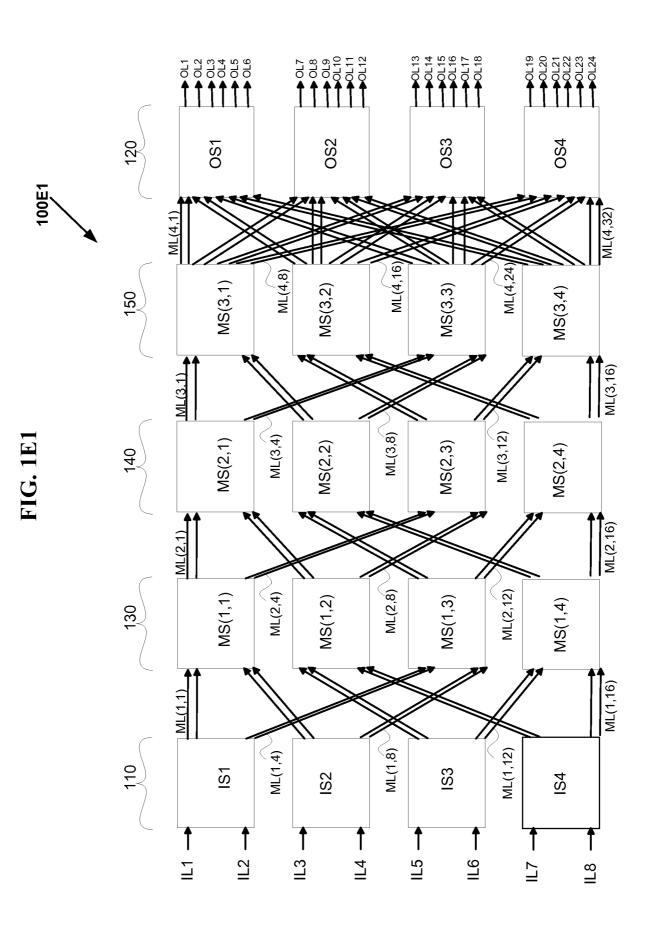

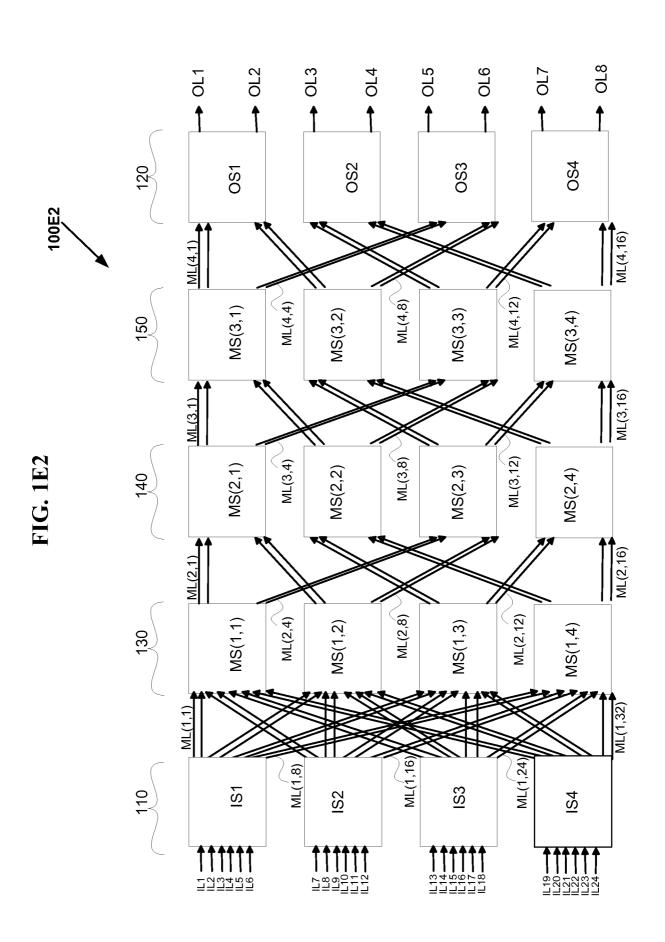

FIG. 1E is a diagram 100E of an exemplary asymmetrical multi-stage network  $V(N_1, N_2, d, 2)$  having inverse Benes connection topology of five stages with N<sub>2</sub> = 8, N<sub>1</sub> = p\* N<sub>2</sub> = 24, where p = 3, and d = 2 with exemplary multicast connections, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

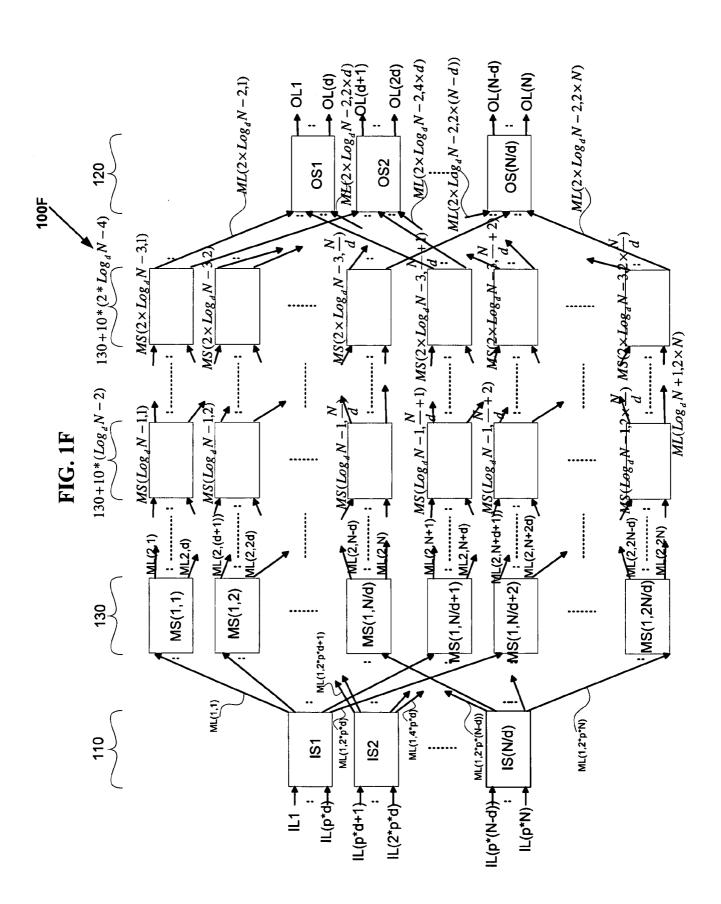

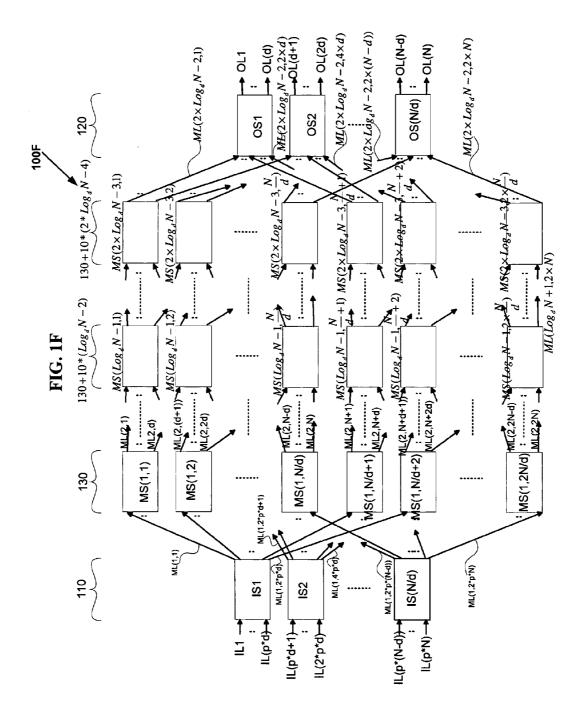

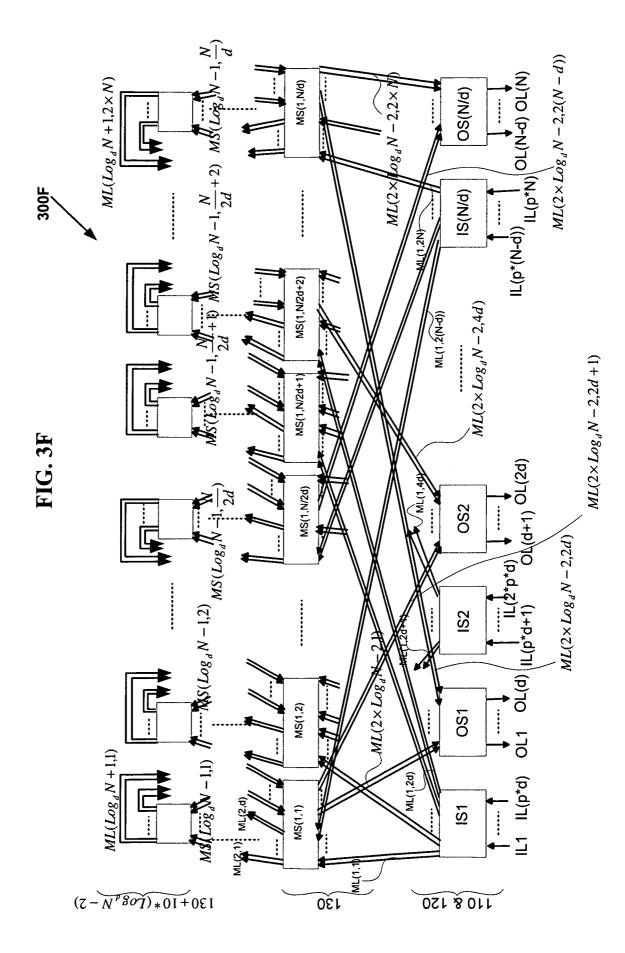

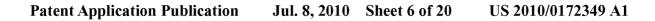

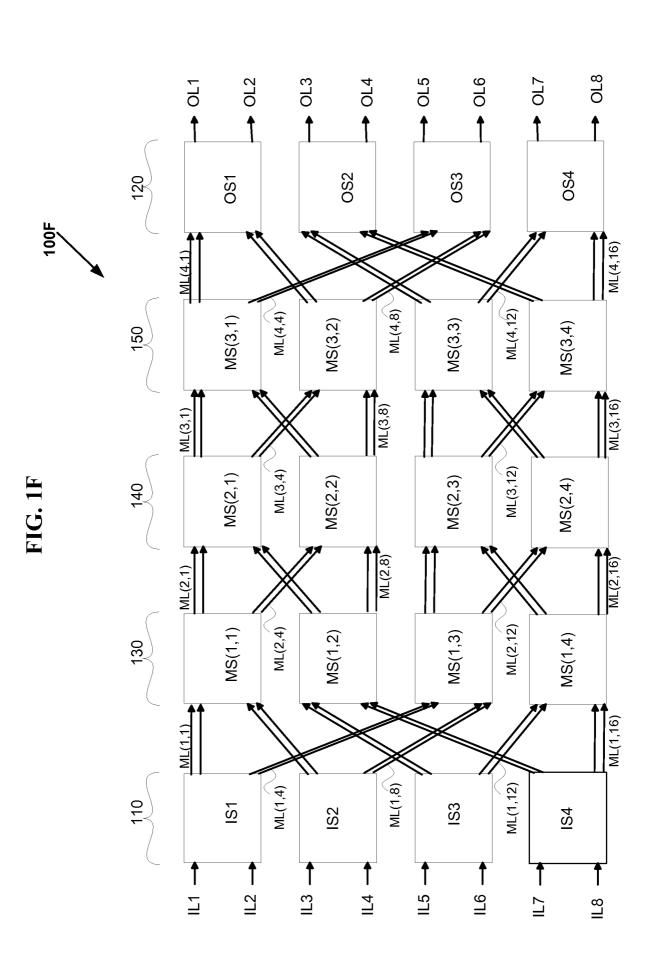

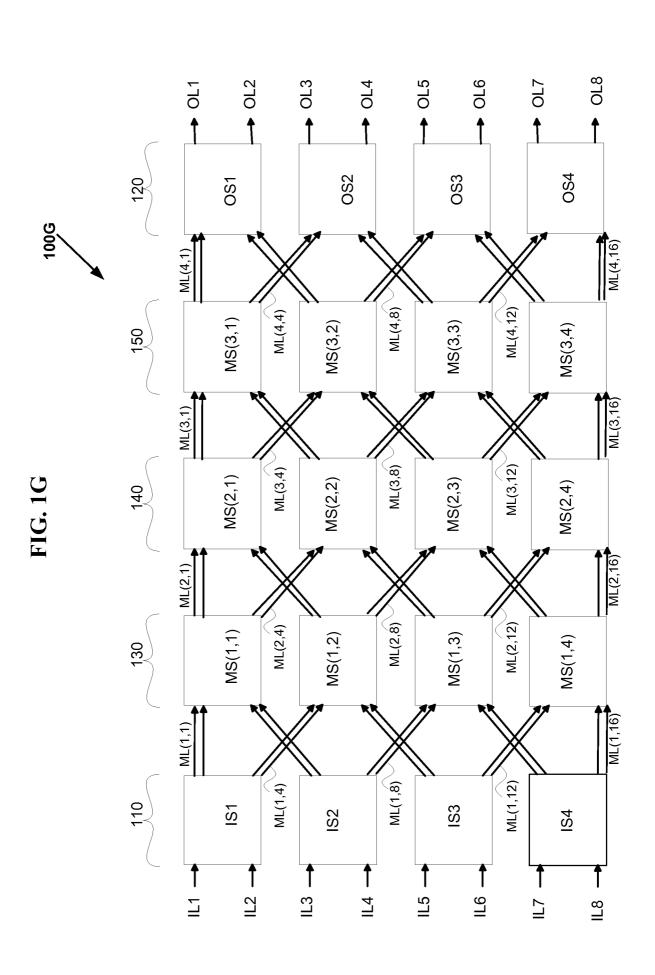

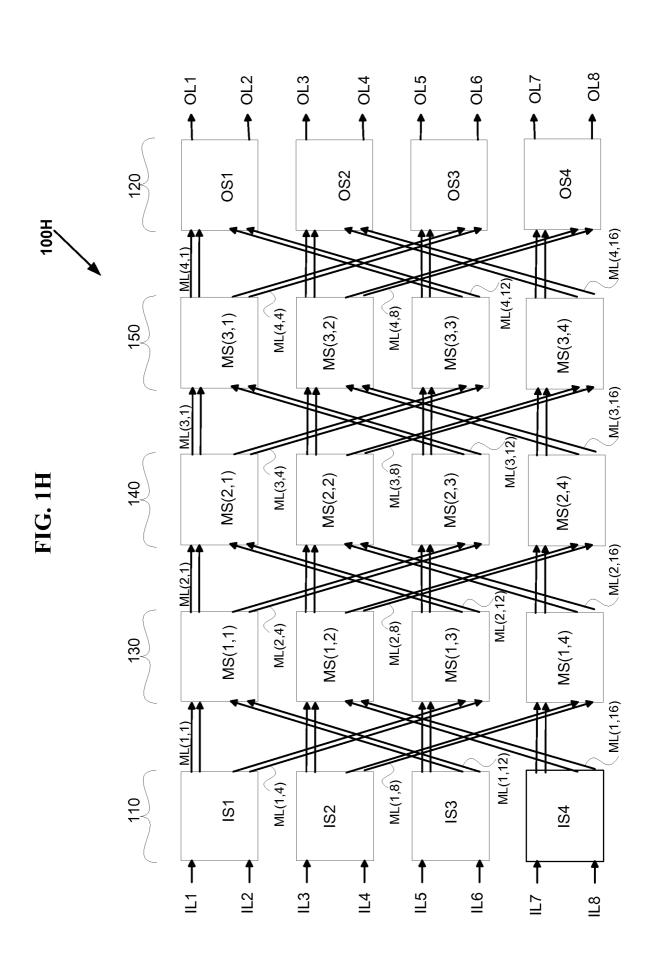

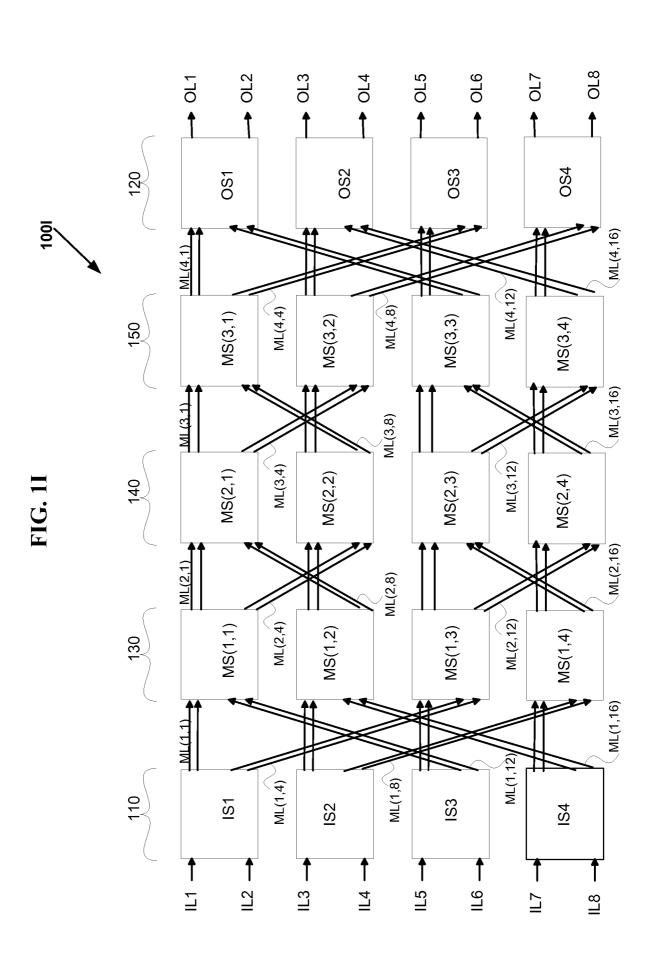

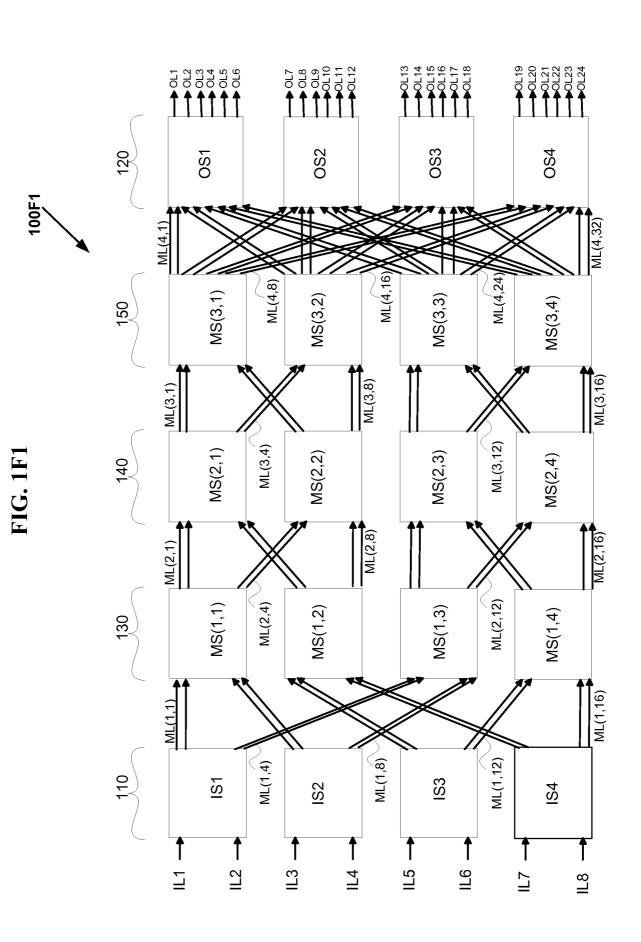

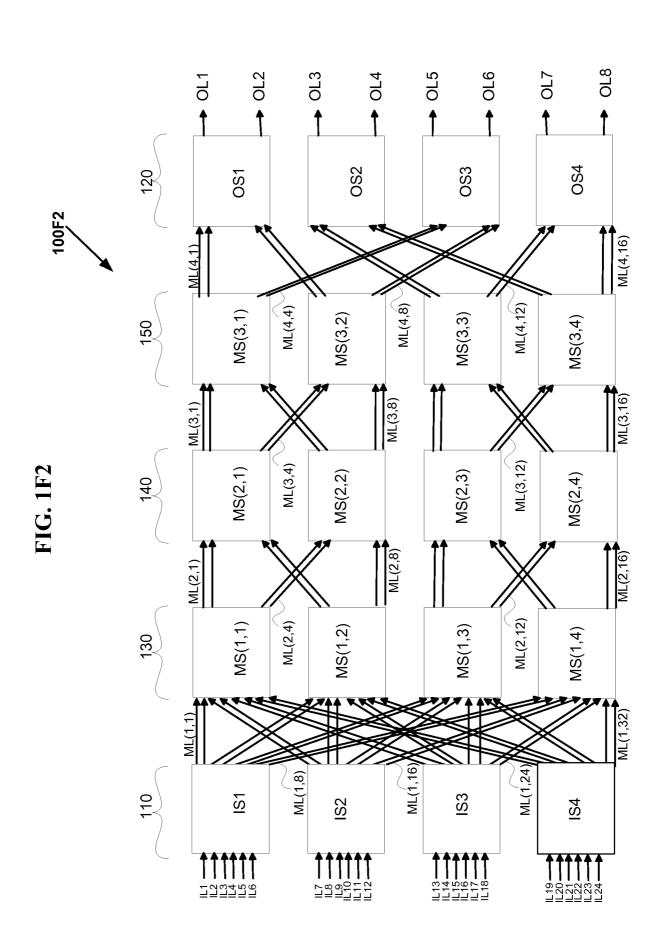

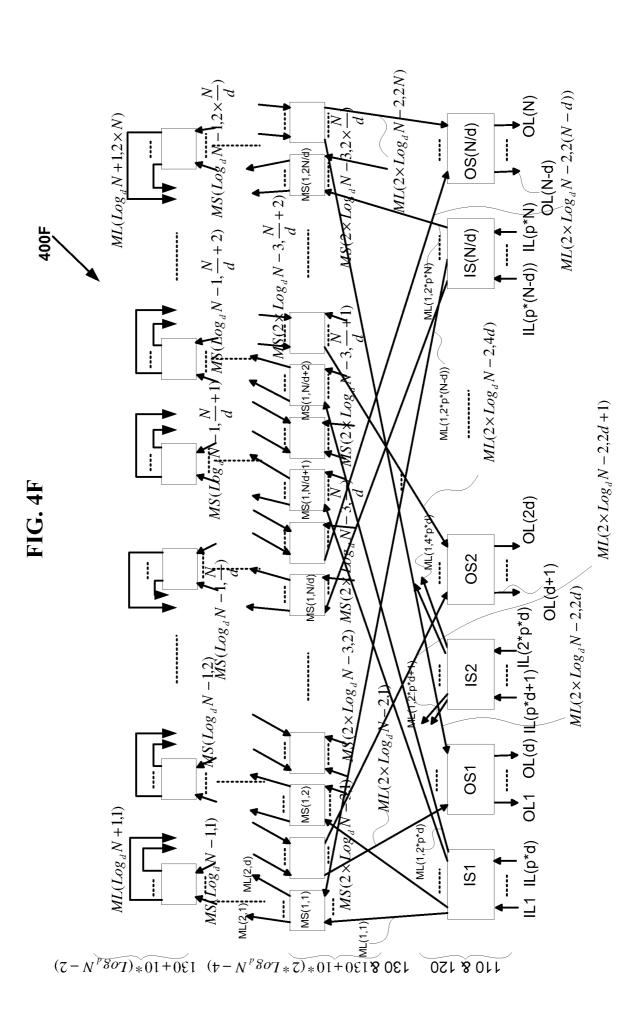

FIG. 1F is a diagram 100F of a general asymmetrical multi-stage network  $V(N_1, N_2, d, 2)$  with  $N_1 = p^* N_2$  and with  $(2 \times \log_d N) - 1$  stages strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fanout multicast connections in accordance with the invention.

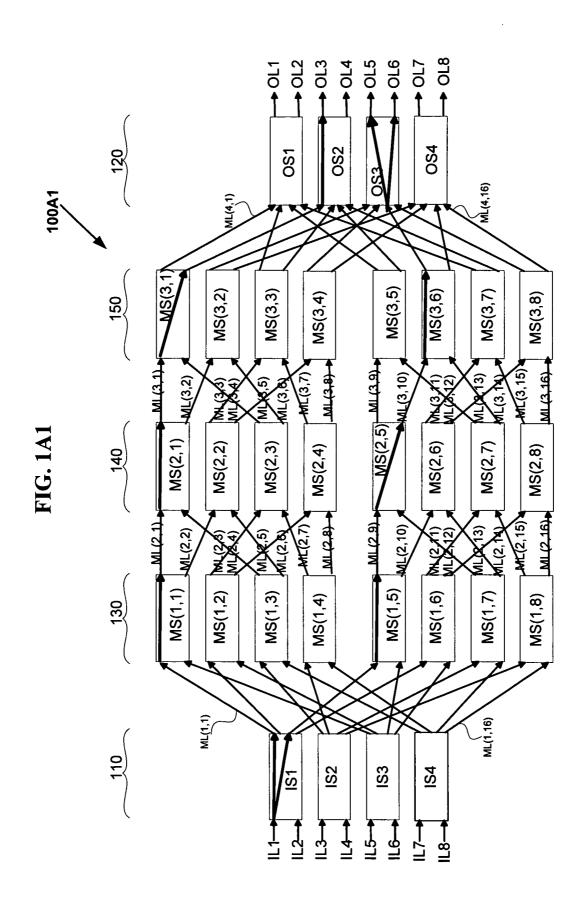

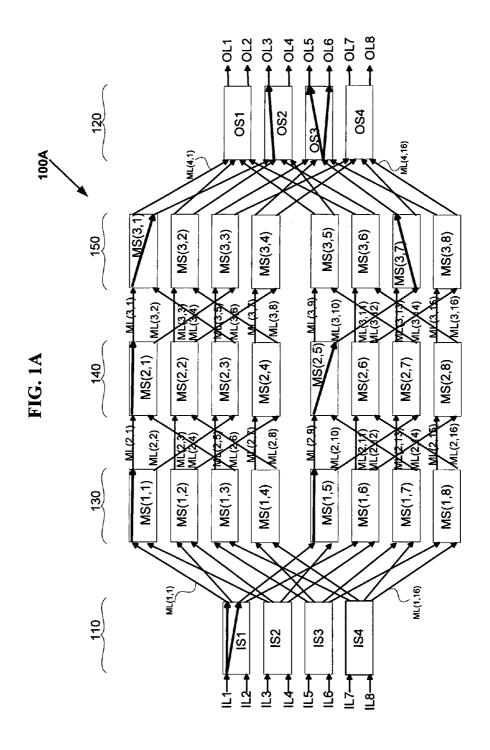

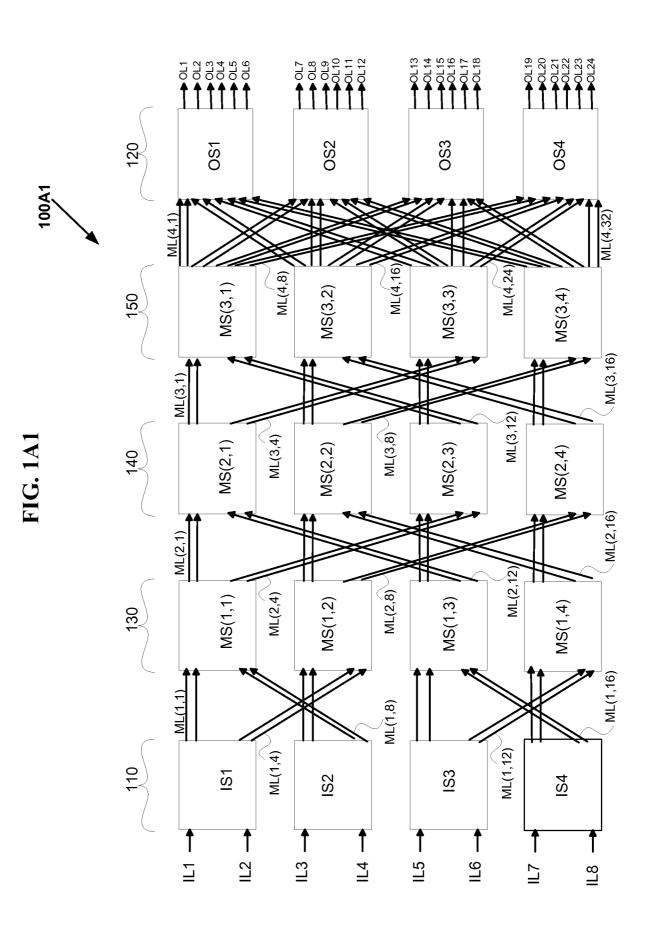

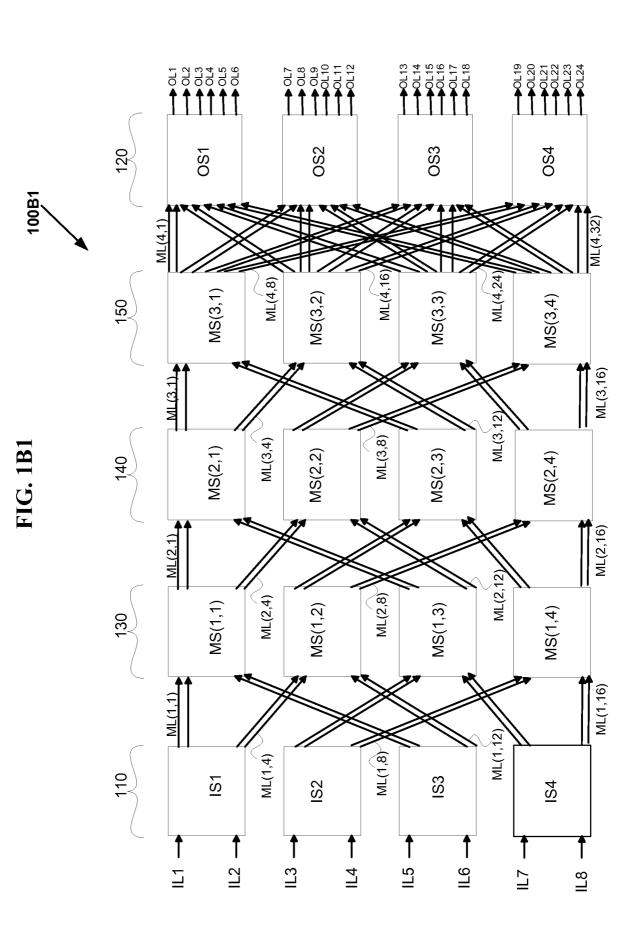

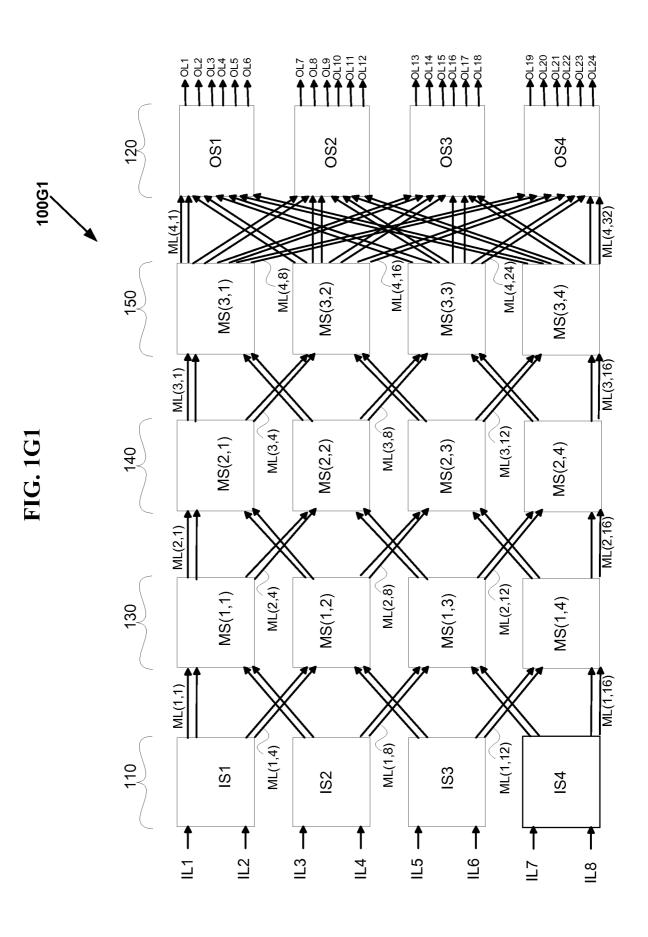

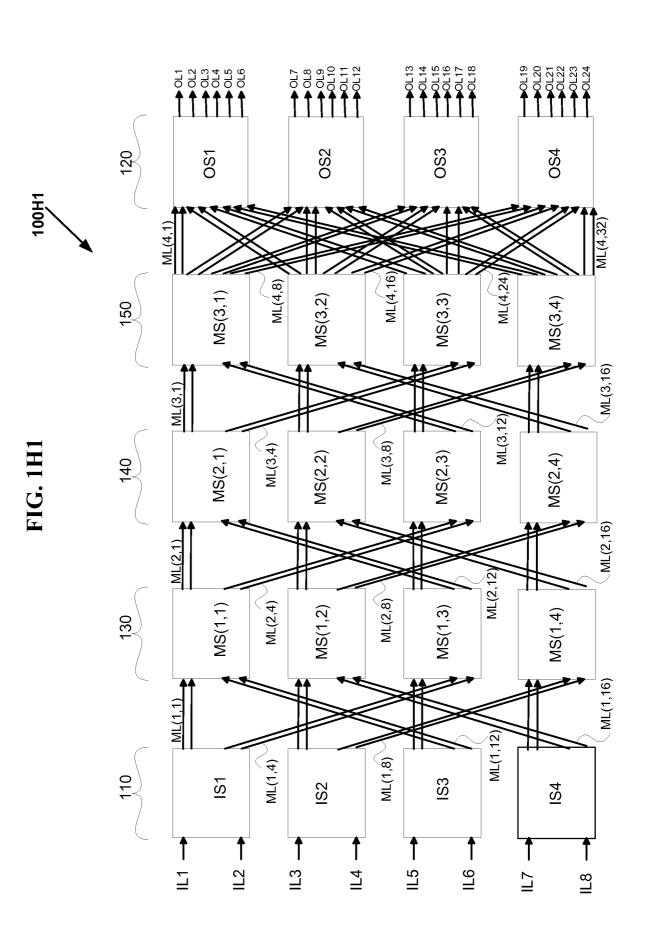

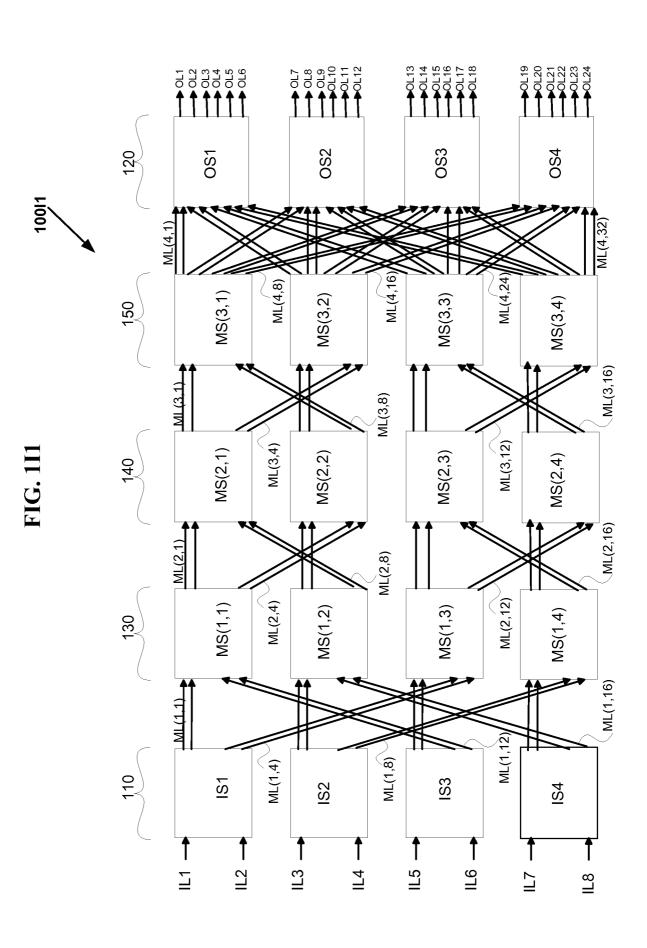

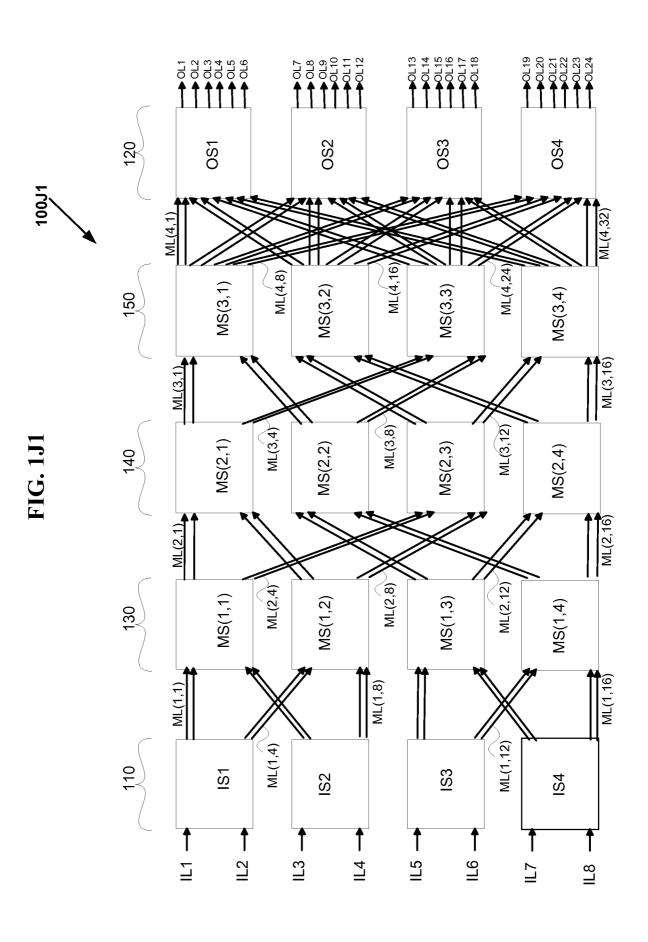

FIG. 1A1 is a diagram 100A1 of an exemplary symmetrical multi-stage network V(N,d,2) having Omega connection topology of five stages with N = 8, d = 2 and s=2 with exemplary multicast connections, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

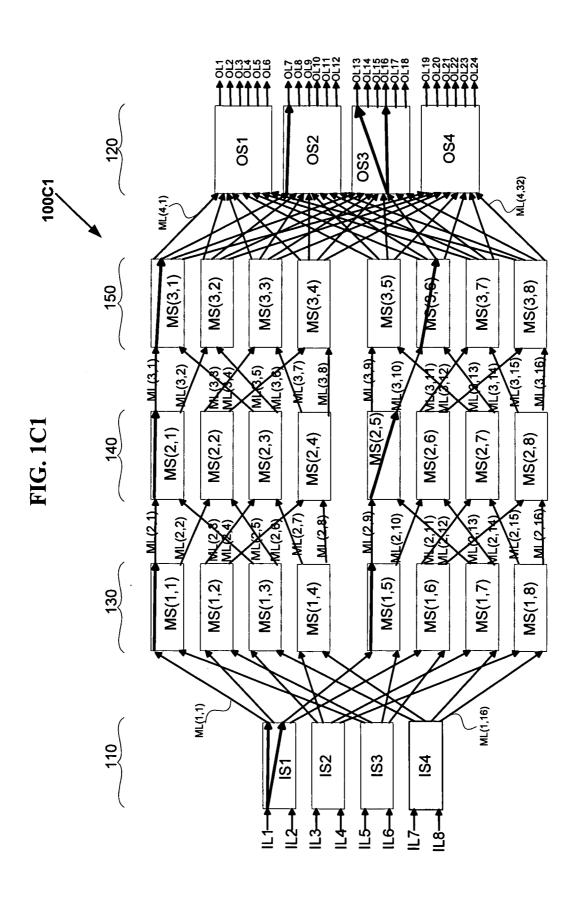

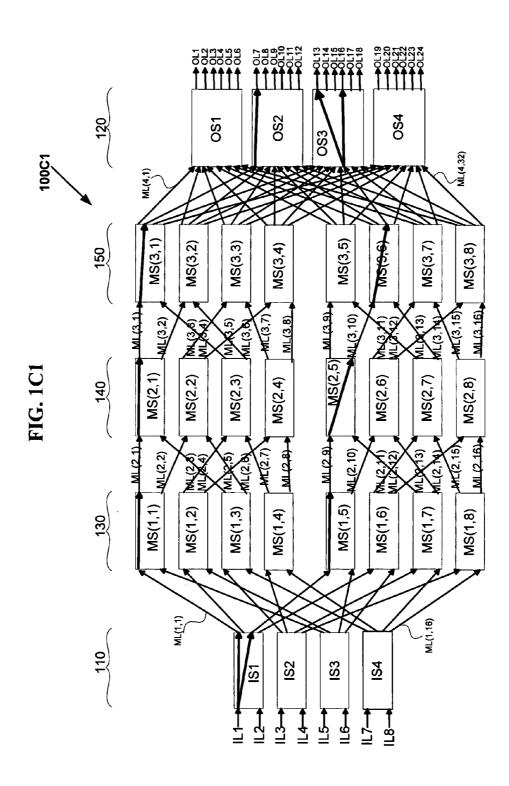

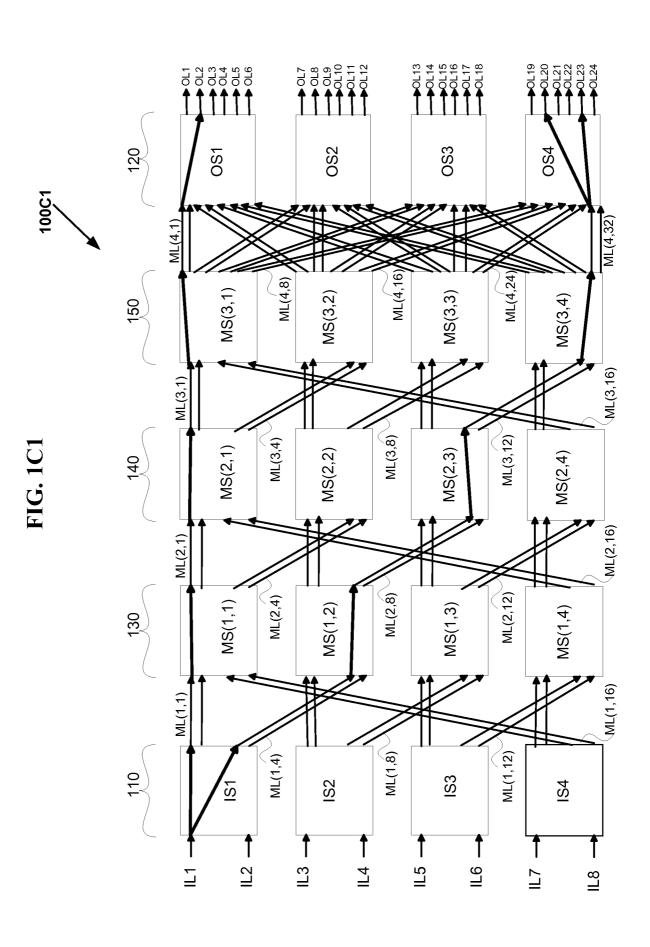

FIG. 1C1 is a diagram 100C1 of an exemplary asymmetrical multi-stage network  $V(N_1, N_2, d, 2)$  having Omega connection topology of five stages with  $N_1 = 8$ ,  $N_2 = p^*$  $N_1 = 24$  where p = 3, and d = 2 with exemplary multicast connections, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

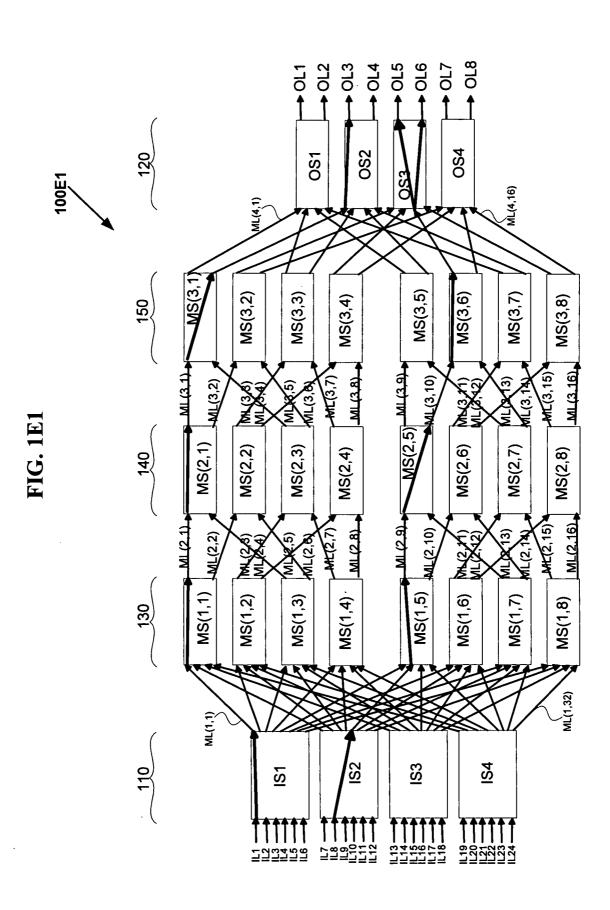

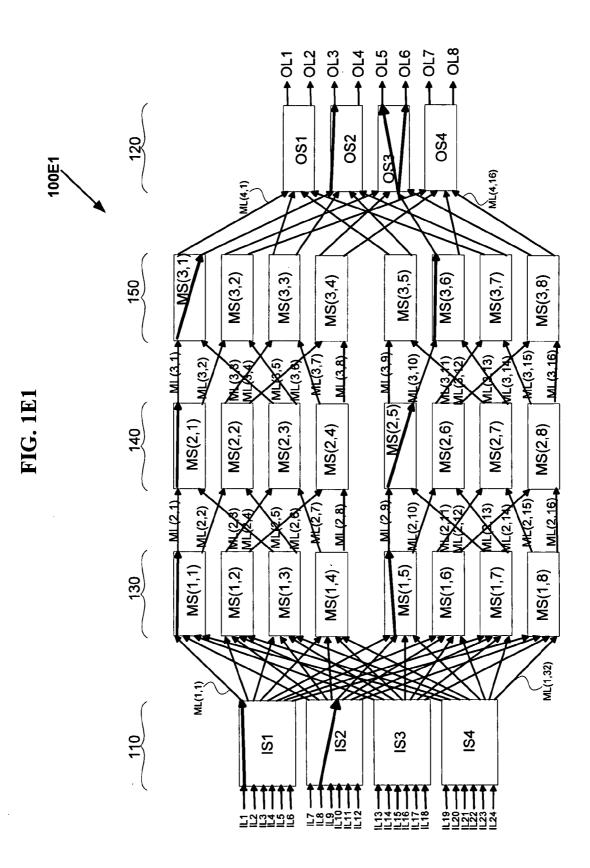

FIG. 1E1 is a diagram 100E1 of an exemplary asymmetrical multi-stage network  $V(N_1, N_2, d, 2)$  having Omega connection topology of five stages with N<sub>2</sub> = 8, N<sub>1</sub> = p\* N<sub>2</sub> = 24, where p = 3, and d = 2 with exemplary multicast connections, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

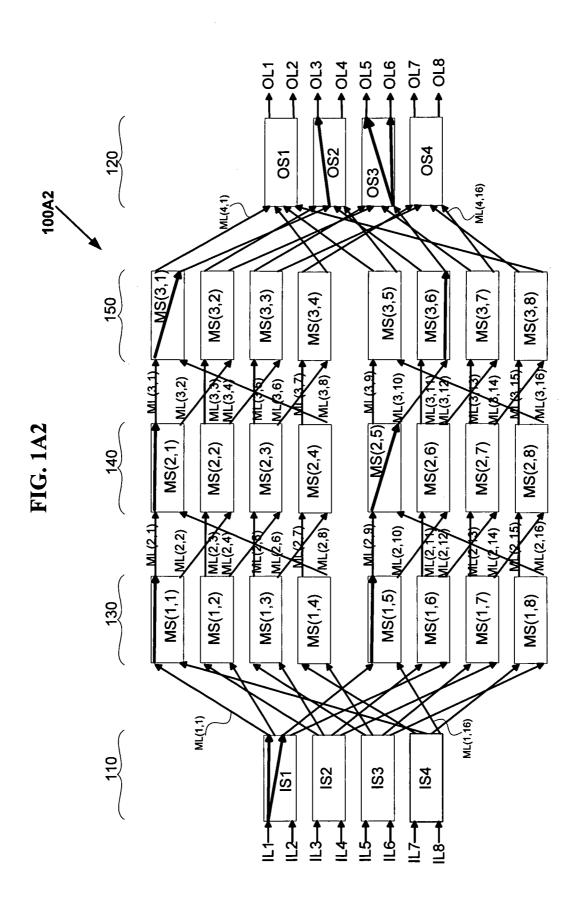

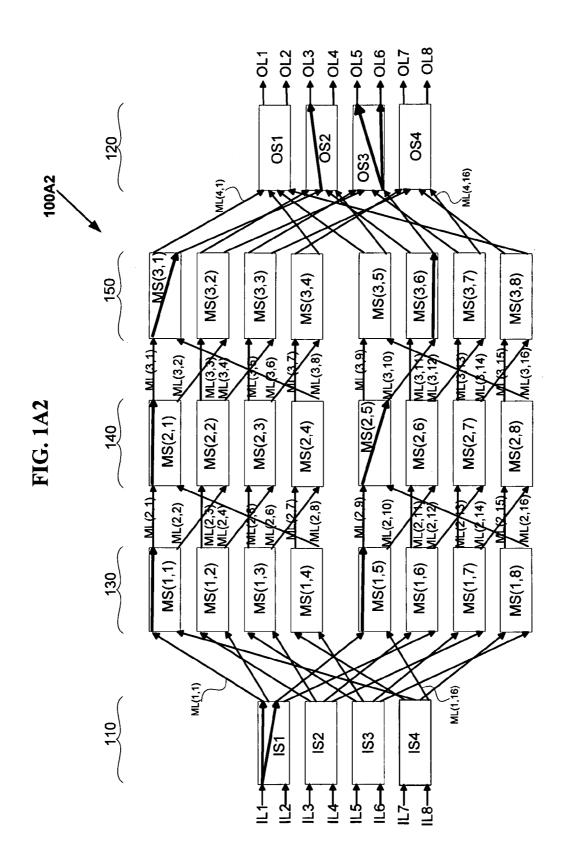

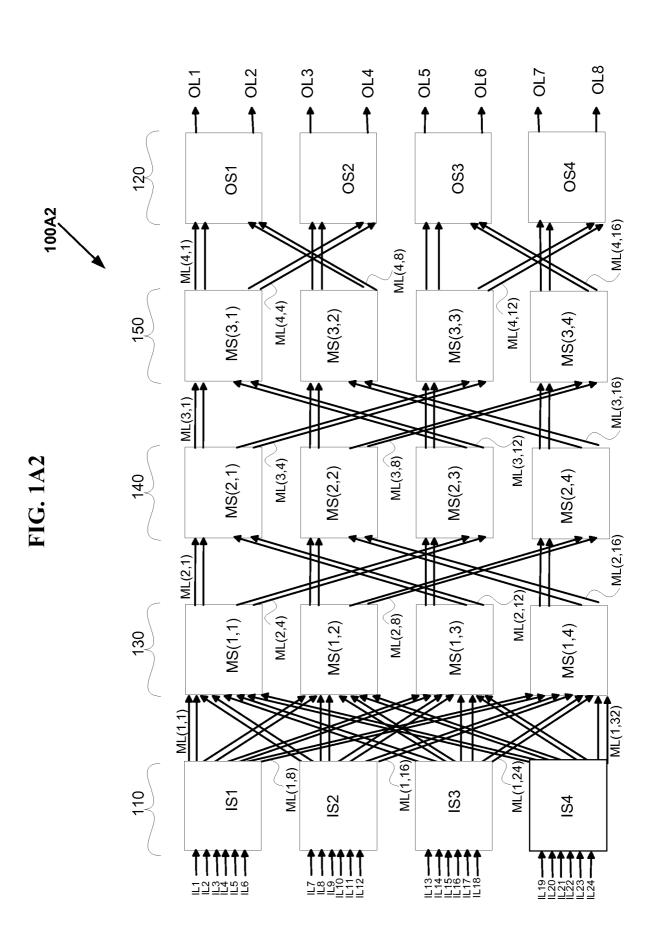

FIG. 1A2 is a diagram 100A2 of an exemplary symmetrical multi-stage network V(N,d,2) having nearest neighbor connection topology of five stages with N = 8, d = 2 and s=2 with exemplary multicast connections, strictly nonblocking network for unicast

10

5

#### WO 2008/109756

#### 8

#### PCT/US2008/056064

connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

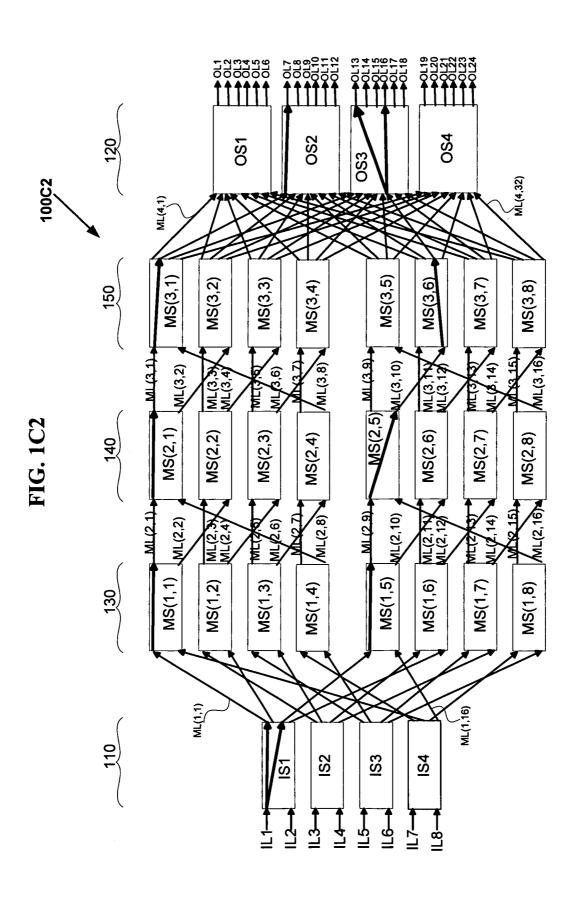

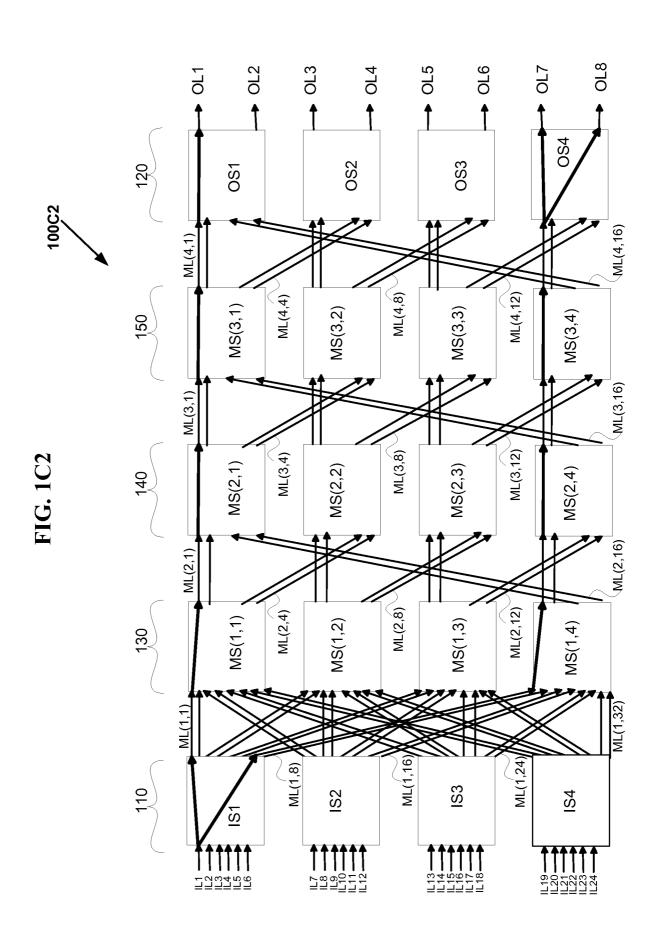

FIG. 1C2 is a diagram 100C2 of an exemplary asymmetrical multi-stage network V(N<sub>1</sub>, N<sub>2</sub>, d, 2) having nearest neighbor connection topology of five stages with N<sub>1</sub> = 8,

N<sub>2</sub> = p\* N<sub>1</sub> = 24 where p = 3, and d = 2 with exemplary multicast connections, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

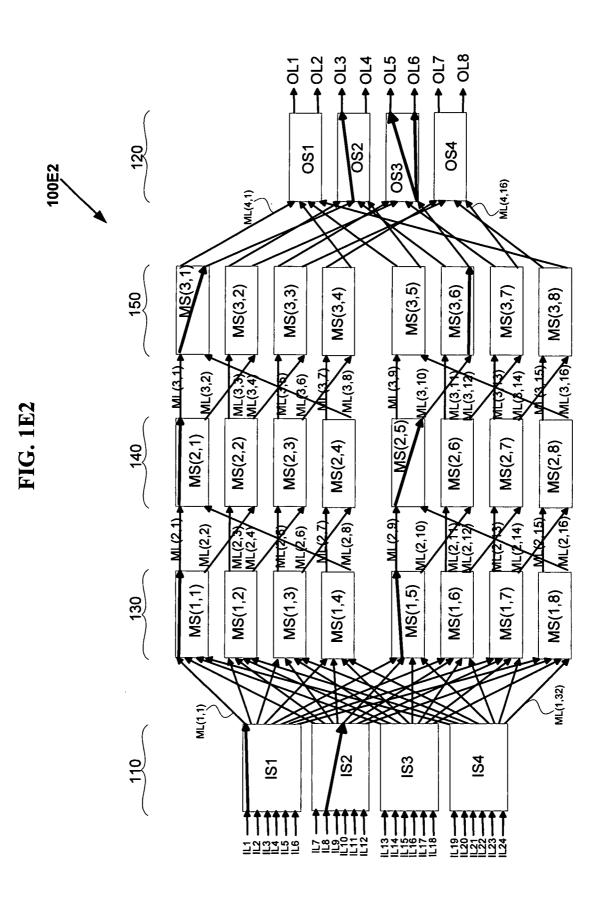

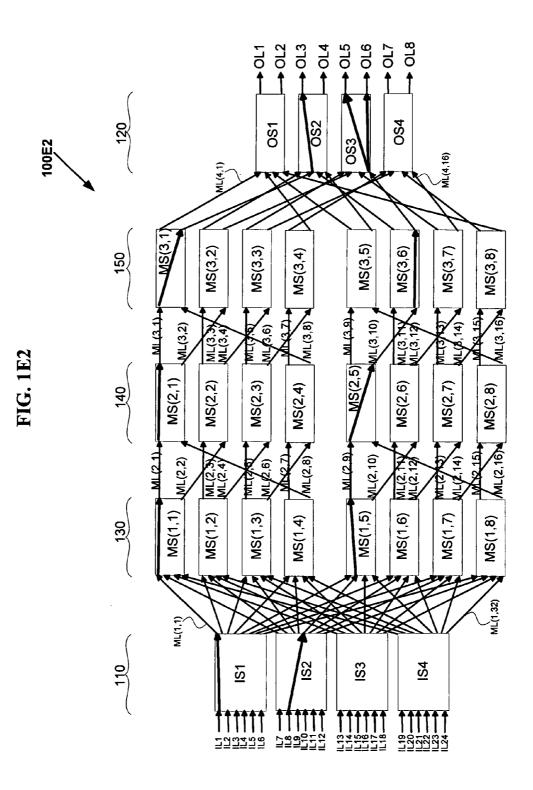

FIG. 1E2 is a diagram 100E2 of an exemplary asymmetrical multi-stage network V(N<sub>1</sub>, N<sub>2</sub>, d, 2) having nearest neighbor connection topology of five stages with N<sub>2</sub> = 8,

N<sub>1</sub> = p\* N<sub>2</sub> = 24, where p = 3, and d = 2 with exemplary multicast connections, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

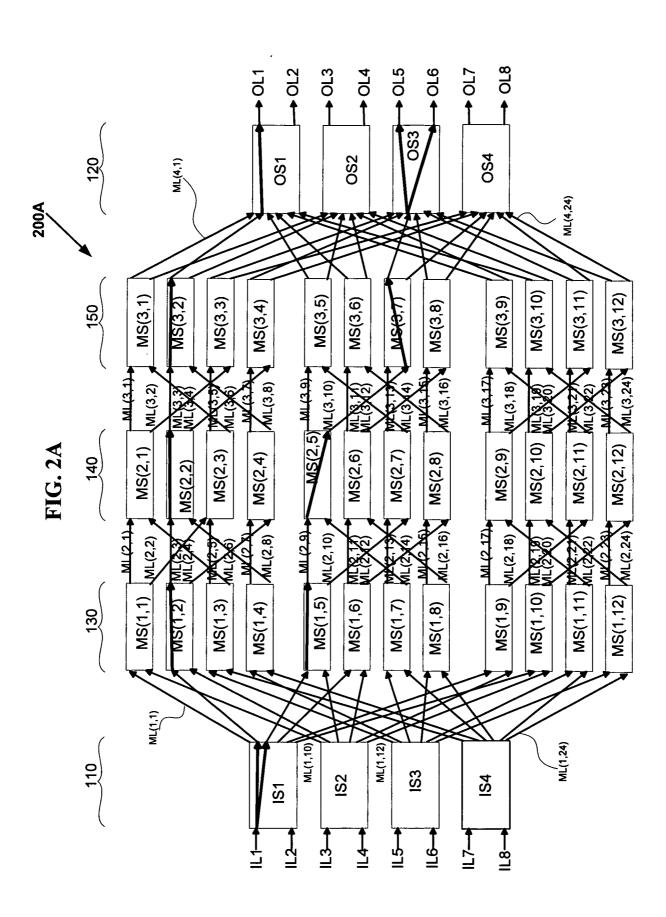

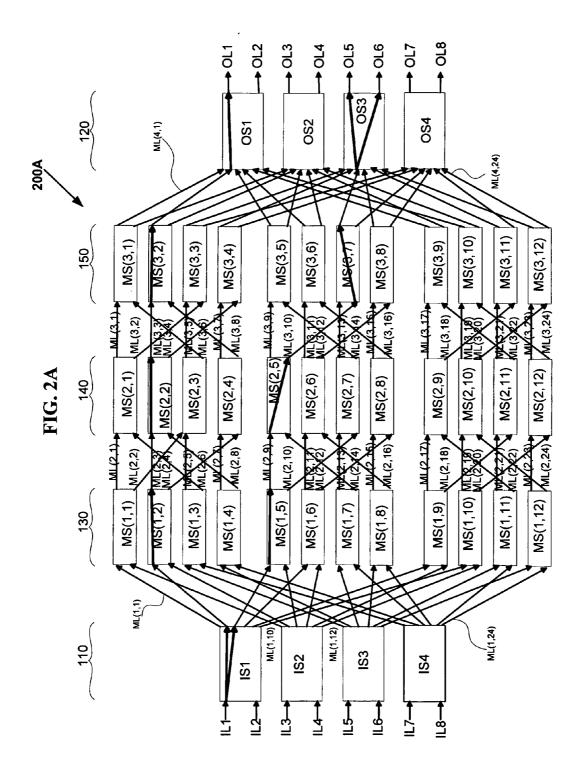

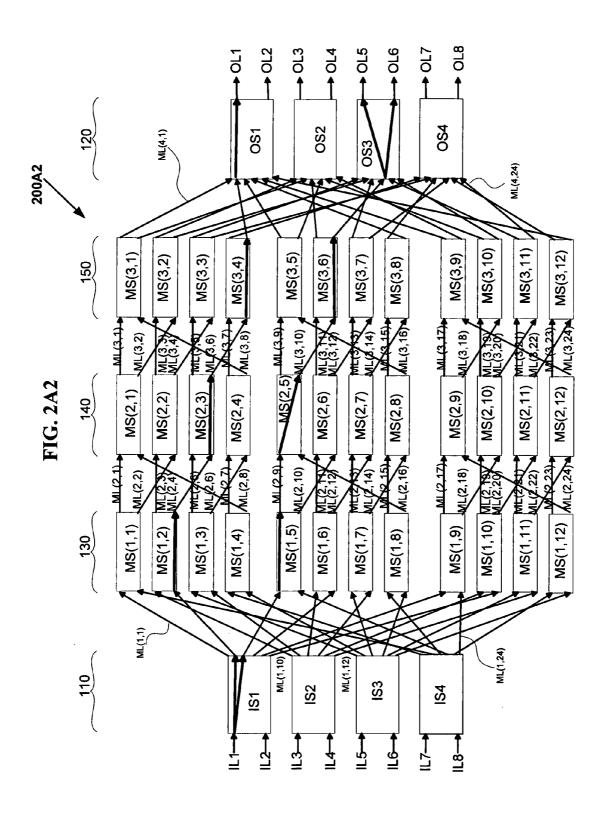

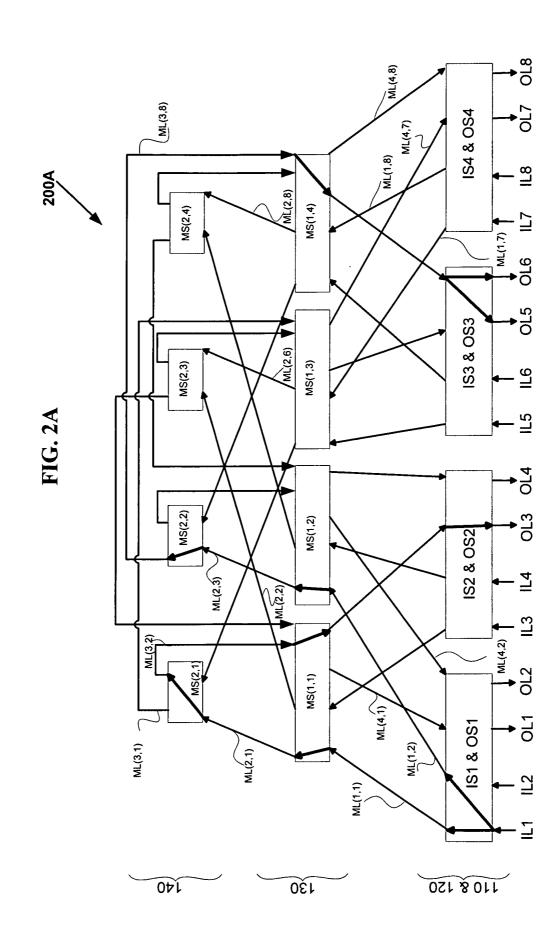

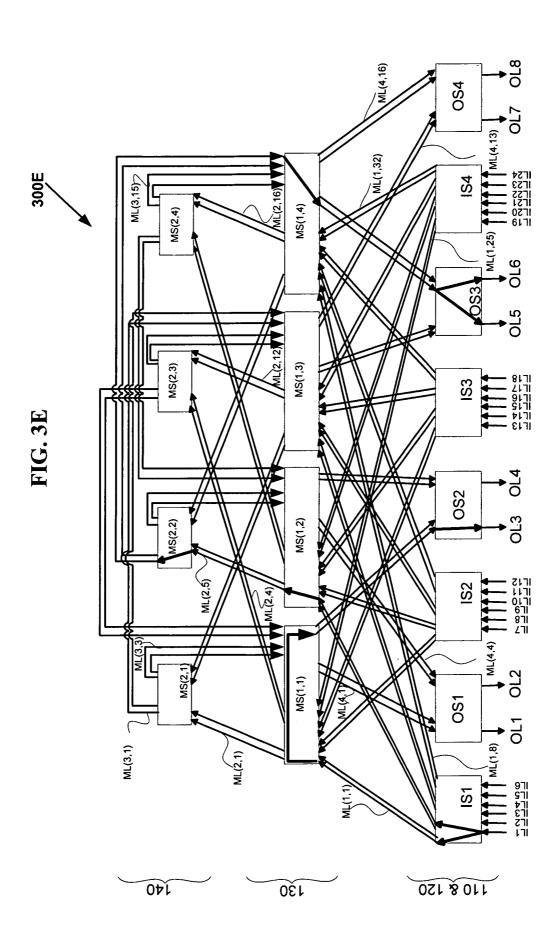

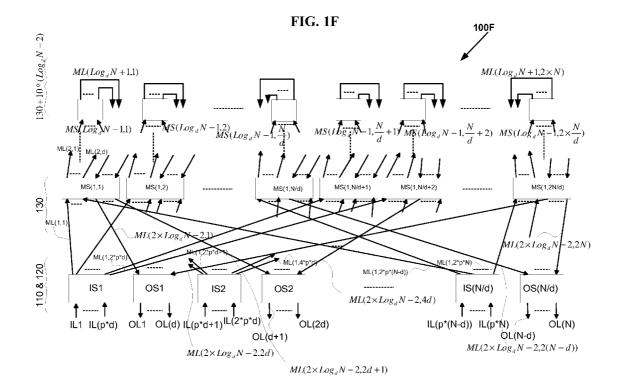

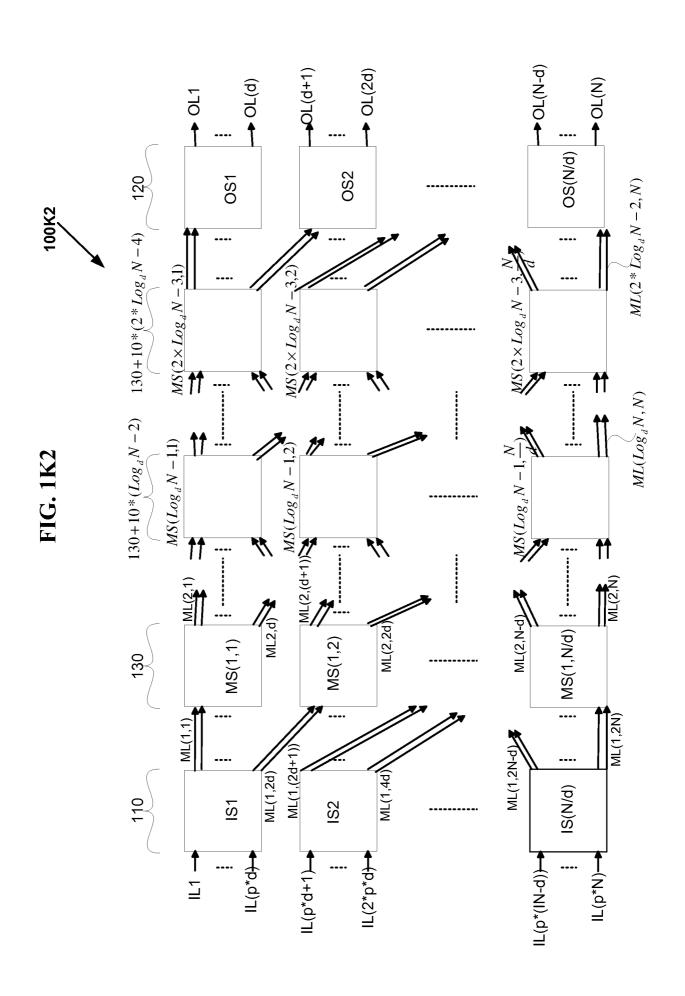

FIG. 2A is a diagram 200A of an exemplary symmetrical multi-stage network V(N, d,3) having inverse Benes connection topology of five stages with N = 8, d = 2 and

s=3 with exemplary multicast connections strictly nonblocking network for arbitrary fanout multicast connections, in accordance with the invention.

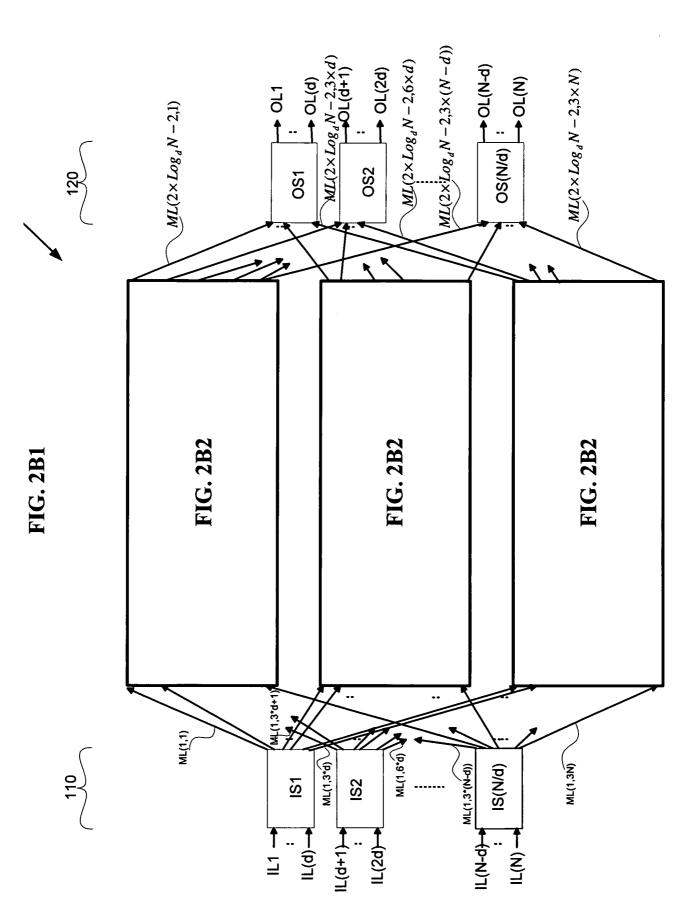

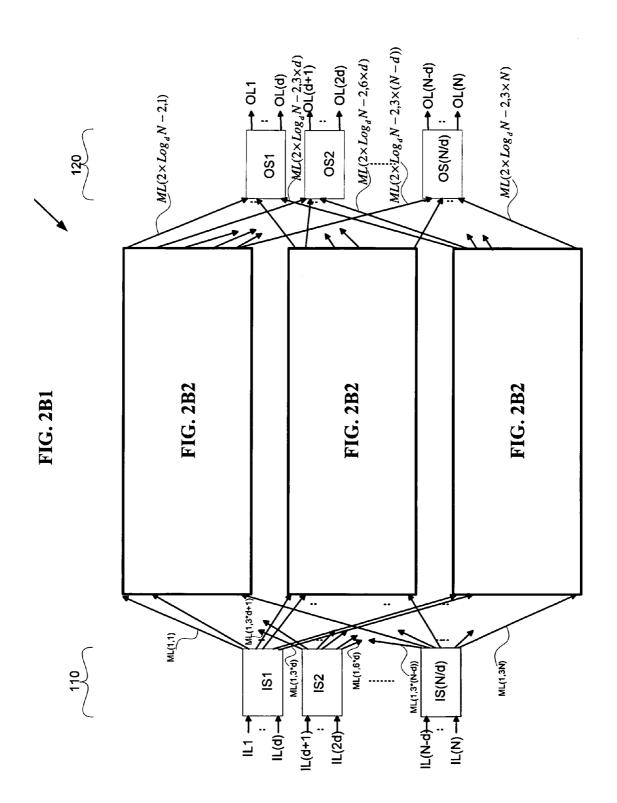

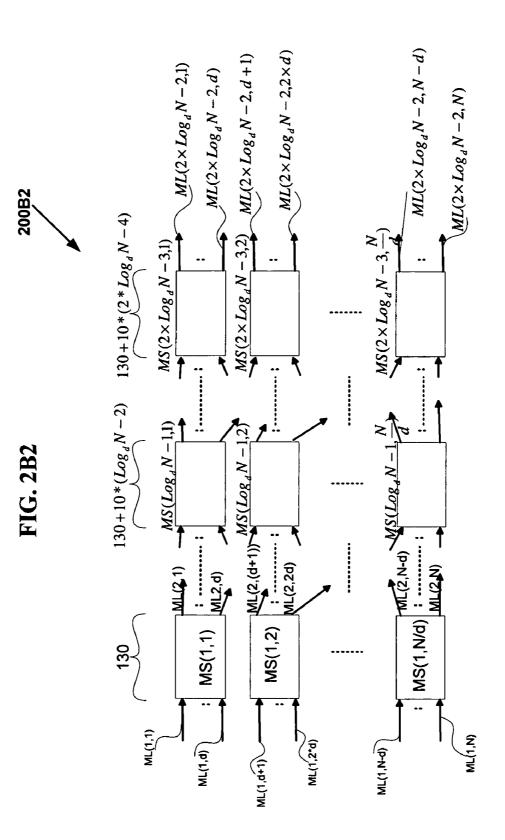

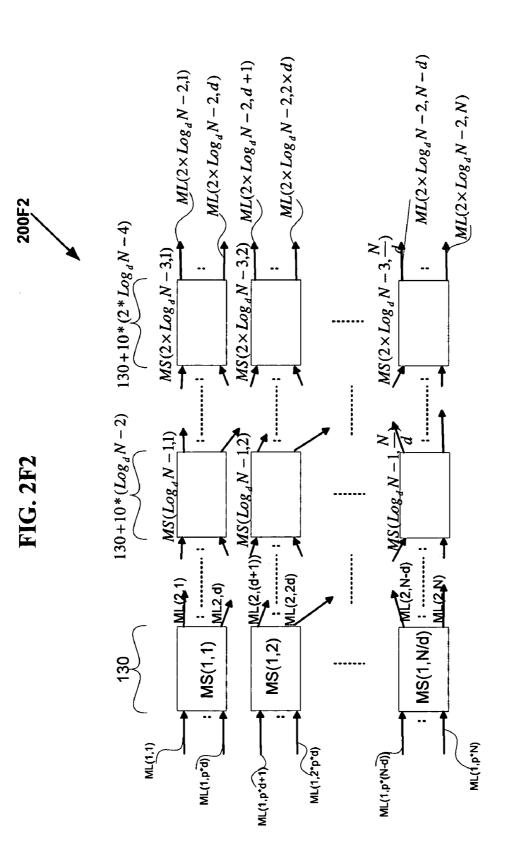

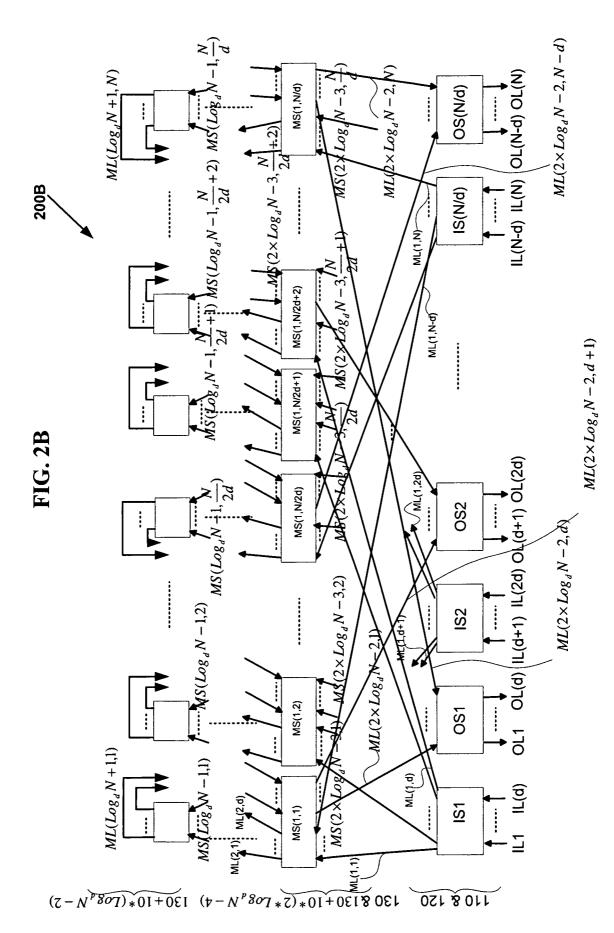

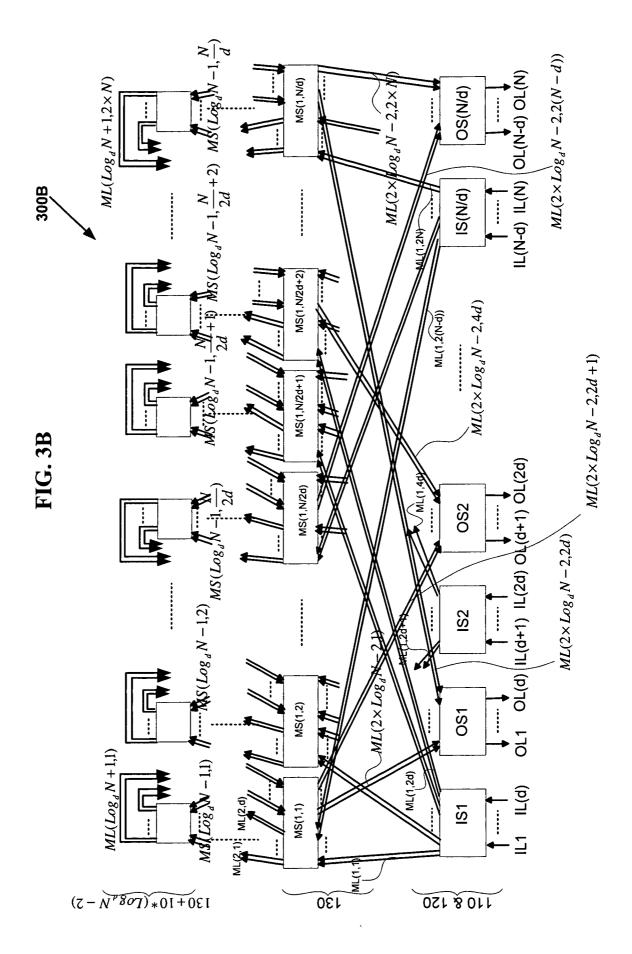

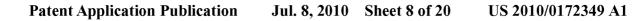

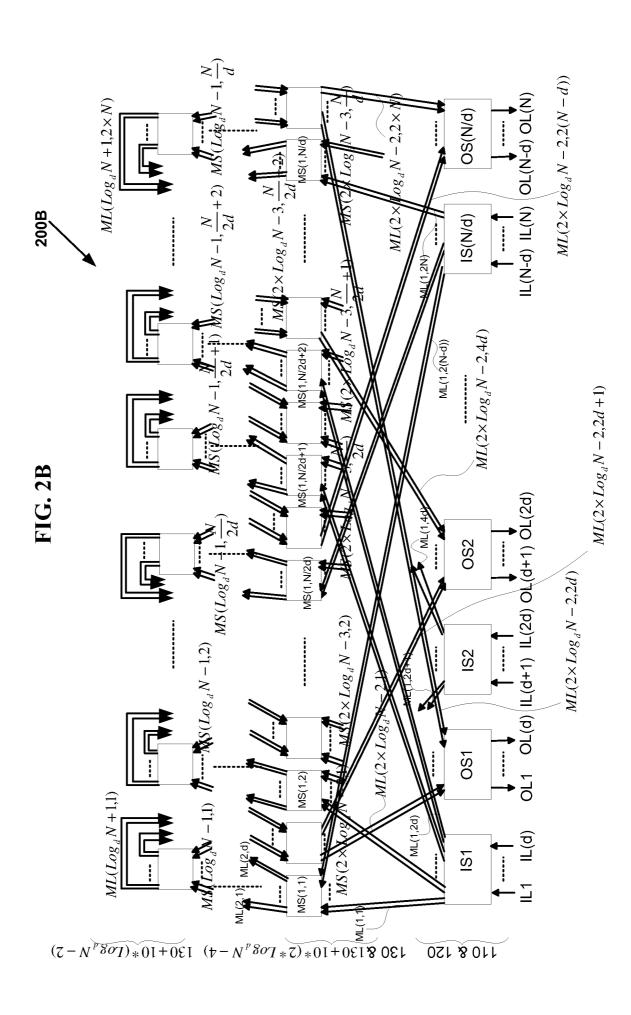

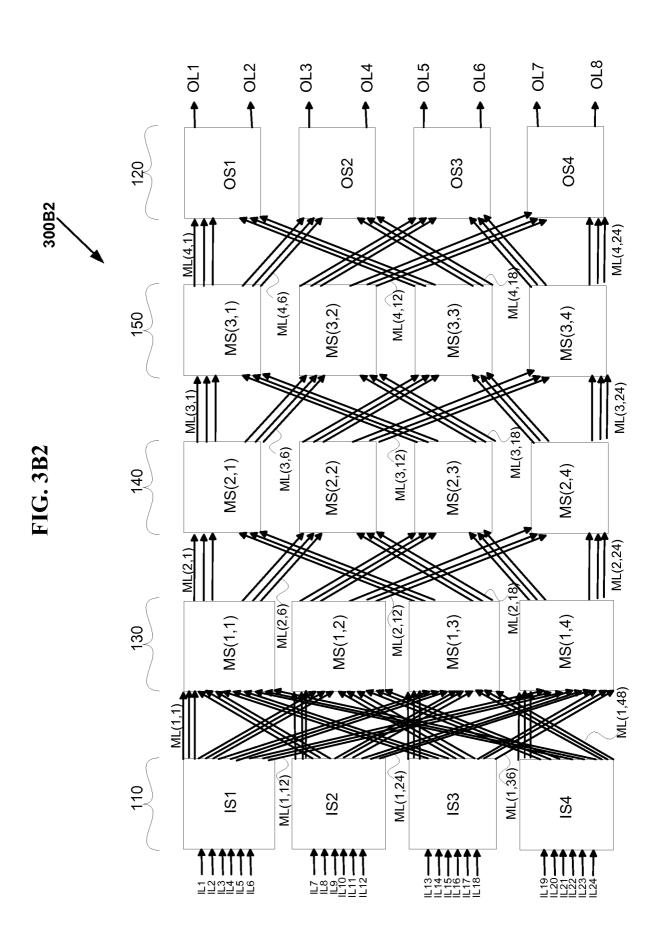

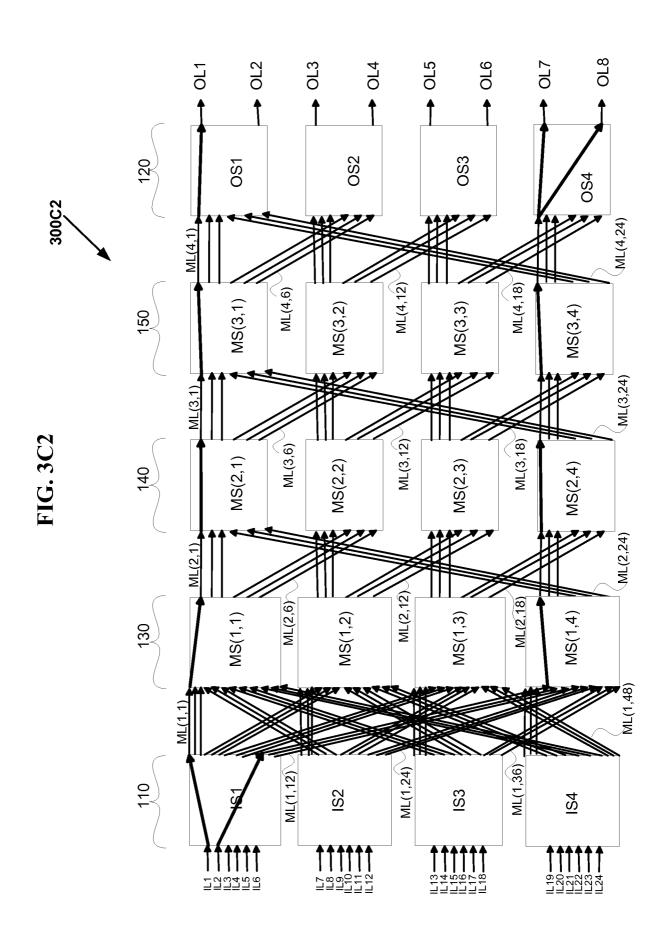

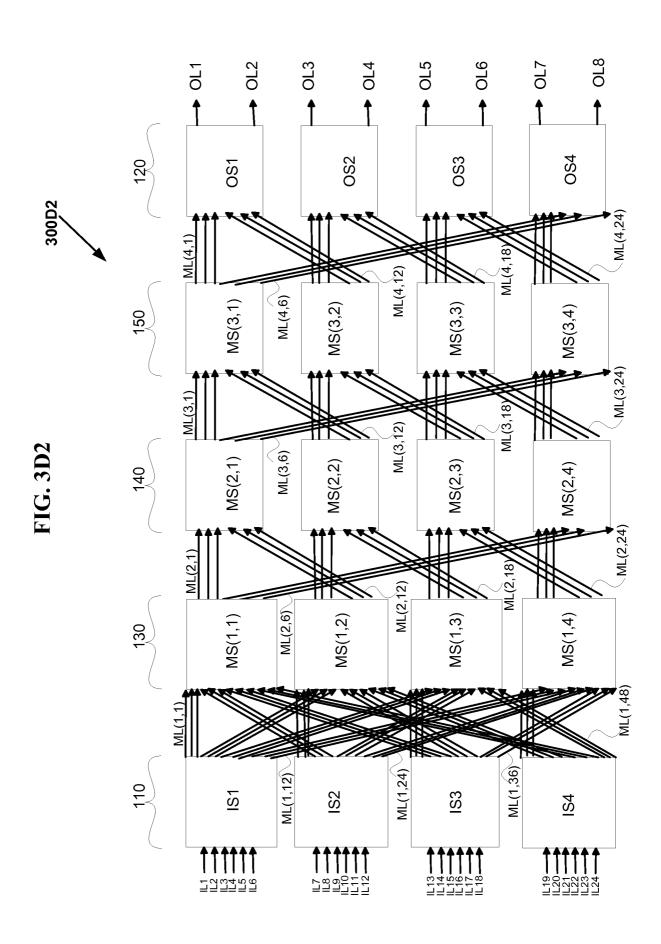

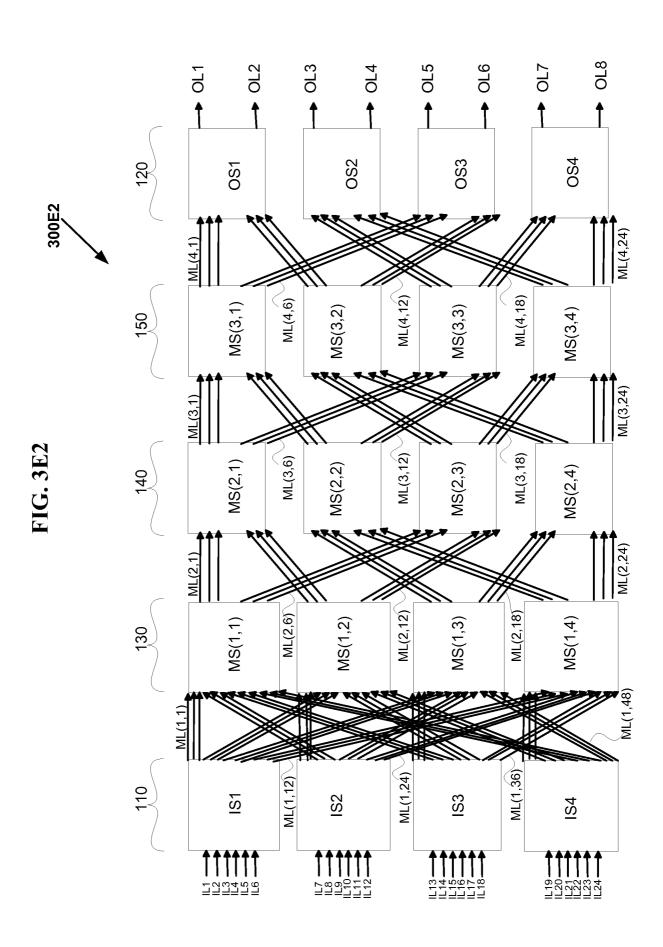

FIG. 2B1 & FIG. 2B2 is a diagram 200B of a general symmetrical multi-stage network V(N, d, 3) with  $(2 \times \log_d N) - 1$  stages strictly nonblocking network for arbitrary fan-out multicast connections in accordance with the invention.

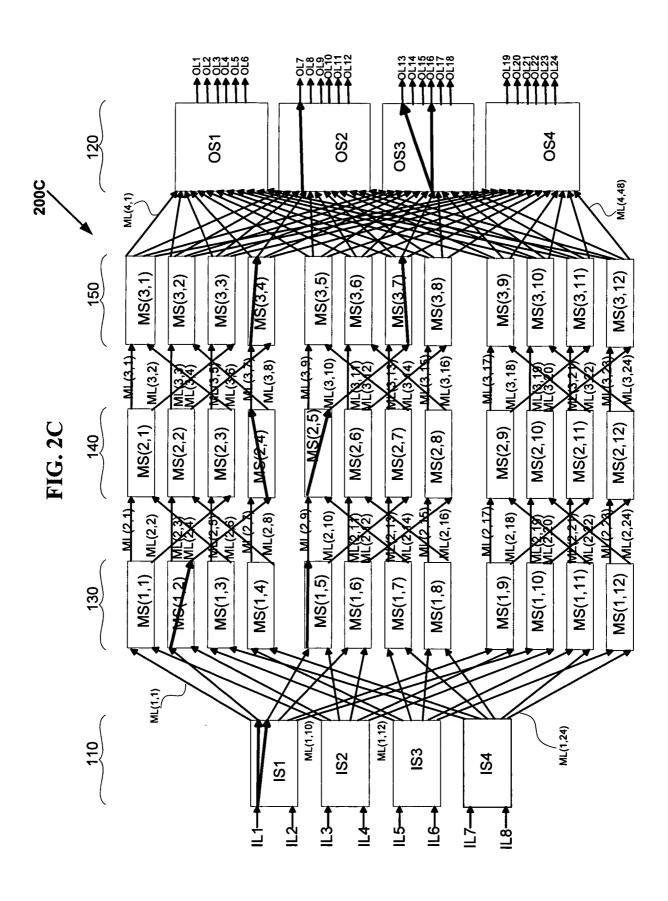

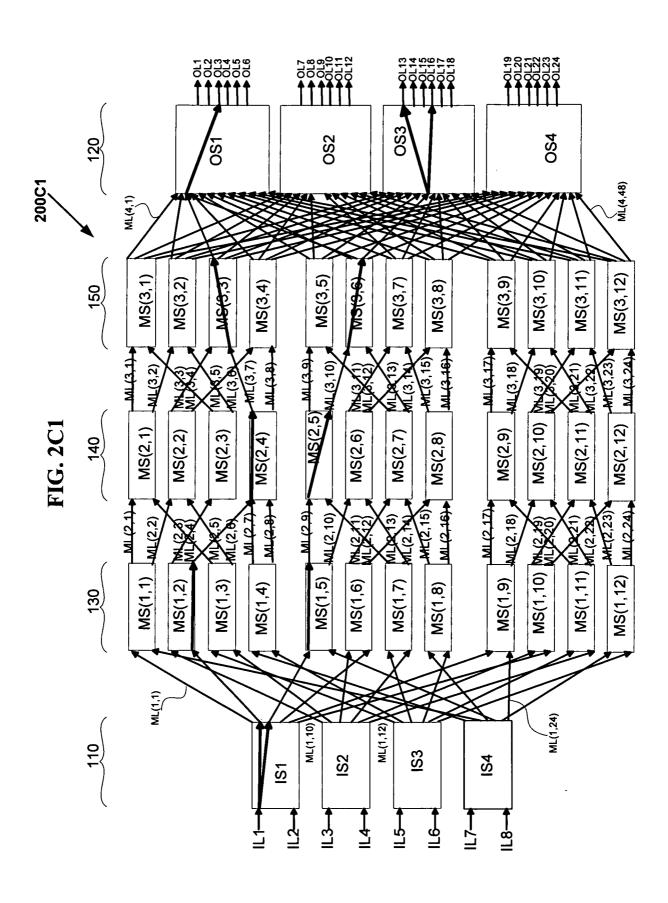

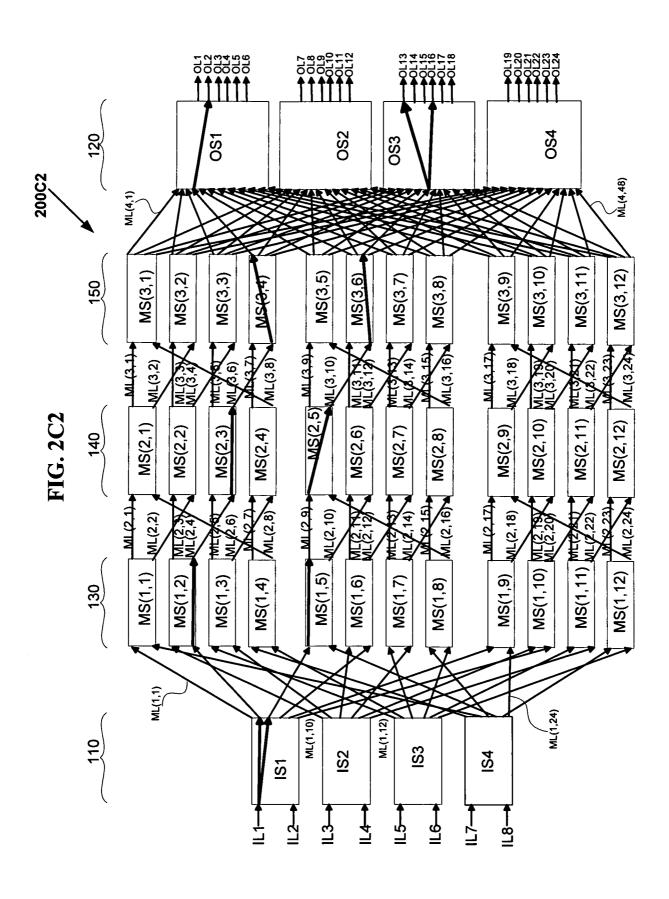

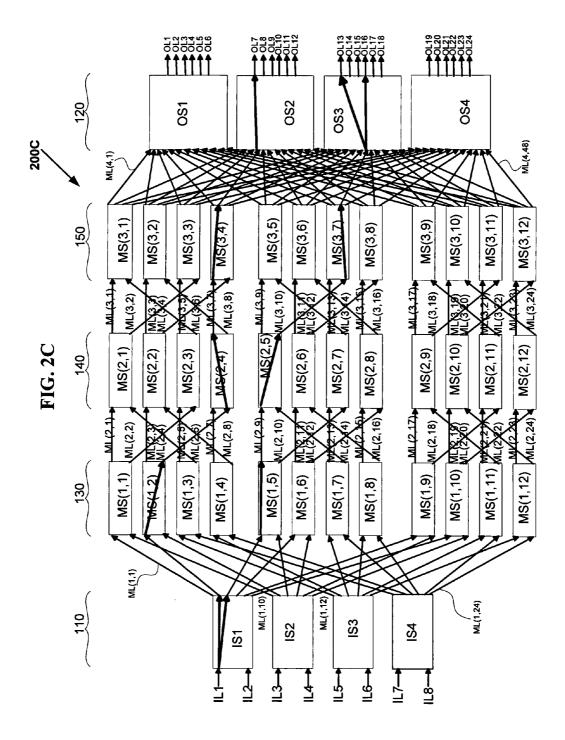

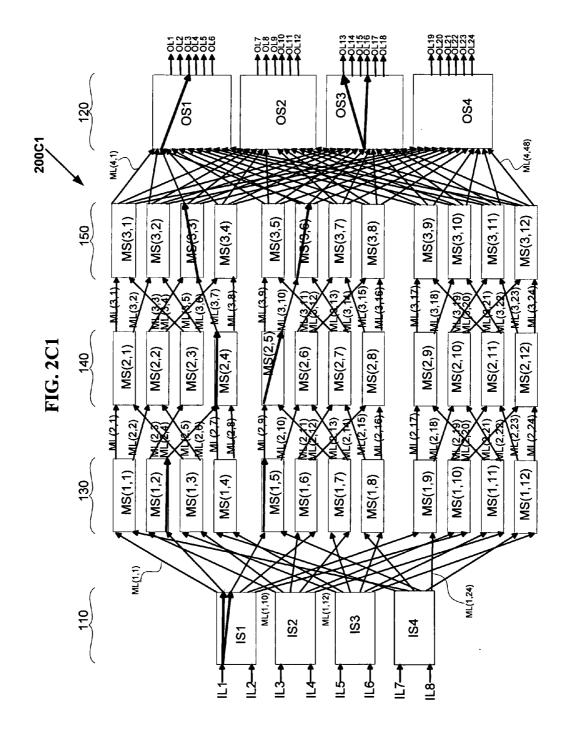

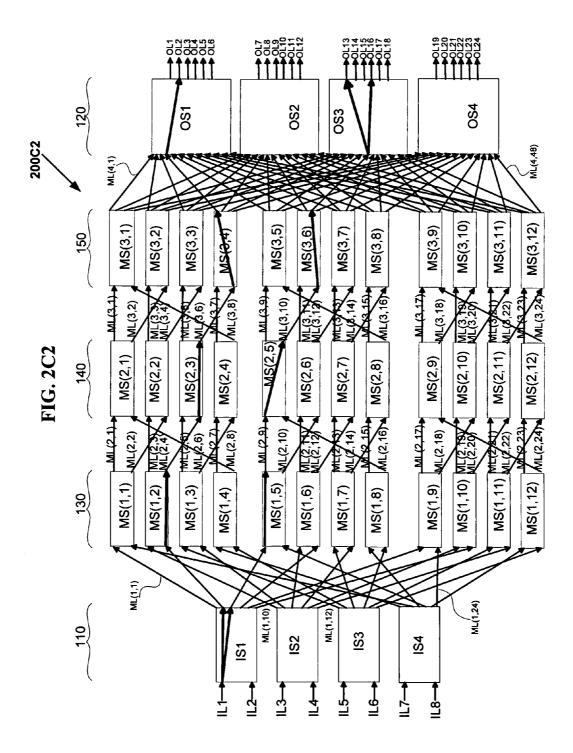

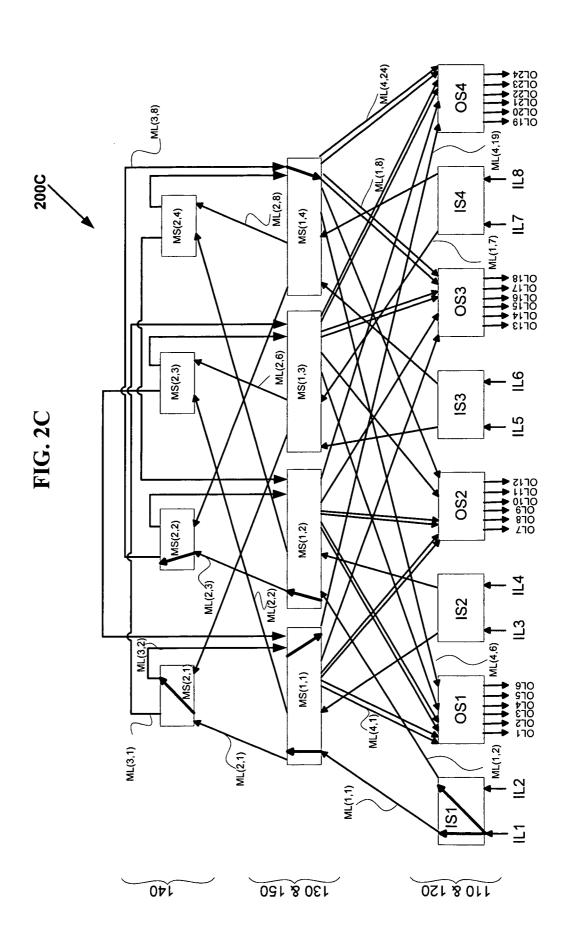

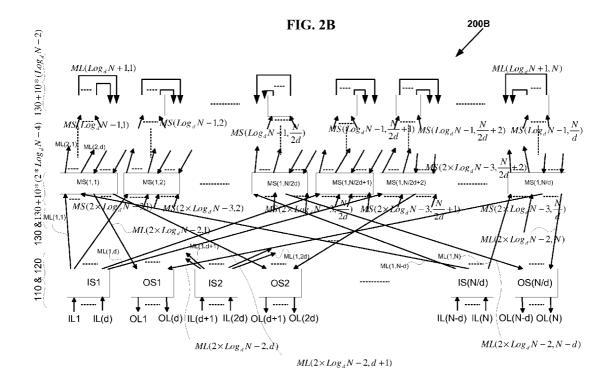

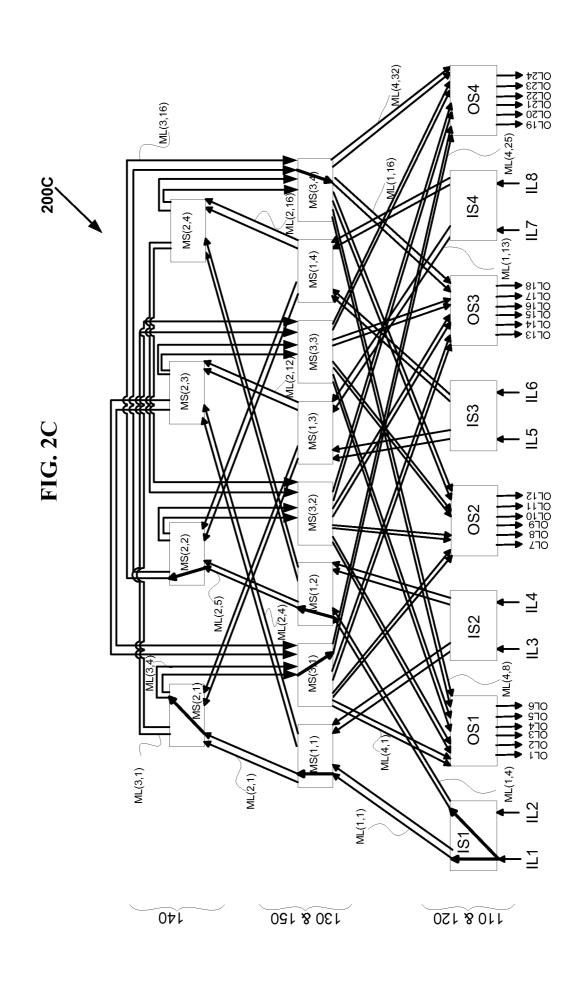

FIG. 2C is a diagram 200C of an exemplary asymmetrical multi-stage network  $V(N_1, N_2, d, 3)$  having inverse Benes connection topology of five stages with N<sub>1</sub> = 8, N2 = p\* N<sub>1</sub> = 24 where p = 3, and d = 2 with exemplary multicast connections strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

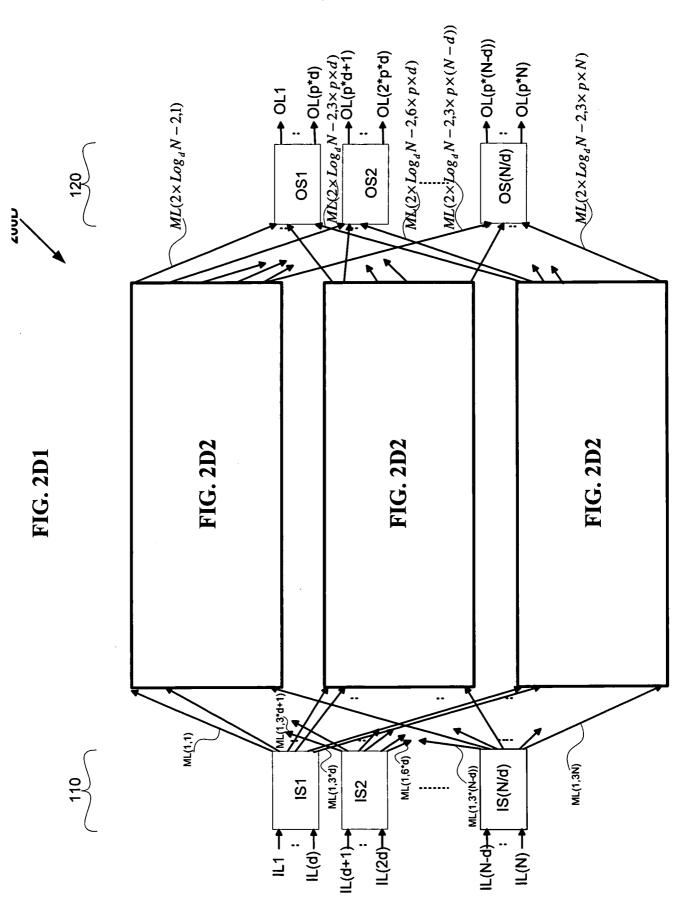

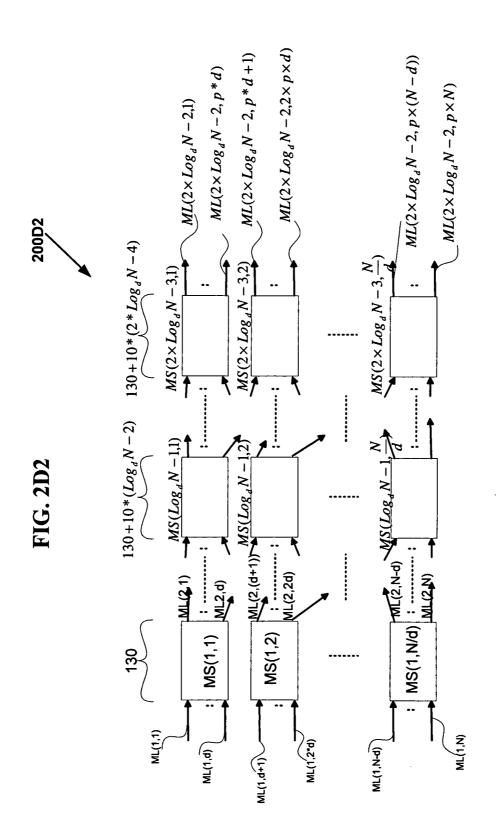

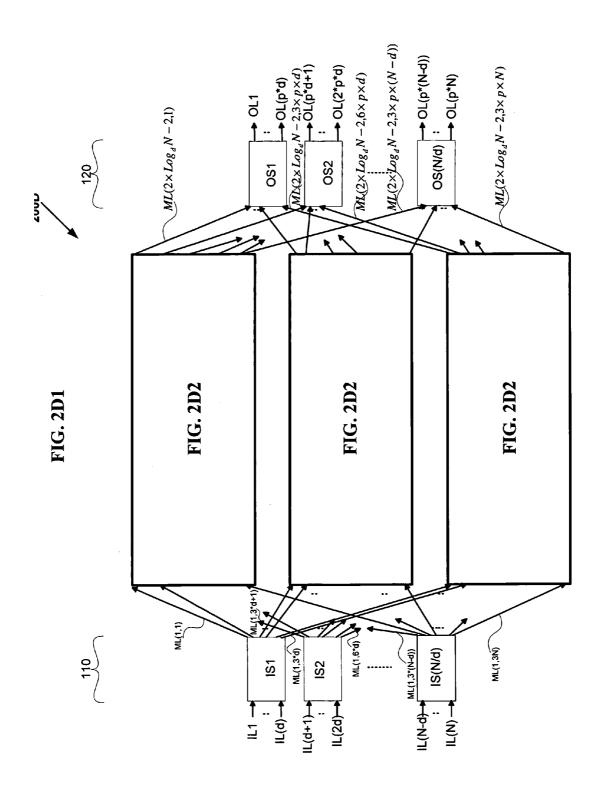

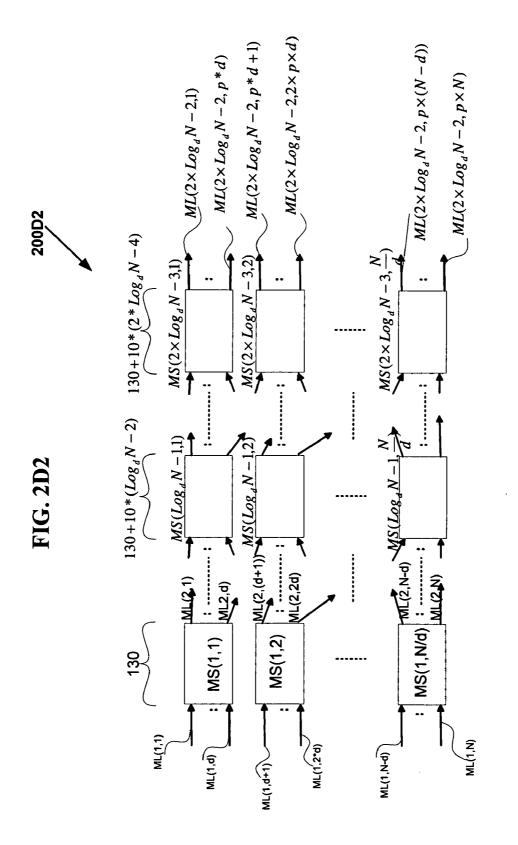

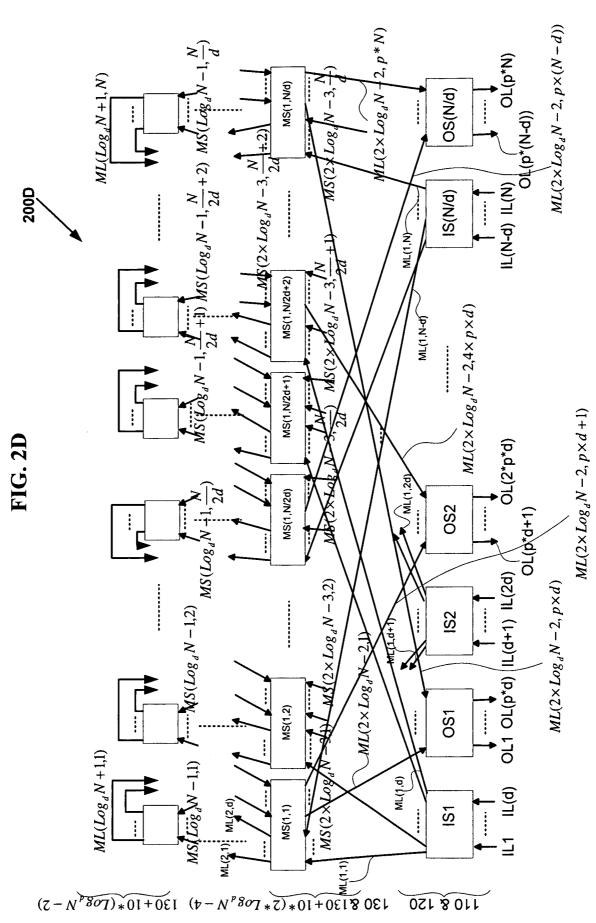

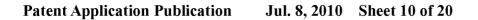

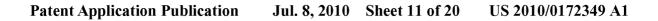

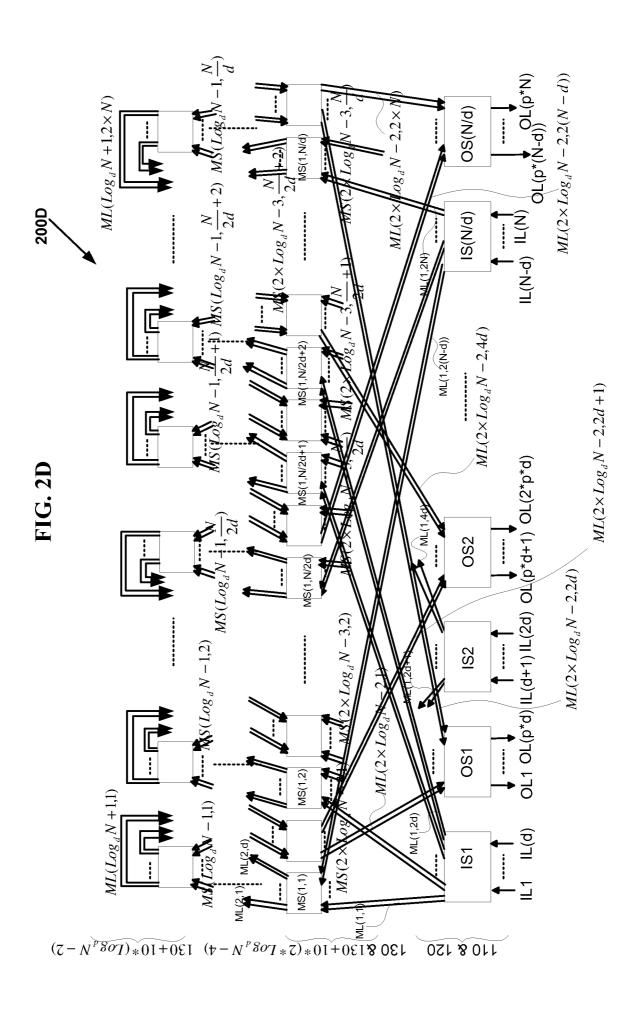

FIG. 2D1 & FIG. 2D2 is a diagram 200D of a general asymmetrical multi-stage network  $V(N_1, N_2, d, 3)$  with  $N_2 = p^* N_1$  and with  $(2 \times \log_d N) - 1$  stages strictly

15

20

25

#### 9

#### PCT/US2008/056064

nonblocking network for arbitrary fan-out multicast connections in accordance with the invention.

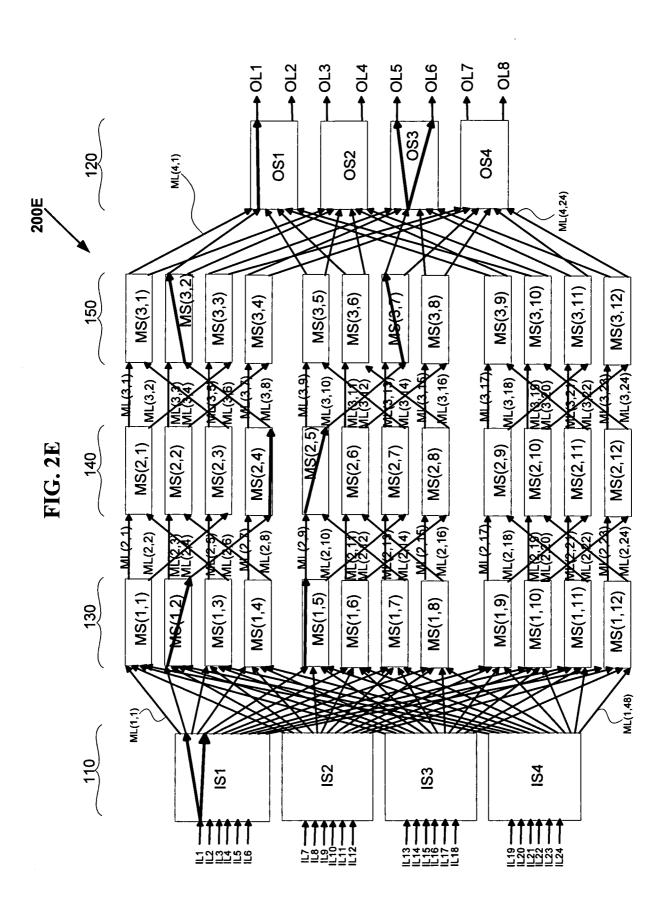

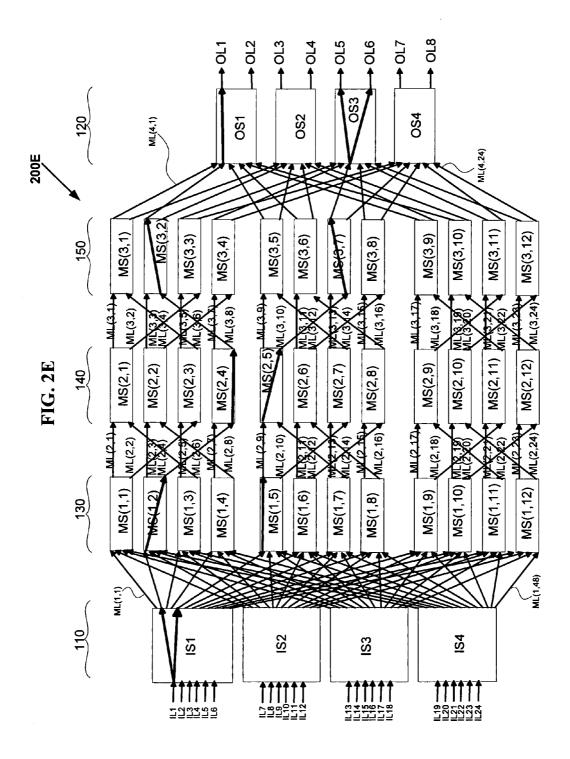

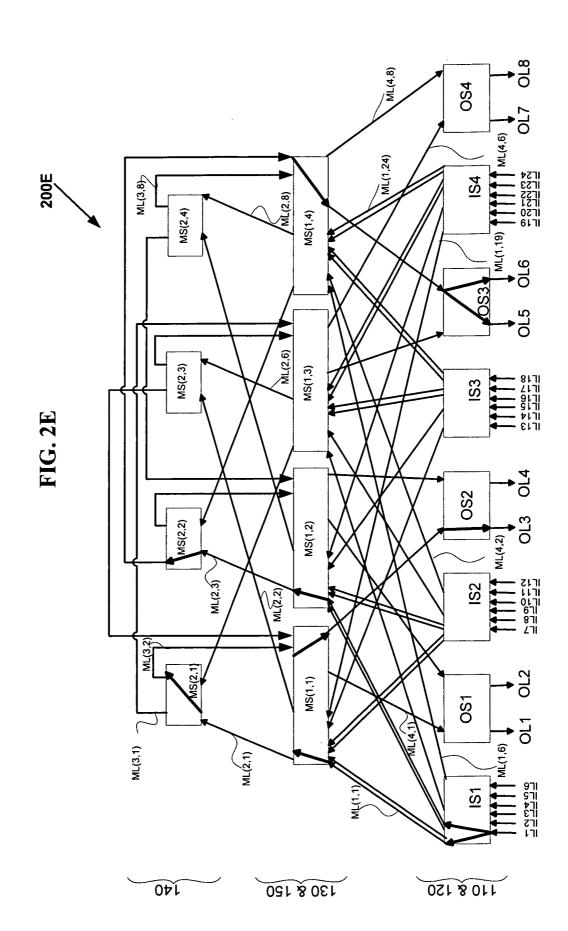

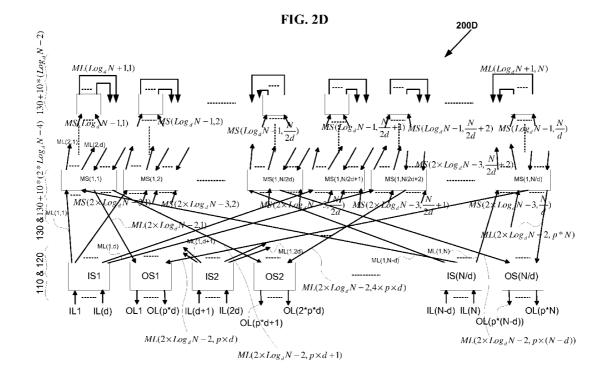

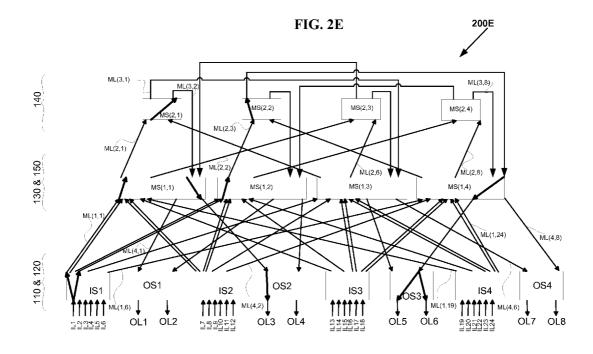

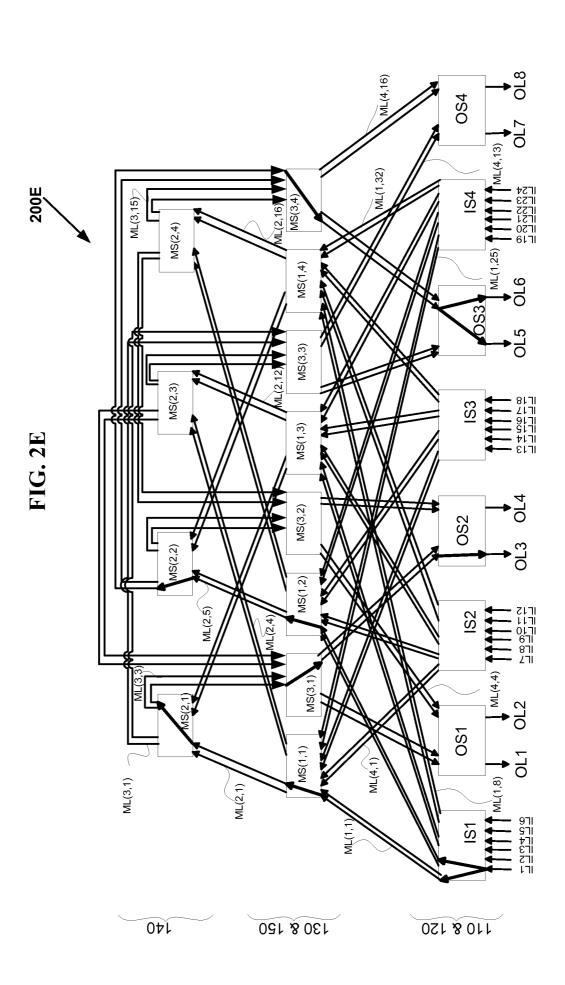

FIG. 2E is a diagram 200E of an exemplary asymmetrical multi-stage network  $V(N_1, N_2, d, 3)$  having inverse Benes connection topology of five stages with N<sub>2</sub> = 8, N<sub>1</sub> 5 = p\* N<sub>2</sub> = 24, where p = 3, and d = 2 with exemplary multicast connections strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

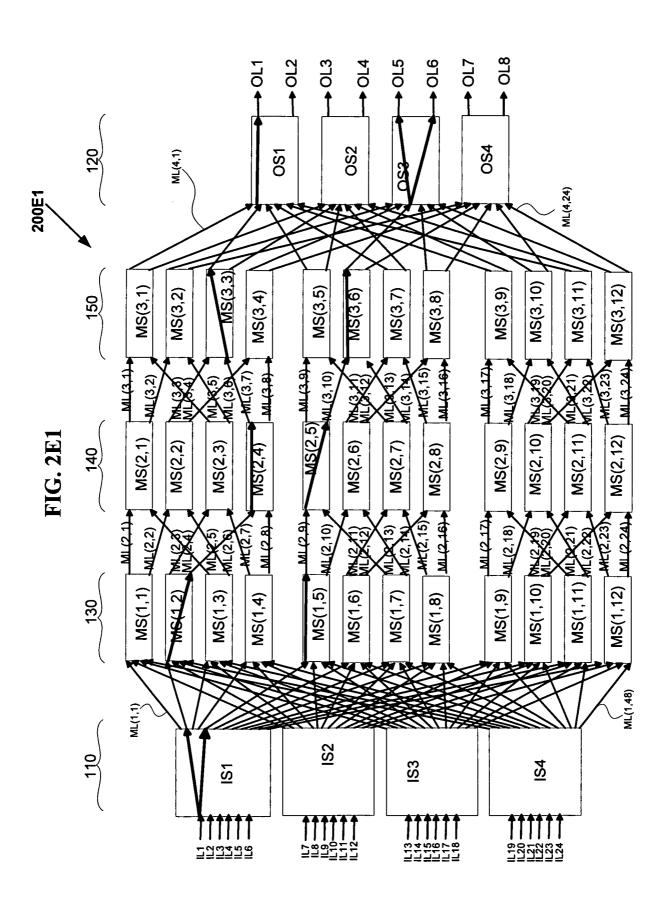

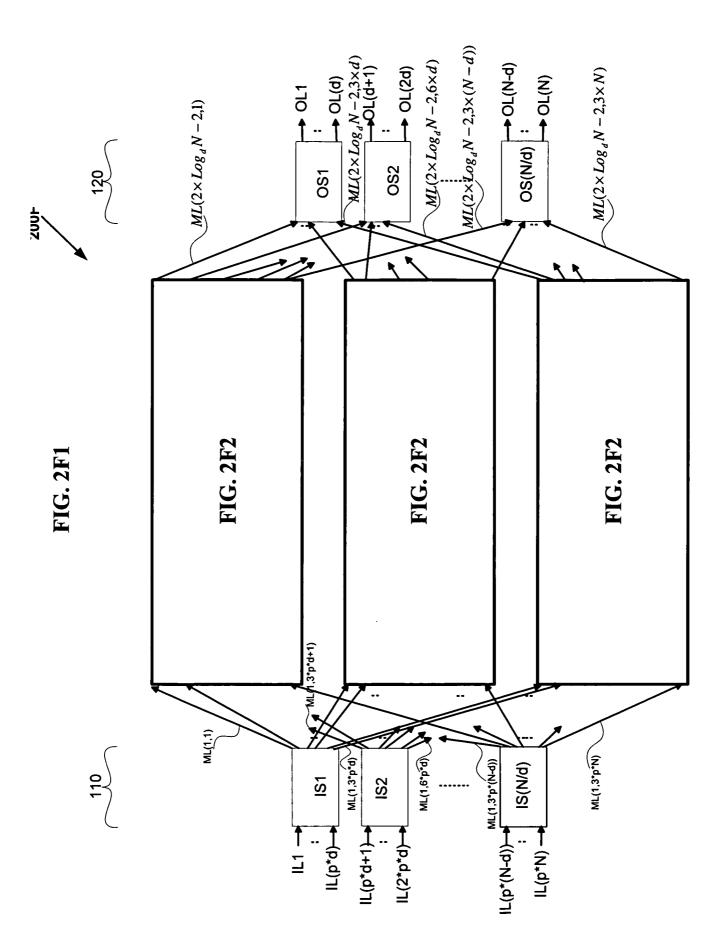

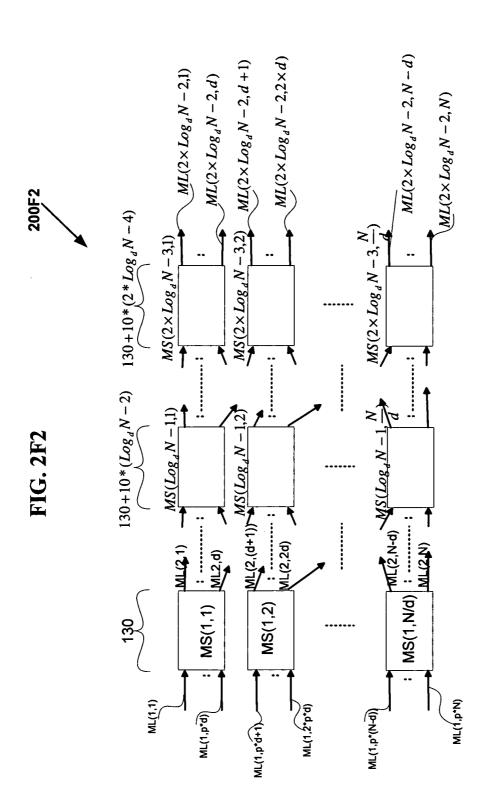

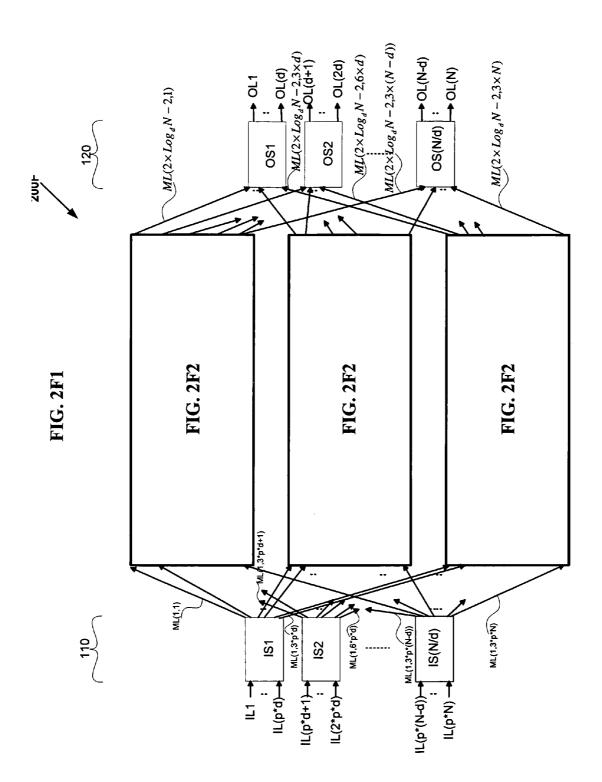

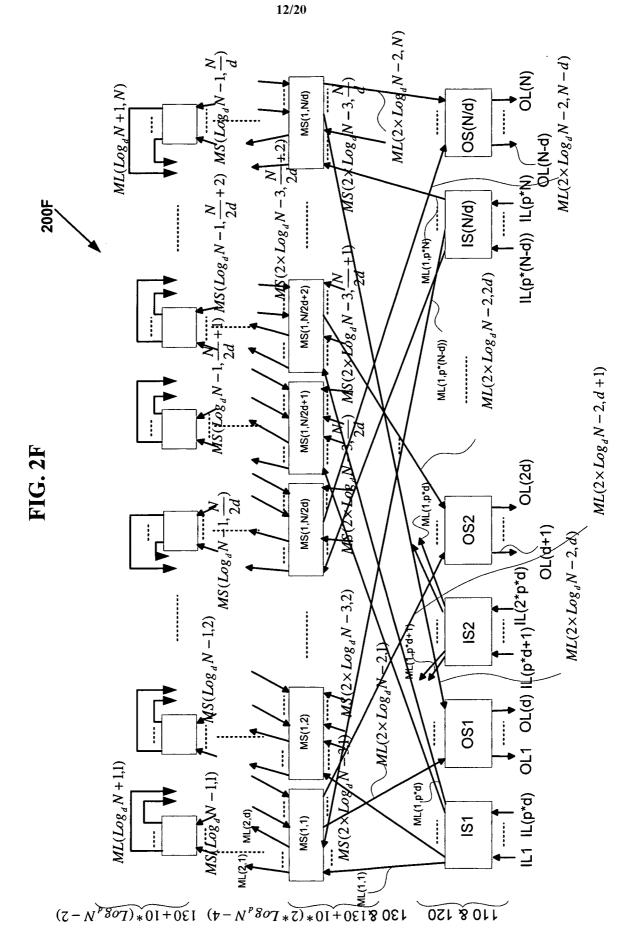

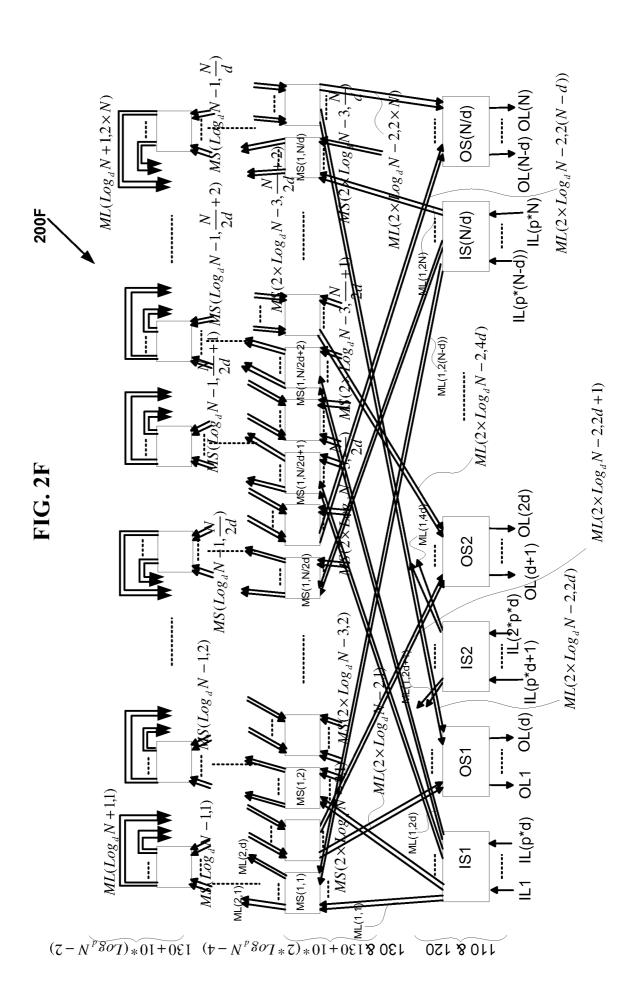

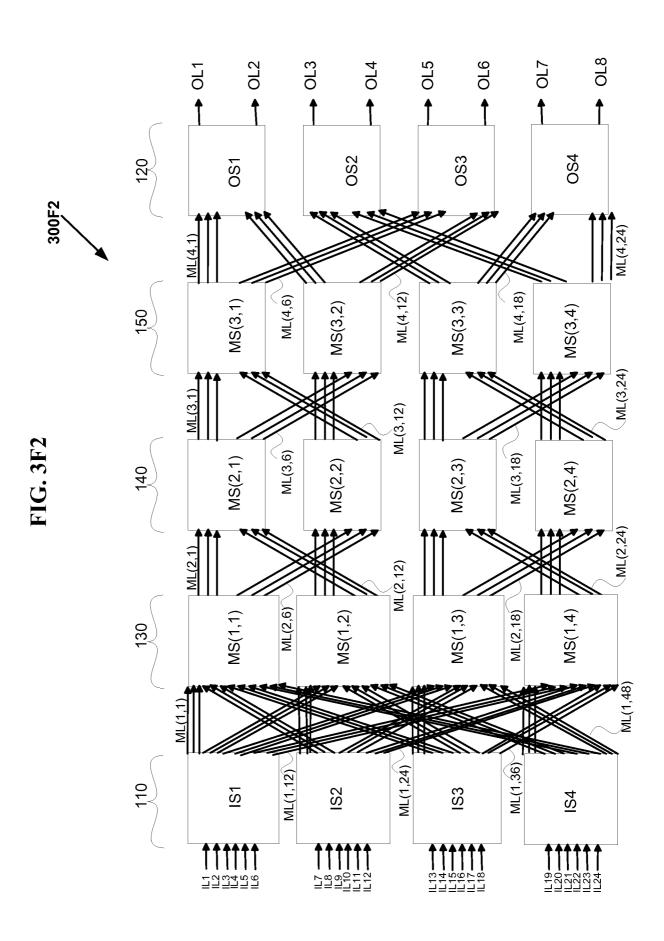

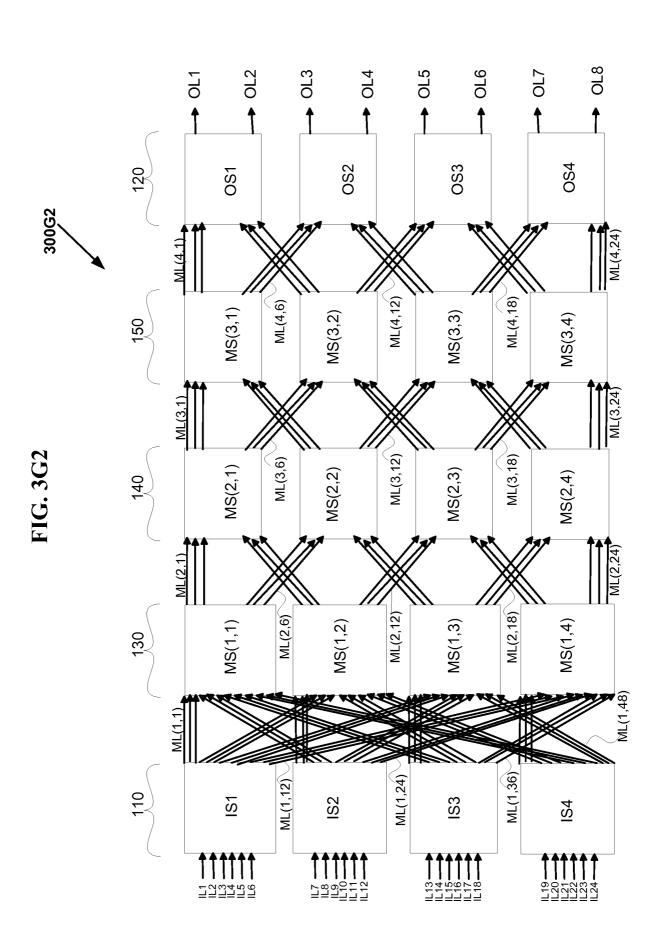

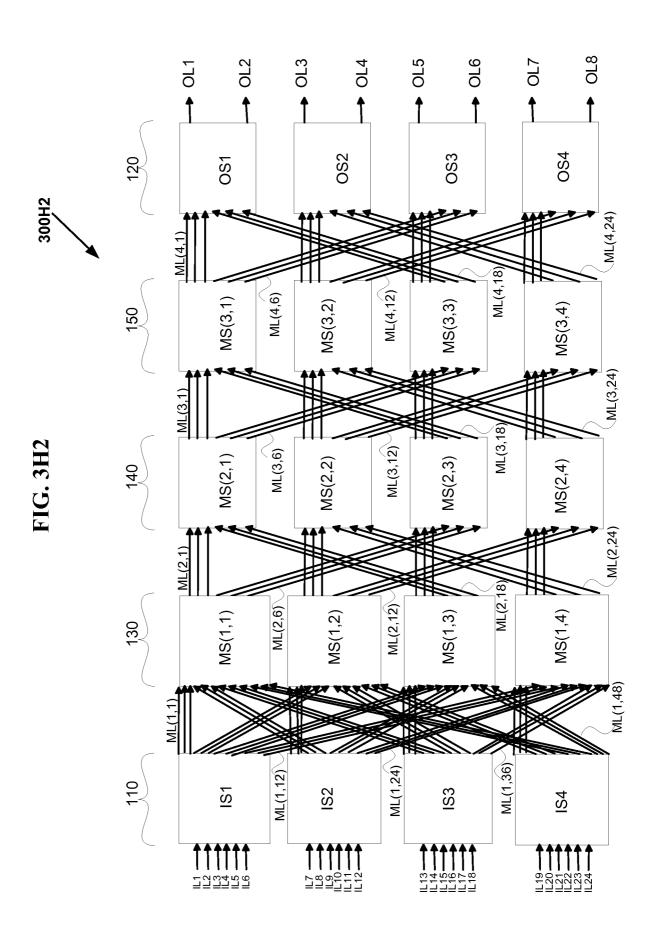

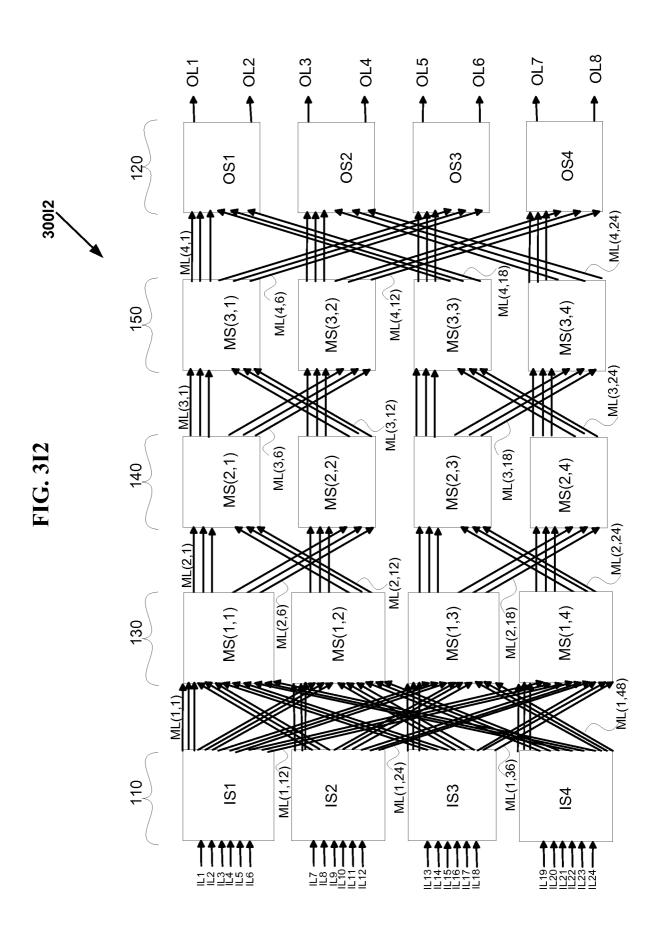

FIG. 2F1 & FIG. 2F2 is a diagram 200F of a general asymmetrical multi-stage network  $V(N_1, N_2, d, 3)$  with  $N_1 = p^* N_2$  and with  $(2 \times \log_d N) - 1$  stages strictly 10 nonblocking network for arbitrary fan-out multicast connections in accordance with the invention.

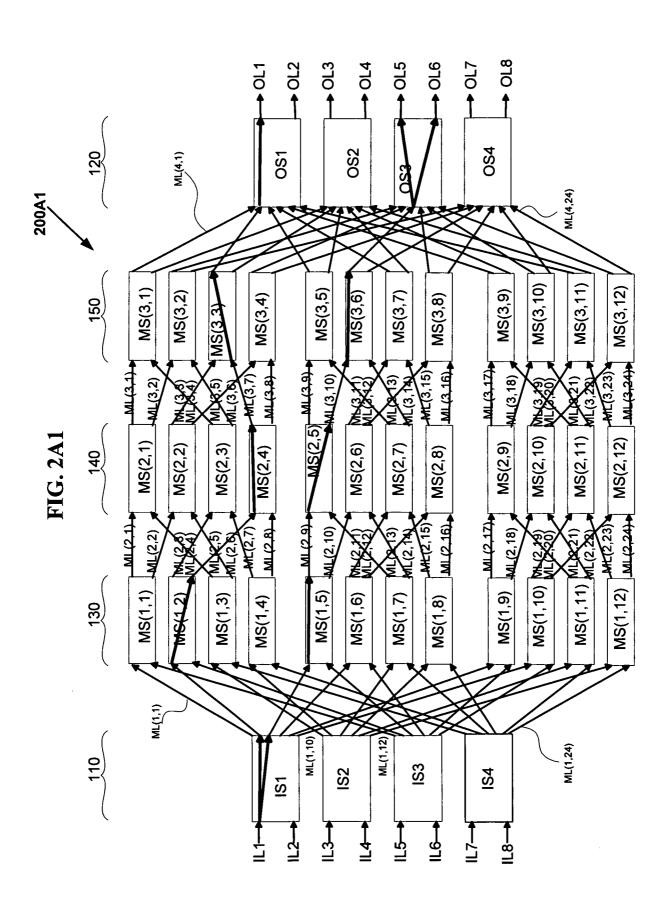

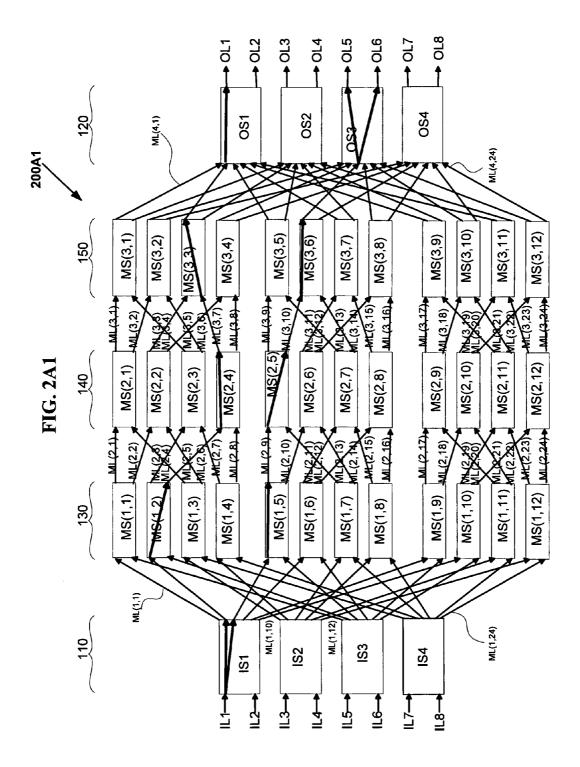

FIG. 2A1 is a diagram 200A1 of an exemplary symmetrical multi-stage network V(N,d,3) having Omega connection topology of five stages with N = 8, d = 2 and s=3 with exemplary multicast connections, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

FIG. 2C1 is a diagram 200C1 of an exemplary asymmetrical multi-stage network  $V(N_1, N_2, d, 3)$  having Omega connection topology of five stages with N<sub>1</sub> = 8, N<sub>2</sub> = p\* N<sub>1</sub> = 24 where p = 3, and d = 2 with exemplary multicast connections, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

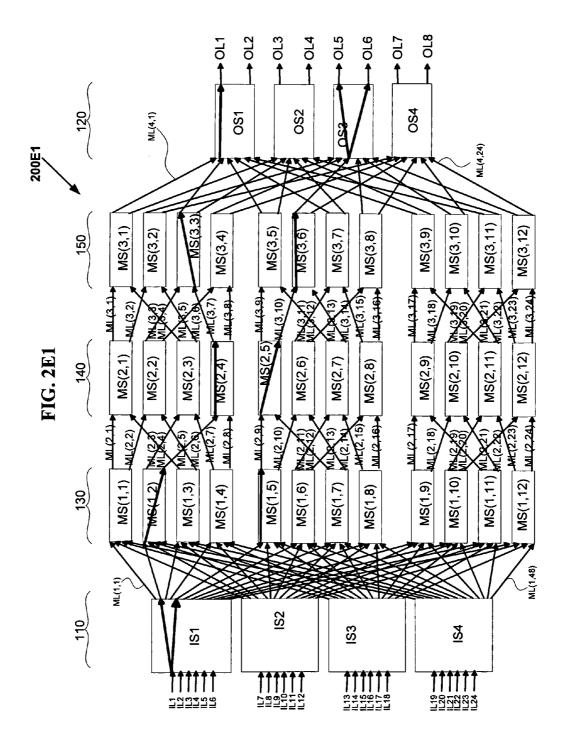

FIG. 2E1 is a diagram 200E1 of an exemplary asymmetrical multi-stage network  $V(N_1, N_2, d, 3)$  having Omega connection topology of five stages with N<sub>2</sub> = 8, N<sub>1</sub> = p\* N<sub>2</sub> = 24, where p = 3, and d = 2 with exemplary multicast connections, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

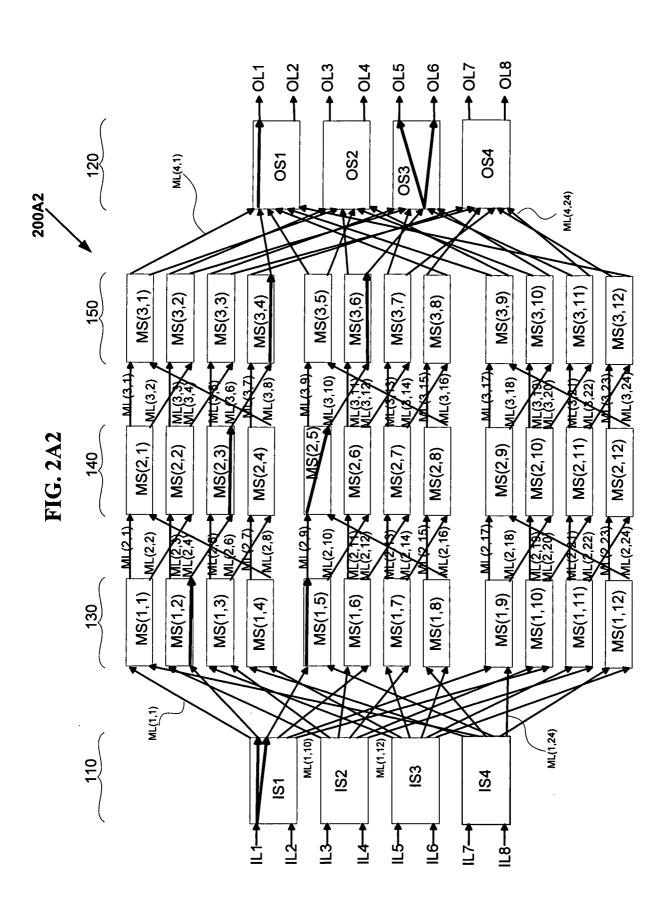

FIG. 2A2 is a diagram 200A2 of an exemplary symmetrical multi-stage network V(N,d,3) having nearest neighbor connection topology of five stages with N = 8, d = 2

#### WO 2008/109756

#### 10

#### PCT/US2008/056064

and s=3 with exemplary multicast connections, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

FIG. 2C2 is a diagram 200C2 of an exemplary asymmetrical multi-stage network V(N<sub>1</sub>, N<sub>2</sub>, d,3) having nearest neighbor connection topology of five stages with N<sub>1</sub> = 8,

N<sub>2</sub> = p\* N<sub>1</sub> = 24 where p = 3, and d = 2 with exemplary multicast connections, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

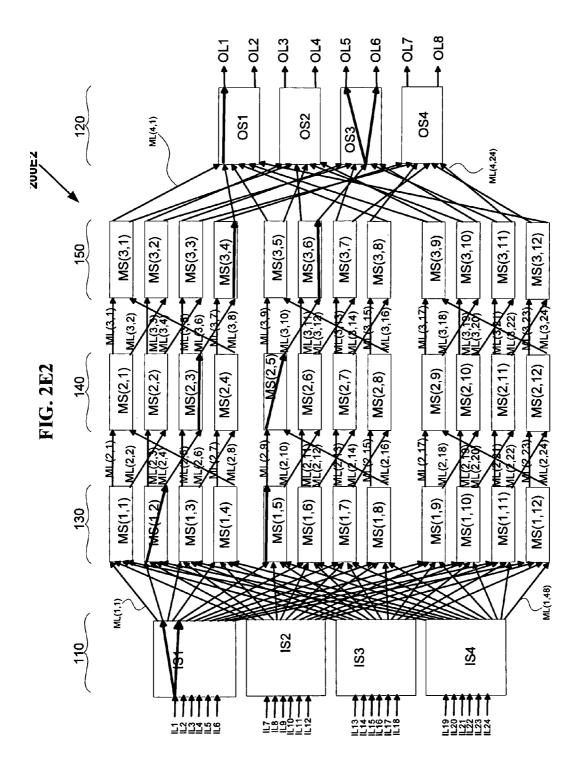

FIG. 2E2 is a diagram 200E2 of an exemplary asymmetrical multi-stage network V(N<sub>1</sub>, N<sub>2</sub>, d,3) having nearest neighbor connection topology of five stages with N<sub>2</sub> = 8,

N<sub>1</sub> = p\* N<sub>2</sub> = 24, where p = 3, and d = 2 with exemplary multicast connections, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

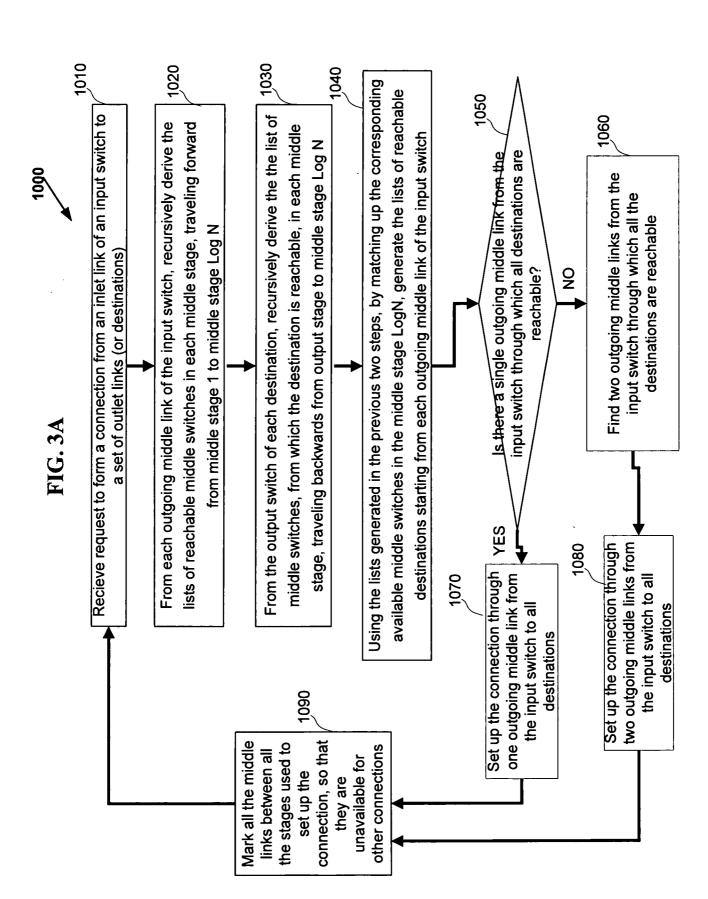

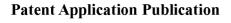

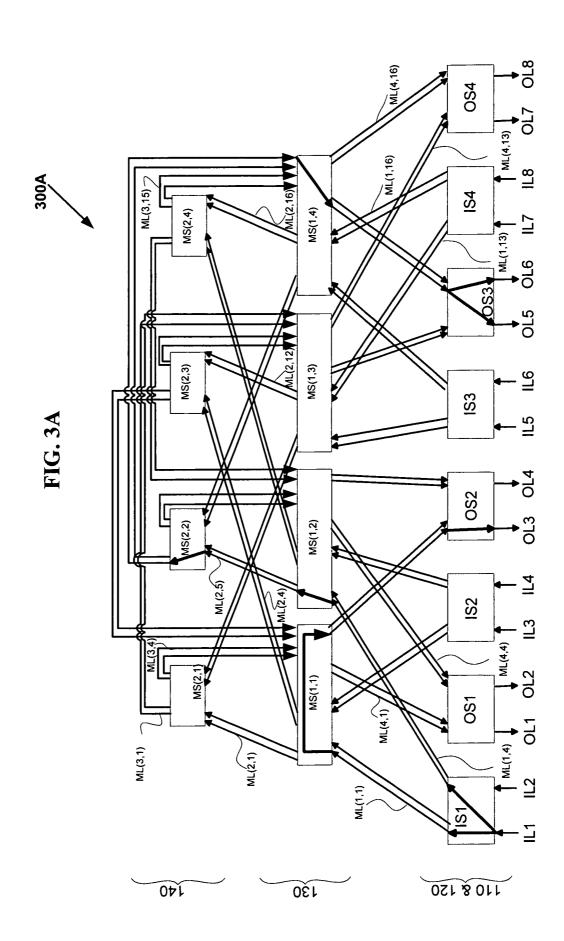

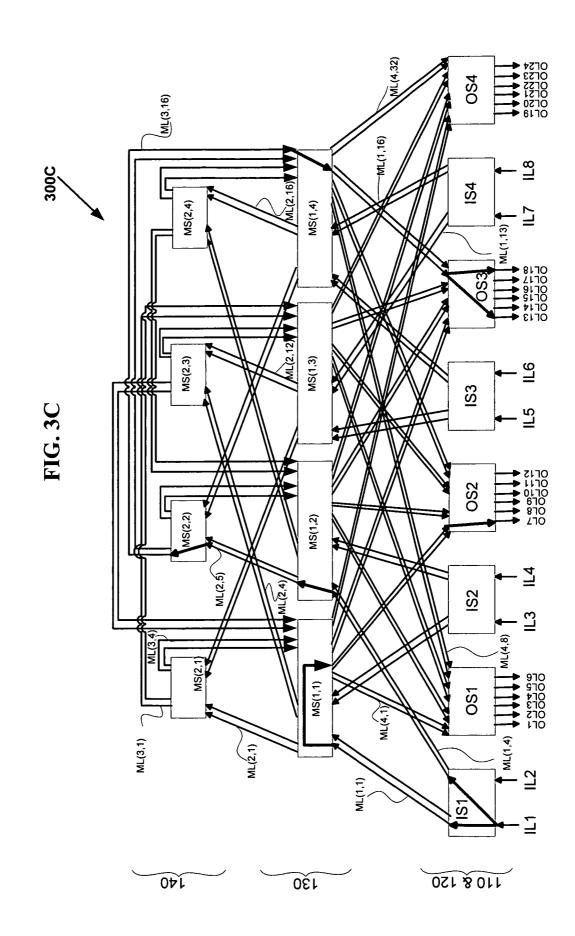

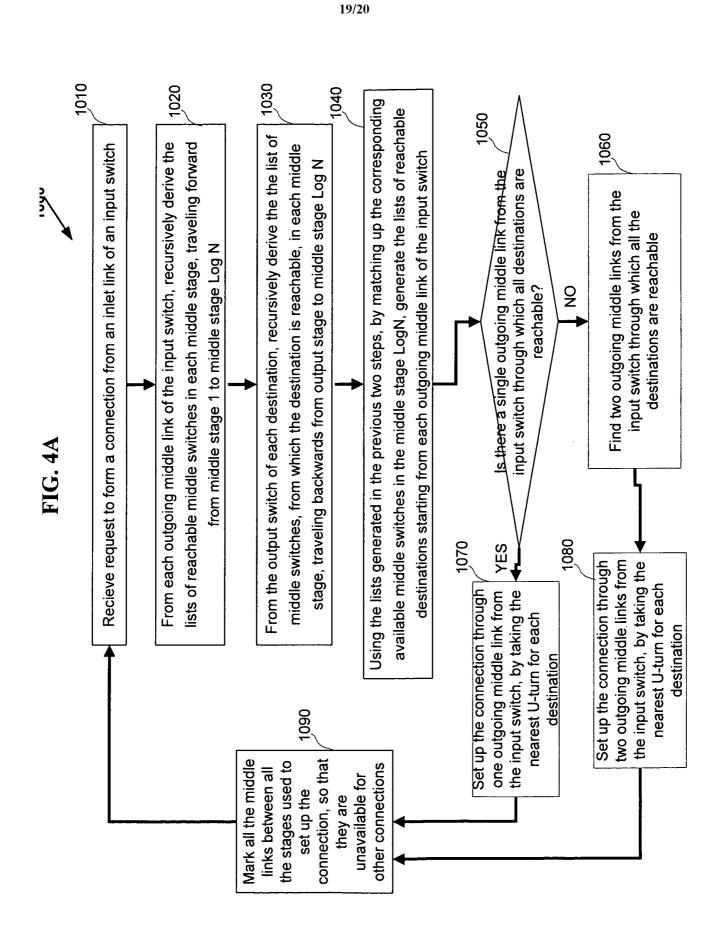

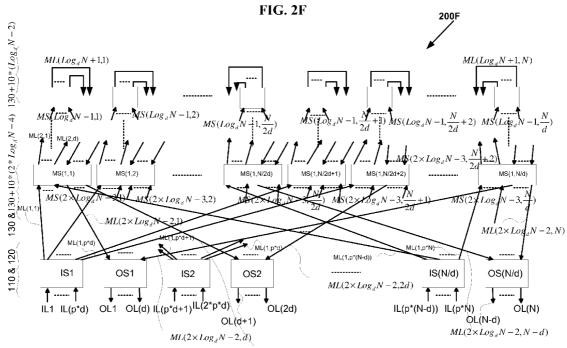

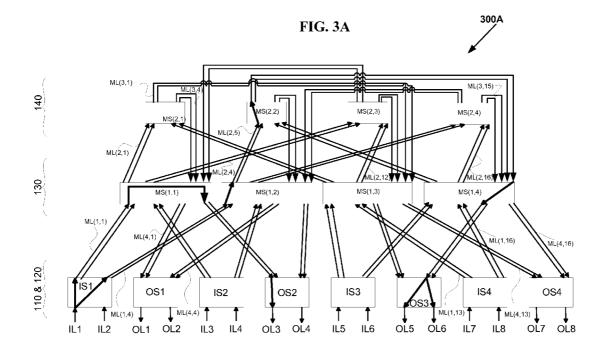

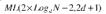

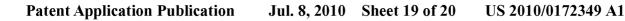

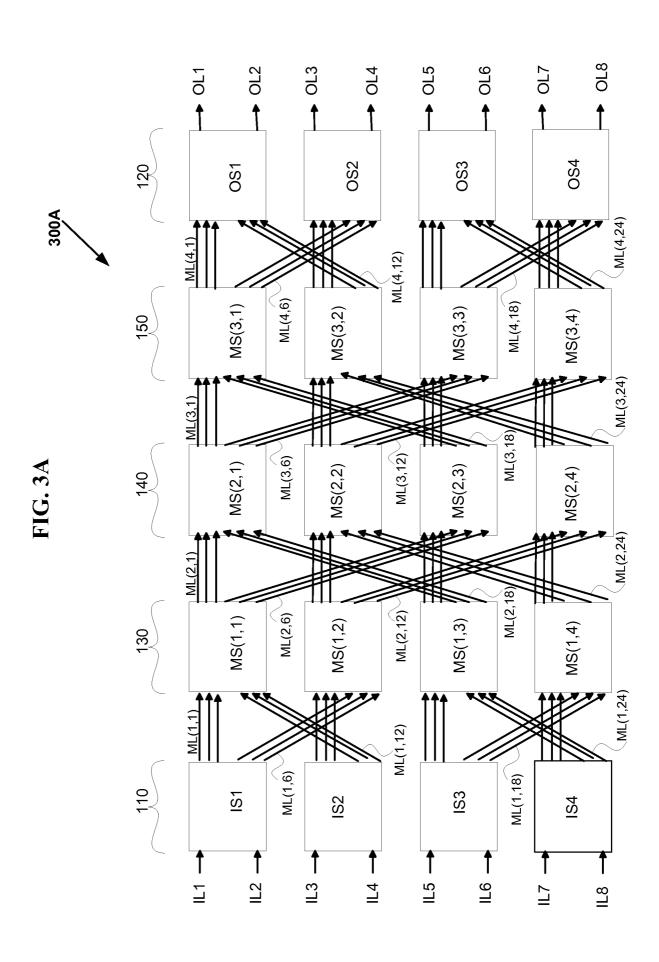

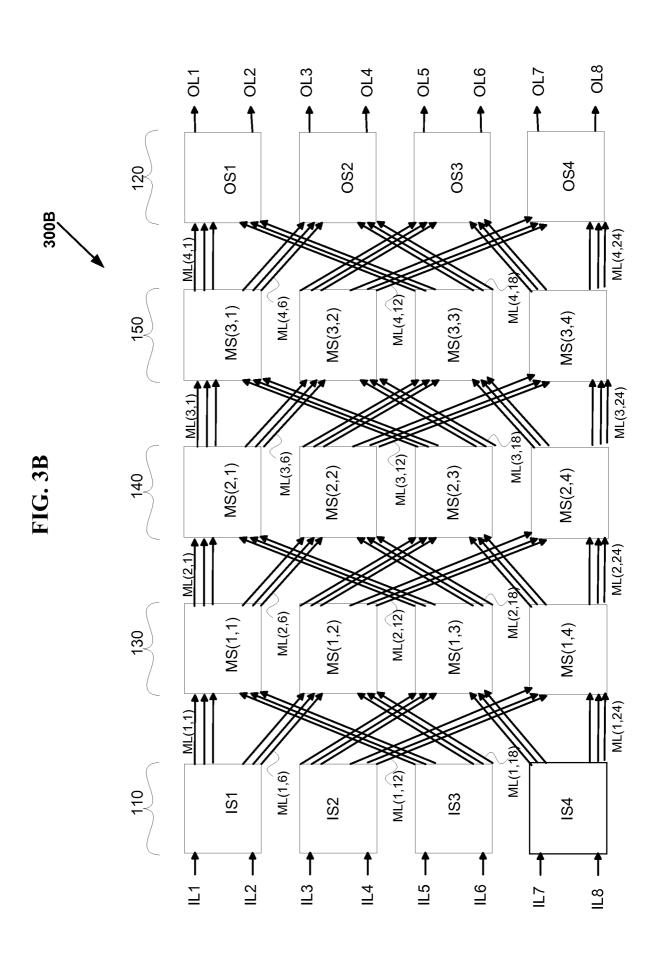

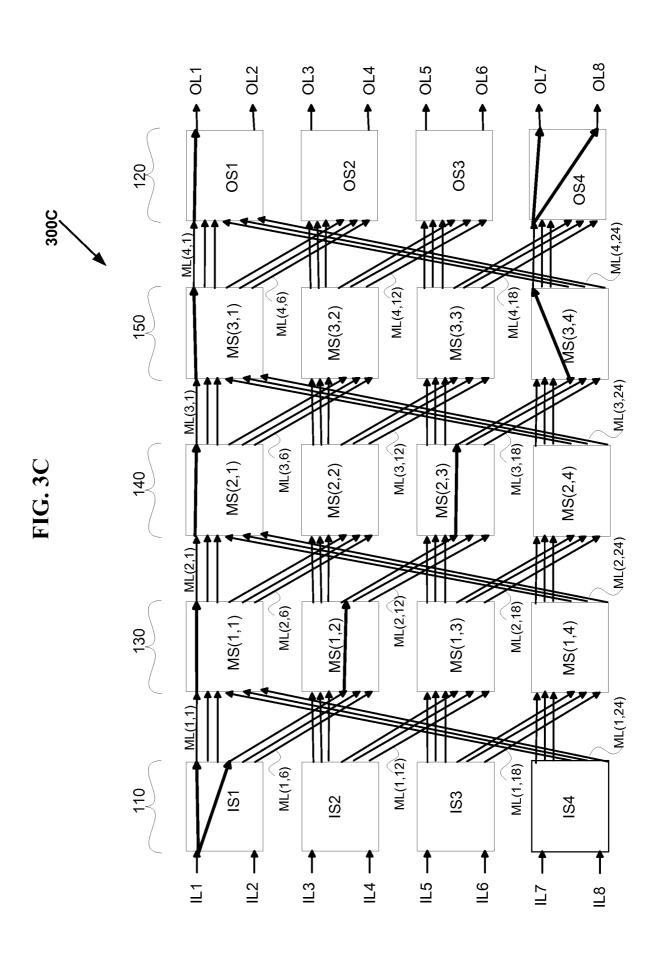

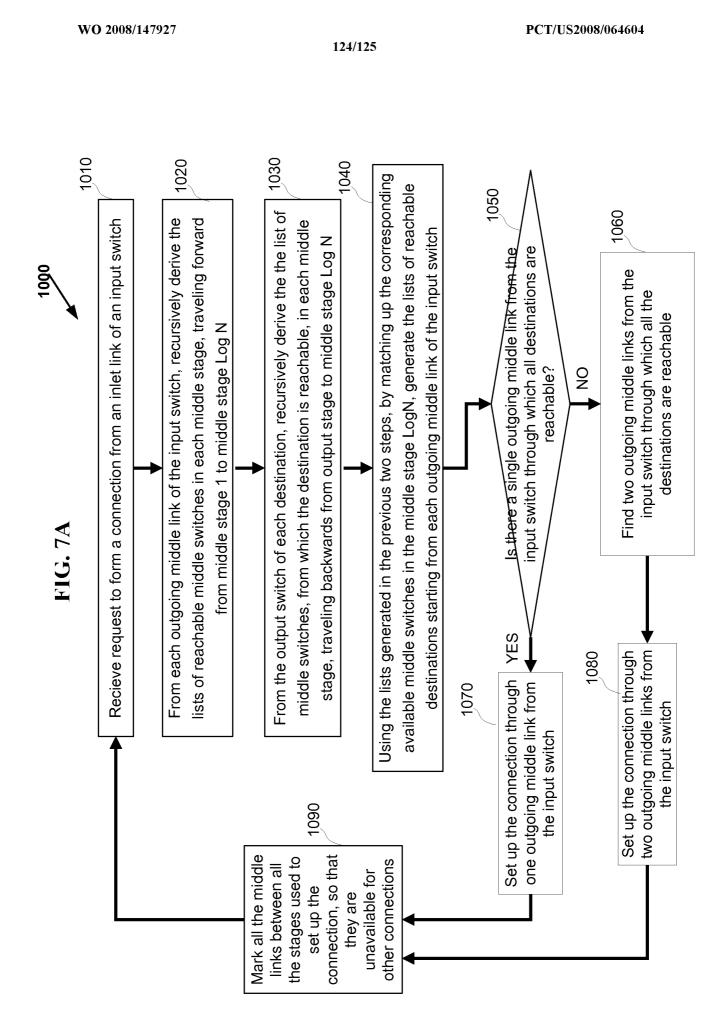

FIG. 3A is high-level flowchart of a scheduling method according to the invention, used to set up the multicast connections in all the networks disclosed in this15 invention.

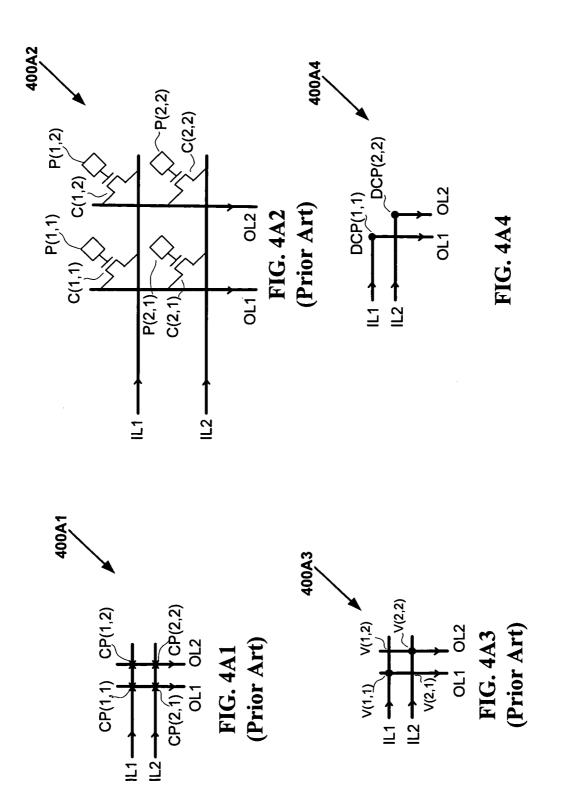

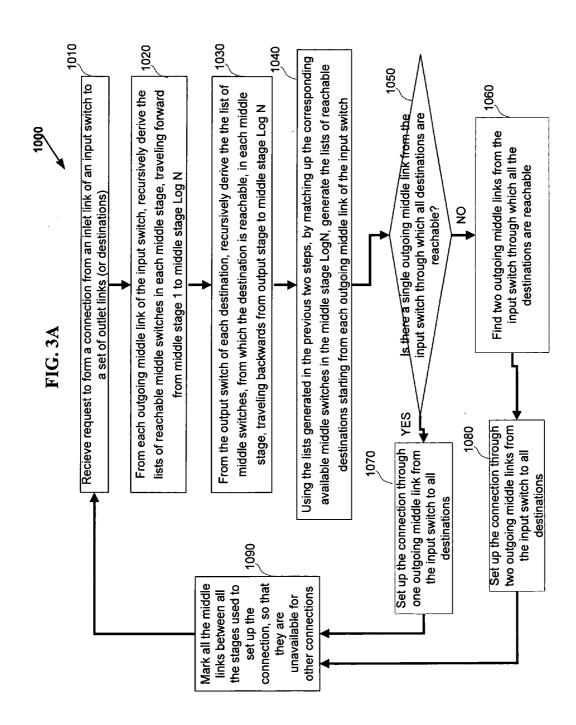

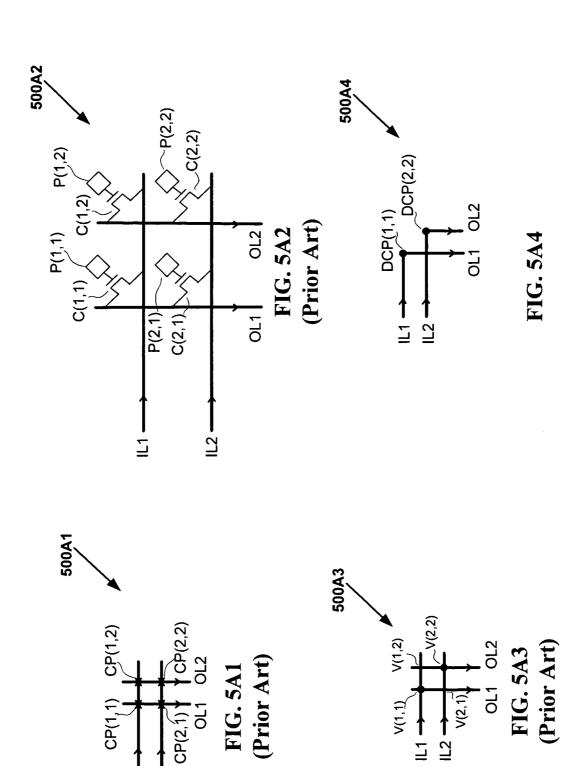

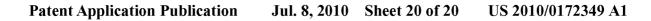

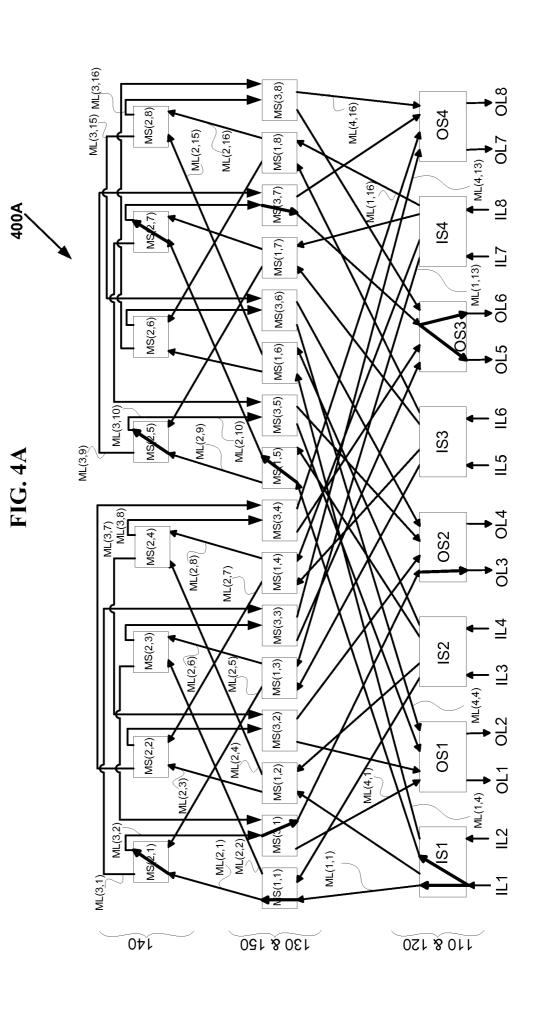

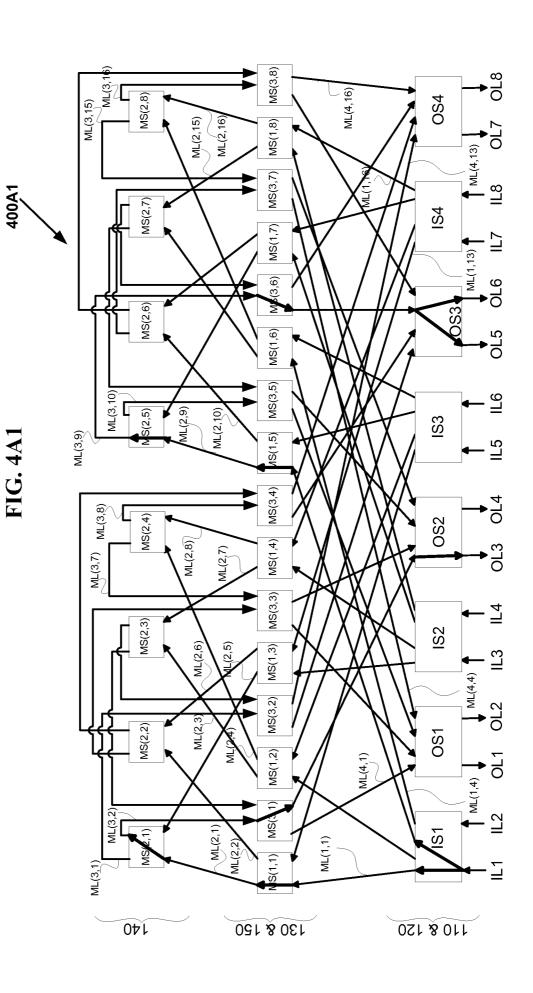

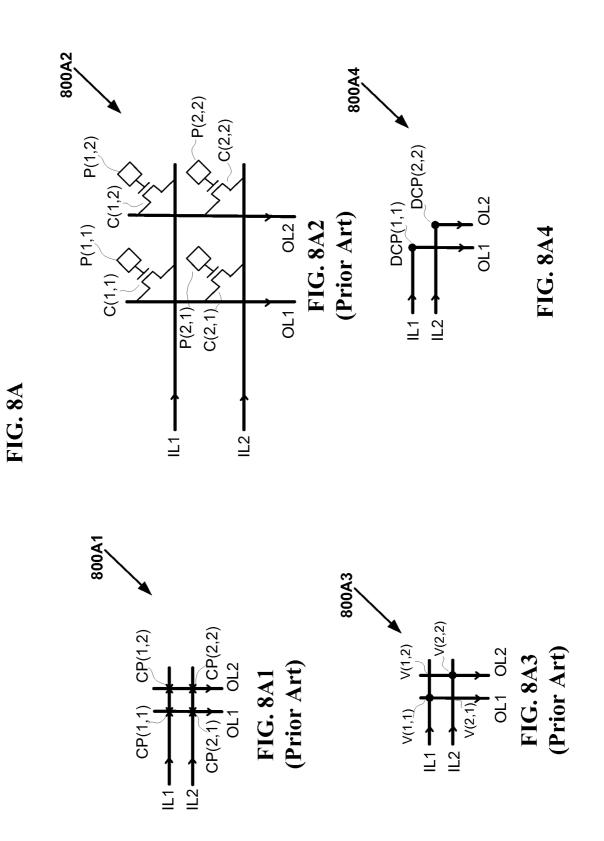

FIG. 4A1 is a diagram 400A1 of an exemplary prior art implementation of a two by two switch; FIG. 4A2 is a diagram 400A2 for programmable integrated circuit prior art implementation of the diagram 400A1 of FIG. 4A1; FIG. 4A3 is a diagram 400A3 for one-time programmable integrated circuit prior art implementation of the diagram 400A1

20 of FIG. 4A1; FIG. 4A4 is a diagram 400A4 for integrated circuit placement and route implementation of the diagram 400A1 of FIG. 4A1.

#### DETAILED DESCRIPTION OF THE INVENTION

The present invention is concerned with the design and operation of large scale crosspoint reduction using arbitrarily large multi-stage switching networks for broadcast, unicast and multicast connections including their generalized topologies. Particularly multi-stage networks with stages more than three and radices greater than or equal to two

#### WO 2008/109756

#### 11

#### PCT/US2008/056064

offer large scale crosspoint reduction when configured with optimal links as disclosed in this invention.

When a transmitting device simultaneously sends information to more than one receiving device, the one-to-many connection required between the transmitting device

and the receiving devices is called a multicast connection. A set of multicast connections is referred to as a multicast assignment. When a transmitting device sends information to one receiving device, the one-to-one connection required between the transmitting device and the receiving device is called unicast connection. When a transmitting device simultaneously sends information to all the available receiving devices, the one-to-all

10 connection required between the transmitting device and the receiving devices is called a broadcast connection.

In general, a multicast connection is meant to be one-to-many connection, which includes unicast and broadcast connections. A multicast assignment in a switching network is nonblocking if any of the available inlet links can always be connected to any

15 of the available outlet links.

In certain multi-stage networks of the type described herein, any connection request of arbitrary fan-out, i.e. from an inlet link to an outlet link or to a set of outlet links of the network, can be satisfied without blocking if necessary by rearranging some of the previous connection requests. In certain other multi-stage networks of the type

20 described herein, any connection request of arbitrary fan-out, i.e. from an inlet link to an outlet link or to a set of outlet links of the network, can be satisfied without blocking with never needing to rearrange any of the previous connection requests.

In certain multi-stage networks of the type described herein, any connection request of unicast from an inlet link to an outlet link of the network, can be satisfied 25 without blocking if necessary by rearranging some of the previous connection requests. In certain other multi-stage networks of the type described herein, any connection request of unicast from an inlet link to an outlet link of the network can be satisfied without blocking with never needing to rearrange any of the previous connection requests.

PCT/US2008/056064

#### WO 2008/109756

Nonblocking configurations for other types of networks with numerous connection topologies and scheduling methods are disclosed as follows:

12

1) Strictly and rearrangeably nonblocking for arbitrary fan-out multicast and unicast for generalized butterfly fat tree networks  $V_{bft}(N_1, N_2, d, s)$  with numerous

5 connection topologies and the scheduling methods are described in detail in U.S. Provisional Patent Application, Attorney Serial No. 60/940, 387 that is incorporated by reference above.

2) Rearrangeably nonblocking for arbitrary fan-out multicast and unicast, and strictly nonblocking for unicast for generalized multi-link multi-stage networks

10 V<sub>mlink</sub> (N<sub>1</sub>, N<sub>2</sub>, d, s) and generalized folded multi-link multi-stage networks

V<sub>fold-mlink</sub> (N<sub>1</sub>, N<sub>2</sub>, d, s) with numerous connection topologies and the scheduling methods are described in detail in U.S. Provisional Patent Application, Attorney Serial No. 60/940, 389 that is incorporated by reference above.

3) Strictly and rearrangeably nonblocking for arbitrary fan-out multicast and 15 unicast for generalized multi-link butterfly fat tree networks  $V_{mlink-bfl}(N_1, N_2, d, s)$  with numerous connection topologies and the scheduling methods are described in detail in U.S. Provisional Patent Application, Attorney Serial No. 60/940, 390 that is incorporated by reference above.

4) Strictly and rearrangeably nonblocking for arbitrary fan-out multicast and 20 unicast for generalized folded multi-stage networks  $V_{fold}(N_1, N_2, d, s)$  with numerous connection topologies and the scheduling methods are described in detail in U.S. Provisional Patent Application, Attorney Serial No. 60/940, 391 that is incorporated by reference above.

5) Strictly nonblocking for arbitrary fan-out multicast for generalized multi-link

multi-stage networks V<sub>mlink</sub> (N<sub>1</sub>, N<sub>2</sub>, d, s) and generalized folded multi-link multi-stage

networks V<sub>fold-mlink</sub> (N<sub>1</sub>, N<sub>2</sub>, d, s) with numerous connection topologies and the scheduling

#### WO 2008/109756

15

20

#### 13

#### PCT/US2008/056064

methods are described in detail in U.S. Provisional Patent Application, Attorney Serial No. 60/940, 392 that is incorporated by reference above.

6) VLSI layouts of generalized multi-stage networks  $V(N_1, N_2, d, s)$ , generalized folded multi-stage networks  $V_{fold}(N_1, N_2, d, s)$ , generalized butterfly fat tree networks

5 V<sub>bft</sub> (N<sub>1</sub>, N<sub>2</sub>, d, s), generalized multi-link multi-stage networks V<sub>mlink</sub> (N<sub>1</sub>, N<sub>2</sub>, d, s), generalized folded multi-link multi-stage networks V<sub>fold-mlink</sub> (N<sub>1</sub>, N<sub>2</sub>, d, s), generalized multi-link butterfly fat tree networks V<sub>mlink-bft</sub> (N<sub>1</sub>, N<sub>2</sub>, d, s), and generalized hypercube networks V<sub>hcube</sub> (N<sub>1</sub>, N<sub>2</sub>, d, s) for s = 1,2,3 or any number in general, are described in detail in U.S. Provisional Patent Application, Attorney Serial No. M-0045 US that is

10 incorporated by reference above.

7) VLSI layouts of numerous types of multi-stage networks with locality exploitation are described in U.S. Provisional Patent Application Serial No. 60/984, 724 entitled "VLSI LAYOUTS OF FULLY CONNECTED NETWORKS WITH LOCALITY EXPLOITATION" by Venkat Konda assigned to the same assignee as the current application, filed November 2, 2007.

8) VLSI layouts of numerous types of multistage pyramid networks are described in U.S. Provisional Patent Application Serial No. 61/018, 494 entitled "VLSI LAYOUTS OF FULLY CONNECTED GENERALIZED AND PYRAMID NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed January 1, 2008.

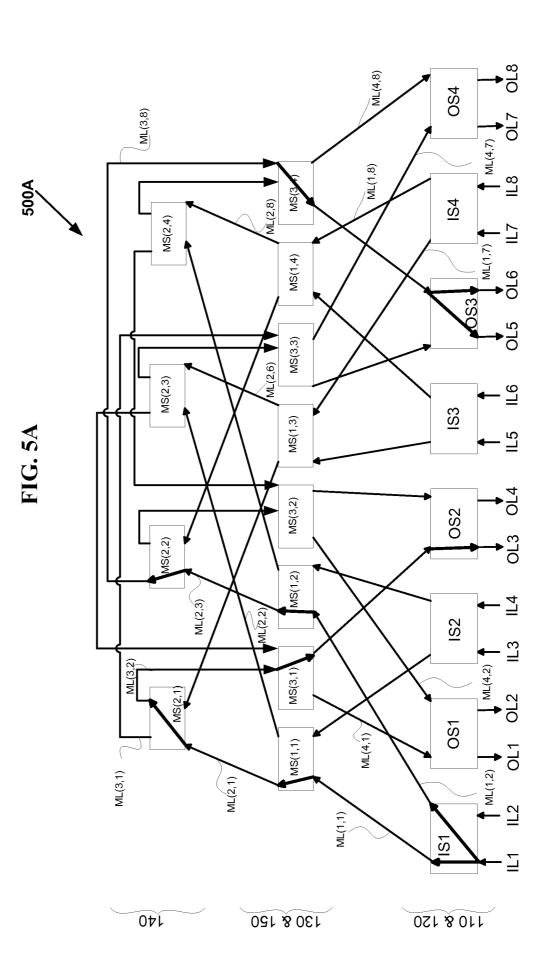

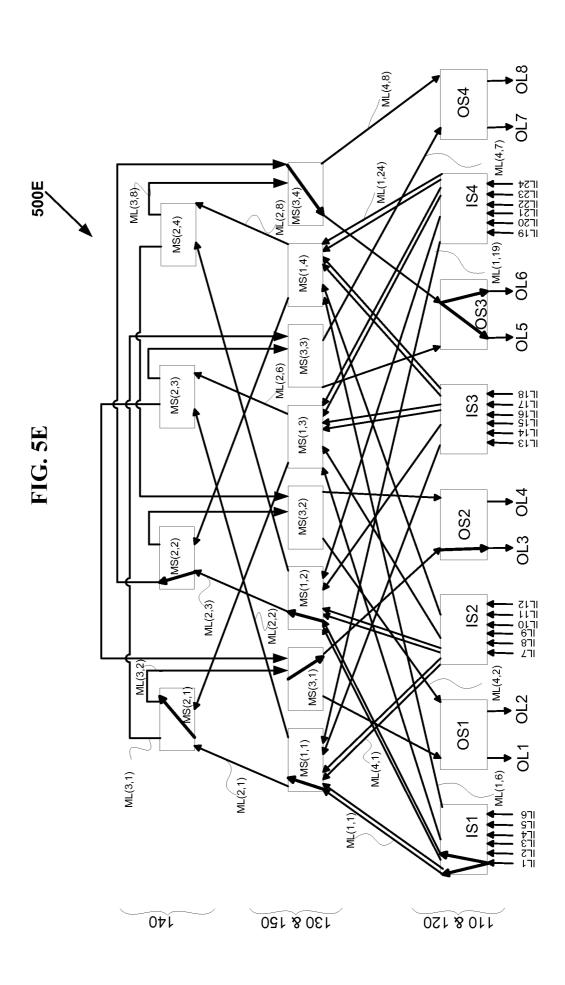

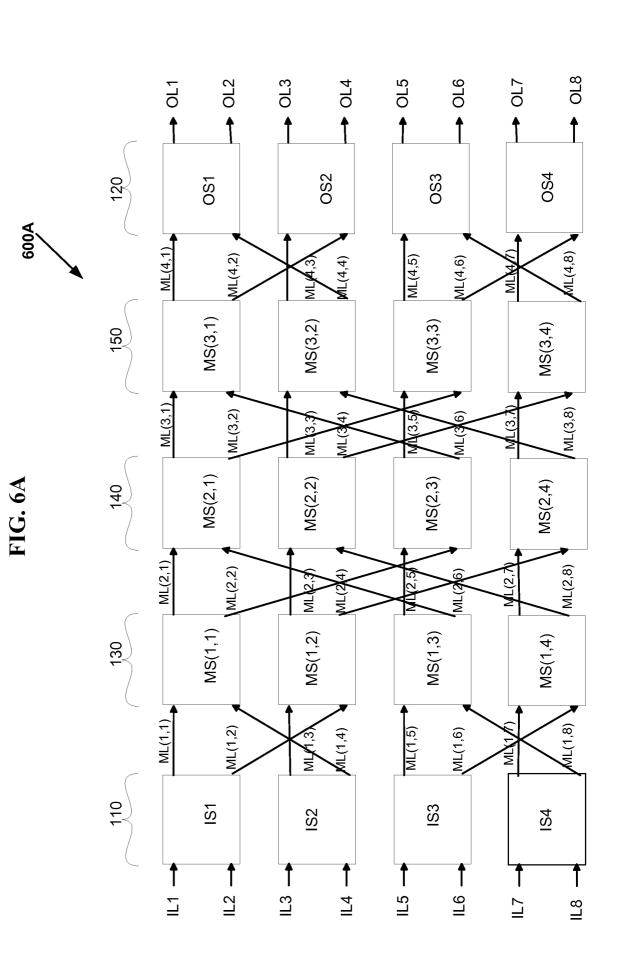

#### Symmetric RNB Embodiments:

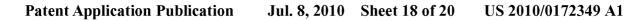

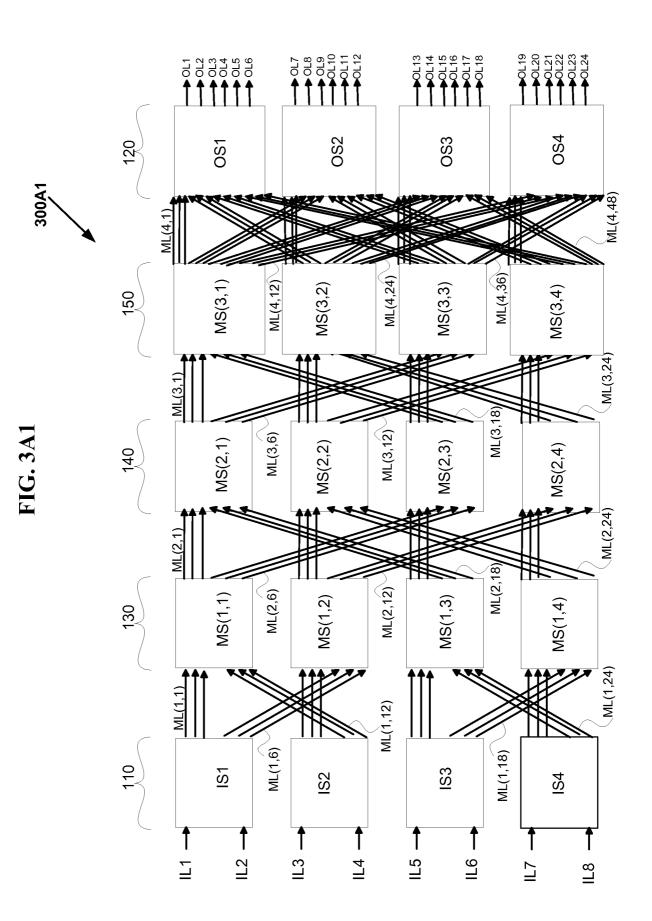

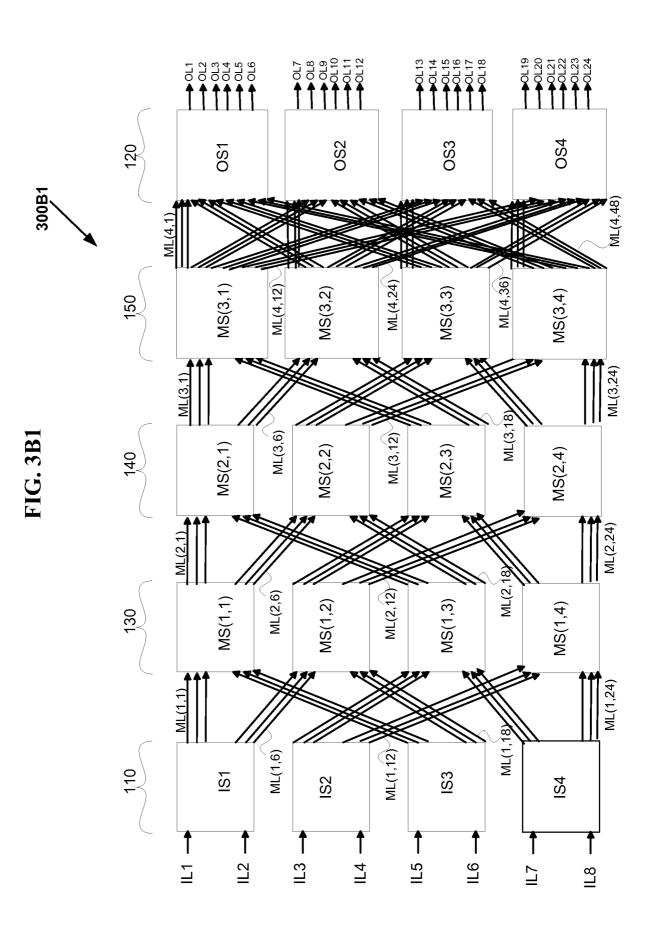

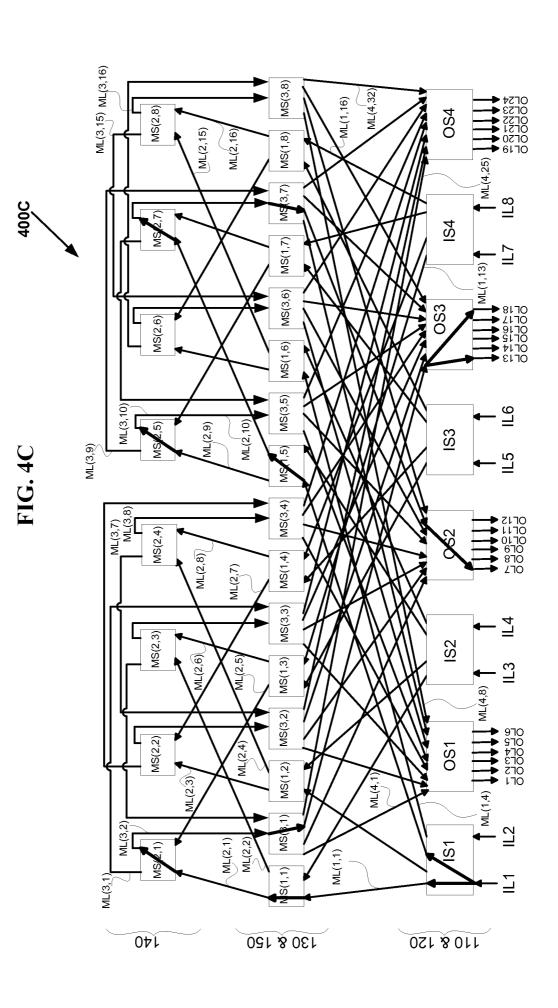

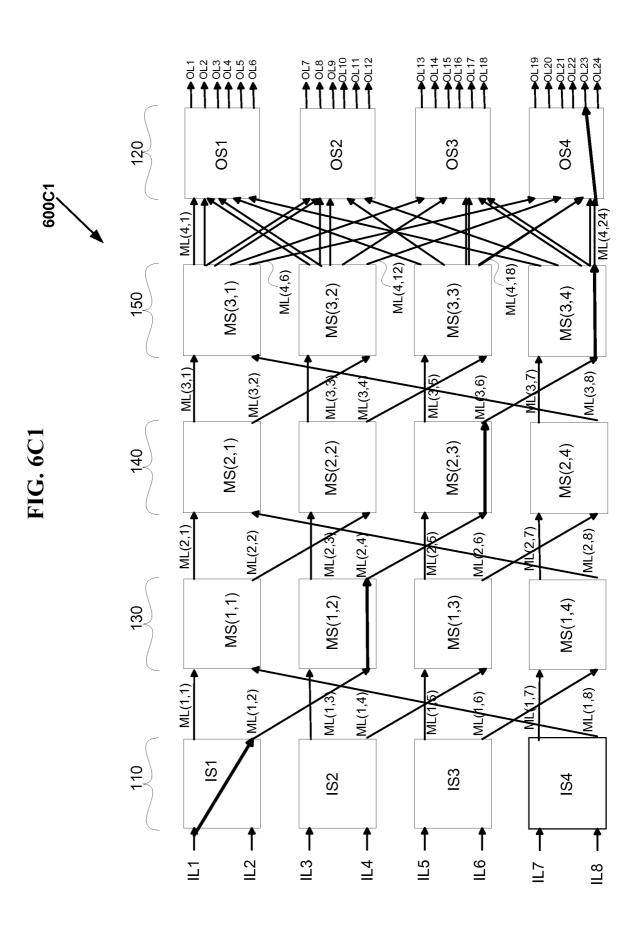

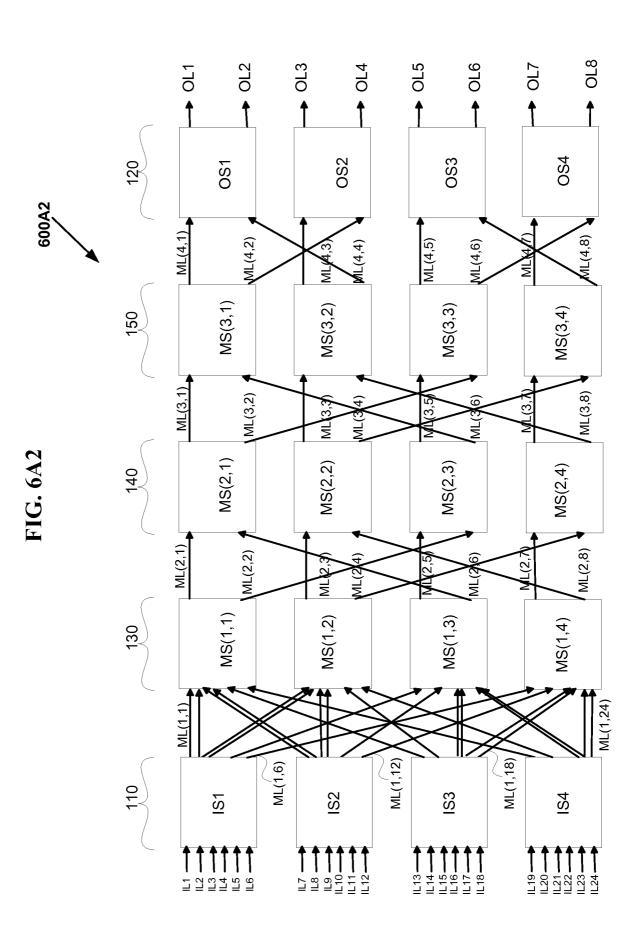

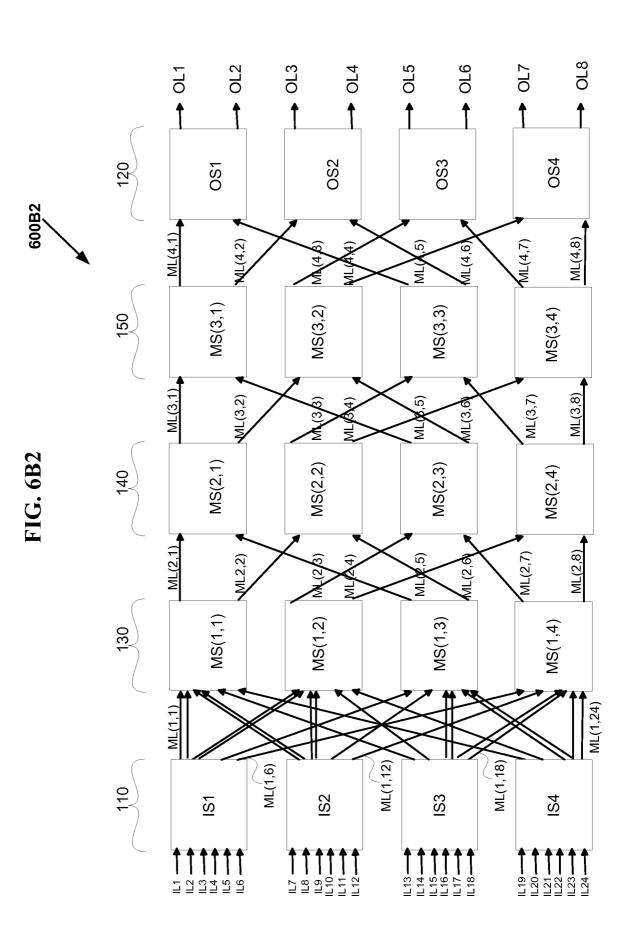

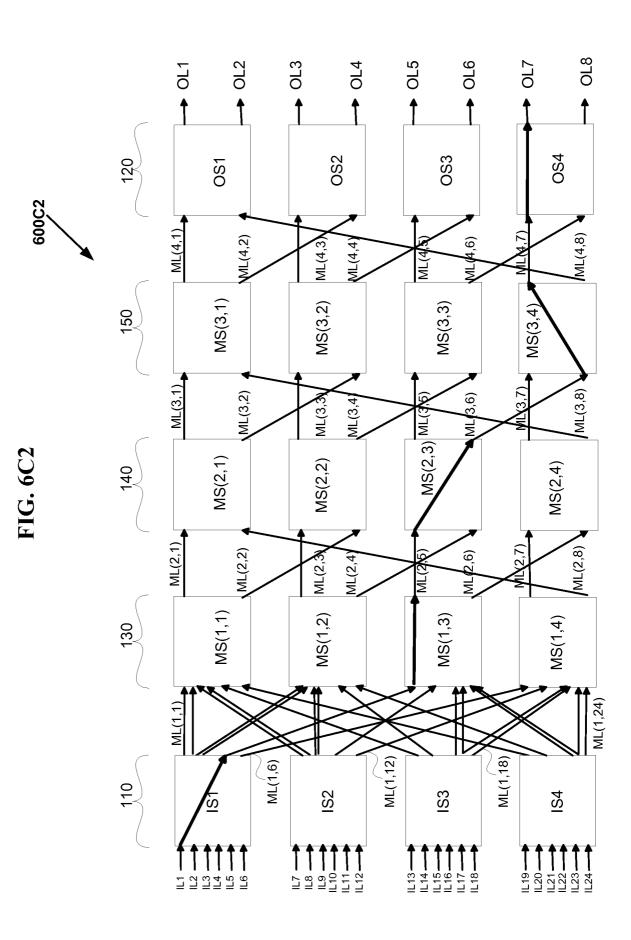

Referring to FIG. 1A, in one embodiment, an exemplary symmetrical multi-stage network 100A with five stages of thirty two switches for satisfying communication 25 requests, such as setting up a telephone call or a data call, or a connection between configurable logic blocks, between an input stage 110 and output stage 120 via middle

#### WO 2008/109756

5

#### PCT/US2008/056064

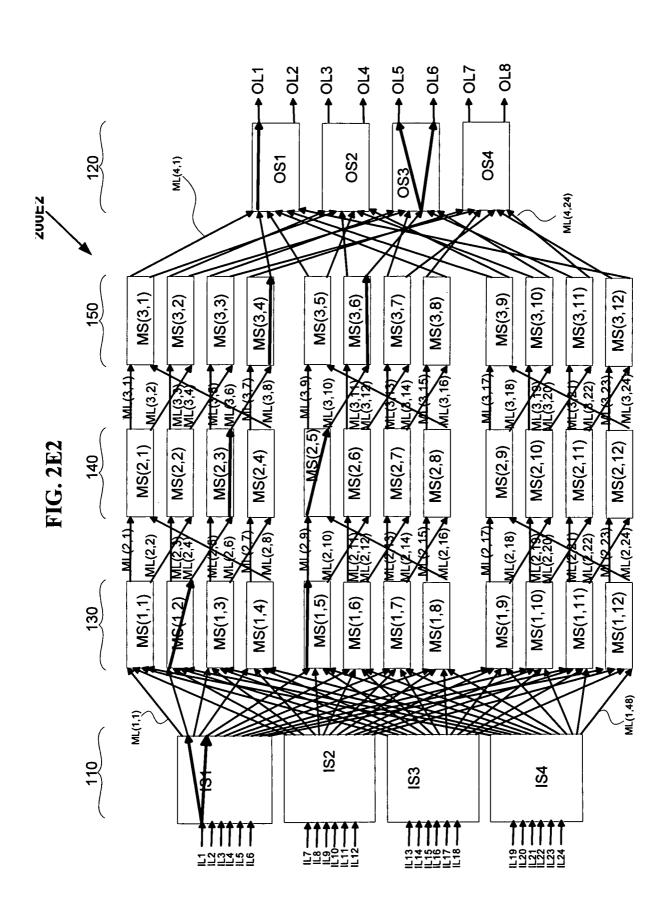

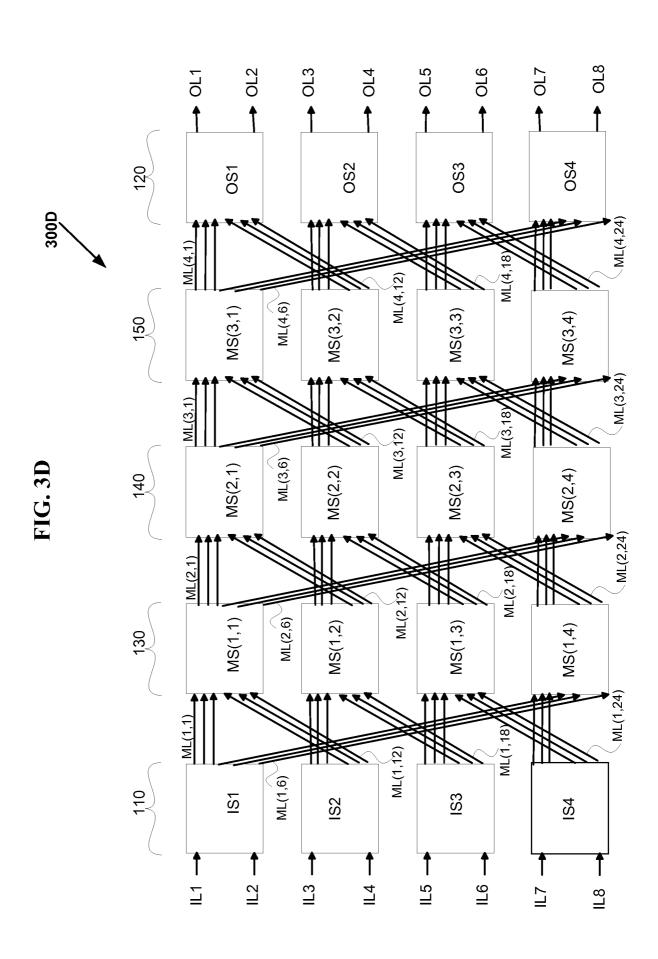

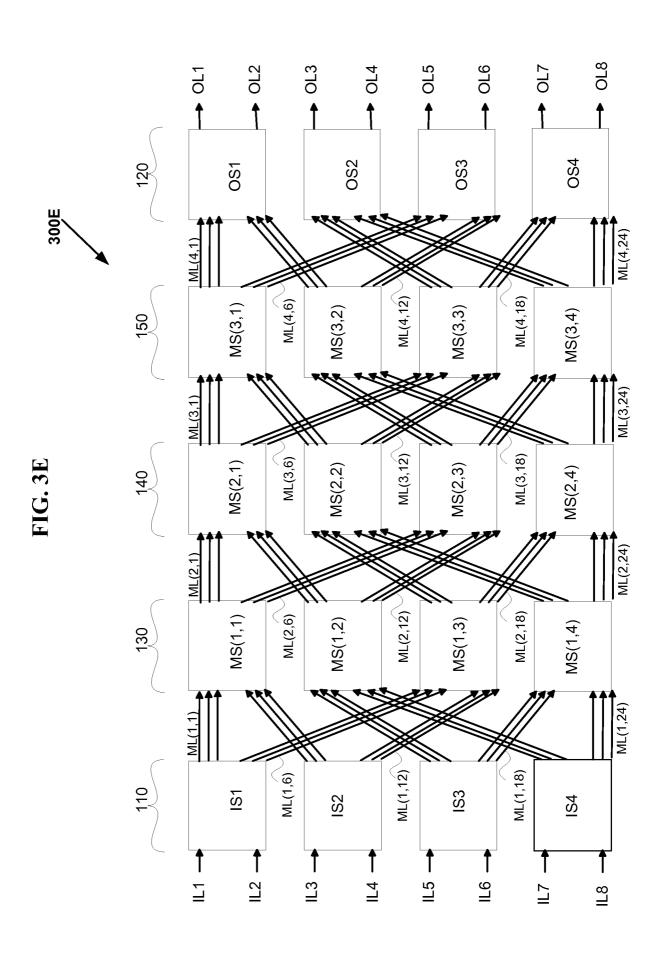

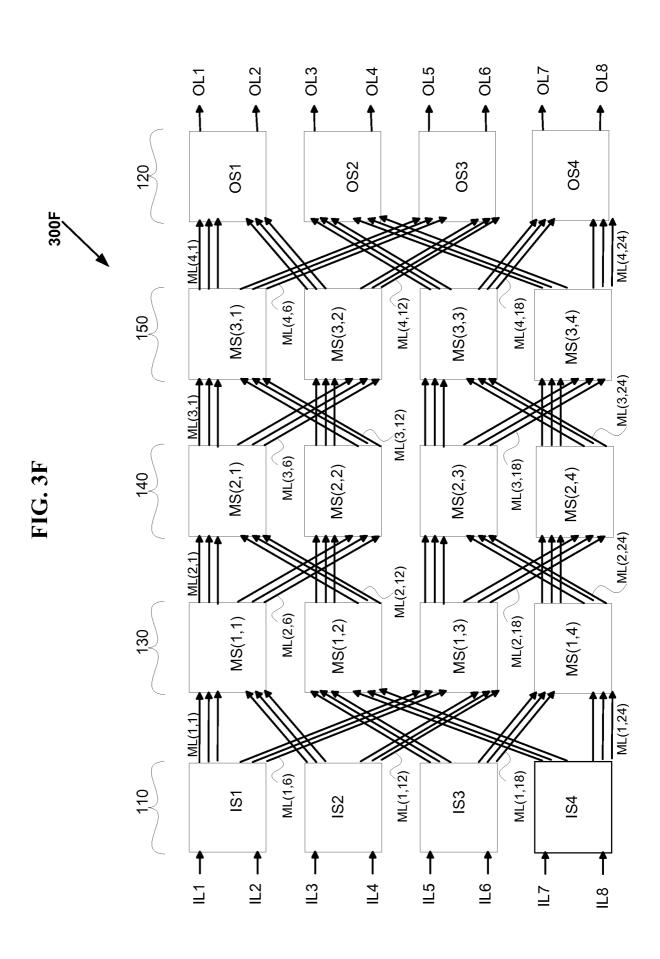

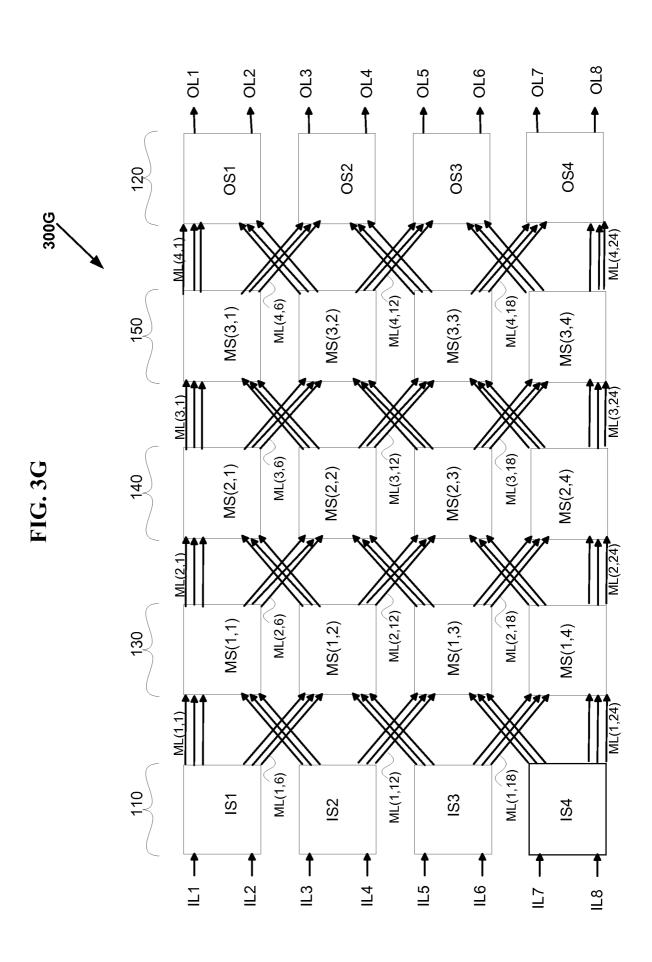

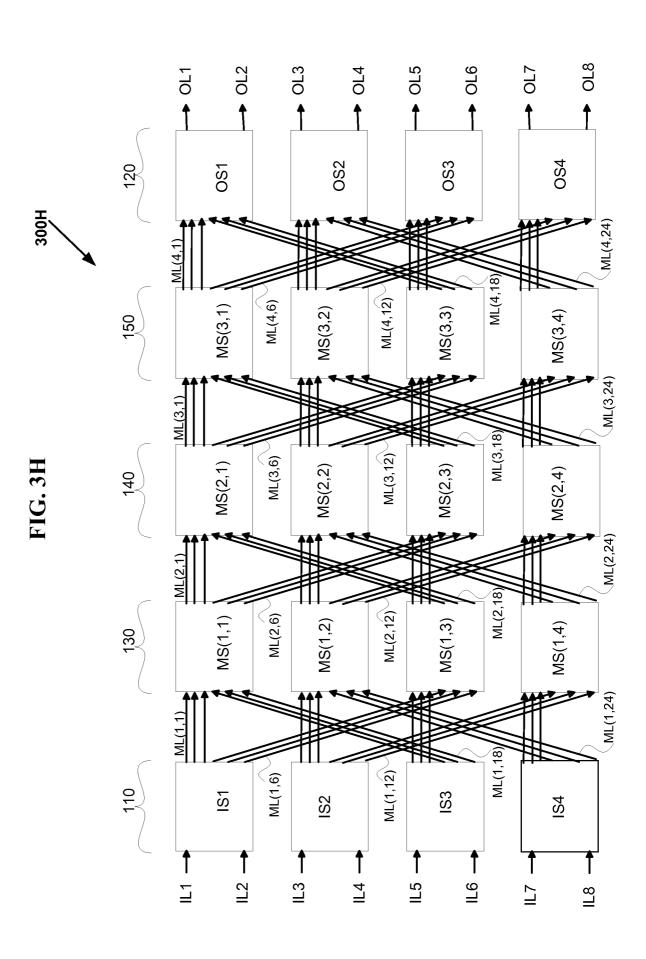

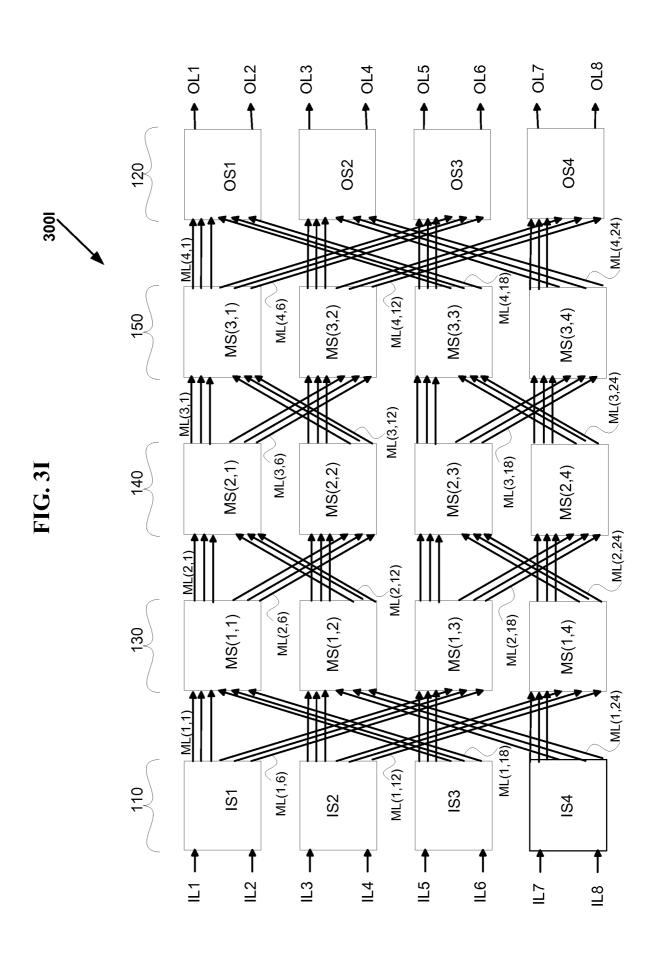

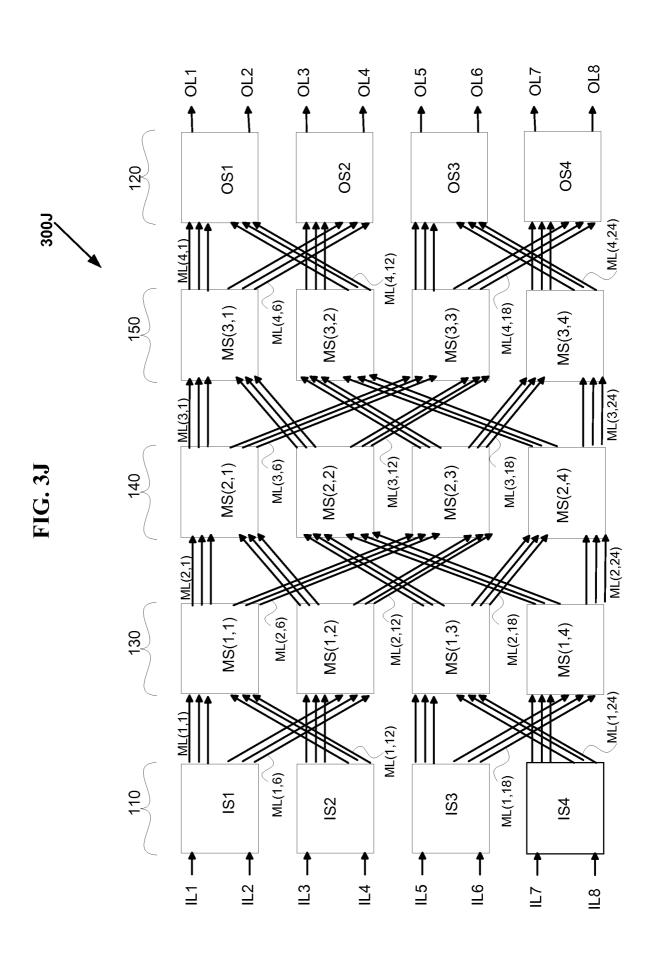

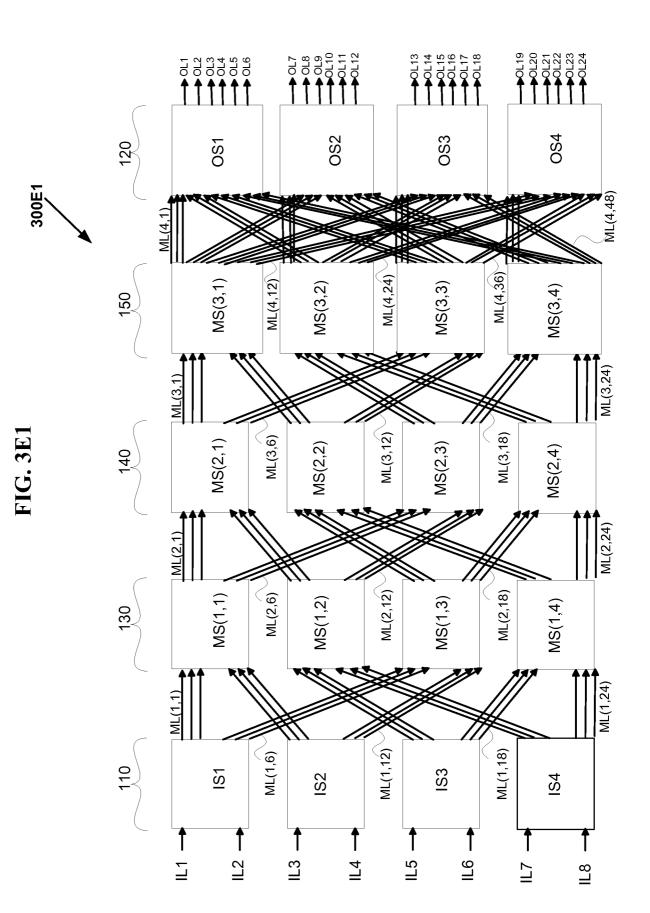

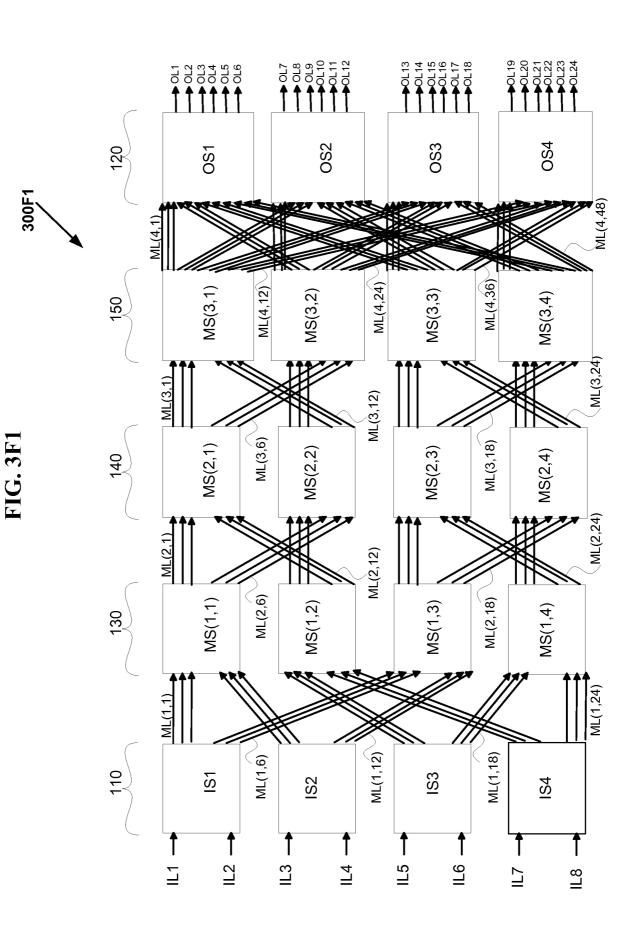

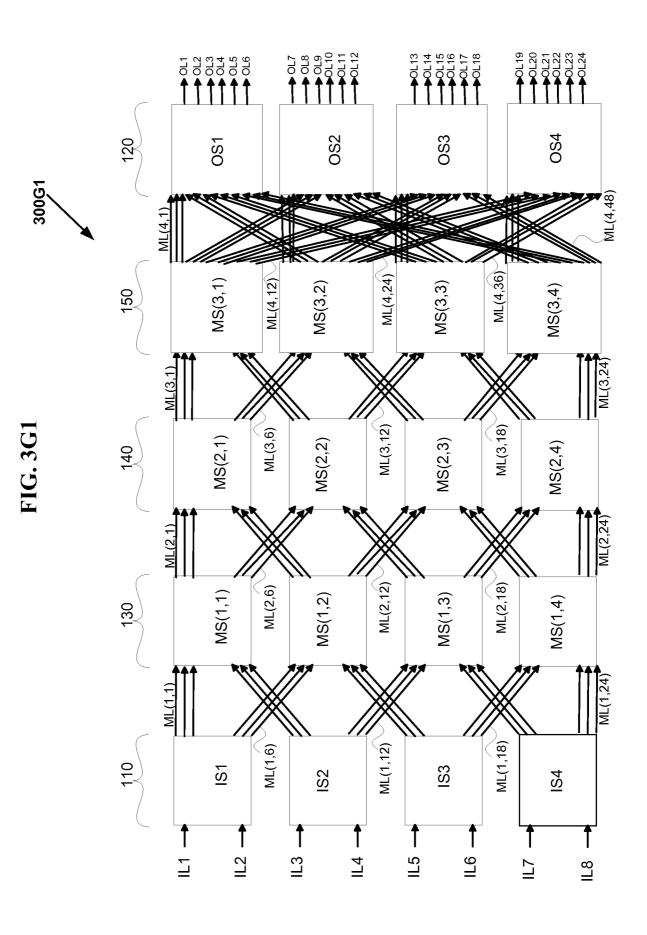

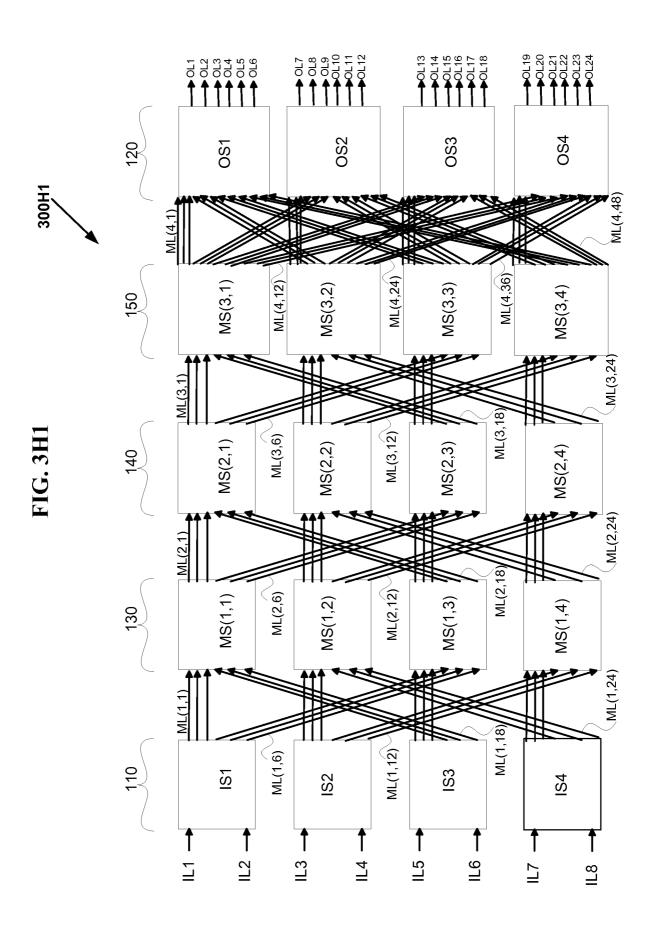

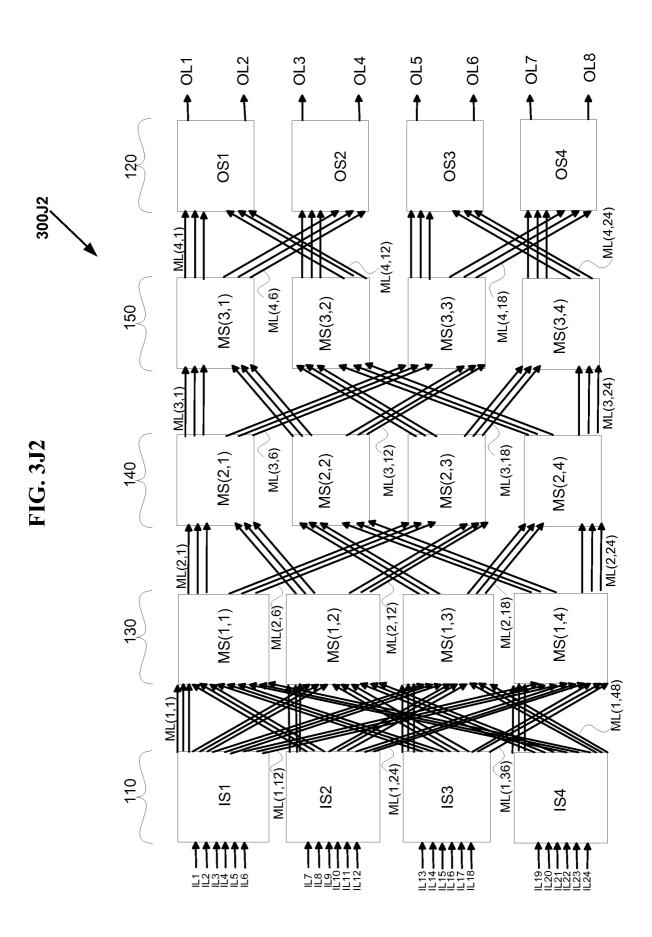

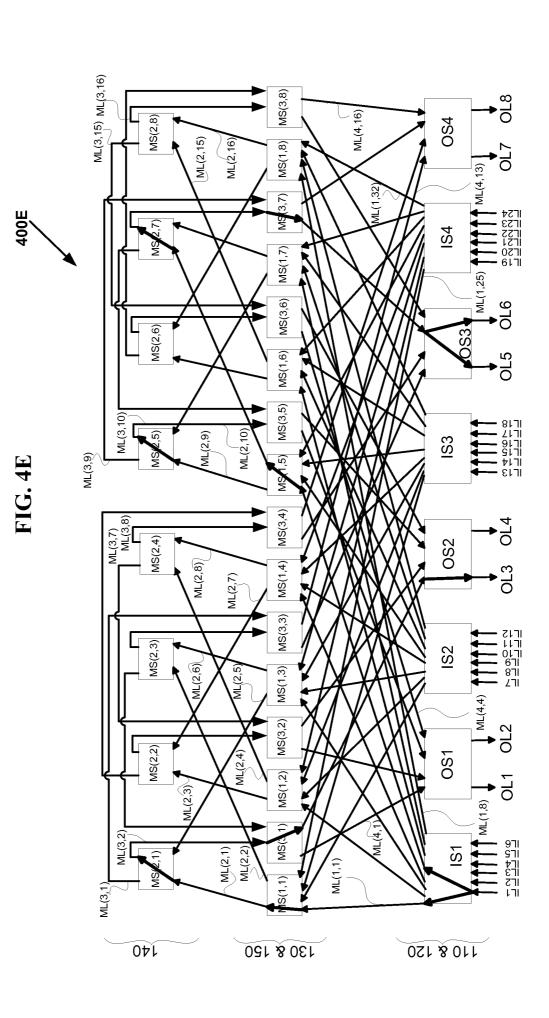

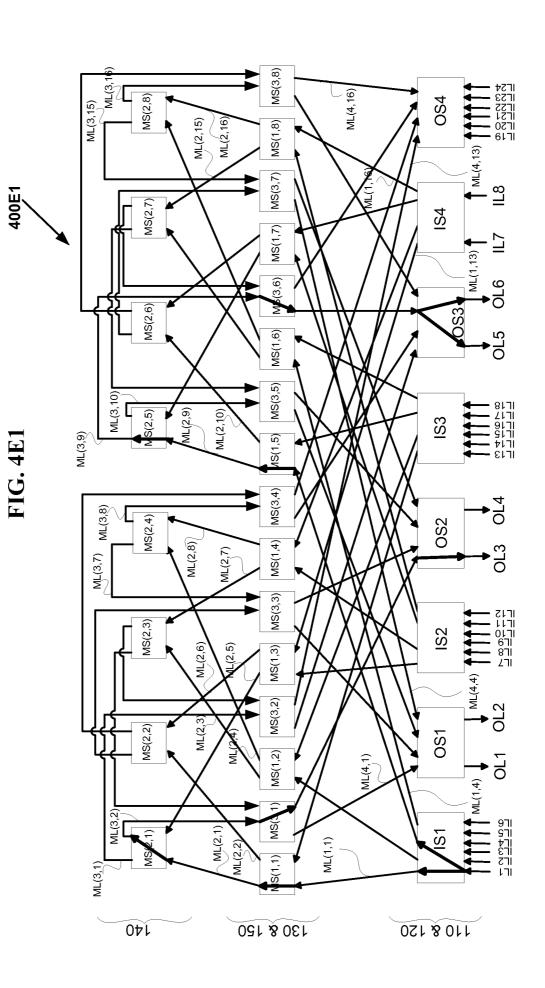

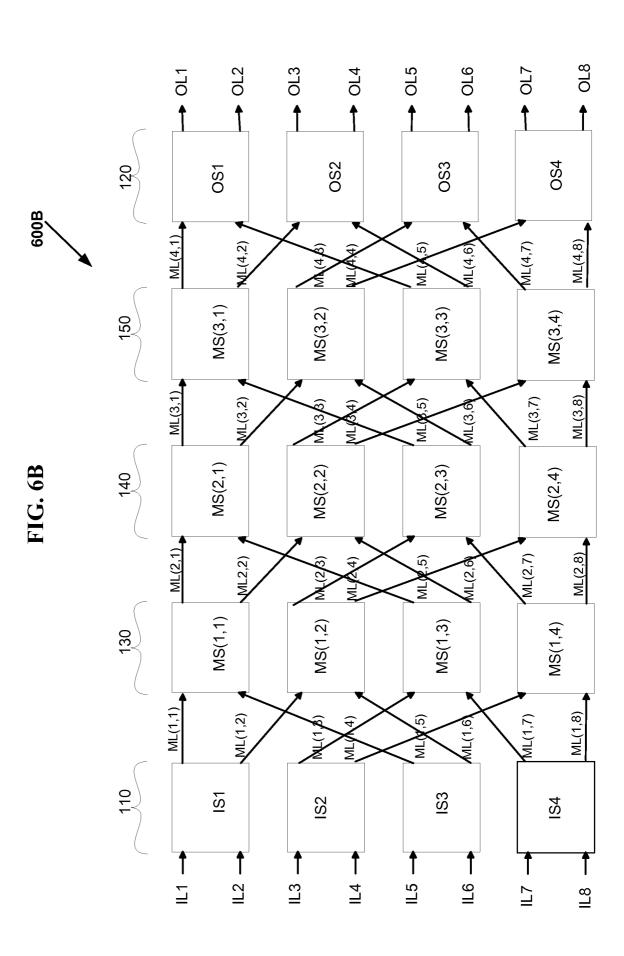

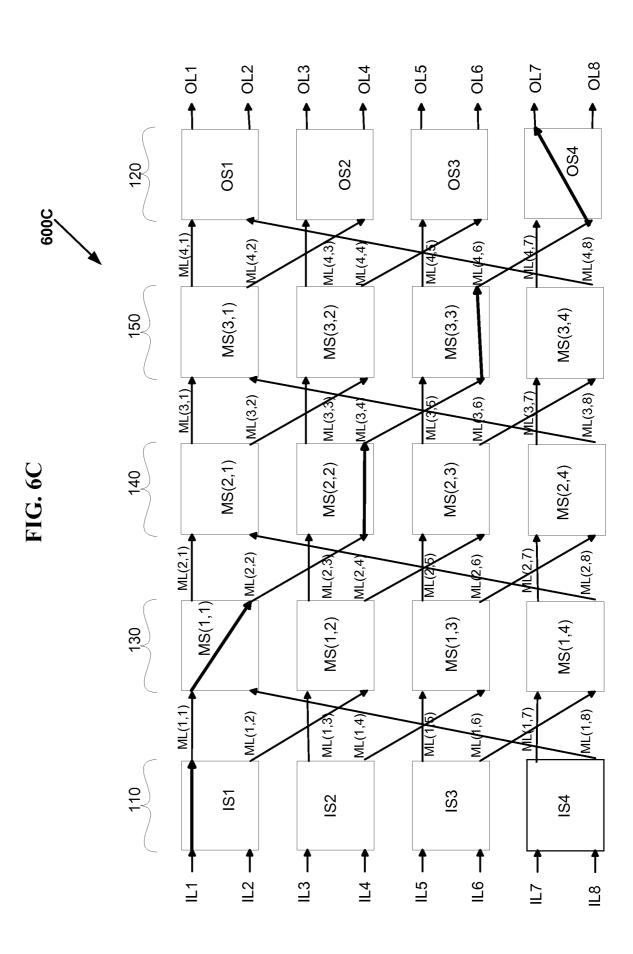

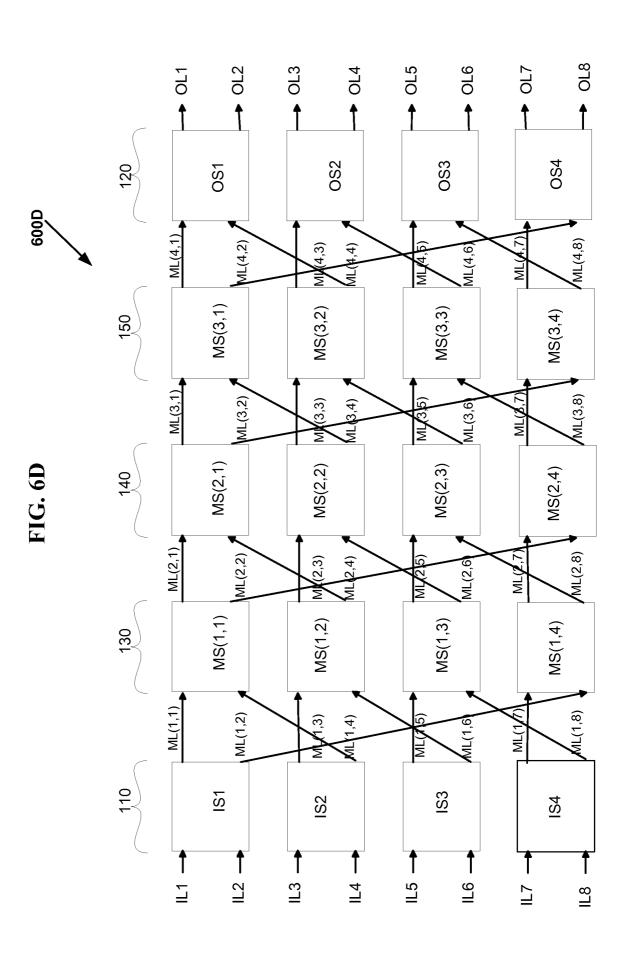

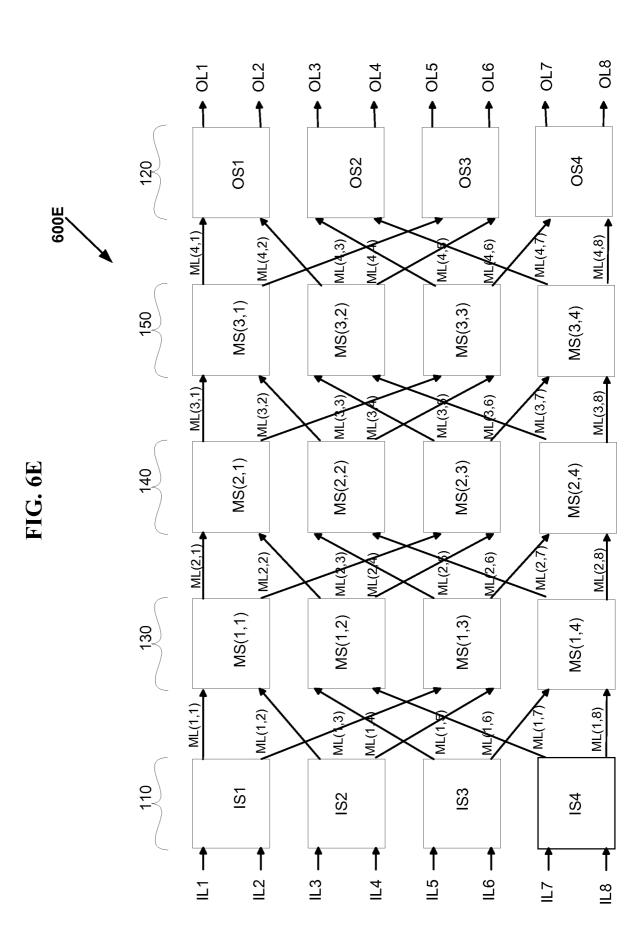

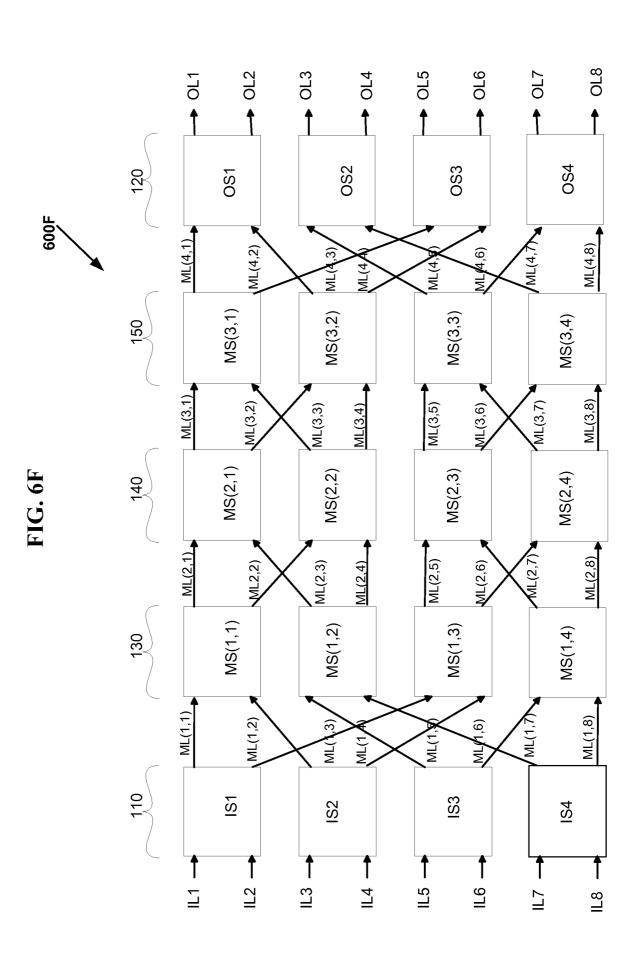

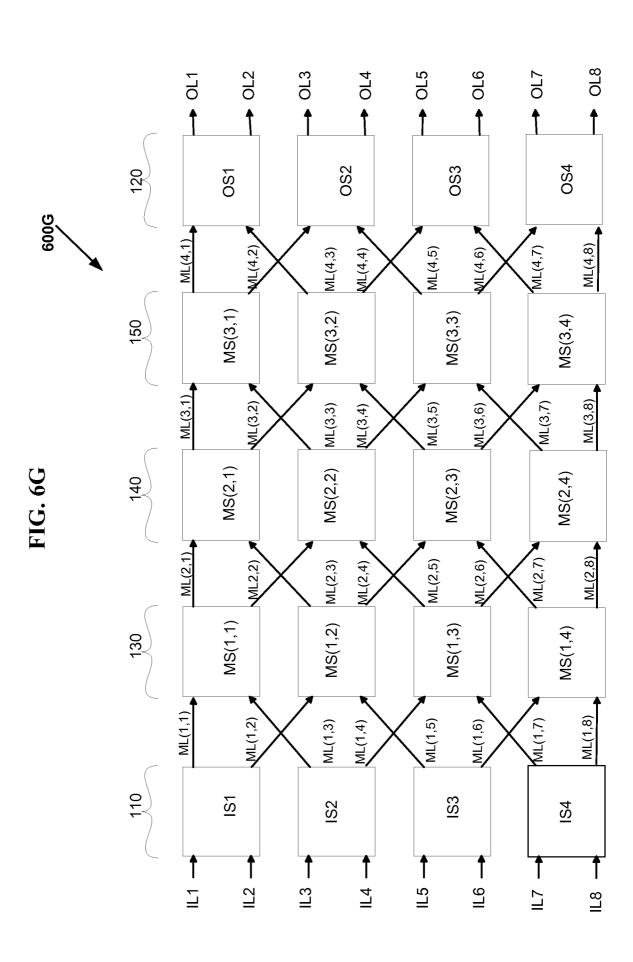

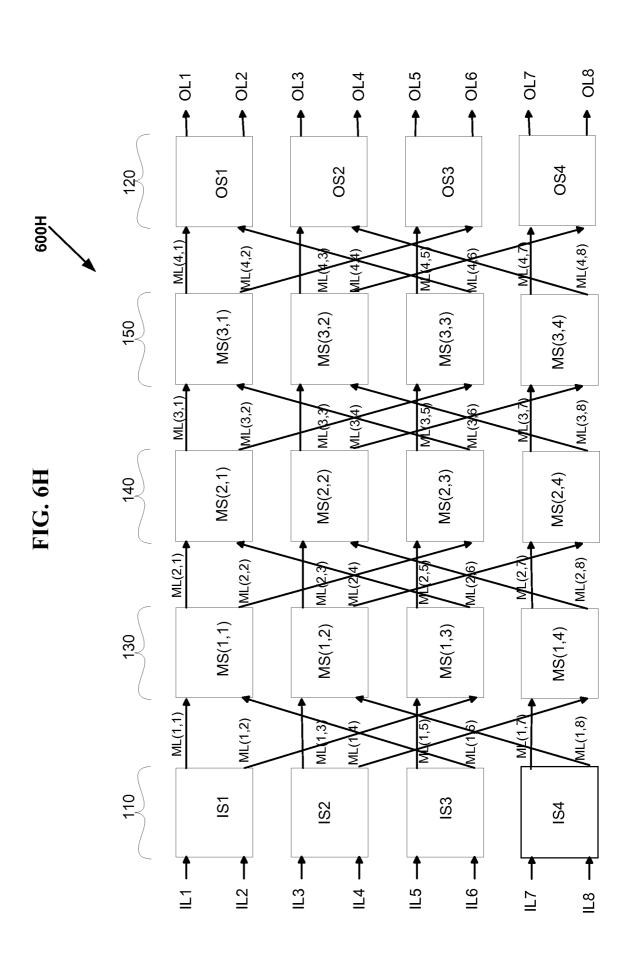

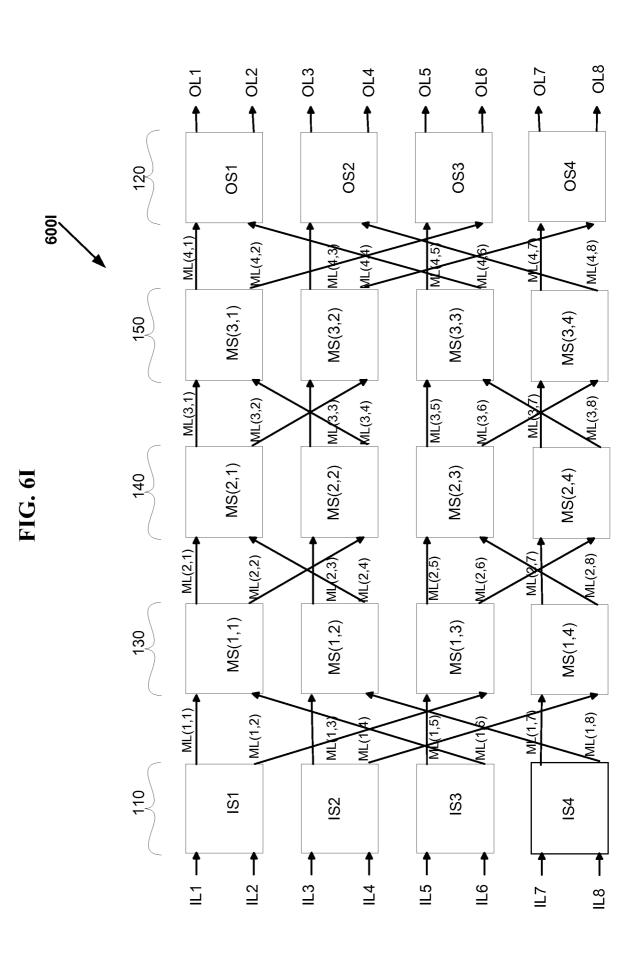

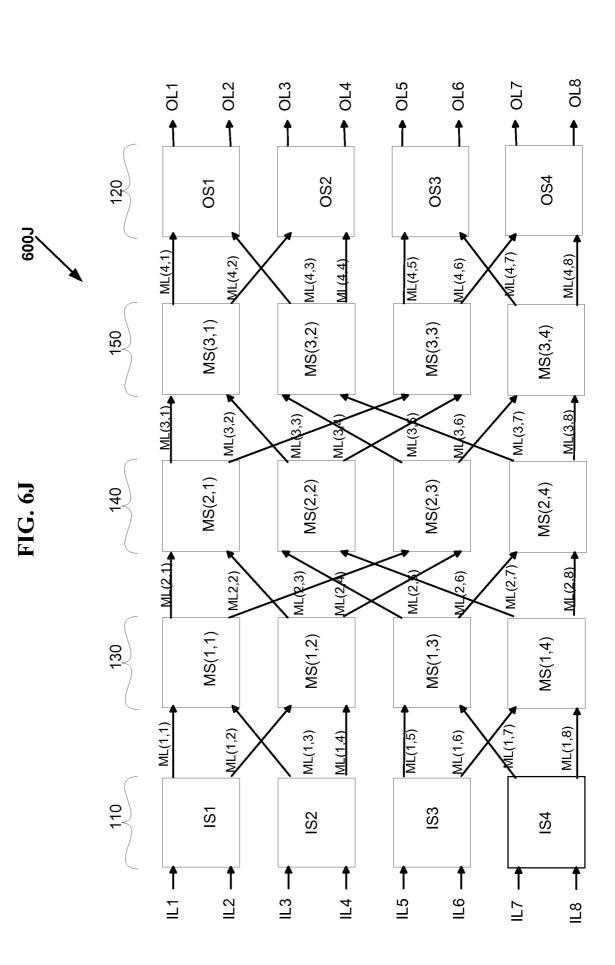

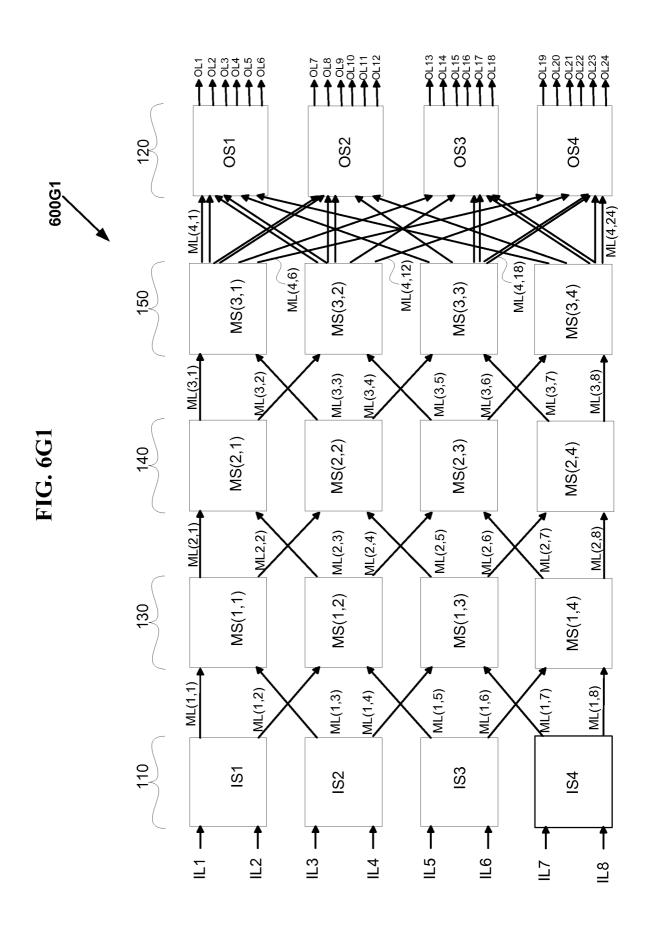

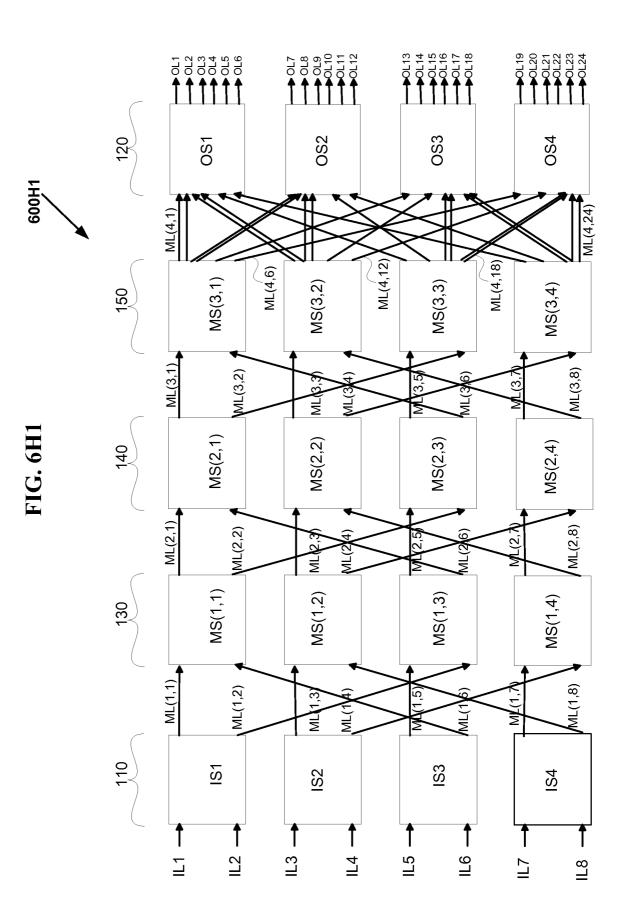

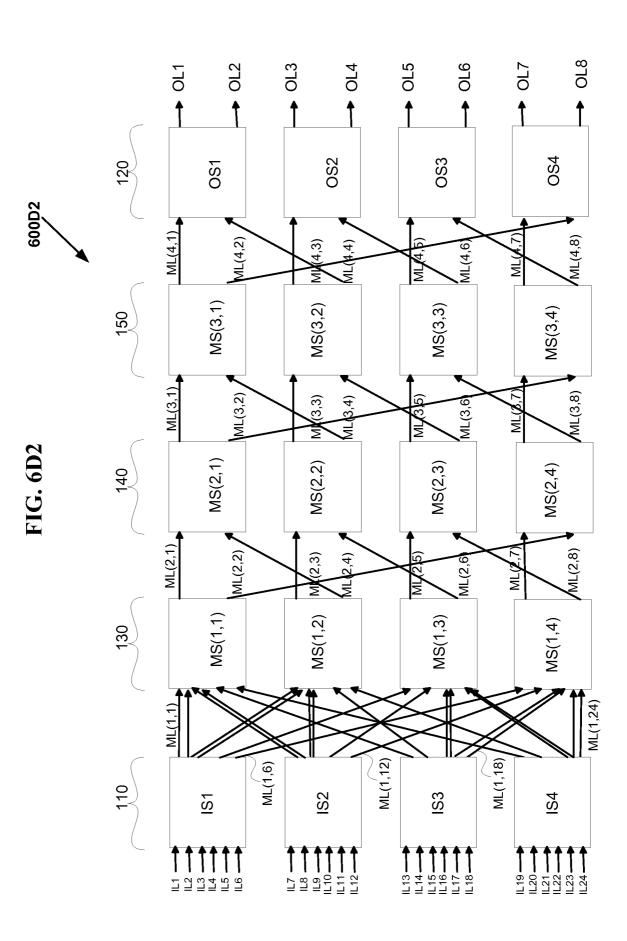

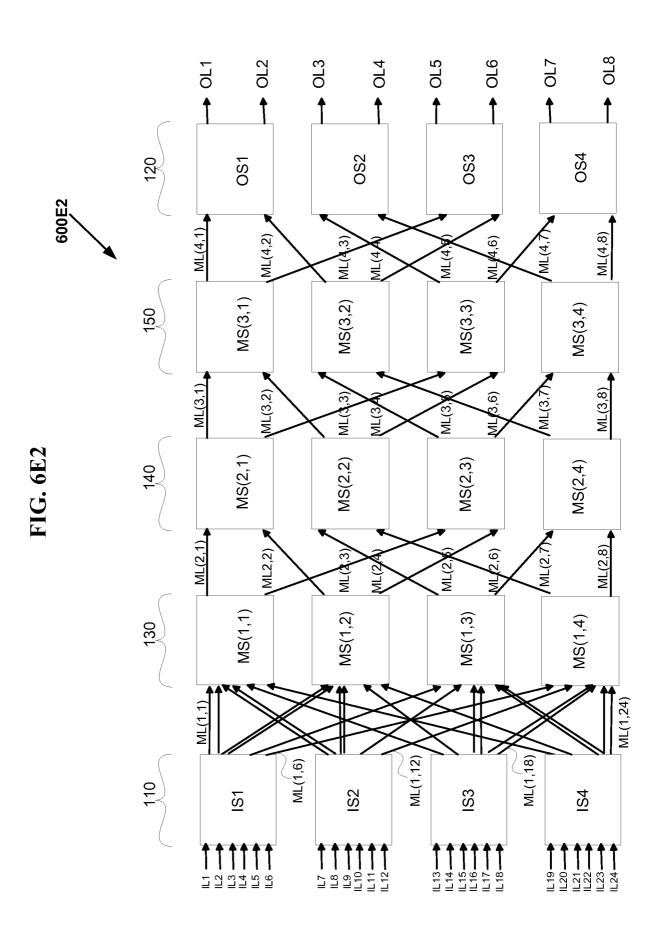

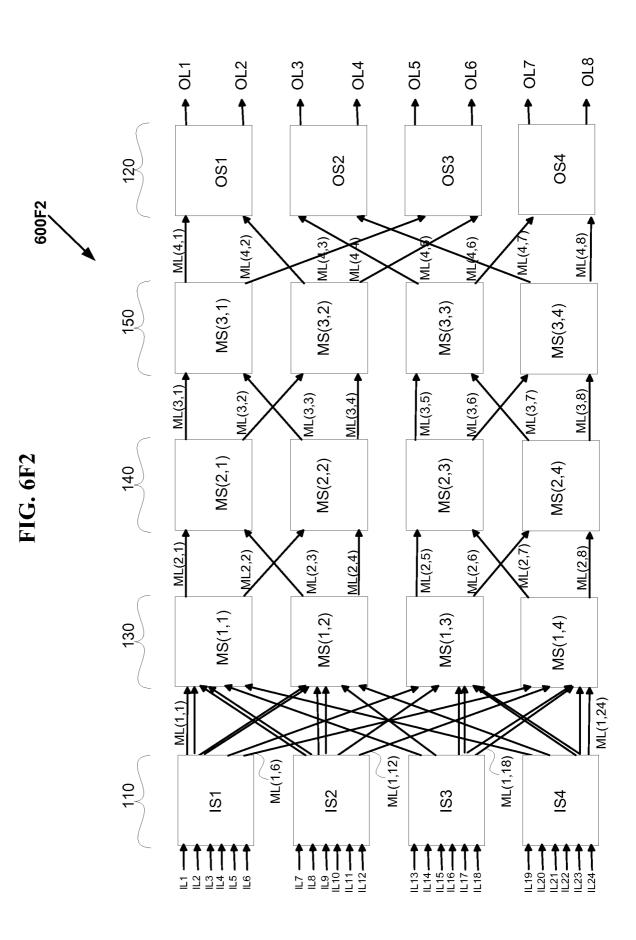

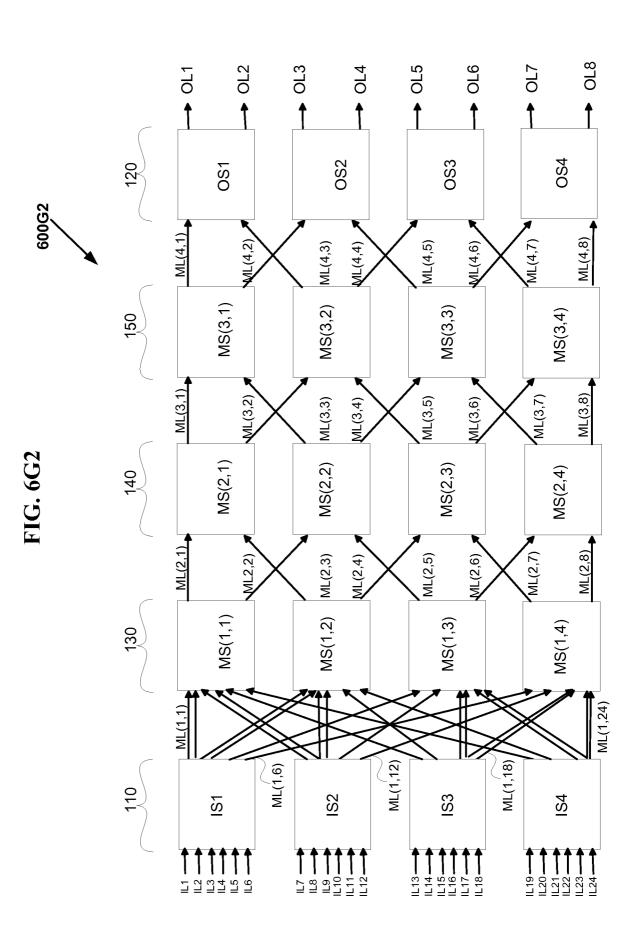

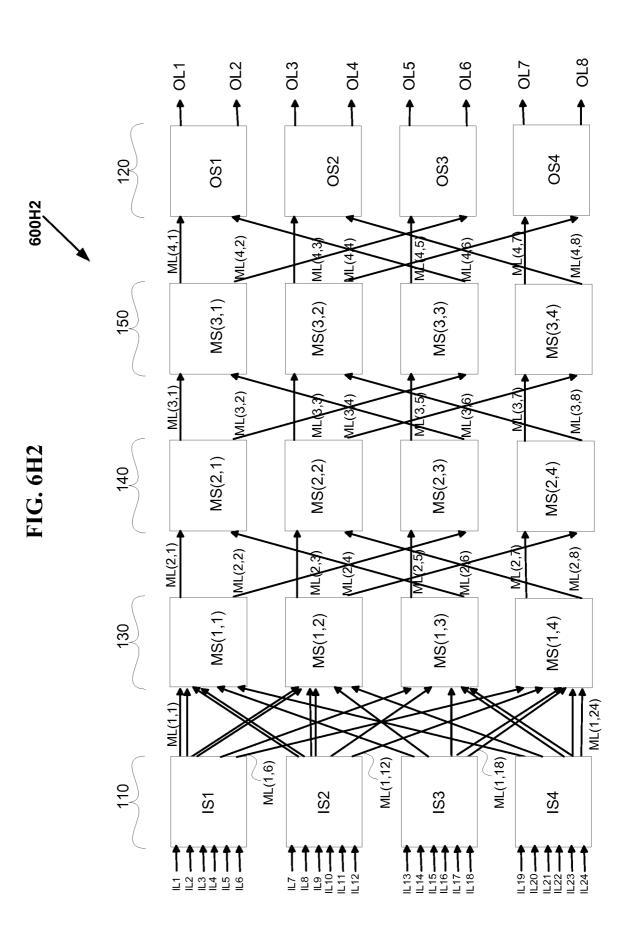

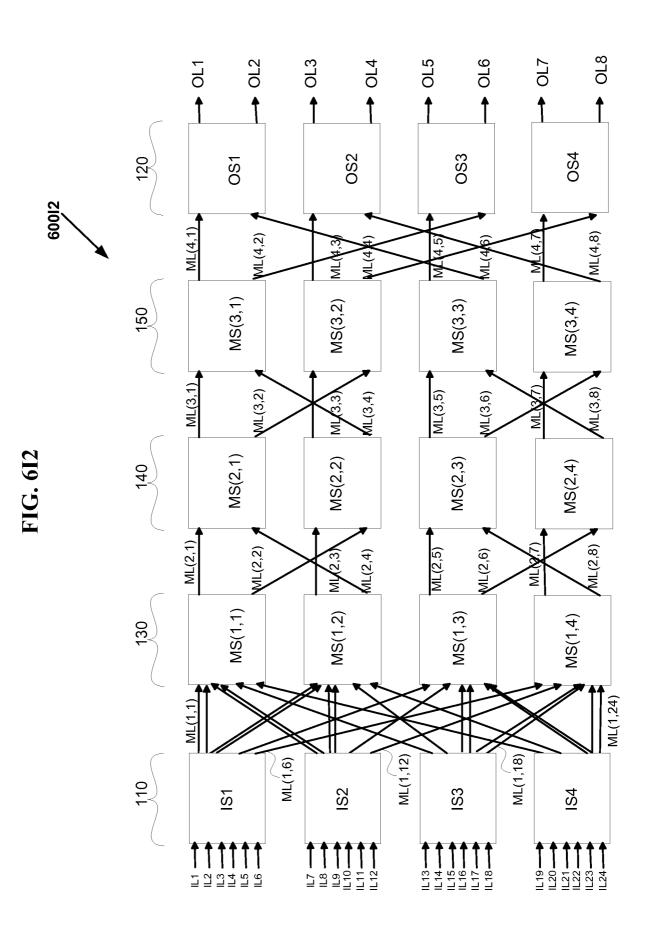

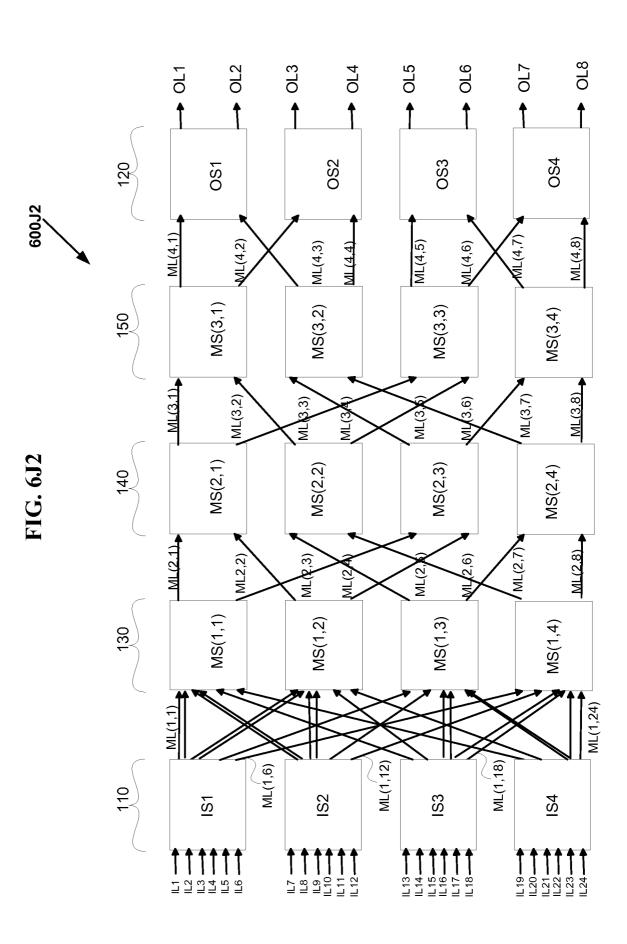

stages 130, 140, and 150 is shown where input stage 110 consists of four, two by four switches IS1-IS4 and output stage 120 consists of four, four by two switches OS1-OS4. And all the middle stages namely middle stage 130 consists of eight, two by two switches MS(1,1) - MS(1,8), middle stage 140 consists of eight, two by two switches MS(2,1) - MS(2,8), and middle stage 150 consists of eight, two by two switches MS(3,1) - MS(3,8).

Such a network can be operated in strictly non-blocking manner for unicast connections, because the switches in the input stage 110 are of size two by four, the switches in output stage 120 are of size four by two, and there are eight switches in each of middle stage 130, middle stage 140 and middle stage 150. Such a network can be

10 operated in rearrangeably non-blocking manner for multicast connections, because the switches in the input stage 110 are of size two by four, the switches in output stage 120 are of size four by two, and there are eight switches in each of middle stage 130, middle stage 140 and middle stage 150.

In one embodiment of this network each of the input switches IS1-IS4 and output switches OS1-OS4 are crossbar switches. The number of switches of input stage 110 and of output stage 120 can be denoted in general with the variable  $\frac{N}{d}$ , where N is the total number of inlet links or outlet links. The number of middle switches in each middle stage is denoted by  $2 \times \frac{N}{d}$ . The size of each input switch IS1-IS4 can be denoted in general with the notation d \* 2d and each output switch OS1-OS4 can be denoted in general with

- 20 the notation 2d \* d. Likewise, the size of each switch in any of the middle stages can be denoted as d \* d. A switch as used herein can be either a crossbar switch, or a network of switches each of which in turn may be a crossbar switch or a network of switches. A symmetric multi-stage network can be represented with the notation V(N, d, s), where N represents the total number of inlet links of all input switches (for example the links

- 25 IL1-IL8), *d* represents the inlet links of each input switch or outlet links of each output switch, and *s* is the ratio of number of outgoing links from each input switch to the inlet links of each input switch. Although it is not necessary that there be the same number of inlet links IL1-IL8 as there are outlet links OL1-OL8, in a symmetrical network they are the same.

14

#### WO 2008/109756

#### 15

#### PCT/US2008/056064

Each of the  $\frac{N}{d}$  input switches IS1 – IS4 are connected to exactly 2×d switches in middle stage 130 through 2×d links (for example input switch IS1 is connected to middle switches MS(1,1), MS(1,2), MS(1,5) and MS(1,6) through the links ML(1,1), ML(1,2), ML(1,3) and ML(1,4) respectively).

Similarly each of the

$$2 \times \frac{N}{d}$$

middle switches MS(2,1) – MS(2,8) in the middle stage 140 are connected from exactly *d* switches in middle stage 130 through *d* links (for example the links ML(2,1) and ML(2,6) are connected to the middle switch MS(2,1)

15 exactly *d* switches in middle stage 150 through *d* links (for example the links ML(3,1) and ML(3,2) are connected from middle switch MS(2,1) to middle switch MS(3,1) and MS(3,3) respectively).

from middle switches MS(1,1) and MS(1,3) respectively) and also are connected to

Similarly each of the  $2 \times \frac{N}{d}$  middle switches MS(3,1) – MS(3,8) in the middle

stage 150 are connected from exactly d switches in middle stage 140 through d links

(for example the links ML(3,1) and ML(3,6) are connected to the middle switch MS(3,1) from middle switches MS(2,1) and MS(2,3) respectively) and also are connected to exactly d output switches in output stage 120 through d links (for example the links ML(4,1) and ML(4,2) are connected to output switches OS1 and OS2 respectively from middle switches MS(3,1)).

#### WO 2008/109756

#### 16

PCT/US2008/056064

Each of the  $\frac{N}{d}$  output switches OS1 – OS4 are connected from exactly 2×*d* switches in middle stage 150 through 2×*d* links (for example output switch OS1 is connected from middle switches MS(3,1), MS(3,2), MS(3,5) and MS(3,6) through the links ML(4,1), ML(4,3), ML(4,9) and ML(4,11) respectively).

Finally the connection topology of the network 100A shown in FIG. 1A is known to be back to back inverse Benes connection topology.

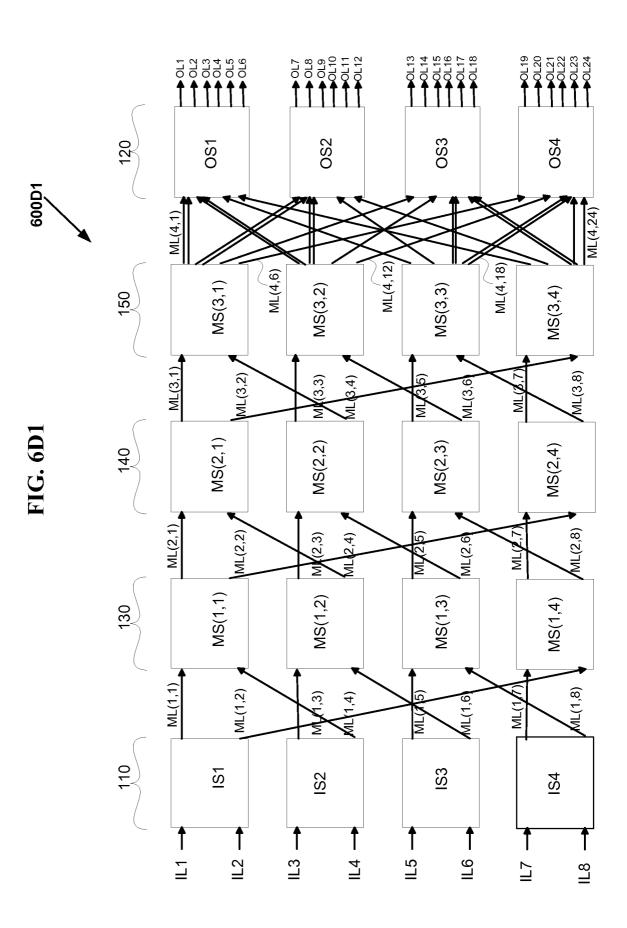

Referring to FIG. 1A1, in another embodiment of network V(N, d, s), an exemplary symmetrical multi-stage network 100A1 with five stages of thirty two switches for satisfying communication requests, such as setting up a telephone call or a

- 10 data call, or a connection between configurable logic blocks, between an input stage 110 and output stage 120 via middle stages 130, 140, and 150 is shown where input stage 110 consists of four, two by four switches IS1-IS4 and output stage 120 consists of four, four by two switches OS1-OS4. And all the middle stages namely middle stage 130 consists of eight, two by two switches MS(1,1) MS(1,8), middle stage 140 consists of eight, two by

- 15 two switches MS(2,1) MS(2,8), and middle stage 150 consists of eight, two by two switches MS(3,1) - MS(3,8).

Such a network can be operated in strictly non-blocking manner for unicast connections, because the switches in the input stage 110 are of size two by four, the switches in output stage 120 are of size four by two, and there are eight switches in each

20 of middle stage 130, middle stage 140 and middle stage 150. Such a network can be operated in rearrangeably non-blocking manner for multicast connections, because the switches in the input stage 110 are of size two by four, the switches in output stage 120 are of size four by two, and there are eight switches in each of middle stage 130, middle stage 140 and middle stage 150.

In one embodiment of this network each of the input switches IS1-IS4 and output switches OS1-OS4 are crossbar switches. The number of switches of input stage 110 and of output stage 120 can be denoted in general with the variable  $\frac{N}{d}$ , where N is the total

5

#### WO 2008/109756

#### 17

#### PCT/US2008/056064

number of inlet links or outlet links. The number of middle switches in each middle stage is denoted by  $2 \times \frac{N}{d}$ . The size of each input switch IS1-IS4 can be denoted in general with the notation d \* 2d and each output switch OS1-OS4 can be denoted in general with the notation 2d \* d. Likewise, the size of each switch in any of the middle stages can be

- 5 denoted as d \* d. A switch as used herein can be either a crossbar switch, or a network of switches each of which in turn may be a crossbar switch or a network of switches. The symmetric multi-stage network of FIG. 1A1 is also the network of the type V(N, d, s), where N represents the total number of inlet links of all input switches (for example the links IL1-IL8), d represents the inlet links of each input switch or outlet links of each

- 10 output switch, and *s* is the ratio of number of outgoing links from each input switch to the inlet links of each input switch. Although it is not necessary that there be the same number of inlet links IL1-IL8 as there are outlet links OL1-OL8, in a symmetrical network they are the same.

Each of the

$$\frac{N}{d}$$

input switches IS1 – IS4 are connected to exactly  $2 \times d$  switches

in middle stage 130 through 2×d links (for example input switch IS1 is connected to middle switches MS(1,1), MS(1,2), MS(1,5) and MS(1,6) through the links ML(1,1), ML(1,2), ML(1,3) and ML(1,4) respectively).

Each of the  $2 \times \frac{N}{d}$  middle switches MS(1,1) – MS(1,8) in the middle stage 130

are connected from exactly d input switches through d links (for example the links 20 ML(1,1) and ML(1,9) are connected to the middle switch MS(1,1) from input switch IS1 and IS3 respectively) and also are connected to exactly d switches in middle stage 140 through d links (for example the links ML(2,1) and ML(2,2) are connected from middle switch MS(1,1) to middle switch MS(2,1) and MS(2,2) respectively).

Similarly each of the  $2 \times \frac{N}{d}$  middle switches MS(2,1) – MS(2,8) in the middle

25 stage 140 are connected from exactly d switches in middle stage 130 through d links (for example the links ML(2,1) and ML(2,5) are connected to the middle switch MS(2,1)

#### PCT/US2008/056064

18

from middle switches MS(1,1) and MS(1,3) respectively) and also are connected to exactly *d* switches in middle stage 150 through *d* links (for example the links ML(3,1)and ML(3,2) are connected from middle switch MS(2,1) to middle switch MS(3,1) and MS(3,2) respectively).

Similarly each of the 2× N/d middle switches MS(3,1) – MS(3,8) in the middle stage 150 are connected from exactly d switches in middle stage 140 through d links (for example the links ML(3,1) and ML(3,5) are connected to the middle switch MS(3,1) from middle switches MS(2,1) and MS(2,3) respectively) and also are connected to exactly d output switches in output stage 120 through d links (for example the links 10 ML(4,1) and ML(4,2) are connected to output switches OS1 and OS2 respectively from middle switches MS(3,1)).

Each of the

$$\frac{N}{d}$$

output switches OS1 – OS4 are connected from exactly  $2 \times d$  switches in middle stage 150 through  $2 \times d$  links (for example output switch OS1 is

connected from middle switches MS(3,1), MS(3,3), MS(3,5) and MS(3,7) through the links ML(4,1), ML(4,5), ML(4,9) and ML(4,13) respectively).

Finally the connection topology of the network 100A1 shown in FIG. 1A1 is known to be back to back Omega connection topology.

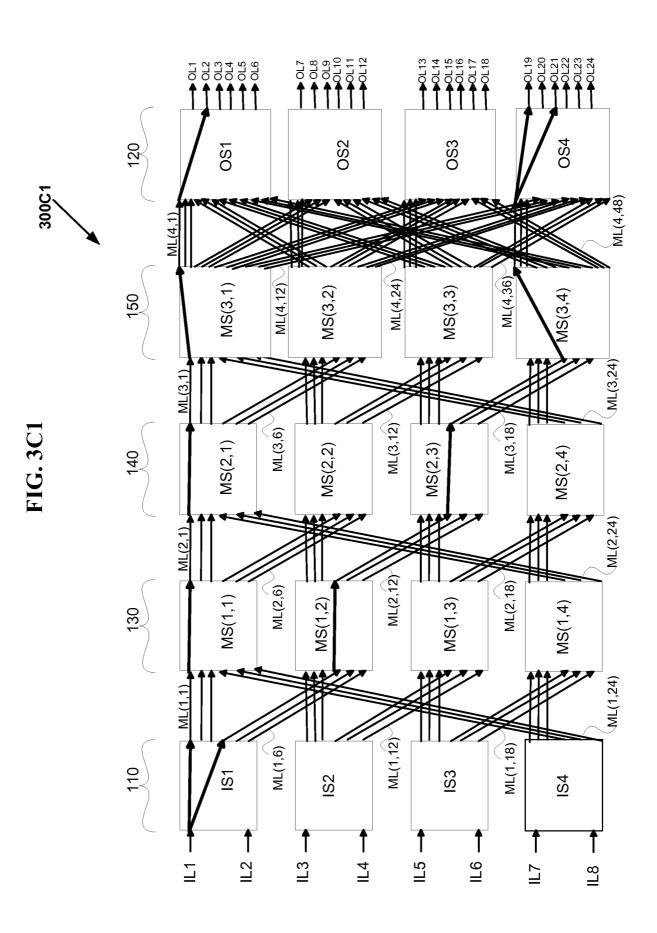

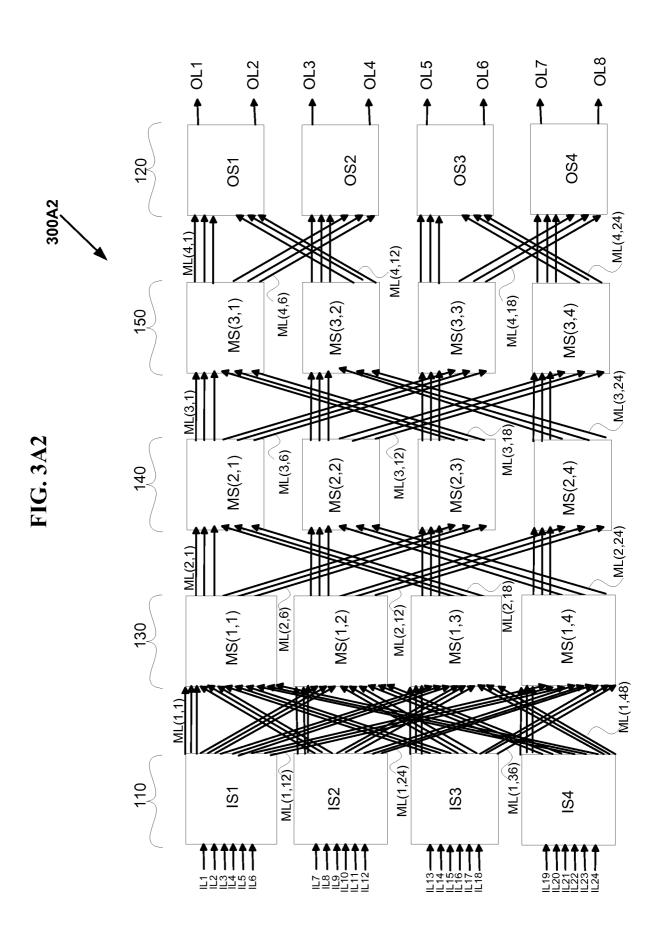

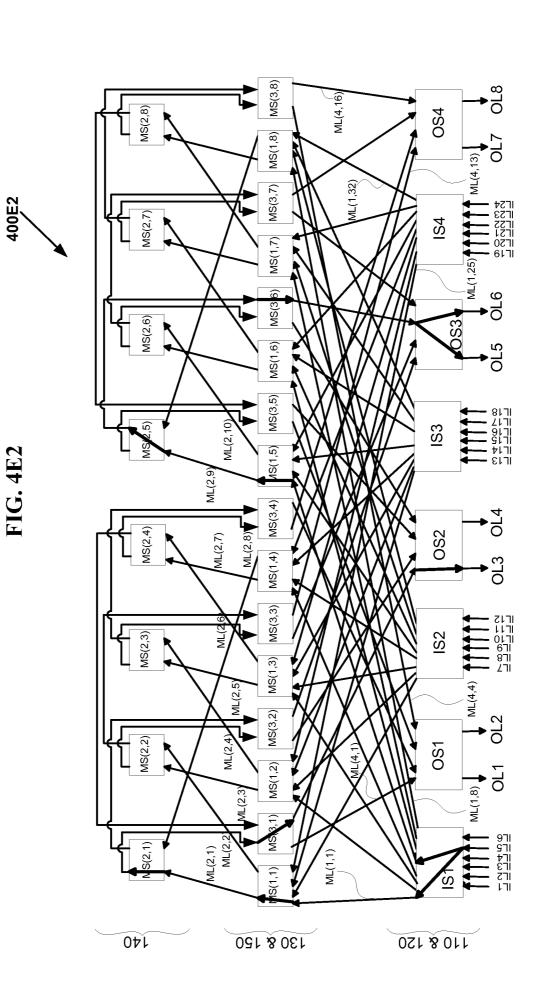

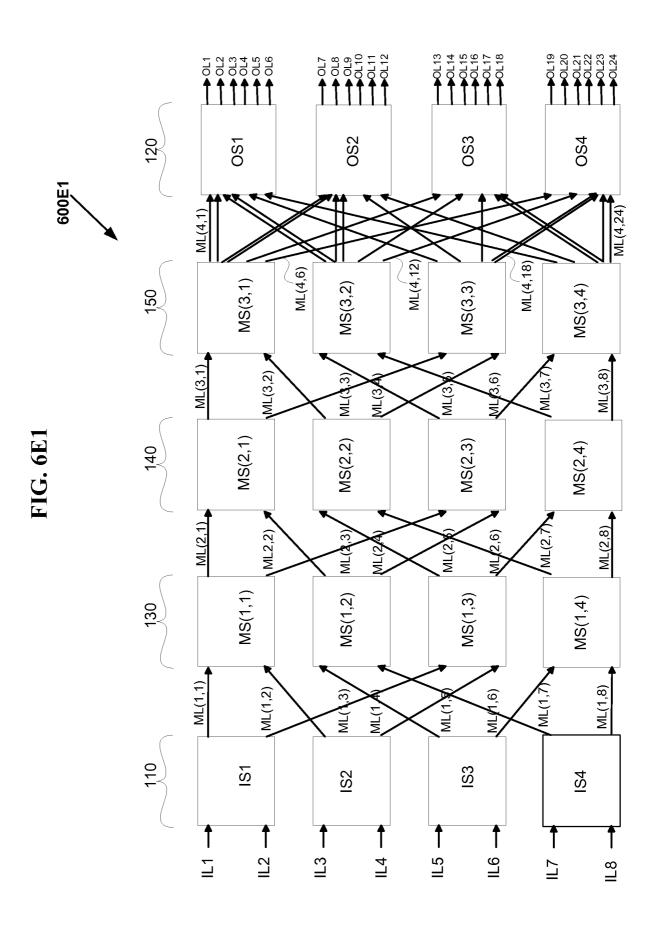

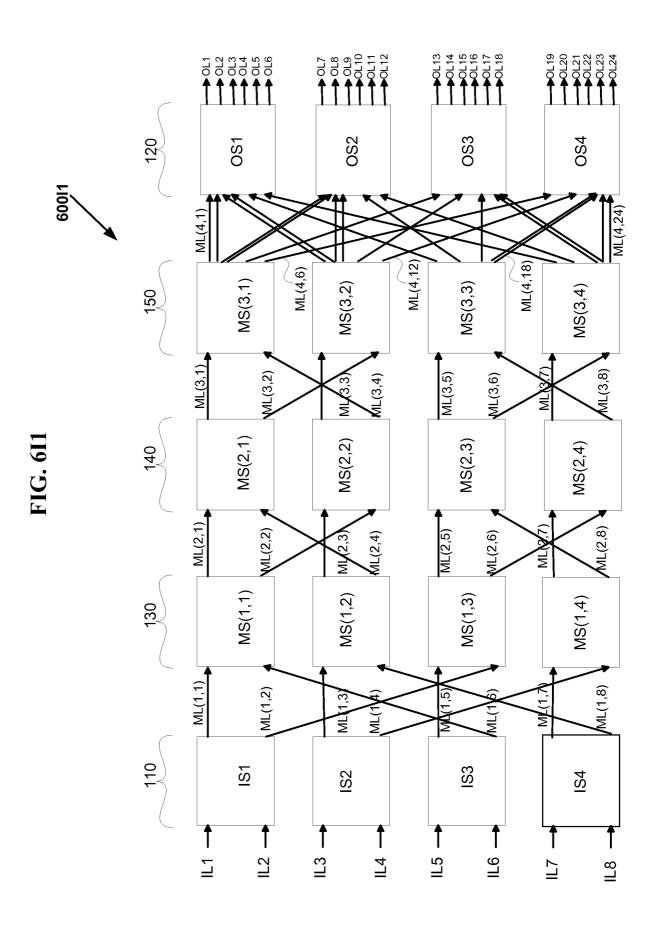

Referring to FIG. 1A2, in another embodiment of network V(N,d,s), an exemplary symmetrical multi-stage network 100A2 with five stages of thirty two

- 20 switches for satisfying communication requests, such as setting up a telephone call or a data call, or a connection between configurable logic blocks, between an input stage 110 and output stage 120 via middle stages 130, 140, and 150 is shown where input stage 110 consists of four, two by four switches IS1-IS4 and output stage 120 consists of four, four by two switches OS1-OS4. And all the middle stages namely middle stage 130 consists of

- eight, two by two switches MS(1,1) MS(1,8), middle stage 140 consists of eight, two by two switches MS(2,1) MS(2,8), and middle stage 150 consists of eight, two by two switches MS(3,1) MS(3,8).

#### WO 2008/109756

#### PCT/US2008/056064

19

Such a network can be operated in strictly non-blocking manner for unicast connections, because the switches in the input stage 110 are of size two by four, the switches in output stage 120 are of size four by two, and there are eight switches in each of middle stage 130, middle stage 140 and middle stage 150. Such a network can be

- 5 operated in rearrangeably non-blocking manner for multicast connections, because the switches in the input stage 110 are of size two by four, the switches in output stage 120 are of size four by two, and there are eight switches in each of middle stage 130, middle stage 140 and middle stage 150.

- In one embodiment of this network each of the input switches IS1-IS4 and output switches OS1-OS4 are crossbar switches. The number of switches of input stage 110 and of output stage 120 can be denoted in general with the variable  $\frac{N}{d}$ , where N is the total number of inlet links or outlet links. The number of middle switches in each middle stage is denoted by  $2 \times \frac{N}{d}$ . The size of each input switch IS1-IS4 can be denoted in general with the notation d \* 2d and each output switch OS1-OS4 can be denoted in general with

- 15 the notation 2d \* d. Likewise, the size of each switch in any of the middle stages can be denoted as d \* d. A switch as used herein can be either a crossbar switch, or a network of switches each of which in turn may be a crossbar switch or a network of switches. The symmetric multi-stage network of FIG. 1A2 is also the network of the type V(N, d, s), where N represents the total number of inlet links of all input switches (for example the

- 20 links IL1-IL8), *d* represents the inlet links of each input switch or outlet links of each output switch, and *s* is the ratio of number of outgoing links from each input switch to the inlet links of each input switch. Although it is not necessary that there be the same number of inlet links IL1-IL8 as there are outlet links OL1-OL8, in a symmetrical network they are the same.

- Each of the  $\frac{N}{d}$  input switches IS1 IS4 are connected to exactly 2×d switches in middle stage 130 through 2×d links (for example input switch IS1 is connected to middle switches MS(1,1), MS(1,2), MS(1,5) and MS(1,6) through the links ML(1,1), ML(1,2), ML(1,3) and ML(1,4) respectively).

25

#### PCT/US2008/056064

Each of the  $2 \times \frac{N}{d}$  middle switches MS(1,1) – MS(1,8) in the middle stage 130 are connected from exactly *d* input switches through *d* links (for example the links ML(1,1) and ML(1,14) are connected to the middle switch MS(1,1) from input switch IS1 and IS4 respectively) and also are connected to exactly *d* switches in middle stage 140

5 through *d* links (for example the links ML(2,1) and ML(2,2) are connected from middle switch MS(1,1) to middle switch MS(2,1) and MS(2,2) respectively).

Similarly each of the

$$2 \times \frac{N}{d}$$

middle switches MS(2,1) – MS(2,8) in the middle

stage 140 are connected from exactly d switches in middle stage 130 through d links (for example the links ML(2,1) and ML(2,8) are connected to the middle switch MS(2,1)

10 from middle switches MS(1,1) and MS(1,4) respectively) and also are connected to exactly *d* switches in middle stage 150 through *d* links (for example the links ML(3,1) and ML(3,2) are connected from middle switch MS(2,1) to middle switch MS(3,1) and MS(3,2) respectively).

Similarly each of the

$$2 \times \frac{N}{d}$$

middle switches MS(3,1) – MS(3,8) in the middle

stage 150 are connected from exactly *d* switches in middle stage 140 through *d* links (for example the links ML(3,1) and ML(3,8) are connected to the middle switch MS(3,1) from middle switches MS(2,1) and MS(2,4) respectively) and also are connected to exactly *d* output switches in output stage 120 through *d* links (for example the links ML(4,1) and ML(4,2) are connected to output switches OS1 and OS2 respectively from middle switches MS(3,1)).

Each of the  $\frac{N}{d}$  output switches OS1 – OS4 are connected from exactly  $2 \times d$

switches in middle stage 150 through  $2 \times d$  links (for example output switch OS1 is connected from middle switches MS(3,1), MS(3,4), MS(3,5) and MS(3,8) through the links ML(4,1), ML(4,2), ML(4,3) and ML(4,4) respectively).

Finally the connection topology of the network 100A2 shown in FIG. 1A2 is hereinafter called nearest neighbor connection topology.

PCT/US2008/056064

#### WO 2008/109756

#### 21

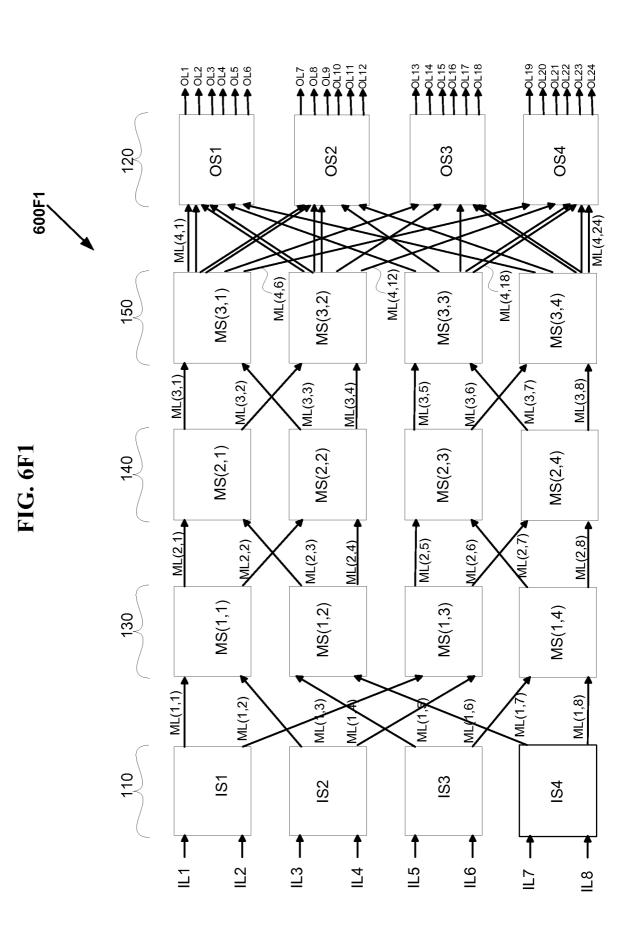

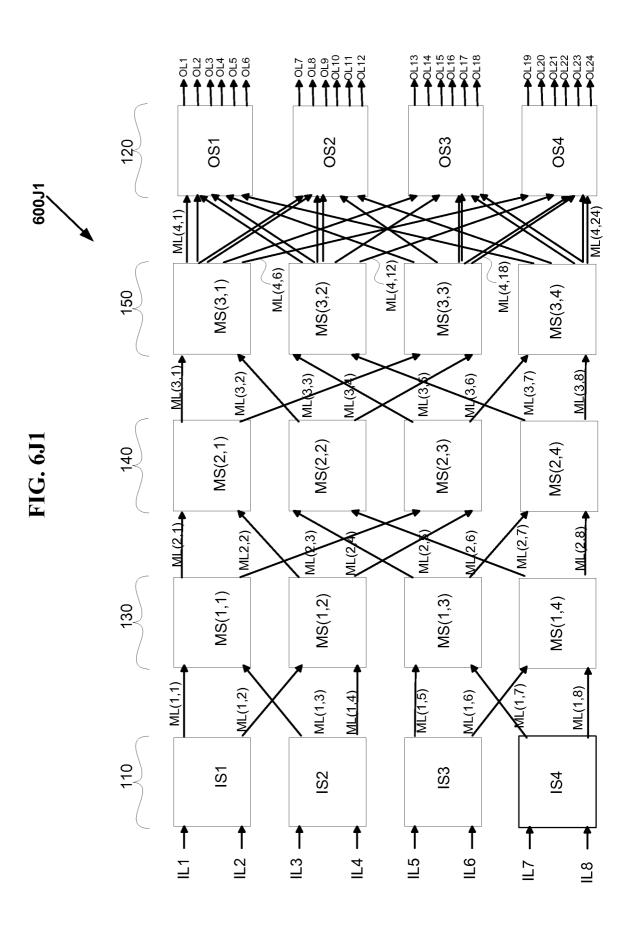

In the three embodiments of FIG. 1A, FIG. 1A1 and FIG. 1A2 the connection topology is different. That is the way the links ML(1,1) - ML(1,16), ML(2,1) - ML(2,16), ML(3,1) - ML(3,16), and ML(4,1) - ML(4,16) are connected between the respective stages is different. Even though only three embodiments are illustrated, in general, the

- 5 network V(N,d,s) can comprise any arbitrary type of connection topology. For example the connection topology of the network V(N,d,s) may be back to back Benes networks, Delta Networks and many more combinations. The applicant notes that the fundamental property of a valid connection topology of the V(N,d,s) network is, when no connections are setup in the network, a connection from any inlet link to any outlet link

- 10 can be setup. Based on this property numerous embodiments of the network V(N,d,s) can be built. The embodiments of FIG. 1A, FIG. 1A1, and FIG. 1A2 are only three examples of network V(N,d,s).

In the three embodiments of FIG. 1A, FIG. 1A1 and FIG. 1A2, each of the links ML(1,1) - ML(1,16), ML(2,1) - ML(2,16), ML(3,1) - ML(3,16) and ML(4,1) - ML(4,1)

- ML(4,16) are either available for use by a new connection or not available if currently used by an existing connection. The input switches IS1-IS4 are also referred to as the network input ports. The input stage 110 is often referred to as the first stage. The output switches OS1-OS4 are also referred to as the network output ports. The output stage 120 is often referred to as the last stage. The middle stage switches MS(1,1) MS(1,8),

- 20 MS(2,1) MS(2,8), and MS(3,1) MS(3,8) are referred to as middle switches or middle ports.

In the example illustrated in FIG. 1A (or in FIG1A1, or in FIG. 1A2), a fan-out of four is possible to satisfy a multicast connection request if input switch is IS2, but only two switches in middle stage 130 will be used. Similarly, although a fan-out of three is possible for a multicast connection request if the input switch is IS1, again only a fan-out of two is used. The specific middle switches that are chosen in middle stage 130 when selecting a fan-out of two is irrelevant so long as at most two middle switches are selected to ensure that the connection request is satisfied. In essence, limiting the fan-out from input switch to no more than two middle switches permits the network 100A (or 100A1,

#### WO 2008/109756

#### 22

#### PCT/US2008/056064

or 100A2), to be operated in rearrangeably nonblocking manner in accordance with the invention.

The connection request of the type described above can be unicast connection request, a multicast connection request or a broadcast connection request, depending on

- 5 the example. In case of a unicast connection request, a fan-out of one is used, i.e. a single middle stage switch in middle stage 130 is used to satisfy the request. Moreover, although in the above-described embodiment a limit of two has been placed on the fanout into the middle stage switches in middle stage 130, the limit can be greater depending on the number of middle stage switches in a network (while maintaining the

- 10 rearrangeably nonblocking nature of operation of the network for multicast connections). However any arbitrary fan-out may be used within any of the middle stage switches and the output stage switches to satisfy the connection request.

#### **Generalized Symmetric RNB Embodiments:**

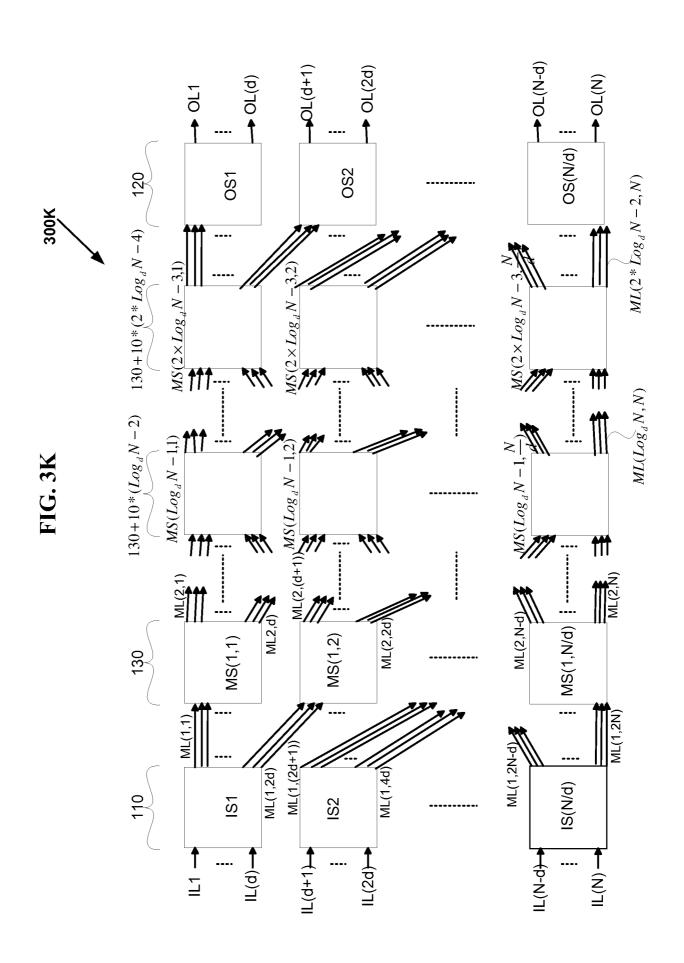

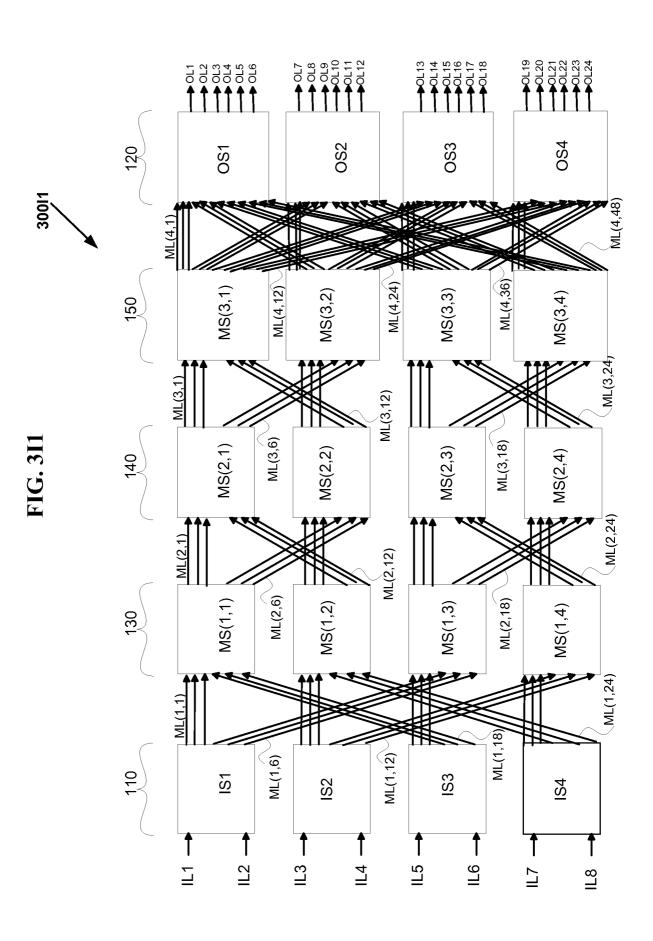

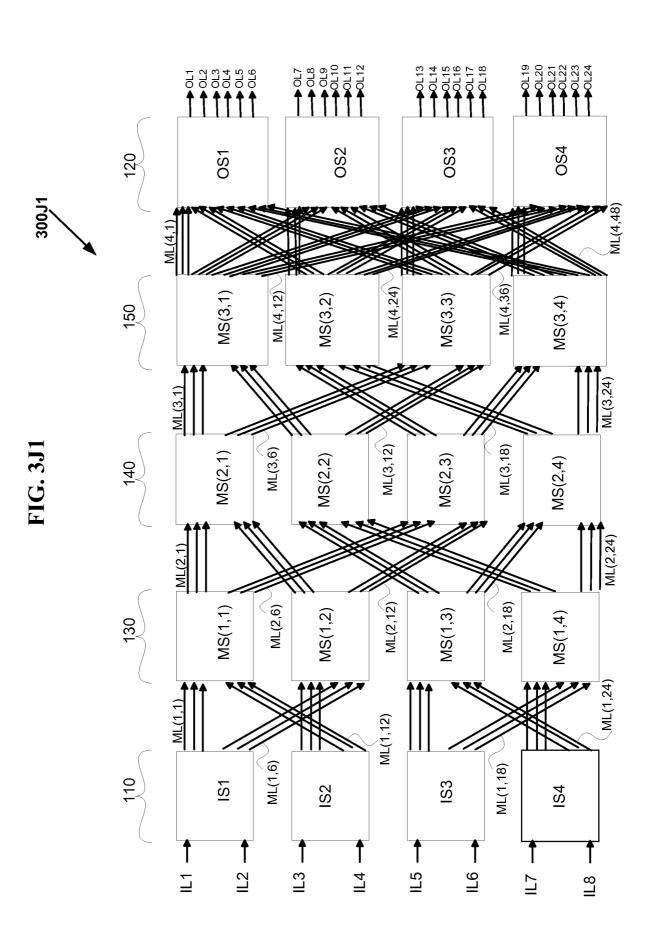

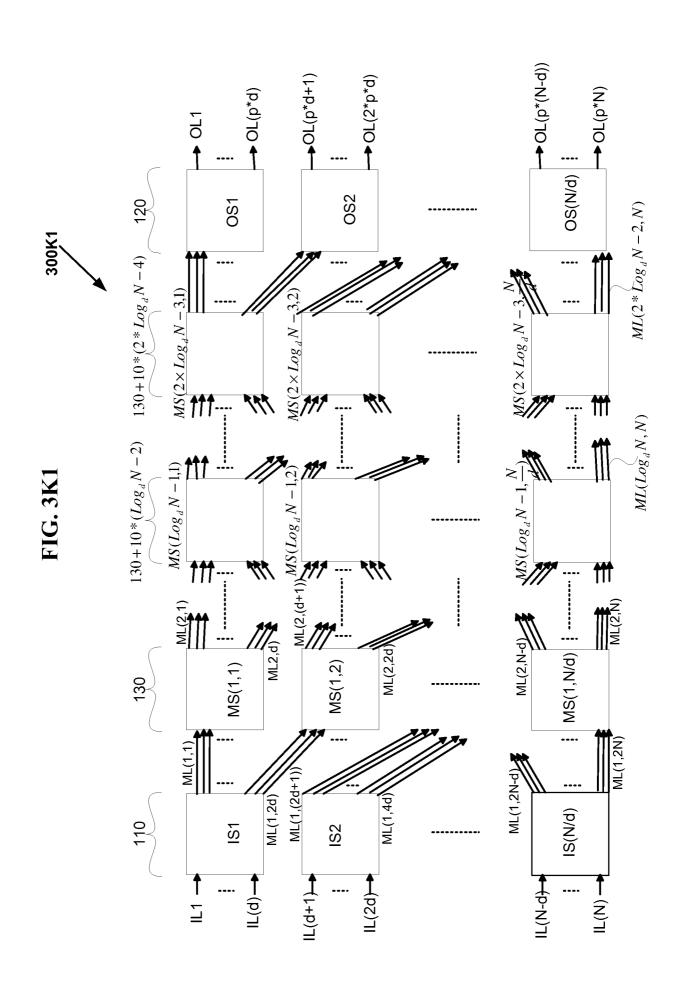

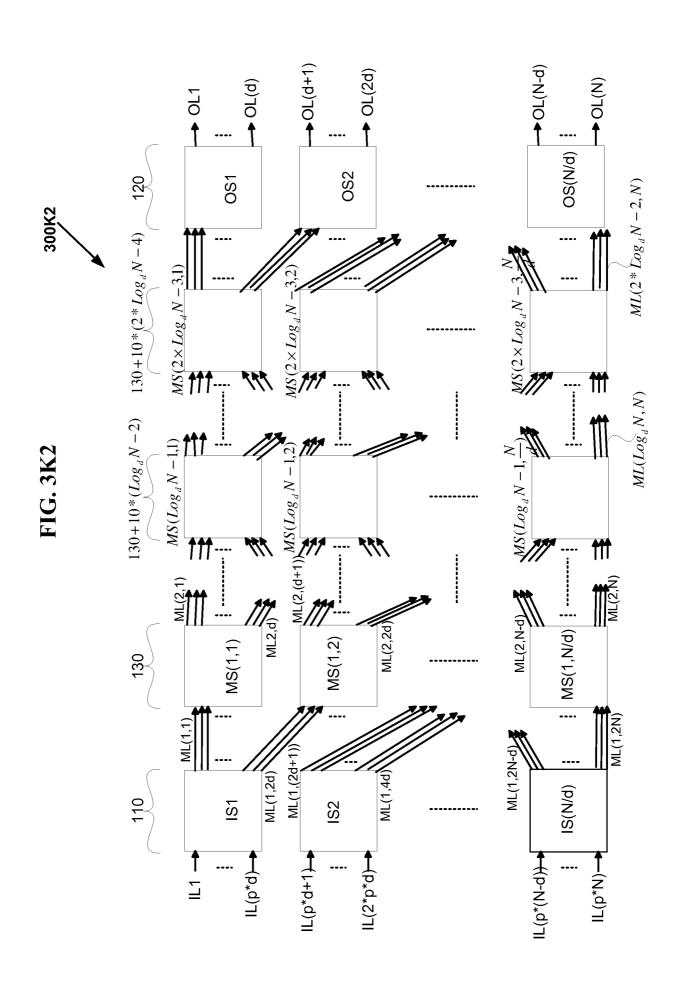

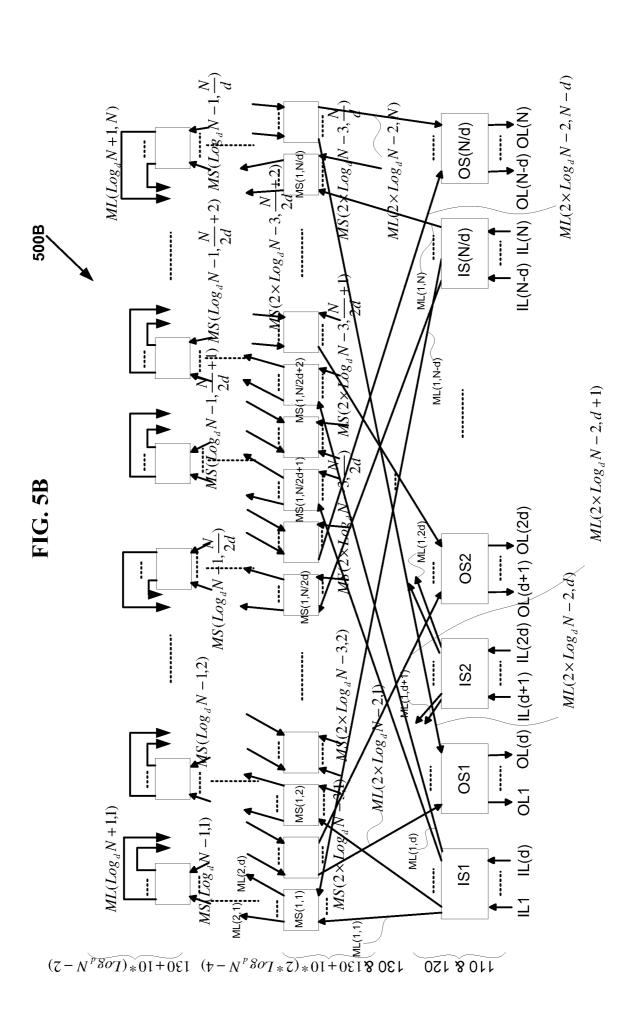

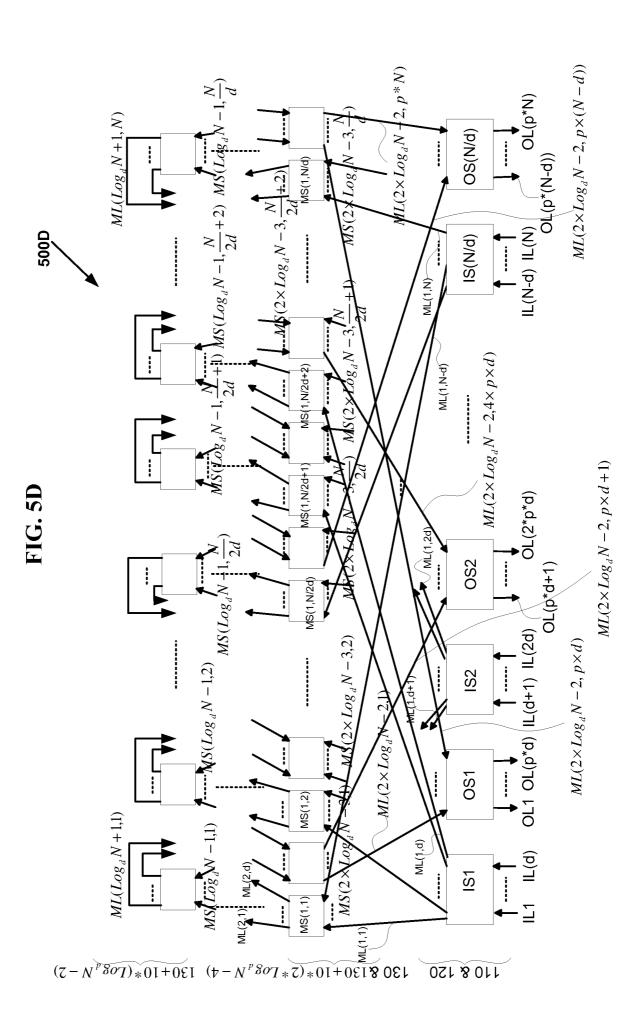

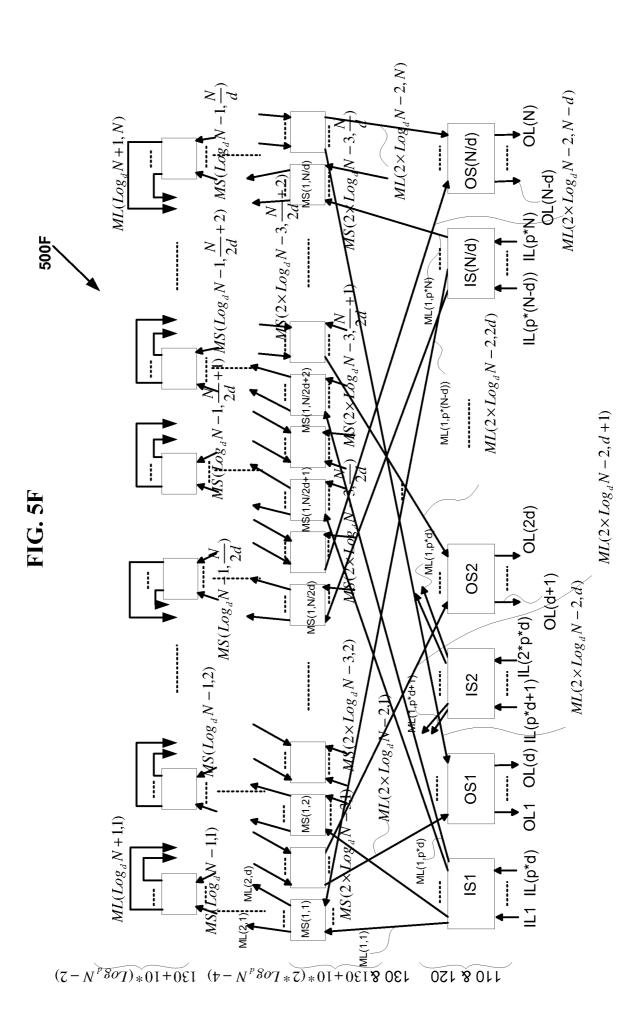

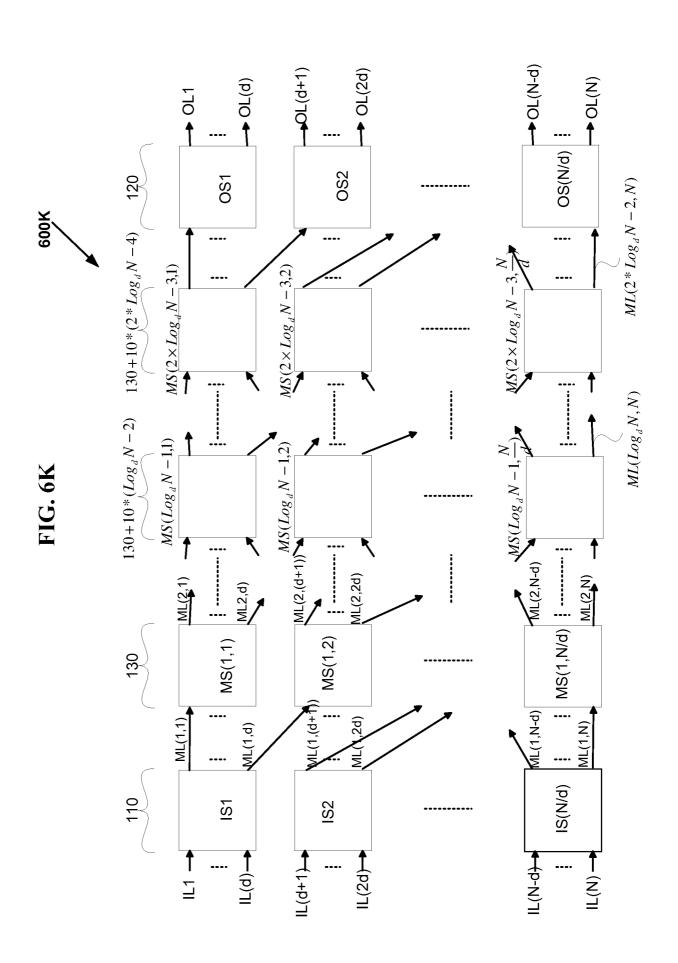

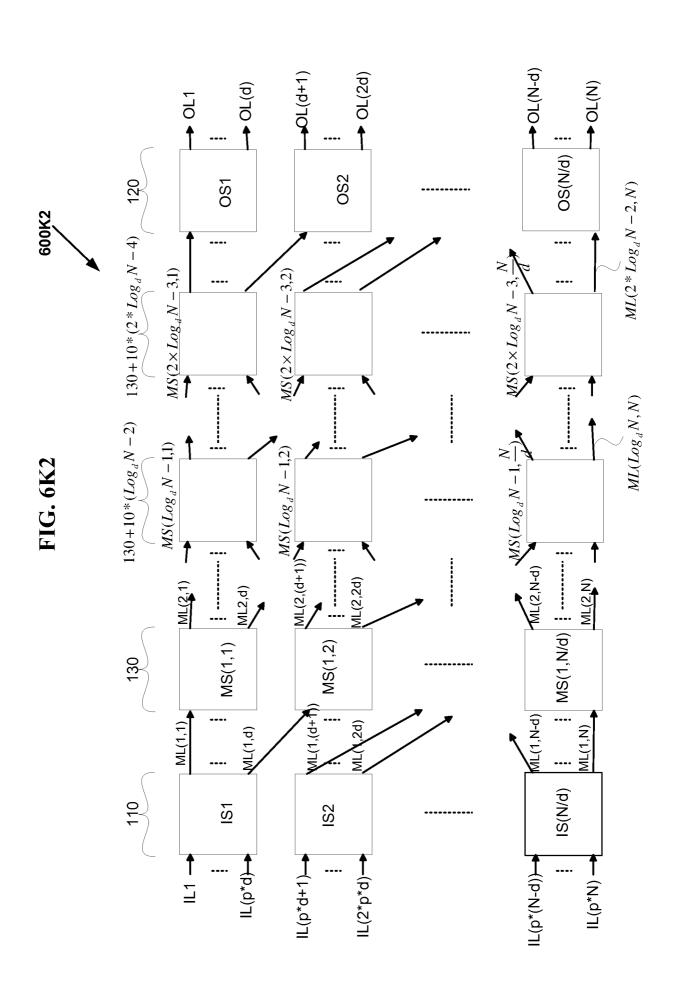

Network 100B of FIG. 1B is an example of general symmetrical multi-stage 15 network V(N,d,s) with  $(2 \times \log_d N) - 1$  stages. The general symmetrical multi-stage network V(N,d,s) can be operated in rearrangeably nonblocking manner for multicast when s = 2 according to the current invention. Also the general symmetrical multi-stage network V(N,d,s) can be operated in strictly nonblocking manner for unicast if s = 2 according to the current invention (And in the example of FIG. 1B, s = 2). The

- 20 general symmetrical multi-stage network V(N, d, s) with  $(2 \times \log_d N) 1$  stages has dinlet links for each of  $\frac{N}{d}$  input switches IS1-IS(N/d) (for example the links IL1-IL(d) to the input switch IS1) and  $2 \times d$  outgoing links for each of  $\frac{N}{d}$  input switches IS1-IS(N/d) (for example the links ML(1,1) - ML(1,2d) to the input switch IS1). There are d outlet links for each of  $\frac{N}{d}$  output switches OS1-OS(N/d) (for example the links OL1-OL(d) to

- 25 the output switch OS1) and  $2 \times d$  incoming links for each of  $\frac{N}{d}$  output switches OS1-

20

#### 23

PCT/US2008/056064

OS(N/d) (for example  $ML(2 \times Log_d N - 2,1) - ML(2 \times Log_d N - 2,2 \times d)$  to the output switch OS1).

Each of the  $\frac{N}{d}$  input switches IS1 – IS(N/d) are connected to exactly 2×d

switches in middle stage 130 through  $2 \times d$  links (for example input switch IS1 is

5 connected to middle switches MS(1,1) - MS(1,d) through the links ML(1,1) - ML(1,d) and to middle switches MS(1,N/d+1) - MS(1,{N/d}+d) through the links ML(1,d+1) -ML(1,2d) respectively.

Each of the

$$2 \times \frac{N}{d}$$

middle switches MS(1,1) – MS(1,2N/d) in the middle stage

130 are connected from exactly d input switches through d links and also are connectedto exactly d switches in middle stage 140 through d links.

Similarly each of the  $2 \times \frac{N}{d}$  middle switches  $MS(Log_d N - 1, 1)$  -

$MS(Log_d N - 1, 2 \times \frac{N}{d})$  in the middle stage  $130 + 10^*(Log_d N - 2)$  are connected from exactly *d* switches in middle stage  $130 + 10^*(Log_d N - 3)$  through *d* links and also are connected to exactly *d* switches in middle stage  $130 + 10^*(Log_d N - 1)$  through *d* links.

15 Similarly each of the

$$2 \times \frac{N}{d}$$

middle switches  $MS(2 \times Log_d N - 3, 1)$  -

$MS(2 \times Log_d N - 3, 2 \times \frac{N}{d})$  in the middle stage  $130 + 10 * (2 * Log_d N - 4)$  are connected from exactly *d* switches in middle stage  $130 + 10 * (2 * Log_d N - 5)$  through *d* links and also are connected to exactly *d* output switches in output stage 120 through *d* links.

Each of the  $\frac{N}{d}$  output switches OS1 – OS(N/d) are connected from exactly  $2 \times d$  switches in middle stage  $130+10*(2*Log_d N-4)$  through  $2 \times d$  links.

#### 24

PCT/US2008/056064

As described before, again the connection topology of a general V(N, d, s) may be any one of the connection topologies. For example the connection topology of the network V(N, d, s) may be back to back inverse Benes networks, back to back Omega networks, back to back Benes networks, Delta Networks and many more combinations.

- 5 The applicant notes that the fundamental property of a valid connection topology of the general V(N,d,s) network is, when no connections are setup in the network, a connection from any inlet link to any outlet link can be setup. Based on this property numerous embodiments of the network V(N,d,s) can be built. The embodiments of FIG. 1A, FIG. 1A1, and FIG. 1A2 are three examples of network V(N,d,s).

- 10 The general symmetrical multi-stage network V(N, d, s) can be operated in rearrangeably nonblocking manner for multicast when s = 2 according to the current invention. Also the general symmetrical multi-stage network V(N, d, s) can be operated in strictly nonblocking manner for unicast if s = 2 according to the current invention.

Every switch in the multi-stage networks discussed herein has multicast

- 15 capability. In a V(N, d, s) network, if a network inlet link is to be connected to more than one outlet link on the same output switch, then it is only necessary for the corresponding input switch to have one path to that output switch. This follows because that path can be multicast within the output switch to as many outlet links as necessary. Multicast assignments can therefore be described in terms of connections between input

- 20 switches and output switches. An existing connection or a new connection from an input switch to r' output switches is said to have fan-out r'. If all multicast assignments of a first type, wherein any inlet link of an input switch is to be connected in an output switch to at most one outlet link are realizable, then multicast assignments of a second type, wherein any inlet link of each input switch is to be connected to more than one outlet link

- in the same output switch, can also be realized. For this reason, the following discussion is limited to general multicast connections of the first type (with fan-out r',  $1 \le r' \le \frac{N}{d}$ ) although the same discussion is applicable to the second type.

#### WO 2008/109756

#### 25

#### PCT/US2008/056064

To characterize a multicast assignment, for each inlet link  $i \in \left\{1, 2, \dots, \frac{N}{d}\right\}$ , let

$I_i = O$ , where  $O \subset \left\{1, 2, ..., \frac{N}{d}\right\}$ , denote the subset of output switches to which inlet link *i*

is to be connected in the multicast assignment. For example, the network of Fig. 1A shows an exemplary five-stage network, namely V(8,2,2), with the following multicast

5 assignment  $I_1 = \{2,3\}$  and all other  $I_j = \phi$  for j = [2-8]. It should be noted that the connection  $I_1$  fans out in the first stage switch IS1 into middle switches MS(1,1) and MS(1,5) in middle stage 130, and fans out in middle switches MS(1,1) and MS(1,5) only once into middle switches MS(2,1) and MS(2,5) respectively in middle stage 140.

The connection  $I_1$  also fans out in middle switches MS(2,1) and MS(2,5) only once into middle switches MS(3,1) and MS(3,7) respectively in middle stage 150. The connection  $I_1$  also fans out in middle switches MS(3,1) and MS(3,7) only once into output switches OS2 and OS3 in output stage 120. Finally the connection  $I_1$  fans out once in the output stage switch OS2 into outlet link OL3 and in the output stage switch OS3 twice into the outlet links OL5 and OL6. In accordance with the invention, each connection can fan out in the input stage switch into at most two middle stage switches in middle stage 130.

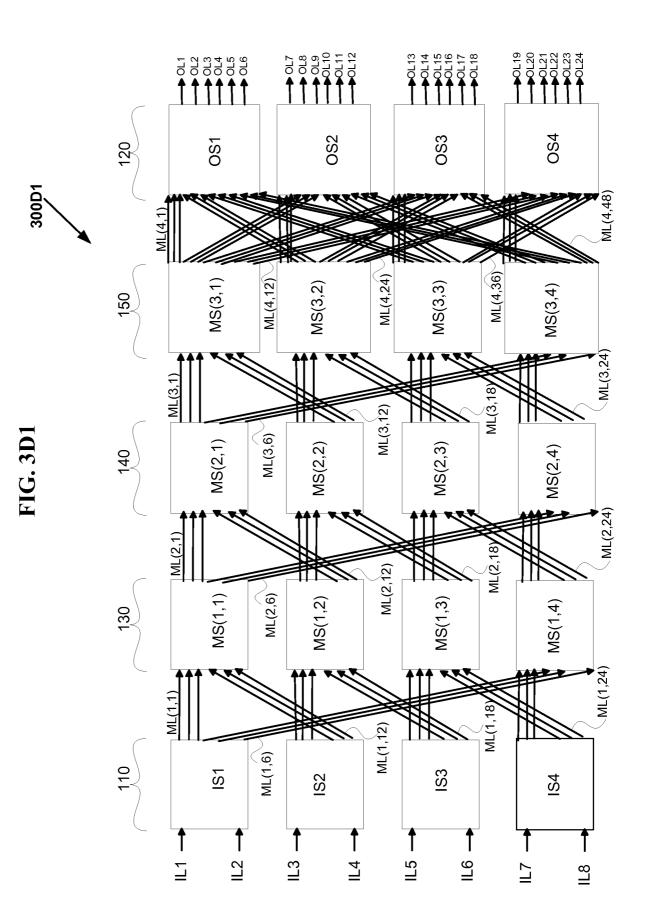

#### Asymmetric RNB $(N_2 > N_1)$ Embodiments:

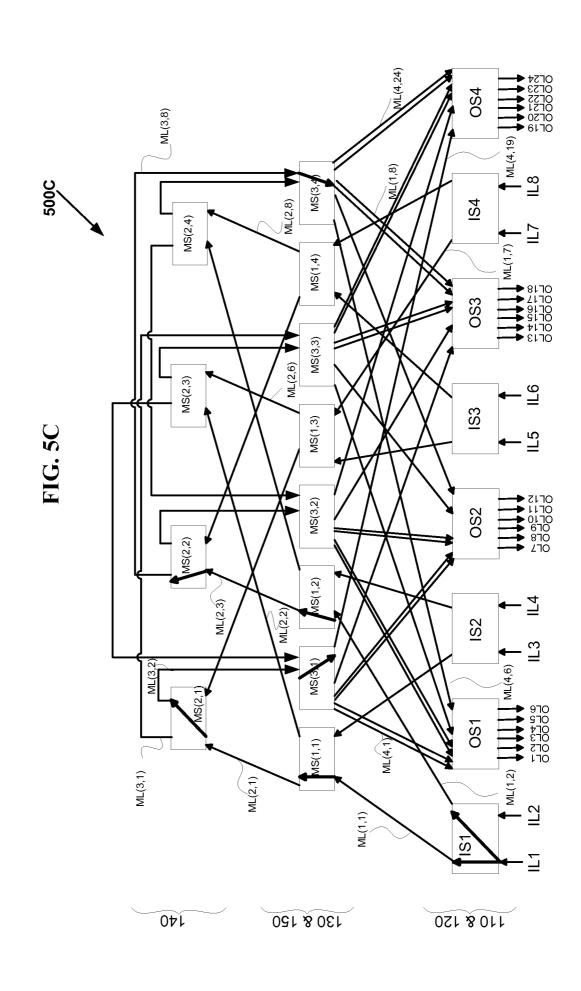

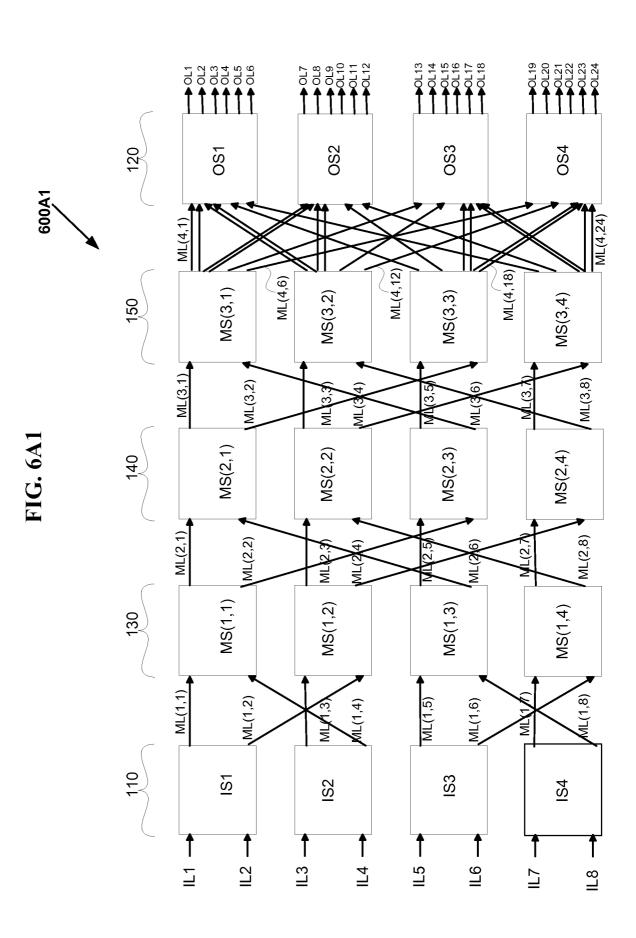

Referring to FIG. 1C, in one embodiment, an exemplary asymmetrical multi-stage network 100C with five stages of thirty two switches for satisfying communication

requests, such as setting up a telephone call or a data call, or a connection between configurable logic blocks, between an input stage 110 and output stage 120 via middle stages 130, 140, and 150 is shown where input stage 110 consists of four, two by four switches IS1-IS4 and output stage 120 consists of four, eight by six switches OS1-OS4. And all the middle stages namely middle stage 130 consists of eight, two by two switches

MS(1,1) - MS(1,8), middle stage 140 consists of eight, two by two switches MS(2,1) - MS(2,8), and middle stage 150 consists of eight, two by four switches MS(3,1) -

MS(3,8).

#### WO 2008/109756

#### PCT/US2008/056064

26

Such a network can be operated in strictly non-blocking manner for unicast connections, because the switches in the input stage 110 are of size two by four, the switches in output stage 120 are of size eight by six, and there are eight switches in each of middle stage 130, middle stage 140 and middle stage 150. Such a network can be

- 5 operated in rearrangeably non-blocking manner for multicast connections, because the switches in the input stage 110 are of size two by four, the switches in output stage 120 are of size eight by six, and there are eight switches of size two by two in each of middle stage 130 and middle stage 140, and eight switches of size two by four in middle stage 150.

- In one embodiment of this network each of the input switches IS1-IS4 and output switches OS1-OS4 are crossbar switches. The number of switches of input stage 110 and of output stage 120 can be denoted in general with the variable  $\frac{N_1}{d}$ , where  $N_1$  is the total number of inlet links or and  $N_2$  is the total number of outlet links and  $N_2 > N_1$  and  $N_2 = p * N_1$  where p > 1. The number of middle switches in each middle stage is

- 15 denoted by  $2 \times \frac{N_1}{d}$ . The size of each input switch IS1-IS4 can be denoted in general with the notation d \* 2d and each output switch OS1-OS4 can be denoted in general with the notation  $(d + d_2) * d$ , where  $d_2 = N_2 \times \frac{d}{N_1} = p \times d$ . The size of each switch in any of the middle stages excepting the last middle stage can be denoted as d \* d. The size of each switch in the last middle stage can be denoted as  $d * \frac{(d + d_2)}{2}$ . A switch as used

- 20 herein can be either a crossbar switch, or a network of switches each of which in turn may be a crossbar switch or a network of switches. An asymmetric multi-stage network can be represented with the notation  $V(N_1, N_2, d, s)$ , where  $N_1$  represents the total number of inlet links of all input switches (for example the links IL1-IL8),  $N_2$  represents the total number of outlet links of all output switches (for example the links OL1-OL24), d

- 25 represents the inlet links of each input switch where  $N_2 > N_1$ , and *s* is the ratio of number of outgoing links from each input switch to the inlet links of each input switch.

#### 27

#### PCT/US2008/056064

Each of the  $\frac{N_1}{d}$  input switches IS1 – IS4 are connected to exactly 2×d switches in middle stage 130 through 2×d links (for example input switch IS1 is connected to middle switches MS(1,1), MS(1,2), MS(1,5) and MS(1,6) through the links ML(1,1), ML(1,2), ML(1,3) and ML(1,4) respectively).

Similarly each of the  $2 \times \frac{N_1}{d}$  middle switches MS(2,1) – MS(2,8) in the middle stage 140 are connected from exactly *d* switches in middle stage 130 through *d* links (for example the links ML(2,1) and ML(2,6) are connected to the middle switch MS(2,1) from middle switches MS(1,1) and MS(1,3) respectively) and also are connected to exactly *d* switches in middle stage 150 through *d* links (for example the links ML(3,1)

15 exactly *d* switches in middle stage 150 through *d* links (for example the links ML(3,1)and ML(3,2) are connected from middle switch MS(2,1) to middle switch MS(3,1) and MS(3,3) respectively).

Similarly each of the  $2 \times \frac{N_1}{d}$  middle switches MS(3,1) – MS(3,8) in the middle

stage 150 are connected from exactly d switches in middle stage 140 through d links 20 (for example the links ML(3,1) and ML(3,6) are connected to the middle switch MS(3,1) from middle switches MS(2,1) and MS(2,3) respectively) and also are connected to exactly  $\frac{d+d_2}{2}$  output switches in output stage 120 through  $\frac{d+d_2}{2}$  links (for example the links ML(4,1), ML(4,2), ML(4,3) and ML(4,4) are connected to output switches OS1, OS2, OS3, and OS4 respectively from middle switches MS(3,1)).

#### WO 2008/109756

5

#### 28

PCT/US2008/056064

Each of the  $\frac{N_1}{d}$  output switches OS1 – OS4 are connected from exactly  $d + d_2$ switches in middle stage 150 through  $d + d_2$  links (for example output switch OS1 is connected from middle switches MS(3,1), MS(3,2), MS(3,3), MS(3,4), MS(3,5), MS(3,6), MS(3,7), and MS(3,8) through the links ML(4,1), ML(4,5), ML(4,9), ML(4,13), ML(4,17), ML(4,21), ML(4,25) and ML(4,29) respectively).

Finally the connection topology of the network 100C shown in FIG. 1C is known to be back to back inverse Benes connection topology.

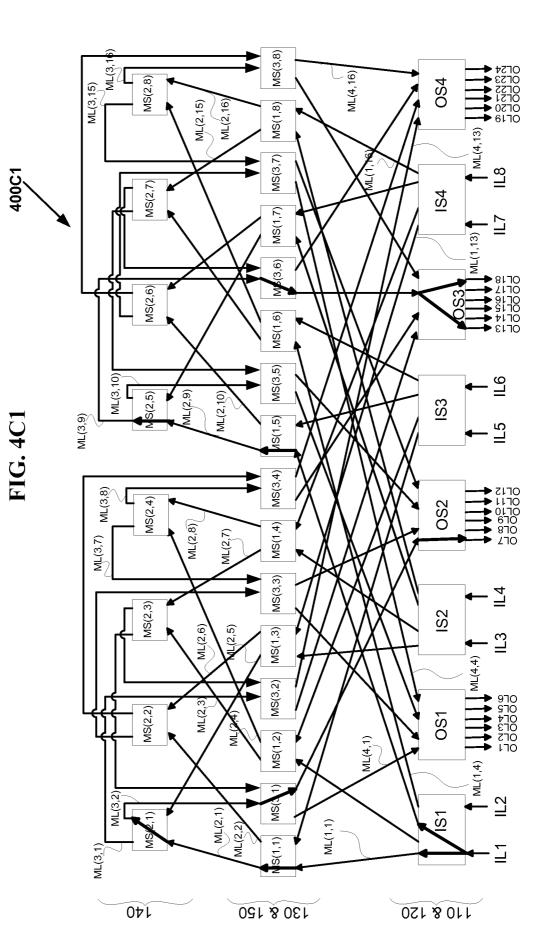

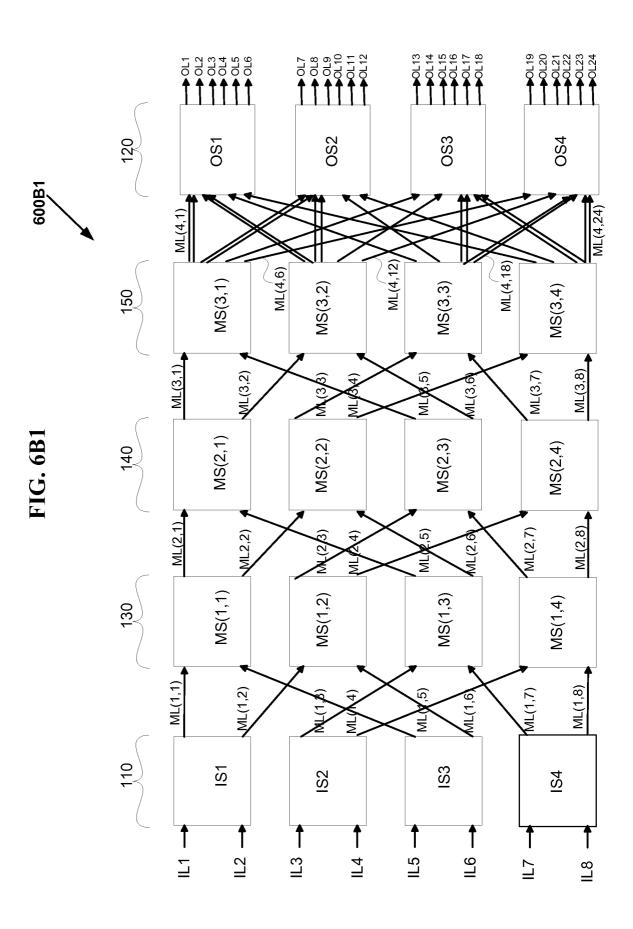

Referring to FIG. 1C1, in another embodiment of network  $V(N_1, N_2, d, s)$ , an exemplary asymmetrical multi-stage network 100C1 with five stages of thirty two

- 10 switches for satisfying communication requests, such as setting up a telephone call or a data call, or a connection between configurable logic blocks, between an input stage 110 and output stage 120 via middle stages 130, 140, and 150 is shown where input stage 110 consists of four, two by four switches IS1-IS4 and output stage 120 consists of four, eight by six switches OS1-OS4. And all the middle stages namely middle stage 130 consists of

- eight, two by two switches MS(1,1) MS(1,8), middle stage 140 consists of eight, two by two switches MS(2,1) MS(2,8), and middle stage 150 consists of eight, two by four switches MS(3,1) MS(3,8).

Such a network can be operated in strictly non-blocking manner for unicast connections, because the switches in the input stage 110 are of size two by four, the switches in output stage 120 are of size eight by six, and there are eight switches in each of middle stage 130, middle stage 140 and middle stage 150. Such a network can be operated in rearrangeably non-blocking manner for multicast connections, because the switches in the input stage 110 are of size two by four, the switches in output stage 120 are of size eight by six, and there are eight switches of size two by two in each of middle stage 130 and middle stage 140, and eight switches of size two by four in middle stage

150.

In one embodiment of this network each of the input switches IS1-IS4 and output switches OS1-OS4 are crossbar switches. The number of switches of input stage 110 and

#### WO 2008/109756

20

#### 29

#### PCT/US2008/056064

of output stage 120 can be denoted in general with the variable  $\frac{N_1}{d}$ , where  $N_1$  is the total number of inlet links or and  $N_2$  is the total number of outlet links and  $N_2 > N_1$  and  $N_2 = p * N_1$  where p > 1. The number of middle switches in each middle stage is denoted by  $2 \times \frac{N_1}{d}$ . The size of each input switch IS1-IS4 can be denoted in general with the notation d \* 2d and each output switch OS1-OS4 can be denoted in general with the 5 notation  $(d + d_2) * d$ , where  $d_2 = N_2 \times \frac{d}{N_1} = p \times d$ . The size of each switch in any of the middle stages excepting the last middle stage can be denoted as d \* d. The size of each switch in the last middle stage can be denoted as  $d * \frac{(d+d_2)}{2}$ . A switch as used herein can be either a crossbar switch, or a network of switches each of which in turn may 10 be a crossbar switch or a network of switches. The asymmetric multi-stage network of FIG. 1C1 is also the network of the type  $V(N_1, N_2, d, s)$ , where  $N_1$  represents the total number of inlet links of all input switches (for example the links IL1-IL8),  $N_2$  represents the total number of outlet links of all output switches (for example the links OL1-OL24), d represents the inlet links of each input switch where  $N_2 > N_1$ , and s is the ratio of

#### 15 number of outgoing links from each input switch to the inlet links of each input switch.

Each of the  $\frac{N_1}{d}$  input switches IS1 – IS4 are connected to exactly 2×d switches in middle stage 130 through 2×d links (for example input switch IS1 is connected to middle switches MS(1,1), MS(1,2), MS(1,5) and MS(1,6) through the links ML(1,1), ML(1,2), ML(1,3) and ML(1,4) respectively).

Each of the  $2 \times \frac{N_1}{d}$  middle switches MS(1,1) – MS(1,8) in the middle stage 130 are connected from exactly *d* input switches through *d* links (for example the links ML(1,1) and ML(1,9) are connected to the middle switch MS(1,1) from input switch IS1 and IS3 respectively) and also are connected to exactly *d* switches in middle stage 140

25

#### 30

#### PCT/US2008/056064

30

through d links (for example the links ML(2,1) and ML(2,2) are connected from middle switch MS(1,1) to middle switch MS(2,1) and MS(2,2) respectively).

Similarly each of the  $2 \times \frac{N_1}{d}$  middle switches MS(2,1) – MS(2,8) in the middle

stage 140 are connected from exactly d switches in middle stage 130 through d links

- 5 (for example the links ML(2,1) and ML(2,5) are connected to the middle switch MS(2,1) from middle switches MS(1,1) and MS(1,3) respectively) and also are connected to exactly d switches in middle stage 150 through d links (for example the links ML(3,1) and ML(3,2) are connected from middle switch MS(2,1) to middle switch MS(3,1) and MS(3,2) respectively).

- Similarly each of the 2× N<sub>1</sub>/d middle switches MS(3,1) MS(3,8) in the middle stage 150 are connected from exactly d switches in middle stage 140 through d links (for example the links ML(3,1) and ML(3,5) are connected to the middle switch MS(3,1) from middle switches MS(2,1) and MS(2,3) respectively) and also are connected to exactly d+d<sub>2</sub>/2 output switches in output stage 120 through d+d<sub>2</sub>/2 links (for example the links ML(4,1), ML(4,2), ML(4,3) and ML(4,4) are connected to output switches OS1, OS2, OS3, and OS4 respectively from middle switches MS(3,1)).

Each of the  $\frac{N_1}{d}$  output switches OS1 – OS4 are connected from exactly  $d + d_2$

switches in middle stage 150 through  $d + d_2$  links (for example output switch OS1 is connected from middle switches MS(3,1), MS(3,2), MS(3,3), MS(3,4), MS(3,5),

MS(3,6), MS(3,7), and MS(3,8) through the links ML(4,1), ML(4,5), ML(4,9), ML(4,13),

ML(4,17), ML(4,21), ML(4,25) and ML(4,29) respectively).

Finally the connection topology of the network 100C1 shown in FIG. 1C1 is known to be back to back Omega connection topology.

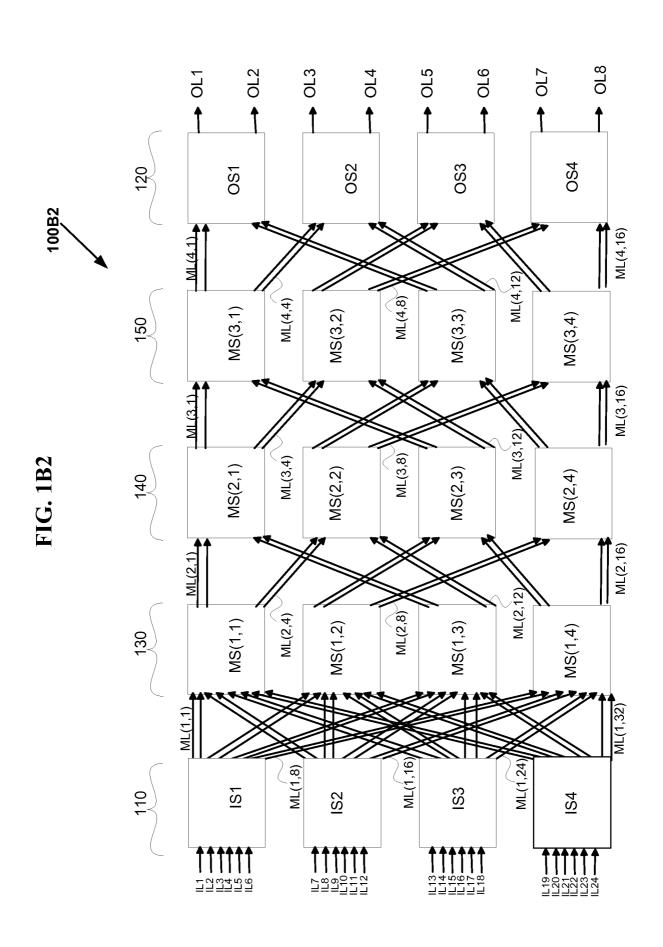

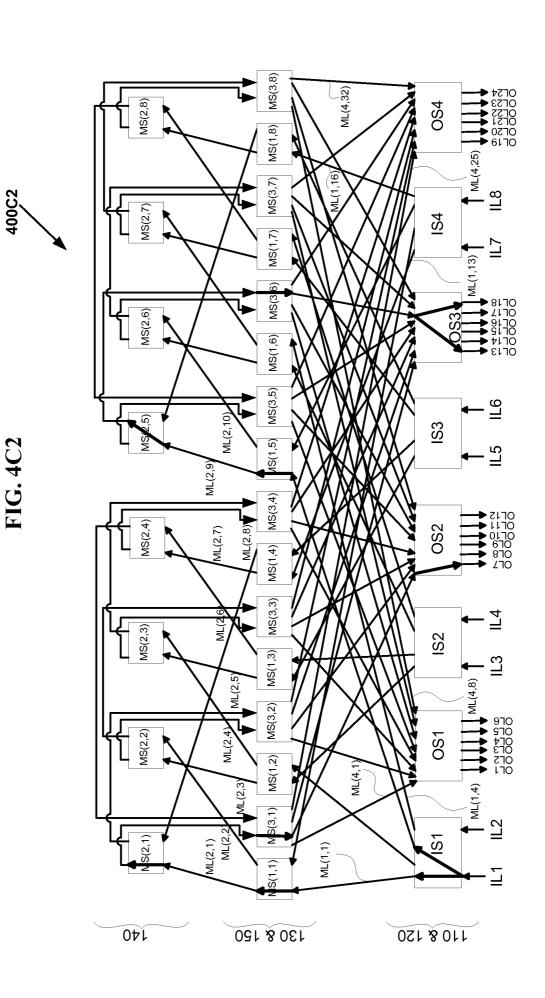

Referring to FIG. 1C2, in another embodiment of network  $V(N_1, N_2, d, s)$ , an exemplary asymmetrical multi-stage network 100C2 with five stages of thirty two

#### WO 2008/109756

#### 31

#### PCT/US2008/056064

switches for satisfying communication requests, such as setting up a telephone call or a data call, or a connection between configurable logic blocks, between an input stage 110 and output stage 120 via middle stages 130, 140, and 150 is shown where input stage 110 consists of four, two by four switches IS1-IS4 and output stage 120 consists of four, eight

5 by six switches OS1-OS4. And all the middle stages namely middle stage 130 consists of eight, two by two switches MS(1,1) - MS(1,8), middle stage 140 consists of eight, two by two switches MS(2,1) - MS(2,8), and middle stage 150 consists of eight, two by four switches MS(3,1) - MS(3,8).