Page 1 of 687 IPR2020-00261 19CV345846 VENKAT KONDA EXHIBIT 2031

Santa Clara – Civil

F. Miller

**Electronically Filed** by Superior Court of CA, 1 **VENKAT KONDA** County of Santa Clara, 6278 Grand Oak Way 2 on 3/22/2021 11:37 PM San Jose, California 95135 Reviewed By: F. Miller Telephone: (408) 472-3273 3 Case #19CV345846 Email: vkonda@gmail.com 4 Envelope: 6087289 Plaintiff Pro se 5 6 SUPERIOR COURT OF CALIFORNIA - COUNTY OF SANTA CLARA 7 UNLIMITED JURISDICTION 8 VENKAT KONDA, Ph.D., an individual, CASE NO. 19CV345846 9 10 **DECLARATION OF VIPIN CHAUDHARY,** Plaintiff, Ph.D. IN SUPPORT OF PLAINTIFF'S 11 FOURTH AMENDED COMPLAINT v. 12 **Department: 2** DEJAN MARKOVIC, Ph.D., an individual; 13 Before: Honorable Drew C. Takaichi CHENG C. WANG, Ph.D., an individual; FLEX LOGIX TECHNOLOGIES, INC., a 14 Date Complaint Filed: April 3, 2019 **Delaware Corporation; THE REGENTS OF** Trial Date: None 15 THE UNIVERSITY OF CALIFORNIA: **GEOFFREY TATE, an individual; PIERRE** 16 LAMOND, an individual; PETER HEBERT, an individual; LESLIE M. LACKMAN, Ph.D., 17 an individual; and DOES 1-20, inclusive, 18 Defendants. 19 20 21 22 I, Vipin Chaudhary, Ph.D., do hereby declare as follows: 23 24 1. I make the statements herein based on my personal knowledge and I could and would 25 competently testify thereto if called as a witness. 26 2. My current *curriculum vitae* is attached hereto as Exhibit K. 27 3. I earned a Bachelor Degree (Hons.) in Computer Science and Engineering from the 28 Indian Institute of Technology, Kharagpur, India in 1986, and the MS degree in Computer Science in

1989 and the Ph.D. degree in Electrical and Computer Engineering in 1992, both from The University of Texas at Austin.

- 4. Currently I am the Endowed Kranzusch Professor and Inaugural Chair, Department of Computer and Data Sciences, Case School of Engineering, Case Western Reserve University, Cleveland, Ohio. Prior to this position, I was a SUNY Empire Innovation Professor between 2011 and 2020 and SUNY Empire Innovation Associate Professor between 2006 and 2011, Computer Science and Engineering at University at Buffalo, The State University of New York. Between June 2016 and June 2020, I was also a Program Director at the Office of Advanced Cyber Infrastructure, Directorate for Computer and Information Science and Engineering, National Science Foundation, Alexandria, Virginia. Prior to the University at Buffalo, I was an Associate Professor, Department of Computer Science, and an Associate Professor, Department of Electrical and Computer Engineering at Wayne State University, Detroit, Michigan between 1998 and 2006, and an Assistant Professor, Department of Electrical and Computer Engineering, Wayne State University between 1992 and 1998.

- 5. I have been active in the field of integrated circuits and interconnection networks for over 30 years, since my Ph.D. Dissertation, awarded in 1992, in the area of parallel and distributed computing where interconnection networks is a major part of my dissertation.

- 6. I have received numerous awards for my work, including the 2019 National Science Foundation Director's Superior Accomplishment Award for my contributions where as a Program Director I co-led the National Strategic Computing Initiative from NSF for the United States and in the working groups of the Quantum Leap Initiative, National Quantum Initiative, National Artificial Intelligence Research Institutes, Cyber, and the I-Corps Program. The I-Corps program is now part of "The American Innovation and Competitiveness Act" that enables commercialization of research and venture startups. The U.S. National Strategic Computing Initiative incorporates many aspects of interconnection networks to make large computer systems.

- 7. I was co-founder of several startups, including as a Senior Director of Advanced Development at Cradle Technologies, Inc., where I was responsible for advanced programming tools development for multi-processor chips where interconnection networks is a key component. In Scalable Informatics, we designed and built some of the highest performance storage and analytics systems. As

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

the world with a unique interconnection network that enabled fast performance at a fraction of the cost. This company was sold to Tata Consulting Services. Prior to this, I was the Chief Architect at Corio, that is known as one of companies that really started the Software-as-a-Service revolution and had a successful IPO in 2000.

- 8. I served as associate Guest Editor, Special Issue of IEICE Transactions on Information and Systems on Hardware/Software Support for High Performance Scientific and Engineering Computing, July 2004. I served as Conference or Symposium Chair in six of the relevant conferences and as workshop chair in more than twenty workshops in the area of interconnection networks. I served as program committee member in more than forty conferences. I taught and created numerous undergraduate and graduate courses where integrated circuits and interconnection networks is an integral part of the subject matter.

- 9. I have supervised numerous doctoral dissertations and Master's theses. I have contributed to numerous book chapters and published numerous papers in refereed journal papers, refereed conference papers and refereed workshops related to integrated circuits and interconnection networks. I have given numerous invited talks at Academic Institutions, Industries, Research Laboratories, conferences and workshops related to integrated circuits and interconnection networks.

- 10. I have known Venkat Konda, Ph.D. (hereinafter referred to as "Dr. Konda") since 1991.

- 11. Dr. Konda contacted me regarding the above-captioned lawsuit.

- 12. Dr. Konda requested that I review a few Konda Technologies (hereinafter referred to as "Konda Tech") Documents listed below identifying Konda Tech's confidential information that is not trade secret information. I agreed to review Konda Tech's documents listed below to identify Konda Tech's confidential information that is non-trade-secret information, and provide the results of my review in this declaration.

- 13. My understanding is that a trade secret is defined in California Civil Code Section 3426.1(d) as:

- "Trade secret" means information, including a formula, pattern, compilation, program, device, method, technique, or process, that:

| 1 |

|---|

| 2 |

| 3 |

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

(1) Derives independent economic value, actual or potential, from not being generally known to the public or to other persons who can obtain economic value from its disclosure or use; and

(2) Is the subject of efforts that are reasonable under the circumstances to maintain its secrecy."

In this declaration, I express my opinion with respect to the subjects covered in subparagraph (1) of the above trade secret definition.

- 14. My understanding is confidential information that is not trade secret information means "confidential information including knowledge about the FPGA industry including contemporary industry analytics and trend analyses, business practices, disadvantages of the competition, advantages vis-à-vis the competition, customer procurement, relationship building, and management, and business successes." This information can be compiled by sweat of the brow and is protectable by being maintained confidential by the compiler of the information and not published.

- 15. Dr. Konda requested me to review the following documents: (1) Konda Tech's confidential Business Presentation to Defendant Markovic on October 7, 2009 in confidence (See, Exhibit 13 in Fourth Amended Complaint "FAC", hereinafter referred to as "Konda Tech 2009 Presentation"); (2) June 23, 2010 DARPA funding proposal (See, Exhibit 14 in FAC) and August 6, 2010 DARPA funding proposal (See, Exhibit 15 in FAC) (hereinafter collectively referred to as "Two Confidential DARPA Proposals"); (3) Konda Tech WIPO WO 2008109756 A1 published on December 9, 2008 (See, Exhibit A attached hereto), Konda Tech WIPO WO 2008147926 A1 published on December 4, 2008 (See, Exhibit C attached hereto), Konda Tech WIPO WO 2008147927 A1 published on December 4, 2008 (See, Exhibit E attached hereto), and Konda Tech WIPO WO 2008147928 A1 published on December 4, 2008 (See, Exhibit G attached hereto) (hereinafter referred to as collectively "2008 Konda Publications"); (4) Konda Tech US patent application US 2010/0135286 A1 publication (See, Exhibit B attached hereto), Konda Tech US patent application US 2010/0172349 A1 publication (See, Exhibit D attached hereto), Konda Tech US patent application US 2011/0044329 A1 publication (See, Exhibit F attached hereto), and Konda Tech US patent application US 2011/0037498 A1 publication (See, Exhibit H attached hereto) (hereinafter referred to as collectively "pre-2010 Konda

1 Publications"); (5) Konda Tech WIPO WO 2011047368 A2 published on April 21, 2011 (hereinafter 2 referred to as "2011 Konda Publication") (See, Exhibit I attached hereto); (6) Konda Tech US patent 3 application US 2012/0269190 A1 publication (hereinafter referred to as "2012 Konda Publication") 4 (See, Exhibit J attached hereto); (7) Defendants Markovic and Wang's paper presented in June 2011 5 (submitted in January 2011) at the 2011 VLSI Circuits Symposium titled "A 1.1 GOPS/mQ FPGA Chip with Hierarchical Interconnect Fabric" unbeknownst to Dr. Konda and without his authorization, 6 7 (hereinafter referred to as "2011 VLSI Paper") (See, Exhibit 20 in FAC); (8) Defendant Wang's PhD 8 Dissertation presented in 2013 titled "Building Efficient, Reconfigurable Hardware using Hierarchical 9 Interconnects" unbeknownst to Dr. Konda and without his authorization (hereinafter referred to as 10 "Wang's 2013 PhD Dissertation") (See, Exhibit 22 in FAC); and (9) Defendants Markovic and Wang presented paper titled "A Multi-Granularity FPGA with Hierarchical Interconnects for Efficient and 11 12 Flexible Mobile Computing" to the 2014 International Solid State Circuits Conference (hereinafter

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

16. I was informed by Dr. Konda that the contents of the "Konda Tech 2009 Presentation," which is marked "confidential," is confidential information even today.

referred to as "2014 ISSCC Paper") (See, Exhibit 24 in FAC).

- 17. I was asked to review if the Konda Tech 2009 Presentation and the Two Confidential DARPA Proposals contain additional confidential information, particularly non-trade-secret information, that is not disclosed in the 2008 Konda Publications. The objective was to determine the Konda Tech confidential information, particularly non-trade-secret information, that was disclosed to Markovic by Dr. Konda in confidence.

- 18. After my review, in my opinion, the Konda Tech 2009 Presentation and the Two Confidential DARPA Proposals contain confidential information that is non-trade-secret information.

- 19. Accordingly in my opinion, the Konda Tech 2009 Presentation and the Two Confidential DARPA Proposals contain confidential information that is non-trade-secret information and that was not disclosed in the 2008 Konda Publications.

- 20. Dr. Konda also requested me to review if confidential information in the Konda Tech 2009 Presentation and the Two Confidential DARPA Proposals that is not disclosed in the 2008 Konda Publications is contained in the 2011 VLSI Paper.

- 3

- 4

- 5

- 7

- 8

- 1011

- 12

- 13

- 1415

- 16

- 17

- 18 19

- 20

- 2122

- 2324

- 2526

- 27

- 28

- 21. After my review, in my opinion, the 2011 VLSI Paper contains confidential information, particularly non-trade-secret information, in the Konda Tech 2009 Presentation and the Two Confidential DARPA Proposals that was not disclosed in the 2008 Konda Publications.

- 22. Accordingly in my opinion, at the time of submission, the 2011 VLSI Paper contains Dr. Konda's confidential information including non-trade-secret information.

- 23. Dr. Konda further requested me to review if confidential non-trade-secret information in the Konda Tech 2009 Presentation and the Two Confidential DARPA Proposals that is not disclosed in the 2008 Konda Publications is contained in Wang's 2013 PhD Dissertation.

- 24. After my review, in my opinion, Wang's 2013 PhD Dissertation contains confidential non-trade-secret information identified in the Konda Tech 2009 Presentation and the Two Confidential DARPA Proposals that is not disclosed in the 2008 Konda Publications.

- 25. Accordingly in my opinion, at the time of submission, Wang's 2013 PhD Dissertation contains Dr. Konda's confidential non-trade-secret information.

- 26. Additionally, Dr. Konda requested me to review if confidential information identified in the Konda Tech 2009 Presentation and the Two Confidential DARPA Proposals that is not disclosed in the 2008 Konda Publications.

- 27. After my review, in my opinion, the 2014 ISSCC Paper contains confidential non-tradesecret information identified in the Konda Tech 2009 Presentation and the Two Confidential DARPA Proposals that is not disclosed in the 2008 Konda Publications.

- 28. Accordingly in my opinion, at the time of submission, the 2014 ISSCC Paper contains Dr. Konda's confidential non-trade-secret information.

- 29. Dr. Konda also requested me to review the texts and diagrams of the 2008 Konda Publications and pre-2010 Konda Publications.

- 30. Based on my analysis, the 2011 VLSI Paper contains substantial portions of the texts and related diagrams of the 2008 Konda Publications and pre-2010 Konda Publications without attribution to Dr. Konda or Konda Tech.

- 31. Dr. Konda additionally requested me to review the texts and diagrams of the 2011 Konda Publication and 2012 Konda Publication.

Page 7 of 687 IPR2020-00261

|   | I |

|---|---|

|   | 2 |

|   | 3 |

|   | 4 |

|   | 5 |

|   | 6 |

|   | 7 |

|   | 8 |

|   | 9 |

| 1 | 0 |

| 1 | 1 |

| 1 | 2 |

| 1 | 3 |

| 1 | 4 |

| 1 | 5 |

| 1 | 6 |

| 1 | 7 |

| 1 | 8 |

| 1 | 9 |

| 2 | 0 |

| 2 | 1 |

| 2 | 2 |

| 2 | 3 |

| 2 | 4 |

| 2 | 5 |

| 2 | 6 |

| 2 | 7 |

|   |   |

28

| 3         | 2. B      | sed on my analysis, Wang's 2013 PhD Dissertation contains substantial portions of |

|-----------|-----------|-----------------------------------------------------------------------------------|

| the texts | and rela  | ted diagrams of the 2008 Konda Publications, pre-2010 Konda Publications, 2011    |

| Konda P   | ublicatio | n, and 2012 Konda publication without attribution to Dr. Konda or Konda Tech.     |

- 33. Also, based on my analysis, the 2014 ISSCC Paper contains substantial portions of the texts and related diagrams of the 2008 Konda Publications, pre-2010 Konda Publications, 2011 Konda Publication, and 2012 Konda publication without attribution to Dr. Konda or Konda Tech.

- 34. Finally, I am not an attorney and offer no legal opinions, but I have extensive experience in interconnect technology, and my opinions expressed herein are based on my own personal knowledge and professional judgment and do not reflect the opinions of my employers. In forming my opinions, I have relied on my knowledge and experience in designing, developing, researching, and teaching related to interconnection networks.

I declare under penalty of perjury under the laws of the State of California that the foregoing is true and correct to the best of my knowledge and that this Declaration was entered into on this 22nd day of March 2021, in Highland Heights, Ohio.

Case No: 19CV345846

Vipin Chaudhary, Ph.D.

# **EXHIBIT F**

US 20110044329A1

# (19) United States

# (12) Patent Application Publication Konda

# (43) **Pub. Date:** Feb. 24, 2011

(10) Pub. No.: US 2011/0044329 A1

#### (54) FULLY CONNECTED GENERALIZED MULTI-LINK MULTI-STAGE NETWORKS

(76) Inventor: Venkat Konda, San Jose, CA (US)

Correspondence Address: Konda Technologies, Inc 6278 GRAND OAK WAY SAN JOSE, CA 95135 (US)

(21) Appl. No.: 12/601,274

(22) PCT Filed: May 22, 2008

(86) PCT No.: **PCT/US08/64604**

§ 371 (c)(1),

(2), (4) Date: **May 31, 2010**

#### Related U.S. Application Data

(60) Provisional application No. 60/940,389, filed on May 25, 2007, provisional application No. 60/940,391, filed on May 25, 2007, provisional application No. 60/940,392, filed on May 25, 2007.

#### **Publication Classification**

(51) **Int. Cl. H04L 12/50** (2006.01) (57) ABSTRACT

A generalized multi-link multi-stage network comprising (2×log<sub>d</sub> N)-1 stages is operated in strictly nonblocking manner for unicast includes an input stage having N/d switches with each of them having d inlet links and 2×d outgoing links connecting to second stage switches, an output stage having N/d switches with each of them having d outlet links and 2xd incoming links connecting from switches in the penultimate stage. The network also has  $(2 \times \log_d N) - 3$  middle stages with each middle stage having N/d switches, and each switch in the middle stage has 2xd incoming links connecting from the switches in its immediate preceding stage, and 2xd outgoing links connecting to the switches in its immediate succeeding stage. Also the same generalized multi-link multi-stage network is operated in rearrangeably nonblocking manner for arbitrary fan-out multicast and each multicast connection is set up by use of at most two outgoing links from the input stage switch.

A generalized multi-link multi-stage network comprising  $(2 \times \log_d N)-1$  stages is operated in strictly nonblocking manner for multicast includes an input stage having N/d switches with each of them having d inlet links and  $3 \times d$  outgoing links connecting to second stage switches, an output stage having N/d switches with each of them having d outlet links and  $3 \times d$  incoming links connecting from switches in the penultimate stage. The network also has  $(2 \times \log_d N)-3$  middle stages with each middle stage having N/d switches, and each switch in the middle stage has  $3 \times d$  incoming links connecting from the switches in its immediate preceding stage, and  $3 \times d$  outgoing links connecting to the switches in its immediate succeeding stage.

Patent Application Publication Feb. 24, 2011 Sheet 1 of 125 US 2011/0044329 A1

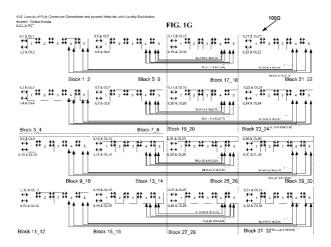

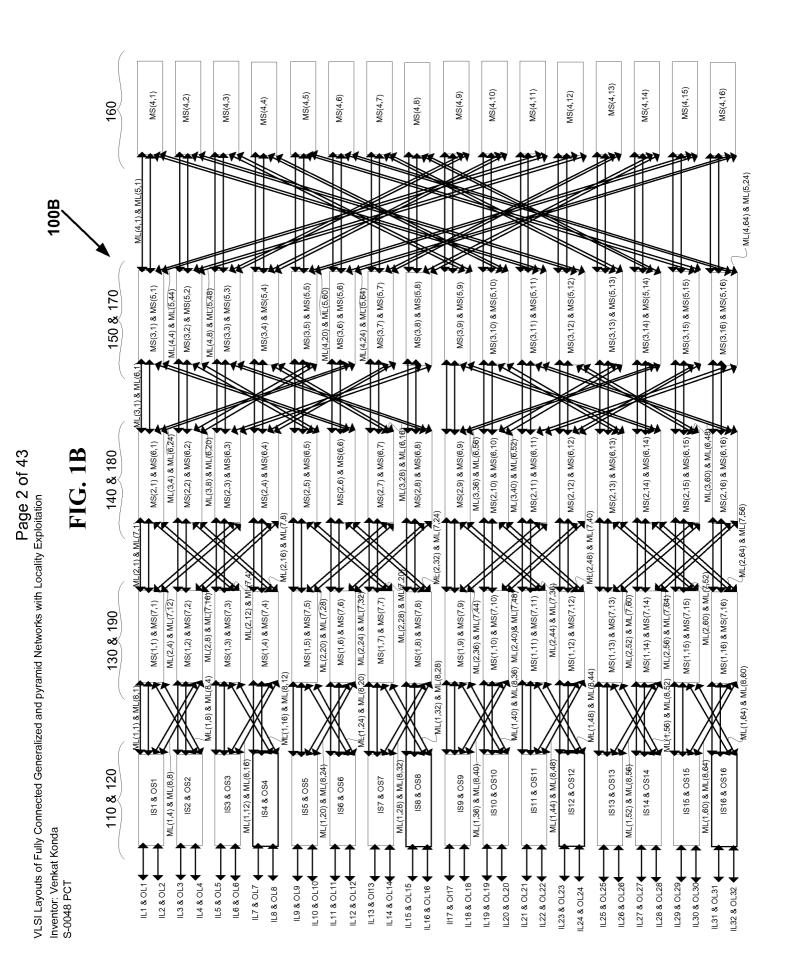

Patent Application Publication Feb. 24, 2011 Sheet 2 of 125 US 2011/0044329 A1

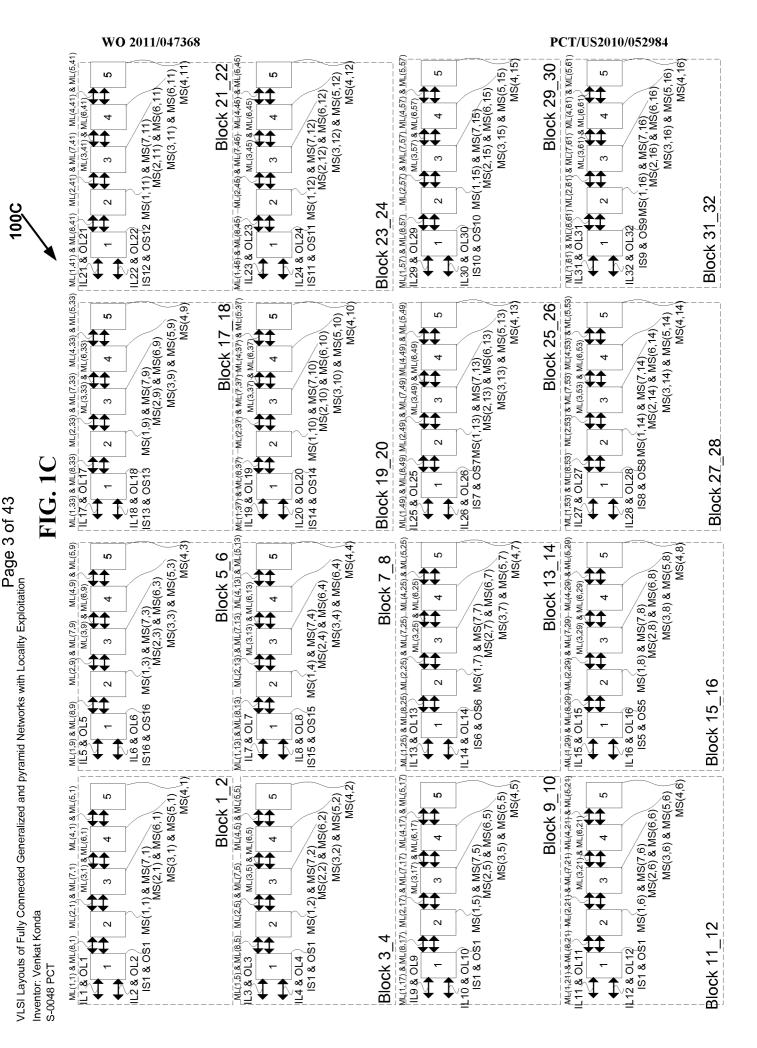

Patent Application Publication Feb. 24, 2011 Sheet 3 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 4 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 5 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 6 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 7 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 8 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 9 of 125 US 2011/0044329 A1

# Patent Application Publication Feb. 24, 2011 Sheet 10 of 125 US 2011/0044329 A1

# Patent Application Publication Feb. 24, 2011 Sheet 11 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 12 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 13 of 125 US 2011/0044329 A1

# Patent Application Publication Feb. 24, 2011 Sheet 14 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 15 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 16 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 17 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 18 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 19 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 20 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 21 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 22 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 23 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 24 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 25 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 26 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 27 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 28 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 29 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 30 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 31 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 32 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 33 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 34 of 125 US 2011/0044329 A1

## Patent Application Publication Feb. 24, 2011 Sheet 35 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 36 of 125 US 2011/0044329 A1

## Patent Application Publication Feb. 24, 2011 Sheet 37 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 38 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 39 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 40 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 41 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 42 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 43 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 44 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 45 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 46 of 125 US 2011/0044329 A1

## Patent Application Publication Feb. 24, 2011 Sheet 47 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 48 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 49 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 50 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 51 of 125 US 2011/0044329 A1

## Patent Application Publication Feb. 24, 2011 Sheet 52 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 53 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 54 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 55 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 56 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 57 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 58 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 59 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 60 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 61 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 62 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 63 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 64 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 65 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 66 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 67 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 68 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 69 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 70 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 71 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 72 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 73 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 74 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 75 of 125 US 2011/0044329 A1

# Patent Application Publication Feb. 24, 2011 Sheet 76 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 77 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 78 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 79 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 80 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 81 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 82 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 83 of 125 US 2011/0044329 A1

# Patent Application Publication Feb. 24, 2011 Sheet 84 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 85 of 125 US 2011/0044329 A1

# Patent Application Publication Feb. 24, 2011 Sheet 86 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 87 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 88 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 89 of 125 US 2011/0044329 A1

# Patent Application Publication Feb. 24, 2011 Sheet 90 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 91 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 92 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 93 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 94 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 95 of 125 US 2011/0044329 A1

# Patent Application Publication Feb. 24, 2011 Sheet 96 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 97 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 98 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 99 of 125 US 2011/0044329 A1

### Patent Application Publication Feb. 24, 2011 Sheet 100 of 125 US 2011/0044329 A1

#### Patent Application Publication Feb. 24, 2011 Sheet 101 of 125 US 2011/0044329 A1

### Patent Application Publication Feb. 24, 2011 Sheet 102 of 125 US 2011/0044329 A1

### Patent Application Publication Feb. 24, 2011 Sheet 103 of 125 US 2011/0044329 A1

### Patent Application Publication Feb. 24, 2011 Sheet 104 of 125 US 2011/0044329 A1

## Patent Application Publication Feb. 24, 2011 Sheet 105 of 125 US 2011/0044329 A1

### Patent Application Publication Feb. 24, 2011 Sheet 106 of 125 US 2011/0044329 A1

Patent Application Publication Feb. 24, 2011 Sheet 107 of 125 US 2011/0044329 A1

### Patent Application Publication Feb. 24, 2011 Sheet 108 of 125 US 2011/0044329 A1

### Patent Application Publication Feb. 24, 2011 Sheet 109 of 125 US 2011/0044329 A1

### Patent Application Publication Feb. 24, 2011 Sheet 110 of 125 US 2011/0044329 A1

### Patent Application Publication Feb. 24, 2011 Sheet 111 of 125 US 2011/0044329 A1

### Patent Application Publication Feb. 24, 2011 Sheet 112 of 125 US 2011/0044329 A1

#### Patent Application Publication Feb. 24, 2011 Sheet 113 of 125 US 2011/0044329 A1

## Patent Application Publication Feb. 24, 2011 Sheet 114 of 125 US 2011/0044329 A1

### Patent Application Publication Feb. 24, 2011 Sheet 115 of 125 US 2011/0044329 A1

## Patent Application Publication Feb. 24, 2011 Sheet 116 of 125 US 2011/0044329 A1

### Patent Application Publication Feb. 24, 2011 Sheet 117 of 125 US 2011/0044329 A1

### Patent Application Publication Feb. 24, 2011 Sheet 118 of 125 US 2011/0044329 A1

### Patent Application Publication Feb. 24, 2011 Sheet 119 of 125 US 2011/0044329 A1

### Patent Application Publication Feb. 24, 2011 Sheet 120 of 125 US 2011/0044329 A1

#### Patent Application Publication Feb. 24, 2011 Sheet 121 of 125 US 2011/0044329 A1

#### Patent Application Publication Feb. 24, 2011 Sheet 122 of 125 US 2011/0044329 A1

### Patent Application Publication Feb. 24, 2011 Sheet 123 of 125 US 2011/0044329 A1

#### Patent Application Publication Feb. 24, 2011 Sheet 124 of 125 US 2011/0044329 A1

## Patent Application Publication Feb. 24, 2011 Sheet 125 of 125 US 2011/0044329 A1

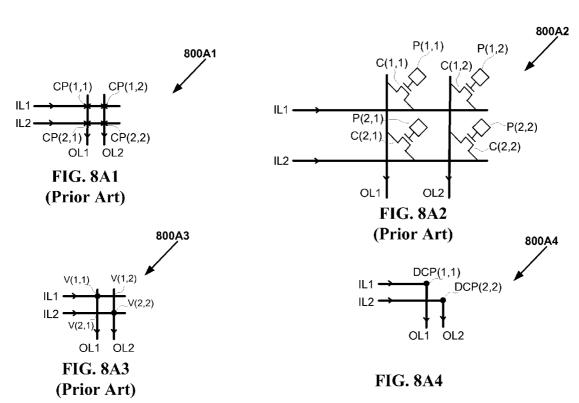

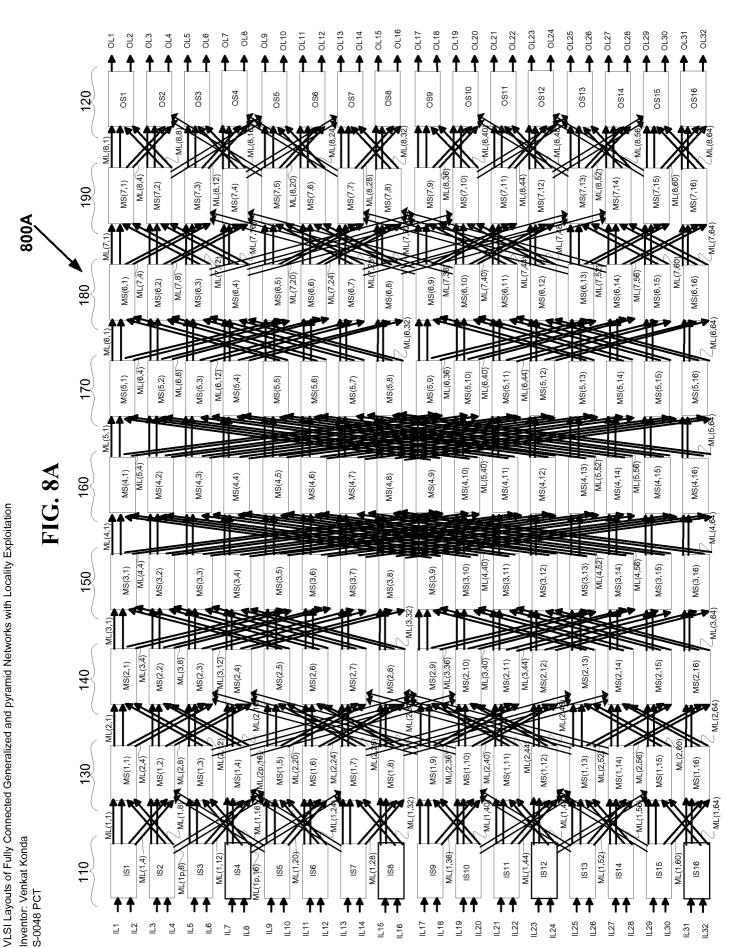

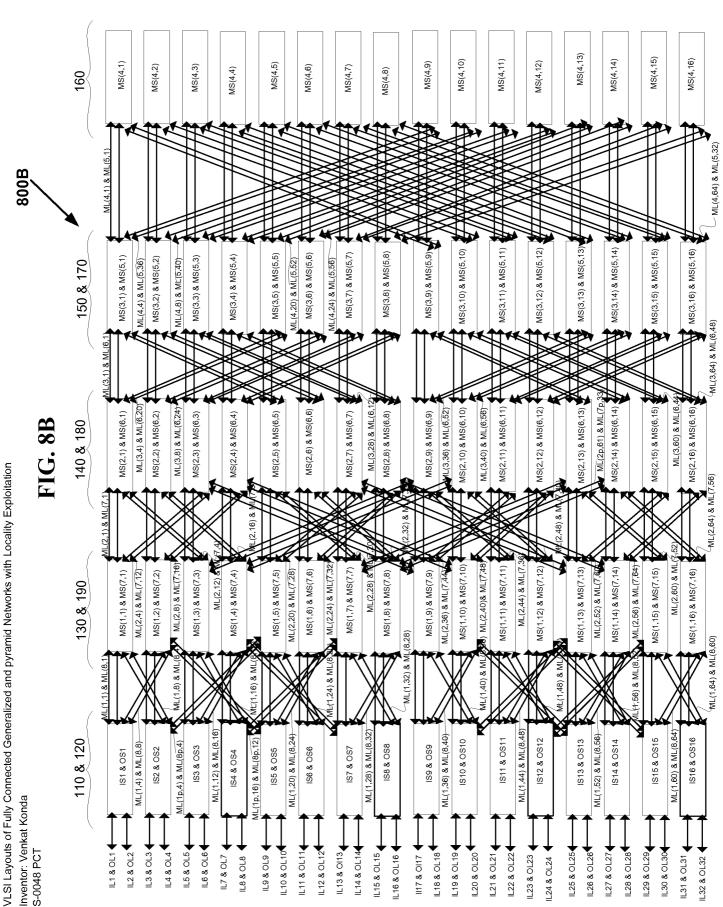

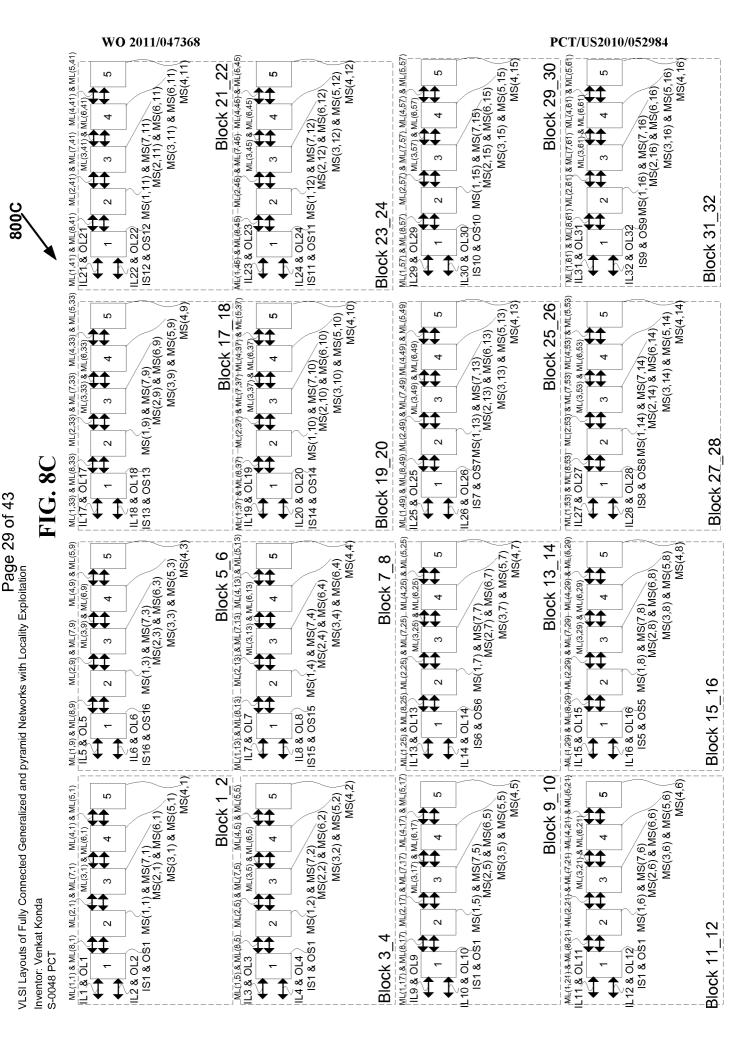

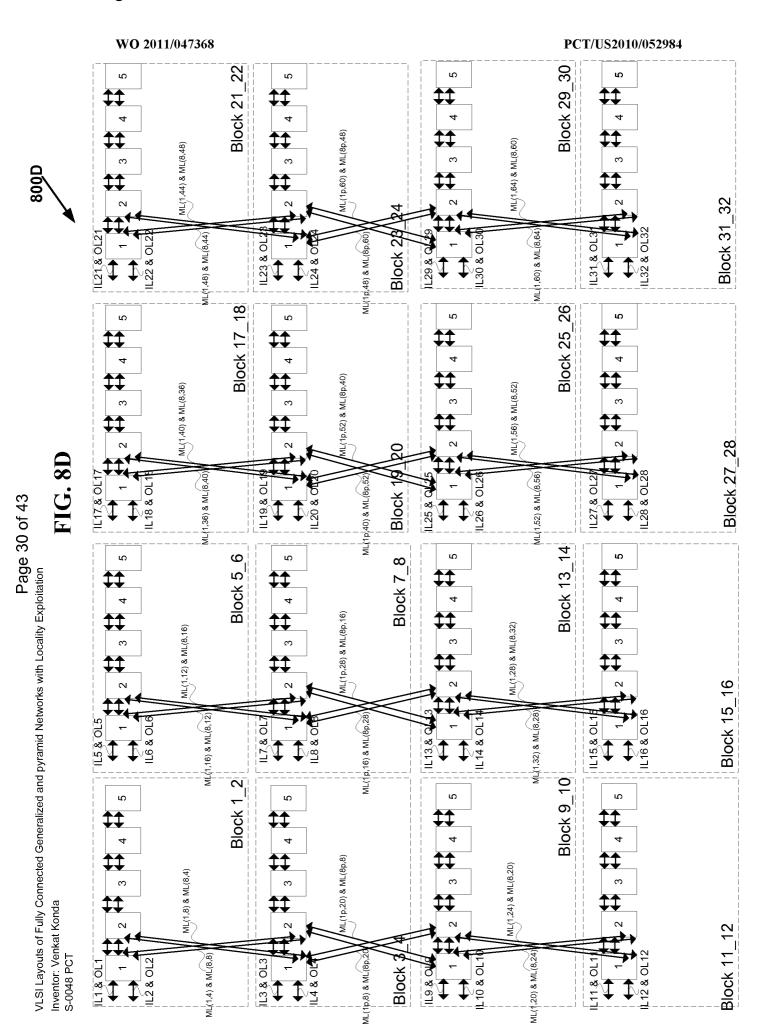

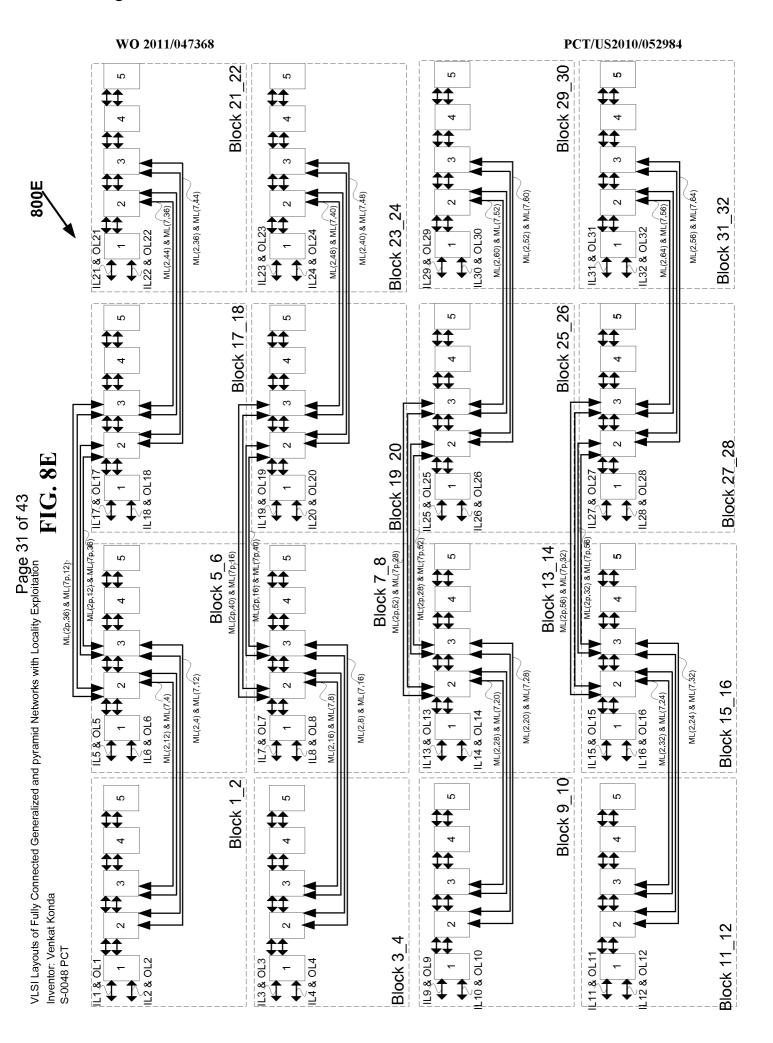

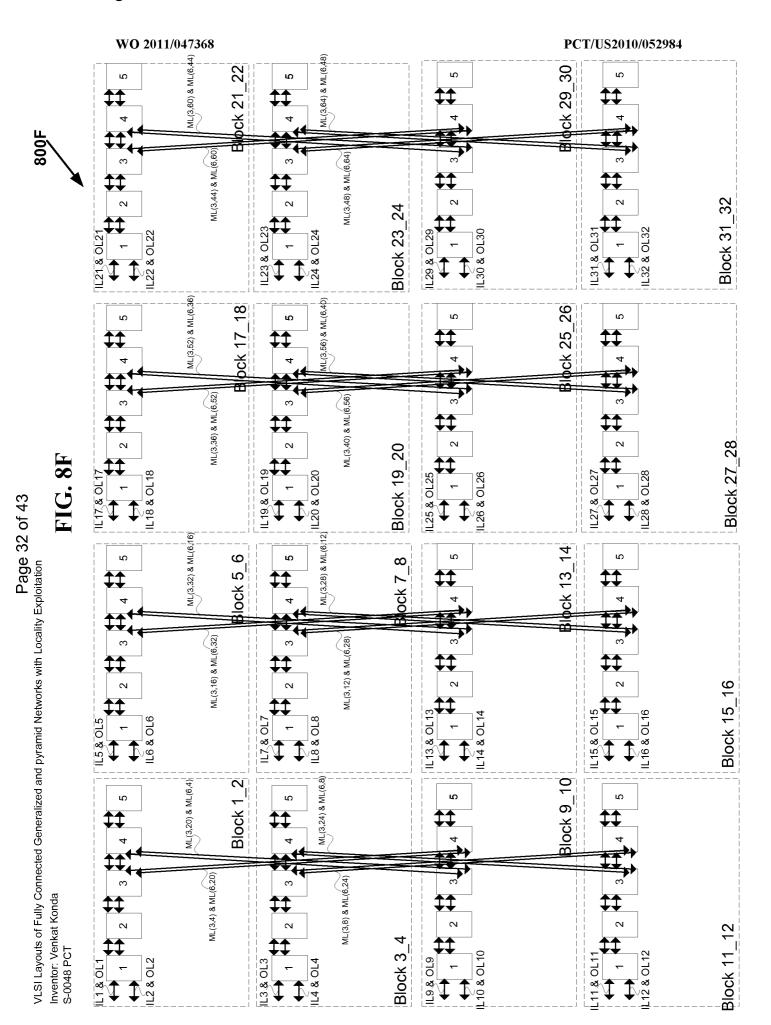

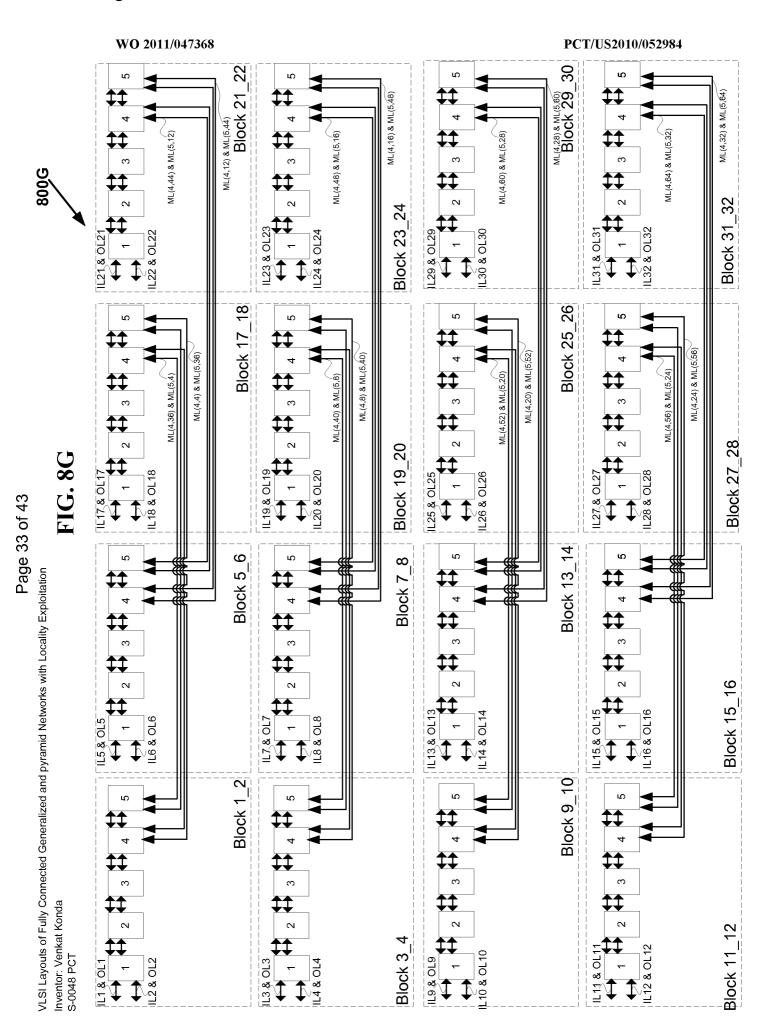

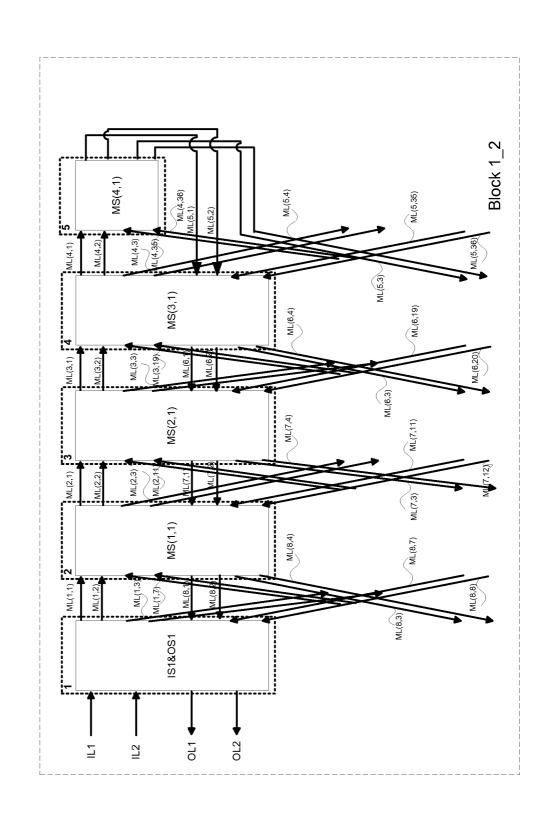

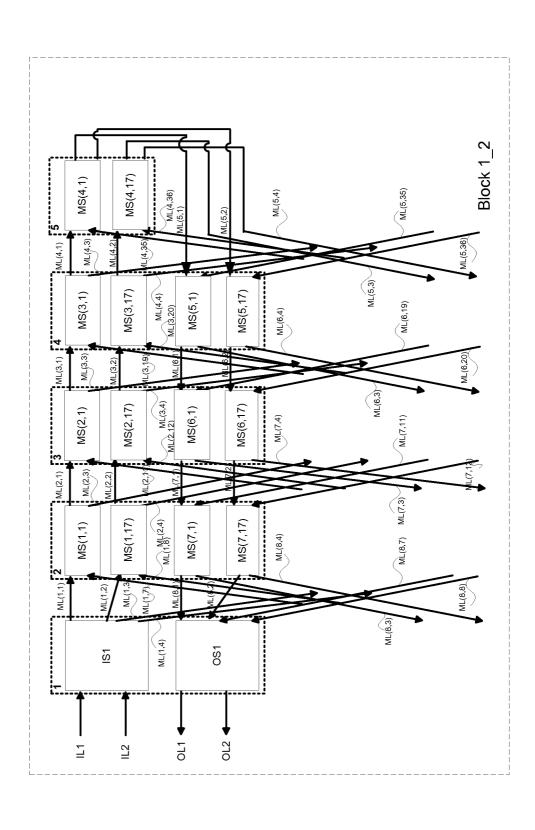

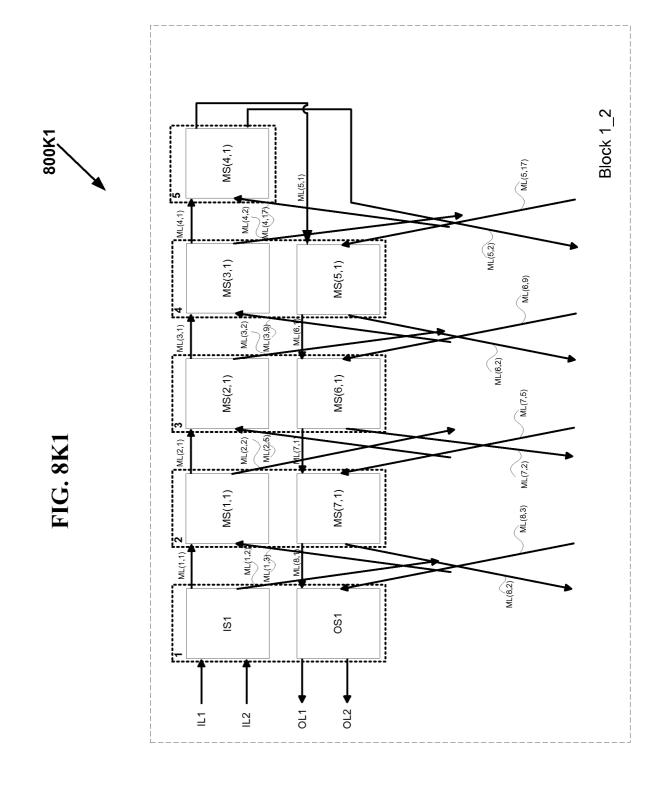

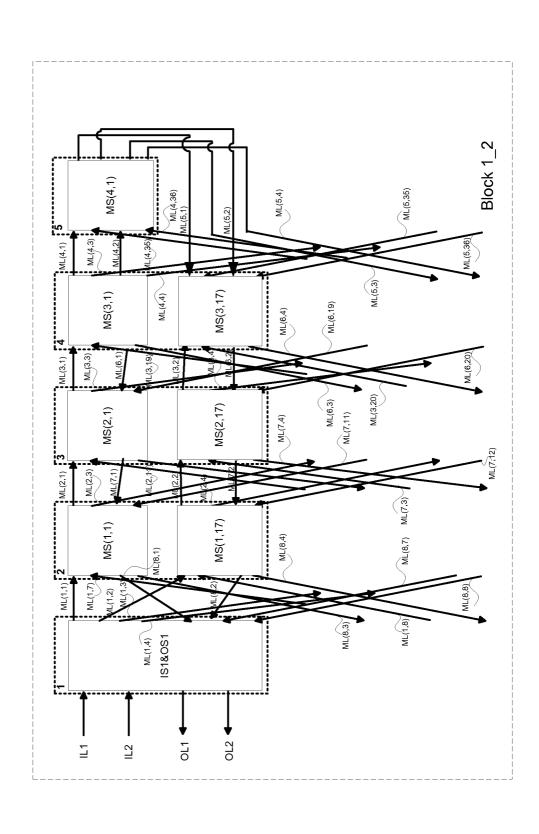

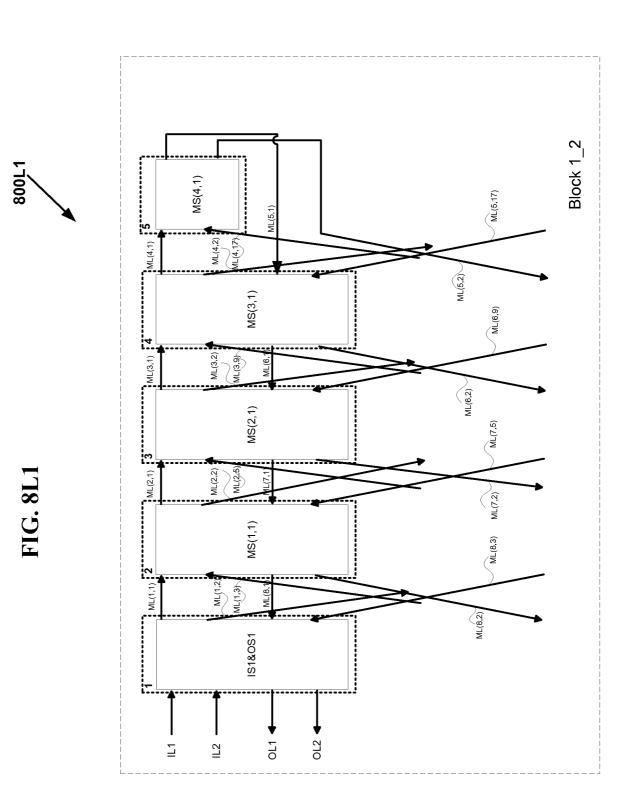

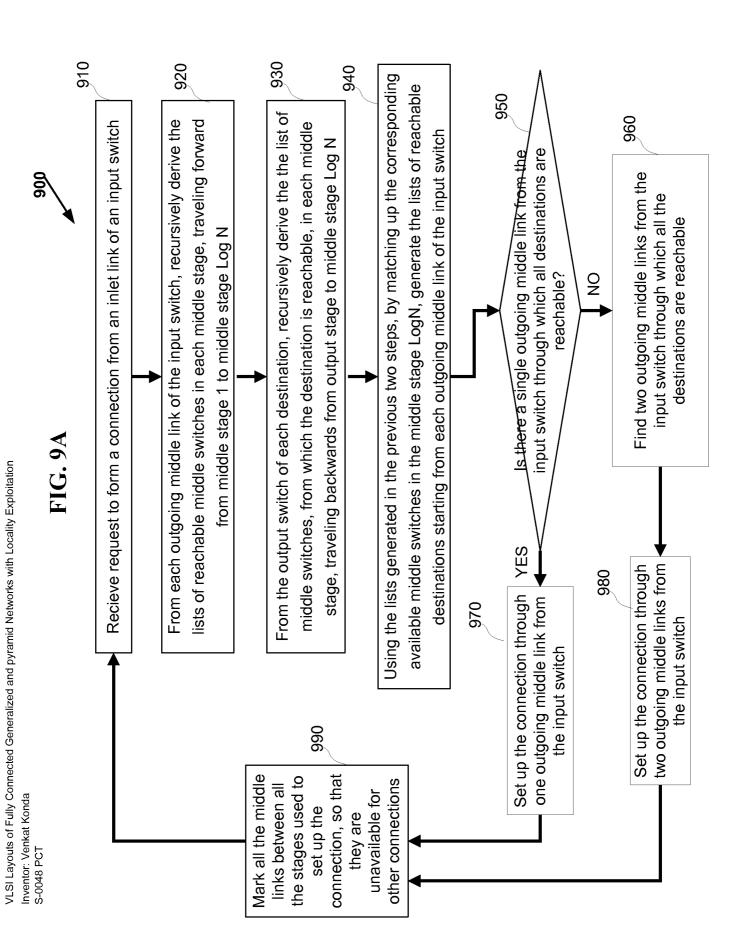

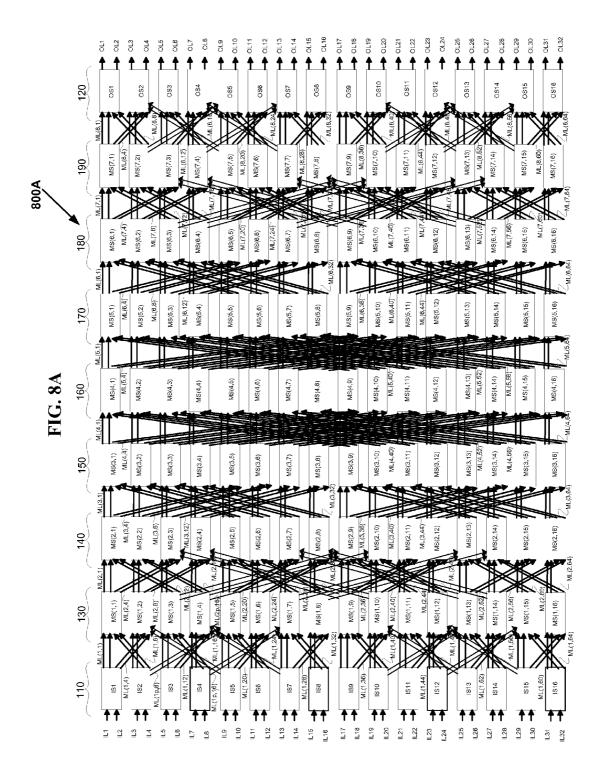

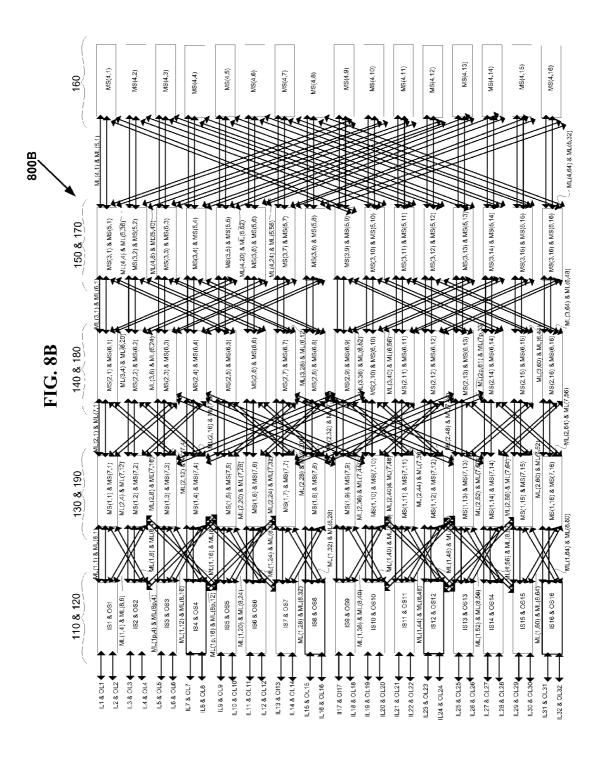

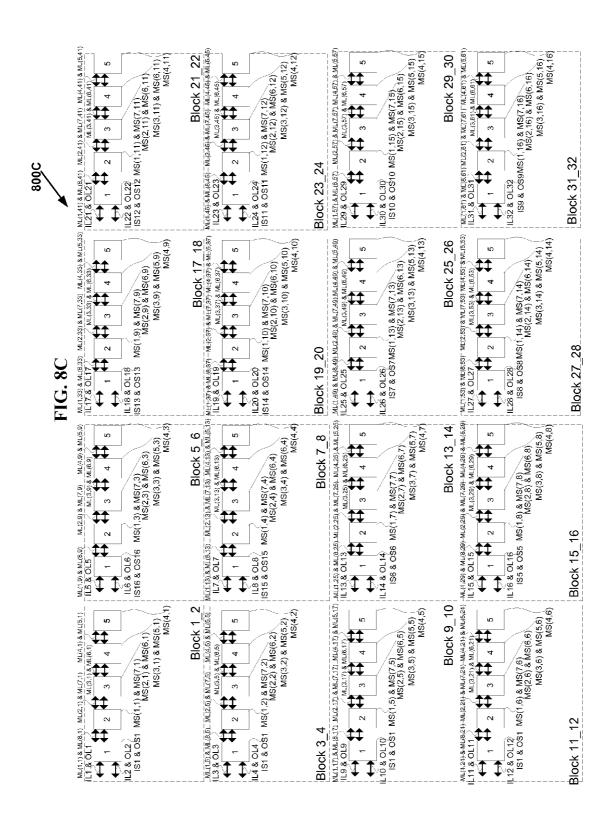

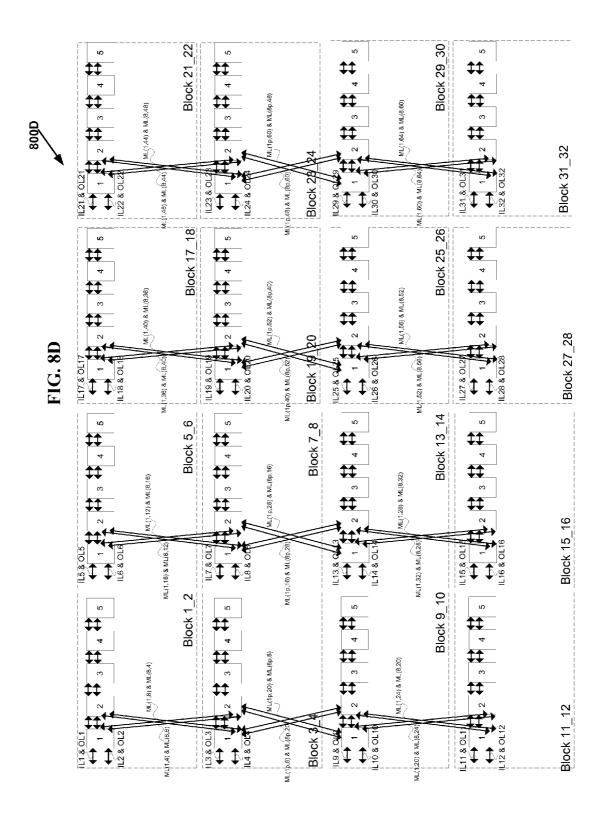

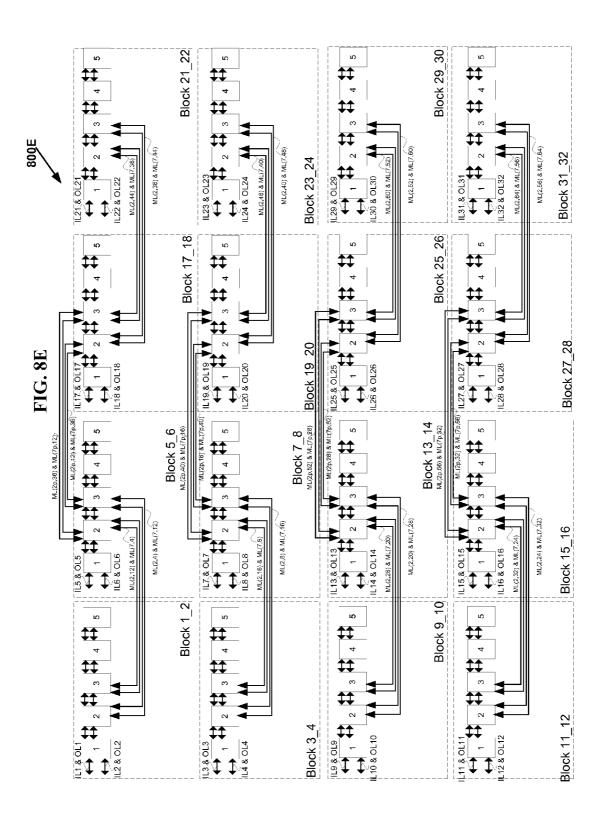

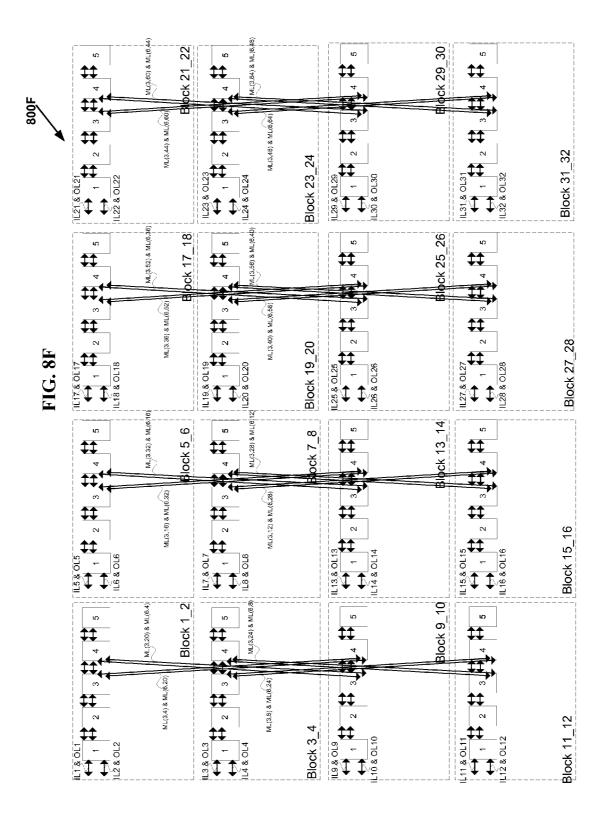

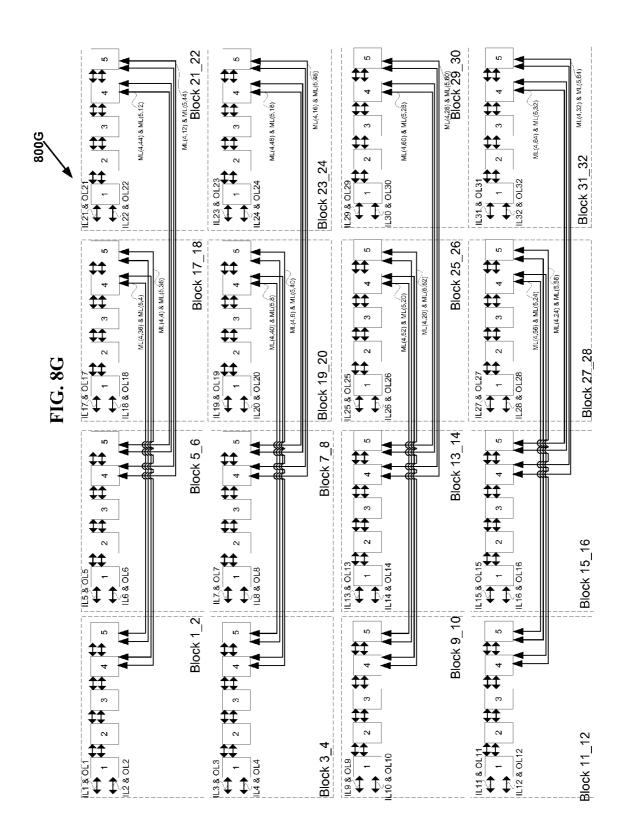

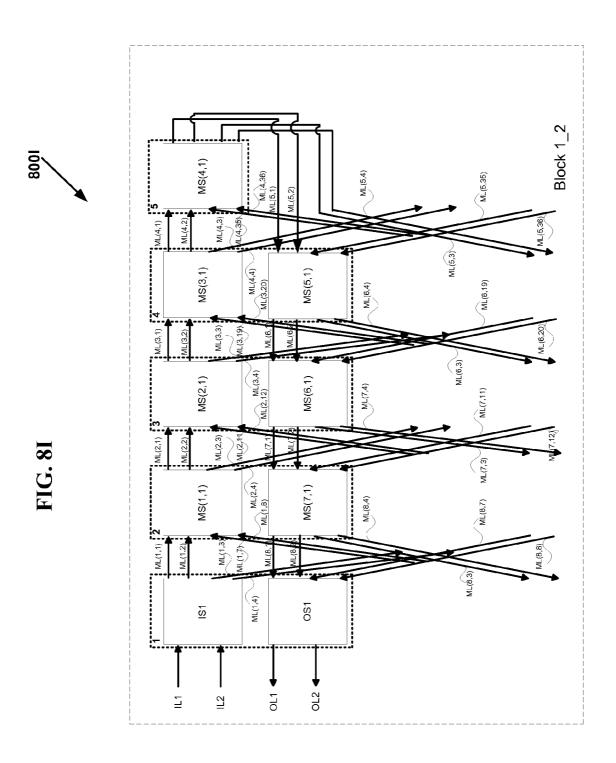

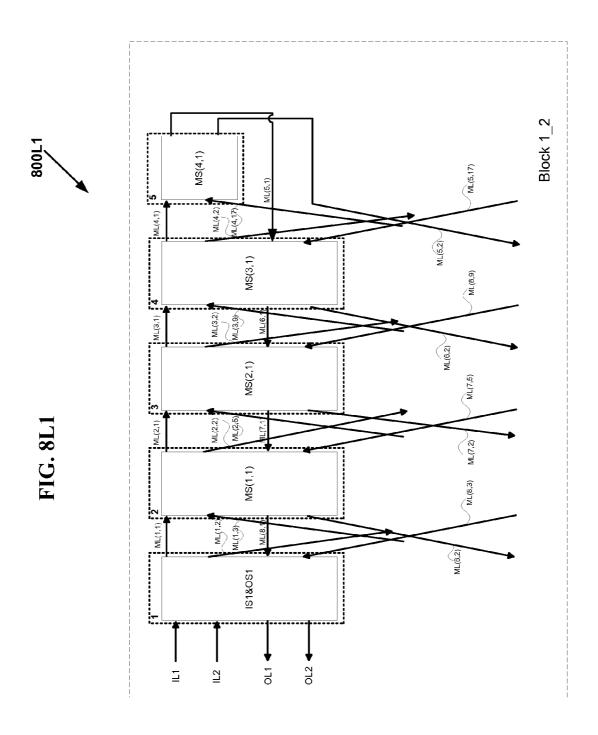

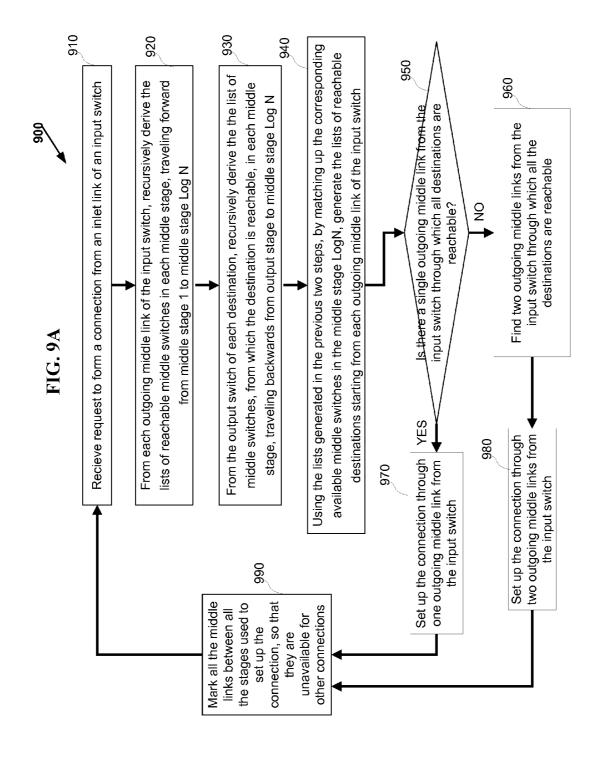

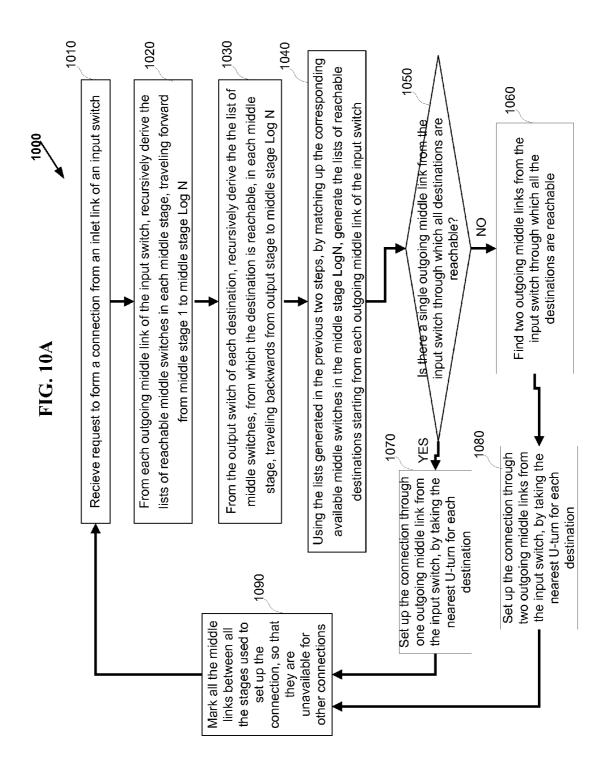

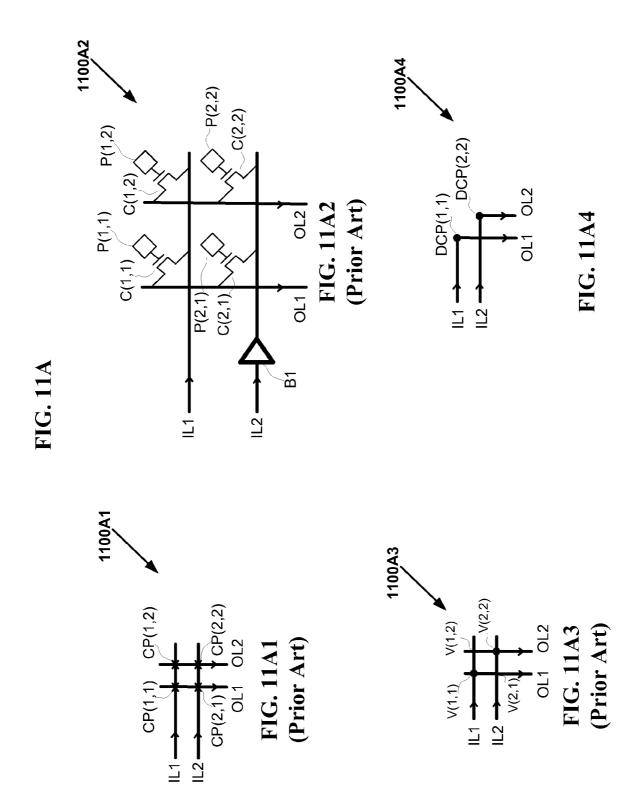

#### FIG. 8A

US 2011/0044329 A1

1

# FULLY CONNECTED GENERALIZED MULTI-LINK MULTI-STAGE NETWORKS

## CROSS REFERENCE TO RELATED APPLICATIONS

[0001] This application is related to and claims priority of the PCT Application Serial No. PCT/US08/64604 entitled "FULLY CONNECTED GENERALIZED MULTI-LINK MULTI-STAGE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 22, 2008, the U.S. Provisional Patent Application Ser. No. 60/940,389 entitled "FULLY CONNECTED GENERAL-IZED REARRANGEABLY NONBLOCKING MULTI-LINK MULTI-STAGE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007, the U.S. Provisional Patent Application Ser. No. 60/940,391 entitled "FULLY CONNECTED GENER-ALIZED FOLDED MULTI-STAGE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007 and the U.S. Provisional Patent Application Ser. No. 60/940,392 entitled "FULLY CON-NECTED GENERALIZED STRICTLY NONBLOCKING MULTI-LINK MULTI-STAGE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007.

[0002] This application is related to and incorporates by reference in its entirety the U.S. application Ser. No. 12/530, 207 entitled "FULLY CONNECTED GENERALIZED MULTI-STAGE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed Sep. 6, 2009, the PCT Application Serial No. PCT/US08/56064 entitled "FULLY CONNECTED GENERALIZED MULTI-STAGE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed Mar. 6, 2008, the U.S. Provisional Patent Application Ser. No. 60/905,526 entitled "LARGE SCALE CROSSPOINT REDUCTION WITH NONBLOCKING UNICAST & MULTICAST IN ARBITRARILY LARGE MULTI-STAGE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed Mar. 6, 2007, and the U.S. Provisional Patent Application Ser. No. 60/940,383 entitled "FULLY CONNECTED GENERALIZED MULTI-STAGE NET-WORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007.

[0003] This application is related to and incorporates by reference in its entirety the US Patent Application Docket No. V-0038US entitled "FULLY CONNECTED GENERAL-IZED BUTTERFLY FAT TREE NETWORKS" by Venkat Konda assigned to the same assignee as the current application filed concurrently, the PCT Application Serial No. PCT/ US08/64603 entitled "FULLY CONNECTED GENERAL-IZED BUTTERFLY FAT TREE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 22, 2008, the U.S. Provisional Patent Application Ser. No. 60/940,387 entitled "FULLY CONNECTED GENERALIZED BUTTERFLY FAT TREE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007, and the U.S. Provisional Patent Application Ser. No. 60/940,390 entitled "FULLY CONNECTED GENERALIZED MULTI-LINK BUTTER-FLY FAT TREE NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007.

[0004] This application is related to and incorporates by reference in its entirety the US Patent Application Docket No. V-0045US entitled "VLSI LAYOUTS OF FULLY CONNECTED GENERALIZED NETWORKS" by Venkat Konda assigned to the same assignee as the current application filed concurrently, the PCT Application Serial No. PCT/US08/64605 entitled "VLSI LAYOUTS OF FULLY CONNECTED GENERALIZED NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 22, 2008, and the U.S. Provisional Patent Application Ser. No. 60/940,394 entitled "VLSI LAYOUTS OF FULLY CONNECTED GENERALIZED NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed May 25, 2007.

[0005] This application is related to and incorporates by reference in its entirety the U.S. Provisional Patent Application Ser. No. 61/252,603 entitled "VLSI LAYOUTS OF FULLY CONNECTED NETWORKS WITH LOCALITY EXPLOITATION" by Venkat Konda assigned to the same assignee as the current application, filed Oct. 16, 2009.

[0006] This application is related to and incorporates by reference in its entirety the U.S. Provisional Patent Application Ser. No. 61/252,609 entitled "VLSI LAYOUTS OF FULLY CONNECTED GENERALIZED AND PYRAMID NETWORKS" by Venkat Konda assigned to the same assignee as the current application, filed Oct. 16, 2009.

#### BACKGROUND OF INVENTION

[0007] Clos switching network, Benes switching network, and Cantor switching network are a network of switches configured as a multi-stage network so that fewer switching points are necessary to implement connections between its inlet links (also called "inputs") and outlet links (also called "outputs") than would be required by a single stage (e.g. crossbar) switch having the same number of inputs and outputs. Clos and Benes networks are very popularly used in digital crossconnects, switch fabrics and parallel computer systems. However Clos and Benes networks may block some of the connection requests.

[0008] There are generally three types of nonblocking networks: strictly nonblocking; wide sense nonblocking; and rearrangeably nonblocking (See V. E. Benes, "Mathematical Theory of Connecting Networks and Telephone Traffic" Academic Press, 1965 that is incorporated by reference, as background). In a rearrangeably nonblocking network, a connection path is guaranteed as a result of the networks ability to rearrange prior connections as new incoming calls are received. In strictly nonblocking network, for any connection request from an inlet link to some set of outlet links, it is always possible to provide a connection path through the network to satisfy the request without disturbing other existing connections, and if more than one such path is available, any path can be selected without being concerned about realization of future potential connection requests. In wide-sense nonblocking networks, it is also always possible to provide a connection path through the network to satisfy the request without disturbing other existing connections, but in this case the path used to satisfy the connection request must be carefully selected so as to maintain the nonblocking connecting capability for future potential connection requests.

[0009] Butterfly Networks, Banyan Networks, Batcher-Banyan Networks, Baseline Networks, Delta Networks, Omega Networks and Flip networks have been widely studied particularly for self routing packet switching applications.

US 2011/0044329 A1

Also Benes Networks with radix of two have been widely studied and it is known that Benes Networks of radix two are shown to be built with back to back baseline networks which are rearrangeably nonblocking for unicast connections.

[0010] U.S. Pat. No. 5,451,936 entitled "Non-blocking Broadcast Network" granted to Yang et al. is incorporated by reference herein as background of the invention. This patent describes a number of well known nonblocking multi-stage switching network designs in the background section at column 1, line 22 to column 3, 59. An article by Y. Yang, and G. M., Masson entitled, "Non-blocking Broadcast Switching Networks" IEEE Transactions on Computers, Vol. 40, No. 9, September 1991 that is incorporated by reference as background indicates that if the number of switches in the middle stage, m, of a three-stage network satisfies the relation m≧min((n−1)(x+r¹/x)) where 1≦x≤min(n−1,r), the resulting network is nonblocking for multicast assignments. In the relation, r is the number of switches in the input stage, and n is the number of inlet links in each input switch.

[0011] U.S. Pat. No. 6,885,669 entitled "Rearrangeably Nonblocking Multicast Multi-stage Networks" by Konda showed that three-stage Clos network is rearrangeably nonblocking for arbitrary fan-out multicast connections when m≥2×n. And U.S. Pat. No. 6,868,084 entitled "Strictly Nonblocking Multicast Multi-stage Networks" by Konda showed that three-stage Clos network is strictly nonblocking for arbitrary fan-out multicast connections when m≥3×n−1.

[0012] In general multi-stage networks for stages of more than three and radix of more than two are not well studied. An article by Charles Clos entitled "A Study of Non-Blocking Switching Networks" The Bell Systems Technical Journal, Volume XXXII, January 1953, No. 1, pp. 406-424 showed a way of constructing large multi-stage networks by recursive substitution with a crosspoint complexity of  $d^2 \times N \times (\log_4 N)^2$ 58 for strictly nonblocking unicast network. Similarly U.S. Pat. No. 6,885,669 entitled "Rearrangeably Nonblocking Multicast Multi-stage Networks" by Konda showed a way of constructing large multi-stage networks by recursive substitution for rearrangeably nonblocking multicast network. An article by D. G. Cantor entitled "On Non-Blocking Switching Networks" 1: pp. 367-377, 1972 by John Wiley and Sons, Inc., showed a way of constructing large multi-stage networks with a crosspoint complexity of  $d^2 \times N \times (\log_d N)^2$  for strictly nonblocking unicast, (by using log<sub>d</sub> N number of Benes Networks for d=2) and without counting the crosspoints in multiplexers and demultiplexers. Jonathan Turner studied the cascaded Benes Networks with radices larger than two, for nonblocking multicast with 10 times the crosspoint complexity of that of nonblocking unicast for a network of size N=256.

[0013] The crosspoint complexity of all these networks is prohibitively large to implement the interconnect for multicast connections particularly in field programmable gate array (FPGA) devices, programmable logic devices (PLDs), field programmable interconnect Chips (FPICs), digital crossconnects, switch fabrics and parallel computer systems.

#### SUMMARY OF INVENTION

[0014] A generalized multi-link multi-stage network comprising  $(2 \times \log_d N) - 1$  stages is operated in strictly nonblocking manner for unicast includes an input stage having N/d switches with each of them having d inlet links and 2×d outgoing links connecting to second stage switches, an output stage having N/d switches with each of them having d outlet

links and  $2\times d$  incoming links connecting from switches in the penultimate stage. The network also has  $(2\times \log_d N)-3$  middle stages with each middle stage having N/d switches, and each switch in the middle stage has  $2\times d$  incoming links connecting from the switches in its immediate preceding stage, and  $2\times d$  outgoing links connecting to the switches in its immediate succeeding stage. Also the same generalized multi-link multi-stage network is operated in rearrangeably nonblocking manner for arbitrary fan-out multicast and each multicast connection is set up by use of at most two outgoing links from the input stage switch.

[0015] A generalized multi-link multi-stage network comprising  $(2 \times \log_d N) - 1$  stages is operated in strictly nonblocking manner for multicast includes an input stage having N/d switches with each of them having d inlet links and  $3 \times d$  outgoing links connecting to second stage switches, an output stage having N/d switches with each of them having d outlet links and  $3 \times d$  incoming links connecting from switches in the penultimate stage. The network also has  $(2 \times \log_d N) - 3$  middle stages with each middle stage having N/d switches, and each switch in the middle stage has  $3 \times d$  incoming links connecting from the switches in its immediate preceding stage, and  $3 \times d$  outgoing links connecting to the switches in its immediate succeeding stage.

#### BRIEF DESCRIPTION OF DRAWINGS

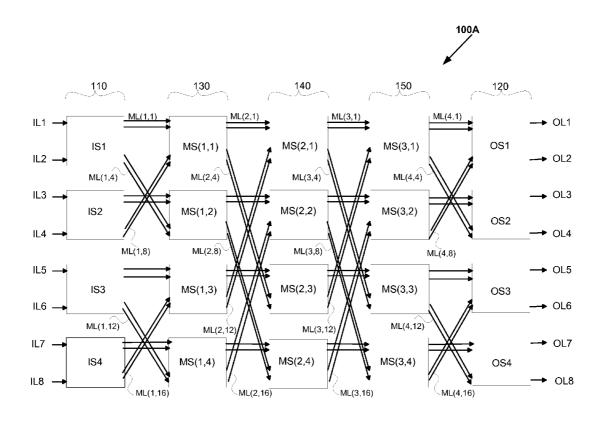

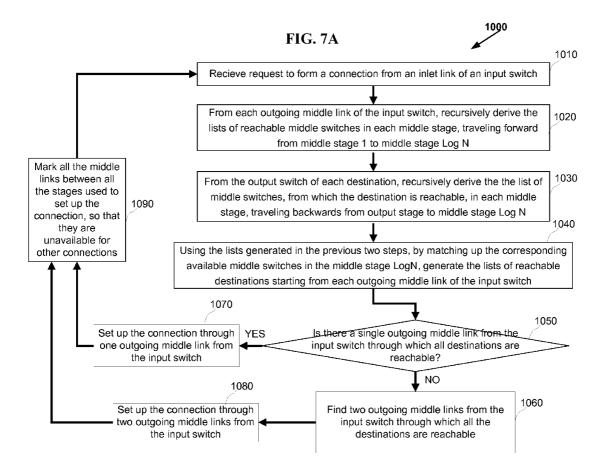

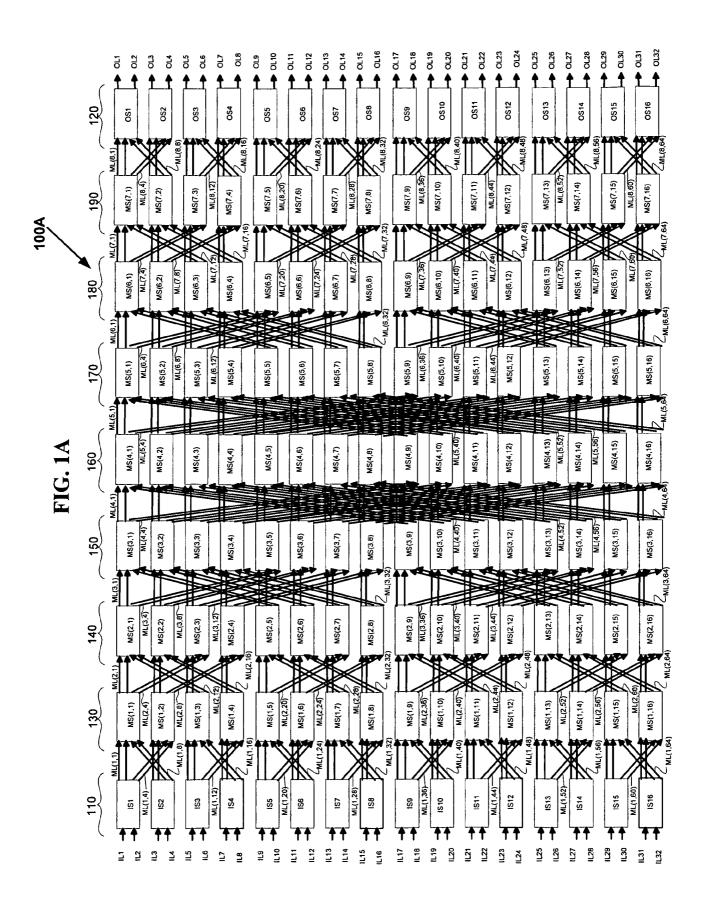

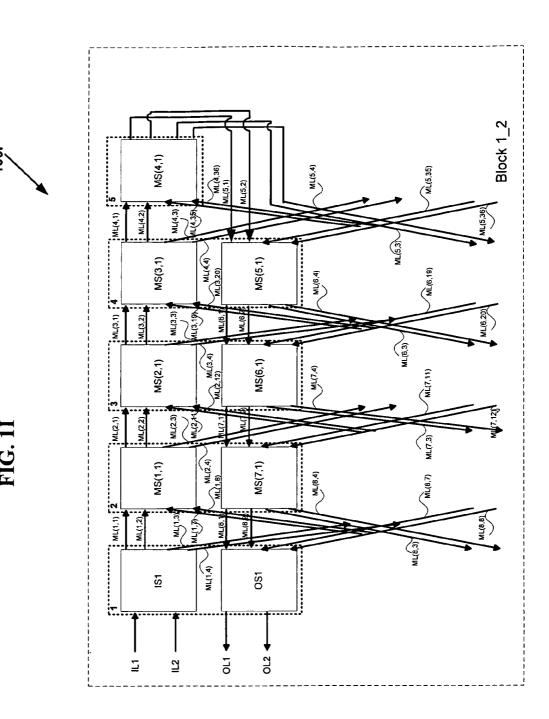

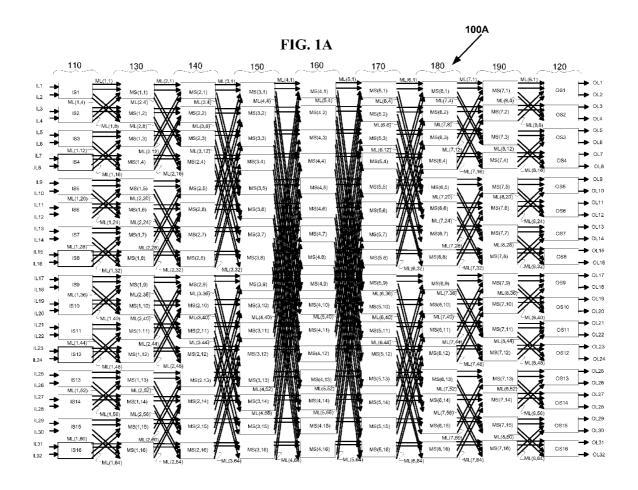

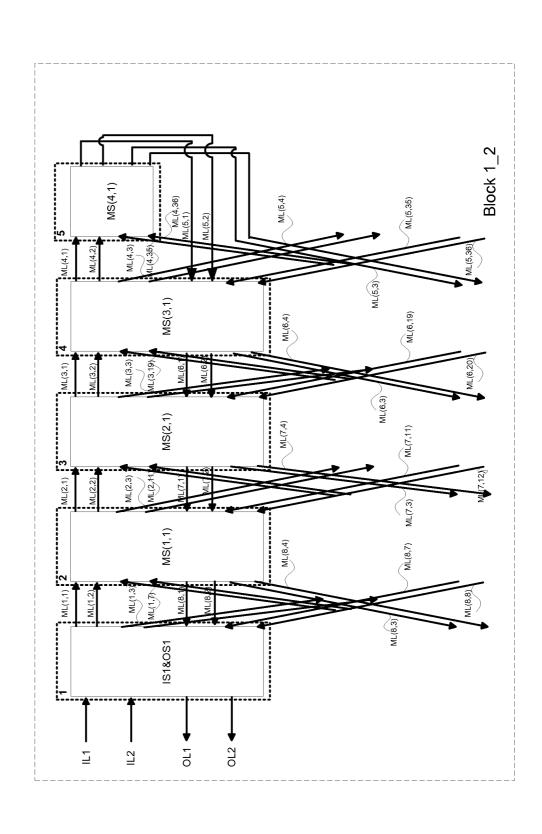

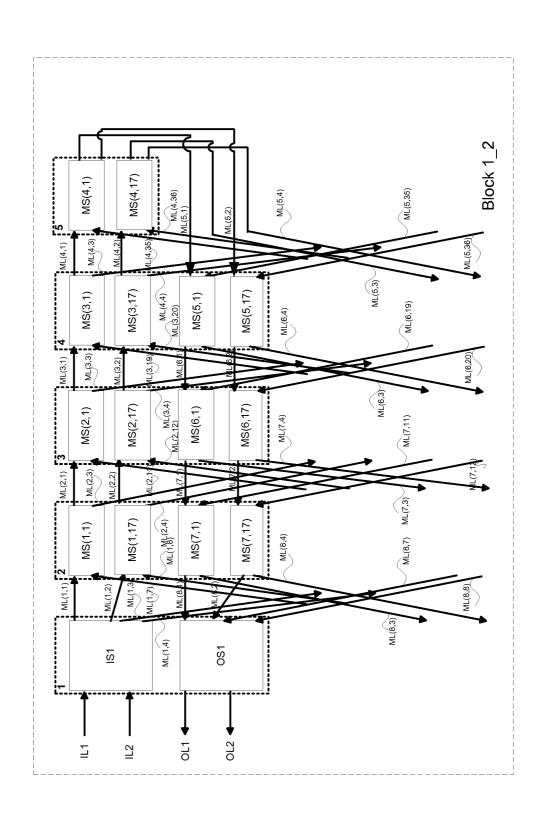

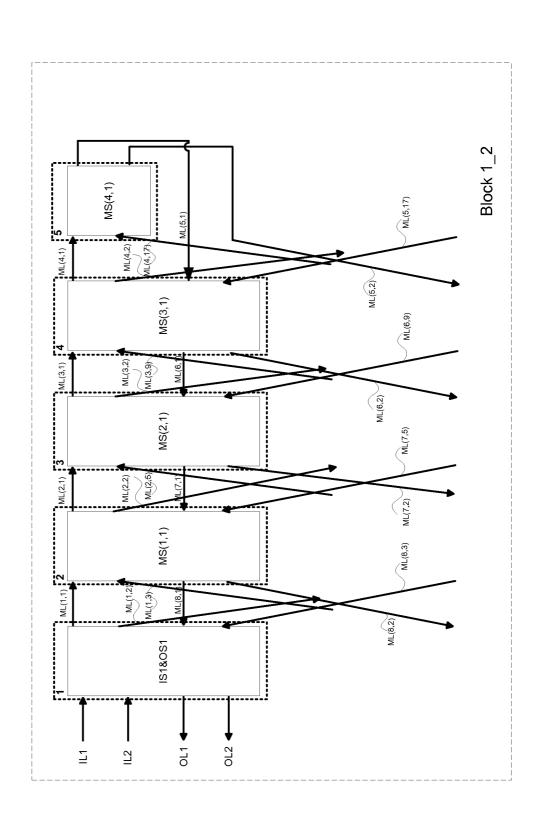

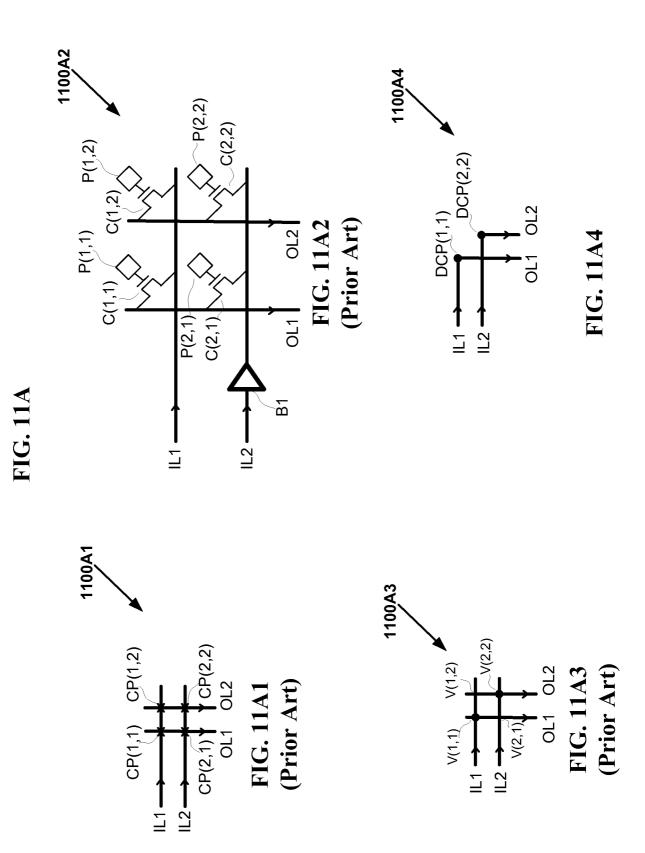

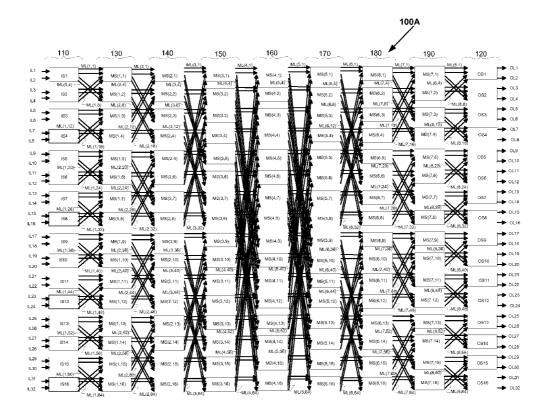

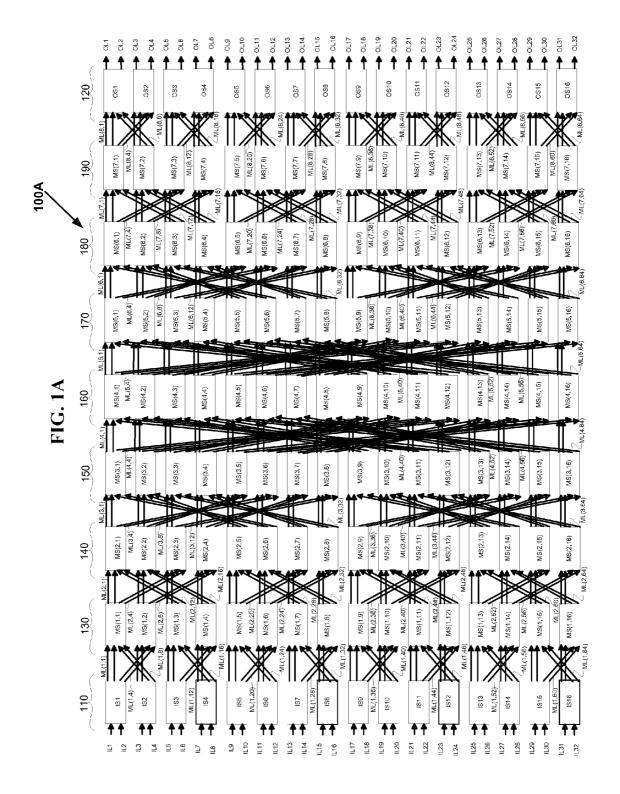

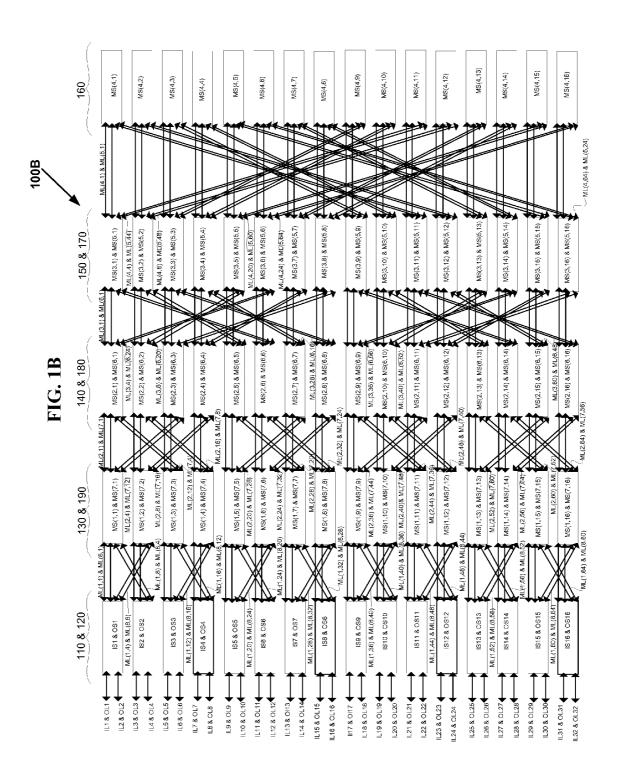

[0016] FIG. 1A is a diagram 100A of an exemplary symmetrical multi-link multi-stage network  $V_{mlink}(N,d,s)$  having inverse Benes connection topology of five stages with N=8, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

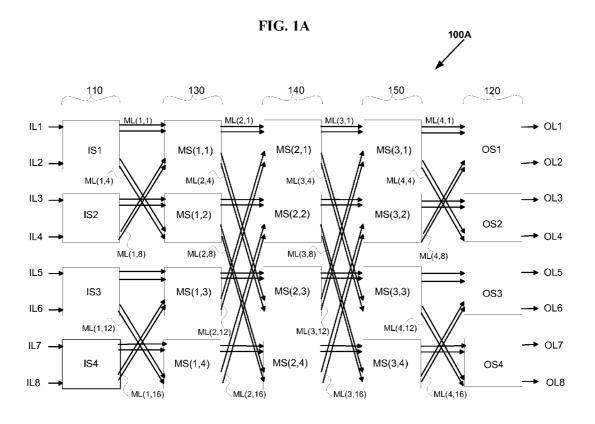

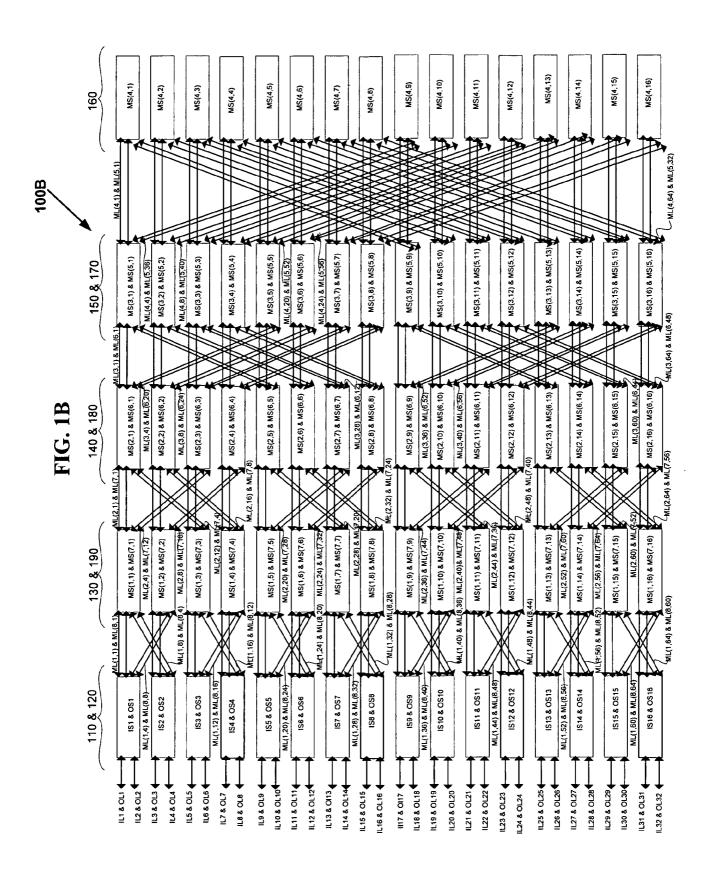

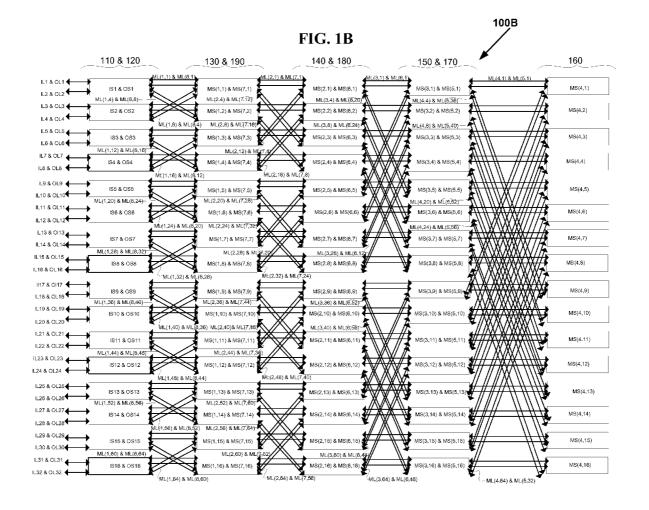

[0017] FIG. 1B is a diagram 100B of an exemplary symmetrical multi-link multi-stage network  $V_{mlink}(N,d,s)$  (having a connection topology built using back-to-back Omega Networks) of five stages with N=8, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

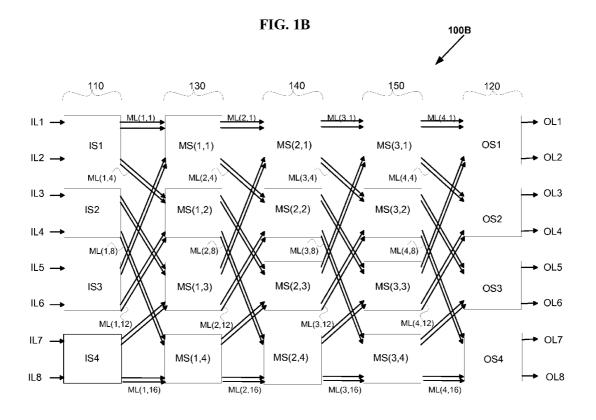

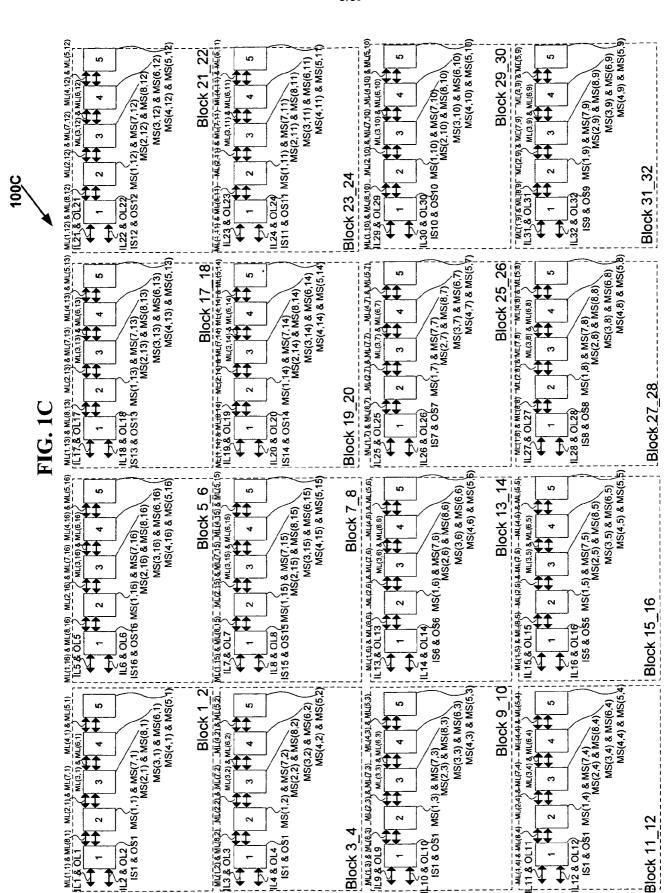

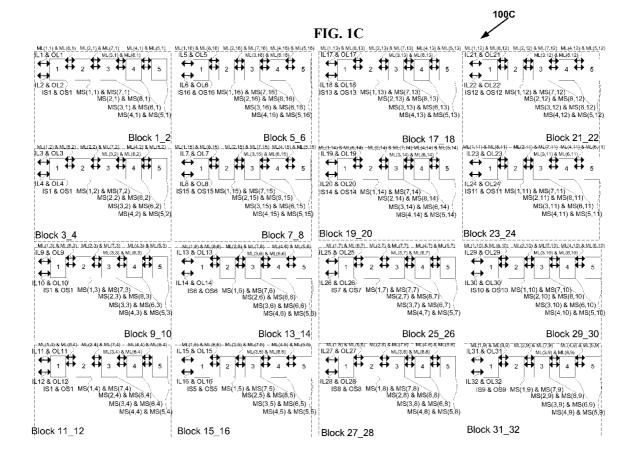

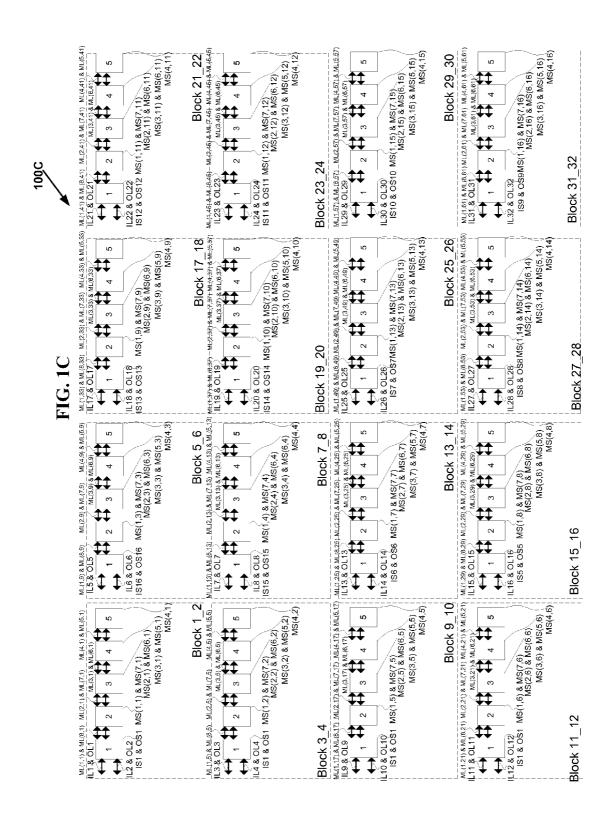

[0018] FIG. 1C is a diagram 100C of an exemplary symmetrical multi-link multi-stage network  $V_{mlink}(N,d,s)$  having an exemplary connection topology of five stages with N=8, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

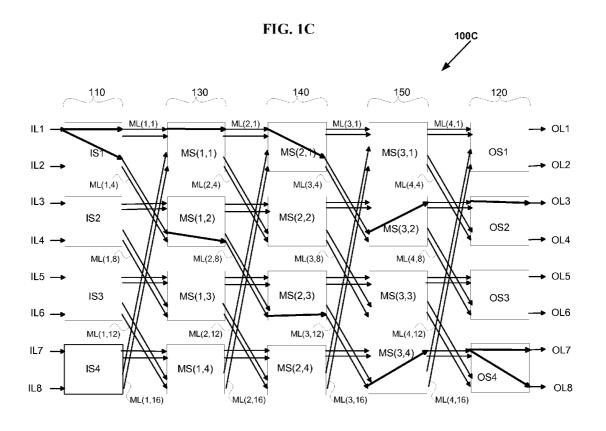

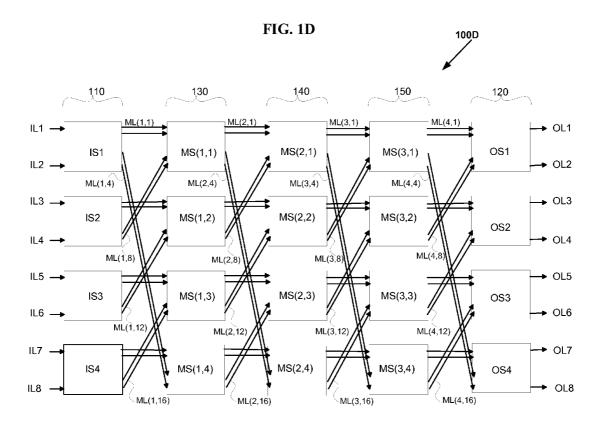

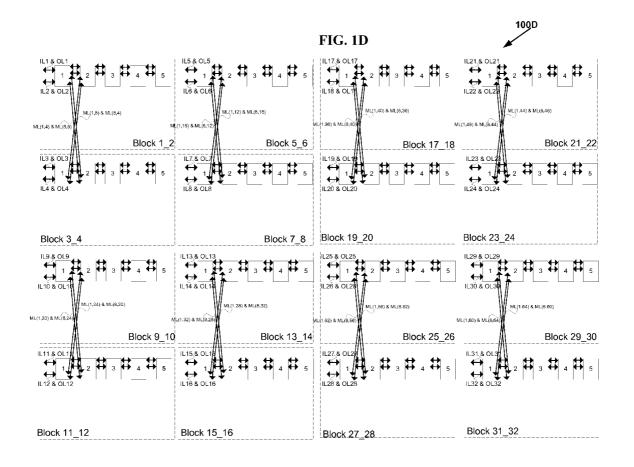

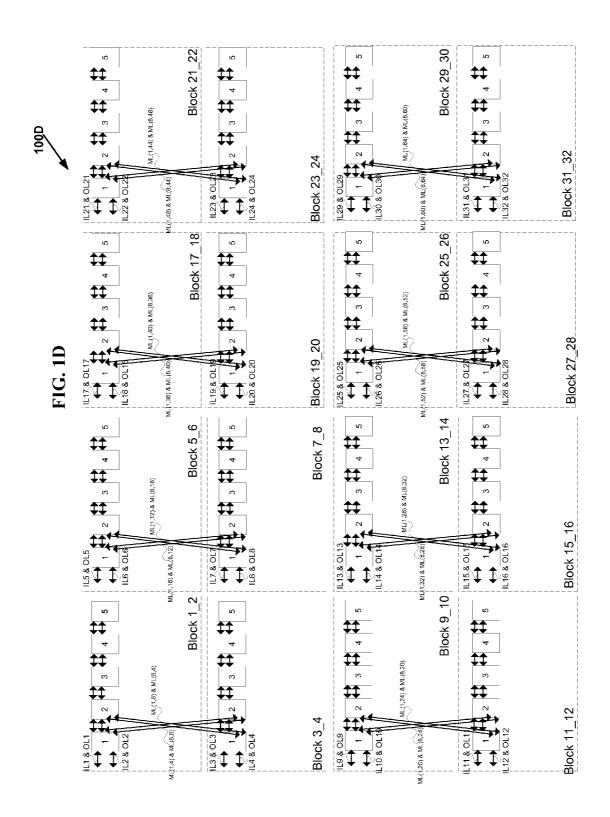

[0019] FIG. 1D is a diagram 100D of an exemplary symmetrical multi-link multi-stage network  $V_{mlink}(N,d,s)$  having an exemplary connection topology of five stages with N=8, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

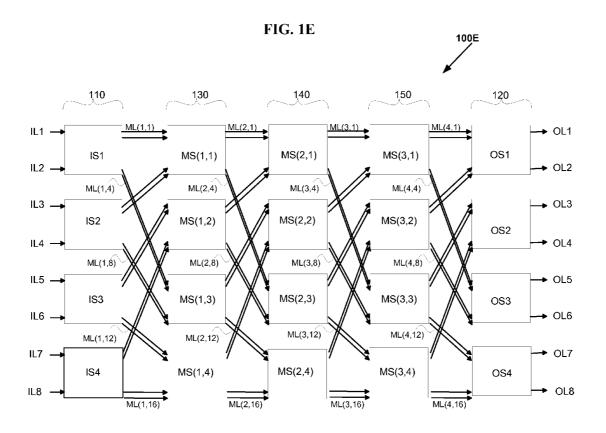

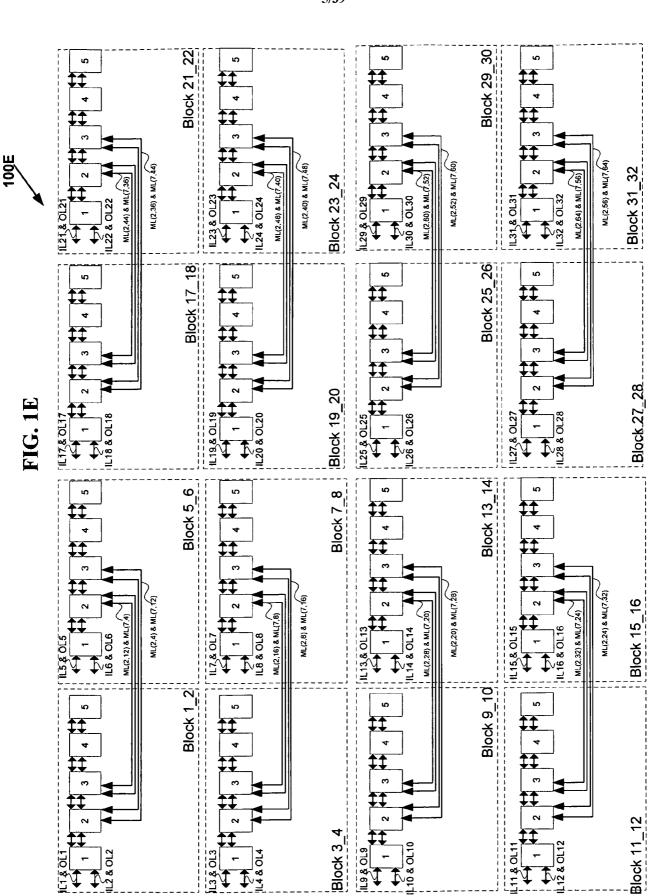

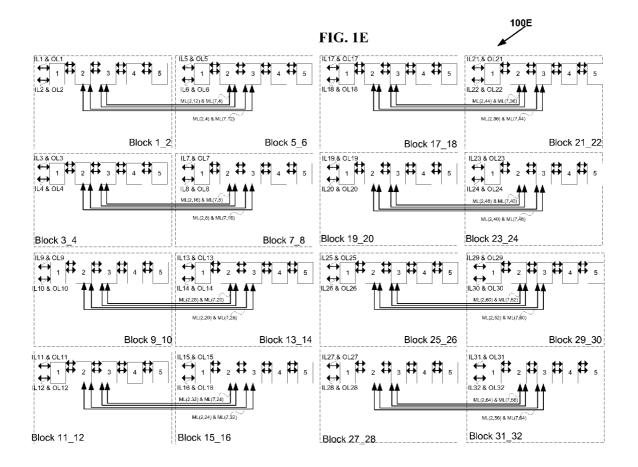

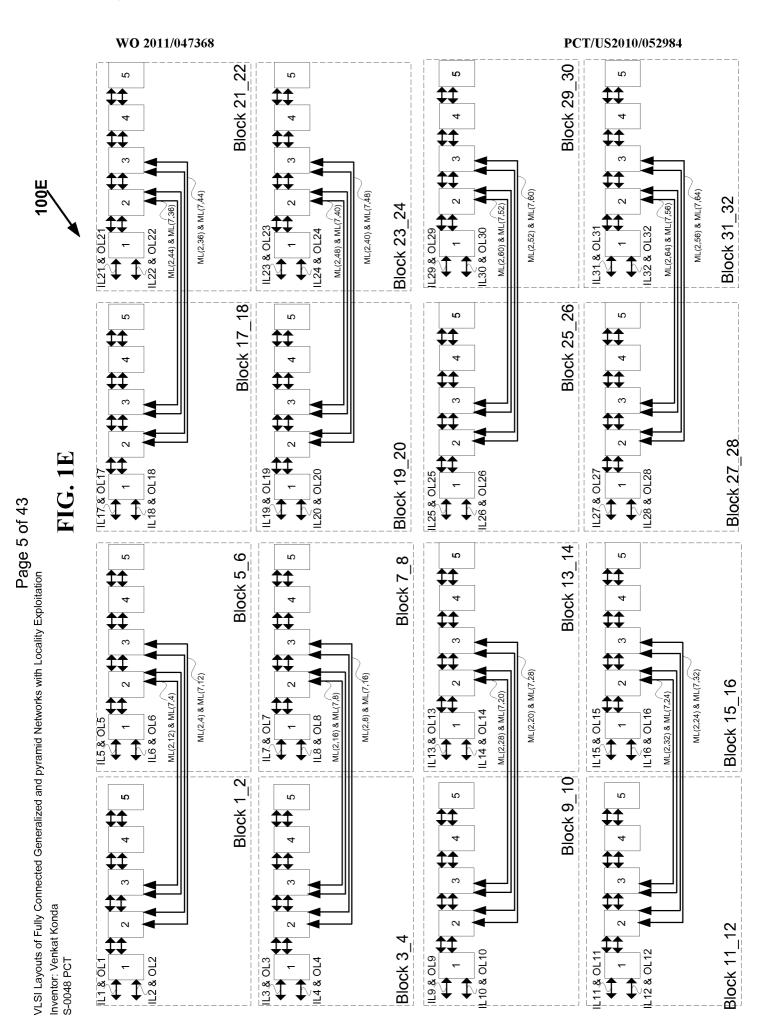

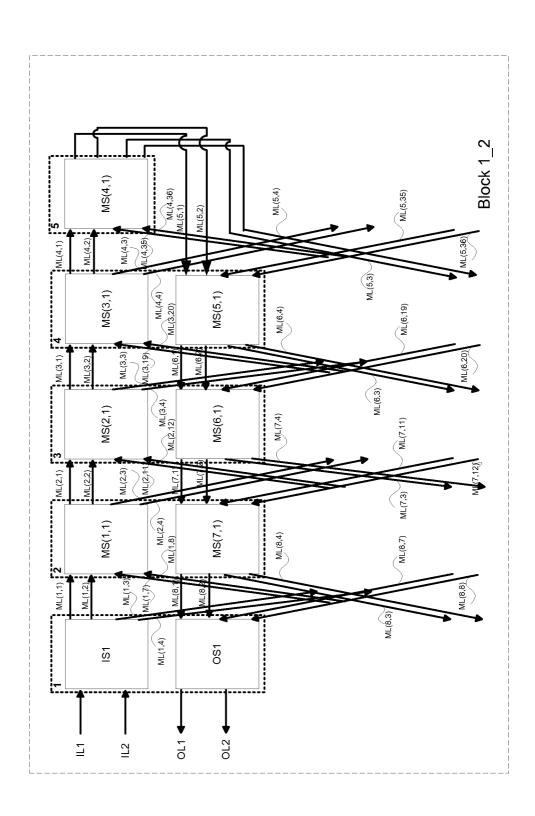

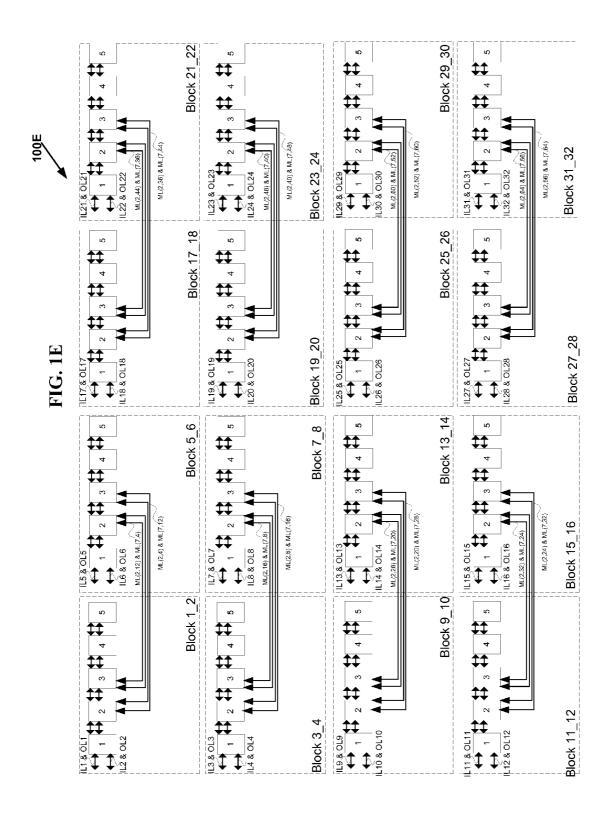

[0020] FIG. 1E is a diagram 100E of an exemplary symmetrical multi-link multi-stage network  $V_{mlink}(N,d,s)$  (having a connection topology called flip network and also known as inverse shuffle exchange network) of five stages with N=8, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

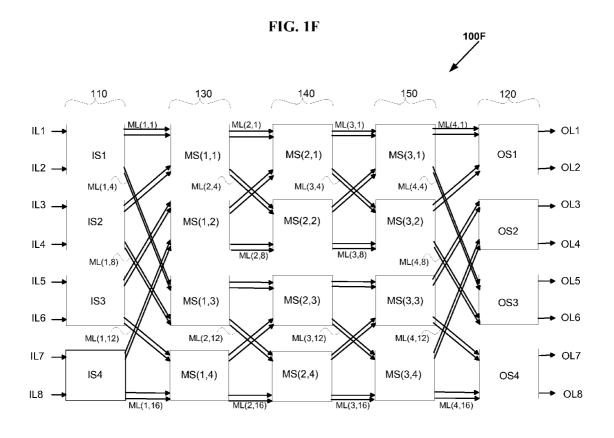

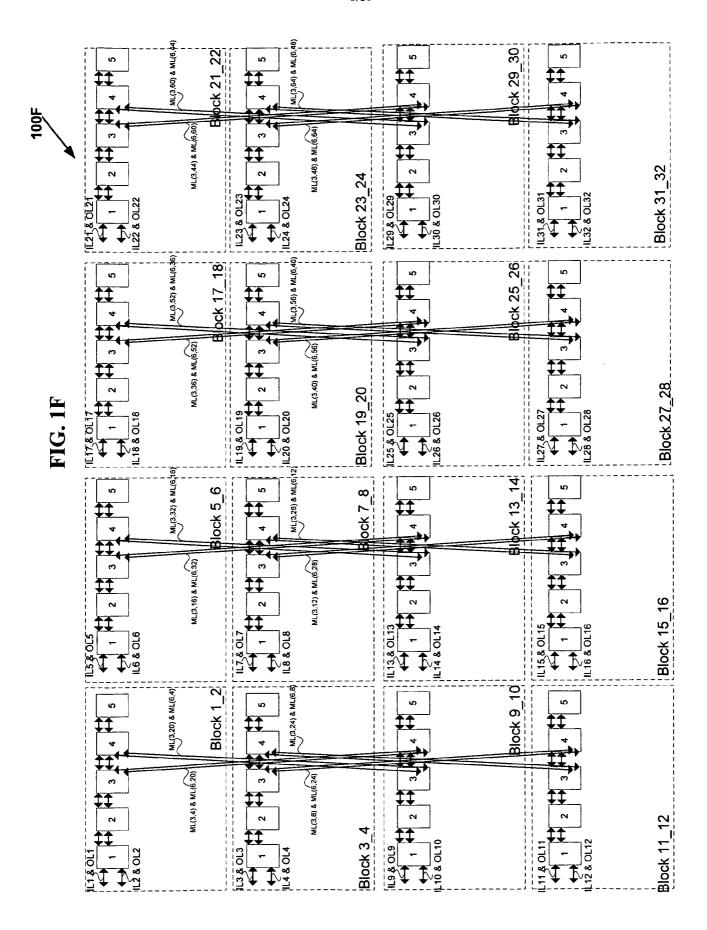

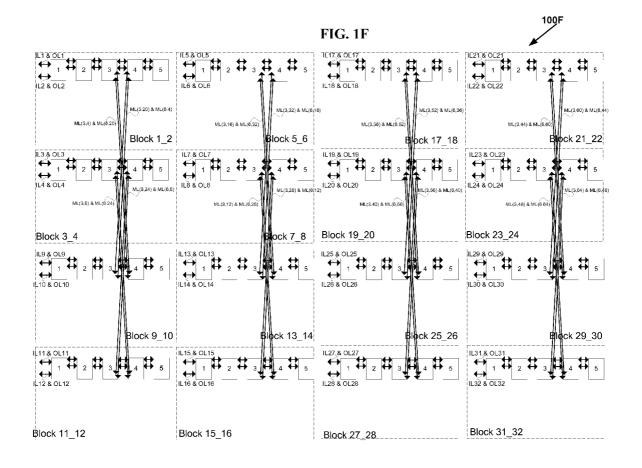

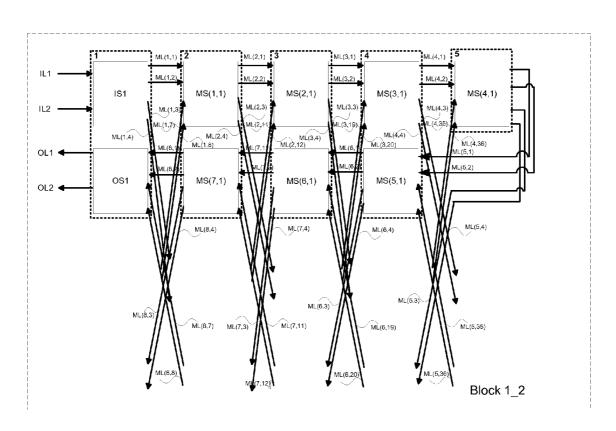

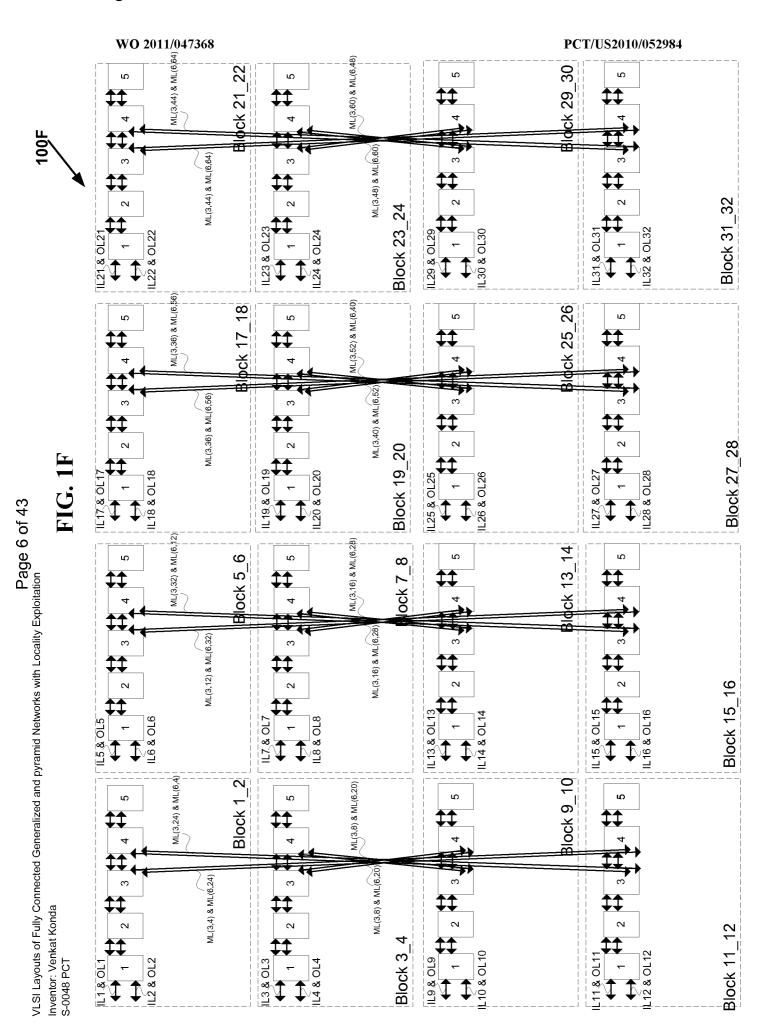

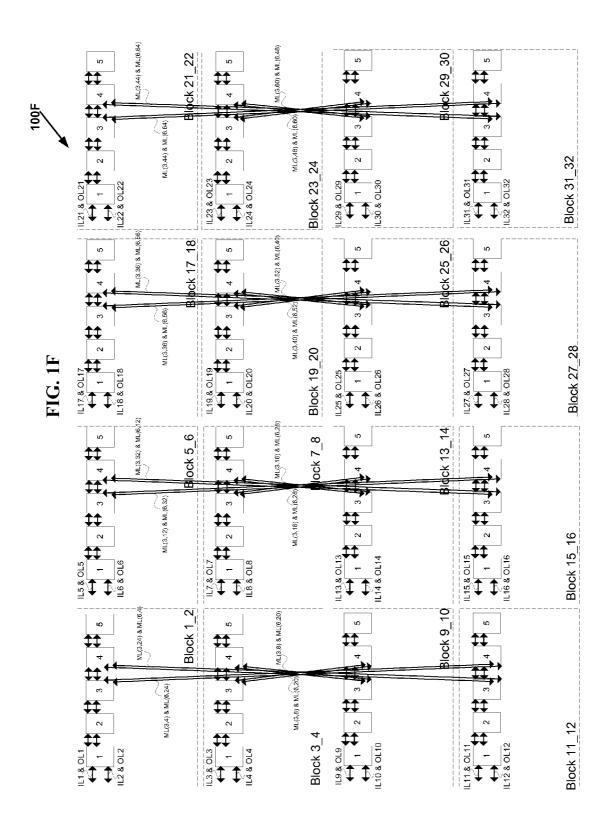

[0021] FIG. 1F is a diagram 100F of an exemplary symmetrical multi-link multi-stage network  $V_{mlink}(N, d, s)$  having

US 2011/0044329 A1

Feb. 24, 2011

Baseline connection topology of five stages with N=8, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the inven-

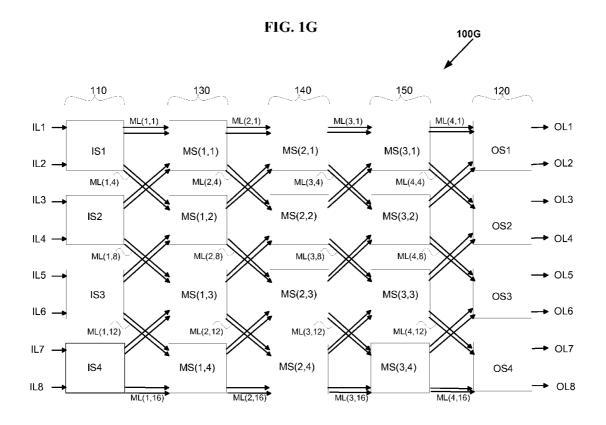

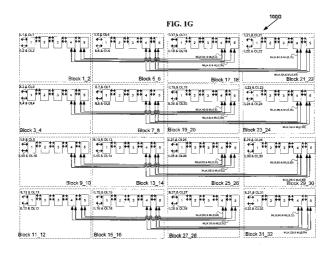

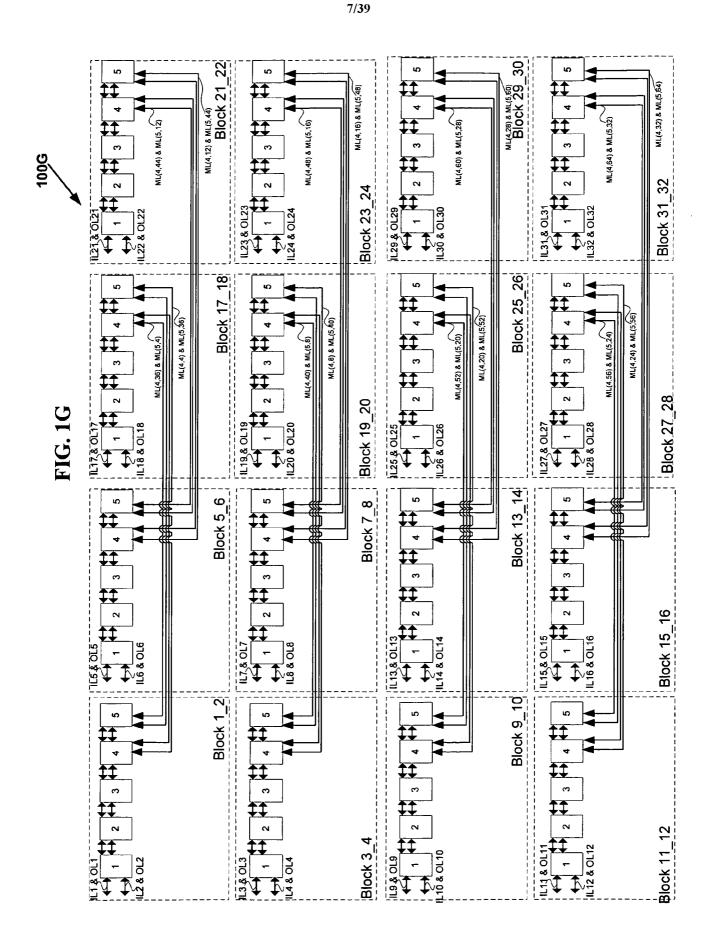

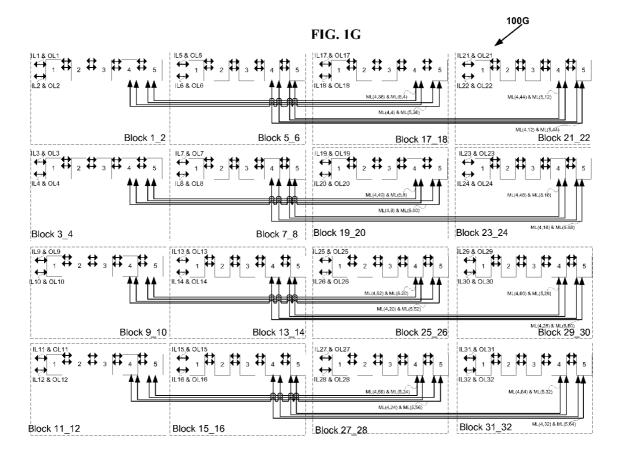

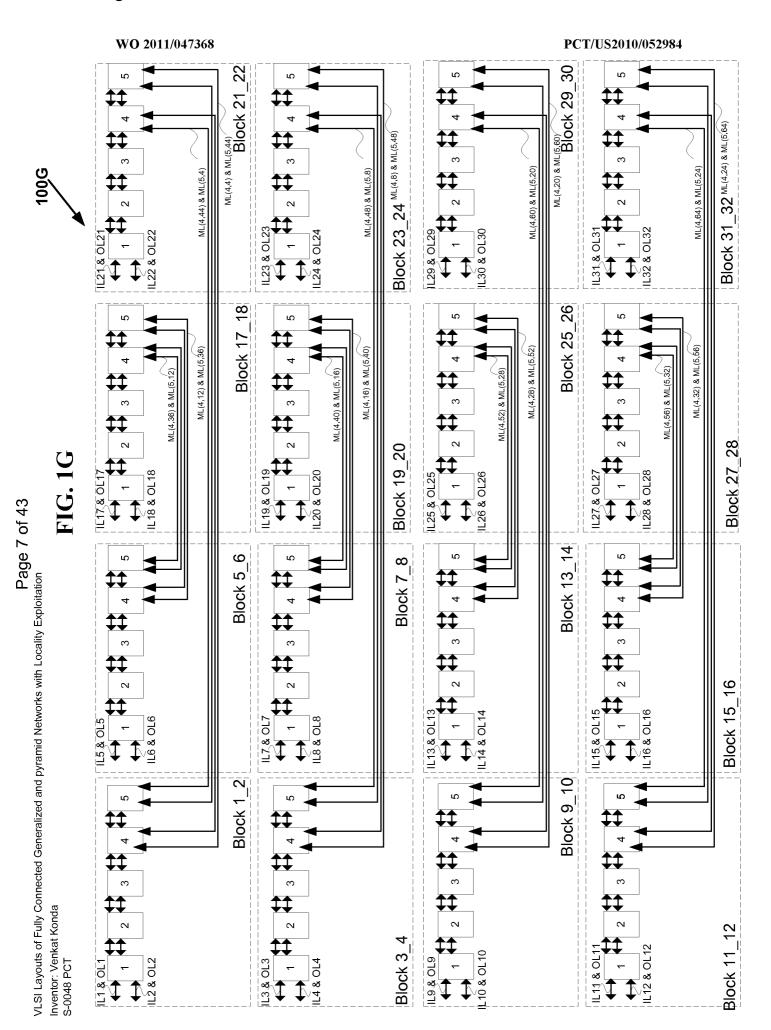

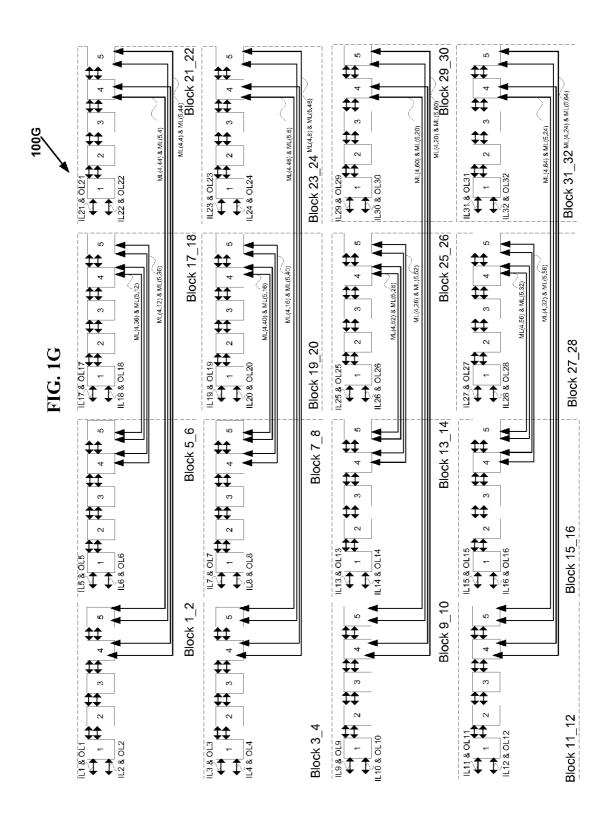

[0022] FIG. 1G is a diagram 100G of an exemplary symmetrical multi-link multi-stage network  $V_{mlink}(N,d,s)$  having an exemplary connection topology of five stages with N=8, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

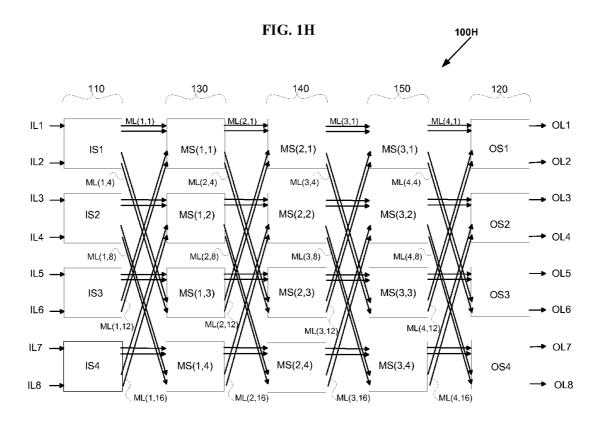

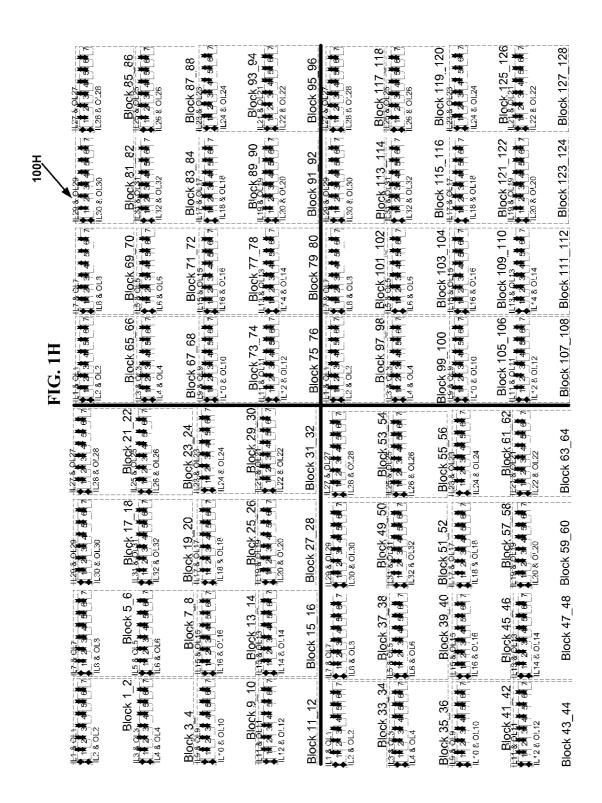

[0023] FIG. 1H is a diagram 100H of an exemplary symmetrical multi-link multi-stage network  $V_{mlink}(N,d,s)$  having an exemplary connection topology of five stages with N=8, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

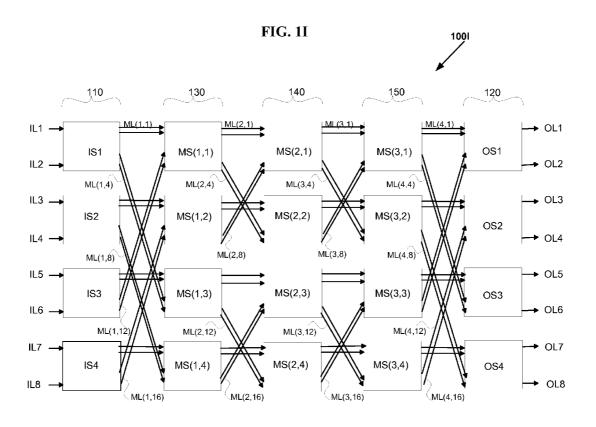

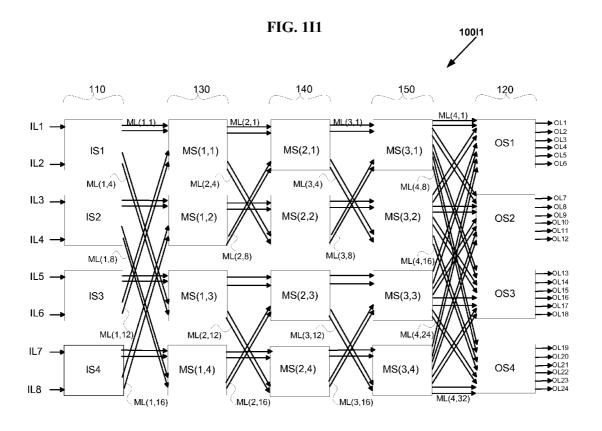

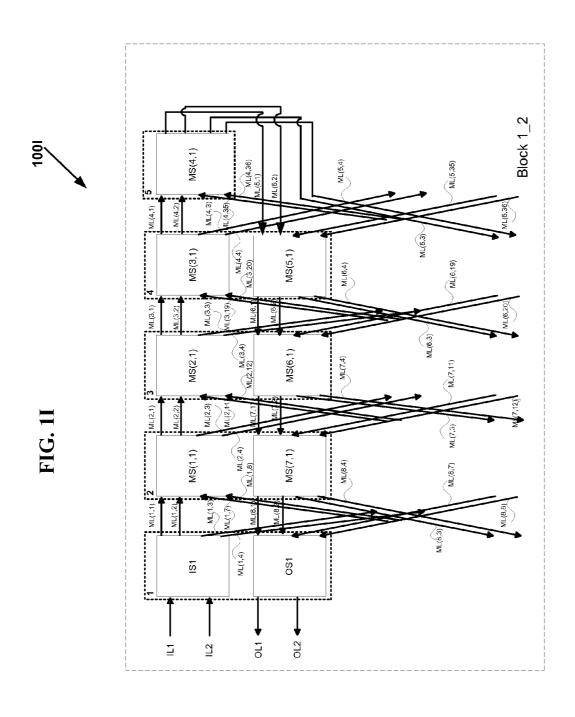

[0024] FIG. 1I is a diagram 100I of an exemplary symmetrical multi-link multi-stage network  $V_{mlink}(N,d,s)$  (having a connection topology built using back-to-back Banyan Networks or back-to-back Delta Networks or equivalently back-to-back Butterfly networks) of five stages with N=8, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

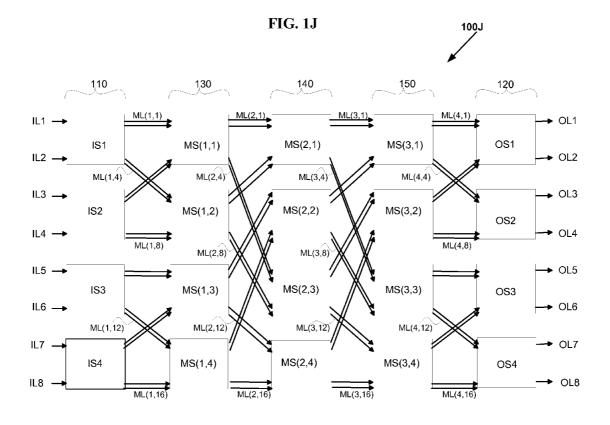

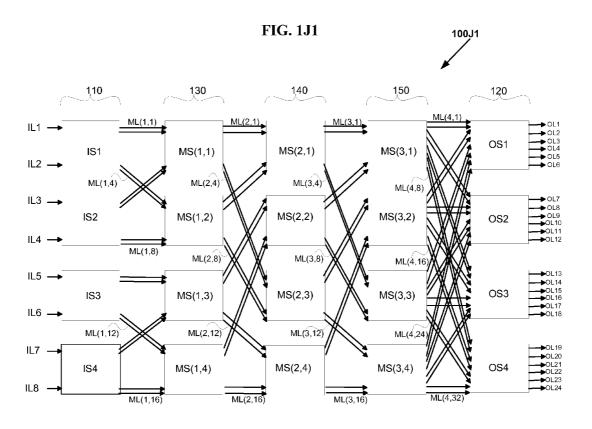

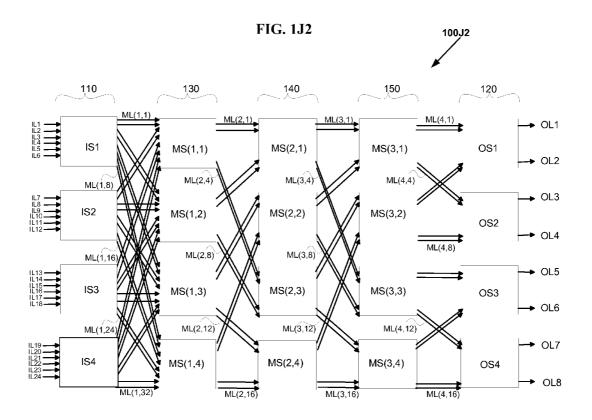

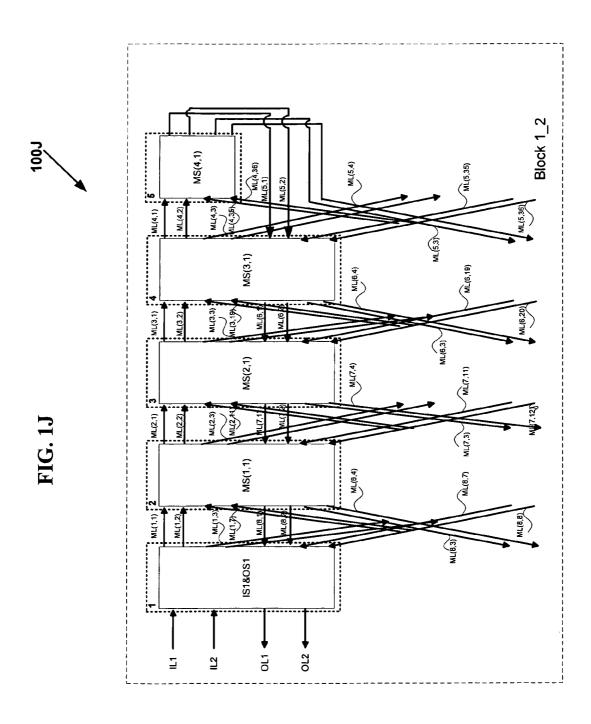

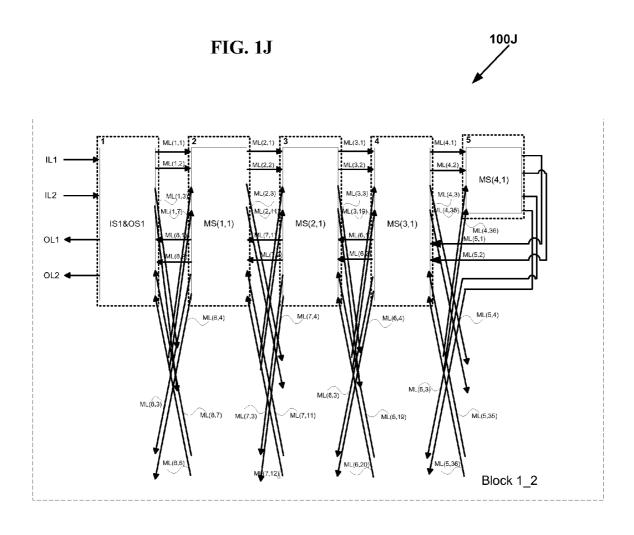

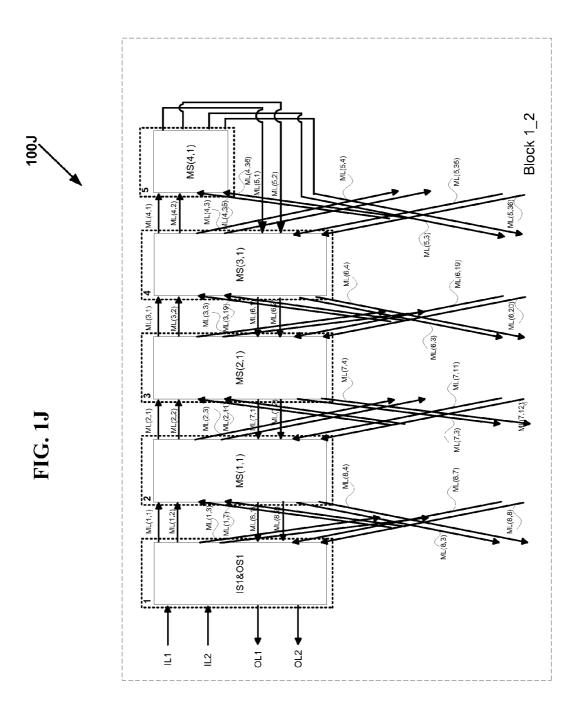

**[0025]** FIG. 1J is a diagram 100J of an exemplary symmetrical multi-link multi-stage network  $V_{mlink}(N,d,s)$  having an exemplary connection topology of five stages with N=8, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

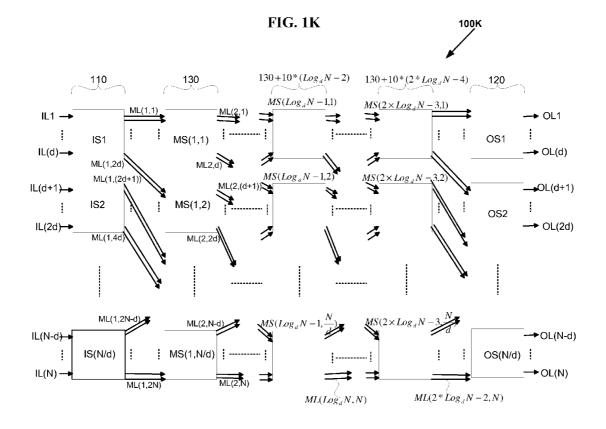

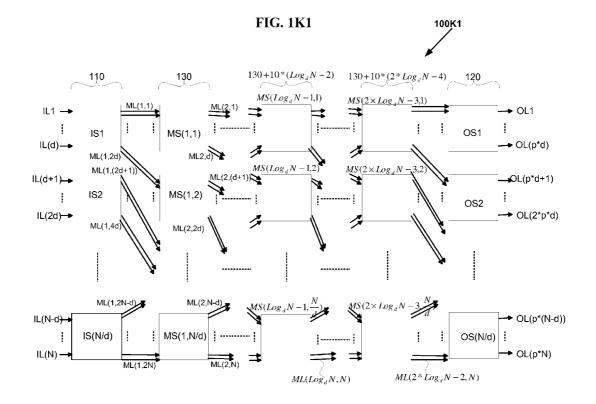

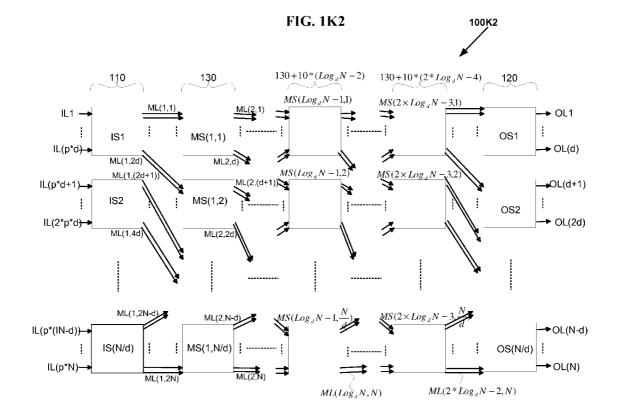

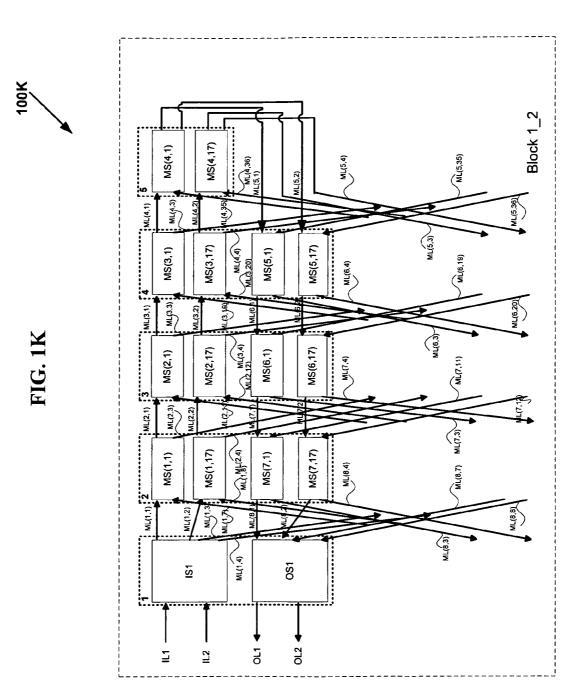

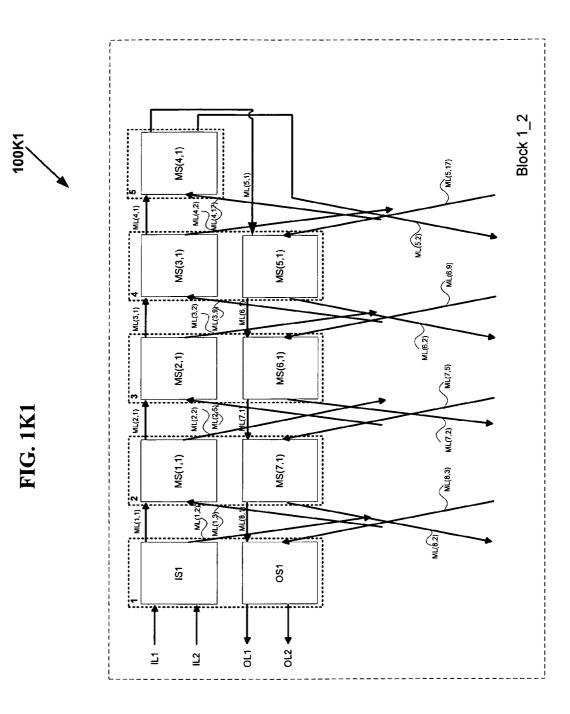

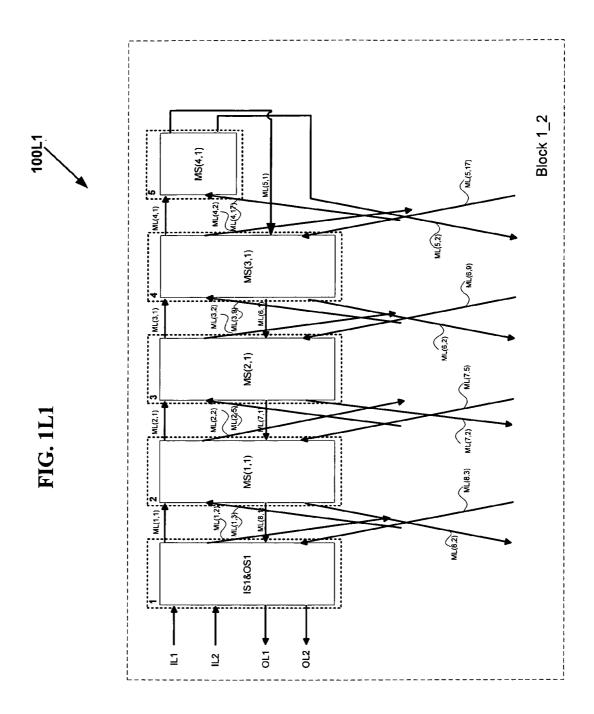

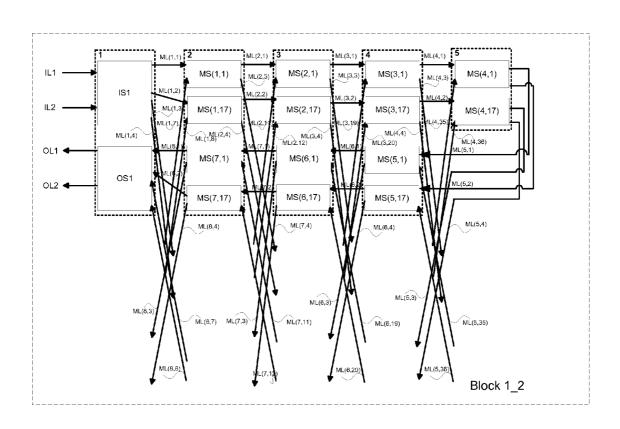

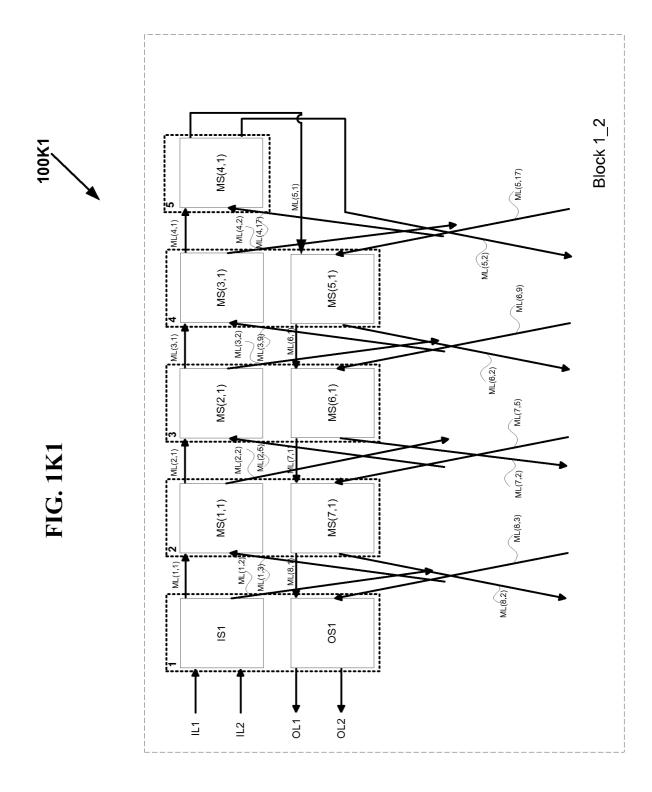

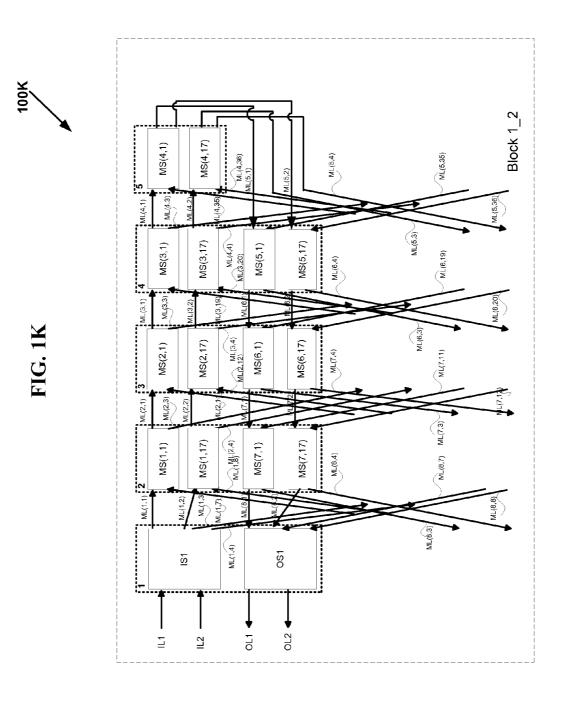

[0026] FIG. 1K is a diagram 100K of a general symmetrical multi-link multi-stage network  $V_{mlink}(N,d,s)$  with  $(2\times\log_dN)-1$  stages with s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

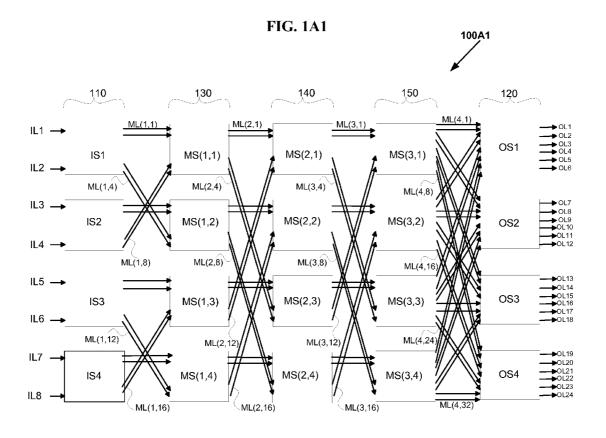

**[0027]** FIG. **1A1** is a diagram **100A1** of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having inverse Benes connection topology of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

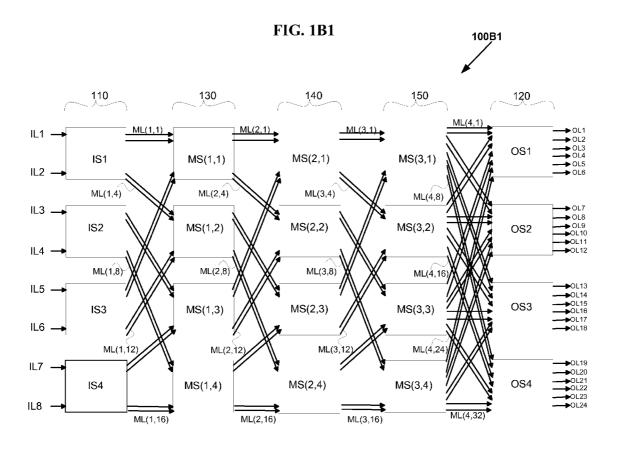

[0028] FIG. 1B1 is a diagram 100B1 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  (having a connection topology built using back-to-back Omega Networks) of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

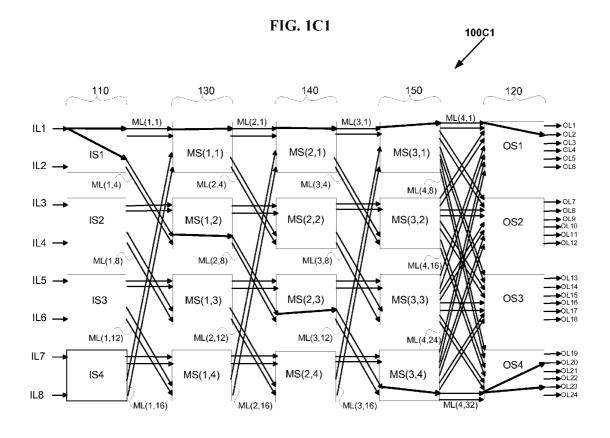

**[0029]** FIG. 1C1 is a diagram 100C1 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having an exemplary connection topology of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

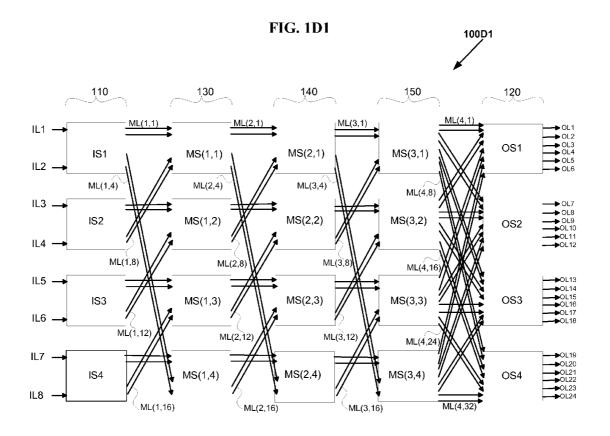

[0030] FIG. 1D1 is a diagram 100D1 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having an exemplary connection topology of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

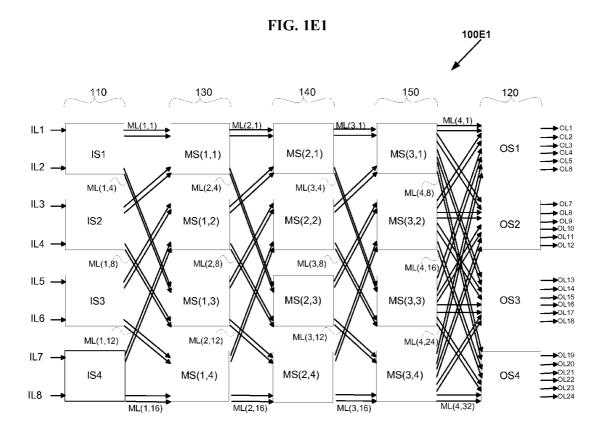

[0031] FIG. 1E1 is a diagram 100E1 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  (having a connection topology called flip network and also known as inverse shuffle exchange network) of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

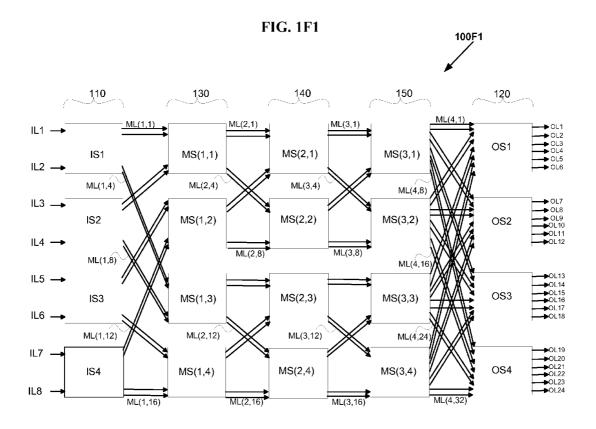

[0032] FIG. 1F1 is a diagram 100F1 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1,\,N_2,\,d,\,s)$  having Baseline connection topology of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, d=2 and s=2, strictly non-blocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

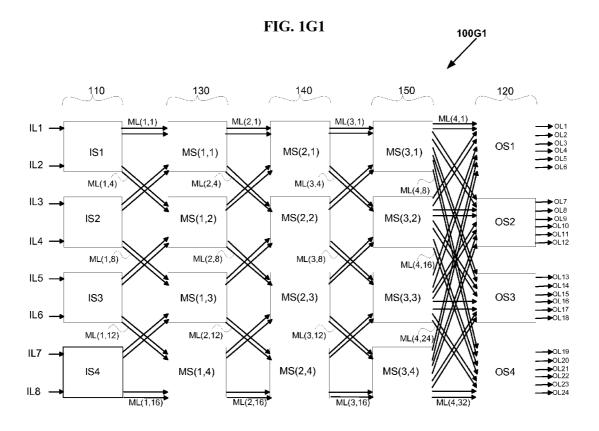

[0033] FIG. 1G1 is a diagram 100G1 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having an exemplary connection topology of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

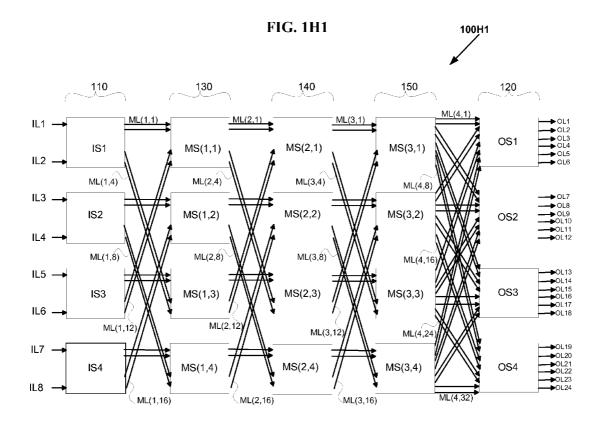

[0034] FIG. 1H1 is a diagram 100H1 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having an exemplary connection topology of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

[0035] FIG. 1I1 is a diagram 100I1 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  (having a connection topology built using back-to-back Banyan Networks or back-to-back Delta Networks or equivalently back-to-back Butterfly networks) of five stages with  $N_1$ =8,  $N_2$ = $p*N_1$ =24 where p=3, d=2 and s=2, strictly non-blocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

[0036] FIG. 1J1 is a diagram 100J1 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having an exemplary connection topology of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, d=2 and s=2, strictly non-blocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

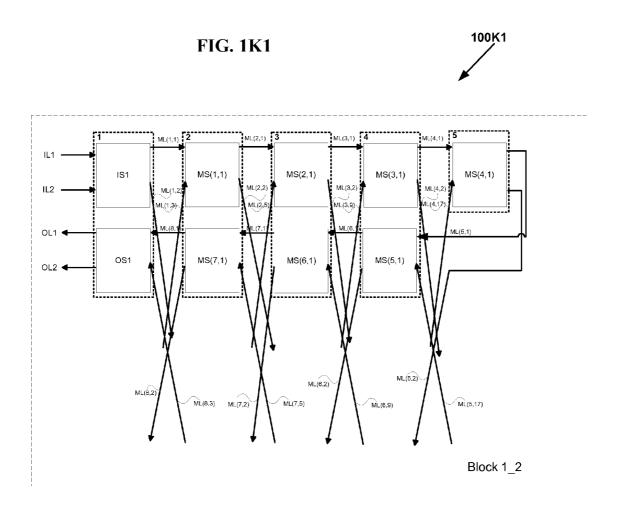

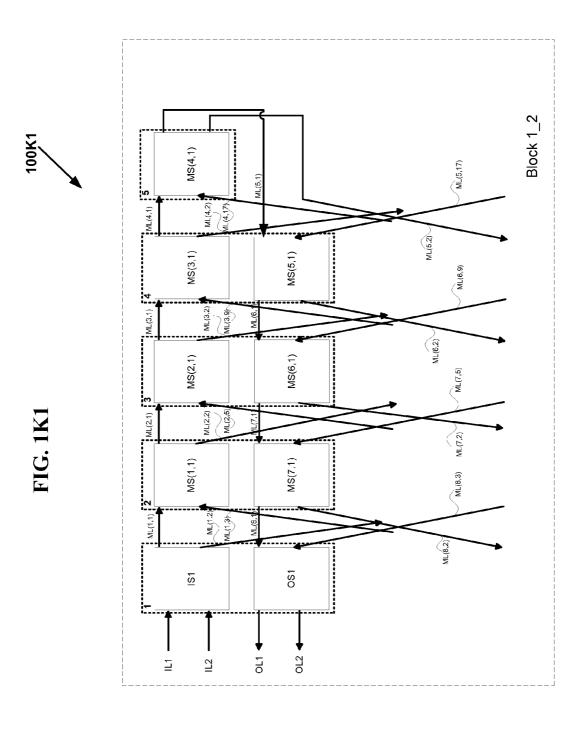

[0037] FIG. 1K1 is a diagram 100K1 of a general asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  with  $(2 \times \log_d N) - 1$  stages with  $N_1 = p * N_2$  and s = 2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

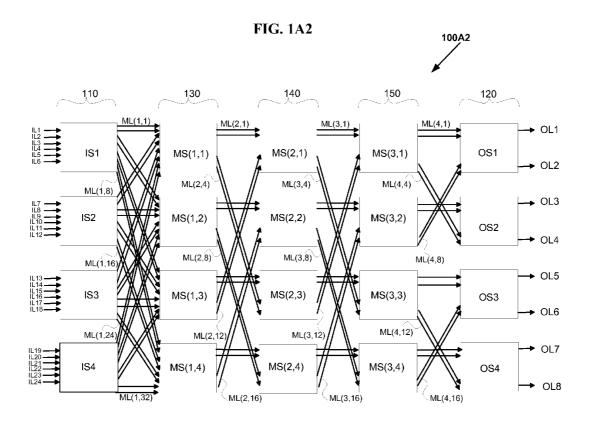

[0038] FIG. 1A2 is a diagram 100A2 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having inverse Benes connection topology of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, d=2 and s=2, strictly nonblocking network for unicast connections and rearrange-

ably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

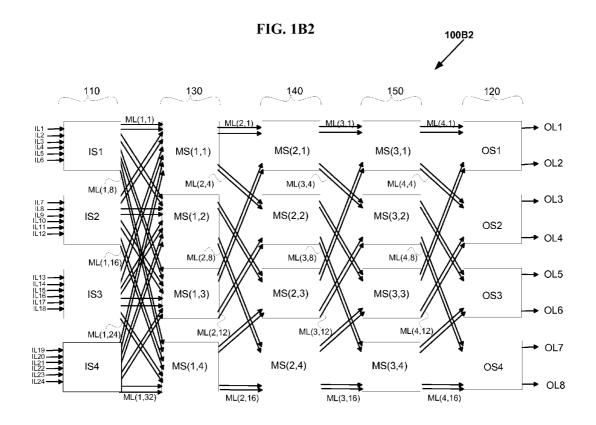

[0039] FIG. 1B2 is a diagram 100B2 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  (having a connection topology built using back-to-back Omega Networks) of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

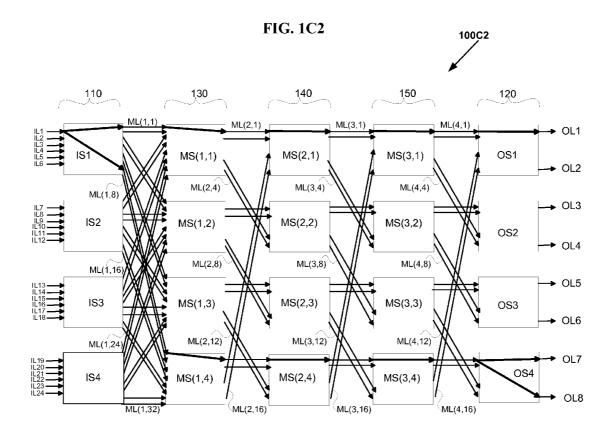

[0040] FIG. 1C2 is a diagram 100C2 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having an exemplary connection topology of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

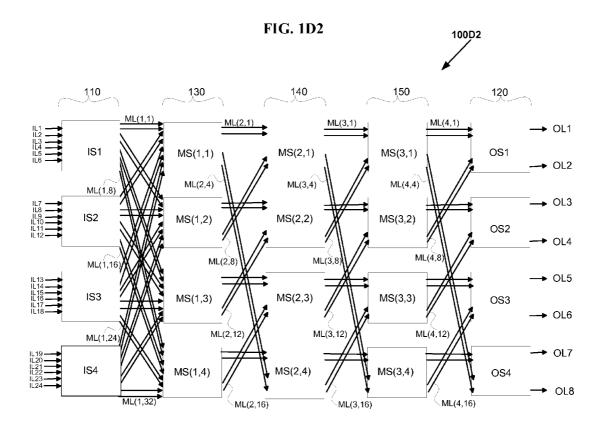

[0041] FIG. 1D2 is a diagram 100D2 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having an exemplary connection topology of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

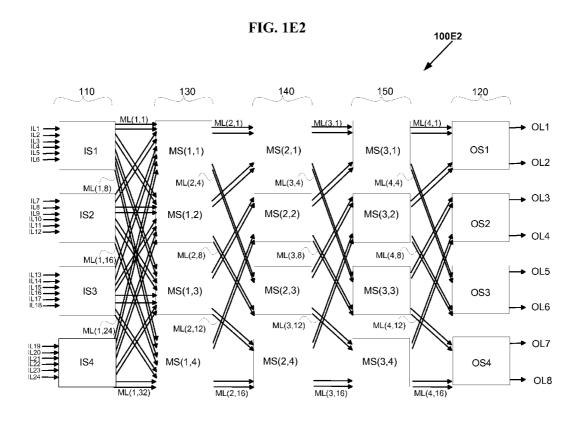

[0042] FIG. 1E2 is a diagram 100E2 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  (having a connection topology called flip network and also known as inverse shuffle exchange network) of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

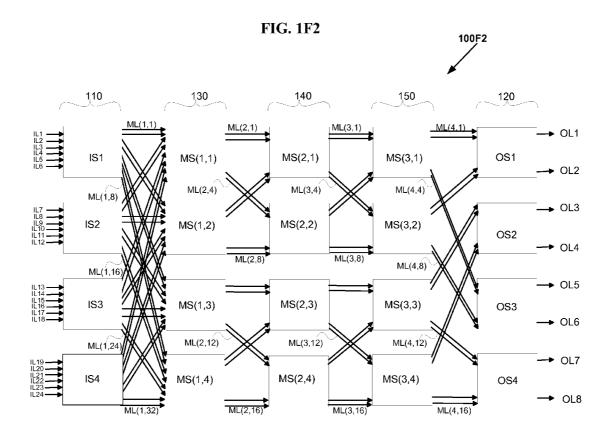

[0043] FIG. 1F2 is a diagram 100F2 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1,\,N_2,\,d,\,s)$  having Baseline connection topology of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, d=2 and s=2, strictly non-blocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

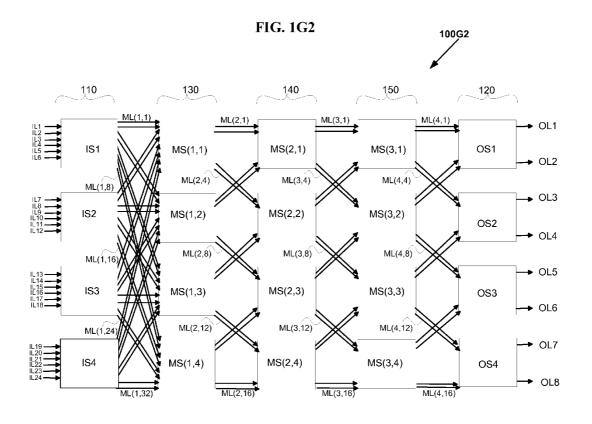

**[0044]** FIG. **1**G**2** is a diagram **100**G**2** of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having an exemplary connection topology of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

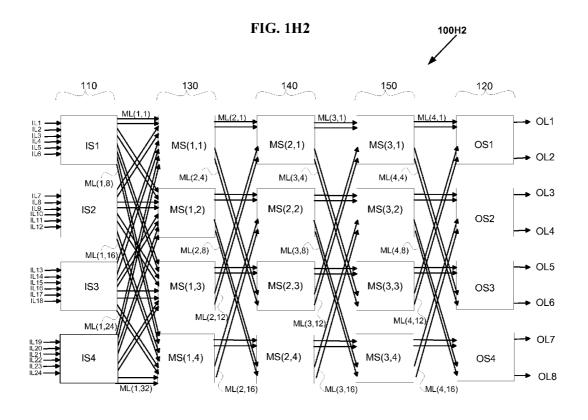

[0045] FIG. 1H2 is a diagram 100H2 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having an exemplary connection topology of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, d=2 and s=2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

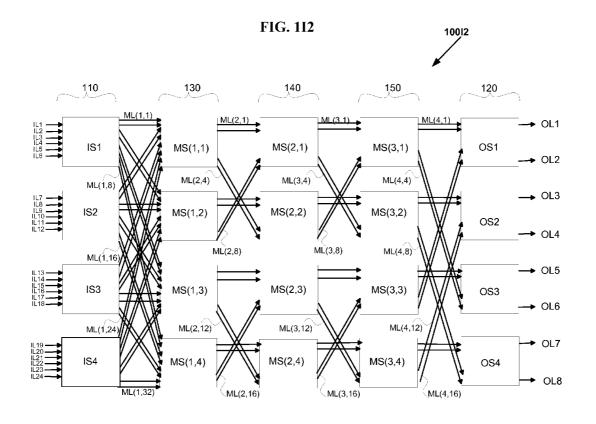

[0046] FIG. 1I2 is a diagram 100I2 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  (having a connection topology built using back-to-back Banyan Networks or back-to-back Delta Networks or equivalently back-to-back Butterfly networks) of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, d=2 and s=2, strictly non-blocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

[0047] FIG. 1J2 is a diagram 100J2 of an exemplary asymmetrical multi-link multi-stage network  $V_{\it mlink}(N_1,\,N_2,\,d,\,s)$

having an exemplary connection topology of five stages with  $N_2$ =8,  $N_1$ = $p^*N_2$ =24, where p=3, d=2 and s=2, strictly non-blocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

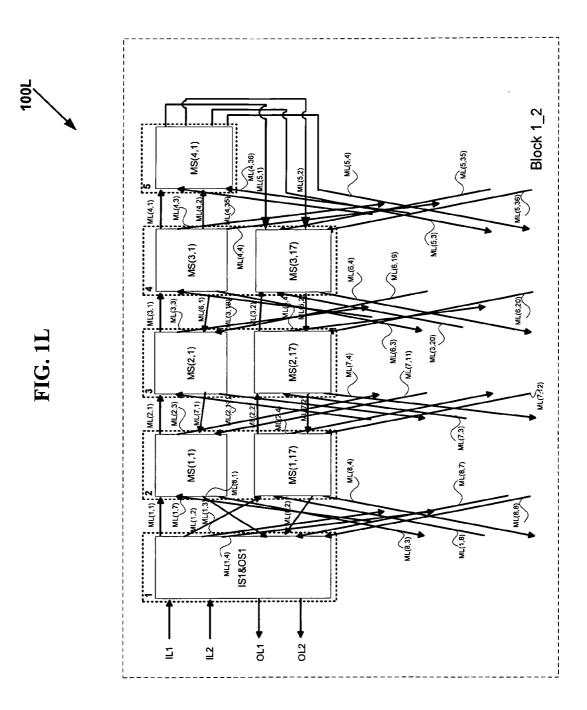

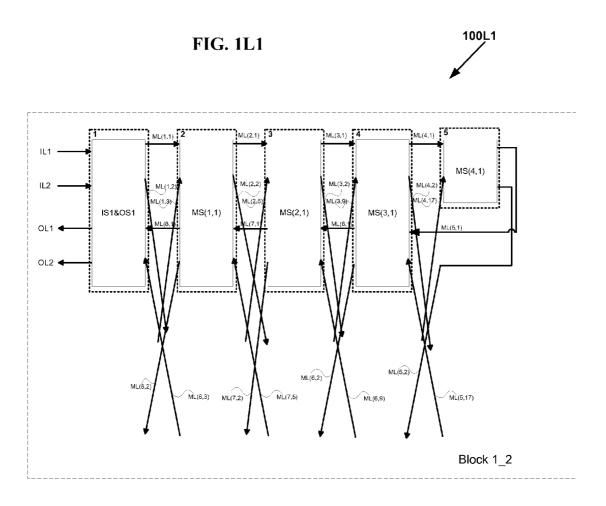

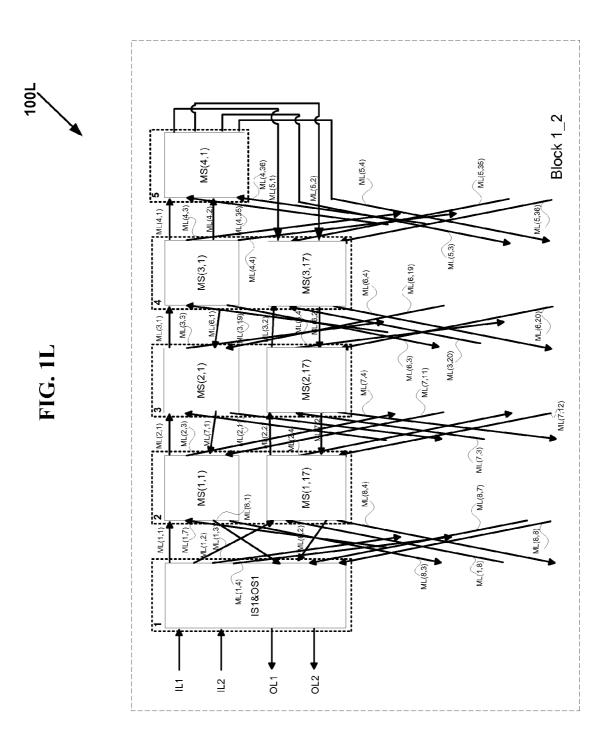

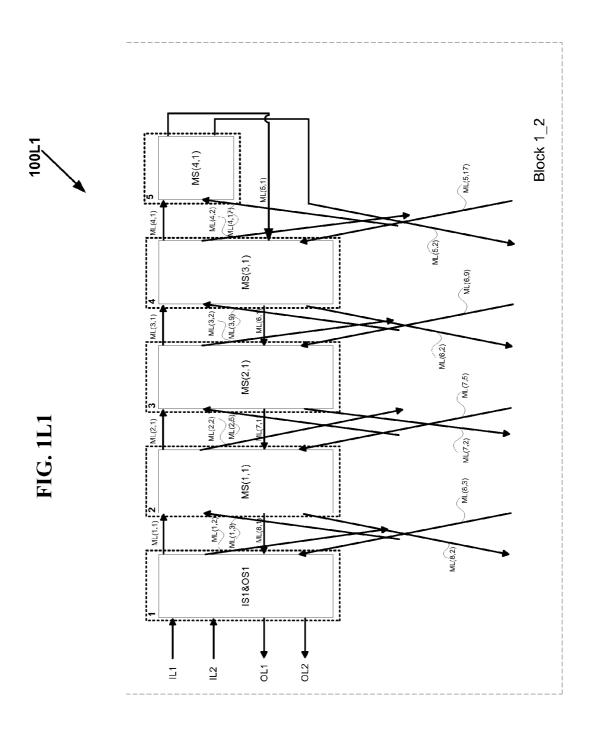

**[0048]** FIG. 1K2 is a diagram 100K2 of a general asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  with  $(2 \times \log_d N) - 1$  stages with  $N_2 = p * N_1$  and s = 2, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

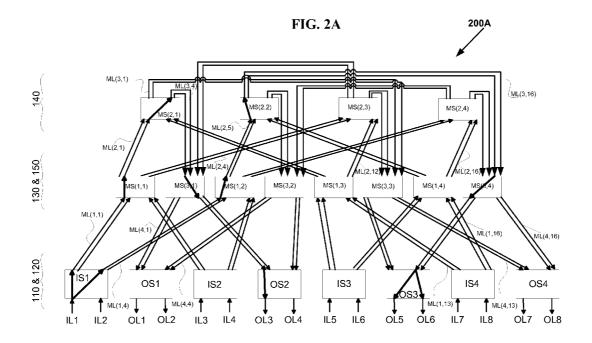

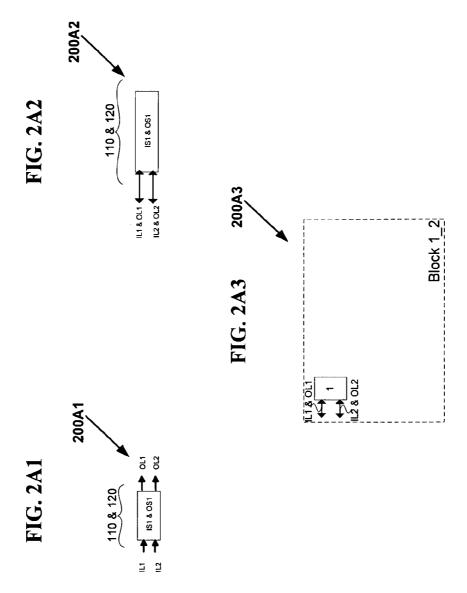

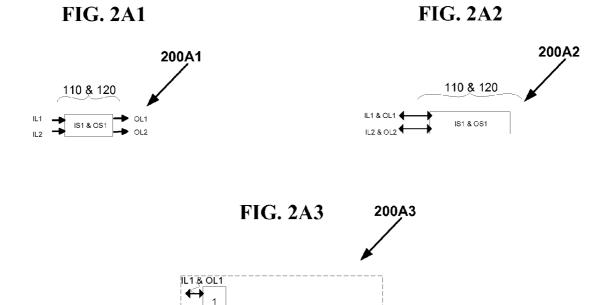

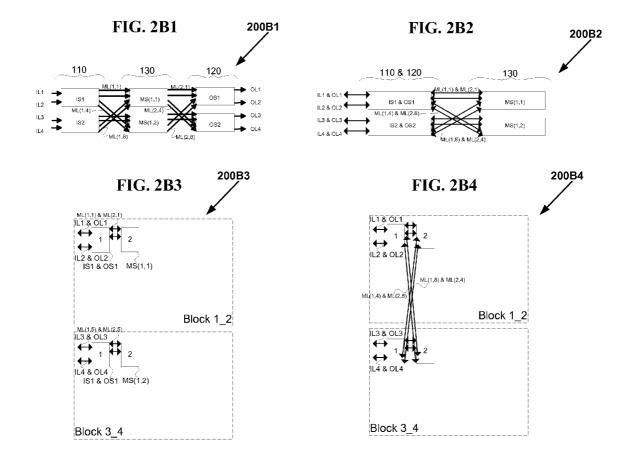

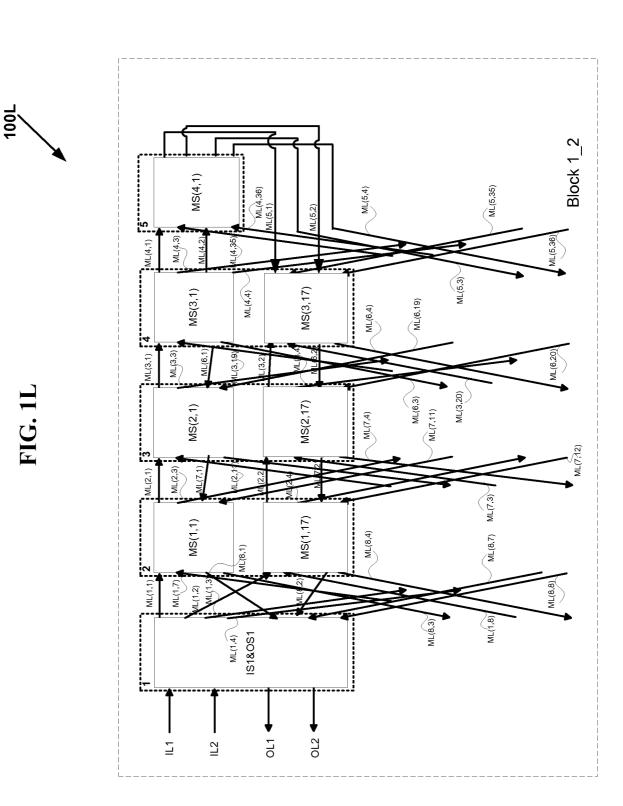

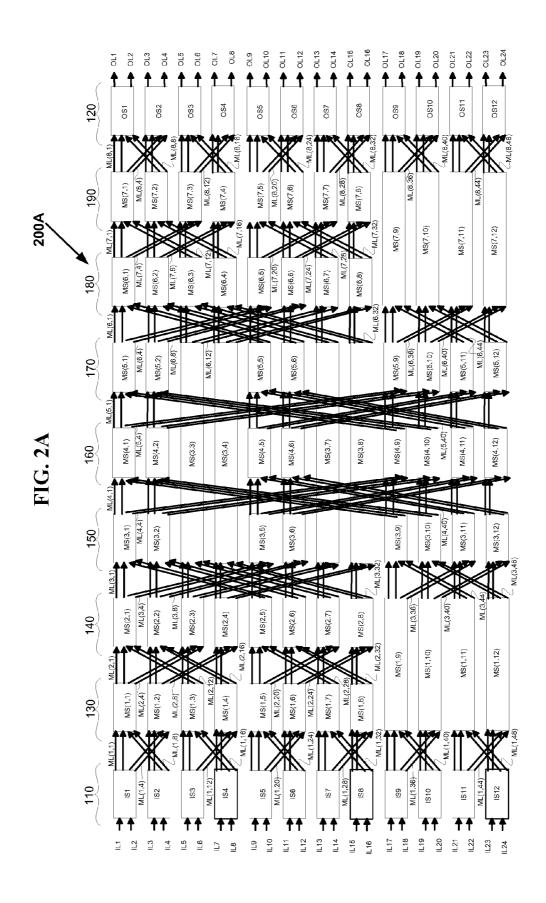

[0049] FIG. 2A is a diagram 200A of an exemplary symmetrical folded multi-link multi-stage network  $V_{fold-link}(N,d,s)$  having inverse Benes connection topology of five stages with N=8, d=2 and s=2 with exemplary multicast connections, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

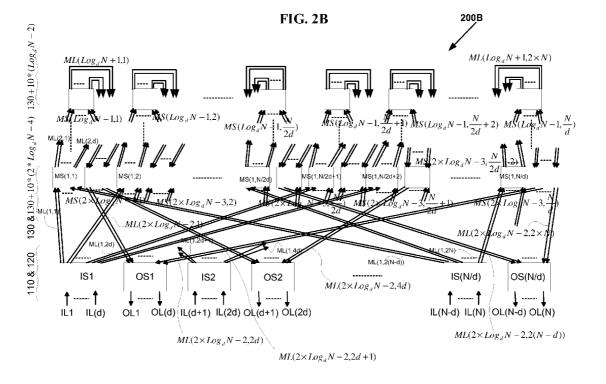

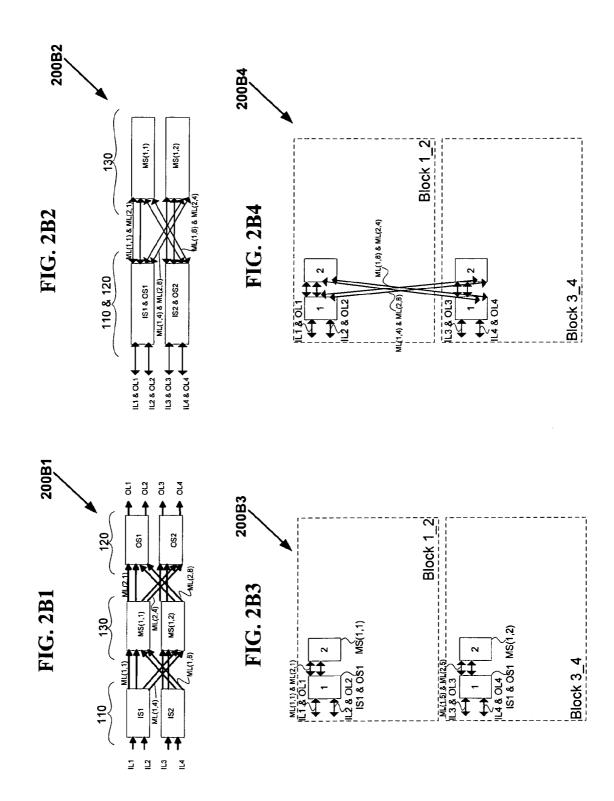

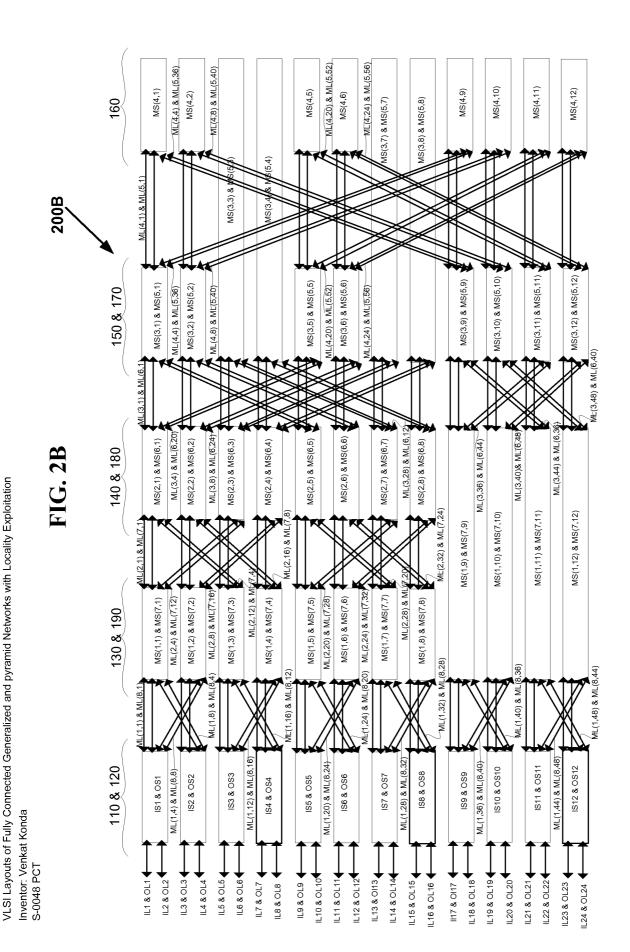

**[0050]** FIG. **2B** is a diagram **200B** of a general symmetrical folded multi-link multi-stage network  $V_{fold-mlink}(N,d,2)$  with  $(2\times\log_d N)-1$  stages strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections in accordance with the invention.

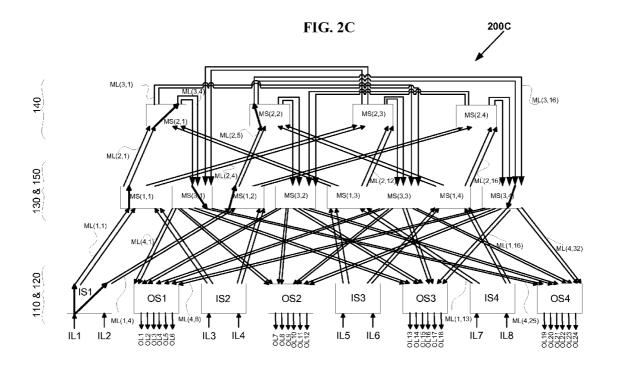

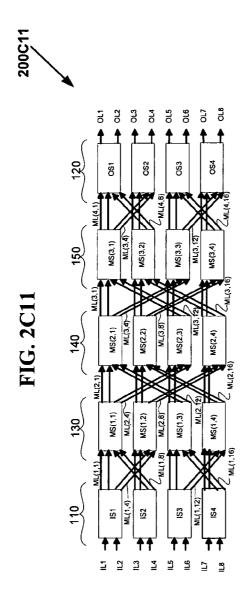

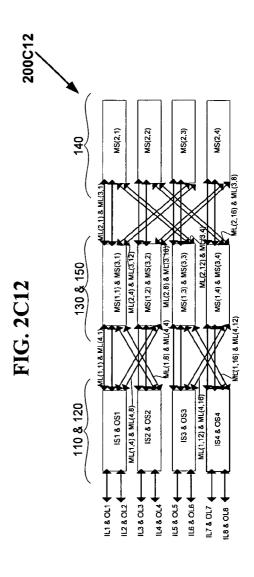

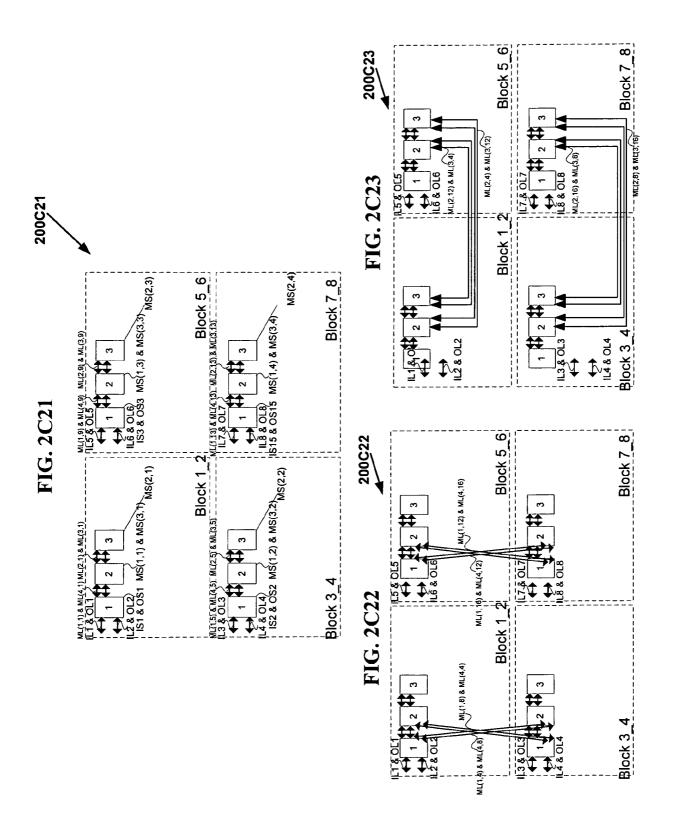

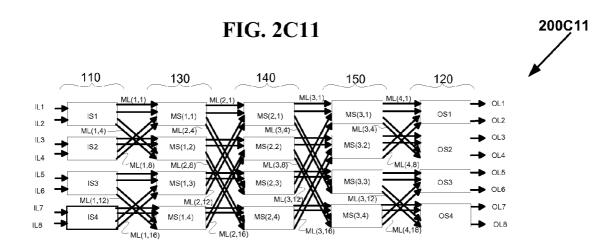

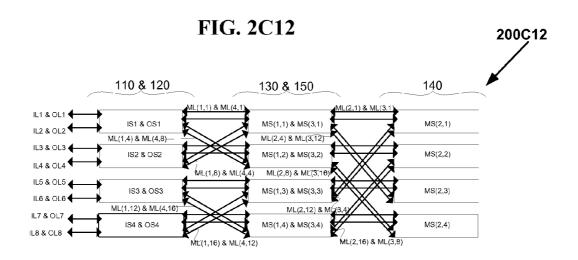

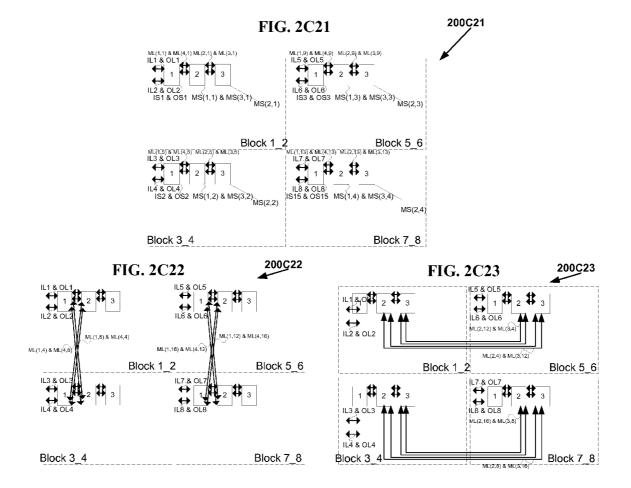

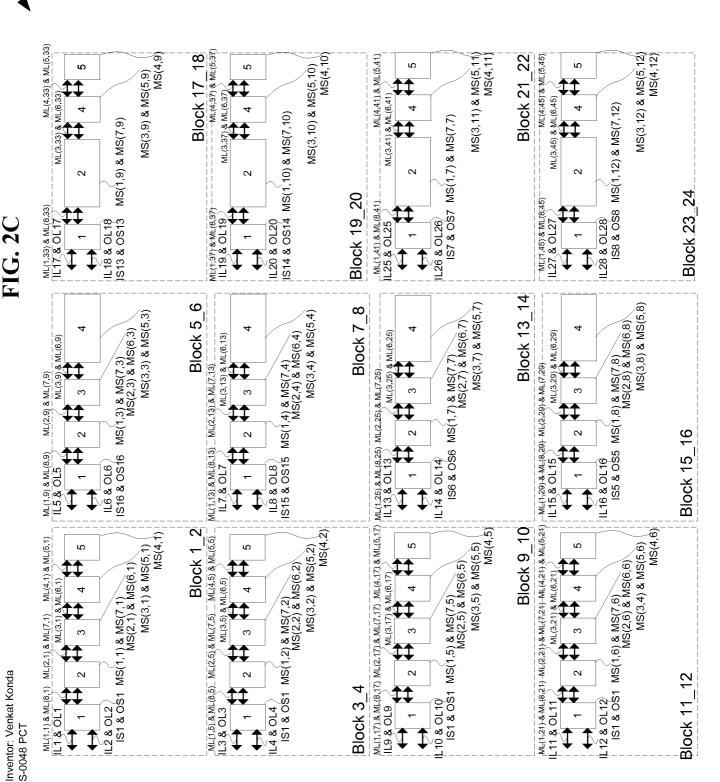

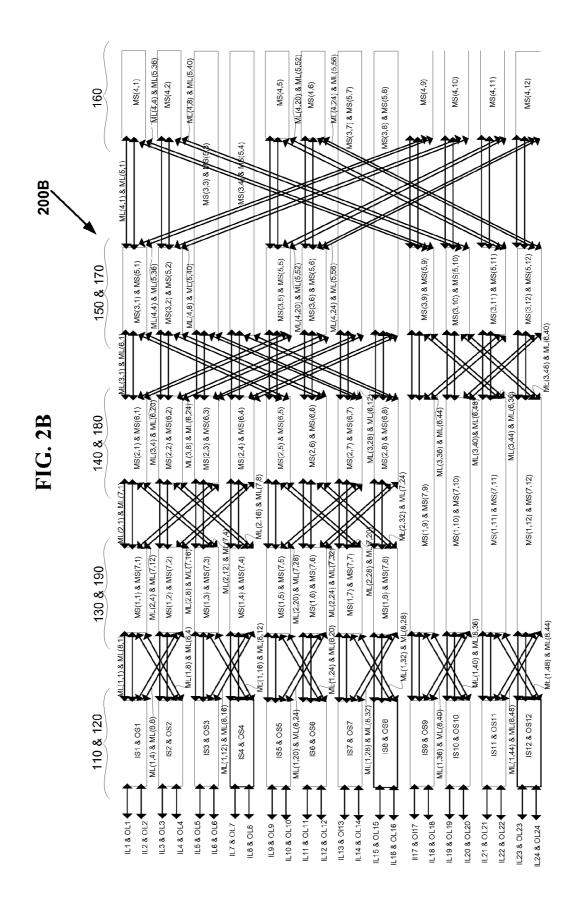

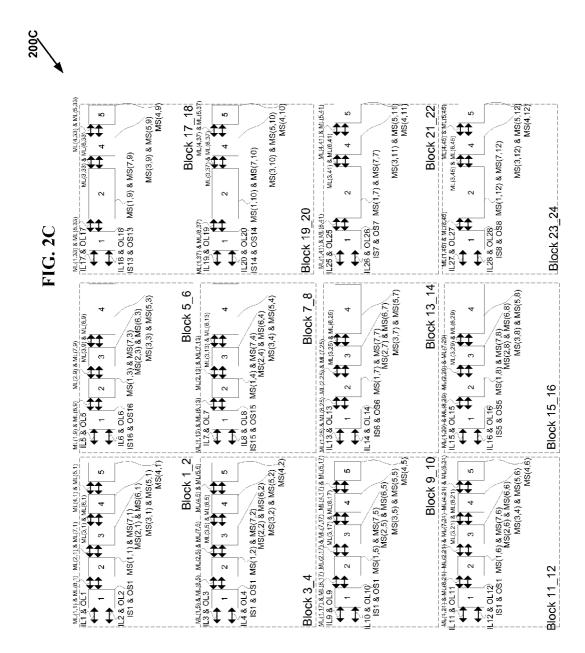

[0051] FIG. 2C is a diagram 200C of an exemplary asymmetrical folded multi-link multi-stage network  $V_{fold\text{-}mlink}(N_1, N_2, d, 2)$  having inverse Benes connection topology of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, and d=2 with exemplary multicast connections, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

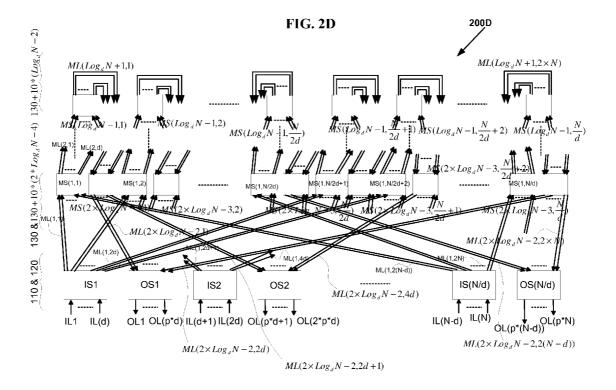

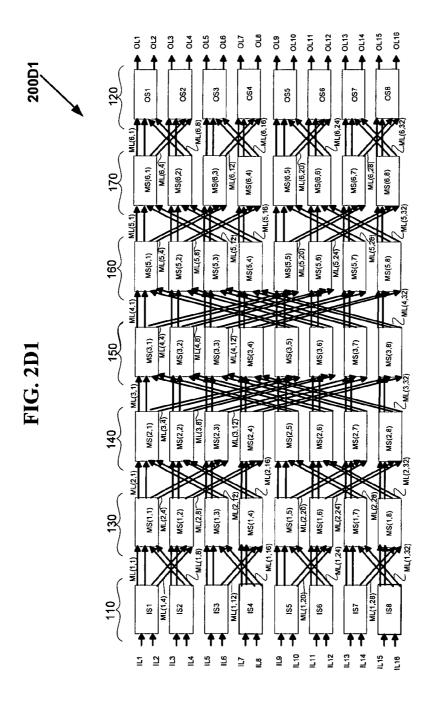

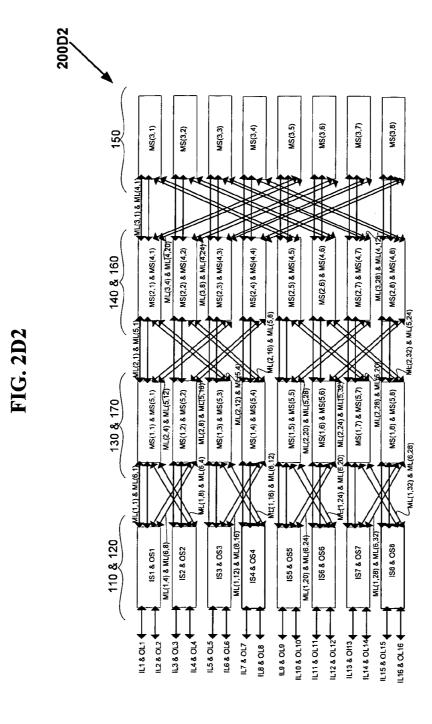

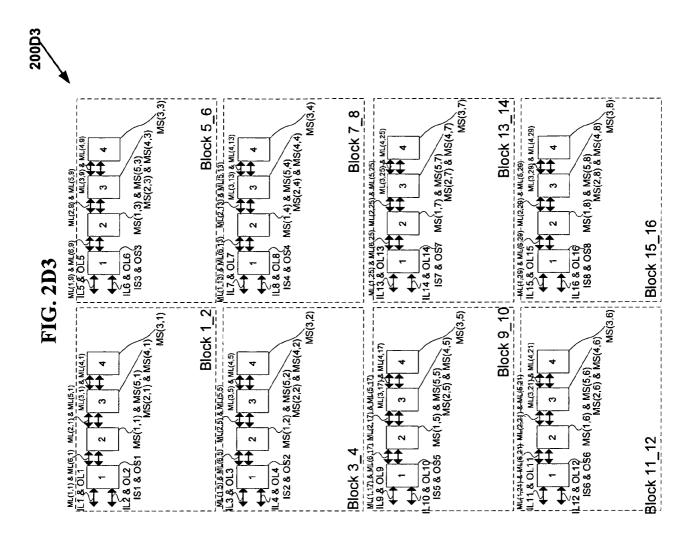

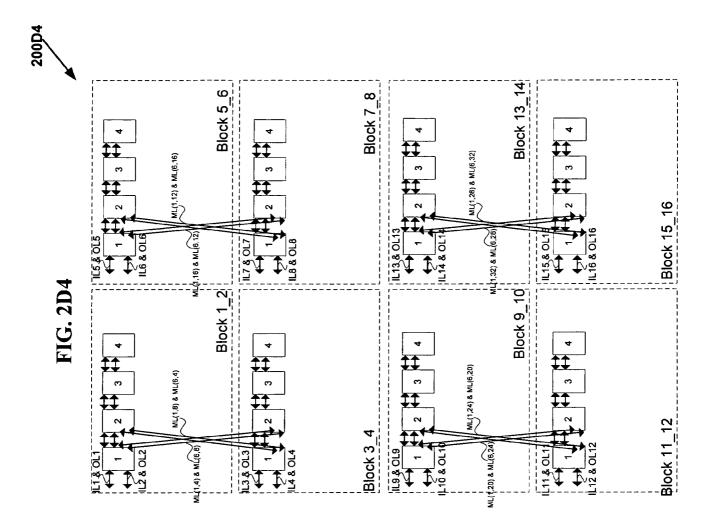

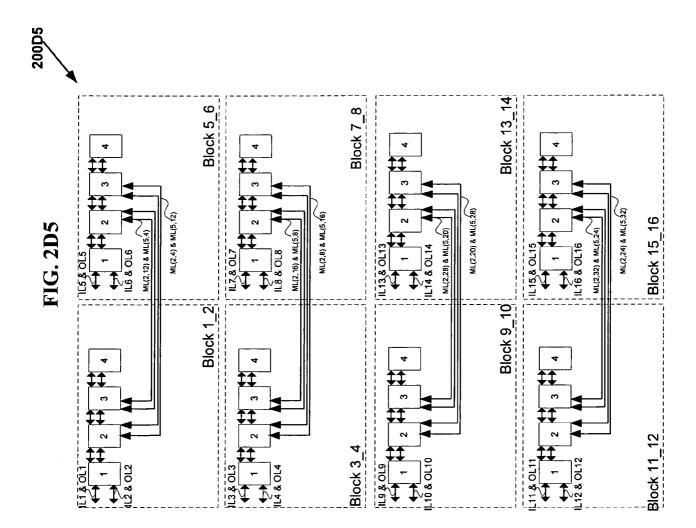

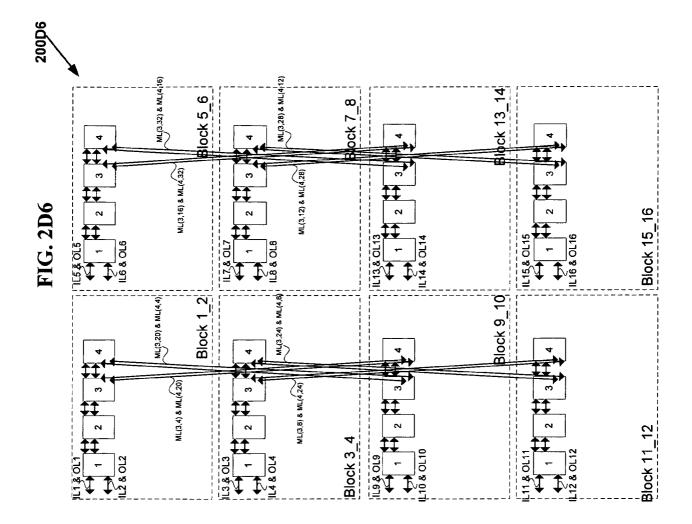

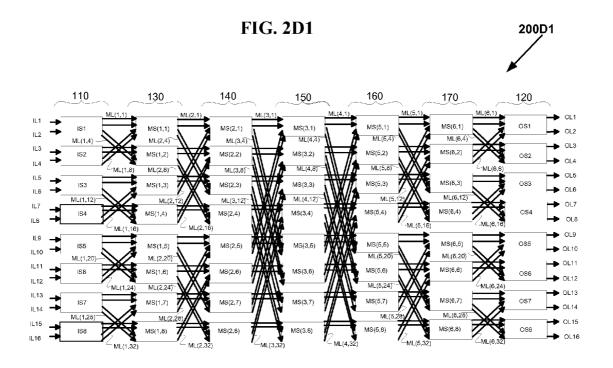

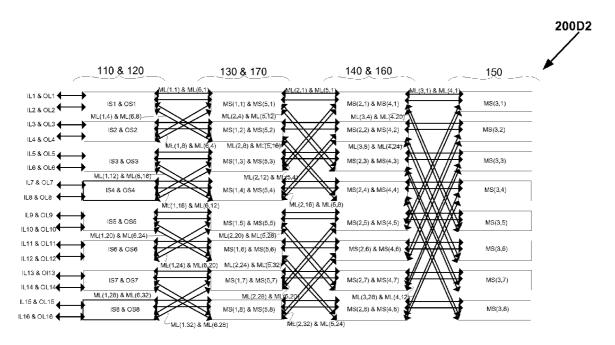

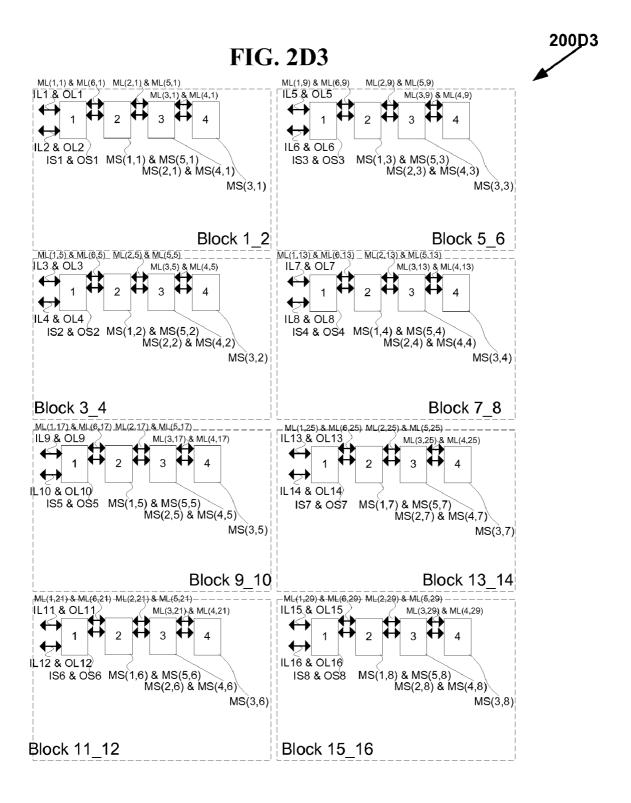

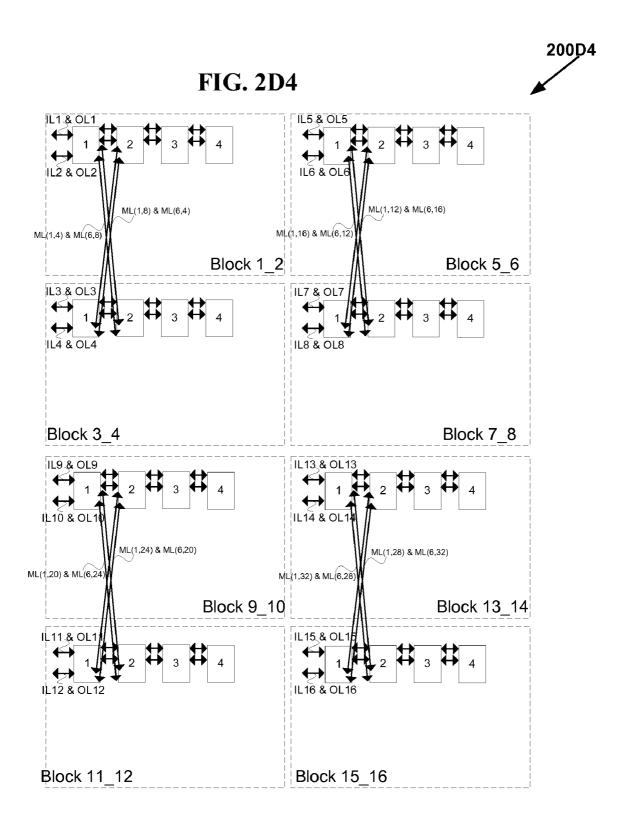

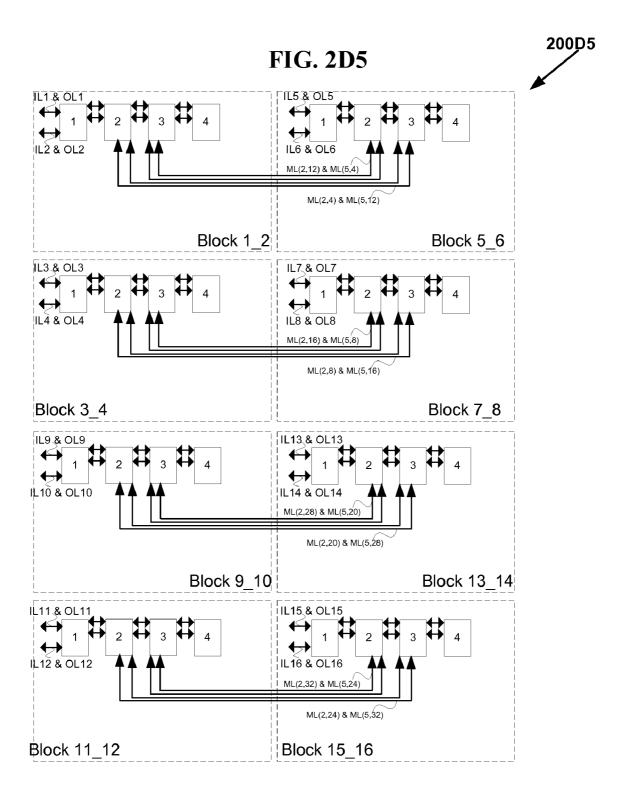

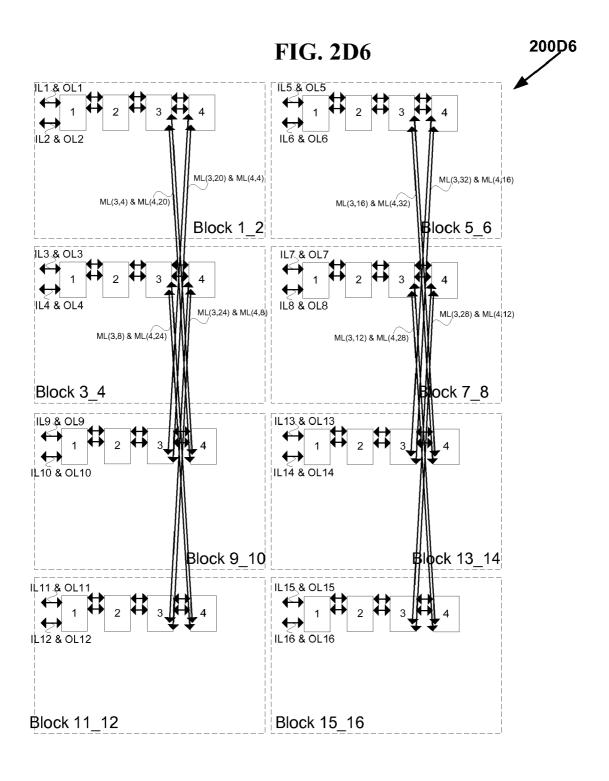

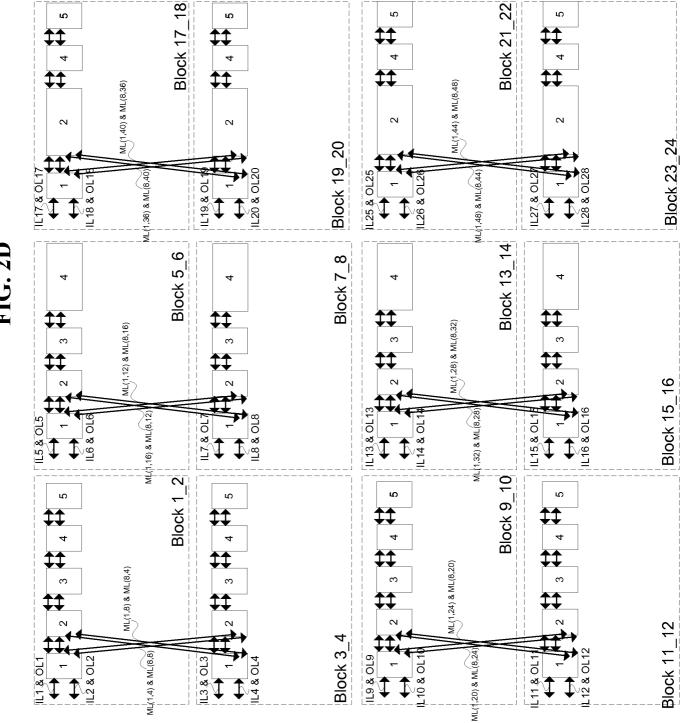

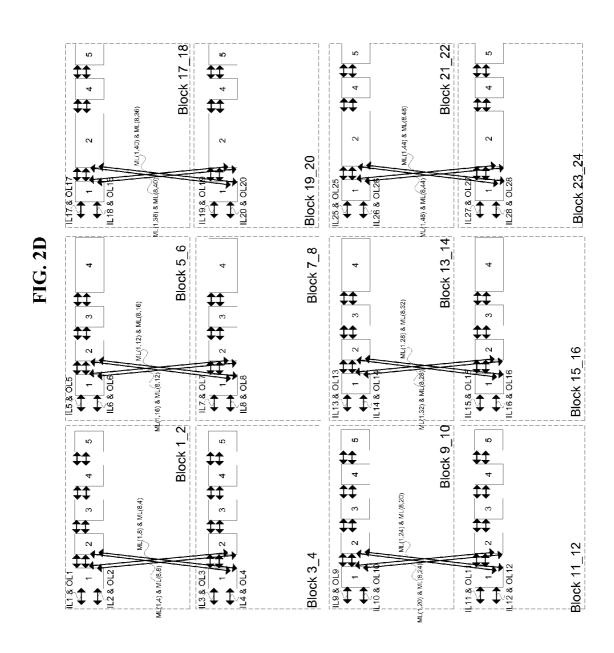

**[0052]** FIG. 2D is a diagram **200**D of a general asymmetrical folded multi-link multi-stage network  $V_{fold-mlink}(N_1, N_2, d, 2)$  with  $N_2=p*N_1$  and with  $(2\times\log_d N)-1$  stages strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections in accordance with the invention.

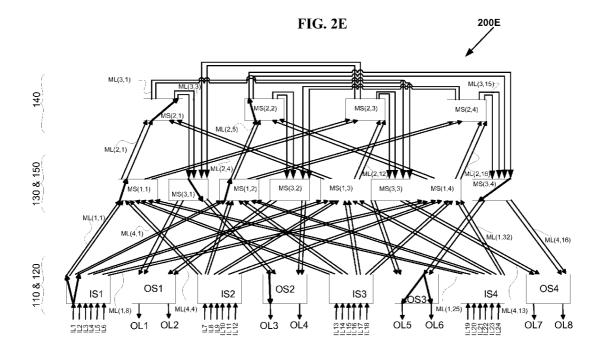

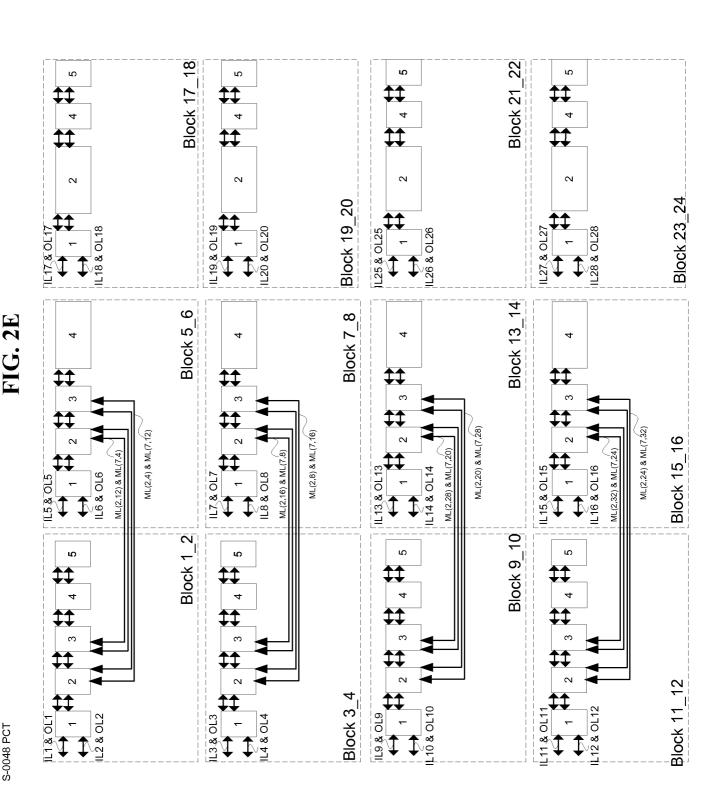

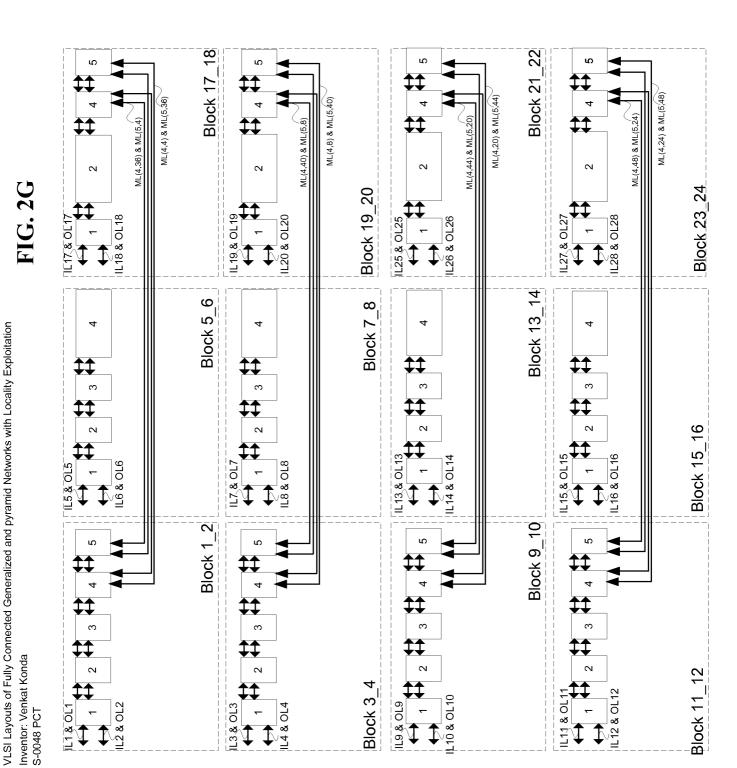

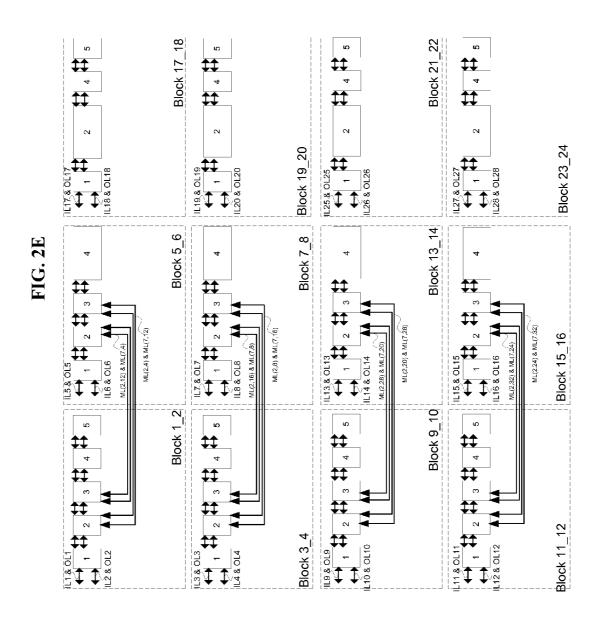

[0053] FIG. 2E is a diagram 200E of an exemplary asymmetrical folded multi-link multi-stage network  $V_{fold-mlink}(N_1, N_2, d, 2)$  having inverse Benes connection topology of five stages with  $N_2$ =8,  $N_1$ = $p*N_2$ =24, where p=3, and d=2 with exemplary multicast connections, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

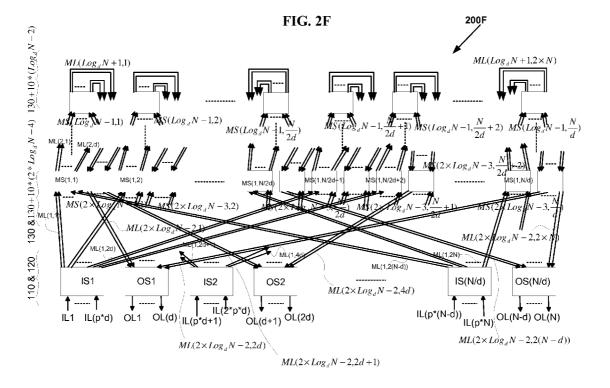

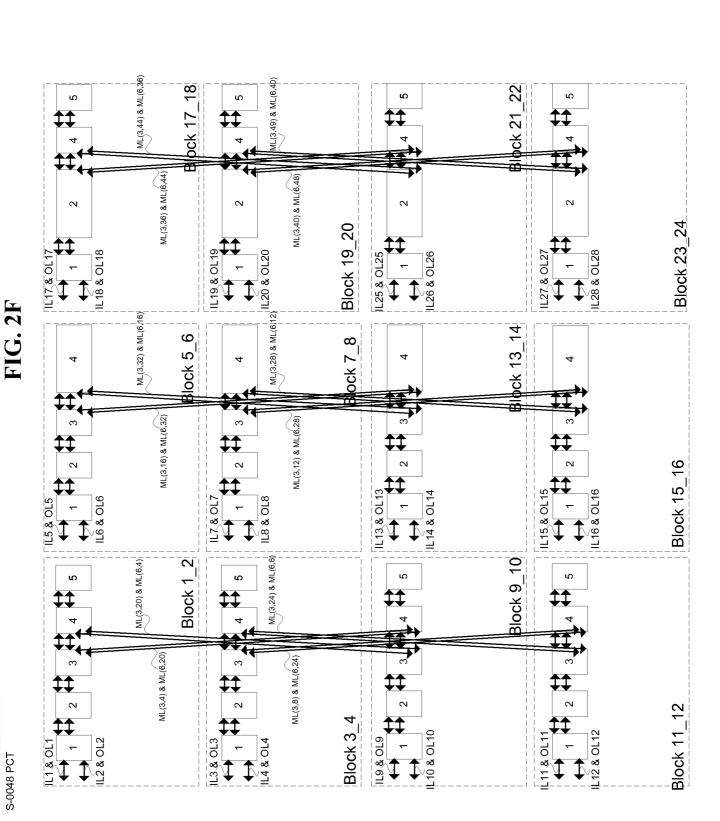

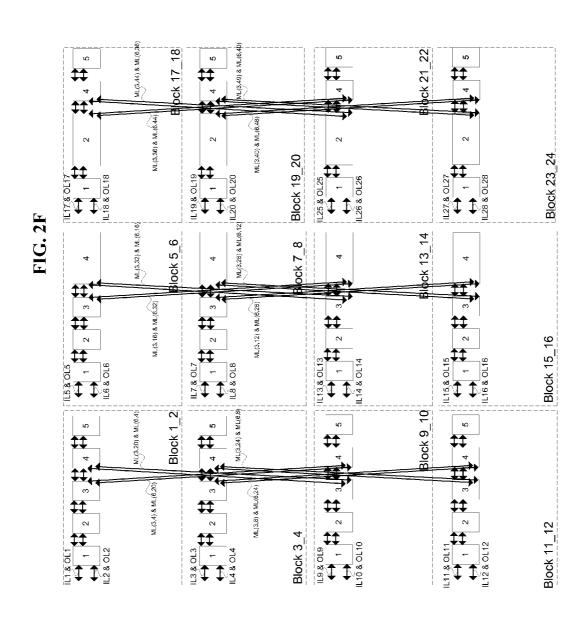

[0054] FIG. 2F is a diagram 200F of a general asymmetrical folded multi-link multi-stage network  $V_{fold-mlink}(N_1,N_2,d,2)$  with  $N_1$ =p\* $N_2$  and with  $(2\times\log_d N)$ -1 stages strictly non-blocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections in accordance with the invention.

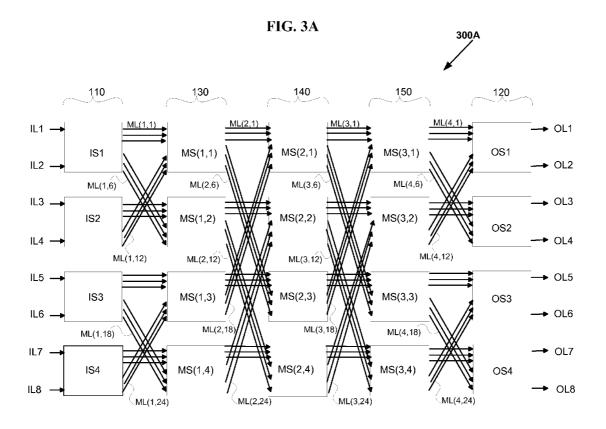

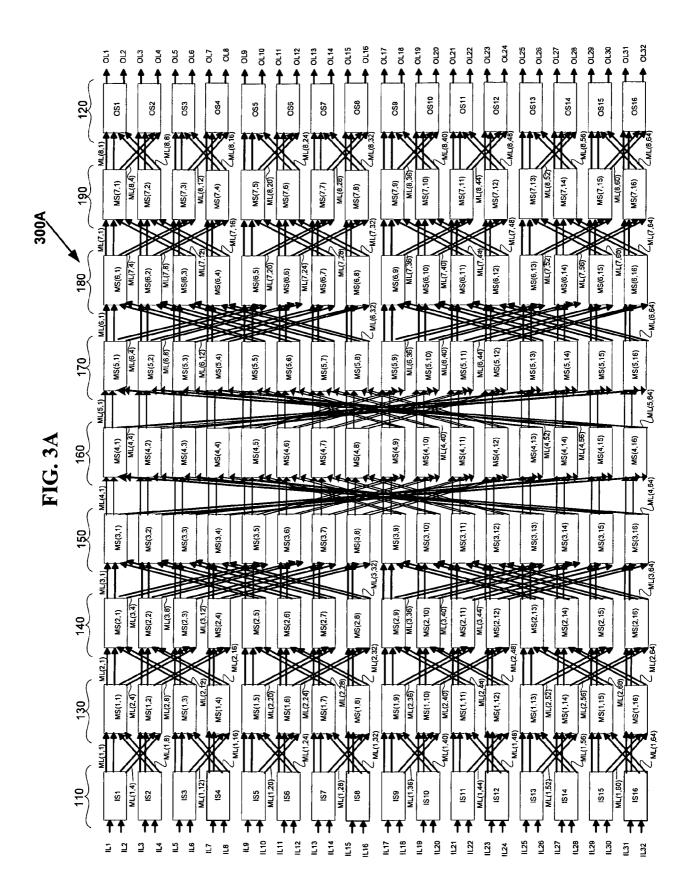

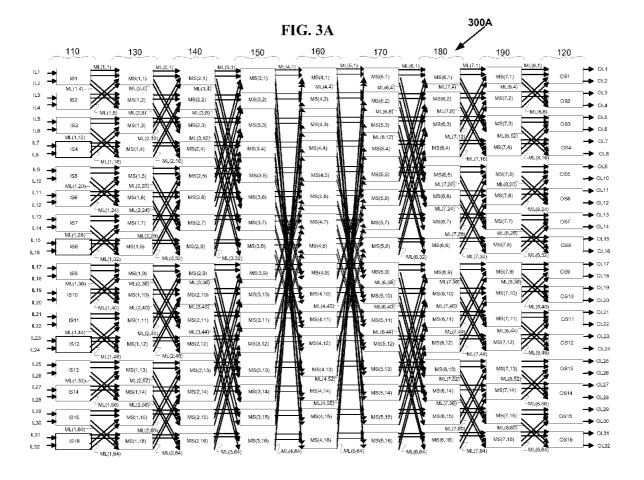

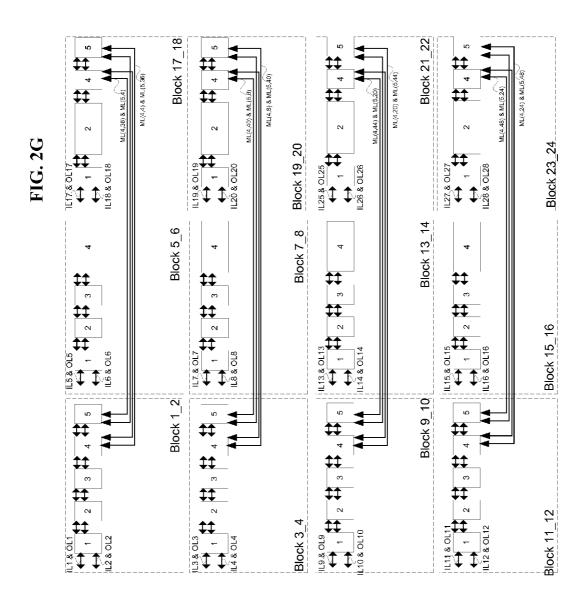

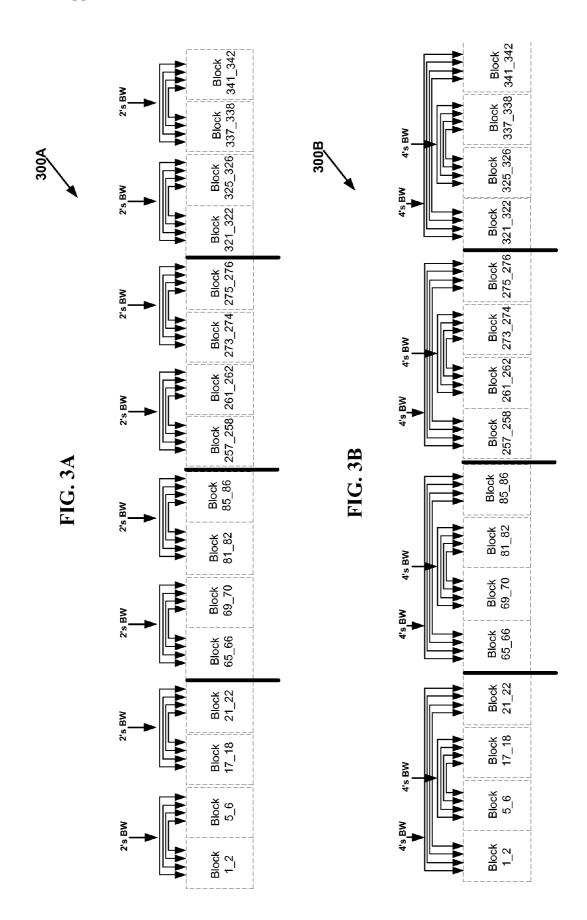

[0055] FIG. 3A is a diagram 300A of an exemplary symmetrical multi-link multi-stage network  $V_{mlink}(N,d,s)$  having inverse Benes connection topology of five stages with N=8, d=2 and s=3, strictly nonblocking network for arbitrary fanout multicast connections, in accordance with the invention.

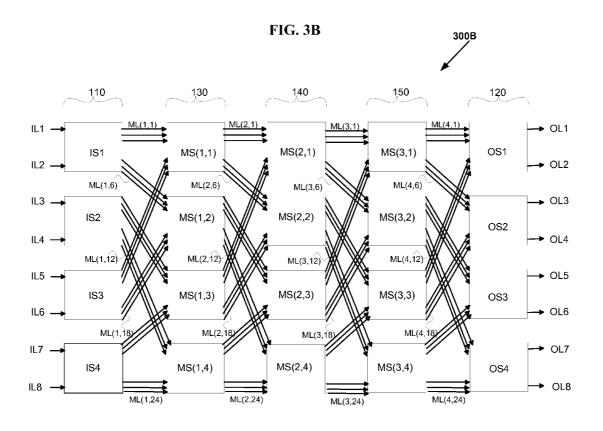

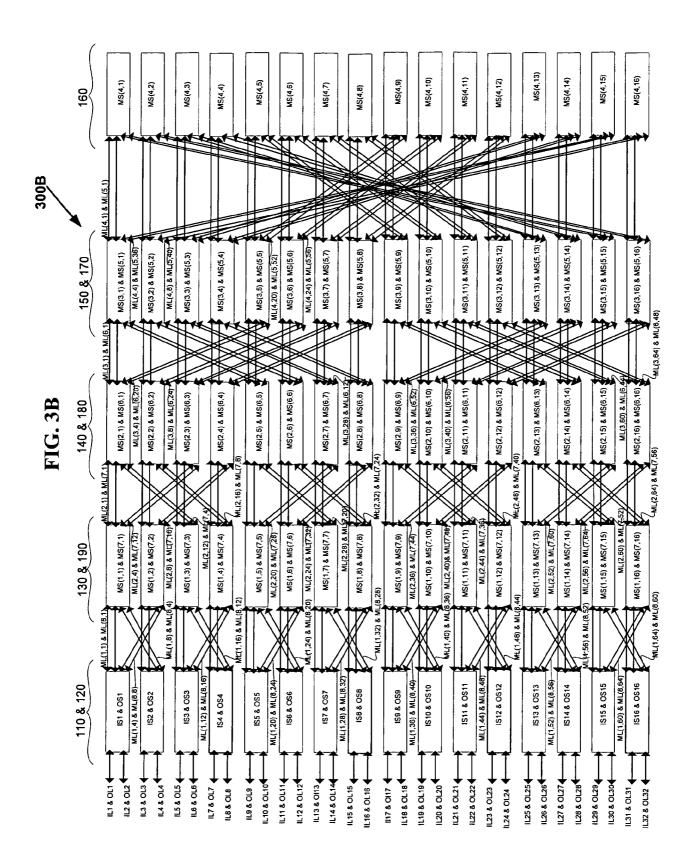

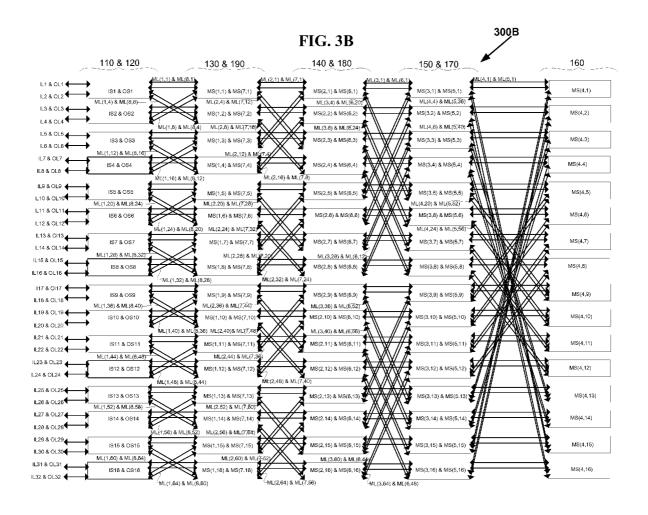

[0056] FIG. 3B is a diagram 300B of an exemplary symmetrical multi-link multi-stage network  $V_{mlink}(N,d,s)$  (having a connection topology built using back-to-back Omega Networks) of five stages with N=8, d=2 and s=3, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

US 2011/0044329 A1

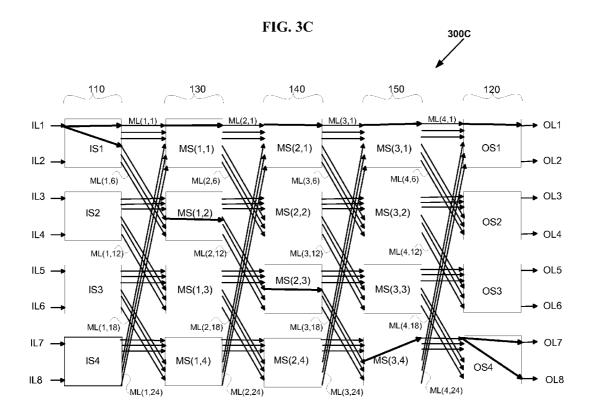

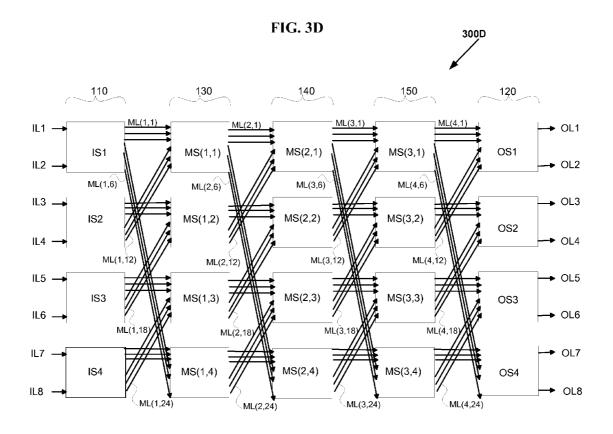

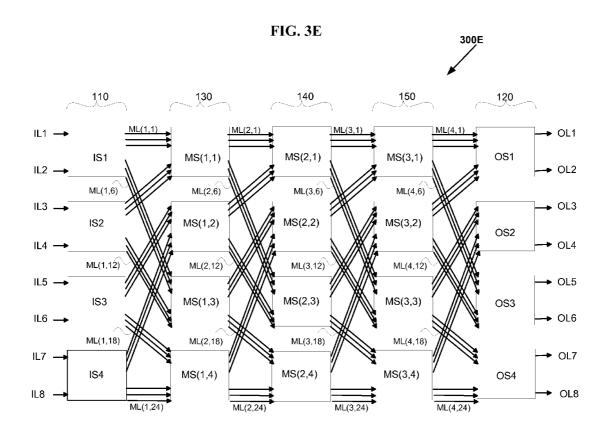

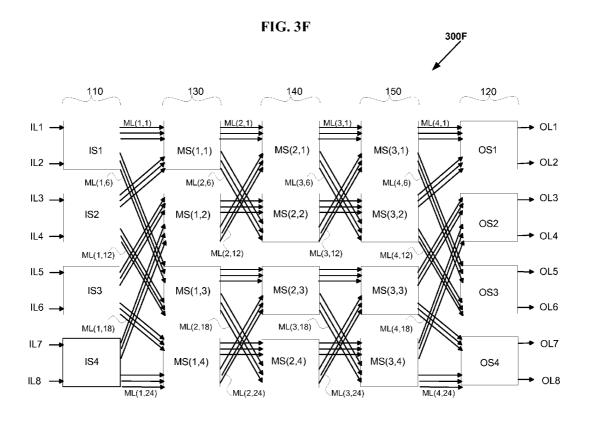

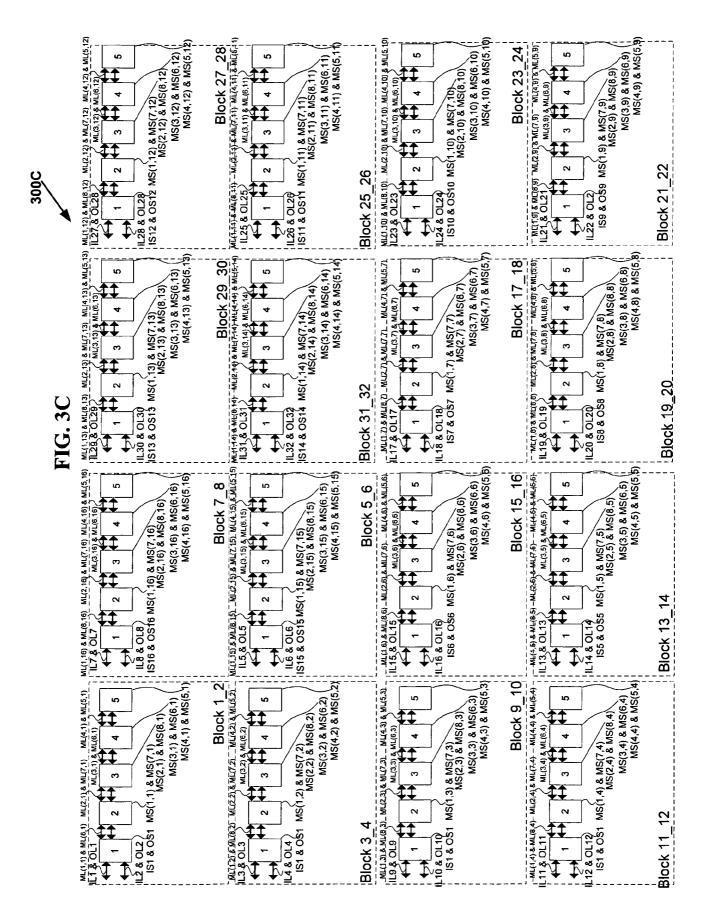

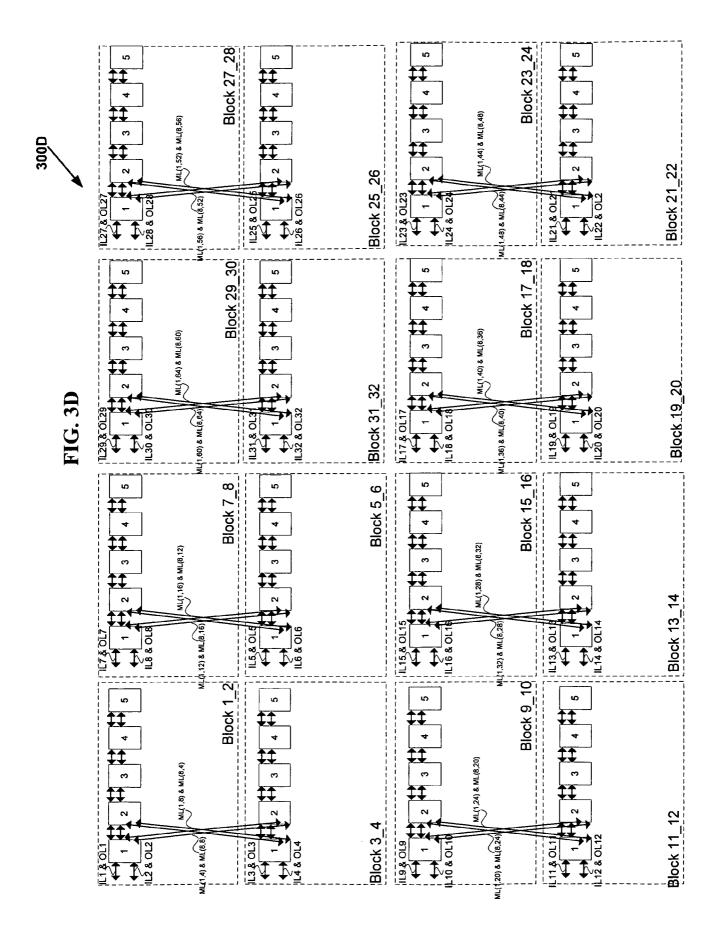

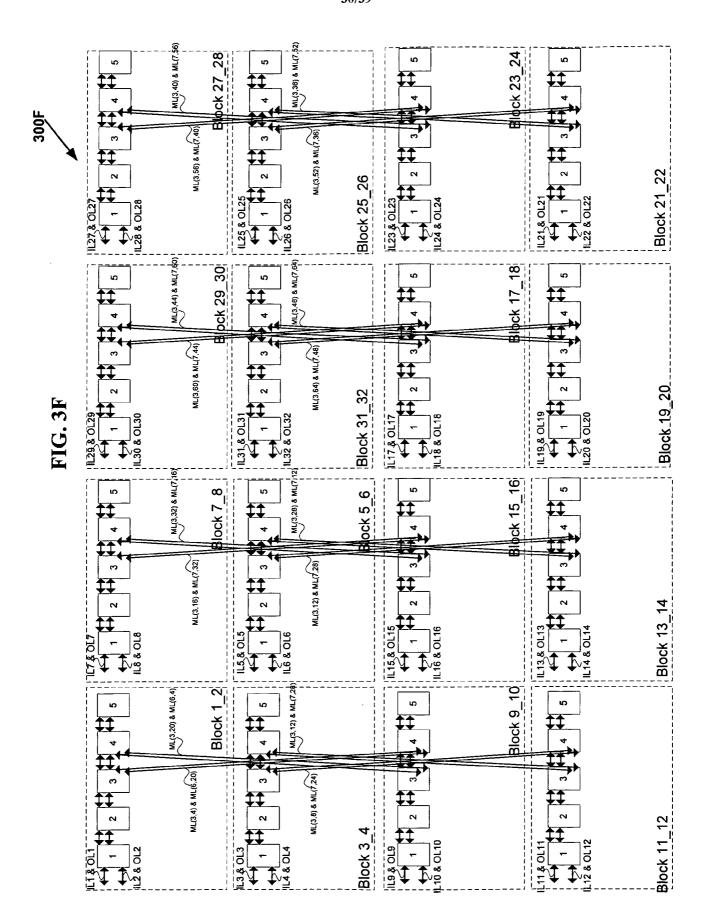

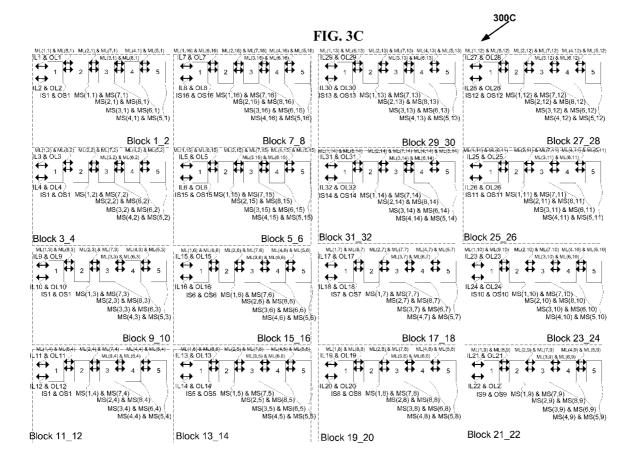

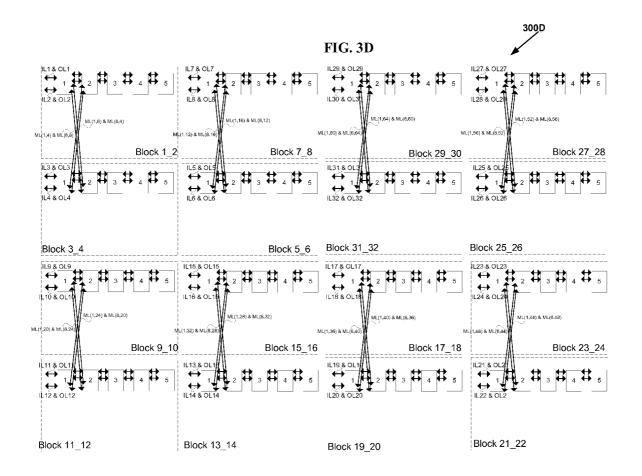

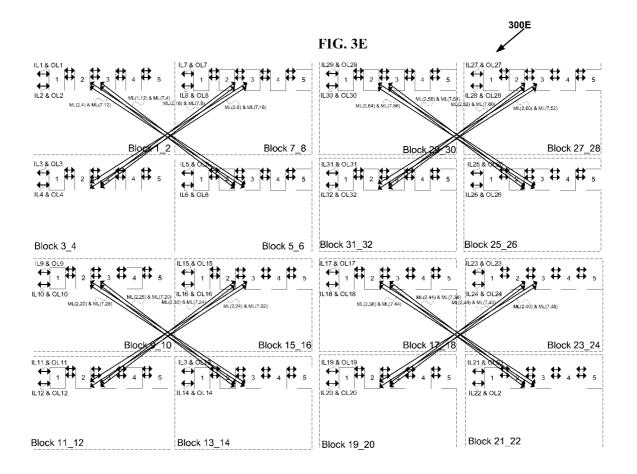

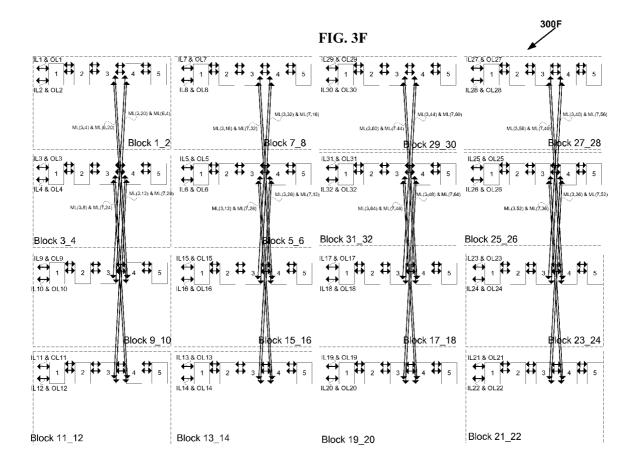

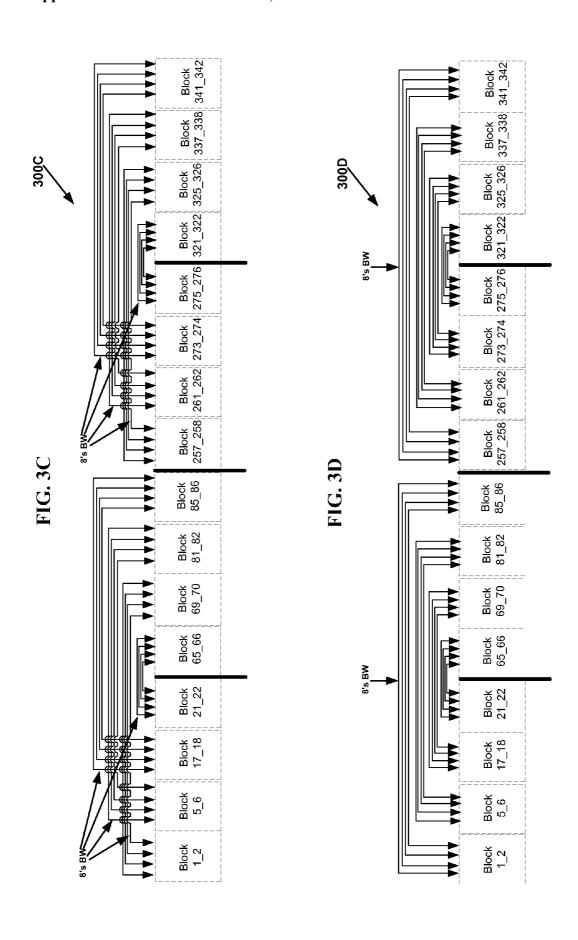

[0057] FIG. 3C is a diagram 300C of an exemplary symmetrical multi-link multi-stage network  $V_{mlink}(N, d, s)$  having an exemplary connection topology of five stages with N=8, d=2 and s=3, strictly nonblocking network for arbitrary fanout multicast connections, in accordance with the invention. [0058] FIG. 3D is a diagram 300D of an exemplary symmetrical multi-link multi-stage network  $V_{mlink}(N, d, s)$  having an exemplary connection topology of five stages with N=8, d=2 and s=3, strictly nonblocking network for arbitrary fanout multicast connections, in accordance with the invention. [0059] FIG. 3E is a diagram 300E of an exemplary symmetrical multi-link multi-stage network  $V_{mlink}(N, d, s)$  (having a connection topology called flip network and also known as inverse shuffle exchange network) of five stages with N=8, d=2 and s=3, strictly nonblocking network for arbitrary fanout multicast connections, in accordance with the invention. [0060] FIG. 3F is a diagram 300F of an exemplary sym $metrical \ multi-link \ multi-stage \ network \ V_{\mathit{mlink}}(N,d,s) \ having$ Baseline connection topology of five stages with N=8, d=2 and s=3, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

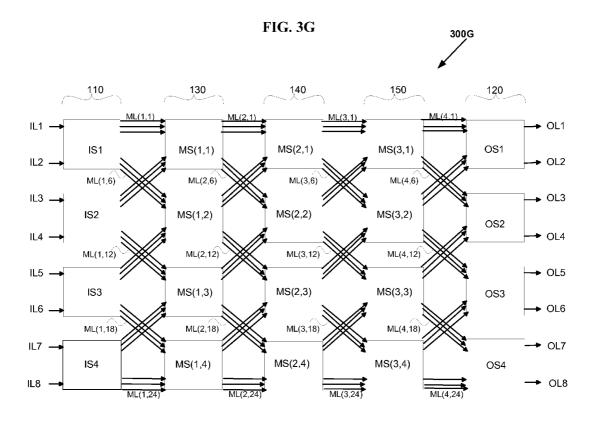

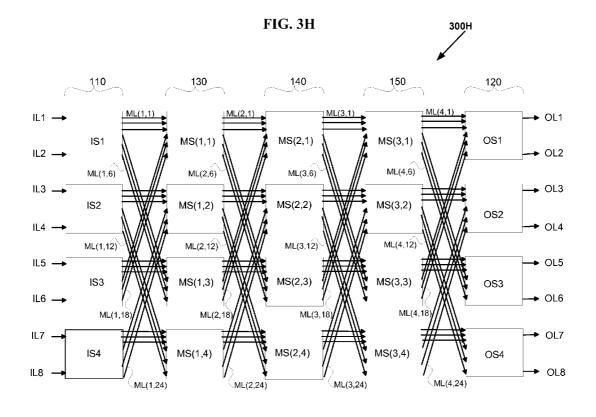

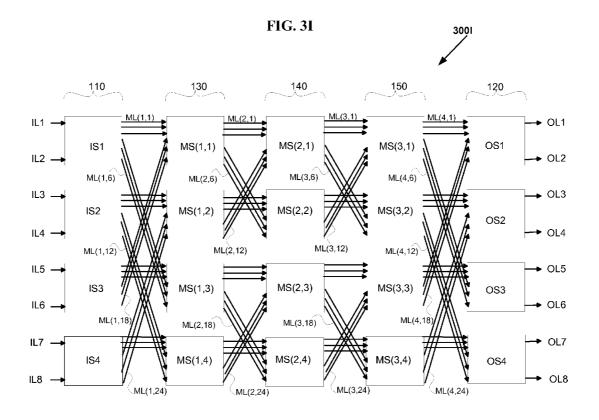

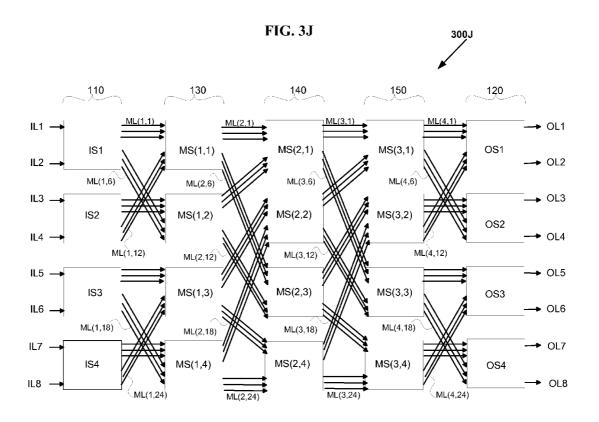

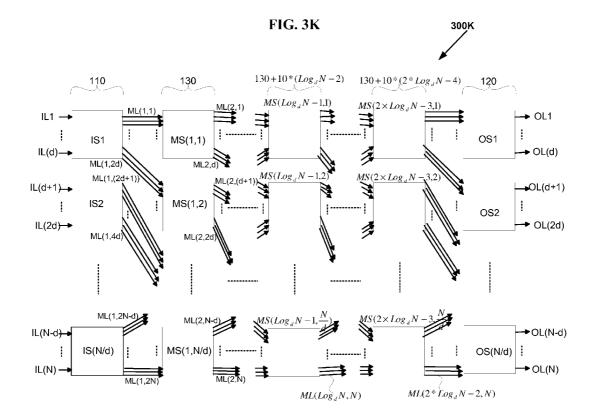

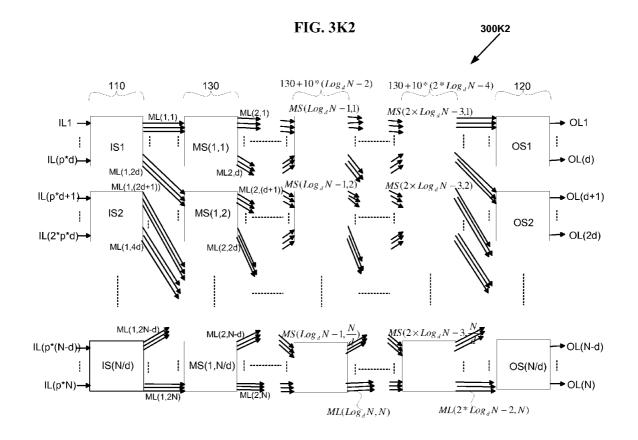

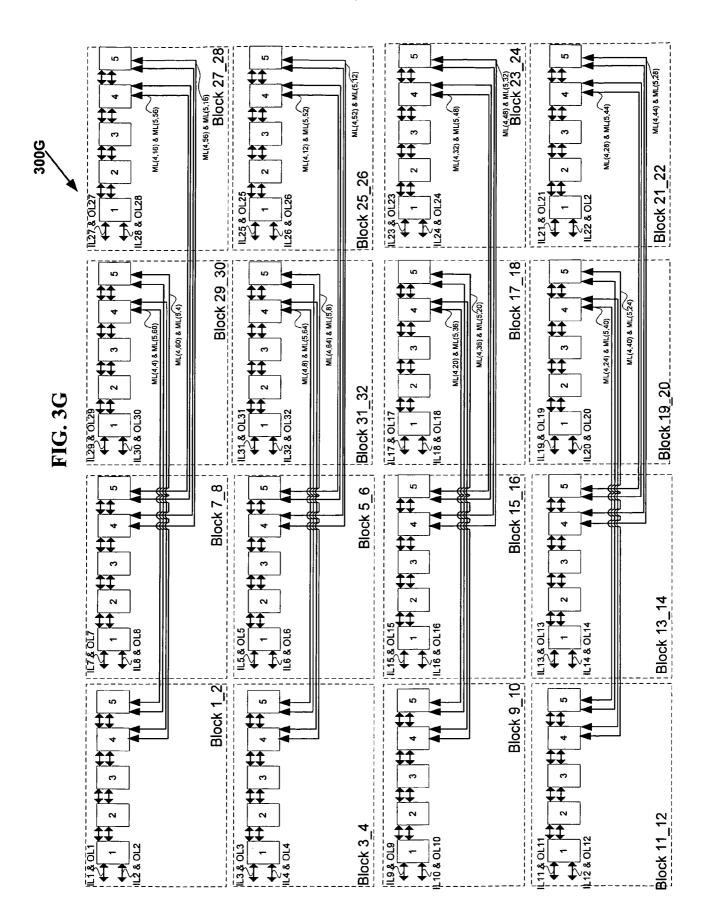

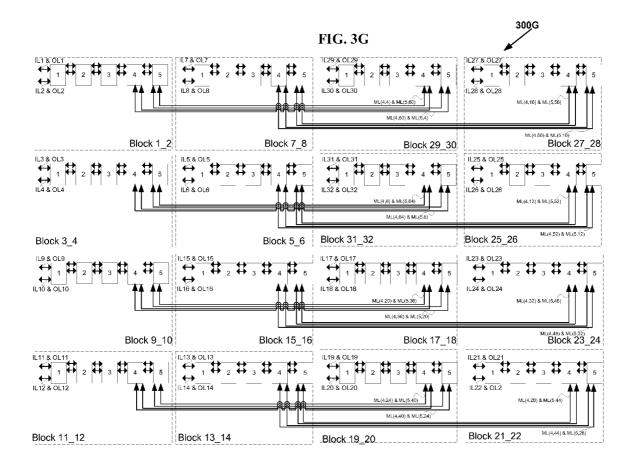

[0061] FIG. 3G is a diagram 300G of an exemplary sym $metrical \ multi-link \ multi-stage \ network \ V_{\mathit{mlink}}(N,d,s) \ having$ an exemplary connection topology of five stages with N=8, d=2 and s=3, strictly nonblocking network for arbitrary fanout multicast connections, in accordance with the invention. [0062] FIG. 3H is a diagram 300H of an exemplary sym $metrical \ multi-link \ multi-stage \ network \ V_{\mathit{mlink}}(N,d,s) \ having$ an exemplary connection topology of five stages with N=8, d=2 and s=3, strictly nonblocking network for arbitrary fanout multicast connections, in accordance with the invention. [0063] FIG. 3I is a diagram 300I of an exemplary symmetrical multi-link multi-stage network  $V_{mlink}(N, d, s)$  (having a connection topology built using back-to-back Banyan Networks or back-to-back Delta Networks or equivalently back-to-back Butterfly networks) of five stages with N=8, d=2 and s=3, strictly nonblocking network for arbitrary fanout multicast connections, in accordance with the invention. [0064] FIG. 3J is a diagram 300J of an exemplary sym $metrical \ multi-link \ multi-stage \ network \ V_{\mathit{mlink}}(N,d,s) \ having$ an exemplary connection topology of five stages with N=8, d=2 and s=3, strictly nonblocking network for arbitrary fanout multicast connections, in accordance with the invention. [0065] FIG. 3K is a diagram 300K of a general symmetrical multi-link multi-stage network  $V_{mlink}(N, d, s)$  with  $(2 \times \log_d$ N)-1 stages with s=3, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the

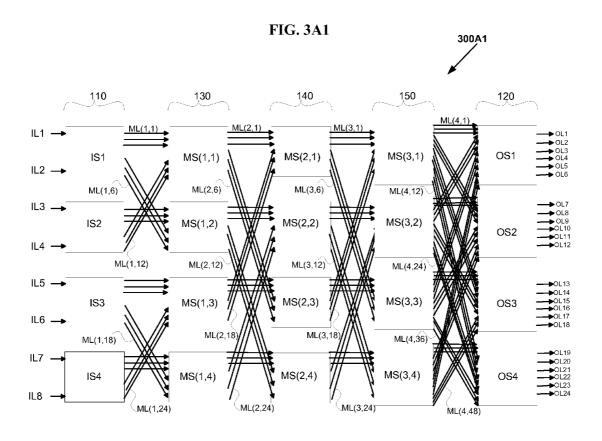

[0066] FIG. 3A1 is a diagram 300A1 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having inverse Benes connection topology of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, d=2 and s=3, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

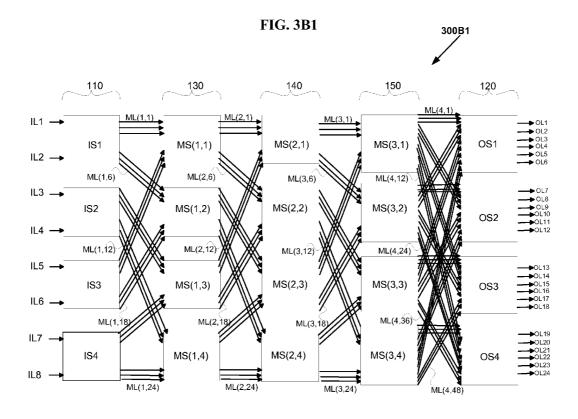

[0067] FIG. 3B1 is a diagram 300B1 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  (having a connection topology built using back-to-back Omega Networks) of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, d=2 and s=3, strictly nonblocking network for arbitrary fan-out multicast connections.

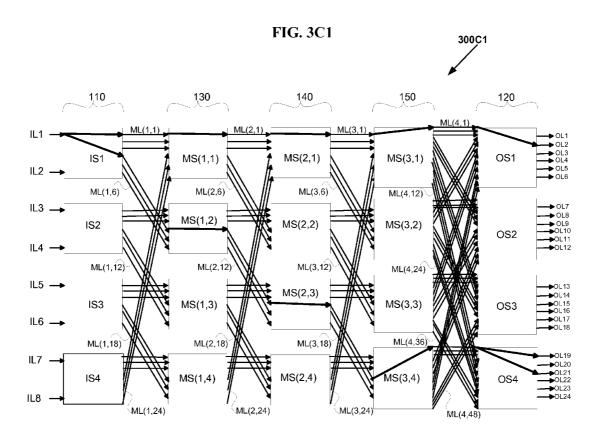

[0068] FIG. 3C1 is a diagram 300C1 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having an exemplary connection topology of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, d=2 and s=3, strictly

nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

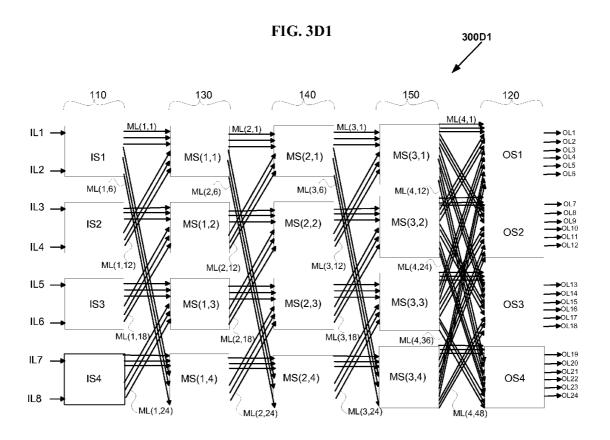

**[0069]** FIG. **3D1** is a diagram **300D1** of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having an exemplary connection topology of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, d=2 and s=3, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

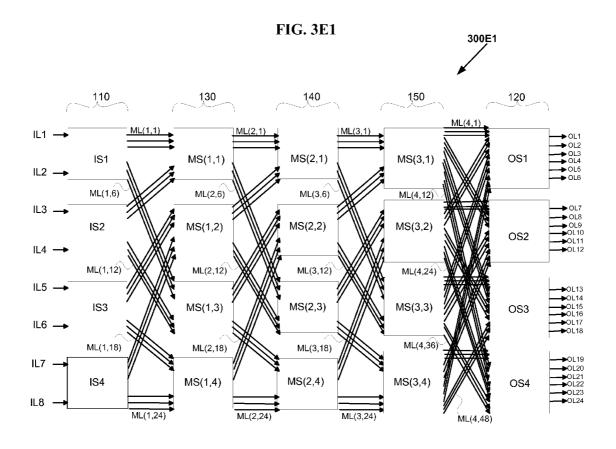

[0070] FIG. 3E1 is a diagram 300E1 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  (having a connection topology called flip network and also known as inverse shuffle exchange network) of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, d=2 and s=3, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

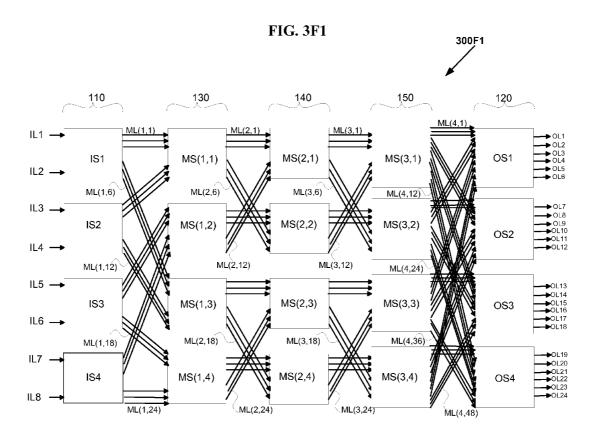

[0071] FIG. 3F1 is a diagram 300F1 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1,\,N_2,\,d,\,s)$  having Baseline connection topology of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, d=2 and s=3, strictly non-blocking network for arbitrary fan-out multicast connections, in accordance with the invention.

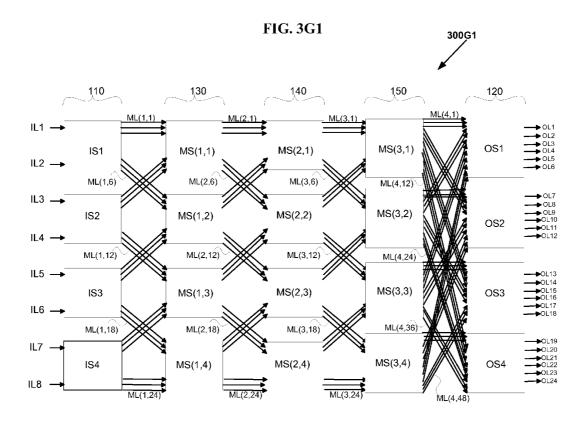

[0072] FIG. 3G1 is a diagram 300G1 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having an exemplary connection topology of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, d=2 and s=3, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

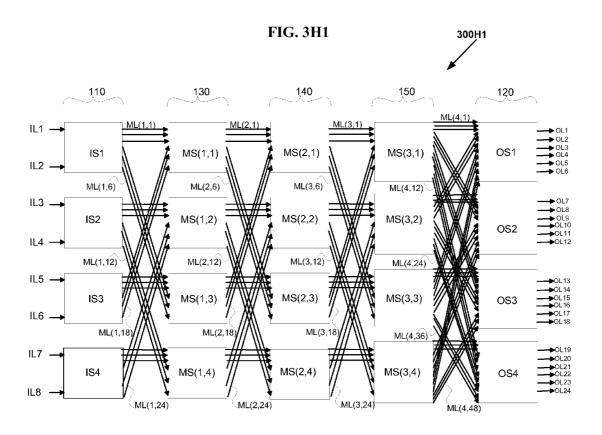

[0073] FIG. 3H1 is a diagram 300H1 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having an exemplary connection topology of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, d=2 and s=3, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

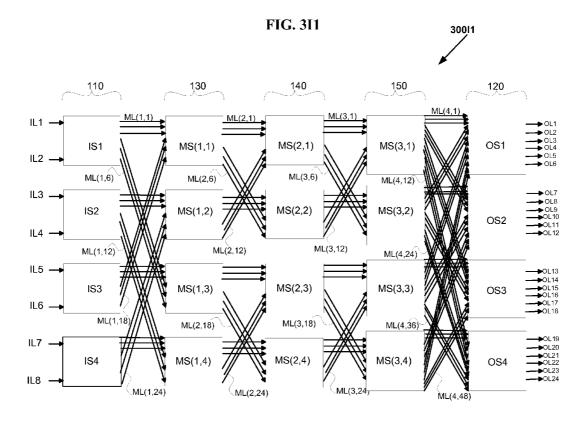

[0074] FIG. 3I1 is a diagram 300I1 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1,\,N_2,\,d,\,s)$  (having a connection topology built using back-to-back Banyan Networks or back-to-back Delta Networks or equivalently back-to-back Butterfly networks) of five stages with  $N_1$ =8,  $N_2$ = $p*N_1$ =24 where p=3, d=2 and s=3, strictly non-blocking network for arbitrary fan-out multicast connections, in accordance with the invention.

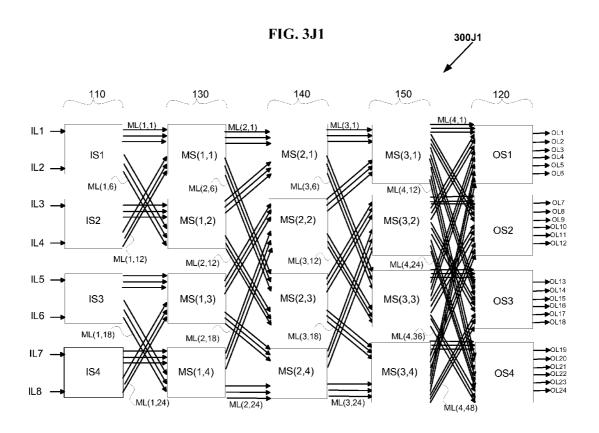

**[0075]** FIG. 3J1 is a diagram 300J1 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having an exemplary connection topology of five stages with  $N_1$ =8,  $N_2$ = $p*N_1$ =24 where p=3, d=2 and s=3, strictly non-blocking network for arbitrary fan-out multicast connections, in accordance with the invention.

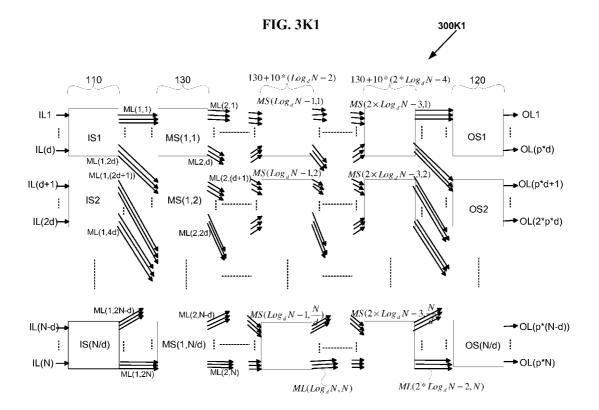

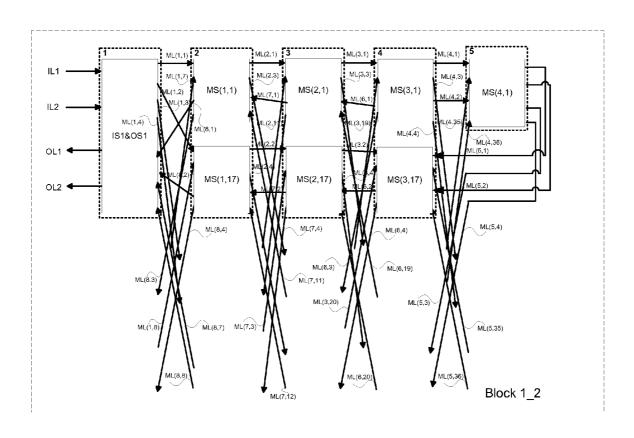

**[0076]** FIG. **3K1** is a diagram **300K1** of a general asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  with  $(2 \times \log_d N) - 1$  stages with  $N_1 = p * N_2$  and s = 3, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

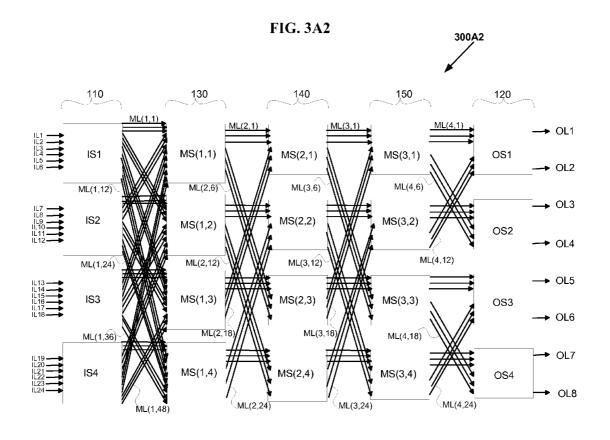

[0077] FIG. 3A2 is a diagram 300A2 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having inverse Benes connection topology of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, d=2 and s=3, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

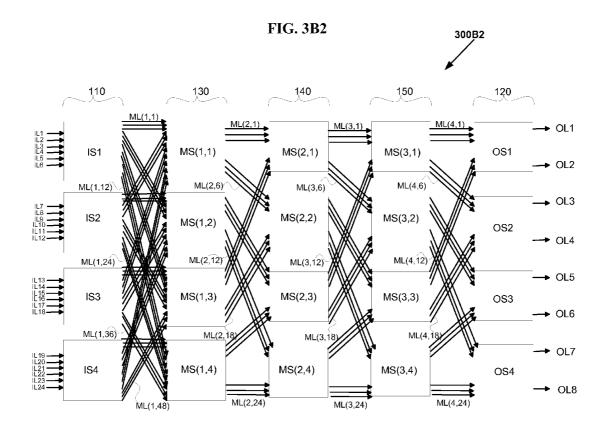

**[0078]** FIG. **3B2** is a diagram **300B2** of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  (having a connection topology built using back-to-back Omega Networks) of five stages with  $N_2$ =8,  $N_1$ = $p*N_2$ =24,

US 2011/0044329 A1

where p=3, d=2 and s=3, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

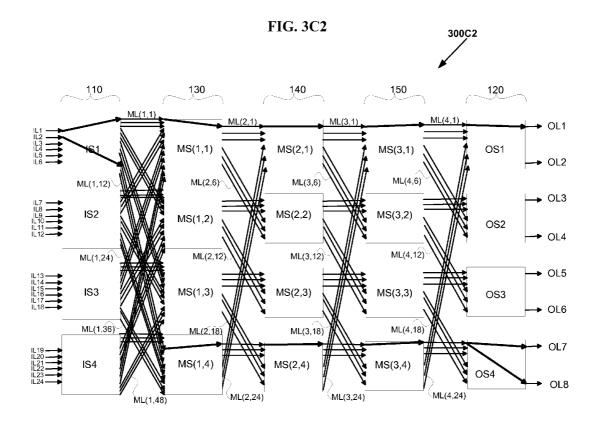

[0079] FIG. 3C2 is a diagram 300C2 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having an exemplary connection topology of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, d=2 and s=3, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

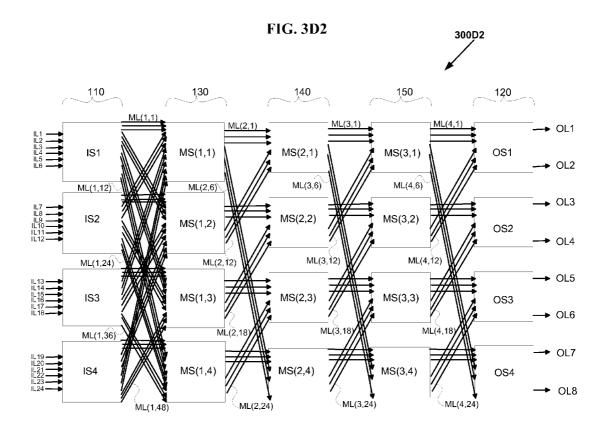

**[0080]** FIG. 3D2 is a diagram 300D2 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having an exemplary connection topology of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, d=2 and s=3, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

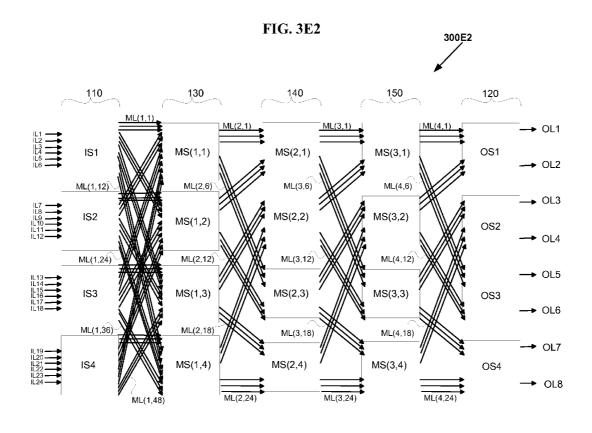

[0081] FIG. 3E2 is a diagram 300E2 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  (having a connection topology called flip network and also known as inverse shuffle exchange network) of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, d=2 and s=3, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

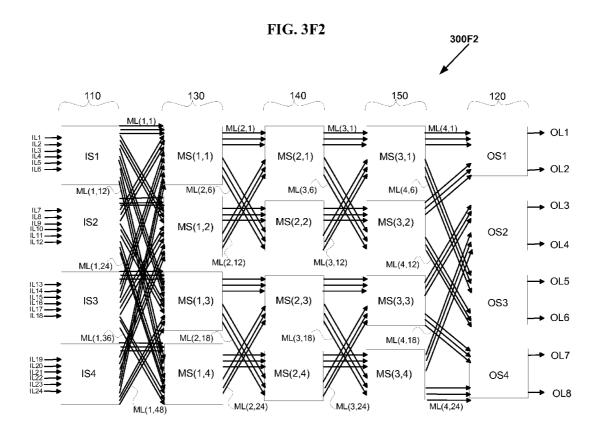

[0082] FIG. 3F2 is a diagram 300F2 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1,\,N_2,\,d,\,s)$  having Baseline connection topology of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, d=2 and s=3, strictly non-blocking network for arbitrary fan-out multicast connections, in accordance with the invention.

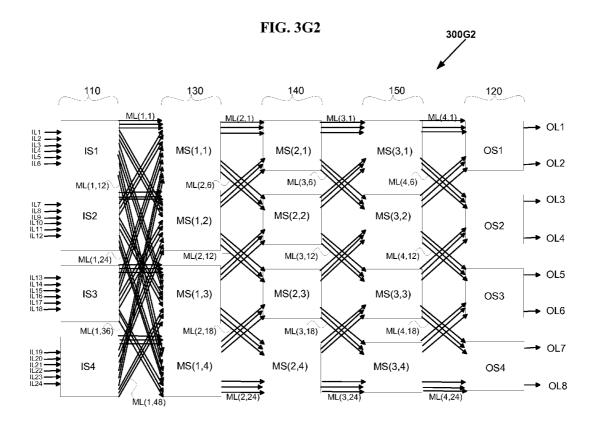

[0083] FIG. 3G2 is a diagram 300G2 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having an exemplary connection topology of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, d=2 and s=3, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

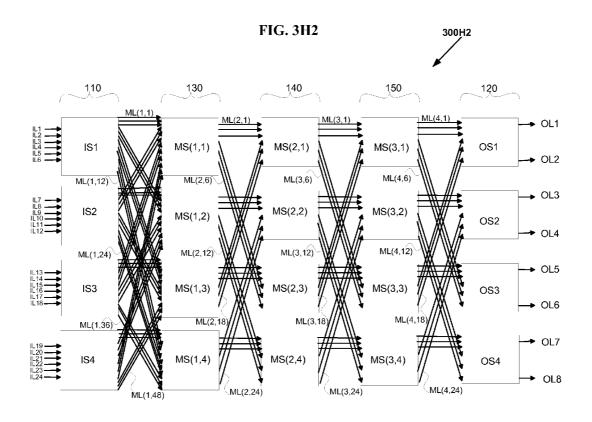

[0084] FIG. 3H2 is a diagram 300H2 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having an exemplary connection topology of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, d=2 and s=3, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

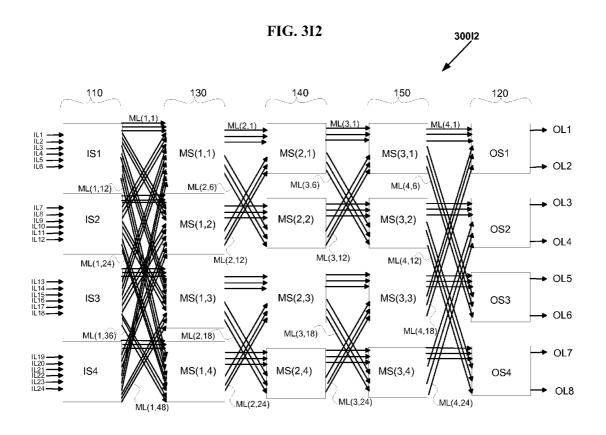

[0085] FIG. 312 is a diagram 30012 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  (having a connection topology built using back-to-back Banyan Networks or back-to-back Delta Networks or equivalently back-to-back Butterfly networks) of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, d=2 and s=3, strictly non-blocking network for arbitrary fan-out multicast connections, in accordance with the invention.

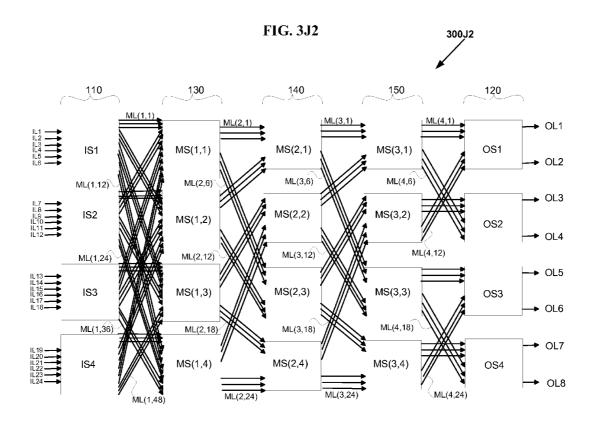

**[0086]** FIG. 3J2 is a diagram 300J2 of an exemplary asymmetrical multi-link multi-stage network  $V_{mlink}(N_1, N_2, d, s)$  having an exemplary connection topology of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, d=2 and s=3, strictly non-blocking network for arbitrary fan-out multicast connections, in accordance with the invention.

[0087] FIG. 3K2 is a diagram 300K2 of a general asymmetrical multi-link multi-stage network  $V_{mlink}(N_1,\,N_2,\,d,\,s)$  with  $(2\times\log_d\,N)-1$  stages with  $N_2=p^*N_1$  and s=3, strictly nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

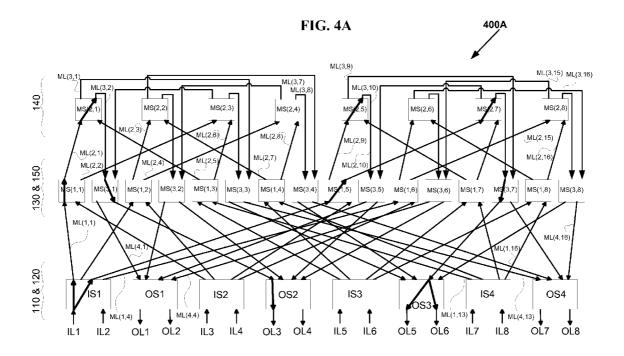

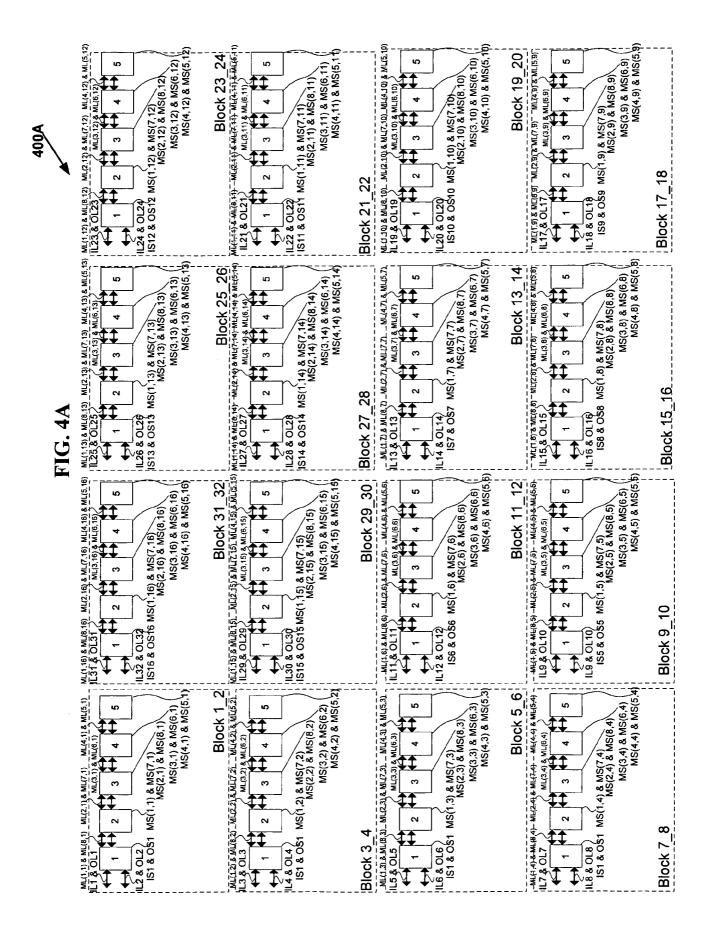

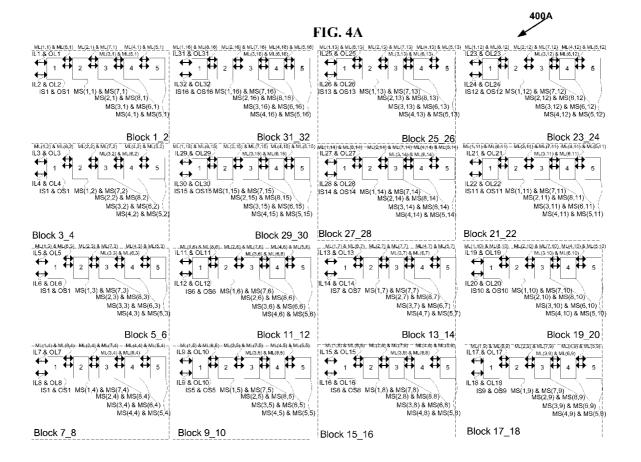

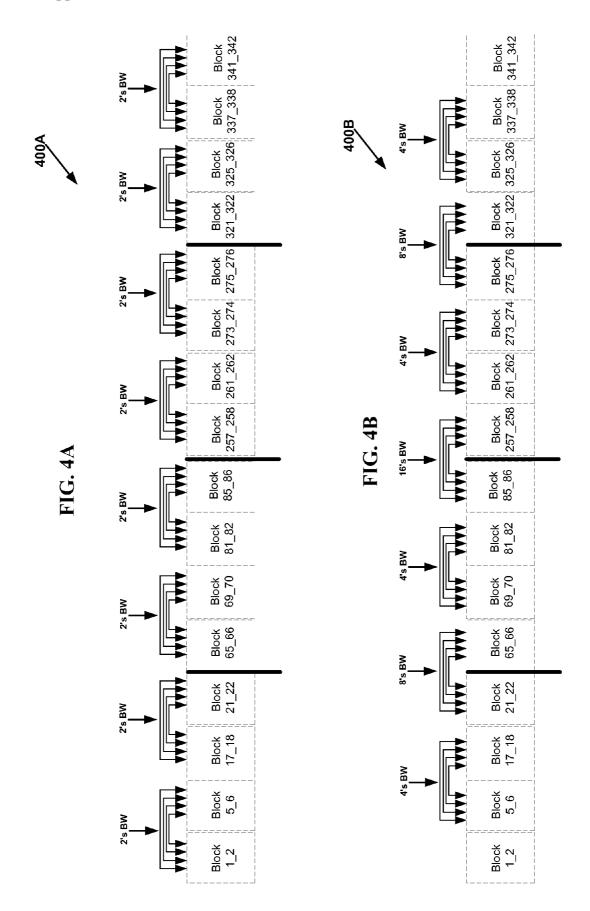

**[0088]** FIG. **4A** is a diagram **400**A of an exemplary symmetrical folded multi-stage network  $V_{fold}(N, d, s)$  having inverse Benes connection topology of five stages with N=8, d=2 and s=2 with exemplary multicast connections, strictly nonblocking network for unicast connections and rearrange-

ably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

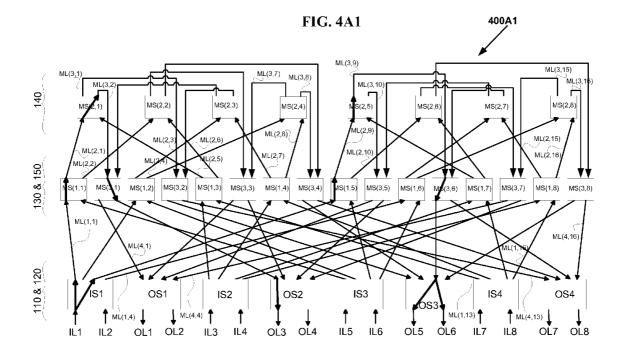

[0089] FIG. 4A1 is a diagram 400A1 of an exemplary symmetrical folded multi-stage network  $V_{fold}(N,\ d,\ 2)$  having Omega connection topology of five stages with N=8, d=2 and s=2 with exemplary multicast connections, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

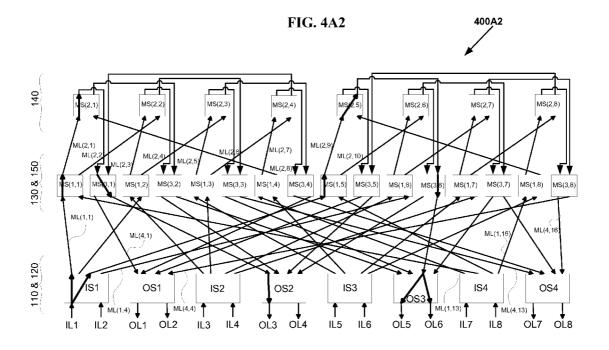

[0090] FIG. 4A2 is a diagram 400A2 of an exemplary symmetrical folded multi-stage network  $V_{fold}(N,\ d,\ 2)$  having nearest neighbor connection topology of five stages with N=8, d=2 and s=2 with exemplary multicast connections, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

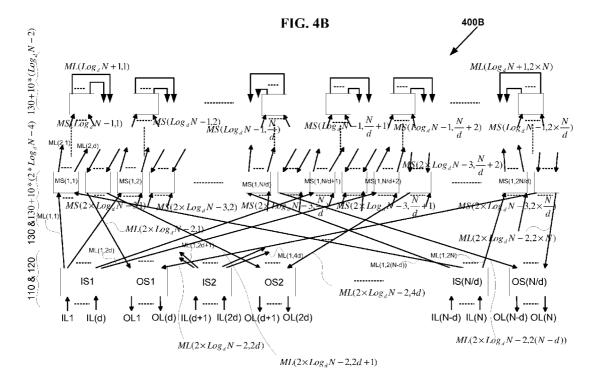

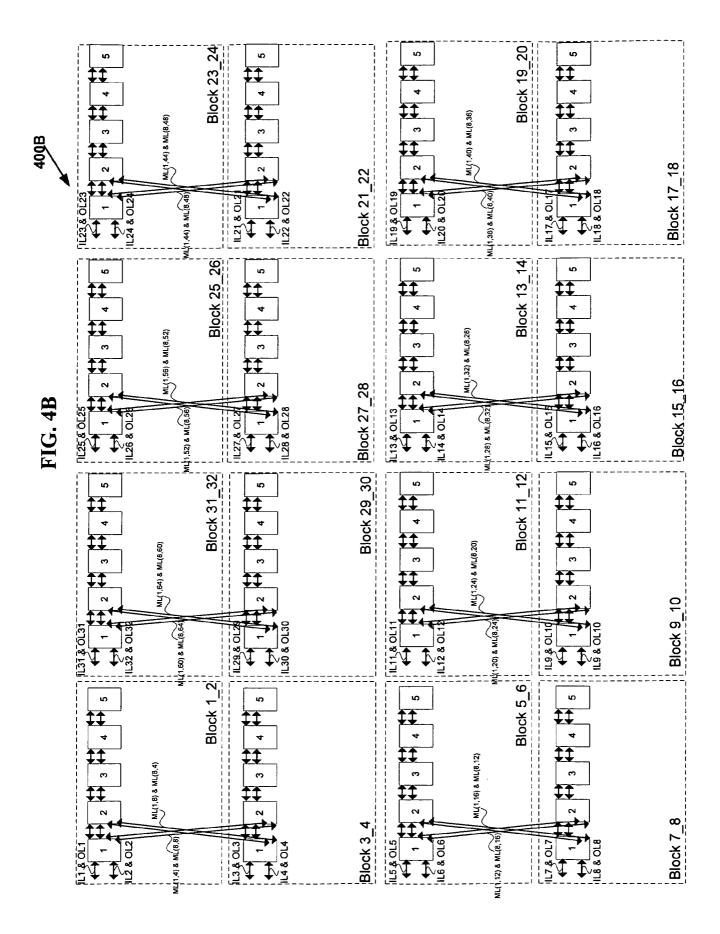

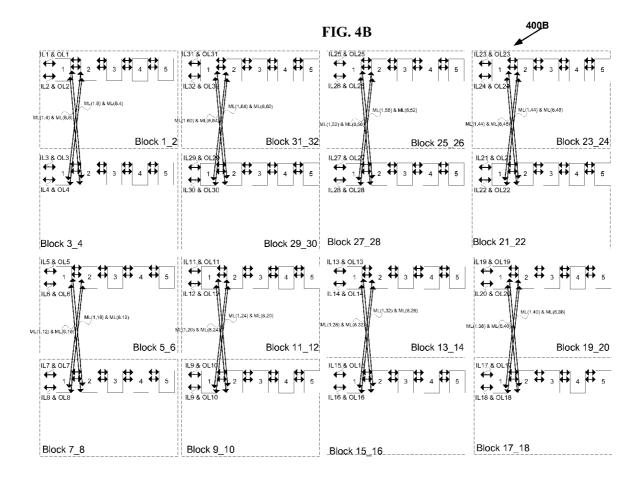

[0091] FIG. 4B is a diagram 400B of a general symmetrical folded multi-stage network  $V_{fold}(N, d, 2)$  with  $(2 \times \log_d N) - 1$  stages strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections in accordance with the invention.

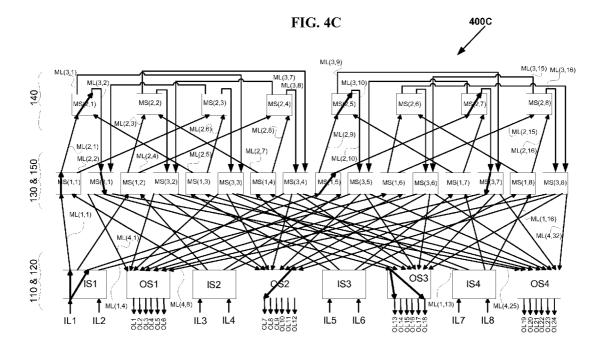

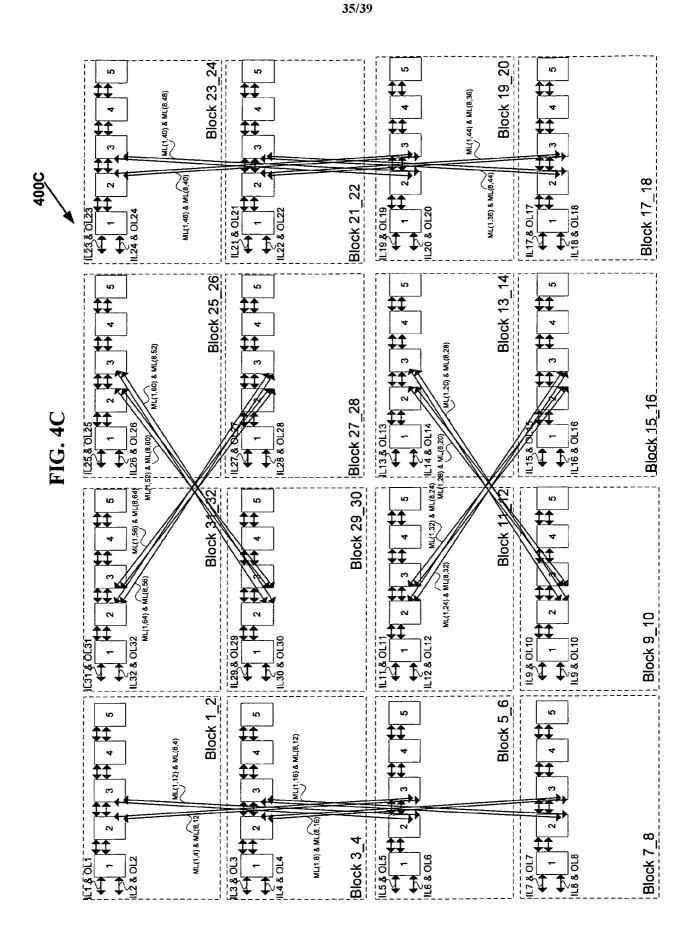

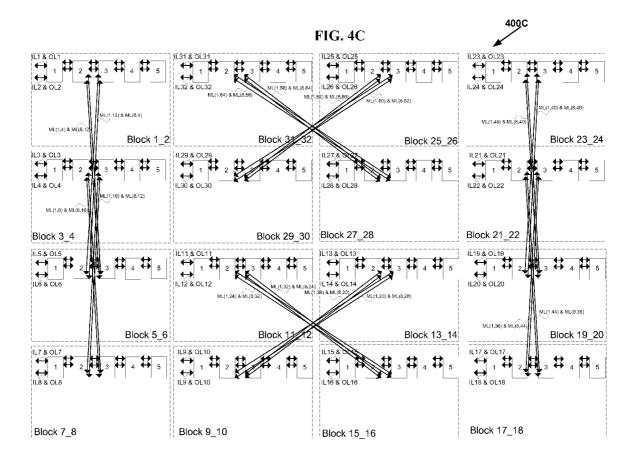

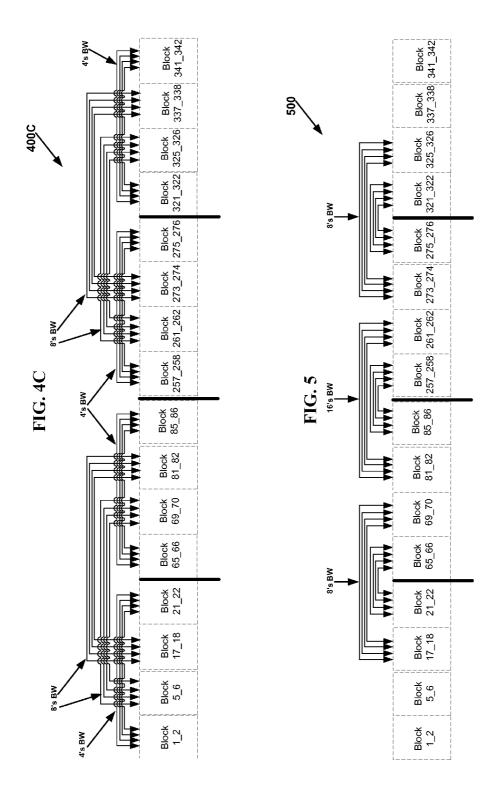

**[0092]** FIG. 4C is a diagram 400C of an exemplary asymmetrical folded multi-stage network  $V_{fold}(N_1, N_2, d, 2)$  having inverse Benes connection topology of five stages with  $N_1$ =8,  $N_2$ = $p*N_1$ =24 where p=3, and d=2 with exemplary multicast connections, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

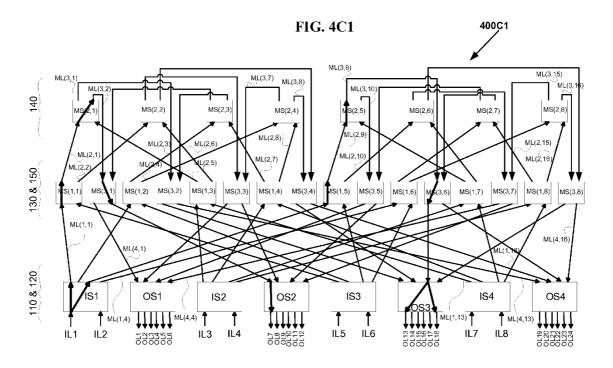

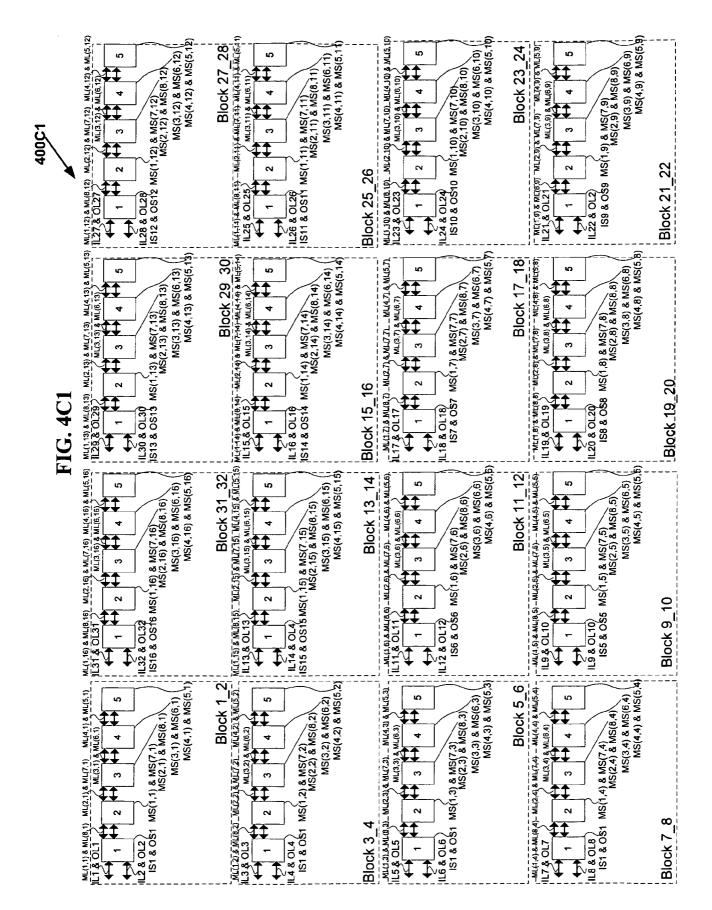

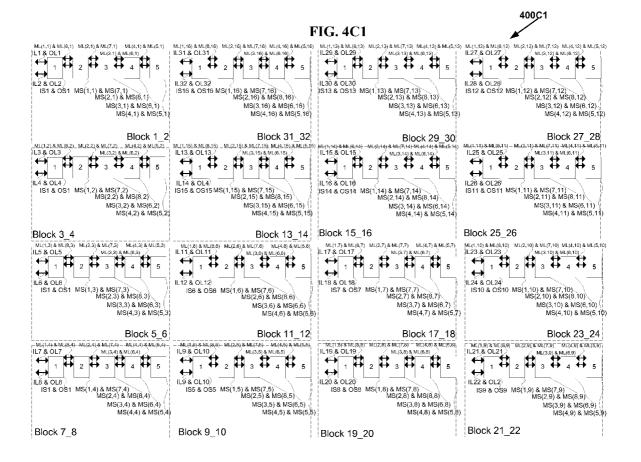

[0093] FIG. 4C1 is a diagram 400C1 of an exemplary asymmetrical folded multi-stage network  $V_{\it fold}(N_1,N_2,d,2)$  having Omega connection topology of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, and d=2 with exemplary multicast connections, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

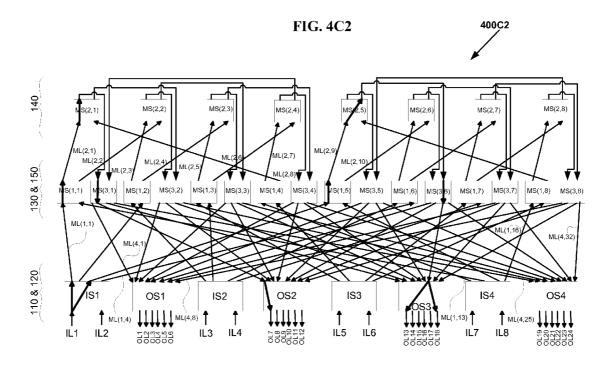

[0094] FIG. 4C2 is a diagram 400C2 of an exemplary asymmetrical folded multi-stage network  $V_{\it fold}(N_1, N_2, d, 2)$  having nearest neighbor connection topology of five stages with  $N_1$ =8,  $N_2$ =p\* $N_1$ =24 where p=3, and d=2 with exemplary multicast connections, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

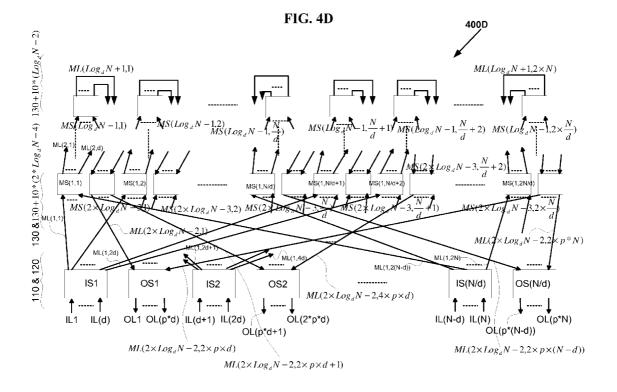

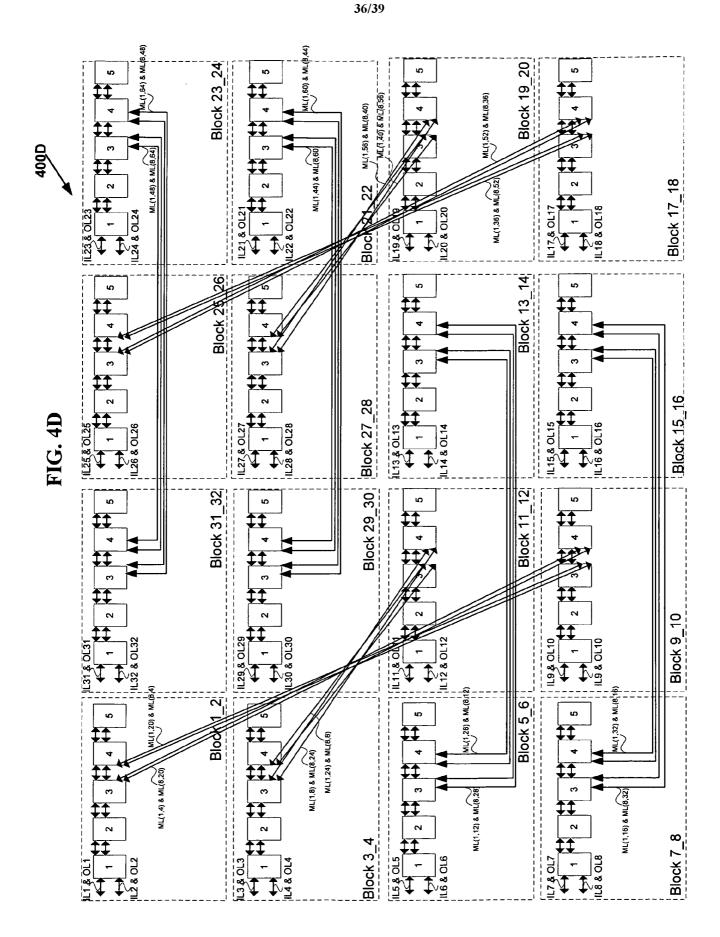

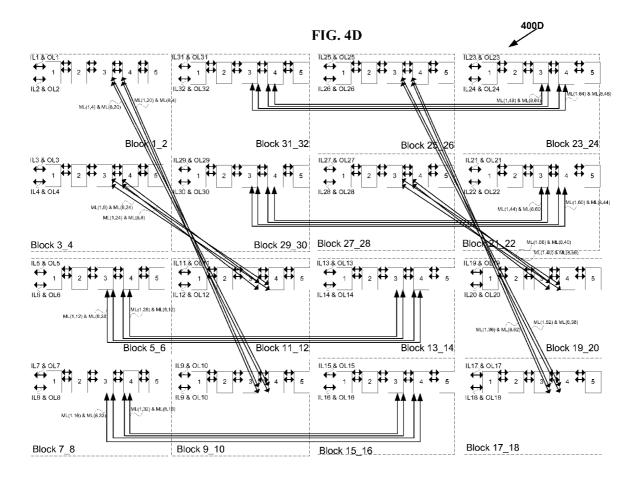

**[0095]** FIG. 4D is a diagram 400D of a general asymmetrical folded multi-stage network  $V_{fold}(N_1, N_2, d, 2)$  with  $N_2$ =p\* $N_1$  and with  $(2 \times \log_d N)$ -1 stages strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections in accordance with the invention.

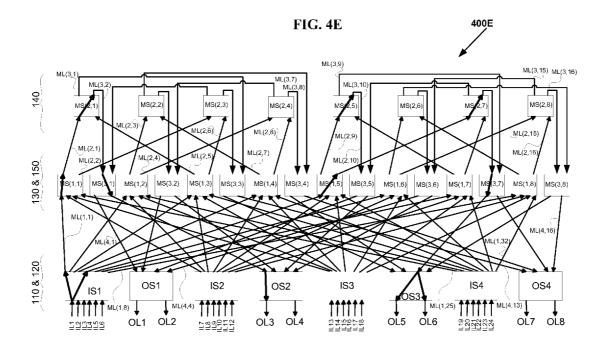

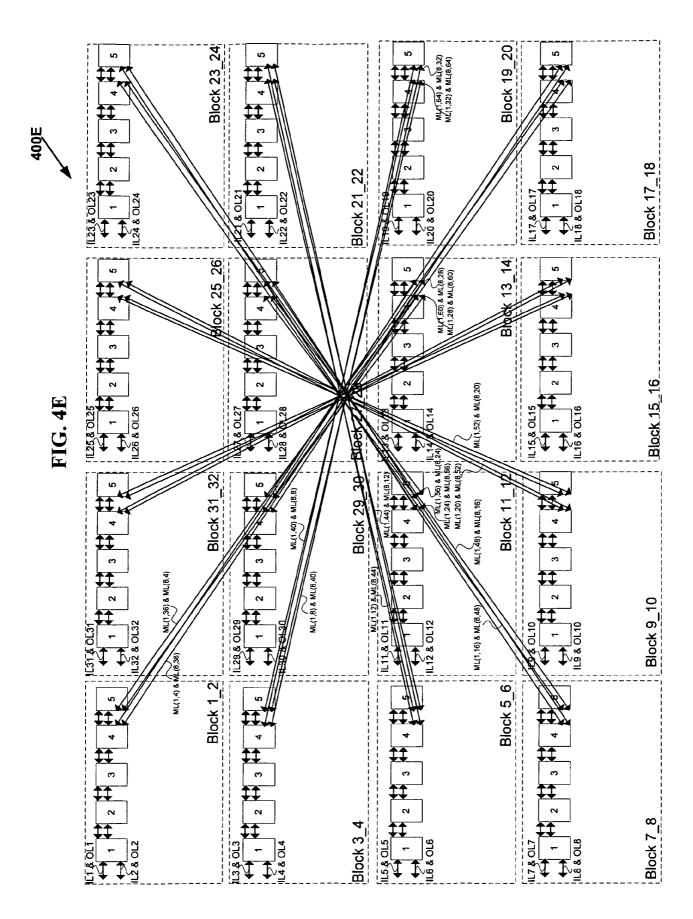

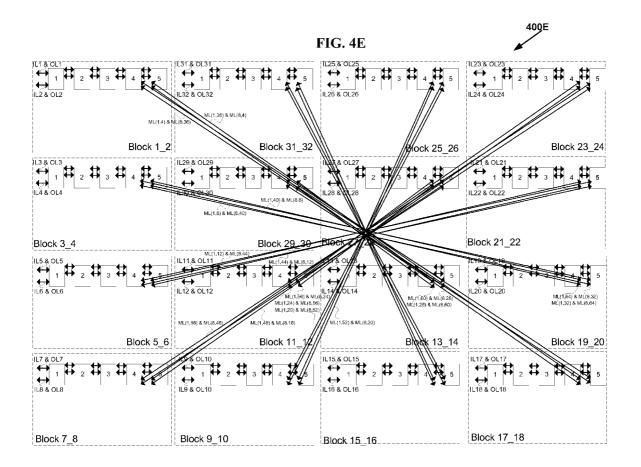

[0096] FIG. 4E is a diagram 400E of an exemplary asymmetrical folded multi-stage network  $V_{fold}(N_1, N_2, d, 2)$  having inverse Benes connection topology of five stages with  $N_2$ =8,  $N_1$ = $p*N_2$ =24, where p=3, and d=2 with exemplary multicast connections, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

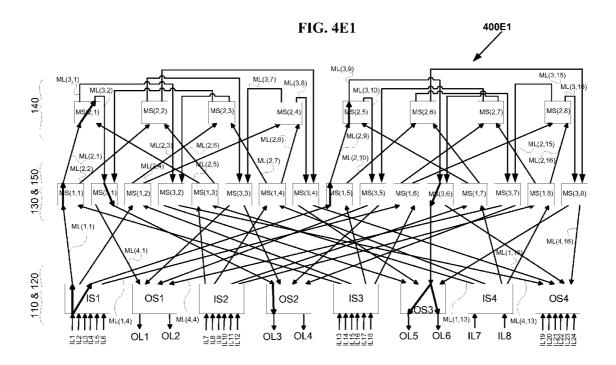

[0097] FIG. 4E1 is a diagram 400E1 of an exemplary asymmetrical folded multi-stage network  $V_{fold}(N_1, N_2, d, 2)$  having Omega connection topology of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, and d=2 with exemplary multicast connections, strictly nonblocking network for unicast con-

US 2011/0044329 A1

Feb. 24, 2011

nections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

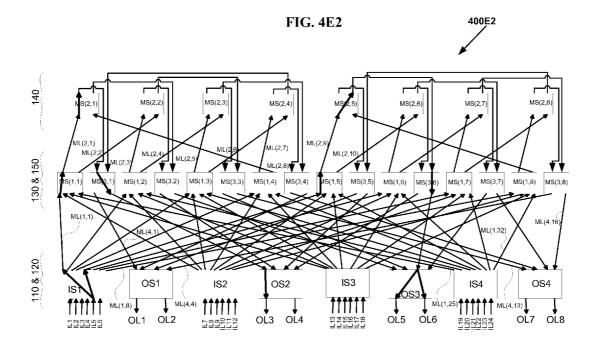

[0098] FIG. 4E2 is a diagram 400E2 of an exemplary asymmetrical folded multi-stage network  $V_{fold}(N_1, N_2, d, 2)$  having nearest neighbor connection topology of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, and d=2 with exemplary multicast connections, strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections, in accordance with the invention.

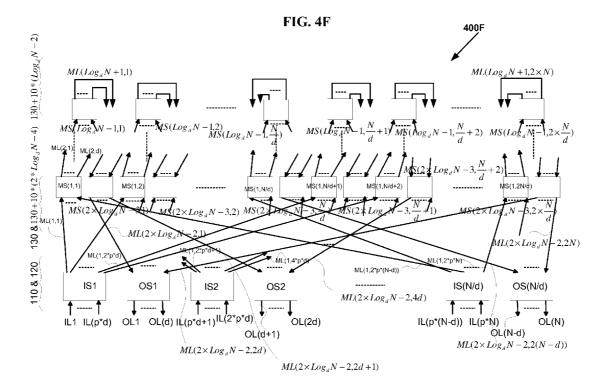

[0099] FIG. 4F is a diagram 400F of a general asymmetrical folded multi-stage network  $V_{fold}(N_1,N_2,d,2)$  with  $N_1$ =p\* $N_2$  and with  $(2\times\log_d N)-1$  stages strictly nonblocking network for unicast connections and rearrangeably nonblocking network for arbitrary fan-out multicast connections in accordance with the invention.

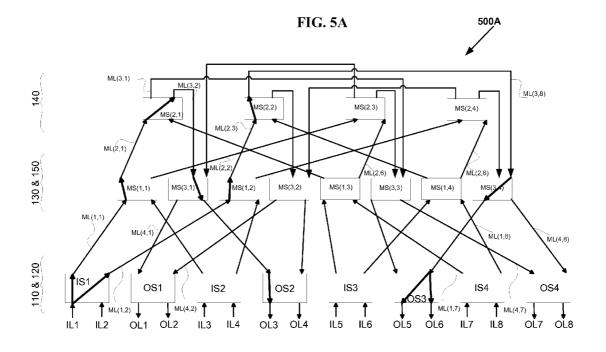

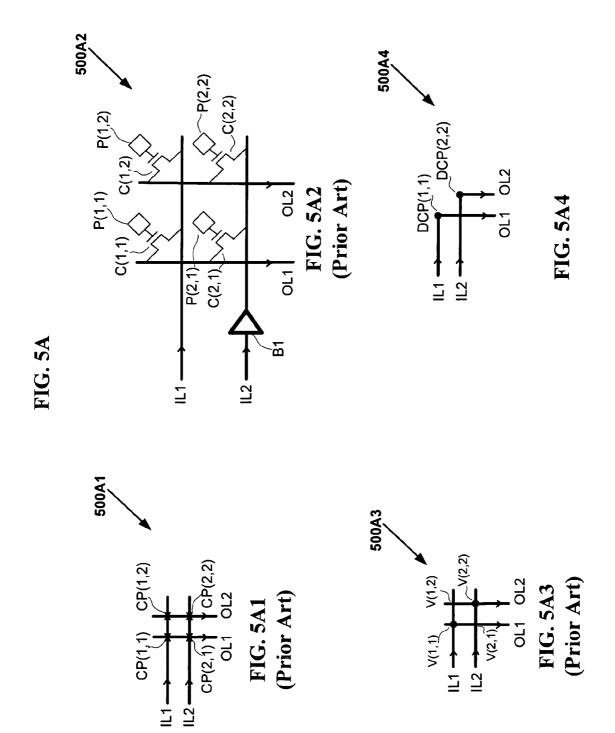

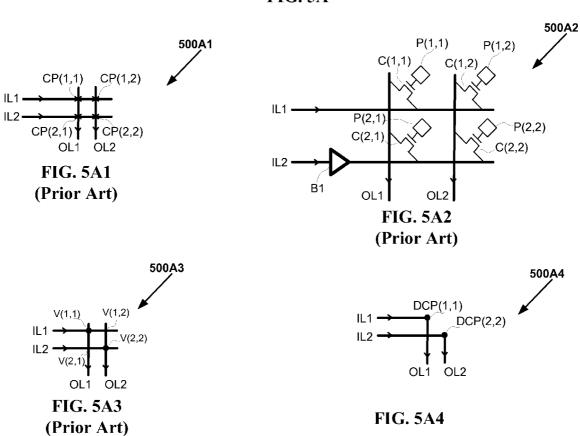

**[0100]** FIG. **5**A is a diagram **500**A of an exemplary symmetrical folded multi-stage network  $V_{fold}(N, d, s)$  having inverse Benes connection topology of five stages with N=8, d=2 and s=1 with exemplary unicast connections rearrangeably nonblocking network for unicast connections, in accordance with the invention.

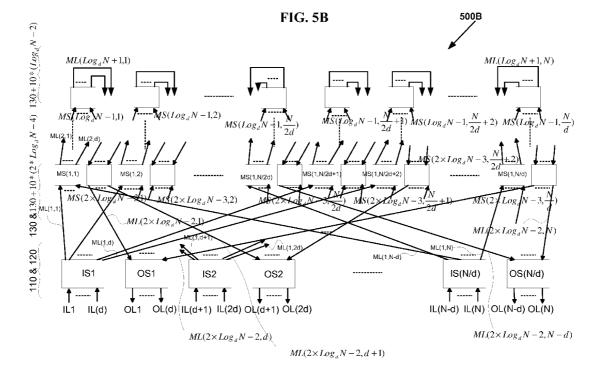

**[0101]** FIG. **5**B is a diagram **500**B of a general symmetrical folded multi-stage network  $V_{fold}(N, d, 1)$  with  $(2 \times \log_d N) - 1$  stages rearrangeably nonblocking network for unicast connections in accordance with the invention.

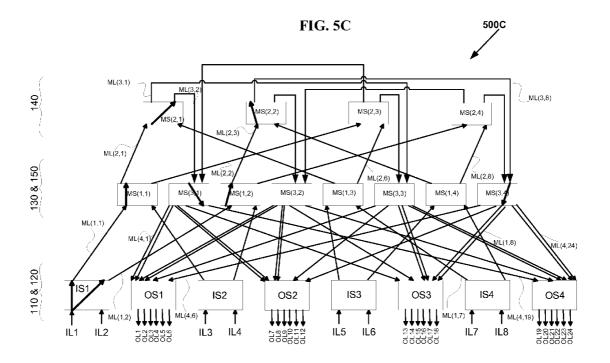

**[0102]** FIG. 5C is a diagram **500**C of an exemplary asymmetrical folded multi-stage network  $V_{fold}(N_1, N_2, d, 1)$  having inverse Benes connection topology of five stages with  $N_1$ =8,  $N_2$ = $p*N_1$ =24 where p=3, and d=2 with exemplary unicast connections rearrangeably nonblocking network for unicast connections, in accordance with the invention.

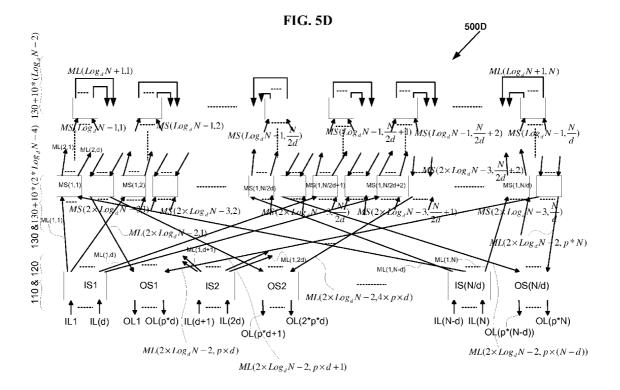

**[0103]** FIG. **5**D is a diagram **500**D of a general asymmetrical folded multi-stage network  $V_{fold}(N_1, N_2, d, 1)$  with  $N_2$ =p\* $N_1$  and with  $(2 \times \log_d N)$ -1 stages rearrangeably non-blocking network for unicast connections in accordance with the invention.

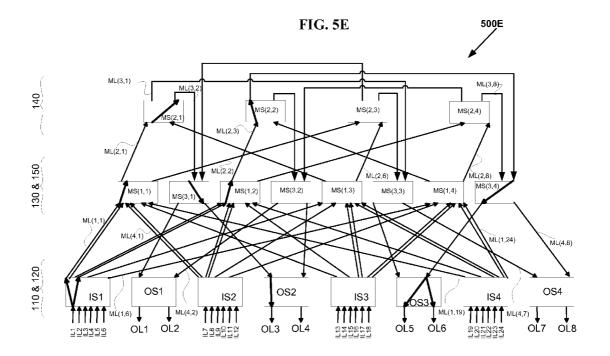

**[0104]** FIG. 5E is a diagram 500E of an exemplary asymmetrical folded multi-stage network  $V_{fold}(N_1, N_2, d, 1)$  having inverse Benes connection topology of five stages with  $N_2$ =8,  $N_1$ =p\* $N_2$ =24, where p=3, and d=2 with exemplary unicast connections rearrangeably nonblocking network for unicast connections, in accordance with the invention.

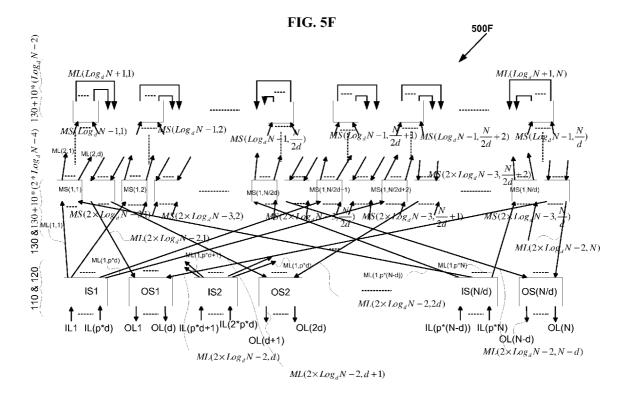

[0105] FIG. 5F is a diagram 500F of a general asymmetrical folded multi-stage network  $V_{fold}(N_1,N_2,d,1)$  with  $N_1$ =p\* $N_2$  and with  $(2\times\log_d N)$ -1 stages rearrangeably nonblocking network for unicast connections in accordance with the invention.

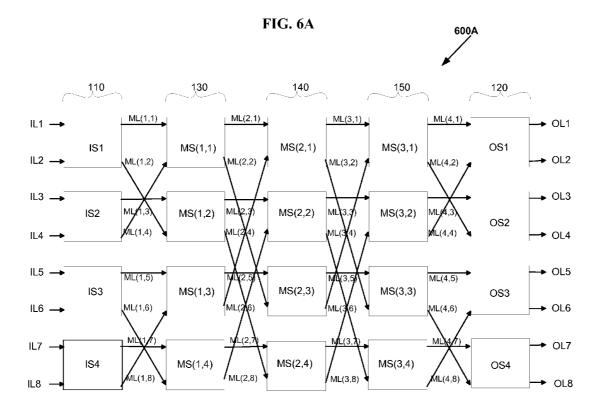

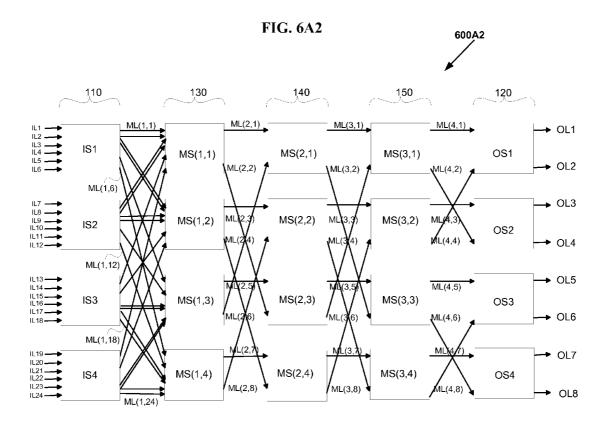

[0106] FIG. 6A is a diagram 600A of an exemplary symmetrical multi-stage network V(N,d,s) having inverse Benes connection topology of five stages with N=8, d=2 and s=1, rearrangeably nonblocking network for unicast connections, in accordance with the invention.

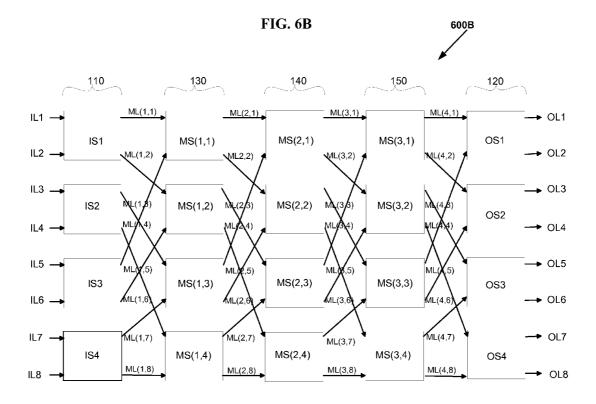

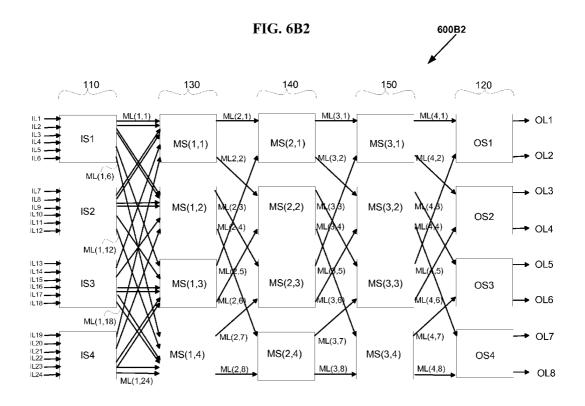

[0107] FIG. 6B is a diagram 600B of an exemplary symmetrical multi-stage network V(N,d,s) (having a connection topology built using back-to-back Omega Networks) of five stages with N=8, d=2 and s=1, rearrangeably nonblocking network for unicast connections.

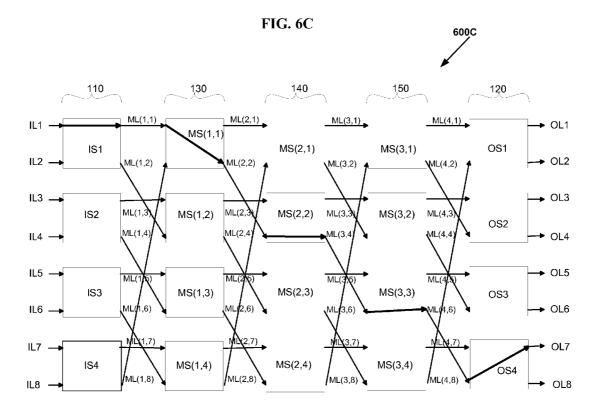

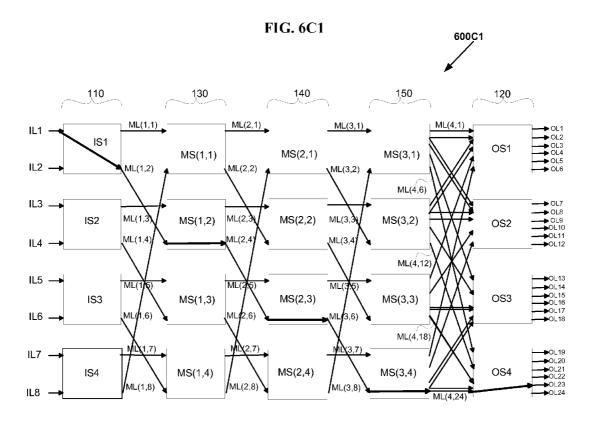

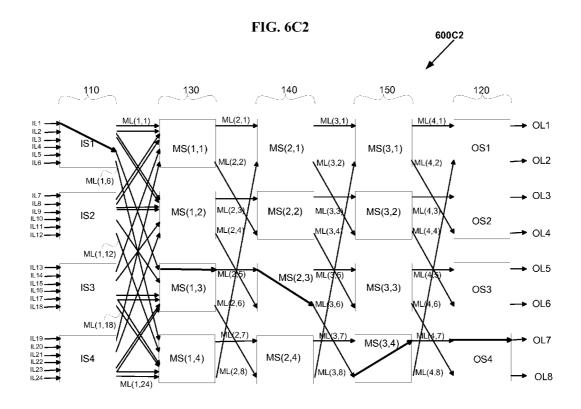

[0108] FIG. 6C is a diagram 600C of an exemplary symmetrical multi-stage network V(N,d,s) having an exemplary connection topology of five stages with N=8, d=2 and s=1, rearrangeably nonblocking network for unicast connections, in accordance with the invention.

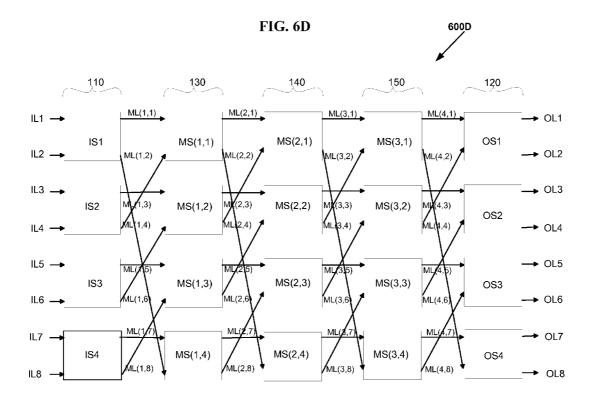

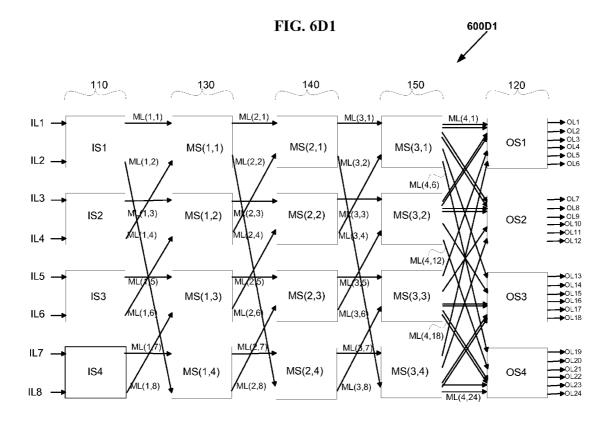

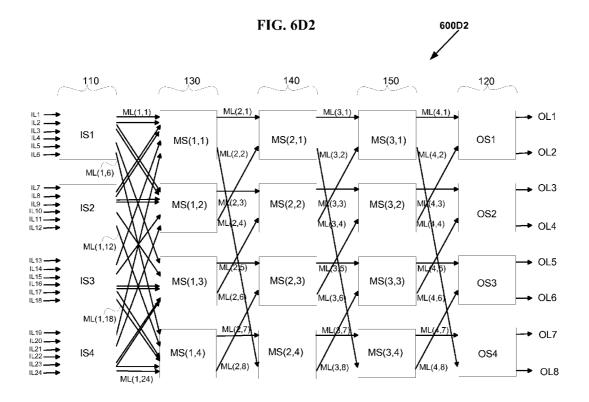

**[0109]** FIG. 6D is a diagram **600**D of an exemplary symmetrical multi-stage network V(N,d,s) having an exemplary connection topology of five stages with N=8, d=2 and s=1, rearrangeably nonblocking network for unicast connections, in accordance with the invention.

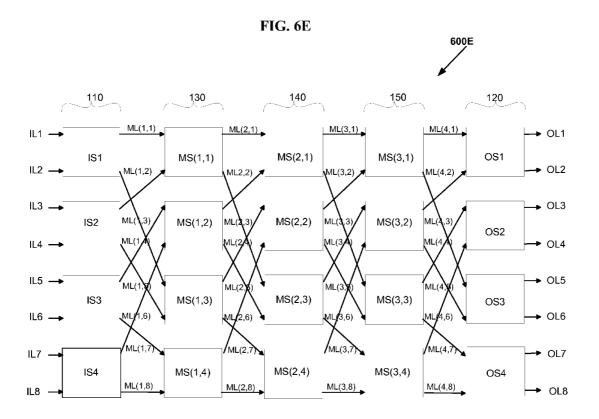

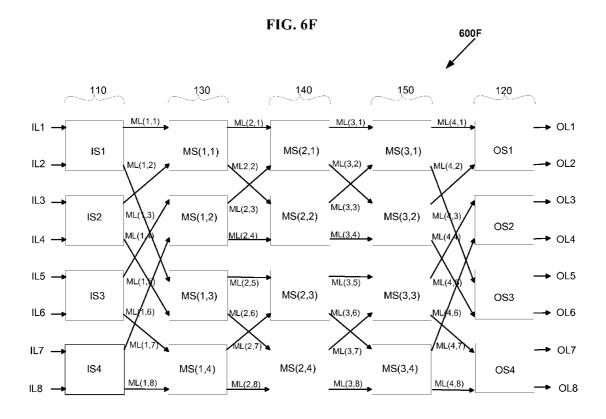

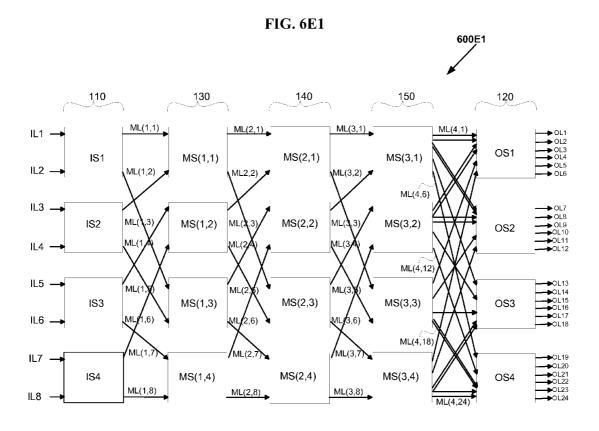

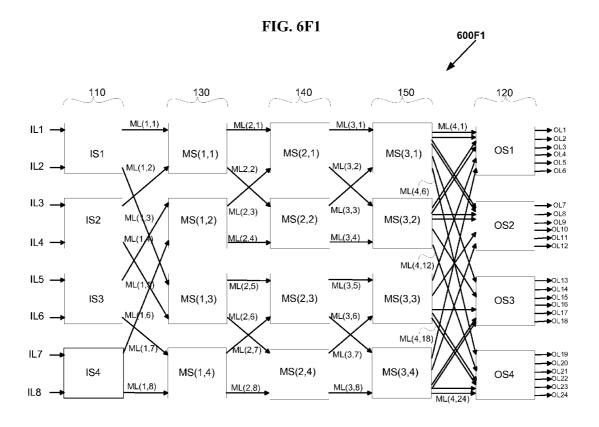

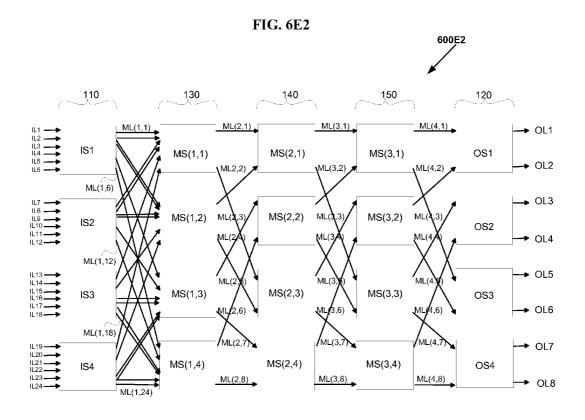

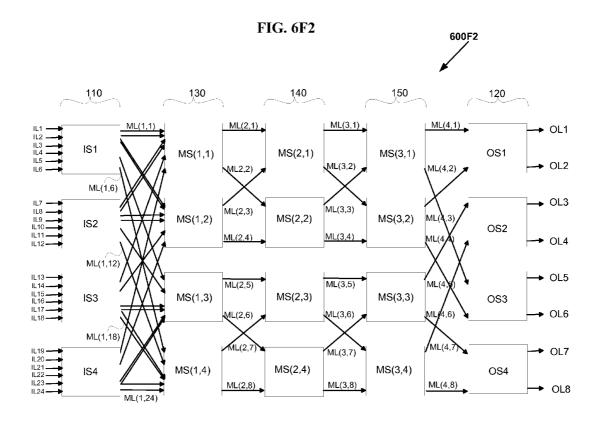

[0110] FIG. 6E is a diagram 600E of an exemplary symmetrical multi-stage network V(N,d,s) (having a connection topology called flip network and also known as inverse shuffle exchange network) of five stages with N=8, d=2 and s=1, rearrangeably nonblocking network for unicast connections. [0111] FIG. 6F is a diagram 600F of an exemplary symmetrical multi-stage network V(N,d,s) having Baseline connection topology of five stages with N=8, d=2 and s=1, rearrangeably nonblocking network for unicast connections.

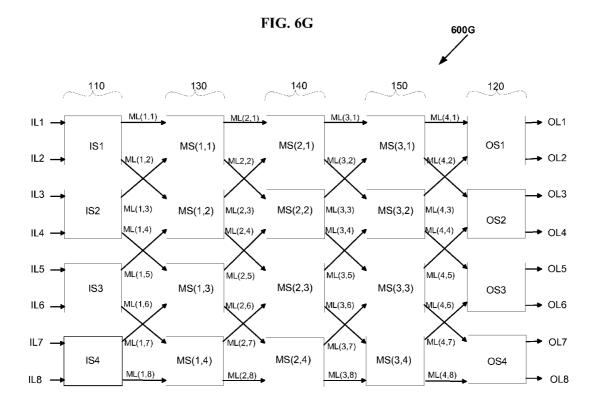

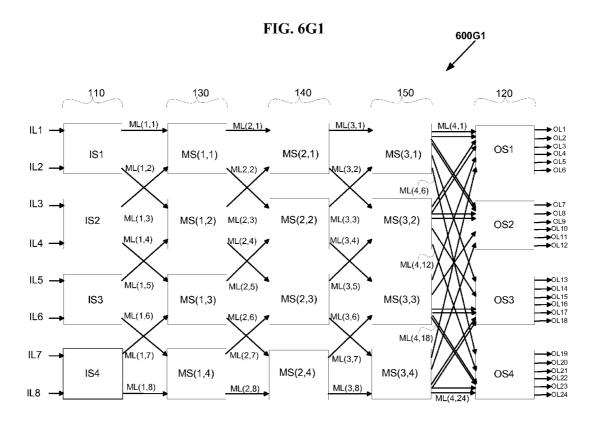

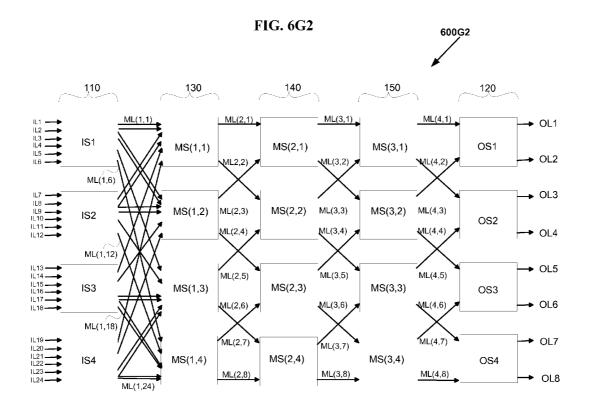

**[0112]** FIG. 6G is a diagram 600G of an exemplary symmetrical multi-stage network V(N,d,s) having an exemplary connection topology of five stages with N=8, d=2 and s=1, rearrangeably nonblocking network for unicast connections, in accordance with the invention.

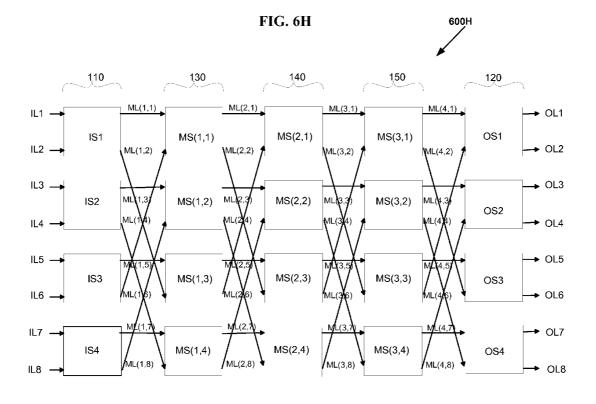

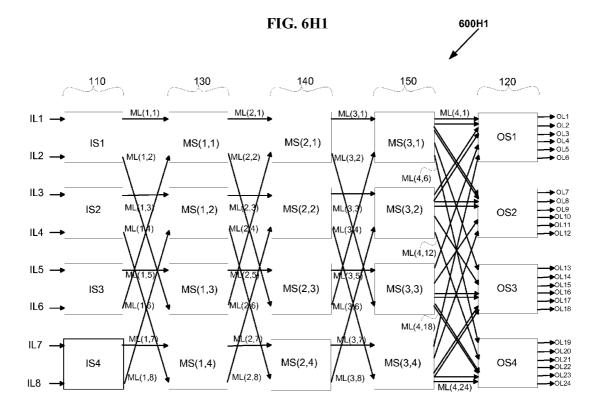

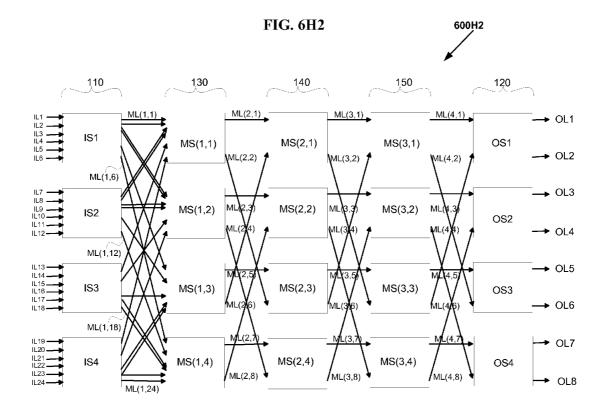

[0113] FIG. 6H is a diagram 600H of an exemplary symmetrical multi-stage network V(N,d,s) having an exemplary connection topology of five stages with N=8, d=2 and s=1, rearrangeably nonblocking network for unicast connections, in accordance with the invention.

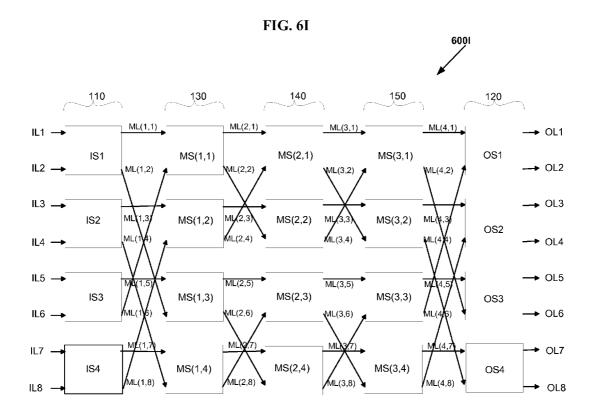

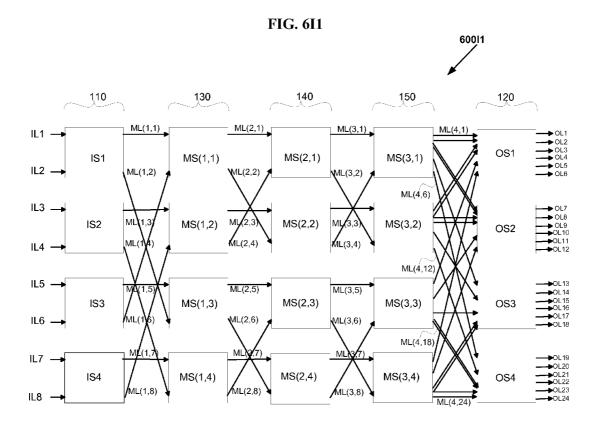

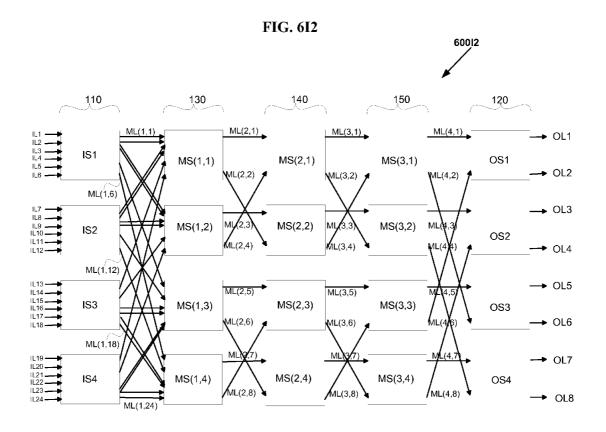

[0114] FIG. 6I is a diagram 600I of an exemplary symmetrical multi-stage network V(N,d,s) (having a connection topology built using back-to-back Banyan Networks or back-to-back Delta Networks or equivalently back-to-back Butterfly networks) of five stages with N=8, d=2 and s=1, rearrangeably nonblocking network for unicast connections.

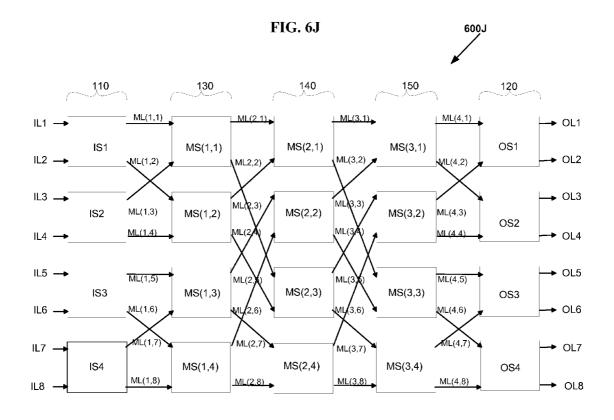

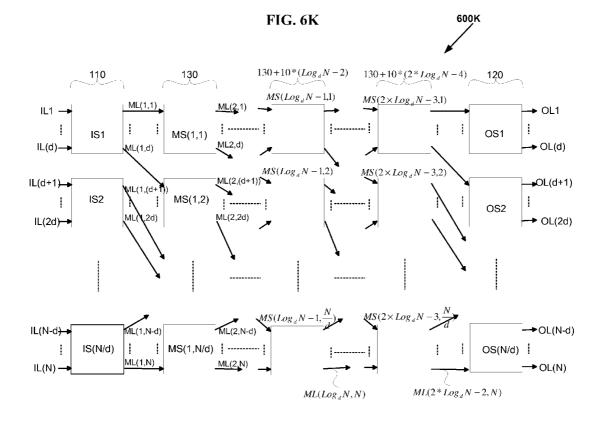

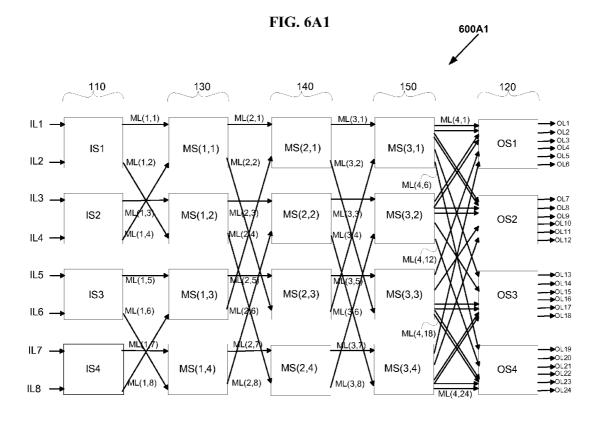

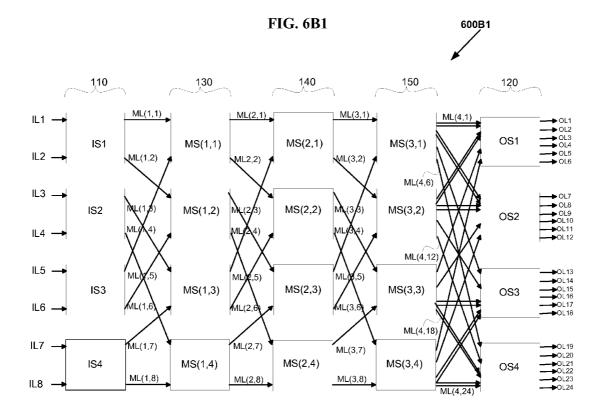

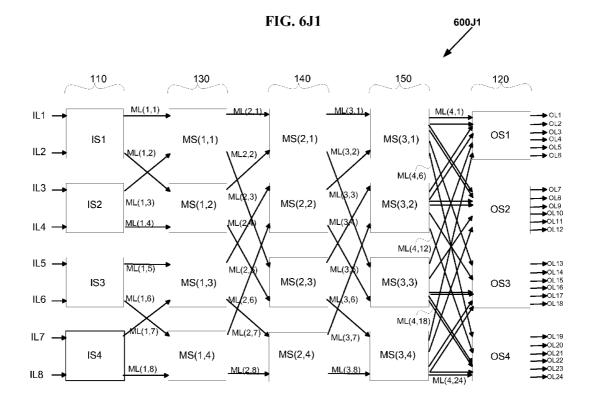

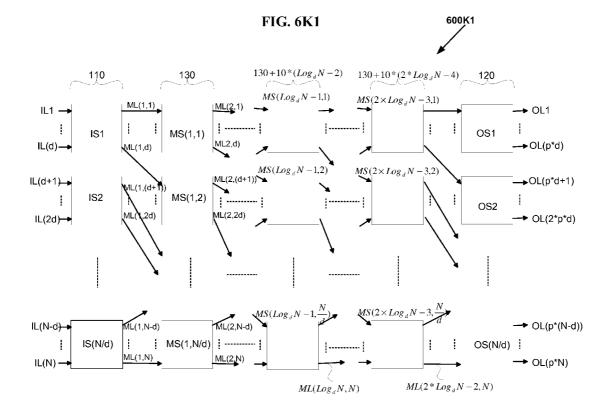

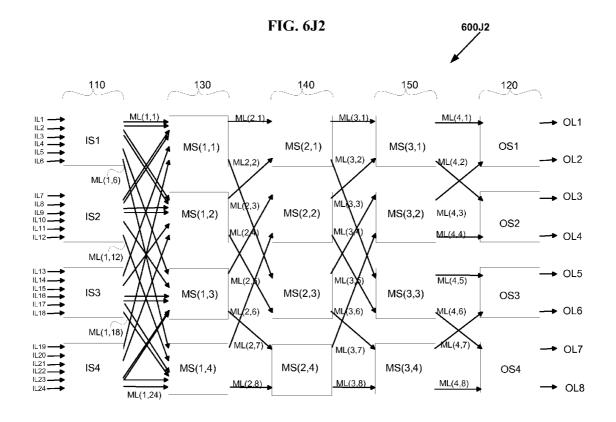

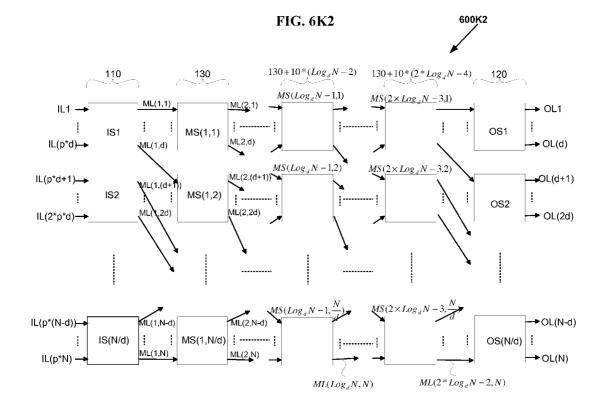

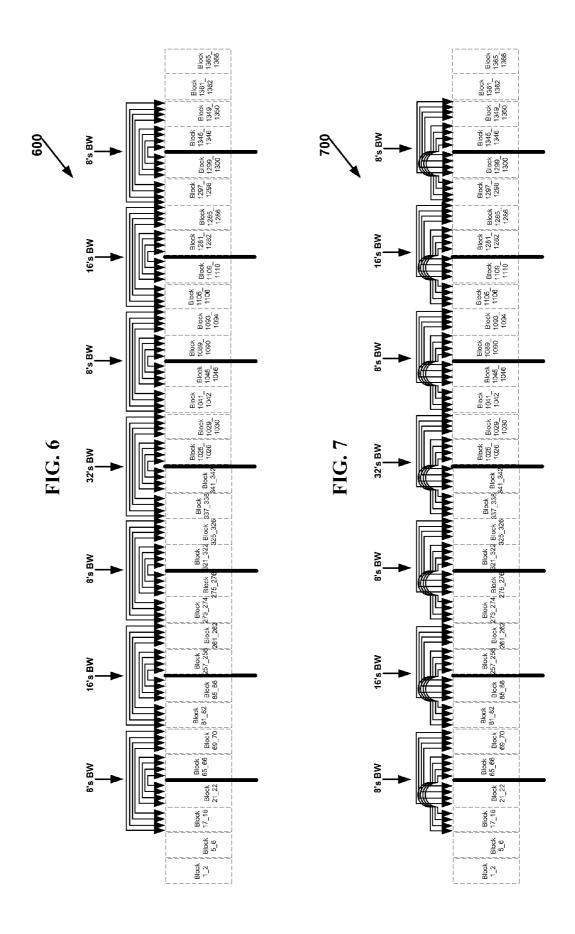

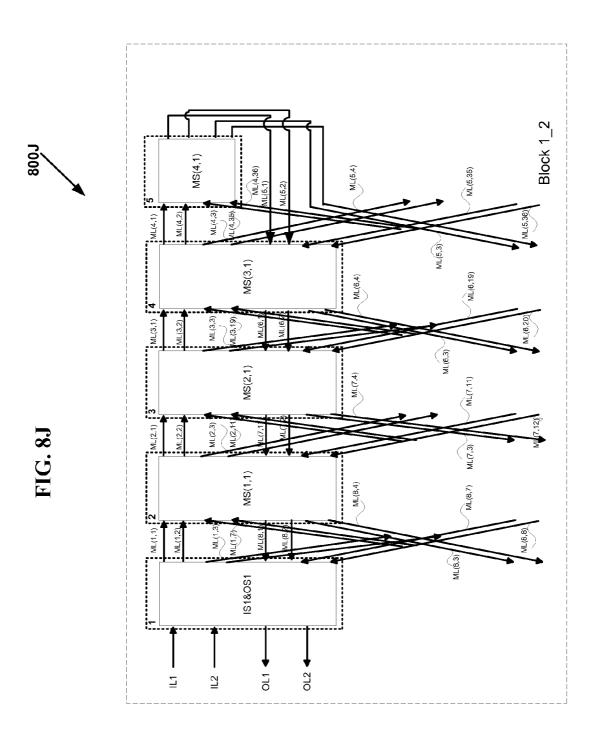

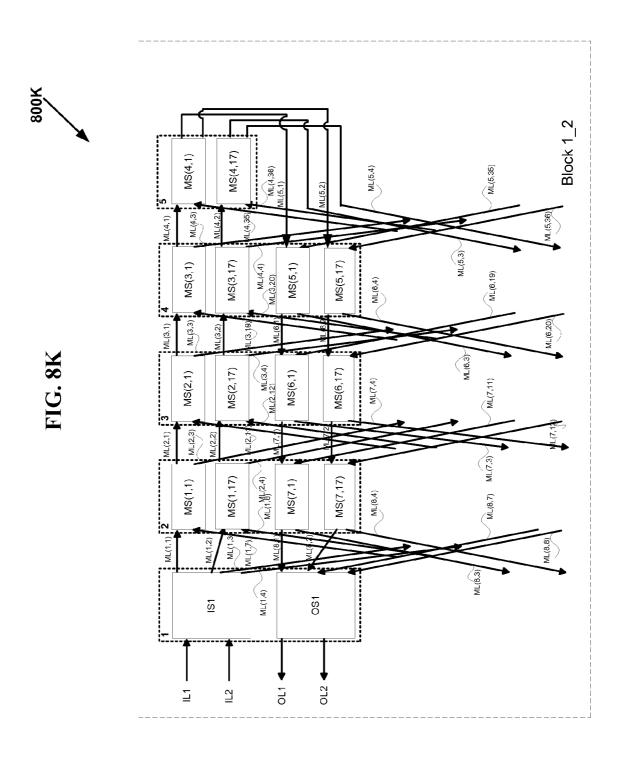

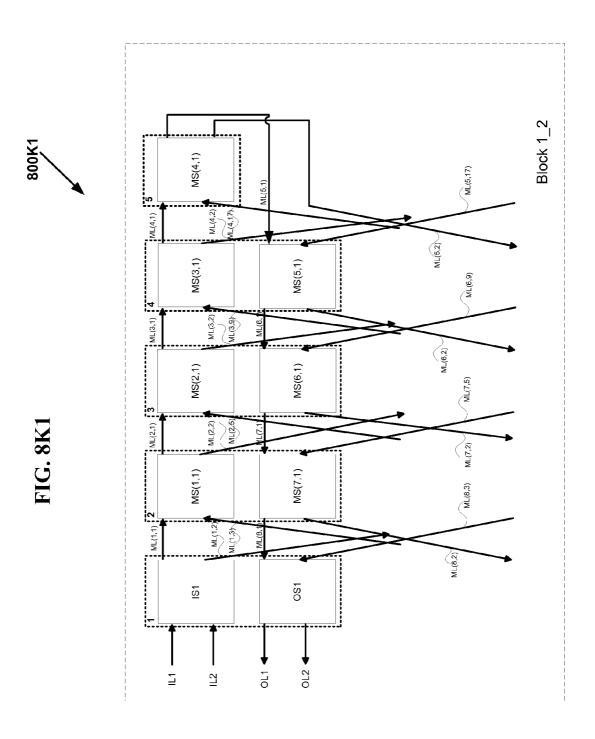

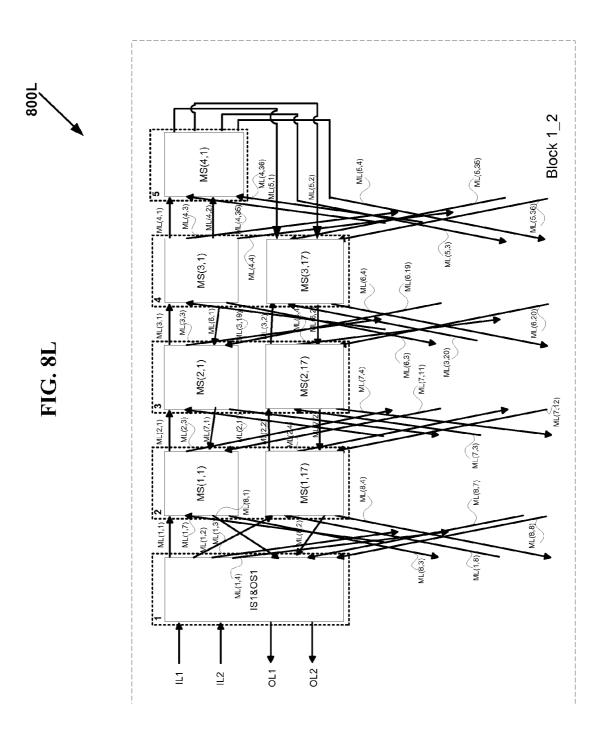

[0115] FIG. 6J is a diagram 600J of an exemplary symmetrical multi-stage network V(N,d,s) having an exemplary connection topology of five stages with N=8, d=2 and s=1, rearrangeably nonblocking network for unicast connections. [0116] FIG. 6K is a diagram 600K of a general symmetrical multi-stage network V(N,d,s) with  $(2\times\log_d N)-1$  stages with s=1, rearrangeably nonblocking network for unicast connections in accordance with the invention.