|                                                                                                                                                            | Page 1 of 483 IPR2020-00261                                                                                                                                                                                                                                                                                                                 | VENKAT KONDA EXHIBIT 2030                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6                                                                                                                                 | Venkat Konda, Ph.D.<br>6278 Grand Oak Way<br>San Jose, CA 95135<br>Telephone: (408) 472-3273<br>Email: vkonda@gmail.com<br>Plaintiff <i>pro se</i><br>IN THE SUPERIOR COURT OF                                                                                                                                                              | Electronically Filed<br>by Superior Court of CA,<br>County of Santa Clara,<br>on 3/22/2021 11:34 PM<br>Reviewed By: F. Miller<br>Case #19CV345846<br>Envelope: 6087286                                                                                                                                                                                                                                                                                                                                      |

| 7                                                                                                                                                          | COUNTY OF SANTA CLARA                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8<br>9                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                             | Case No. 19CV345846                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10                                                                                                                                                         | VENKAT KONDA, Ph.D., an individual, )<br>Plaintiff, )                                                                                                                                                                                                                                                                                       | Unlimited Civil Case                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11                                                                                                                                                         | v. )                                                                                                                                                                                                                                                                                                                                        | PLAINTIFF'S FOURTH AMENDED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12                                                                                                                                                         | )<br>DEJAN MARKOVIC, Ph.D., an individual;                                                                                                                                                                                                                                                                                                  | COMPLAINT FOR:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <ol> <li>13</li> <li>14</li> <li>15</li> <li>16</li> <li>17</li> <li>18</li> <li>19</li> <li>20</li> <li>21</li> <li>22</li> <li>23</li> <li>24</li> </ol> | CHENG C. WANG, Ph.D., an individual;<br>FLEX LOGIX TECHNOLOGIES, INC., a<br>Delaware Corporation; THE REGENTS<br>OF THE UNIVERSITY OF<br>CALIFORNIA; GEOFFREY TATE, an<br>individual; PIERRE LAMOND, an<br>individual; PETER HEBERT, an<br>individual; LESLIE M. LACKMAN, Ph.D.,<br>an individual; and DOES 1-20, inclusive,<br>Defendants. | <ol> <li>Unfair Business Practices</li> <li>Unfair Competition - Passing off</li> <li>Fraud: Intentional<br/>Misrepresentation</li> <li>Fraud: Concealment</li> <li>Conversion</li> <li>Breach of Confidential Relationship</li> <li>Intentional Interference With<br/>Prospective Economic Relations</li> <li>Ongoing Conspiracy</li> <li>Department: 2<br/>Before: Honorable Drew C. Takaichi</li> <li>Date Complaint Filed: April 3, 2019<br/>Trial Date: None</li> <li>DEMAND FOR JURY TRIAL</li> </ol> |

| 25                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 26                                                                                                                                                         | Plaintiff Venkat Konda, Ph.D. (hereinafter referred to as "Dr. Konda" or "Plaintiff")                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 27<br>28                                                                                                                                                   | alleges as follows in this Fourth Amended Complaint:                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                            | Plaintiff's Fourth Amended Complaint<br>-1-                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Page 2 of 483 IPR2020-00261

#### VENKAT KONDA EXHIBIT 2030

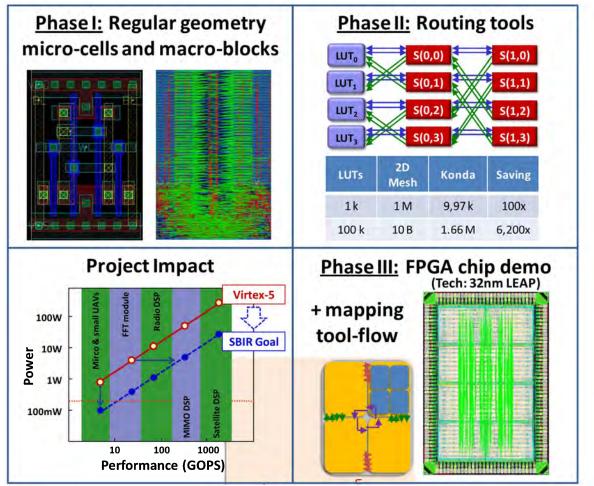

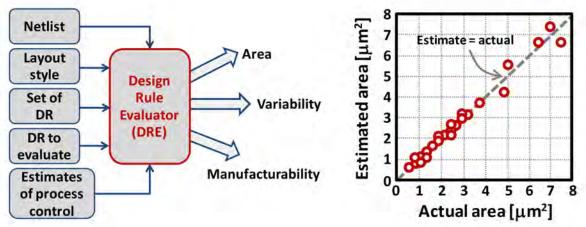

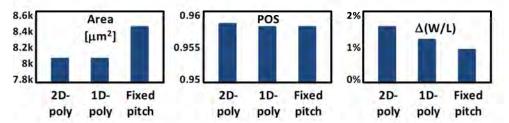

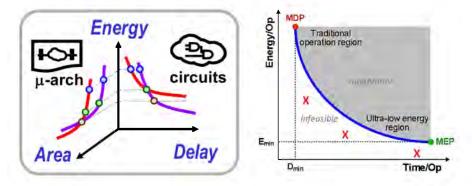

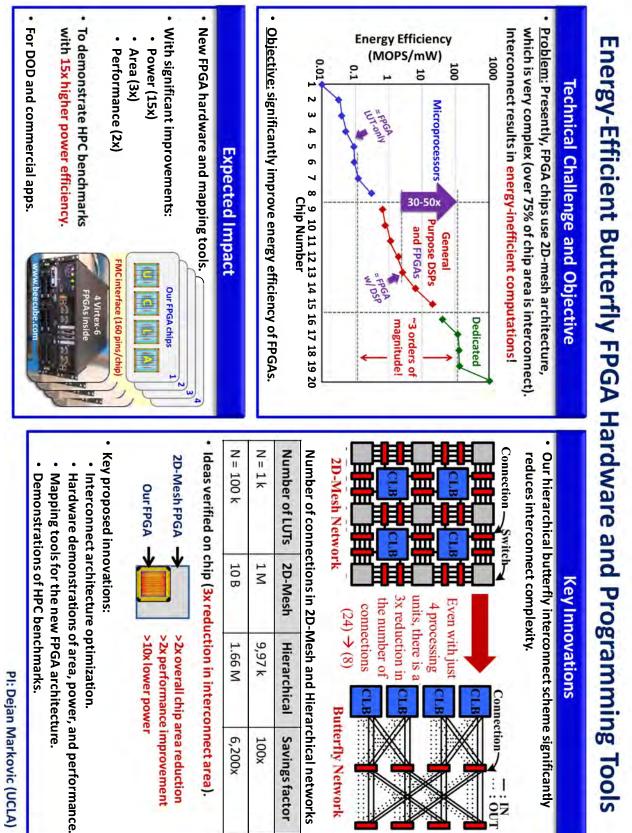

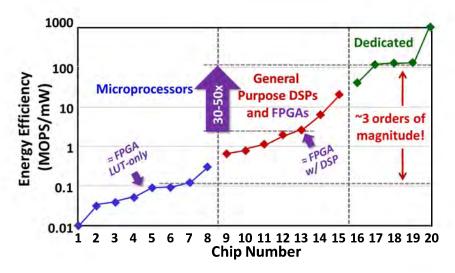

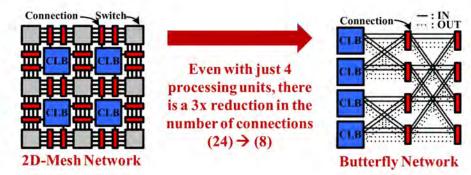

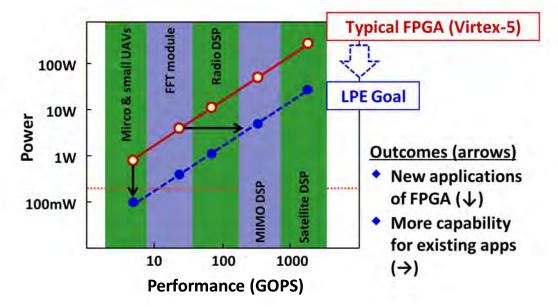

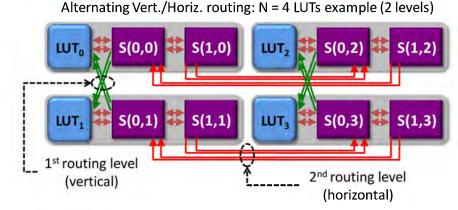

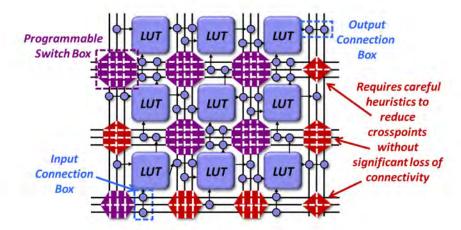

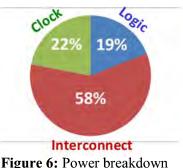

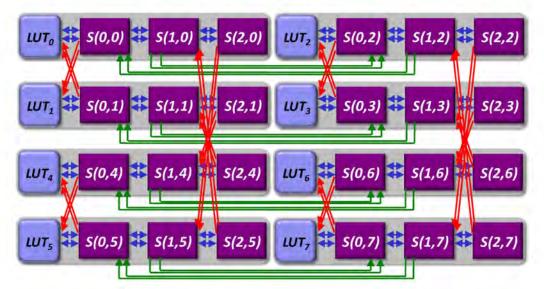

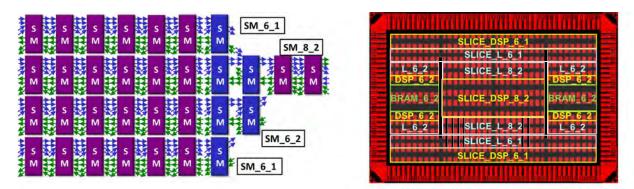

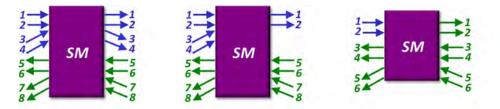

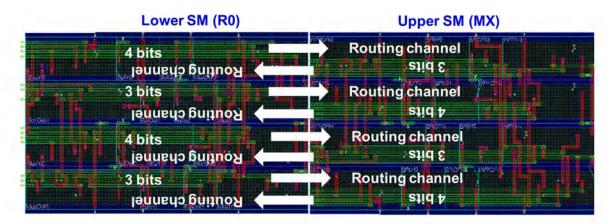

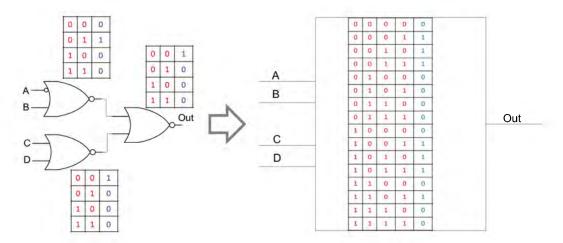

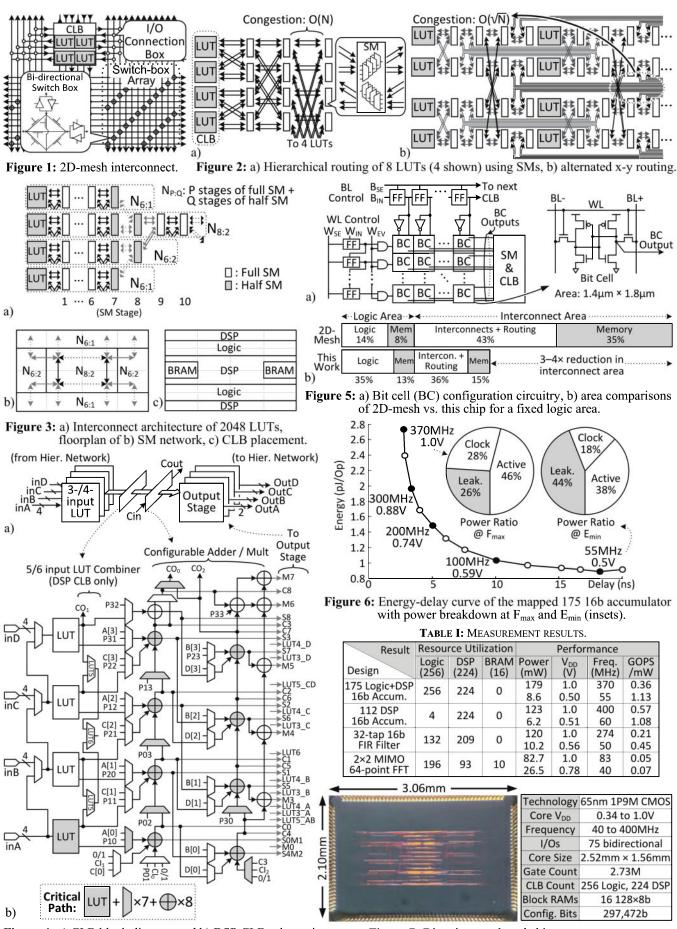

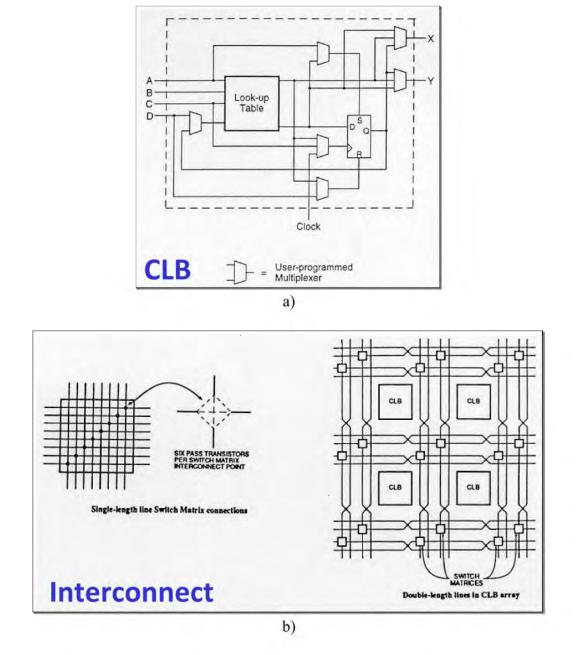

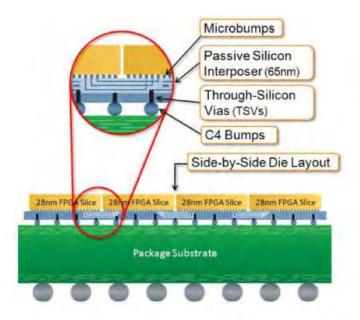

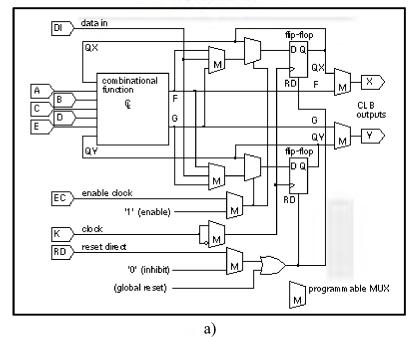

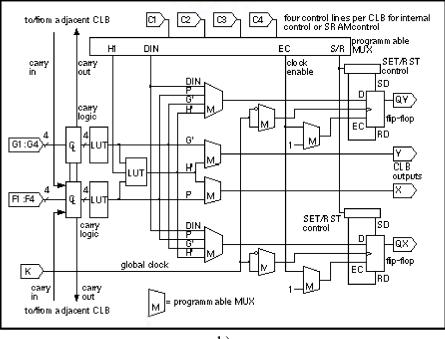

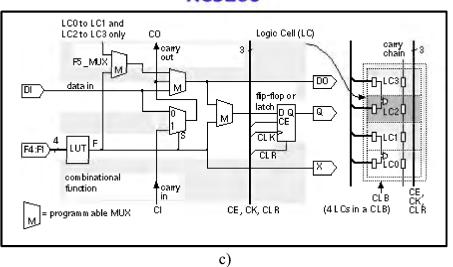

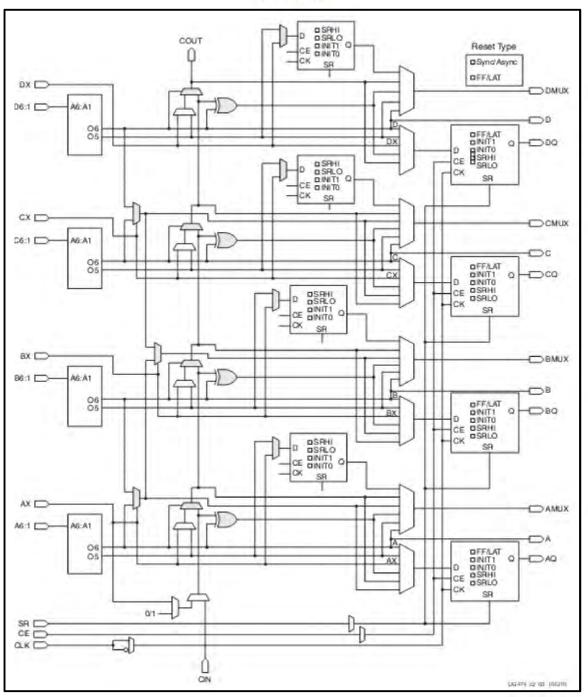

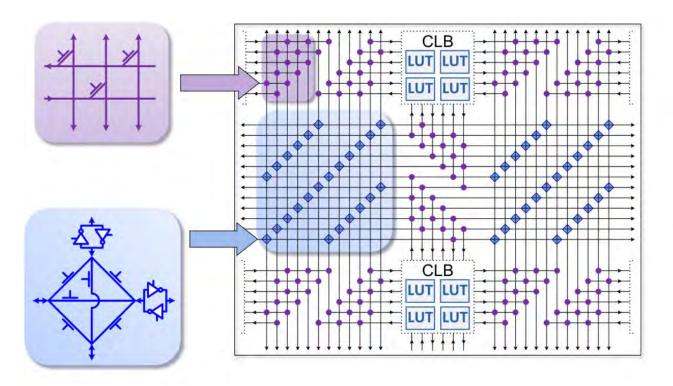

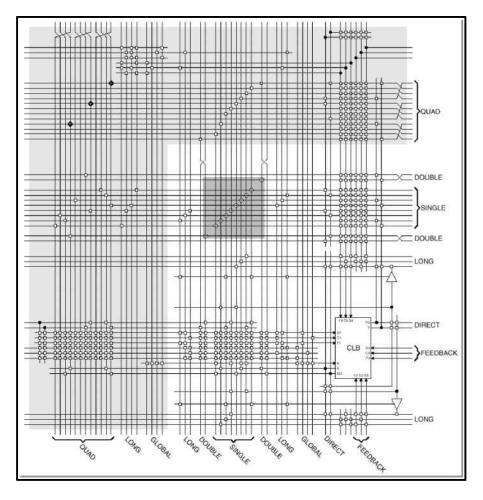

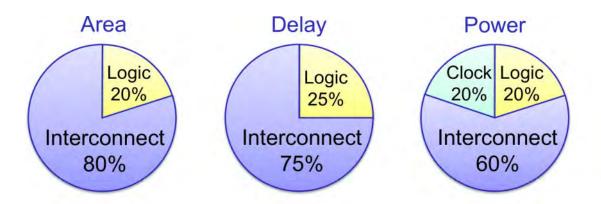

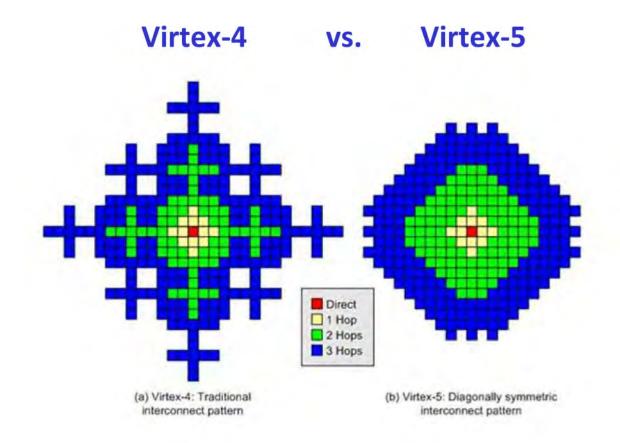

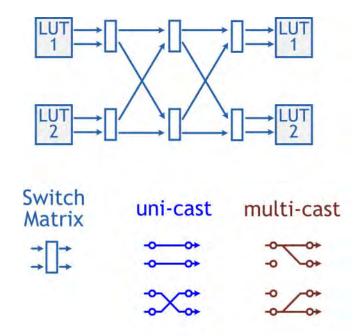

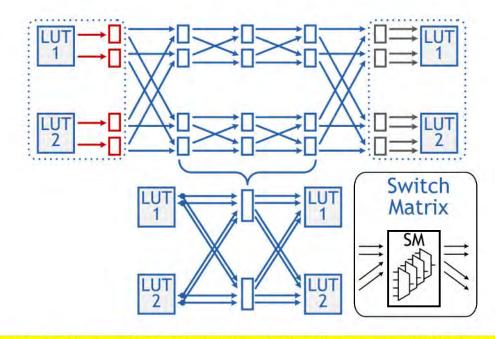

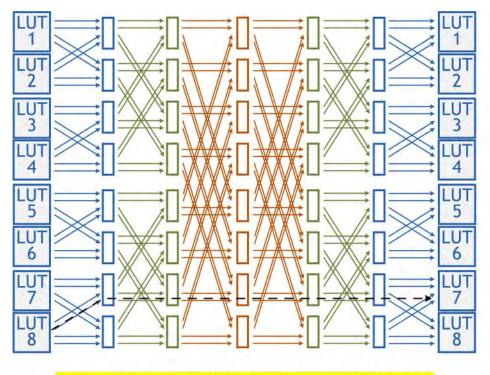

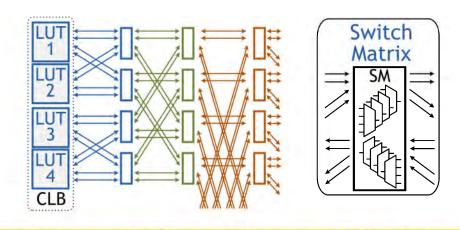

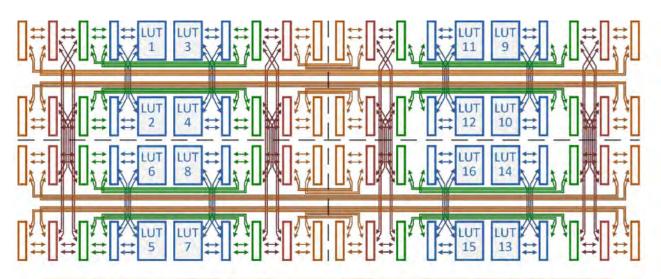

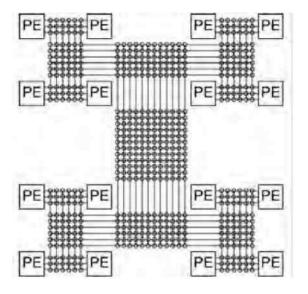

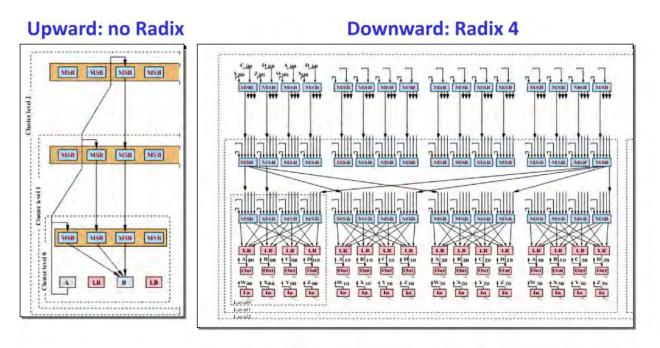

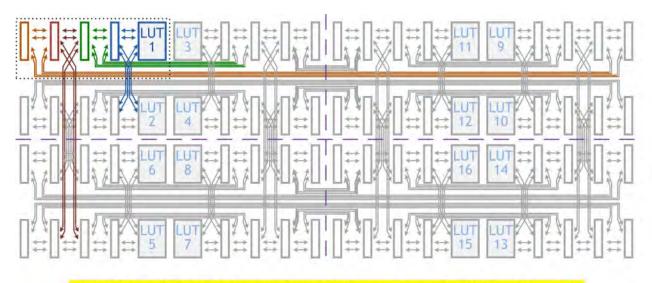

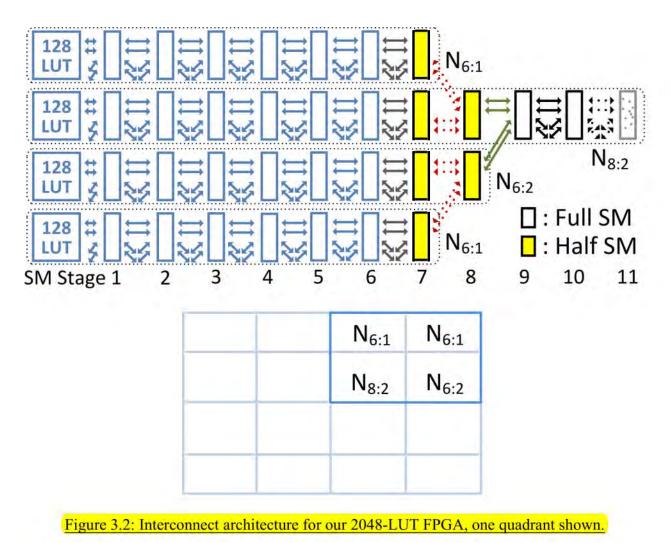

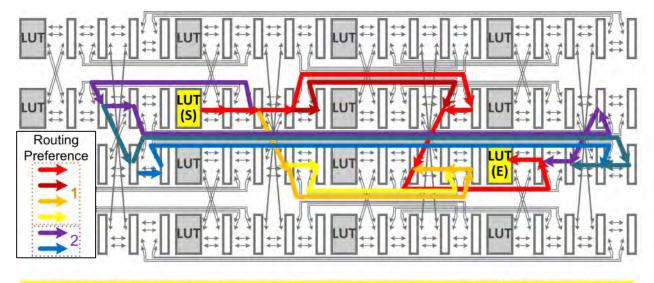

1. This case involves a surreptitious scheme by a professor, Dejan Markovic, Ph.D. (hereinafter referred to as "Defendant Markovic" or "Markovic") who recruited and conspired with one of the graduate students he advised, Cheng C. Wang, Ph.D. (hereinafter referred to as "Defendant Wang" or "Wang"), (hereinafter collectively referred to as "Defendants Markovic and Wang"), at the University of California Los Angeles (hereinafter referred to as "UCLA") which is part of the University of California system, to falsely claim innovation of certain technology by covertly implementing Dr. Konda's innovations, publishing technical papers as if it were their technology, and receiving illicit financial benefits, by passing off Dr. Konda's innovations pilfered from Dr. Konda and his Silicon Valley company, Konda Technologies, Inc. (hereinafter referred to as "Konda Tech") as their own. Through deception and manipulation (i.e., constantly trolling for and obtaining confidential business know-how, and product knowhow for years starting in 2009 - 2014 by blatantly lying and brazenly concealing their misdeeds under the cloak of legitimacy afforded by their association with UCLA, which has knowingly benefitted from illicitly commercializing Dr. Konda's innovations. Defendants Markovic and Wang used Dr. Konda's confidential information disclosed by Dr. Konda to Defendant Markovic in confidence and additional documents including the text and diagrams published in Dr. Konda's published patent applications and patents without authorization or attribution to launch commercial products without the knowledge of Dr. Konda, through a now-dissolved California Corporation Hierlogix, Inc. formed by Defendants Markovic and Wang with funding by UCLA's Institute for Technology Advancement (hereinafter referred to as "UCLA/ITA") and its successor Defendant Flex Logix Technologies, Inc. (hereinafter referred to as "Flex Logix"). 2. Dr. Konda's confidential business information and practices relates to Field Programmable Gate Arrays (hereinafter referred to as "FPGAs"). FPGAs are semiconductor devices that comprise a matrix of configurable logic blocks (CLBs) having one or more Lookup Tables connected via a programmable interconnection network. After being fabricated, FPGAs can be reprogrammed for a desired application or functionality requirements. They are used in many different applications from simple devices such as calculators to sophisticated artificial

#### Plaintiff's Fourth Amended Complaint

intelligence (AI) systems that require high-speed logic operations. FPGAs can perform these

-2-

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

27

#### VENKAT KONDA EXHIBIT 2030

operations faster than a software application running on a computer's central processing unit (CPU).

3. Defendant Markovic was introduced to Dr. Konda by Flavio Bonomi, Ph.D. (hereinafter referred to as "Dr. Bonomi"), who was a Cisco Fellow, Vice President and the Head of the Advanced Architecture and Research Organization at Cisco Systems, Inc. in San Jose, California (hereinafter referred to as "Cisco") in 2009. After funding was orally offered by the Cisco Angel Network (based on Dr. Konda's goodwill in the industry), but later rescinded, Defendant Markovic reached out to Dr. Konda to troll for information beginning in or around March, 2009 and continuing through at least March, 2014.

4. Unbeknownst to Dr. Konda, Defendant Markovic seized the opportunity by conspiring with Defendant Wang, then a Ph.D. candidate studying under Markovic and looking for a Ph.D. Dissertation topic, to immediately begin implementing integrated circuit devices based on the disclosures in the 2008 Konda Publications without authorization from Dr. Konda or Konda Tech.

5. On the pretense of obtaining funding for Konda Tech, Defendant Markovic arranged for a presentation by Dr. Konda to UCLA/ITA including Defendant Leslie M. Lackman, Ph.D. (hereinafter referred to as "Dr. Lackman") on October 12, 2009, obtaining proprietary and confidential materials from Dr. Konda five days prior to the presentation in confidence. However, funding was not forthcoming because, as Defendant Markovic knew beforehand but concealed from Dr. Konda, the prerequisite nexus of a relationship between UCLA and Dr. Konda or Konda Tech did not exist. Nevertheless, within less than two months after the presentation to UCLA/ITA, in December, 2009, unbeknownst to Dr. Konda at that time, Defendant Wang covertly implemented and fabricated FPGA devices comprising CLBs and interconnect using published information through the graduate program at UCLA under the guidance of Defendant Markovic without Plaintiff's authorization.

26 6. Finding a research topic for a doctoral dissertation is the single most challenging task for a Ph.D. student, such as Defendant Wang. A Ph.D. advisor's first task is to let his student know 28 how to carefully conceive a novel topic. It is very common for a Ph.D. student to propose a

#### Page 4 of 483 IPR2020-00261

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

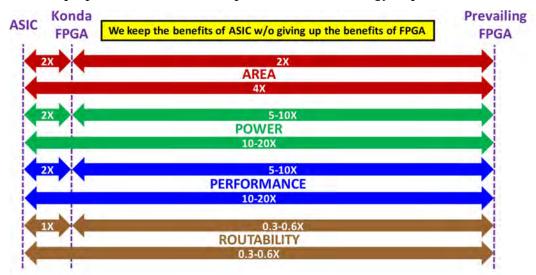

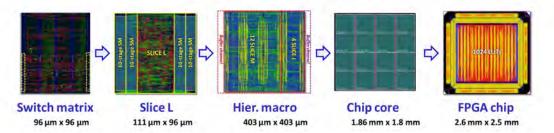

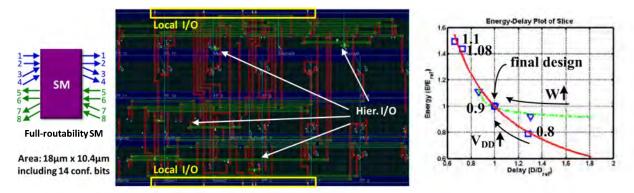

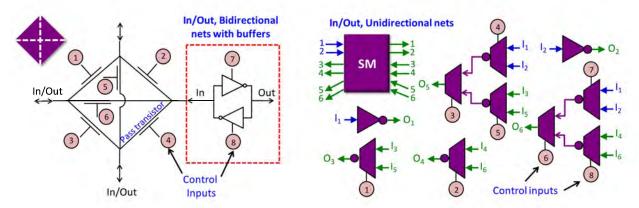

23

24

#### VENKAT KONDA EXHIBIT 2030

concept and later learn that it was already pursued by someone earlier. And, the Ph.D. student

must then find another research topic. However, here, Defendant Markovic in concert with

Defendant Wang knowingly, brazenly chose to implement Dr. Konda's innovations as his topic.

As a result, Defendant Wang's Ph.D. dissertation is essentially a plagiarization of Dr. Konda's

published patent applications and patents and additional confidential information obtained by

Defendant Markovic from Dr. Konda through a confidential relationship.

7. Defendants Markovic and Wang fraudulently based Defendant Wang's Ph.D. dissertation on Dr. Konda's innovations and then proceeded to commercialize their surreptitious work as a business opportunity to make financial gains, refusing to acknowledge the ownership of Dr. Konda, and in the process damaging Konda Tech and Dr. Konda.

8. Without disclosing that Defendants Markovic and Wang had implemented FPGA devices based on Dr. Konda's publications, Markovic eight to nine months after Dr. Konda's confidential presentation to UCLA/ITA including Dr. Lackman, contacted Dr. Konda to solicit him to submit a confidential joint proposal to DARPA. When Dr. Konda learned that covert work had been carried out without his authorization at UCLA as described in the draft confidential DARPA proposal prepared by Defendant Markovic, Dr. Konda told Markovic that Markovic was not authorized to have done that work and to cease any further work at UCLA. However, again on the pretense of obtaining funding for Konda Tech, but in actuality to obtain funding for Markovic's and Wang's development of software tools to program FPGA devices they had covertly implemented, Dr. Konda agreed to the submission of the confidential DARPA proposal with Dr. Konda as the Principal Investigator, because Defendant Markovic would obtain a license to carry on any further work at UCLA; otherwise Markovic promised that he would cease any further implementation of Dr. Konda's innovations at UCLA **as an academic project only**.

9. Approximately five weeks later while the first confidential DARPA proposal was still

pending, Defendant Markovic then solicited Dr. Konda to join in submitting a second

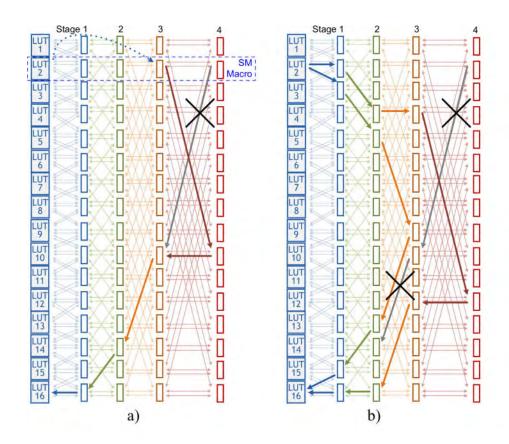

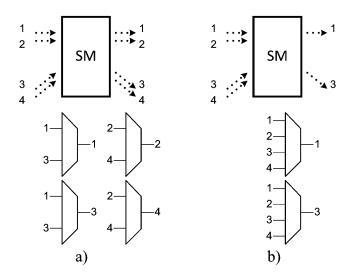

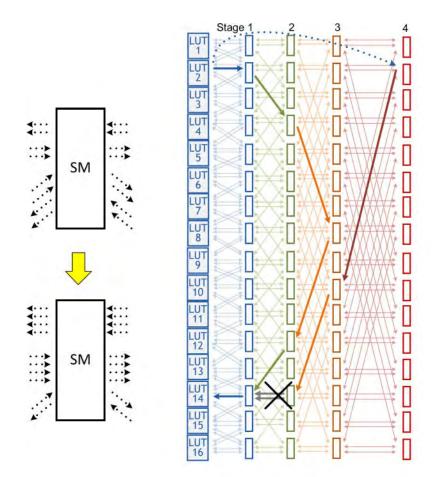

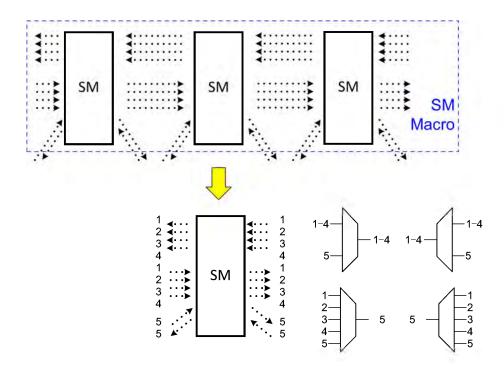

confidential DARPA proposal, but with UCLA as the Principal Investigator. Defendant

Markovic again promised Dr. Konda that if the second confidential DARPA proposal were to be

#### VENKAT KONDA EXHIBIT 2030

granted, he would agree to a license to carry out any further work at UCLA, and otherwise Markovic would cease all further implementation of Dr. Konda's innovations at UCLA **as an academic project only**.

10. Both of the confidential DARPA proposals were rejected in late 2010. At that point, Dr. Konda believed that all of the FPGA device work incorporating Dr. Konda's patent applications and patents and confidential information disclosed by Dr. Konda in connection with the confidential DARPA proposals at UCLA had ceased, **as an academic project only,** based on the prior representations of Defendant Markovic.

11. At or around that time, Dr. Konda contacted Defendant Markovic to inform him in confidence that Konda Tech had licensed a commercial FPGA supplier, QuickLogic Corporation (hereinafter referred to as "QuickLogic"), with whom Dr. Konda had worked between late September, 2010 and mid-January, 2011 to prove the value of Dr. Konda's innovations. Defendant Markovic seized that opportunity to troll for confidential information regarding Dr. Konda's work with QuickLogic. Dr. Konda informed Defendant Markovic in confidence regarding the licensee information and other confidential business information. Defendant Markovic was keenly interested in this information and further inquired what other FPGA suppliers Dr. Konda had contacted. At that time Markovic misrepresented to Dr. Konda that he and his students had stopped implementing Dr. Konda's innovations.

12. Unbeknownst to Dr. Konda, Defendants Markovic and Wang concealed that they had formed Hierlogix Inc. ("Hierlogix") on January 4, 2011 with its principal place of business at Defendant Wang's private residence. Hence, Defendants Markovic and Wang stopped the academic project of implementing the disclosures in the 2008 Konda Publications using the confidential and proprietary implementation details and technical know-how which Dr. Konda had disclosed to Defendant Markovic in confidence to prepare the Two Confidential DARPA Proposals which Dr. Konda had previously disclosed to Defendant Markovic in confidence and brazenly, but covertly started commercializing the results of their purported academic work without a license or authorization from Dr. Konda.

#### Page 6 of 483 IPR2020-00261

#### VENKAT KONDA EXHIBIT 2030

13. Unbeknownst to Dr. Konda, Defendants Markovic and Wang raised funding from UCLA/ITA for Hierlogix. Hierlogix is substantially based on confidential business knowledge and practices based on the confidential and propriety presentation given by Dr. Konda to UCLA/ITA on October 12, 2009 and the confidential DARPA proposals.

14. Unbeknownst to Dr. Konda at that time, Defendants Markovic and Wang also concealed that they had submitted a paper based on Dr. Konda's innovations in January 2011 to the VLSI Symposium without any authorization by or attribution to Dr. Konda. More particularly, the paper was based on Konda Tech's 2D BFT layouts which are the cornerstone for achieving area, power, and performance improvements in FPGAs. The paper was presented by Defendants Markovic and Wang as their own innovation at the VLSI Symposium in June 2011.

15. Also, unbeknownst to Dr. Konda, Defendant Wang was completing his Ph.D. program under the guidance of Defendant Markovic and submitted his dissertation based on the covert implementation of Dr. Konda's innovations without attribution to Dr. Konda, yet Wang was awarded his Ph.D. in June 2013 and recognized for having submitted a distinguished Ph.D. dissertation under the supervision of Defendant Markovic.

16. In April 2013, Defendant Markovic invited Dr. Konda by email to meet him at Stanford University while Markovic represented that he was a "Visiting Professor." When they met, Dr. Konda inquired to confirm whether Defendant Markovic and his students had indeed discontinued implementing Dr. Konda's innovations as part of the academic work at UCLA. Defendant Markovic falsely replied "yes." During the conversation, Defendant Markovic also asked Dr. Konda to inform him in confidence of the names of customers Dr. Konda was currently working with. Thus, Defendant Markovic repeatedly trolled for Dr. Konda's confidential business knowledge and practices which Dr. Konda disclosed in confidence believing that Defendant Markovic was helping to find funding and/or business opportunities for Dr. Konda, while all the time Markovic was misrepresenting and concealing facts as to Defendants Markovic's and Wang's activities.

17. In January, 2014, while Defendant Markovic represented himself to be a "VisitingProfessor" at Stanford University, Dr. Konda and Defendants Markovic and Wang were invited

#### Page 7 of 483 IPR2020-00261

#### VENKAT KONDA EXHIBIT 2030

to a meeting with Dr. Bonomi at his residence. Dr. Bonomi had recently founded a startup company, Nebliolo Technologies, Inc. (hereinafter referred to as "Nebliolo") and was interested 3 in obtaining a supplier of FPGAs based on Dr. Konda's innovations. He invited Defendants 4 Markovic and Wang whom he understood had founded a semiconductor design company that he 5 thought might be able to develop FPGAs based on Dr. Konda's innovations in an embedded FPGA block to supply to Nebliolo. At that meeting, Defendant Markovic mentioned that he was 6 in the process of raising funding for a startup company. When Dr. Konda queried Markovic if the 8 startup was in the area of wireless and digital signal processors (DSPs), Defendant Markovic said 9 "yes," which was an intentional misrepresentation. Defendant Markovic concealed the facts that 10 Hierlogix had been founded by Markovic and Wang three years earlier to commercialize FPGAs and that the technological focus of the startup for which he was seeking funding was to produce embedded FPGA blocks (hereinafter referred to as "eFPGAs") covertly implementing Dr. 12 13 Konda's innovations without having a license.

18. Unbeknownst to Dr. Konda at that time, Defendants Markovic and Wang concealed the fact that they were involved in founding Defendant Flex Logix on February 26, 2014 as the successor to Hierlogix to continue the commercialization of eFPGA blocks implementing and passing off Dr. Konda's innovations as their own innovations.

19. In or about December, 2015 Dr. Konda arranged to meet with Professor Vaughn Betz, Ph.D. (hereinafter referred to as "Dr. Betz") in the Department of Electrical and Computer Engineering at the University of Toronto, Toronto, Canada, to discuss certain results Dr. Konda had achieved with the Versatile Place and Route (hereinafter referred to as "VPR") tool suite developed by Dr. Betz using VPR to implement Dr. Konda's innovations. Dr. Konda met with Dr. Betz in Toronto on or about December 18, 2015. During their meeting, Dr. Betz asked Dr. Konda if he had heard of Flex Logix. Dr. Konda responded that he was not aware of Flex Logix. Nor was Dr. Konda aware of any paper submitted by Defendants Markovic and Wang, Wang's Ph.D. dissertation, Hierlogix, or Flex Logix at the time of his meeting with Dr. Betz on December 18, 2015.

28

1

2

7

11

14

15

16

17

18

19

20

21

22

23

24

25

26

27

Page 8 of 483 IPR2020-00261

#### VENKAT KONDA EXHIBIT 2030

20. After returning to California after his meeting with Dr. Betz on December 18, 2015, Dr. Konda began to investigate to uncover facts regarding the activities of Defendants Markovic and Wang and to investigate Flex Logix. In his pursuit to uncover the facts, Dr. Konda prepared an email which he sent to Flex Logix and UCLA and others on March 27, 2016 requesting additional information from, and action by, those entities regarding possible wrongdoing that he first suspected had occurred on the part of Defendants Markovic and Wang when his investigation yielded information during the weekend of March 26-27, 2016, when he first formed a suspicion that Flex Logix appeared to be implementing eFPGAs based on Dr. Konda's innovations.

21. Due to the intentional misrepresentations and concealment of Defendants Markovic and Wang, Dr. Konda was unsuspecting until that time of the illicit activities of Markovic and Wang until he was able to piece together the facts included in his March 27, 2016 email. Until then, Dr. Konda was in disbelief that Defendant Markovic would have betrayed the confidences and trust of the relationship he believed he had with Dr. Markovic, who cloaked himself with and exploited the pretextual credibility of UCLA, heretofore promoted as a respected educational institution, but now exposed as a commonplace cutthroat competitor whose employees (*i.e.*, Defendant Markovic) deprive unsuspecting inventors of their innovations. In view of the intentional misrepresentations, concealment, and breach of the confidential relationship by Defendant Markovic and his co-conspirator Wang, the facts regarding their wrongdoing were concealed and thus not previously discoverable or known by Dr. Konda. At the time that he prepared his March 27, 2016 email, Dr. Konda realized for the first time that he has been harmed by the concealed, unauthorized commercialization of Dr. Konda's innovations by the Defendants.

22. Beginning March 27, 2016 until July 2018, Chief Executive Officer Geoffrey Tate

(hereinafter referred to as "CEO Tate" or "Mr. Tate") of Flex Logix continuously dragged Dr.

Konda into email interactions and face-to-face meetings under the pretense of continuous

settlement negotiations, seeking more and more information from Dr. Konda.

23. Then, notwithstanding the continuing settlement negotiations, on July 13, 2018, FlexLogix filed a lawsuit in the Federal District Court against Konda Tech and Dr. Konda for unfairbusiness practices.

24. Subsequently, after Dr. Konda and Konda Tech prepared counterclaims to be filed in the Federal District Court action, Flex Logix requested to extend settlement discussions to prevent Konda Tech and Dr. Konda from filing the counterclaims.

25. Later, on December 10, 2018, Flex Logix voluntarily dismissed the lawsuit after the Federal District Court ordered Konda Tech and Dr. Konda to answer the lawsuit filed by Flex Logix by December 10, 2018.

26. On December 17, 2018, Konda Tech filed a lawsuit against Flex Logix in the Federal District Court. After Flex Logix filed a motion to dismiss on January 24, 2019, Konda Tech filed a First Amended Complaint on February 21, 2019, with additional causes of action, including, fraud – intentional misrepresentation, and fraud – concealment. On March 18, 2019 Flex Logix filed another motion to dismiss.

27. On April 3, 2019, Dr. Konda filed his California state complaint and dismissed the District Court action, without prejudice.

28. On June 3, 2019, CEO Tate of Flex Logix threatened an eFPGA vendor at Design Automation Conference 2019 (hereinafter referred to as "DAC 2019"), Las Vegas that the vendor should not do business with Konda Tech or Dr. Konda.

29. As an unnecessary adjunct to the "Motion for Protective Order," counsel for the Defendants Markovic, Wang, and Flex Logix, Mr. Steven M. Perry (hereinafter referred to as "Mr. Perry"), publicly e-filed his declaration together with Dr. Konda's confidential Trade Secret List without notifying or obtaining authorization from Dr. Konda and without filing the Trade Secret List using the "Confidential" selection under the "Security and Optional Services" category on the e-filing system. Thus, Mr. Perry made Dr. Konda's confidential Trade Secret List public in furtherance of the ongoing conspiracy to deprive Dr. Konda of his trade secrets. 30. On January 15, 2020, Defendants Markovic, Wang, Flex Logix, The Regents of the University of California (hereinafter referred to as "UC Regents"), Mr. Tate, Mr. Pierre Lamond

Plaintiff's Fourth Amended Complaint

-9-

1

#### Page 10 of 483 IPR2020-00261

#### VENKAT KONDA EXHIBIT 2030

(hereinafter referred to as "Mr. Lamond"), Mr. Peter Hebert (hereinafter referred to as "Mr.

Hebert), and Leslie M. Lackman Ph.D. (hereinafter referred to as "Dr. Lackman") committed

witness tampering by threatening a Professor at UC Davis (hereinafter referred to as "Prof. at UC Davis") who provided a declaration in support of the confidential trade secret document indeed

containing confidential trade secrets and with particularity, which was provided by Dr. Konda

during the meet and confer process to resolve a discovery dispute.

31. As a result, all Defendants have committed actionable acts and continued their ongoing conspiracy even after Dr. Konda's original complaint and First Amended Complaint were filed.

#### PARTIES

32. Plaintiff Venkat Konda, Ph.D. is and at all times herein mentioned was a resident of Santa Clara County, California. Konda Tech, a California Corporation, has assigned to Dr. Konda as the sole shareholder and owner of Konda Tech the right to bring this action in his individual capacity, as well as all right, title, and interest to recover damages and injunctive relief.

33. Plaintiff is informed and believes, and thereupon alleges, that Defendant Markovic is an individual who is a resident of California and conducts business in Santa Clara County, California.

34. Plaintiff is informed and believes, and thereupon alleges, that Defendant Wang is an individual who is a resident of California and conducts business in Santa Clara County, California.

35. Plaintiff is informed and believes that Defendant The Regents of the University of California have their principal office in California and conduct business in Santa Clara County, California.

36. Plaintiff is informed and believes that Flex Logix has its principal place of business and conducts business in Santa Clara County, California.

37. Plaintiff is informed and believes, and thereupon alleges, that Defendant Mr. Tate is an individual who is a resident of California and conducts business in Santa Clara County, California.

38. Plaintiff is informed and believes, and thereupon alleges, that Defendant Mr. Lamond is an individual who is a resident of California and conducts business in Santa Clara County, California.

39. Plaintiff is informed and believes, and thereupon alleges, that Defendant Mr. Hebert is an individual who is a resident of California and conducts business in Santa Clara County, California.

40. Plaintiff is informed and believes, and thereupon alleges, that Defendant Dr. Lackman is an individual who is a resident of California and conducts business in Santa Clara County, California.

41. Plaintiff is ignorant of the true names and capacities of Defendants sued herein as DOES 1 through 20, inclusive, and therefore sues these Defendants by such fictitious names. Plaintiff prays leave to amend this Fourth Amended Complaint to allege their true names and capacities when the same have been ascertained.

42. Plaintiff is informed and believes, and thereupon alleges, that each of the Defendants sued herein is responsible in some manner for the occurrences herein alleged, and that Plaintiff's damages were proximately caused by such Defendants.

43. Plaintiff is informed and believes, and thereupon alleges, that at all times herein mentioned, each of the Defendants, was and were, at all times, acting as principals or agents, employees, or representatives within the purpose and scope of such agency, employment, or representation as being responsible in some manner for the occurrences herein alleged.

### JURISDICTION AND VENUE

44. This Court has jurisdiction over this Fourth Amended Complaint pursuant to California Code of Civil Procedure Section 395(a) as the transactions, occurrences, and omissions to act giving rise to the liability on the part of the Defendants occurred in Santa Clara County,

California and/or they have directed their unlawful acts complained of herein in Santa Clara County, California.

45. This Court has personal jurisdiction over the Defendants for the additional reason that they have engaged in systematic and continuous contacts with Santa Clara County, California, *inter alia*, regularly conducting and soliciting business in Santa Clara County, and deriving substantial benefit from products and/or services provided to persons in Santa Clara County, California.

#### FACTUAL BACKGROUND

46. Dr. Konda has a Ph.D. in Computer Science and Engineering from the University Of Louisville, Kentucky. Dr. Konda is a pioneer in FPGA routing fabric and interconnection networks technology. Dr. Konda has been granted more than fifteen patents in the technology as of today. Dr. Konda founded Konda Tech, a California corporation, in 2007. Konda Tech's business is based on Dr. Konda's work, and provides chip and system level interconnect technology solutions. Konda Tech has licensed FPGA interconnect architecture intellectual property rights to two FPGA chip vendors, the first of which has made and sold three generations of chips.

47. In 2008, four of Dr. Konda's patent applications were published, namely, WIPO WO

2008109756 A1 published on December 9, 2008 (*See*, Declaration of Vipin Chaudhary, Ph.D.

("Dr. Chaudhary Decl.") Exhibit A attached thereto), WIPO WO 2008147926 A1 published on

December 4, 2008 (*See*, Dr. Chaudhary Decl. Exhibit C attached thereto), WIPO WO

2008147927 A1 published on December 4, 2008 (*See*, Dr. Chaudhary Decl. Exhibit E attached

hereto), and WIPO WO 2008147928 A1 published on December 4, 2008 (*See*, Dr. Chaudhary

Decl. Exhibit G attached thereto) (hereinafter referred to collectively as the "2008 Konda

Publications").

48. In late 2008, on a plane from San Francisco to New Orleans, Dr. Bonomi met Defendant

Markovic of the Department of Electrical Engineering, University of California at Los Angeles,

California. Defendant Markovic told Dr. Bonomi that his research interest and expertise was in

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

21

#### VENKAT KONDA EXHIBIT 2030

digital circuits, Digital Signal Processors ("DSPs"), and wireless systems. Defendant Markovic had not conducted any research in FPGAs prior to the time that he met Dr. Bonomi.

49. In or around January 2009, Dr. Konda was introduced to Defendant Markovic by Dr. Bonomi. Defendant Markovic was and is a UCLA professor teaching technology courses in circuits and embedded systems (which technology overlaps and complements Dr. Konda's innovations in FPGA routing fabric, but does not involve FPGA design or interconnection networks for FPGAs). Defendant Markovic also has interactions with UCLA/ITA. Defendant Markovic was not focused on FPGA work until he learned of Dr. Konda. Konda Tech was one of six startups that received an oral offer for funding from Cisco, led by Dr. Bonomi. Defendant Markovic was aware of the oral offer to fund Konda Tech. (See, Exhibit 10 attached hereto.) The Cisco offer was later rescinded for all six startups so Cisco funding for Konda Tech did not materialize. Defendant Markovic became aware that Cisco's offer to Konda Tech had been rescinded, and that Konda Tech was still looking for funding. At that time Defendant Markovic began to troll Dr. Konda for confidential information. (See, Exhibit 11 attached hereto.)

50. Unbeknownst to Dr. Konda, Defendant Markovic seized the opportunity to involve Defendant Wang, then a Ph.D. candidate working under Markovic and looking for a Ph.D. Dissertation topic, immediately began implementing integrated circuit devices based on the disclosures in the 2008 Konda Publications without authorization from Dr. Konda or Konda Tech.

20 51. Defendant Markovic further seized the opportunity to contact Dr. Konda, misrepresenting that Konda Tech could receive funding through UCLA/ITA. (See, Exhibit 12 attached hereto.) 22 Defendant Markovic concealed the fact from Dr. Konda that Markovic and Wang had already 23 started implementing the disclosures in the 2008 Konda Publications as integrated devices in 24 Markovic's lab at UCLA. Hence, Defendant Markovic, by presenting himself as an advisor to 25 Dr. Konda and purporting to arrange funding for Konda Tech, obtained confidential information from Dr. Konda in confidence and thus entered into a confidential relationship with Dr. Konda. 26 27 Defendant Markovic suggested that Dr. Konda make a presentation to UCLA/ITA. Dr. Konda 28 provided Konda Tech's confidential Business Presentation to Defendant Markovic on October 7,

#### Page 14 of 483 IPR2020-00261

#### VENKAT KONDA EXHIBIT 2030

1 2009 in confidence. (See, Exhibit 13 attached hereto in a Confidential and sealed envelope.) However, after Dr. Konda arrived in Los Angeles on October 12, 2009 to present the confidential Konda Tech business plan to UCLA/ITA, Defendant Markovic for the first time told Dr. Konda that Dr. Konda should not expect UCLA/ITA to fund Konda Tech, because UCLA/ITA does not fund technologies innovated outside UCLA. Dr. Konda did not suspect any wrongdoing by Markovic at that time because Markovic was a professor at UCLA, a world renowned educational institution. Since the confidential Konda Tech Business Presentation was also sent to UCLA/ITA on October 7, 2009, Dr. Konda made a presentation on October 12, 2009 to UCLA/ITA in confidence. Defendant Markovic began the presentation by presenting the confidential Konda Tech Business Presentation to Defendant Dr. Lackman, Deputy Director, Institute for Technology Advancement, UCLA and the other UCLA/ITA Directors in attendance, including Winn Hong. Dr. Lackman stopped Defendant Markovic after one slide and questioned Defendant Markovic "Whose business plan is it?" or words to that effect. The confidential Konda Tech Business Presentation was clearly marked "Konda Tech confidential and proprietary" on all of the slides. Defendant Markovic replied "It is Dr. Konda's." Dr. Lackman then said "Let Dr. Konda present it."

52. Dr. Konda's confidential presentation on October 12, 2009 to UCLA/ITA was fruitless, confirming what Defendant Markovic told Dr. Konda just prior to Dr. Konda presenting to UCLA/ITA. UCLA/ITA rejected funding for Konda Tech on the basis that the complete Konda Tech Business Presentation involved innovations outside UCLA and had nothing to do with UCLA or Defendant Markovic.

53. After presenting to UCLA/ITA on October 12, 2009, Defendant Markovic asked Dr. Konda to give a seminar on the 2008 Konda's publications to Defendant Markovic's students. Dr. Konda obliged Defendant Markovic by presenting an overview to Defendant Markovic's students only with respect to disclosures of the 2008 Konda Publications. Among those in attendance at the October 12, 2009 seminar was Defendant Wang.

54. When Dr. Konda presented to Defendant Markovic's students on October 12, 2009, Dr. Konda clearly told those in attendance that what Dr. Konda was presenting to them was patent

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

#### VENKAT KONDA EXHIBIT 2030

pending technology by a commercial company, Konda Tech, and that the presented material was published as 2008 Konda Publications by then. So, no confidential material was presented by Dr. Konda to the students.

55. Defendant Markovic invited Dr. Konda to UCLA to gain access to the confidential Konda Tech Business Presentation and to give a seminar to Defendant Markovic's students including Defendant Wang. Defendant Markovic beginning at that time and continuing for the ensuing four years, trolled Dr. Konda to learn about all details of Dr. Konda's technology including not only the disclosures in Konda Tech's pending patent applications, but also confidential and proprietary implementation details, technical know-how, and business knowhow, and the then customers and potential customers of Konda Tech and Konda Tech's interaction with them which Plaintiff disclosed to Defendant Markovic in confidence in the belief that Defendant Markovic would maintain the information confidential. As a result, Defendant Markovic insidiously learned about FPGA business models and the know-how of the FPGA industry with respect to interconnect technology and its evolution.

56. In June and July 2010, Defendant Markovic called Dr. Konda, and told him that he wanted to use Konda's confidential information in submitting two different confidential proposals for DARPA funding for Konda Tech. Dr. Konda advised that he did not then have the time to work with Defendant Markovic. However, both times, Defendant Markovic assured Dr. Konda that he would not have to spend any time on the confidential DARPA proposals, and that Markovic would incorporate the Konda's confidential information with the disclosures in the 2008 Konda Publications, as well as confidential and proprietary implementation details and technical know-how which Plaintiff had disclosed to Markovic in confidence, with the understanding that the DARPA proposals were confidential. But, Defendant Markovic deceived Dr. Konda by concealing that Konda Tech confidential proprietary information was revealed to Defendant Wang. Defendant Markovic assured Dr. Konda that he would secure a license from Konda Tech should a DARPA grant be approved for a DARPA project.

Page 16 of 483 IPR2020-00261

#### VENKAT KONDA EXHIBIT 2030

57. Attached hereto as Exhibits 14 and 15 are the June 23, 2010 and August 6, 2010

confidential DARPA funding proposals (hereinafter referred to as "Two Confidential DARPA

Proposals") that followed those conversations between Dr. Konda and Defendant Markovic.

58. The Two Confidential DARPA Proposals make clear that Konda's confidential and

proprietary information was at the heart of what Defendants Markovic and Wang were hoping to accomplish:

Konda Technologies inventions with regular VLSI layouts for Benes/BFT based hierarchical networks are seminal and subsumes all the other known network topologies such as Clos networks, hypercube networks, cube-connected cycles and pyramid networks, which makes these networks implementable in a FPGA devices with regular structures both interconnect distribution-wise and layout-wise which is the key to exploit improved area, power, and performance of FPGA devices. The regularity of Konda hierarchical layout is also the key for its commercializability in System-on-Chip interconnect devices, FPIC devices as well.

Indeed, the Two Confidential DARPA Proposals state that they "will make use of hierarchically routed and proprietary Konda interconnect architecture." The first confidential DARPA Proposal further estimated that Dr. Konda and Konda Tech would complete 620 task hours of the estimated 1020 task hours for key personnel.

59. On October 8, 2010, Dr. Konda disclosed in confidence to Defendant Markovic by email that Konda Tech secured a license from QuickLogic, and Defendant Markovic acknowledged the receipt of that email on October 10, 2010. (*See*, Exhibit 17 attached hereto.) Accordingly, Defendant Markovic learned the commercial viability of Konda's confidential and proprietary information and the disclosures in the 2008 Konda Publications in FPGA products.

60. The Two Confidential DARPA Proposals, replete with references to Konda's confidential information and the disclosures in the 2008 Konda publications, were rejected. However, unbeknownst to Dr. Konda, Defendants Markovic and Wang were not dissuaded from continuing to work on implementation of Konda's confidential and proprietary information and disclosures in the 2008 Konda Publications without authorization from Dr. Konda. In 2010, Defendant Markovic told Dr. Konda over the phone that his students, including Defendant Wang, were implementing disclosures in the 2008 Konda Publications as an "academic project," specifically the 2D layout, on an FPGA chip. When Defendant Markovic told Dr. Konda that his students

#### Page 17 of 483 IPR2020-00261

#### VENKAT KONDA EXHIBIT 2030

had begun implementing Dr. Konda's technology, Dr. Konda told him to stop. Dr. Konda told Defendant Markovic that without a license from Konda Tech, Dr. Konda did not agree that he or UCLA had a right to implement Konda Tech's technology and to stop immediately. Defendant Markovic's answer was, as a university professor, he could "implement any publicly available technology including any technology disclosed in patents or patent applications," or words to that effect. However, Defendant Markovic intentionally misrepresented the fact that the confidential and proprietary information also obtained from Dr. Konda in confidence was being used in connection with the work performed by Defendants Markovic and Wang **solely for academic purposes at UCLA**.

61. By January 2011, Defendant Markovic had trolled Dr. Konda in confidence to obtain the following confidential information including knowledge about the FPGA industry, such information compiled by sweat of the brow and protectable by being maintained confidential by the compiler of the information and not published. including contemporary industry analytics and trend analyses, business practices, disadvantages of the competition, advantages vis-à-vis the competition, customer procurement, relationship building, and management, and business successes ("Konda Business Knowledge and Practices") of Dr. Konda by misrepresenting and concealing Markovic's intent as to use of the information :

a) Dr. Konda did not publish technical papers at technical conferences, and that the reviewers of technical papers are typically not knowledgeable about patents/patent publications such as Dr. Konda's patent publications, including the 2008 Konda Publications;

b) Dr. Konda did not attend generic integrated circuit conferences;

c) Dr. Konda attends only FPGA conferences;

d) Dr. Konda was not building an FPGA product company and had adopted a licensing model including the then Konda's patent publications and trade secret know-how.

62. Unbeknownst to Plaintiff, in defiance of Plaintiff's demand to Defendant Markovic to

stop implementing disclosures in the 2008 Konda Publications, Defendants Markovic and Wang founded Hierlogix on January 4, 2011 to commercialize Konda's technology using the

Plaintiff's Fourth Amended Complaint -17-

1

#### Page 18 of 483 IPR2020-00261

#### VENKAT KONDA EXHIBIT 2030

1 confidential and proprietary implementation details and technical know-how which Dr. Konda 2 had disclosed to Defendant Markovic in confidence to prepare the Two Confidential DARPA 3 Proposals, without authorization from Dr. Konda. (See, Exhibit 36 attached hereto.) Notably, 4 Hierlogix was incorporated within approximately three months after the Two Confidential 5 DARPA Proposals were rejected. Also, unbeknownst to Dr. Konda, on or about March 27, 2016, Hierlogix was funded by UCLA/ITA, of which Defendant Lackman is a board member and participated in the decision to fund Hierlogix. Hierlogix even today on the UCLA/ITA website at https://www.ita.ucla.edu/companies/ describes "Hierlogix provides Energy-Efficient Hierarchical FPGA and Programming Tools. By developing a revolutionary new interconnect architecture, Hierlogix can provide hardware and software tools that are capable of greatly reducing FPGA power and size requirements, while producing higher speeds and performance." The "revolutionary new interconnect architecture" is in fact proprietary to Dr. Konda as disclosed in the 2008 Konda Publications.

63. In or around January 11, 2011, Defendant Markovic called Plaintiff to engage in continued trolling of Konda Business Knowledge and Practices. During that call Dr. Konda again asked if Defendant Markovic and his students had stopped implementing the disclosures in the 2008 Konda Publications. Defendant Markovic intentionally misrepresented to Dr. Konda that he and his students had stopped doing any kind of FPGA work implementing the disclosures in the 2008 Konda Publications. Dr. Konda believed what Defendant Markovic said, because Markovic had never worked in FPGAs, let alone attended any FPGA specific conferences that Dr. Konda attends. For these reasons, Dr. Konda believed Defendant Markovic that he and his students had stopped implementing the disclosures in the 2008 Konda Publications prior to 2011.

64. During the same conversation in or around January 11, 2011, Defendant Markovic again congratulated Dr. Konda for securing a license from QuickLogic and suggested that he would speak to and would introduce Dr. Konda to another potential licensing customer, i.e., ST Microelectronics.

65. On the same day, Defendant Markovic introduced Dr. Konda to ST Microelectronics, and

a conference call was scheduled for January 18, 2011. Defendant Markovic also joined the call

#### Page 19 of 483 IPR2020-00261

#### VENKAT KONDA EXHIBIT 2030

and obtained additional Konda Business Knowledge and Practices discussed with ST Microelectronics. (*See*, Exhibit 18 attached hereto.)

66. Unbeknownst to Dr. Konda at the time of the conference call with ST Microelectronics, Defendant Markovic concealed that he was working on a technical paper to submit to the 2011 Symposium on VLSI Circuits. The call for papers announcement for the 2011 Symposium on VLSI Circuits stated that the last day for a paper submission was 17:00 JST, January 24, 2011. (*See*, Exhibit 19 attached hereto.)

67. As noted earlier, Defendant Markovic learned in confidence from Dr. Konda that Dr. Konda did not publish at technical conferences or in journals. It is common knowledge that reviewers of technical conferences do not search patents or published patent applications for prior publication of subject matter. Defendants Markovic and Wang plagiarized the disclosures in the 2008 Konda Publications and at the 2011 Symposium on VLSI Circuits without authorization from or attribution to Dr. Konda. Accordingly, Defendants Markovic and Wang deceived the technical reviewers of 2011 Symposium on VLSI Circuits and passed off of Dr. Konda's innovations for interconnection networks for FPGAs as their innovations.

68. In June 2011, unbeknownst to Dr. Konda and without his authorization or attribution to Dr. Konda, Defendants Markovic and Wang presented a paper at the 2011 VLSI Circuits Symposium titled "A 1.1 GOPS/mQ FPGA Chip with Hierarchical Interconnect Fabric" (hereinafter referred to as "2011 VLSI Paper"), based on the disclosures in the 2008 Konda Publications as well as the confidential and proprietary implementation details and technical know-how which Dr. Konda had disclosed to Defendant Markovic in confidence to prepare the Two Confidential DARPA Proposals, as well as Konda Business Knowledge and Practices, which Dr. Konda had previously disclosed to Defendant Markovic in confidence. (*See*, Dr. Chaudhary Decl. at ¶¶ 16-19, ¶¶ 20-22 and ¶¶ 29-30.) Attached hereto as Exhibit 20 is the 2011 VLSI Paper in which Defendants Markovic and Wang falsely claim Dr. Konda's innovations as their innovations.

69. Dr. Konda now believes that Defendants Markovic and Wang conspired so that Dr. Markovic provided Defendant Wang with access to the confidential Konda Tech Business

Presentation to UCLA/ITA on October 12, 2009 which was clearly marked "Konda Tech confidential and proprietary." (*See*, Exhibit 13 attached hereto.)

70. Defendant Markovic breached his obligation of confidentiality by trolling for and using Konda Business Knowledge and Practices provided to him in confidence, and used his UCLA professorship as a ploy not only for his illicit implementation of the disclosures in the 2008 Konda Publications using the confidential and proprietary implementation details and technical know-how which Dr. Konda had disclosed to Defendant Markovic in confidence to prepare the Two Confidential DARPA Proposals, without authorization from Dr. Konda, but also by using Konda Business Knowledge and Practices obtained in confidence to eliminate the industry learning and jump start his commercialization of the technology. Defendants Markovic and Wang covertly incorporated Hierlogix on January 4, 2011 to commercialize published as well as confidential and proprietary technical information, as well as Konda Business Knowledge and Practices received in confidence without the authorization of Plaintiff to compete with Dr. Konda. Defendants Markovic and Wang blatantly plagiarized the disclosures in the 2008 Konda Publications and shamelessly published the 2011 VLSI Paper in which they intentionally misrepresented that Dr. Konda's alternate vertical and horizontal layout of Benes/BFT layouts was their innovation in furtherance of their illicit scheme of violating Konda Business Knowledge and Practices received in confidence and obtained by trolling Dr. Konda and unfairly competing against Dr. Konda. (See, Dr. Chaudhary Decl. at ¶¶ 16-19, ¶¶ 20-22 and ¶¶ 29-30.) 71. Unbeknownst to Dr. Konda, UCLA/ITA funded Hierlogix pursuant to a decision made by Dr. Lackman, Deputy Director of UCLA/ITA. Dr. Lackman was fully aware of the confidential and proprietary Konda Technologies Business Presentation and yet funded Hierlogix which is based on the disclosures in the 2008 Konda Publications using the confidential and proprietary implementation details and technical know-how which Dr. Konda had disclosed to Defendant

Markovic in confidence to prepare the Two Confidential DARPA Proposals, as well as Konda Business Knowledge and Practices disclosed in confidence to Markovic.

72. Hierlogix even today on the UCLA/ITA the website at https://www.ita.ucla.edu/companies/ describes: "Hierlogix provides Energy-Efficient

Hierarchical FPGA and Programming Tools. By developing a revolutionary new interconnect architecture, Hierlogix can provide hardware and software tools that are capable of greatly 3 reducing FPGA power and size requirements, while producing higher speeds and performance." 4 The "revolutionary new interconnect architecture" is in fact Dr. Konda's innovation.

73. The WIPO WO 2011047368 A2 publication was published on April 21, 2011 (hereinafter referred to as the "2011 Konda Publication"). (See, Dr. Chaudhary Decl. Exhibit I attached thereto.)

74. Subsequently, Defendant Markovic invited Dr. Konda by email in April 2013 to meet him at Stanford University when he represented to Dr. Konda that he was a "Visiting Professor." (See, Exhibit 21 attached hereto.) Prior to this invitation from Defendant Markovic, Dr. Konda received a LinkedIn connection request from Dr. Lackman. Dr. Konda was surprised to receive LinkedIn connection request from Dr. Lackman. Dr. Konda did not accept the connection request from Dr. Lackman.

75. When Dr. Konda met Markovic at Stanford University, Dr. Konda inquired whether Defendant Markovic and his students had stopped implementing the disclosures in the 2008 Konda Publications using the confidential and proprietary implementation details and technical know-how which Dr. Konda had disclosed to Defendant Markovic in confidence to prepare the Two Confidential DARPA Proposals as part of academic work at UCLA. Defendant Markovic replied "yes," intentionally misrepresenting that he and his students, including Defendant Wang, were no longer working on implementing the disclosures in the 2008 Konda Publications using the confidential and proprietary implementation details and technical know-how which Dr. Konda had disclosed to Defendant Markovic in confidence to prepare the Two Confidential DARPA Proposals. During the conversation, Defendant Markovic trolled Dr. Konda to provide the names of customers he was working with to license to obtain additional Konda Business Knowledge and Practices, and Dr. Konda did so in confidence, because he was not aware that Dr. Markovic had betrayed him. During this meeting, Dr. Konda mentioned to Markovic that he received a LinkedIn connection request from Defendant Lackman, and Dr. Konda expressed

1

2

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

1

2

3

4

5

6

7

8

9

11

14

15

16

17

21

22

24

25

26

27

28

#### VENKAT KONDA EXHIBIT 2030

surprise why Dr. Lackman sent such a request. Defendant Markovic responded he did not know about the LinkedIn connection request from Defendant Lackman.

76. Dr. Konda a few days later tried to accept the LinkedIn connection request from Defendant Lackman, which was not active anymore (i.e., it must have been withdrawn). Dr. Konda did not pay any interest in it at that time. However Dr. Konda now suspects that Markovic talked to Dr. Lackman to withdraw Dr. Lackman's LinkedIn connection request to Dr. Konda. Dr. Konda now further believes that Dr. Lackman is fully aware that Hierlogix is founded based on stealing Konda Tech's FPGA interconnect technology and joined the ongoing conspiracy by Markovic and Wang.

10 77. Between 2011 and 2014, Defendant Markovic and Dr. Konda had occasional phone calls, during which they spoke about the progress of their respective work and Defendant Markovic trolled for further Konda Business Knowledge and Practices, but Defendant Markovic never 12 13 disclosed that the disclosures in the 2008 Konda Publications using the confidential and proprietary implementation details and technical know-how which Dr. Konda had disclosed to Defendant Markovic in confidence to prepare the Two Confidential DARPA Proposals was the subject of Defendant Markovic's work or Defendant Wang's 2013 Ph.D. dissertation titled, "Building Efficient, Reconfigurable Hardware using Hierarchical Interconnects" (hereinafter 18 referred to as "Wang's 2013 Ph.D. Dissertation"). Defendant Markovic also concealed that he 19 and Defendant Wang had founded Hierlogix on January 4, 2011 to illicitly commercialize the 20 disclosures in the 2008 Konda Publications using the confidential and proprietary implementation details and technical know-how which Dr. Konda had disclosed to Defendant Markovic in confidence to prepare the Two Confidential DARPA Proposals, as well as Konda 23 Business Knowledge and Practices disclosed in confidence to Markovic.

78. Dr. Konda was unaware of Wang's 2013 Ph.D. Dissertation until subsequent to December 18, 2015. Attached hereto as Exhibit 22 is a copy of Chapters II and III and portions of Chapters V and VI of Wang's 2013 Ph.D. Dissertation. The disclosure in Chapters II and III and portions of Chapters V and VI of Wang's 2013 Ph.D. dissertation brazenly copies the 2008 Konda Publications and 2011 Konda Publication, especially the figures and layouts, as shown by

the highlighted portions of Exhibit 22. (*See*, Dr. Chaudhary Decl. at ¶¶ 16-19, ¶¶ 23-25 and ¶¶ 29, 31-32.)

79. On January 28, 2014, Dr. Konda met with Defendants Markovic and Wang at the home of Dr. Bonomi. (See, Exhibit 23 attached hereto.) Dr. Bonomi, who was no longer at Cisco, had invited them to his home because he wanted to share that he was in the process of forming his own startup company, and wanted a supplier that would provide FPGAs under license from Dr. Konda and was looking for potential implementation help from Defendants Markovic and Wang. During the course of the discussions, Defendants Markovic and Wang stated that they were looking for funding for a separate startup, but when queried if their startup was in the field of wireless and DSP, Defendant Markovic replied "yes" which was an intentional misrepresentation and a concealment of the fact that Defendants Markovic and Wang had already started up Hierlogix three years earlier with funding by UCLA/ITA to commercialize FPGAs. During the meeting, Dr. Konda was requested to give an update of Dr. Konda's activities and details of Konda Business Knowledge and Practices. Defendant Markovic stated that he was potentially interested in working with Dr. Bonomi and cryptically stated that he "may need to license from Konda Tech". Dr. Konda replied that most of the Konda patents were published or granted and suggested that Defendant Markovic check them on the Web to see if a license was needed and if so, to contact Dr. Konda to obtain a license.

80. While Dr. Bonomi was trying to set up the meeting on January 28, 2014, Dr. Bonomi and Dr. Konda were not aware that Defendants Markovic and Wang had founded the FPGA startup Hierlogix three years earlier. Dr. Konda was not aware of the 2011 VLSI Paper and Wang's 2013 Ph.D. Dissertation was on FPGA interconnects. Defendants Markovic and Wang concealed from Dr. Bonomi and Dr. Konda that Wang's 2013 Ph.D. Dissertation was on FPGA interconnects. Defendants Markovic and Dr. Konda that they had founded an FPGA company called Hierlogix and were in the process of founding its successor Flex Logix. Otherwise, Dr. Bonomi would not have set up the meeting at his home for Dr. Bonomi and Dr. Konda to meet with Defendants Markovic and Wang. (*See*, Dr. Bonomi's declaration attached hereto.)

Page 24 of 483 IPR2020-00261

#### VENKAT KONDA EXHIBIT 2030

81. A couple of weeks after the January 28, 2014 meeting with Dr. Bonomi, unbeknownst to Dr. Konda at the time, Defendants Markovic and Wang submitted a paper titled "A Multi-Granularity FPGA with Hierarchical Interconnects for Efficient and Flexible Mobile Computing" to the 2014 International Solid State Circuits Conference (hereinafter referred to as the "2014 ISSCC Paper"). The 2014 ISSCC Paper is attached hereto as Exhibit 24. The 2014 ISSCC Paper is based on the disclosures in the 2008 Konda Publications and 2011 Konda Publication using the confidential and proprietary implementation details and technical know-how which Dr. Konda had disclosed to Defendant Markovic in confidence to prepare the Two Confidential DARPA Proposals and 2011 Konda Publication. The 2014 ISSCC Paper describes and demonstrates technologies that were innovated by Dr. Konda, and monetized by Konda Tech and reveals the illicit scheme of Defendants Markovic and Wang of violating the disclosures in the 2008 Konda Publications and 2011 Konda Publication using the confidential and proprietary implementation details and technical know-how which Dr. Konda had disclosed to Defendant Markovic in confidence to prepare the Two Confidential DARPA Proposals, as well as Konda Business Knowledge and Practices disclosed in confidence to Markovic, and unfairly competing against Konda Tech, as well as falsely passing off Dr. Konda's innovations as their innovations. (*See*, Dr. Chaudhary Decl. at ¶¶ 16-19, ¶¶ 26-28 and ¶ 29, ¶ 31, ¶ 33.)

82. While submitting papers to integrated circuit conferences, Defendants Markovic and Wang never attended or submitted any paper to the International Symposium on FPGAs held annually in Monterey, California. This is the primary FPGA conference, and one they know Dr. Konda attends every year based on Konda Business Knowledge and Practices obtained in confidence by Defendant Markovic.

83. Until on or around March 2014, Defendant Markovic was pursuing Dr. Bonomi to serve as a reference for him, as he was applying to move as a Professor to Stanford University, Stanford, California (hereinafter referred to as "Stanford") as well as California Institute of Technology, Pasadena, California (hereinafter referred to as "Cal Tech"). (See, Dr. Bonomi's declaration attached hereto.)

#### Page 25 of 483 IPR2020-00261

#### VENKAT KONDA EXHIBIT 2030

84. On February 18, 2014, Dr. Bonomi also set up a meeting for Dr. Konda and Defendants Markovic and Wang to meet with Sundar Iyer, Ph.D. (hereinafter referred to as "Dr. Iyer"), Cofounder and Chief Executive Officer of Memoir Technologies Inc. (hereinafter referred to as "Memoir") a company in the field of computer memory technologies. The objective of this meeting was for Dr. Iyer to share his experiences of building intellectual property companies with Dr. Konda, Dr. Markovic, and Dr. Wang. Notably, Defendants Markovic and Wang did not use either Hierlogix's or Flex Logix's email IDs in communicating to arrange the meeting with Dr. Iyer to conceal their involvement with those companies from Dr. Konda. (*See*, Exhibit 25 attached hereto.)

85. Dr. Konda and Defendants Markovic and Wang met Dr. Iyer at Memoir's offices on

March 5, 2014. At that meeting, Defendants Markovic and Wang again concealed from Dr.

Konda the fact that both Hierlogix and their new startup Flex Logix were building FPGA

products based on the disclosures in the 2008 Konda Publications and 2011 Konda Publication

using the confidential and proprietary implementation details and technical know-how which Dr.

Konda had disclosed to Defendant Markovic in confidence to prepare the Two Confidential

DARPA Proposals relating to the revolutionary interconnect architecture innovated by Dr.

Konda. (*See*, Exhibit 25 attached hereto.)

86. While Dr. Bonomi was trying to set up the meeting with Dr. Iyer on March 5, 2014, Dr. Bonomi and Dr. Konda were not aware that Defendants Markovic and Wang had built the FPGA startup Hierlogix or recently founded Flex Logix. Dr. Konda was not aware of the 2011 VLSI Paper and 2014 ISSCC Paper, or that the topic of Wang's 2013 Ph.D. Dissertation was FPGA interconnects based on the disclosures in the 2008 Konda Publications and 2011 Konda Publication using the confidential and proprietary implementation details and technical knowhow which Dr. Konda had disclosed to Defendant Markovic in confidence to prepare the Two Confidential DARPA Proposals. Defendants Markovic and Wang concealed from Dr. Bonomi and Dr. Konda that Wang's 2013 Ph.D. Dissertation was on FPGA interconnects. Defendants Markovic and Wang did not tell Dr. Bonomi and Dr. Konda about the 2011 VLSI Paper or the 2014 ISSCC Paper. Defendants Markovic and Wang did not tell Dr. Bonomi and Dr. Konda that

#### Page 26 of 483 IPR2020-00261

#### VENKAT KONDA EXHIBIT 2030

they had built an FPGA company called Hierlogix. While Dr. Bonomi was trying to set up the

meeting with Dr. Iyer on March 5, 2014, Defendants Markovic and Wang did not tell Dr.

Bonomi and Dr. Konda that they founded Flex Logix on February 26, 2014. Otherwise, Dr.

Bonomi would not have set up the meeting with Dr. Iyer at Dr. Iyer's office for Dr. Konda and

Defendants Markovic and Wang to meet with Dr. Iyer on March 5, 2014. And, Dr. Konda would

not have attended the meeting on March 5, 2014 to avoid being trolled by Defendants Markovic

and Wang for more Konda Business Knowledge and Practices.

87. Unbeknownst to Dr. Konda at the time of the meeting at Dr. Iyer's office, Defendants Markovic and Wang had already founded Flex Logix on February 26, 2014 as the successor to Hierlogix to illicitly compete against Konda Tech based on implementing the disclosures in the 2008 Konda Publications and 2011 Konda Publication using the confidential and proprietary implementation details and technical know-how which Dr. Konda had disclosed to Defendant Markovic in confidence to prepare the Two Confidential DARPA Proposals without authorization from Dr. Konda. (*See*, Exhibit 49 attached hereto.)

88. Dr. Konda's expertise is not circuit design, so Dr. Konda never attended integrated circuits conferences nor followed what is published at such conferences.

89. The 2011 VLSI Paper was published after Hierlogix was founded and the 2014 ISSCC

Paper was published after Flex Logix was founded. Notably, the 2011 VLSI Paper and the 2014

ISSCC Paper list Defendants Markovic and Wang as affiliated with UCLA only to conceal from

Dr. Konda that Defendants Markovic and Wang were associated in any way with those

companies.

90. Dr. Konda was not aware of the 2011 VLSI Paper, Wang's 2013 Ph.D. Dissertation, and the 2014 ISSCC Paper, until subsequent to December 18, 2015 when Dr. Konda was told about Flex Logix by Dr. Betz during the visit to Dr. Betz's office. At that time, Dr. Konda first learned about Flex Logix and started investigating Flex Logix.

91. The conduct of Defendants Markovic and Wang makes clear that they employed subterfuge and deceit to gain access to confidential and proprietary implementation details and technical know-how which Dr. Konda had disclosed to Defendant Markovic in confidence to

#### Page 27 of 483 IPR2020-00261

#### VENKAT KONDA EXHIBIT 2030

prepare the Two Confidential DARPA Proposals, develop their fraudulent credibility in the FPGA technology through papers submitted to integrated circuits conferences based on the disclosures in the 2008 Konda Publications and 2011 Konda Publication using the confidential and proprietary implementation details and technical know-how which Dr. Konda had disclosed to Defendant Markovic in confidence to prepare the Two Confidential DARPA Proposals, as well as Konda Business Knowledge and Practices disclosed in confidence to Markovic, to launch their own startup company Hierlogix with funding by UCLA/ITA and its successor Flex Logix in competition with Konda Tech, covertly usurping Konda Business Knowledge and Practices received in confidence from Dr. Konda as the cornerstone for establishing and operating those companies.

92. It must be noted that the 2008 Konda Publications and 2011 Konda Publication are the key reasons Markovic and Wang were able to implement FPGAs and to found Hierlogix and Flex Logix, combined with the Konda Business Knowledge and Practices Markovic and Wang learned in confidence from Dr. Konda that 1) Dr. Konda was not publishing technical papers in refereed conferences, 2) Konda Tech has a licensing business model, and 3) Dr. Konda does not attend circuits conferences.

93. Unbeknownst to Dr. Konda, Flex Logix was in stealth mode from its inception in February 2014 until on or about March 2015.

94. In the first part of December, 2015, Dr. Konda contacted Dr. Betz, and they agreed to meet on December 18, 2015 in Toronto, Canada. They met on December 18, 2015 from approximately 1:00 – 2:30 PM at Dr. Betz's office at the University of Toronto to discuss certain results Dr. Konda had achieved using the Versatile Place and Route tool suite (hereinafter referred to as "VPR") as part of Konda Business Knowledge and Practices. VPR was built by Dr. Betz and his students working for several years at the Department of Electrical and Computer Engineering at the University of Toronto, Toronto, Canada, and Dr. Betz was interested in discussing Dr. Konda's results.

95. Dr. Betz was aware of Dr. Konda's patents and published patent applications and Konda Business Knowledge and Practices received in confidence since last quarter of 2012 as both of them interacted regarding Konda Business Knowledge and Practices.

96. During the meeting, Dr. Betz asked Dr. Konda "Have you given a license to Flex Logix?"

or words to that effect. Dr. Konda was shocked when Dr. Betz asked him that question. Then,

Dr. Konda replied that he hadn't heard about Flex Logix and inquired of Dr. Betz about Flex

Logix. Dr. Betz told Dr. Konda that Flex Logix is an FPGA startup co-founded by Defendant

Markovic and his student Defendant Wang.

97. At the same meeting, Dr. Betz told Dr. Konda that he had immediately realized Flex Logix's purported interconnect technology is a knock-off of the disclosures in the 2008 Konda Publications and 2011 Konda Publication.

98. After his meeting with Dr. Betz on December 18, 2015, Dr. Konda immediately started investigating what Dr. Betz said to him by first visiting the website for Flex Logix (www.flex-logix.com). Dr. Konda discovered that Flex Logix's products purport to be eFPGA blocks and that Defendants Markovic and Wang had intentionally misrepresented to Dr. Konda at the January 28, 2014 meeting with Dr. Bonomi that they were involved with a startup company in the digital signal processor (DSP) field for communications applications. As Dr. Konda continued his investigation he thereafter discovered Wang's 2013 Ph.D. Dissertation and after analyzing the dissertation determined that it plagiarized the disclosure in the 2008 Konda Publications and 2011 Konda Publication. (*See*, Dr. Chaudhary Decl. at ¶¶ 16-19, ¶¶ 23-25 and ¶¶ 29, 31-32.) Dr. Konda later discovered for the first time the 2014 ISSCC Paper and determined that it described an implementation of the plagiarized the disclosures in the 2008 Konda Publications and 2011 Konda Publication. (*See*, Dr. Chaudhary Decl. at ¶¶ 16-19, ¶¶ 26-28 and ¶ 29, ¶ 31, ¶ 33.)

99. Notably, Flex Logix touts the 2014 ISSCC paper on its website as describing Flex

Logix's "new, patented interconnect, XFLX<sup>TM</sup>" misleading the public that Dr. Konda's

innovations are instead the innovations of Flex Logix. *See*, <u>http://www.flex-logix.com/fpga-</u>

<u>tutorial/</u>.

#### Page 29 of 483 IPR2020-00261

#### VENKAT KONDA EXHIBIT 2030