#### US006119250A

### **United States Patent** [19]

### Nishimura et al.

[11] Patent Number:

6,119,250

[45] **Date of Patent:**

Sep. 12, 2000

$\begin{array}{cccc} 07038417 & 2/1995 & Japan \ . \\ 7\text{-}38417 & 2/1995 & Japan \ . \end{array}$

### 11/ 2/1995 Japan.

Y. Matsuya, et al., "1V, 10MHz High–Speed Digital Circuit Technology with Multi–Threshold CMOS", Technical Report of IEICE, ICD93–107, pp. 23–27, 1993–10.

OTHER PUBLICATIONS

C.Q. Tong, et al., "IDDQ Testing in Low Power Supply CMOS Circuits", Proc. of IEEE 1996 Custom Integrated Circuits Conference, pp. 467–470, 1996.

T. Kuroda, "A High–Speed Low Power 0.3  $\mu$ m CMOS Gate Array with Variable Threshold Voltage (VT) Scheme", Proc. of IEEE 1996 Custom Integrated Circuits Conference, pp. 53–56, 1996.

T. Kuroda, et al., A 0.9V 150 HMz 10mW 4mm<sup>2</sup> 2–D discrete Cosine Transform Core Processor with Variable–Threshold–voltage Scheme, Proc. of 1996 IEEE International Sold–State Circuits Conference, pp. 166–167, 1996.

Primary Examiner—Hoa T. Nguyen Attorney, Agent, or Firm—McDermott, Will & Emery

#### [57] ABSTRACT

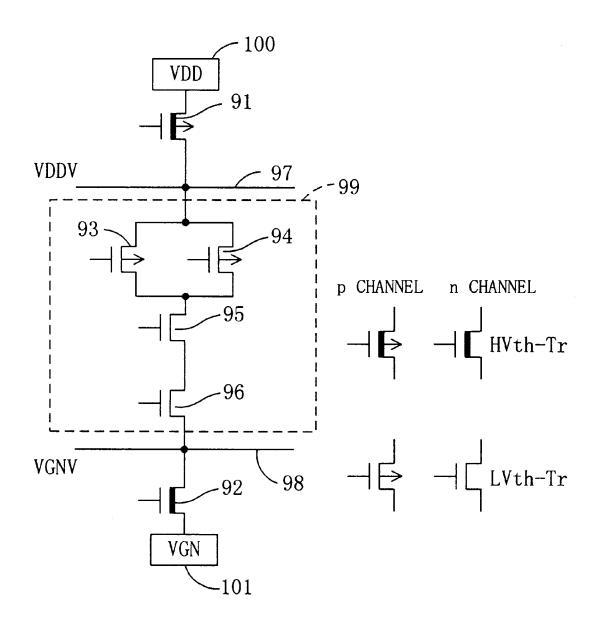

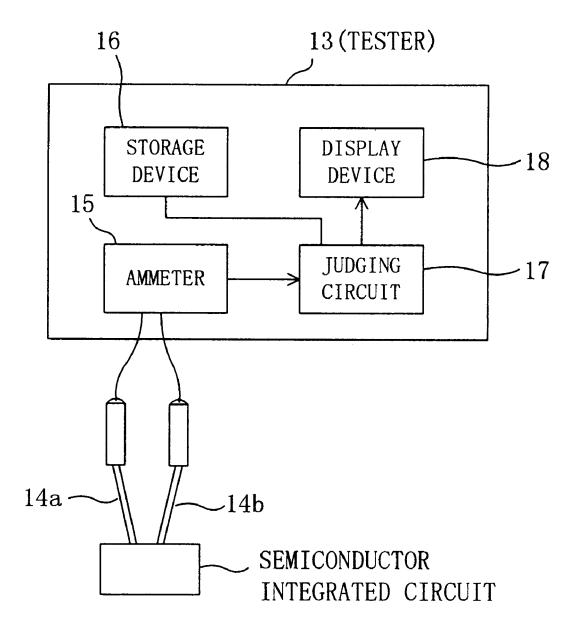

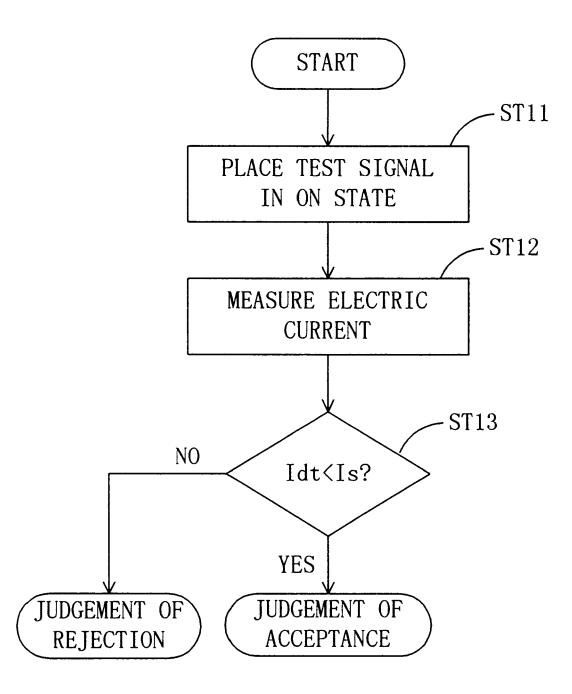

A test-target circuit is constructed of circuit blocks each comprising low-Vth MOS transistors including address buffers and a timing generator. A test enable signal for indication of a test, an operation selection signal for indication of an operation, and a block selection signal used to select a desired circuit block are provided. A high-Vth NMOS and a high-Vth PMOS transistor are provided in order to provide to a test circuit one of detected currents of the circuit blocks that was selected by placing a block selection signal and the test enable signal in the state of HIGH.

### 11 Claims, 19 Drawing Sheets

|                                           |                     |   |                 |                                                                                             |            |                        |                | ,          | 6                |      |

|-------------------------------------------|---------------------|---|-----------------|---------------------------------------------------------------------------------------------|------------|------------------------|----------------|------------|------------------|------|

| D.1                                       |                     | ١ | VREF            | , I11                                                                                       | TE         | Ĵ                      | VCIR           | S11        | CP               | ∘ BS |

| D11 ← : : : : : : : : : : : : : : : : : : |                     |   |                 | :<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>:<br>: |            | (AB)<br>:<br>:<br>(M1) | <br>           | :<br>S31   |                  |      |

|                                           | REGISTER<br>CIRCUIT | · | TEST<br>CIRCUIT | :                                                                                           | :          | TEST-TARGET<br>CIRCUIT |                | :          | SCAN<br>REGISTER |      |

| D3n ←                                     |                     |   |                 | < 13n<br>⋮                                                                                  |            | (Mn)                   | <br> <br> <br> | < S3n<br>: |                  |      |

| D61 ←                                     |                     | T |                 | :<br><u>I61</u>                                                                             | :<br> <br> | :<br>(TG)              | :<br>          | S61        |                  |      |

|                                           | 250                 |   | 240             | 22                                                                                          | 0B         | 230                    | GND            | 220A       | 210              |      |

### [54] SEMICONDUCTOR INTEGRATED CIRCUIT [75] Inventors: Kazuko Nishimura, Kyoto; Hironori Akamatsu, Osaka; Akira Matsuzawa, Kyoto; Mitsuyasu Ohta, Osaka, all of [73] Assignee: Matsushita Electric Industrial Co., Ltd., Osaka, Japan [21] Appl. No.: 09/083,389 [22] Filed: May 22, 1998 Related U.S. Application Data Continuation of application No. 08/888,920, Jul. 7, 1997, [63] Pat. No. 5,978,948. [30] Foreign Application Priority Data Japan ...... 8-175304 May 23, 1997 [JP] Japan ...... 9-133369 Int. Cl.<sup>7</sup> ...... G11C 29/00 [52] **Field of Search** ...... 714/718, 724, 714/736, 733, 735; 365/201 [56] **References Cited** U.S. PATENT DOCUMENTS

### FOREIGN PATENT DOCUMENTS

57-087149

5/1982

Japan .

62-154638

7/1987

Japan .

04055778

2/1992

Japan .

06160487

6/1994

Japan .

06334010

12/1994

Japan .

6,119,250

Fig. 1 PRIOR ART

LOGIC CIRCUIT  $\infty$ 7a (LOGIC BLOCK)  $\mathcal{O}$ Fig. VGNV 6a NORMAL CONTROL SIGNAL TEST CONTROL UNIT NORMAL CONTROL UNIT Sdt.

6,119,250

Fig. 3

Fig. 4

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.