#### Affidavit from Pedro Arroyo

I, Pedro Arroyo, being of full age and duly sworn, deposes and says as follows:

- I am an employee of the Cornell University Library, and specifically the Acquisitions and E-Resources Licensing Services unit, located at Cornell University, Ithaca, New York 14853. I am familiar with the policies and procedures of the Library as they relate to the receipt, cataloging, and tracking of books and I have personal knowledge of the facts set forth below. I am familiar with these procedures because I have been employed by the Library since 1996, where I began in Technical Services as a Searching/Fastcatting assistant, then a unit supervisor in 2002. I have held my current position as Acquisitions Coordinator since 2010.

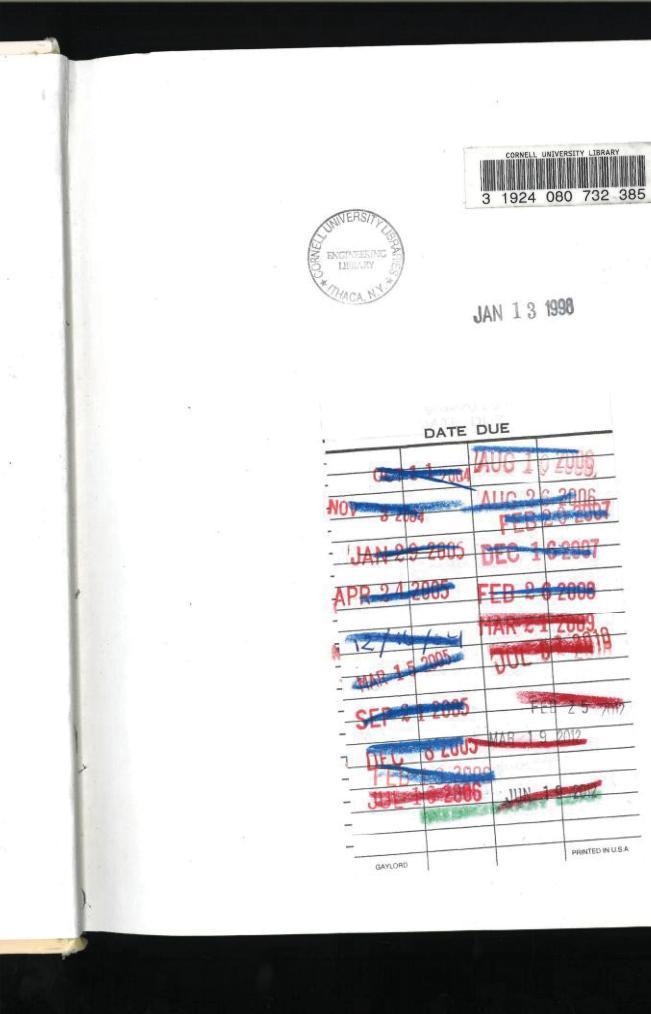

- 2. The Cornell Library holds an original copy of a publication, Analog integrated circuit design by David Johns and Ken Martin (New York : John Wiley & Sons, 1997). A copy of the cover page, the preliminary pages, the table of contents, and pages 19-26 of this publications are included as Attachment A. WilmerHale requested information about Analog integrated circuit design / Johns and Martin (1997) specifically when this item was first made publicly available by the Cornell Library. As best I can determine from my review of the Library's records and my knowledge of the Library's standard procedures, Analog integrated circuit design / Johns and Martin (1997) was cataloged and publicly available at the Engineering Library, in its public stacks, shelved by its Library of Congress classification system number, as of January 13, 1998.

- 3. My opinion that Analog integrated circuit design / Johns and Martin (1997) was cataloged and publicly available at the Cornell University Library as of January 13, 1998 is based on my review of the MARC records for this item, the date stamp on a preliminary page inside the item, and my knowledge of the Library's standard procedures at the time relevant to date stamping, cataloging, and shelving items. I have not seen any indication that Analog integrated circuit design / Johns and Martin (1997) would have been an exception to the Library's standard practice of making the volume available to the public within a few days of the date stamp. The Library maintains a searchable and publicly accessible catalog of its publications. Therefore, as of January 13, 1998, any member of the public could have located Analog integrated circuit design by searching our catalog by subject matter, author, or title.

- 4. I declare that all statements made herein of my own knowledge are to the best of my knowledge true and that all statements made on information and belief are believed to be true; and further that these statements were made with the knowledge that willful

**INTEL 1234**

false statements and the like so made are punishable by fine or imprisonment, or both under Section 1001 of Title 18 of the United States Code.

5. I declare under the penalty of perjury that the foregoing is true and correct.

Executed on October 22. 2018 at Cornell University, Ithaca, New York 14853.

en C. Aucho (Signature)

Pedro C. Arroyo (name printed)

Sworn to before me this

22<sup>nd</sup> day of October, 2018,

MONR 'enon

Notary<sup>®</sup>Public

LYNDSI R. PRIGNON Notary Public, State of New York No. 01PR6069103 Qualified in Tompkins County Commission Expires January 22, 20 <u>2.2</u> Attachment A

# ANALOG INTEGRATED CIRCUIT DESIGN

DAVID A. JOHNS KEN MARTIN

## ANALOG INTEGRATED CIRCUIT DESIGN

David Johns Ken Martin University of Toronto

John Wiley & Sons, Inc. New York • Chichester • Brisbane Toronto • Singapore • Weinheim Acquisitions Editor Marketing Manager Production Manager Senior Production Editor Designer Manufacturing Manager Illustration Editor Charity Robey Jay Kirsch Lucille Buonocore Tracey Kuehn Kevin Murphy Mark Cirillo Sigmund Malinowski

This book was set in Times Roman by Publication Services and printed and bound by R.R. Donnelley/Crawfordsville. The cover was printed by Lehigh Press.

Recognizing the importance of preserving what has been written, it is a policy of John Wiley & Sons, Inc., to have books of enduring value published in the United States printed on acid-free paper, and we exert our best efforts to that end.

The paper in this book was manufactured by a mill whose forest management programs include sustained yield harvesting of its timberlands. Sustained yield harvesting principles ensure that the number of trees cut each year does not exceed the amount of new growth.

Copyright © 1997, by John Wiley & Sons, Inc.

All rights reserved. Published simultaneously in Canada.

Reproduction or translation of any part of this work beyond that permitted by Sections 107 and 108 of the 1976 United States Copyright Act without the permission of the copyright owner is unlawful. Requests for permission or further information should be addressed to the Permissions Department, John Wiley & Sons, Inc.

## Library of Congress Cataloging-in-Publication Data:

Johns, David, 1958– Analog integrated circuit design / David Johns, Ken Martin. p. cm. Includes bibliographical references. ISBN 0-471-14448-7 (cloth : alk. paper) 1. Linear integrated circuits—Design and construction. I. Martin, Kenneth W. (Kenneth W.) 1952– . II. Title. TK7874.J65 1996 621.3815—dc20 96-34365

ISBN 0-471-14448-7

Printed in the United States of America

10 9 8 7 6 5 4 3 2

## Contents

#### INTEGRATED-CIRCUIT DEVICES AND MODELLING **CHAPTER 1**

Semiconductors and pn Junctions 1 1.1

16

- 1.2 MOS Transistors

- 1.3 Advanced MOS Modelling 39

- 42 1.4 Bipolar-Junction Transistors

- Device Model Summary 56 1.5

- SPICE-Modelling Parameters 61 1.6 65

- Appendix 1.7

- 78 References 1.8

- 78 1.9 Problems

#### PROCESSING AND LAYOUT **CHAPTER 2**

- 2.1 CMOS Processing 82

- 2.2 Bipolar Processing 95

- 2.3 CMOS Layout and Design Rules 96

- Analog Layout Considerations 105 2.4

- 118 2.5 Latch-Up

- 121 References 2.6

- Problems 121 2.7

#### **CHAPTER 3**

## BASIC CURRENT MIRRORS AND SINGLE-STAGE AMPLIFIERS

- Simple CMOS Current Mirror 125 3.1

- 128 Common-Source Amplifier 3.2

- Source-Follower or Common-Drain Amplifier 129 3.3

- 132 Common-Gate Amplifier 3.4

- Source-Degenerated Current Mirrors 135 3.5

- High-Output-Impedance Current Mirrors 137 3.6

- 140 Cascode Gain Stage 3.7

- MOS Differential Pair and Gain Stage 142 3.8

- 146 Bipolar Current Mirrors 3.9

- Bipolar Gain Stages 149 3.10

82

1

Contents xi

181

221

256

Frequency Response 154 3.11 SPICE Simulation Examples 169 3.12 References 176 3.13 176 3.14 Problems NOISE ANALYSIS AND MODELLING **CHAPTER 4** Time-Domain Analysis 181 4.1186 4.2 Frequency-Domain Analysis Noise Models for Circuit Elements 196 4.3 4.4 Noise Analysis Examples 204 4.5 References 216 217 4.6 Problems BASIC OPAMP DESIGN AND COMPENSATION **CHAPTER 5** 5.1 Two-Stage CMOS Opamp 221 5.2 Feedback and Opamp Compensation 232 SPICE Simulation Examples 251 5.3 5.4 References 252 253 5.5 Problems ADVANCED CURRENT MIRRORS AND OPAMPS **CHAPTER 6** 256 Advanced Current Mirrors 6.1 Folded-Cascode Opamp 266 6.2 273 Current-Mirror Opamp 6.3 278 6.4 Linear Settling Time Revisited Fully Differential Opamps 280 6.5 287 Common-Mode Feedback Circuits 6.6 291 Current-Feedback Opamps 6.7 295 6.8 SPICE Simulation Examples 299 6.9 References 6.10 Problems 300 **CHAPTER 7 COMPARATORS** 304 7.1 Using an Opamp for a Comparator 308 7.2 Charge-Injection Errors 7.3 Latched Comparators 317 321 7.4 Examples of CMOS and BiCMOS Comparators 7.5 **Examples of Bipolar Comparators** 328 7.6 References 330

7.7 Problems 331

Contents xii SAMPLE AND HOLDS, VOLTAGE REFERENCES, **CHAPTER 8** 334 AND TRANSLINEAR CIRCUITS Performance of Sample-and-Hold Circuits 334 8.1 MOS Sample-and-Hold Basics 336 8.2 Examples of CMOS S/H Circuits 343 8.3 Bipolar and BiCMOS Sample and Holds 349 8.4 Bandgap Voltage Reference Basics 353 8.5 Circuits for Bandgap References 357 8.6 Translinear Gain Cell 364 8.7 Translinear Multiplier 366 8.8 368 References 8.9 370 8.10 Problems 373 DISCRETE-TIME SIGNALS **CHAPTER 9** 9.1 Overview of Some Signal Spectra 373 9.2 Laplace Transforms of Discrete-Time Signals 374 9.3 z-Transform 377 9.4 Downsampling and Upsampling 379 382 **Discrete-Time Filters** 9.5 9.6 Sample-and-Hold Response 389 References 391 9.7 391 Problems 9.8 394 SWITCHED-CAPACITOR CIRCUITS **CHAPTER 10** 394 **Basic Building Blocks** 10.1 398 Basic Operation and Analysis 10.2 First-Order Filters 409 10.3 415 **Biquad Filters** 10.4 Charge Injection 423 10.5 Switched-Capacitor Gain Circuits 427 10.6 433 Correlated Double-Sampling Techniques 10.7 Other Switched-Capacitor Circuits 434 10.8 References 441 10.9 443 Problems 10.10 445 DATA CONVERTER FUNDAMENTALS CHAPTER 11 11.1 Ideal D/A Converter 445 Ideal A/D Converter 447 11.2 448 Quantization Noise 11.3 452 11.4 Signed Codes

Performance Limitations 454 11.5

References 461 11.6

11.7 Problems 461

#### NYQUIST-RATE D/A CONVERTERS CHAPTER 12

463 Decoder-Based Converters 12.1

469 **Binary-Scaled Converters** 12.2

- 475 Thermometer-Code Converters 12.3

- Hybrid Converters 481 12.4

484 12.5 References

12.6 Problems 484

#### NYQUIST-RATE A/D CONVERTERS CHAPTER 13

487 Integrating Converters 13.1 492 Successive-Approximation Converters 13.2 504 Algorithmic (or Cyclic) A/D Converter 13.3 507 Flash (or Parallel) Converters 13.4 513 Two-Step A/D Converters 13.5 516 Interpolating A/D Converters 13.6 519 Folding A/D Converters 13.7 523 Pipelined A/D Converters 13.8 Time-Interleaved A/D Converters 526 13.9 13.10 References 527

528 Problems 13.11

#### **OVERSAMPLING CONVERTERS** CHAPTER 14

531 Oversampling without Noise Shaping 14.1 538

557

- Oversampling with Noise Shaping 14.2 547

- System Architectures 14.3

- 551 **Digital Decimation Filters** 14.4 555

- Higher-Order Modulators 14.5 Bandpass Oversampling Converters

- 14.6 559 **Practical Considerations**

- 14.7 Multi-Bit Oversampling Converters

- 565 14.8 568 Third-Order A/D Design Example 14.9

- References 571

- 14.10 572

14.11 Problems

#### **CHAPTER 15 CONTINUOUS-TIME FILTERS**

- 575 15.1 Introduction to G<sub>m</sub>-C Filters

- 15.2 **Bipolar Transconductors** 584

463

487

531

xiv Contents

- 15.3 CMOS Transconductors Using Triode Transistors 597

- 15.4 CMOS Transconductors Using Active Transistors 607

- 15.5 BiCMOS Transconductors 616

- 15.6 MOSFET-C Filters 620

- 15.7 Tuning Circuitry 626

- 15.8 Dynamic Range Performance 635

- 15.9 References 643

- 15.10 Problems 645

## CHAPTER 16 PHASE-LOCKED LOOPS

- 16.1 Basic Loop Architecture 648

- 16.2 PLLs with Charge-Pump Phase Comparators

- 16.3 Voltage-Controlled Oscillators 670

- 16.4 Computer Simulation of PLLs 680

- 16.5 Appendix 689

- 16.6 References 692

- 16.7 Problems 693

INDEX

648

696

sometimes used in digital circuits, where the circle indicates that a low voltage on the gate turns the transistor on, as opposed to a high voltage for an n-channel transistor (Fig. 1.7(a)). The symbols of Fig. 1.8(d) or Fig. 1.8(e) might be used in larger circuits where many transistors are present, to simplify the drawing somewhat. They will not be used in this text.

#### **Basic Operation**

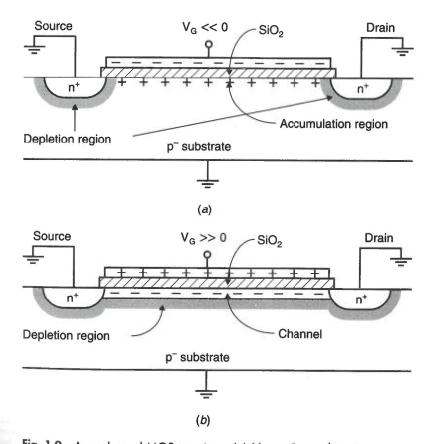

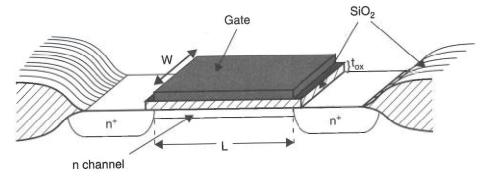

The basic operation of MOS transistors will be described with respect to an n-channel transistor. First, consider the simplified cross sections shown in Fig. 1.9, where the source, drain, and substrate are all connected to ground. In this case, the MOS transistor operates similarly to a capacitor. The gate acts as one plate of the capacitor, and the surface of the silicon, just under the thin insulating  $SiO_2$ , acts as the other plate.

If the gate voltage is very negative, as shown in Fig. 1.9(*a*), positive charge will be attracted to the channel region. Since the substrate was originally doped  $p^-$ , this negative gate voltage has the effect of simply increasing the channel doping to  $p^+$ ,

resulting in what is called an *accumulated channel*. The n<sup>+</sup> source and drain regions are separated from the p<sup>+</sup>-channel region by depletion regions, resulting in the equivalent circuit of two back-to-back diodes. Thus, only leakage current will flow even if one of the source or drain voltages becomes large (unless the drain voltage becomes so large as to cause the transistor to break down).

In the case of a positive voltage being applied to the gate, the opposite situation occurs, as shown in Fig. 1.9(b). For small positive gate voltages, the positive carriers in the channel under the gate are initially repulsed and the channel changes from a  $p^{-}$  doping level to a depletion region. As a more positive gate voltage is applied, the gate attracts negative charge from the source and drain regions, and the channel becomes an n region with mobile electrons connecting the drain and source regions.<sup>5</sup> In short, a sufficiently large positive gate-source voltage changes the channel beneath the gate to an n region, and the channel is said to be *inverted*.

The gate-source voltage, for which the concentration of electrons under the gate is equal to the concentration of holes in the p<sup>-</sup> substrate far from the gate, is commonly referred to as the *transistor threshold voltage* and denoted V<sub>tn</sub> (for n-channel transistors). For gate-source voltages larger than V<sub>tn</sub>, there is an n-type channel present, and conduction between the drain and the source can occur. For gate-source voltages less than V<sub>tn</sub>, it is normally assumed that the transistor is off and no current flows between the drain and the source. However, it should be noted that this assumption of zero drain-source current for a transistor that is off is only an approximation. In fact, for gate voltages around V<sub>tn</sub>, there is no abrupt current change, and for gate-source voltages slightly less than V<sub>tn</sub>, small amounts of *subthreshold current* can flow, as discussed in Section 1.3.

When the gate-source voltage,  $V_{GS}$ , is larger than  $V_{tn}$ , the channel is present. As  $V_{GS}$  is increased, the density of electrons in the channel increases. Indeed, the carrier density, and therefore the charge density, is proportional to  $V_{GS} - V_{tn}$ , which is often called the *effective gate-source voltage* and denoted  $V_{eff}$ . Specifically, define

$$V_{\rm eff} \equiv V_{\rm GS} - V_{\rm tn} \tag{1.54}$$

The charge density of electrons is then given by

$$Q_{n} = C_{ox}(V_{GS} - V_{tn}) = C_{ox}V_{eff}$$

(1.55)

Here, Cox is the gate capacitance per unit area and is given by

$$C_{ox} = \frac{K_{ox}\varepsilon_0}{t_{ox}}$$

(1.56)

where  $K_{ox}$  is the relative permittivity of SiO<sub>2</sub> (approximately 3.9) and  $t_{ox}$  is the thickness of the thin oxide under the gate. A point to note here is that (1.55) is only accurate when both the drain and the source voltages are zero.

<sup>5.</sup> The drain and source regions are sometimes called diffusion regions or junctions for historical reasons. This use of the word *junction* is not synonymous with our previous use, in which it designated a pn interface of a diode.

To obtain the total gate capacitance, (1.56) should be multiplied by the effective gate area, WL, where W is the gate width and L is the effective gate length. These dimensions are shown in Fig. 1.10. Thus the total gate capacitance,  $C_{gs}$ , is given by

$$C_{\rm qs} = WLC_{\rm ox} \tag{1.57}$$

and the total charge of the channel,  $Q_{T-n}$ , is given by

$$Q_{T-n} = WLC_{ox}(V_{GS} - V_{tn}) = WLC_{ox}V_{eff}$$

(1.58)

The gate capacitance,  $C_{gs}$ , is one of the major load capacitances that circuits must be capable of driving. Gate capacitances are also important when one is calculating *charge injection*, which occurs when a MOS transistor is being turned off because the channel charge,  $Q_{T-n}$ , must flow from under the gate out through the terminals to other places in the circuit.

Next, if the drain voltage is increased above 0 V, a drain-source potential difference exists. This difference results in current flowing from the drain to the source.<sup>6</sup> The relationship between  $V_{DS}$  and the drain-source current,  $I_D$ , is the same as for a resistor, assuming  $V_{DS}$  is small. This relationship is given [Sze, 1981] by

$$I_{D} = \mu_{n} Q_{n} \frac{W}{L} V_{DS}$$

(1.59)

where  $\mu_n \cong 0.06 \text{ m}^2/\text{Vs}$  is the mobility of electrons near the silicon surface, and  $Q_n$  is the charge concentration of the channel per unit area (looking from the top down). Note that as the channel length increases, the drain-source current decreases, whereas this current increases as either the charge density or the transistor width increases. Using (1.58) and (1.59) results in

$$I_{D} = \mu_{n}C_{ox}\frac{W}{L}(V_{GS} - V_{tn})V_{DS} = \mu_{n}C_{ox}\frac{W}{L}V_{eff}V_{DS}$$

(1.60)

Fig. 1.10 The important dimensions of a MOS transistor.

6. The current is actually conducted by negative carriers (electrons) flowing from the source to the drain. Negative carriers flowing from source to drain results in a positive current from drain to source,  $I_{DS}$ .

where it should be emphasized that this relationship is only valid for drain-source voltages near zero (i.e.,  $V_{DS}$  much smaller than  $V_{eff}$ ).

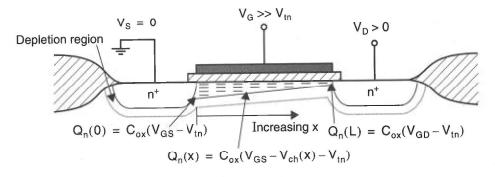

As the drain-source voltage increases, the channel charge concentration decreases at the drain end. This decrease is due to the smaller gate-to-channel voltage difference across the thin gate oxide as one moves closer to the drain. In other words, since the drain voltage is assumed to be at a higher voltage than the source, there is an increasing voltage gradient from the source to the drain, resulting in a smaller gate-to-channel voltage near the drain. Since the charge density at a distance x from the source end of the channel is proportional to  $V_G - V_{ch}(x) - V_{tn}$ , as  $V_G - V_{ch}(x)$  decreases, the charge density also decreases.<sup>7</sup> This effect is illustrated in Fig. 1.11.

Note that at the drain end of the channel, we have

$$V_{G} - V_{ch}(L) = V_{GD} \tag{1.61}$$

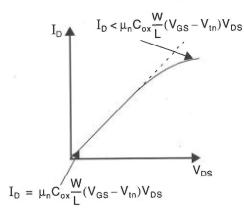

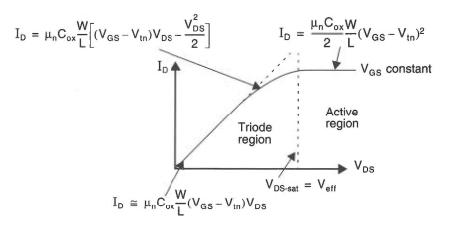

For small  $V_{DS}$ , we saw from (1.60) that  $I_D$  was linearly related to  $V_{DS}$ . However, as  $V_{DS}$  increases, and the charge density decreases near the drain, the relationship becomes nonlinear. In fact, the linear relationship for  $I_D$  versus  $V_{DS}$  flattens for larger  $V_{DS}$ , as shown in Fig. 1.12.

Fig. 1.11 The channel charge density for  $V_{DS} > 0$ .

Fig. 1.12 For  $V_{DS}$  not close to zero, the  $I_D$  versus  $V_{DS}$  relationship is no longer linear.

7.  $V_G - V_{CH}(x)$  is the gate-to-channel voltage drop at distance x from the source end, with  $V_G$  being the same everywhere in the gate, since the gate material is highly conductive.

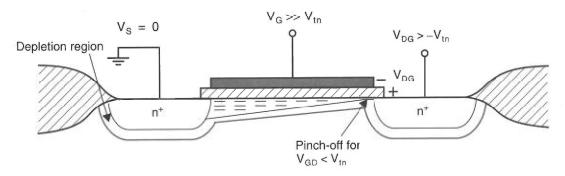

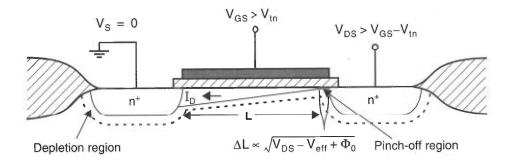

As the drain voltage is increased, at some point the gate-to-channel voltage at the drain end will decrease to the threshold value  $V_{tn}$ —the minimum gate-to-channel voltage needed for n carriers in the channel to exist. Thus, at the drain end, the channel becomes *pinched off*, as shown in Fig. 1.13. This pinch-off occurs at  $V_{GD} = V_{tn}$ , since the channel voltage at the drain end is simply equal to  $V_D$ . Thus, pinch-off occurs for

$$V_{\rm DG} > -V_{\rm tn} \tag{1.62}$$

Denoting  $V_{DS-sat}$  as the drain-source voltage when the channel becomes pinched off, we can substitute  $V_{DG} = V_{DS} - V_{GS}$  into (1.62) and find an equivalent pinch-off expression

$$V_{\rm DS} > V_{\rm DS-sat} \tag{1.63}$$

where  $V_{DS-sat}$  is given<sup>8</sup> by

$$V_{\text{DS-sat}} = V_{\text{GS}} - V_{\text{tn}} = V_{\text{eff}}$$

(1.64)

The electron carriers travelling through the pinched-off drain region are velocity saturated, similar to a gas under pressure travelling through a very small tube. If the drain-gate voltage rises above this critical pinch-off voltage of  $-V_{tn}$ , the charge concentration in the channel remains constant (to a first-order approximation) and the drain current no longer increases with increasing  $V_{DS}$ . The result is the current-voltage relationship shown in Fig. 1.14 for a given gate-source voltage. In the region of operation where  $V_{DS} > V_{DS-sat}$ , the drain current is independent of  $V_{DS}$  and is called the *active region*.<sup>9</sup> The region where  $I_D$  changes with  $V_{DS}$  is called the *triode region*. When MOS transistors are used in analog amplifiers, they almost always are biased in the active region. When they are used in digital logic gates, they often operate in both regions.

Fig. 1.13 When  $V_{DS}$  is increased so that  $V_{GD} < V_{tn}$ , the channel becomes pinched off at the drain end.

<sup>8.</sup> Because of the body effect, the threshold voltage at the drain end of the transistor is increased, resulting in the true value of  $V_{\text{DS-sat}}$  being slightly lower than  $V_{\text{eff}}$ .

<sup>9.</sup> Historically, the active region was called the saturation region, but this led to confusion because in the case of bipolar transistors, the saturation region occurs for small  $V_{CE}$ , whereas for MOS transistors it occurs for large  $V_{DS}$ . The renaming of the saturation region to the active region is becoming widely accepted.

Fig. 1.14 The  $I_D$  versus  $V_{DS}$  curve for an ideal MOS transistor. For  $V_{DS} > V_{DS-sat}$ ,  $I_D$  is approximately constant.

Before proceeding, it is worth discussing the terms *weak, moderate,* and *strong inversion*. As just discussed, a gate-source voltage greater than  $V_{tn}$  results in an inverted channel, and drain-source current can flow. However, as the gate-source voltage is increased, the channel does not become inverted (i.e., n-region) suddenly, but rather gradually. Thus, it is useful to define three regions of channel inversion with respect to the gate-source voltage. In most circuit applications, noncutoff MOS-FET transistors are operated in strong inversion, with  $V_{eff} > 100 \text{ mV}$  (many prudent circuit designers use a minimum value of 200 mV). As the name suggests, strong inversion occurs when the channel is strongly inverted. It should be noted that all the equation models in this section assume strong inversion operation. Weak inversion occurs when  $V_{GS}$  is approximately 100 mV or more below  $V_{tn}$  and is discussed as subthreshold operation in Section 1.3. Finally, moderate inversion is the region between weak and strong inversion.

#### Large-Signal Modelling

The *triode region equation* for a MOS transistor relates the drain current to the gatesource and drain-source voltages. It can be shown (see Appendix) that this relationship is given by

$$I_{D} = \mu_{n}C_{ox}\left(\frac{W}{L}\right)\left[(V_{GS} - V_{tn})V_{DS} - \frac{V_{DS}^{2}}{2}\right]$$

(1.65)

As  $V_{DS}$  increases,  $I_D$  increases until the drain end of the channel becomes pinched off, and then  $I_D$  no longer increases. This pinch-off occurs for  $V_{DG} = -V_{tn}$ , or approximately,

$$V_{DS} = V_{GS} - V_{tn} = V_{eff} \tag{1.66}$$

Right at the edge of pinch-off, the drain current resulting from (1.65) and the drain current in the active region (which, to a first-order approximation, is constant with

respect to  $V_{DS}$ ) must have the same value. Therefore, the *active region equation* can be found by substituting (1.66) into (1.65), resulting in

$$I_{D} = \frac{\mu_{n}C_{ox}}{2} \left(\frac{W}{L}\right) (V_{GS} - V_{tn})^{2}$$

(1.67)

For  $V_{DS} > V_{eff}$ , the current stays constant at the value given by (1.67), ignoring second-order effects such as the finite output impedance of the transistor. This equation is perhaps the most important one that describes the large-signal operation of a MOS transistor. It should be noted here that (1.67) represents a squared current-voltage relationship for a MOS transistor in the active region. In the case of a BJT transistor, an exponential current-voltage relationship exists in the active region.

As just mentioned, (1.67) implies that the drain current,  $I_D$ , is independent of the drain-source voltage. This independence is only true to a first-order approximation. The major source of error is due to the channel length shrinking as  $V_{DS}$  increases. To see this effect, consider Fig. 1.15, which shows a cross section of a transistor in the active region. A pinched-off region with very little charge exists between the drain and the channel. The voltage at the end of the channel closest to the drain is fixed at  $V_{GS} - V_{tn} = V_{eff}$ . The voltage difference between the drain and the near end of the channel lies across a short depletion region often called the *pinch-off region*. As  $V_{DS}$  becomes larger than  $V_{eff}$ , this depletion region surrounding the drain junction increases its width in a square-root relationship with respect to  $V_{DS}$ . This increase in the width of the depletion region surrounding the drain junction decreases the effective channel length. In turn, this decrease in effective channel length increases the drain current, resulting in what is commonly referred to as *channel-length modulation*.

To derive an equation to account for channel-length modulation, we first make use of (1.11) and denote the width of the depletion region by  $x_d$ , resulting in

$$\begin{aligned} \mathbf{x}_{d} &\cong \mathbf{k}_{ds} \sqrt{\mathbf{V}_{\text{D-ch}} + \Phi_{0}} \\ &= \mathbf{k}_{ds} \sqrt{\mathbf{V}_{\text{DG}} + \mathbf{V}_{\text{tn}} + \Phi_{0}} \end{aligned} \tag{1.68}$$

where

$$k_{ds} = \sqrt{\frac{2K_s\varepsilon_0}{qN_A}}$$

(1.69)

Fig. 1.15 Channel length shortening for  $V_{DS} > V_{eff}$ .

and has units of  $m/\sqrt{V}$ . Note that  $N_A$  is used here since the n-type drain region is more heavily doped than the p-type channel (i.e.,  $N_D >> N_A$ ). By writing a Taylor approximation for  $I_D$  around its operating value of  $V_{DS} = V_{GS} - V_{tn} = V_{eff}$ , we find  $I_D$  to be given by

$$I_{D} = I_{D-sat} + \left(\frac{\partial I_{D}}{\partial L}\right) \left(\frac{\partial L}{\partial V_{DS}}\right) \Delta V_{DS} \cong I_{D-sat} \left(1 + \frac{k_{ds}(V_{DS} - V_{eff})}{2L\sqrt{V_{DG} + V_{tn} + \Phi_{0}}}\right)$$

(1.70)

where  $I_{D-sat}$  is the drain current when  $V_{DS} = V_{eff}$ , or equivalently, the drain current when the channel-length modulation is ignored. Note that in deriving the final equation of (1.70), we have used the relationship  $\partial L/\partial V_{DS} = -\partial x_d / \partial V_{DS}$ . Usually, (1.70) is written as

$$I_{D} = \frac{\mu_{n}C_{ox}}{2} \left(\frac{W}{L}\right) (V_{GS} - V_{tn})^{2} [1 + \lambda (V_{DS} - V_{eff})]$$

(1.74)

where  $\lambda$  is the output impedance constant (in units of V<sup>-1</sup>) given by

$$\lambda = \frac{k_{ds}}{2L\sqrt{V_{DG} + V_{tn} + \Phi_0}} = \frac{k_{ds}}{2L\sqrt{V_{DS} - V_{eff} + \Phi_0}}$$

(1.72)

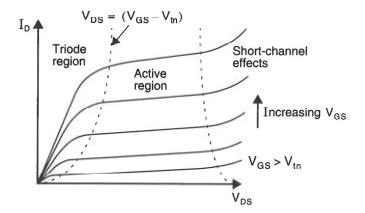

Equation (1.71) is accurate until  $V_{DS}$  is large enough to cause second-order effects, often called *short-channel effects*. For example, (1.71) assumes that current flow down the channel is not *velocity-saturated* (i.e., increasing the electric field no longer increases the carrier speed). Velocity saturation commonly occurs in new technologies that have very short channel lengths and therefore large electric fields. If  $V_{DS}$  becomes large enough so short-channel effects occur,  $I_D$  increases more than is predicted by (1.71). Of course, for quite large values of  $V_{DS}$ , the transistor will eventually break down.

A plot of  $I_D$  versus  $V_{DS}$  for different values of  $V_{GS}$  is shown in Fig. 1.16. Note that in the active region, the small (but nonzero) slope indicates the small dependence of  $I_D$  on  $V_{DS}$ .

Fig. 1.16 I<sub>D</sub> versus V<sub>DS</sub> for different values of V<sub>GS</sub>.