In fact, the interaction field of a many-body system is usually expressed as empirical potential among the atoms (particles) of the many-body system under study and it should includes energy terms that represent bonded and non-bonded (Van der Waals and Coulombic forces) interactions. By limiting our attention to the simulation of a biological system, a typical force field used in classical MD simulations appears to be like follows

$$V = \sum_{\text{bonds}} K_b [b - b_0]^2 + \sum_{\text{angles}} K_{\Theta} [\Theta - \Theta_0]^2$$

$$+ \sum_{\text{diltedrals}} K_{\phi} [1 + \cos(n\phi - \delta)] + \sum_{\text{improper}} K_{\xi} [\xi - \xi_0]^2$$

$$+ \sum_{i} \sum_{j} \varepsilon_{ij} \left[ \left( \frac{\alpha_{ij}}{r_{ij}} \right)^{12} - \left( \frac{\alpha_{ij}}{r_{ij}} \right)^{6} \right] + \sum_{i} \sum_{j} \frac{q_i q_j}{4\pi \epsilon r_{ij}}.$$

$$(10a)$$

$$+\sum_{i}\sum_{j}\varepsilon_{ij}\left[\left(\frac{\alpha_{ij}}{r_{ij}}\right)^{12}-\left(\frac{\alpha_{ij}}{r_{ij}}\right)^{6}\right]+\sum_{i}\sum_{j}\frac{q_{i}q_{j}}{4\pi\epsilon r_{ij}}.$$

(10b)

The first four terms (Eq. (10a)) represent the bonded potential. The last one (Eq. (10b)) gives the non-bonded energy contribution to the total potential and it is the most time-consuming task (≈ 85-90% of the total CPU time).

Each pair interaction ij in Eq. (10b) has to be calculated to obtain the energy due to the non-bonded forces. The number of pairs to be calculated is halved using Newton's third law  $F_l = -F_l$ .

The number of pair interactions can be further reduced including only atom pairs within a cutoff distance. Therefore, at each step a generic atom i has a set of j different atoms to interact with (the non-bonded pair list). This list can be updated every n steps, with  $n \simeq 10$ .

Parallelization can be achieved with a particle decomposition scheme, i.e. a number of i particles is assigned to each processor (home particles) [7]. Then, each processor will calculate independently the pair interactions of the i home particles with the j particles.

It is worth noting that in a shared memory machine the replicated data model is automatically obtained, i.e. data about every atom in the system is available to each processor, while in a distributed memory architecture position. and undergone force of each particle, have to be communicated between the machine processors.

Once obtained the interaction forces on each atom, the Newton's equations of motion can be numerically integrated using, for example, the leap-frog algorithm [7].

The integration is not a computationally demanding task but it can be nevertheless performed in parallel on each home particle. A longer integration time step permits to simulate longer times with the same number of steps. If the bond-stretching vibrations have to be taken into account, the time step cannot be longer than 0.25 fs. The application of distance constraints between bonded atoms, with algorithms like SHAKE [32], permits to increase the time step to 2 fs.

After the non bonded interaction calculations, SHAKE is the most computational-intensive part of the classical MD calculation. Modern MD simulations of biological systems include a great number of solvent molecules on which it is possible the application of independent distance constraints by different processors. Constraints application to protein or DNA, on the contrary, is better performed by one processor. A good load balancing can be obtained with a functional parallelism, i.e. assigning different tasks (solvent distance constraints, solute distance constraints, bonded calculations, etc.) to different processors.

### 3.3.1. Test case

GROMACS version 1.6 [4], from Groeningen BIOSON Research Institute, is an efficient parallel MD code, particularly suited to simulate biological systems. GROMACS has been parallelized using a message-passing model. Both PVM [33] (Parallel Virtual Machines) and MPI [34] (Message Passing Interface) have been utilized within the GROMACS software.

As biological test case we chose to simulate the Major Histocompatibility Complex macromolecule class II (MHC II) complexed with an antigenic peptide and water molecules.

Table 6 MHC II simulated on a Compaq ES40 cluster

| SMP mach. | Nodes | E.T. (s) | Speedup | % parallel code |

|-----------|-------|----------|---------|-----------------|

| 1         | 1     | 932      | 1       | N.A.            |

|           | 2     | 467      | 2.0     | 99,8            |

|           | 3     | 346      | 2.7     | 94.3            |

|           | 4     | 281      | 3,3     | 93.1            |

| 2         | 2     | 470      | 2.0     | 99.1            |

|           | 4.    | 281      | 3.3     | 93 L            |

|           | 6     | 215      | 4.3     | 92.3            |

|           | 8     | 168      | 5.5     | 93.7            |

| 3         | 3     | 349      | 2.7     | 93.8            |

|           | 6     | 216      | 4.3     | 92.2            |

|           | 9     | 146      | 6.4     | 94,9            |

|           | 12    | 114      | 8.2     | 95,8            |

| 1         | -4    | 284      | 3.3     | 92.7            |

|           | 8     | 168      | 5.5     | 93.7            |

|           | 12    | 113      | 8.2     | 95.9            |

|           | 16    | 101      | 9.2     | 95.1            |

Table 7 MHC II simulated on a IBM 8x SP3 cluster

| SMP mach | Nodes | E.T. (s) | Speedup | % parallel code |

|----------|-------|----------|---------|-----------------|

| 1        | 1     | 1594     | 1       | N.A.            |

|          | 8     | 313      | 5.1     | 91.8            |

| 2        | 16    | 191      | 8.3     | 93.9            |

MHC II are immunoglobulin-like proteins present in variety of cells, which bind antigens from endocytosed plasma membrane and extracellular proteins. Antigen-MHC II complexes are recognized at the surface of the cell by helper T-cells promoting activation of an immune response.

MHC II is composed by 7776 atoms, the antigenic peptide by 280 atoms and there are 17296 water molecules giving a total of 59 863 atoms. The system was simulated for 100 steps with a time step of 2 fs; a non-bonded cutoff radius of 1.8 nm was used updating the non-bonded pair list every 10 steps.

Table 6 (cluster of Compaq ES40, 4x ev6@500 MHz) and Table 7 (cluster of IBM SP3, 8x PWIII@222 MHz) show the test case results. In column one the number of SMP machines involved in the test run is shown; in column two the total number of processors and in the remaining columns the elapsed time, the speedups of the MPI and the two the total number of processors and in the remaining columns the enapsed time, the speedups of the lyrr and the portion of parallelized code as extrapolated by the Amdhal law, are reported. The last data were calculated using the following equation:  $\alpha = \frac{3 \times p - p}{3 \times p - 3}$  where S is the speedup and p the number of processors.

It is worth noting the variability of the extrapolated parallel portion of the code that varies from a maximum of

99.8% (one Compaq ES40 machine, 2 processors) to a minimum of 91.8% (one IBM SP3 machine, 8 processors).

This behaviour is due to the simultaneous use of different parallelization schemes: particle decomposition for the non-bonded force calculation that represents the 90.2% of serial calculation time; functional parallelism for the remaining portion of the code.

For this reason the parallel efficiency of the code strongly depends on the simulated system and on the condition of the simulation. Nevertheless, the weight of the computational core (the non-bonded force calculation) can be considered as the minimum portion of parallel code obtainable in a real simulation.

# 3.4. Atomic and Molecular Physics: The electron-molecule scattering treated with the Single Center Expansion (SCE) method

The application of the central field model in quantum mechanics yields to the factorization of the wavefunction in its radial and angular part and it has been and is nowadays, applied to the quantum description of bound and continuum electronic states of atoms [35] while several attempts have been made in the past to extend it to bound molecular systems [36].

One of the most successful application of this model has been the treatment of the scattering processes which occur in the collision of electrons with polyatomic non-linear targets, known as the Single Center Expansion (SCE) method. A general discussion on the computational aspects of this model has been given before [37] and specific results have also been analyzed elsewhere [38,39]. We will therefore only outline here the basics of the generation of the SCE numerical wavefunction and its related molecular properties. The full details on the mathematical and numerical aspects of SCE procedure are given elsewhere. We refer the interested reader to a recent paper which describes the SCELib code a computational procedure for the SCE pre-processing phase, combined in a single set of programs [11].

# 3.4.1. The SCE wavefunction and related molecular properties

In the present computational approach one needs a general-purpose quantum chemistry code that is employed to generate the Single Determinant description, (near to the Hartree-Fock — HF — limit) of the target electronic wavefunction, and an interface with a numerical procedure that can give us all the necessary quantities as being referred to the molecular Centre Of Mass (C.O.M.) as expansion centre [37].

In most of the numerical methods employed to solve the scattering equations one then converts the CC equations into a set of coupled radial equations by making first a single centre expansion (SCE) of the bound and continuum functions and then by integrating over all the angular coordinates. Limiting our attention to the ground state wavefunction, one therefore writes down the bound orbitals as expansions around the centre of mass, from which the body-fixed (BF) frame of reference originates:

$$\phi_i(\mathbf{r}) = r^{-1} \sum_{kl} u_{kl}^i(r) X_{kl}^{i,l'nl}(\theta, \phi),$$

(11)

Here i labels a specific, multicenter molecular orbital (MO), which contributes to the density of the bound electrons in the nonlinear target, while the indices  $|p\mu\rangle$  for the continuum functions label one of the relevant Irreducible Representations (IR) and one of its components, respectively. The index h labels a specific basis, at a given angular momentum l, for the pth IR that one is considering [40].

In order to perform expansions (11), one needs, therefore, to start from the multicenter wavefunction which describes the target molecule and then generate by quadrature each of the  $u^k_{hl}(r)$  coefficients; they were obtained for the first time by numerical quadrature of the multicenter GTO's given as Cartesian Gaussian functions [41]. The X angular functions used in (11) are symmetry-adapted, generalized harmonics build as linear combinations of spherical harmonics  $Y_l^m(\theta, \phi)$  which, for a given l, form a basis of the (2l+1)-dimensional IR of the full rotation group [40,42].

After one obtains the radial coefficients  $u_{hl}^k(r)$ , each bound one-electron wavefunction is also expanded about the C.O.M. in terms of the X functions

$$u_i(\mathbf{r}) = r^{-1} \sum_{hl} u_{hl}^i(r) X_{hl}^{p\mu}(\theta, \phi)$$

(12)

then, the one-electron density function can be written as usual

$$\rho(\mathbf{r}) = \int |\psi(x_1, x_2, ..., x_N)|^2 dx_2 ... dx_N = 2 \times \sum_i |u_i(\mathbf{r})|^2,$$

(13)

where the factor 2 is due to the sum over spin, and the i sum is over each doubly occupied orbital. Once the quantity  $\rho(\mathbf{r})$  is obtained from the bound-state wavefunction  $u_i(\mathbf{r})$  of Eq. (13), it can be expanded in terms of symmetry-adapted functions belonging to the  $A_1$  irreducible representation as

$$\rho(\mathbf{r}) = r^{-1} \sum_{hlm} \rho_{hlm}(r) X_{hlm}^{A_1}(\theta, \phi), \qquad (14)$$

where

$$\rho_{hlm}(\mathbf{r}) = 2 \times \sum_{i} \int_{0}^{\pi} \sin(\theta) \, d\theta \int_{0}^{2\pi} u_{i}(\mathbf{r}) \cdot u_{i}(\mathbf{r}) \, d\phi. \tag{15}$$

Once the SCE one-electron density has been computed from Eqs. (14) and (15) one is able to derive from it all the molecular quantities which depend on the electronic distribution, either by integration, like the electronic Static Potential  $\int \rho(\mathbf{r}) d\mathbf{r}$ , or by differentiation like the density gradient  $(\nabla \rho)$  and Laplacian  $(\nabla^2 \rho)$ .

By using the SCELib [43] API (Application Program Interface) one has access to a large set of these molecular properties being calculated with respect to the molecular COM and for the first time we coded in it the gradient and Laplacian of the electronic density and static potential as explained in details in the next section.

## 3.4.2. Numerical implementation details

A feature common to all SCE molecular properties is that they can be expressed as

$$f(r,\theta,\phi) = \sum_{hlm} F_{hlm}(r) X_{hlm}^{A_L}(\theta,\phi), \tag{16}$$

where the f represent a given molecular property, function of the spherical coordinates as dot product of a radial component F times an angular analytic function X.

In a similar manner are expressed the gradient and Laplacian of the f:

$$\nabla f(r,\theta,\phi) = \sum_{lm} \nabla \left[ F_{lm}(r) X_{lm}(\theta,\phi) \right]$$

$$= \sum_{lm} \left[ \frac{\mathrm{d}F_{lm}}{\mathrm{d}r} X_{lm} \hat{\mathbf{e}}_r + \frac{F_{lm}}{r} \left( \frac{\partial X_{lm}}{\partial \theta} \hat{\mathbf{e}}_\theta + \frac{m}{\sin \theta} X_{lm} \hat{\mathbf{e}}_\phi \right) \right]$$

(17)

and

$$\nabla^{2} f(r, \theta, \phi) = \sum_{lm} \nabla^{2} \left[ F_{lm}(r) X_{lm}(\theta, \phi) \right]$$

$$= \sum_{lm} \left[ \frac{d^{2} F_{lm}}{dr^{2}} + \frac{2}{r} \frac{dF_{lm}}{dr} - \frac{l(l+1)}{r^{2}} \right] X_{lm}$$

(18)

but we let the interested reader to the specific literature [44] for the necessary mathematical backgrounds and numerical implementation details.

On Eqs. (16)–(18) above, the angular part is analytic and the radial part is numerical as derived from the SCE procedure. This last fact suggest that when one want to calculate a given property over a given  $(r, \theta, \phi)$  grid, the most time consuming section will be the calculation of the  $F_{lm}(r)$ ,  $F'_{lm}(r)$  and  $F''_{lm}(r)$ . In order to improve the calculation of the  $F_{lm}(r)$  and of its r derivatives, a natural way to proceed is to post-fit it after the SCE procedure, with a suitable fitting function.

In a first approach, we used a cubic spline fitting [45] of the  $F_{lm}(r)$  function. The spline fitting has the property that the fitted function can be very efficiently evaluated at each r point but more important, that one can obtains its first and second derivatives with respect to r from the same fitting parameters of the  $F_{lm}(r)$ . Thus, when one has fitted the  $F_{lm}(r)$  function with a cubic spline, by calculating the four parameters needed at each r point, a single call to an evaluation routine can efficiently return the  $F_{lm}(r)$ ,  $F_{lm}^{l}(r)$  and  $F_{lm}^{ll}(r)$ .

For what concerns the angular part of our SCE functions, a natural limit arise on the floating point representation of the  $X_{lm}$  (i.e. the  $Y_{lm}$ ); in fact, it is well known that over a certain value of l one reaches the limit of the double precision floating point arithmetic. To overcome this limit, one can either use a quadrupole precision floating point arithmetic (currently available on 64 bits computers) or use specifically designed routines for multiple precision fit/evaluation of the  $Y_{lm_n}$  and even available on Internet [46].

### 3.4.3. Numerical results

In this section we will report some calculation examples by limiting the resulting data to the pre-processing part of the whole electron-molecule SCE scattering procedure. These results refer to those recently reported in the literature [11] but are enriched with more informations on the inner profiling of the SCELib code used for the test. This could offer a way to the reader to better analyze the relative importance of the various code sections with the aim to extract the numerical intensive kernels and evaluate them in detail. However, we should warn again the reader that we are referring to the pre-processing part of the whole electron-molecule computational procedure, and that the successive scattering calculation is likewise CPU and I/O demanding as stated in a recently published paper [47], where a new method of integration of the scattering equations has been presented.

An even more interesting aspect to discuss of the pre-processing part, would be the fact that through an interface code — the SCELib API — one is able to use the pre-processing data to map a given molecular property (static potential, electron density, etc.) over a generic Cartesian grid. This of course, could be of more general use in many related scientific areas, but we should leave the interested reader to some preliminary results obtained using a prototype version of the SCELib API set of programs [43].

As a test case to discuss, we chose a  $C_{20}$  molecule, the  $SO_2$  system, with a number of electrons able to produce a timing long enough to avoid any random measurement error in the parallel runs. For the  $SO_2$  molecule, we started from its HF/D95\*\* optimized geometry (R(SO) = 1.423 Å,  $\overline{OSO} = 118.1^\circ$ ) and using this electronic solution to derive the SCE wavefunction of Eq. (12) with the SCELib package. Furthermore, we used a  $R, \theta, \phi$  of  $300 \times 96 \times 84$  for a total of 2419 200 points,  $L_{MAX}$  was set to 10 and the Centre Of Mass (COM) chosen as expansion centre. This required a scratch memory usage of about 300 MB, which is small enough to be easily managed by the server class machines under test. In the followings, we decided to show only the results coming from the most time-consuming part of the SCELib package, the *sphint* function, which performs the Single Centre Expansion of the GTO wavefunction of a SCF run. In this program, the grid evaluation of the GTO wavefunction and the subsequent angular integration are carried out and to show its performances the Table 8 reports the overall elapsed time of the *sphint* code section together with the corresponding speed-ups on the IBM, Compaq and SUN SMP parallel machines of the p-threaded SCELib version using from 1 to 14 nodes.

Its is evident from the reported data that all the machines show a fairly linear speed-up and in the case of the ES4500 this trend is maintained up to n=14. We should note however, that in this latter case we observe a superlinear speed-up between 4 and 12 nodes which is quite unusual for this kind of parallel architecture where for this type of floating-point intensive codes one usually find a performance bottleneck beyond 8 CPUs. This particular behaviour has been described and explained in detail in Ref. [11] and it will not repeated here.

Table 8

SO<sub>2</sub> SCELib sphint parallel runs on IBM, SUN and Compaq SMP architectures. Elapsed Time (E.T.) in seconds and speedup vs. the number of nodes

|       | IBM 43P-260 |         | Compaq ES40 |         | SUN ES4500 |         |

|-------|-------------|---------|-------------|---------|------------|---------|

| Nodes | E.T. (s)    | Speedup | E,T. (s)    | Speedup | E.T. (s)   | Speedup |

| 1     | 208.9       | 1.0     | 104.1       | 1.0     | 393.3      | 1.0     |

| 2     | 104.1       | 2.0     | 52.6        | 2.0     | 183.3      | 2.1     |

| 4     |             |         | 25.9        | 4.0     | 89.6       | 4.4     |

| 8     |             |         |             |         | 45.1       | 8.7     |

| 12    |             |         |             |         | 32.0       | 12,3    |

| 14    |             |         |             |         | 28,5       | 13.8    |

More interesting to discuss here, is the analysis of the relative performances of the leading computational parts of the SCELib code. To this end, we report in the followings, the profiling informations of the test performed on the same molecular system cited above but but over a smaller grid (100R points) and scrially ran over a single CPU Alpha ev67@667 MHz CPU, with the standard prof Unix profiler under the Tru64 V5.0A Operating System.

| %time                                                         | seconds                                                                                                      | cum %                        | cum sec                                                                       | procedure (file)                                                                                                                          |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 51.6<br>47.0<br>0.7<br>0.3<br>0.1<br>0.1<br>0.0<br>0.0<br>0.0 | 17.4873<br>15.9287<br>0.2529<br>0.0967<br>0.0488<br>0.0283<br>0.0215<br>0.0088<br>0.0029<br>0.0029<br>0.0020 | 99.4<br>99.7<br>99.8<br>99.9 | 17.49<br>33.42<br>33.67<br>33.81<br>33.84<br>33.86<br>33.86<br>33.88<br>33.88 | CalcMO ( <scelib>) sphint (<scelib>) pow_di (<scelib>) SubPointC (<scelib>) gangf (<scelib>)</scelib></scelib></scelib></scelib></scelib> |

It is evident from the data reported that 99.9% of the computing time refers to the part of the code running in parallel that is, the *sphint* function. In fact, apart from the preparation routines (from *setinp* to *mkgrid*) the rest of the functions are called from *sphint* and among these, the most time consuming one is *CalcMO*. This behaviour confirm the linear speedup found over the three parallel SMP architectures used for the tests where we used a pthreaded version of the *sphint* function, so that the whole computational kernel was eligible to be run in parallel.

It is interesting to point out the fact that two routines, Calc MO and sphint, account for the majority of the CPU time spent for the calculation. In the former function the Gaussian wavefunction is calculated over a convenient  $(\theta, \phi)$  grid and then used by the latter (the "caller") to perform a Gauss-Legendre (Gauss-Chebyshev) angular integration. These two steps are necessary to evaluate the  $u^i_{hl}(r)$  terms of Eq. (11) and once carried out, the one-electron density can be calculated and from it, all the necessary molecular properties referred to a Single Centre of reference. The computing time of the evaluation/integration steps is strictly bound to the low level routines used by the two functions cited above. While the evaluation step depends from the exp function calculation of the Gaussian

basis set (see Eq. (3)), the integration phase is totally bound to the evaluation of the angular spherical harmonies  $Y_{lm}$  functions (see Eq. (11)). This behaviour is quite interesting because it shows explicitly the dependence of the two major stages of the pre-processing calculation phase performed in *sphint* from the basic low-level routines exp and  $Y_{lm}$ .

## 4. The commonly shared numerical behaviour

The first element of similarity among the codes we analyzed so far, is that we have a code implementation dependency. By this we mean that the user is not guaranteed that the same binary code is executed on different architectures, due to the fact, for example, that different algorithms can be used by low-level vendor routines at run-time.

A second element of similarity can be found by looking at the pre-processing behaviour of these codes (a situation that we refer to as job type dependency). By this we mean that the user is not guaranteed that the same code sections will perform exactly at the same computational rates when applied to different molecular systems. In examples, if you change your molecule geometry or, even if you change some run-time parameters in the input, you are not assured that the same code section will performs at a constant computational rate.

This is a common behavior of many codes in this and other scientific areas, which have years of development behind, containing several thousands of FORTRAN/C source lines: it is well known to the users (end-users or developers) of the codes mentioned above, that even the traditional (serial) profiling stage can be a cumbersome activity due to the hidden complexity of the source files.

Nonetheless, we have seen as they share specific features which make possible to derive some common conclusions on the best numerical environment for those applications. We would point out in fact as stated in Eq. (3), the central role played by the exp function in quantum chemistry and in molecular physics. At the same time, the BLAS low-level routines are of paramount importance in materials science as well as in quantum chemistry as reported in Eqs. (1) and (9). Furthermore, the evaluation of the most time-consuming part of the potential used in classical MD of biomolecules and reported in Eq. (10b) closely relates to the expression of any SCE molecular property and its gradient/laplacian of Eqs. (11)–(18), where the dependency on 1/r at various ranks is clearly evident.

These last comments suggested us to try a sort of summary of the numeric needs of these closely related computational areas. We will sketch these requirements in a short report (Table 9) where we would focus the attention on those low-level routines which are the computational cores of the above cited codes. These computational kernels are generally small, cleaned sections of code that we would expect to be ported on highly optimized silicon chips and dedicated to the high performance scientific computing community.

Table 9

A tentative attempt to summarize the most time consuming low-level routines needed in (bio)chemical-physics simulations

| Function class                 | Function type                |

|--------------------------------|------------------------------|

| Basic mathematical functions   | exp, F,                      |

| Linear algebra basic functions | BLAS LI-3,                   |

| Polynomial functions           | Legendre, Hennite, Chebyshey |

| Simple fitting functions       | Splines, N rank polynomials, |

| Series expansions              | Fast Fourier transform,      |

### 5. Conclusions

We have seen in the previous sections how many aspects join apparently different scientific fields, in the computational area of (bio)chemical-physics. From the computational side these similarities become even more evident and a common set of functions and routines are frequently used in the majority of the codes adopted in this area of computing.

This suggests a reasonable request to electronic engineers: why do not exploit the porting of these computational kernels on optimized silicon chips? We are really confident that this could improve the performances of the codes used in these area by several order of magnitude. By the way, we are not underestimating the inner complexity in the design and manufacture of these special-purpose (SP) devices, but we would conversely focus attention of the designers on the possible benefits of these SP chips to this (not so) specific field of application.

First of all, let imagine this SP chip integrated as a co-processor in any serial or parallel architecture by means of the PCI (Peripheral Component Interconnect) connector of its board. A part from the key technical issues regarding the data bandwidth toward the *General Purpose* (GP) CPU, this component could co-operate with it to solve specific numeric problem, by leaving to the main GP processor the remaining of the workload (I/O, devices management, etc.). This hypothetic system with SP and GP processors coupled together could be a viable High Performance Computing (HPC) solution for this and many other computational areas, providing one is able to easily administer the SP processors within the GP system.

In fact the SP boards could be designed to solve many different specific numerical problems (not necessary only in the area of (bio)chemical-physics) but, in our opinion, the whole system should conforms to the following requirements:

- The SP chip must have an Application Program Interface (API) so that it can be easily used as the corresponding software functions they refer to.

- The SP API library should be as conformant as possible to the corresponding software counterparts and in a second step, the SP API should be able to conform to the underlying hardware present (see, e.g., the role played by the GL/OpenGL library in the graphic area of computing).

- The best hardware solution for this computational area would be a combination of GP/SP processors with the

maximum configuration flexibility (e.g., you change your GP system and maintain the SP boards on the new

system).

This combination of GP/SP chips could operate at impressive computational rates with minimal increasing of the hardware complexity as the PC market clearly shows. In fact the idea of merging GP and SP devices is not new. Intel Co., has introduced three years ago the MMX SP (SIMD) chip into its series of Pentium processor with significant performance gains in executing multimedia X86 instructions.

This last point open the discussion on the possible benefits of a mixed GP/SP architecture for this area of computing, a topic which is outside the scope of this paper. We would in any case point out that, differently from other computational areas like High Energy Physics or Astrophysics, <sup>6</sup> the codes mentioned above require CPU as well as memory and storage I/O top performances. Hence, the mixed GP/SP solution to the computing environment could surely represent the best viable way to High Performance Computing in the short-medium terms.

Furthermore, the expected performances of the SP chips dedicated to this High Performance area of Computing are at least of one order of magnitude better than the corresponding GP RISC processors (the SP chip will eventually perform with greater performances over the GP counterpart and stated by the published vendor benchmarks). This, together with the expected feasibility of the SP board over a standard PCI bus, can improve the large diffusion of this kind of HPC solution with immediate economic benefits for the producer.

<sup>&</sup>lt;sup>6</sup> The interested reader can refers to the articles on the parallel SP machines, APE and GRAPE, presented in this issue for any specific computational details.

### Acknowledgements

We wish to thanks the kind help of Prof. F.A. Gianturco and Prof. L. Colombo for many helpful discussions on the topics covered by this paper, Dr. A. Pieretti for the Gaussian98 results and the CASPUR computational centre for providing the computer architectures used in this work.

### References

- E.g. see, E. Clementi, G. Corongiu (Eds.), METECC-95, STEF, Italy, 1995.

M.J. Frish, G.W. Trucks, H.B. Schlegel, G.E. Scuseria, M.A. Robb, J.R. Cheesman, V.G. Zakrrewsky, J.A. Montgomery, R.E. Strabmann, J.C. Burant, S. Dapprich, J.M. Millam, A.D. Daniels, K.N. Kudin, M.C. Strain, O. Farkas, J. Tomasi, V. Barone, M. Cossi, R. Cammi, B. Menucci, C. Pomelli, C. Adamo, S. Clifford, J. Ochtersky, G.A. Petersson, P.Y. Ayala, Q. Cui, K. Morokuma, D.K. Malick, A. D. Rabuck, K. Raghavachari, J.B. Foresman, J. Cioslowsky, J.V. Ortiz, B.B. Stefanov, G. Liu, A. Liashenko, P. Piskorz, I. Komáromi, R. Gomperts, R.L. Martin, D.J. Fox, T. Keith, M.A. Al-Laham, C.Y. Peng, A. Nanayakkara, C. Gonzales, M. Challacombo, P.M.W. Gill, B.G. Johnson, W. Chen, M.W. Wong, J.L. Andres, M. Head-Gordon, E.S. Replogle, J.A. Pople, Gaussian R. (Revision A.7), Gaussian Inc., Pittsburg, PA, 1008

- See, e.g., W.F. van Gunsteren, X. Daura, A.E. Mark, GROMOS force field, in: N.L. Allinger, T. Clark, J. Gasteiger, P.A. Kollman, H.F. Schaefer III, P. Schreiner (Eds.), Encyclopedia of Computational Chemistry, Vol. 2, Wiley and Sons, London, 1998, pp. 1211–1216.

S. Achterop, R.v. Drunen, D.v.d. Spoel, A. Sijbers, H. Keegstra, B. Reitsma, M.K.R. Renardus, Gormacs: A Parallel Computer for Molecular Dynamics Simulations, Proceedings of Physics Computing 92, Vol. 1, World Scientific, Singapore, 1993

- [5] R. Car, M. Parinello, Phys. Rev. Lett. 55 (1985) 2471.

- C.Z. Wang, K.M. Ho, in: 1. Prigogine, A.A. Rice (Eds.), Advances in Chemical Physics, Vol. LXXXIX, p. 651.

- [7] H.J.C. Berendsen et al., Selected parallel applications and pratical elements, in: Aspects of Computational Science, NCF, 1995, Chapter

- [8] D.G. Green, K.E. Meacham, M. Surridge, F. van Hoesel, H.J.C. Berendsen, Parallelization of Molecular Dynamics Code. GROMOS87 parallelization for distributed memory architecture, in: Methods and Techniques in Computational Chemistry: METECC-95, STEF, 1995.

[9] D. Roccatano, R. Bizzarn, G. Chillemi, N. Sanna, A. Di Nola, J. Comput. Chem. 19 (1998) 685.

- [10] E.g. see, http://www.caspur.it.

- [11] N. Sanna, F.A. Gianturco, SCELib: A parallel computational library of molecular properties in the single center approach, Comput. Phys. Comm. 128 (2000) 139.

- [12] Digital Extended Mathematical Library (DXML), http://www.digital.com/hpc/software/dxml.html.

[13] Engeneering and Scientific Subroutine Library (ESSL), http://www.research.ibm.com/acte/Opt\_Lib/Topic\_OptLibraries.html.

- [14] Sec. e.g., a recent unpublised work by K. Goto on some BLAS subroutines implemented on the Alpha ev56/ev6 microprocessors, by directly contacting the author at the e-mail goto@statabo.rm.or.jp.

[15] R.G. Parr, W. Yang, Density Functional Theory of Atoms and Molecules, Oxford University Press, New York, 1989

- [16] L. Colombo, M. Rosati, Parallel tight-binding molecular dynamics simulations on symmetric multiprocessing platforms, Comput. Phys. Comm. 128 (2000) 108.

- G. Chillenti, A. Pieretti, M. Rosati, N. Sanna, The Performance of chemical-physics codes on CASPUR parallel architectures, CASPUR

- [18] A.J. van der Steen (Ed.), Aspects of Computational Science, NCF Publ., Den Haag, The Netherlands, 1995.

[19] C.C. Roothaan, Rev. Mod. Phys. 23 (1951) 69.

- G.G. Hall, Proc. Roy. Soc. (London) A 205 (1951) 541.

- [20] E. Clementi (Ed.), Appendices 7C-7E in MOTECC-90, Modern Techniques in Computational Chemistry, ESCOM, Leiden, The

- [21] R.C. Raffenetti, Chem. Phys. Lett. 20 (1973) 335.

- [22] For a discussion of SCF convergence and stability see, H.B. Schlegel, J. McDouall, in: C. Ogretir, I.G. Csizmadia (Eds.), Computational Advances in Organic Chemistry, Kluwer, The Netherlands, 1991

- [23] W.J. Hehre, L. Radom, P.v.R. Schleyer, J.A. Pople, Ab Initio Molecular Orbital Theory, Wiley and Sons, New York, 1986.

[24] M.P. Alfen, D.J. Tildesley, Computer Simulations of Liquids, Oxford University Press, Oxford, 1991.

[25] L. Colombo, in: D. Stauffer (Ed.), Annual Review of Computational Physics U, World Scientific, Singapore, 1996, p. 147.

- [26] I. Kwon, R. Biswas, C.Z. Wang, K.M. Ho, C.M. Soukoulis, Phys. Rev. B 49 (1994) 7242.

[27] http://www.netlib.org/lapack/.

- [28] G.H. Golub, C.F. Van Loan, Matrix Computations, 3rd edn., Johns Hopkins University Press, Baltimore, 1996

- [29] I.J. Dongarra, D.C. Sorensen, A fully parallel algorithm for the symmetric eigenvalue problem, SIAM J. Sci. Stat. Comp. 8 (1987) 175-

- [30] http://www.nag.com/numeric/FS/FS.html/.

[31] http://www.netlib.org/blas/.

- [32] J.-P. Ryckaert, G. Ciccotti, H.J.C. Berendsen, J. Comput. Phys. 23 (1977) 327.

- J.-P. Kyckaert, G. Ciccotti, H.J.C. Berendsen, J. Comput. Phys. 23 (1977) 327.

A. Beguelin, J. Dongarra, A. Geist, R. Manchek, V. Sunderam, Oak Ridge Natl. Laboratory Tech Report TM-11826 1, 1991.

W. Gropp, E. Lusk, A. Skjellum, Using MPI Portable Parallel Programming with the Message Passing, MIT Press, 1994.

B.H. Bransdsen, C.J. Joachain, Physics of Atoms and Molecules, J. Wiley and Sons, New York, 1987, p. 290.

See, e.g., R. Moccia, J. Chem. Phys. 40 (1964) 2164, 2176, 2186.

See, e.g., F.A. Gianturco, D.G. Thompson, A.K. Jain, in: W.M. Huo, F.A. Gianturco (Eds.), Computational Methods for Electron Molecule Publishers. Physics Man. Mach. 2016. See, e.g., F.A. Gianturco, D.G. Thompson, A.K. Jain, in: W.M. Huo, F.A. Gianturco (Eds.), Computational Methods for Electron Molecule Collisions, Plenum, New York, 1994.

See, e.g., F.A. Gianturco, R.R. Lucchese, N. Sanna, J. Chem. Phys. 104 (17) (1996) 6482.

See, e.g., F.A. Gianturco, R.R. Lucchese, N. Sanna, J. Phys. B: At. Mol. Opt. Phys. 32 (1999) 2181.

S.L. Altmann, The Cubic group, Proc. Camb. Phil. Soc. 53 (1957) 343.

F.A. Gianturco, R.R. Lucchese, N. Sanna, J. Chem. Phys. 100 (9) (1994) 1.

H.H.H. Homeier, E.O. Steinborn, J. Mol. Struct. (Theochem) 368 (1996) 31.

N. Sanna, F.A. Gianturco, R.R. Gianturco, R.C. Gianturco, C.C. Lib API: an interface to the parallel computation of molecular properties, in preparation.

N. Sanna, Vector spherical harmonics: Concepts and applications to the single centre expansion method, Comput. Phys. Comm. 132 (2000) 66.

- (2000) 66.

[45] W.H. Press et al., Numerical Recipes, 2nd edn., Cambridge University Press, 1992.

[46] See, e.g., J.M. Smith, F.W.J. Olver, D.W. Lozier, Extended-range arithmetic and normalized legendre polynomials, in: ACM Trans. Math. Software, March 1981, pp. 93–105.

[47] R. Curik, F.A. Gianturco, N. Sanna, J. Phys. B (2000) to be published.

# Attachment 5A

# Splash 2

FPGAs in a Custom Computing Machine

Duncan A. Buell Jeffrey M. Arnold Walter J. Kleinfelder

Splash 2

FPGAs in a Custom

Computing Machine

# Splash 2 FPGAs in a Custom Computing Machine

Duncan A. Buell Jeffrey M. Arnold Walter J. Kleinfelder Editors Center for Computing Sciences Bowie, Maryland

IEEE Computer Society Press Los Alamitos, California

Washington

Brussels

Tokyo

### Library of Congress Cataloging-in-Publication Data

Buell, Duncan A.

Splash 2: FPGAs in a custom computing machine / Duncan A. Buell. Jeffrey M. Arnold, Walter J. Kleinfelder.

p. cm.

Includes bibliographical references and index.

ISBN 0-8186-7413-X

1. Spash 2 (Computer) 2. Electronic digital computers-Design and construction. I. Arnold, Jeffrey M. II. Kleinfelder, Walter J.

III. Title.

QA76.8.S65B84 004.2 '2-dc20

95-47397 CIP

IEEE Computer Society Press 10662 Los Vaqueros Circle P.O. Box 3014 Los Alamitos, CA 90720-1264

Copyright @ 1996 by The Institute of Electrical and Electronics Engineers, Inc. All rights reserved.

Copyright and Reprint Permissions: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy isolated pages beyond the limits of US copyright law, for private use of their patrons. Other copying, reprint, or republication requests should be addressed to: IEEE Copyrights Manager, IEEE Service Center, 445 Hoes Lane, P.O. Box 1331, Piscataway, NJ 08855-1331.

# IEEE Computer Society Press Order Number BP07413 Library of Congress Number 95-47397 ISBN 0-8186-7413-X

Additional copies may be ordered from:

IEEE Computer Society Press Customer Service Center 10662 Los Vaqueros Circle P.O. Box 3014

Los Alamitos, CA 90720-1264 Tel: +1-714-821-8380 Fax: +1-714-821-4641

Email: cs.books@computer.org

IEEE Service Center 445 Hoes Lane

P.O. Box 1331 Piscataway, NJ 08855-1331 Tel: +1-908-981-1393

Fax: +1-908-981-9667

mis.custserv@computer.org

IEEE Computer Society 13. Avenue de l'Aquilon B-1200 Brussels BELGIUM

Tel: +32-2-770-2198 Fax: +32-2-770-8505 euro.ofc@computer.org IEEE Computer Society Ooshima Building

2-19-1 Minami-Aoyama Minato-ku, Tokyo 107 JAPAN

Tel: +81-3-3408-3118 Fax: +81-3-3408-3553

tokyo.ofc@computer.org

QA76. 8

Assistant Publisher: Matt Loeb Technical Editor: Dharma P. Agrawal Acquisitions Assistant: Cheryl Smith Advertising/Promotions: Tom Fink Production Editor: Lisa O'Conner

Cover Image: Dan Kopetzky, Center for Computing Sciences

Printed in the United States of America

The Institute of Eleberca And Electronics Engineers, Inc

AUG 8 - 1996 F

# **Contents**

|   | PRE | FACE                                                                                                                                         | xi |

|---|-----|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1 | CUS | STOM COMPUTING MACHINES: AN INTRODUCTION                                                                                                     | 1  |

|   | 1.1 | Introduction 1                                                                                                                               |    |

|   | 1.2 | The Context for Splash 2 4                                                                                                                   |    |

|   |     | 1.2.1 FPGAs, 4<br>1.2.2 Architecture, 5<br>1.2.3 Programming, 6                                                                              |    |

| 2 | THE | ARCHITECTURE OF SPLASH 2                                                                                                                     | 10 |

|   | 2.1 | Introduction 10                                                                                                                              |    |

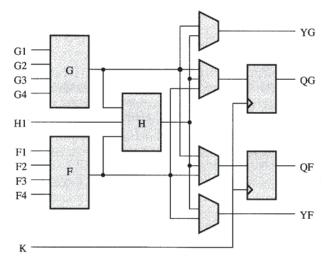

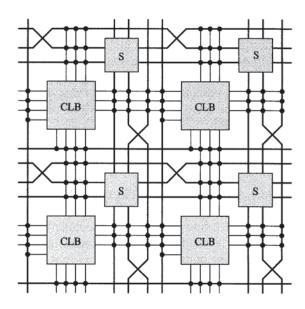

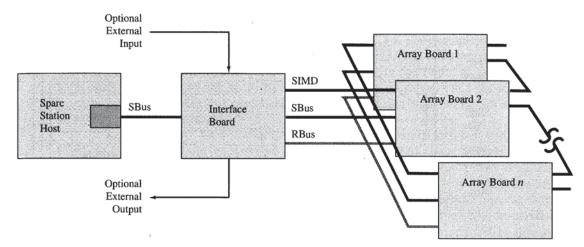

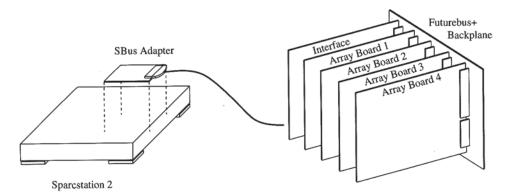

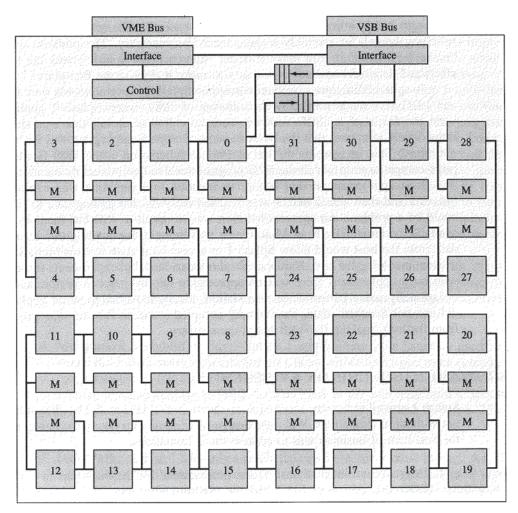

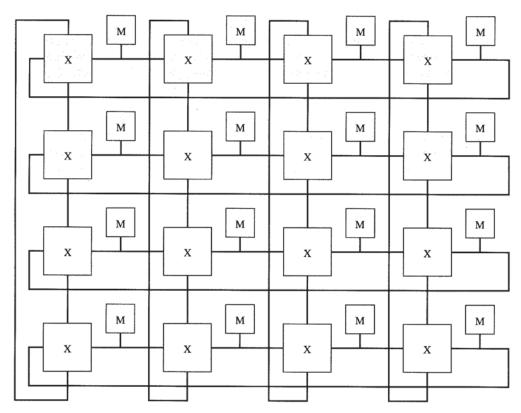

|   | 2.2 | The Building Blocks 11                                                                                                                       |    |

|   | 2.3 | The System Architecture 12                                                                                                                   |    |

|   | 2.4 | Data Paths 13                                                                                                                                |    |

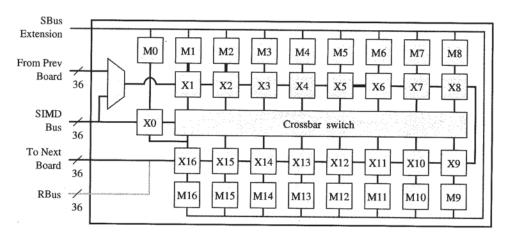

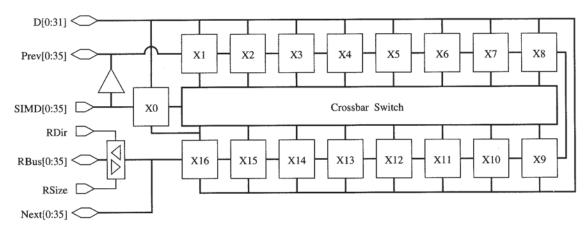

|   | 2.5 | The Splash 2 Array Board 16                                                                                                                  |    |

|   |     | <ul> <li>2.5.1 The Linear Array, 16</li> <li>2.5.2 The Splash 2 Crossbar, 16</li> <li>2.5.3 Xilinx Chip X0 and Broadcast Mode, 17</li> </ul> |    |

|   | 2.6 | The Interface Board and Control Features 17                                                                                                  |    |

|   |        | INDIVAKE IVII LEMENTATION                                                                                                                                                       | ,  |

|---|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 3.1    | Introduction 19                                                                                                                                                                 |    |

|   | 3.2    | Development Board Design 21                                                                                                                                                     |    |

|   | 3.3    | Interface Board Design 21                                                                                                                                                       |    |

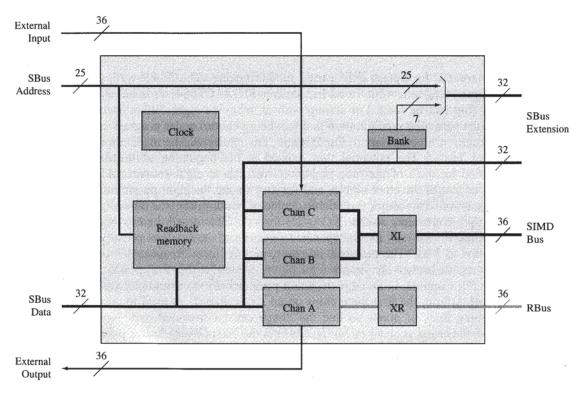

|   |        | 3.3.1 DMA Channel, 23 3.3.2 XL and XR, 23 3.3.3 Interrupts, 24 3.3.4 Clock, 24 3.3.5 Programming and Readback, 24 3.3.6 Miscellaneous Registers, 25                             |    |

|   | 3.4    | Array Board Design 25                                                                                                                                                           |    |

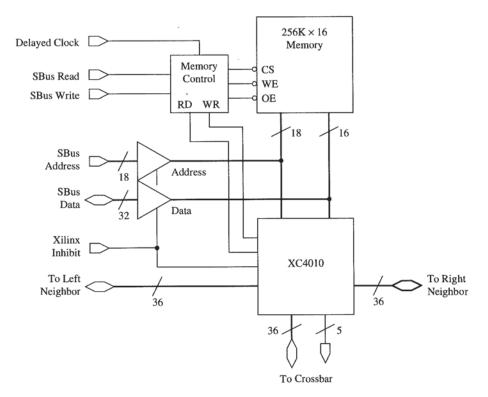

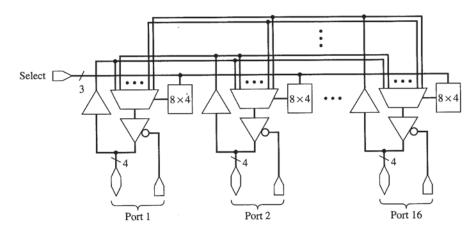

|   |        | 3.4.1 Processing Element, 26 3.4.2 Control Element, 28 3.4.3 External Memory Access, 28 3.4.4 Crossbar, 28 3.4.5 Programming and Readback, 29 3.4.6 Miscellaneous Registers, 29 |    |

| 4 | \$ SPL | ASH 2: THE EVOLUTION OF A NEW ARCHITECTURE                                                                                                                                      | 31 |

|   | 4.1    | Splash 1 31                                                                                                                                                                     |    |

|   | 4.2    | Splash 2: Thoughts on a Redesign 34                                                                                                                                             |    |

|   | 4.3    | Programming Language 36                                                                                                                                                         |    |

|   | 4.4    | Choice of FPGAs 37                                                                                                                                                              |    |

|   | 4.5    | Choice of Host and Bus 38                                                                                                                                                       |    |

|   | 4.6    | Chip-to-Chip Interconnections 39                                                                                                                                                |    |

|   | 4.7    | Multitasking 42                                                                                                                                                                 |    |

|   | 4.8    | Chip X0 and Broadcast 43                                                                                                                                                        |    |

|   | 4.9    | Other Design Decisions 43                                                                                                                                                       |    |

| 5 | SOFT   | TWARE ARCHITECTURE                                                                                                                                                              | 46 |

|   | 5.1    | Introduction 46                                                                                                                                                                 |    |

|   | 5.2    | Background 47                                                                                                                                                                   |    |

|   | 5.3    | VHDL as a Programming Language 49                                                                                                                                               |    |

|   |        | 5.3.1 History and Purpose of VHDL, 50 5.3.2 VHDL Language Features, 50 5.3.3 Problems with VHDL, 51                                                                             |    |

|   | 5.4    | Software Environment 51                                                                                                                                                         |    |

|   |        |                                                                                                                                                                                 |    |

|   |        |                                                                                                                                                                                 |    |

|      | Programmer's View of Splash 2 55                                                                                                                                                                               | 5.5     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|      | <ul> <li>5.5.1 Programming Process, 55</li> <li>5.5.2 Processing Element View, 56</li> <li>5.5.3 Interface Board View, 57</li> <li>5.5.4 Host View, 57</li> </ul>                                              |         |

| 60   | TWARE IMPLEMENTATION                                                                                                                                                                                           | 6 SOF   |

| ,2,2 | Introduction 60                                                                                                                                                                                                | 6.1     |

|      | VHDL Environment 60                                                                                                                                                                                            | 6.2     |

|      | <ul> <li>6.2.1 Splash 2 VHDL Library, 61</li> <li>6.2.2 Standard Entity Declarations, 61</li> <li>6.2.3 Programming Style, 64</li> </ul>                                                                       |         |

|      | Splash 2 Simulator 66                                                                                                                                                                                          | 6.3     |

|      | <ul> <li>6.3.1 Structure, 66</li> <li>6.3.2 Configuring the Simulator, 67</li> <li>6.3.3 Input and Output, 68</li> <li>6.3.4 Crossbar and Memory Models, 68</li> <li>6.3.5 Hardware Constraints, 70</li> </ul> |         |

|      | Compilation 70                                                                                                                                                                                                 | 6.4     |

|      | 6.4.1 Logic Synthesis, 70<br>6.4.2 Physical Mapping, 71<br>6.4.3 Debugging Support, 71                                                                                                                         |         |

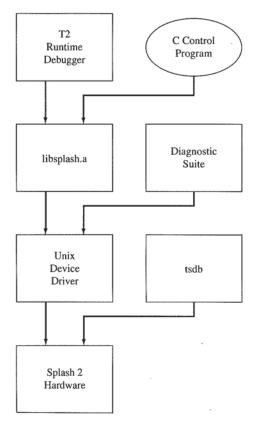

|      | Runtime System 72                                                                                                                                                                                              | 6.5     |

|      | 6.5.1 T2: A Symbolic Debugger, 72<br>6.5.2 Runtime Library, 73<br>6.5.3 Device Driver, 74                                                                                                                      |         |

|      | Diagnostics 75                                                                                                                                                                                                 | 6.6     |

|      |                                                                                                                                                                                                                |         |

| 77   | TA PARALLEL PROGRAMMING MODEL                                                                                                                                                                                  | 7 A DAT |

|      | Introduction 78                                                                                                                                                                                                | 7.1     |

|      | Data-parallel Bit C 80                                                                                                                                                                                         | 7.2     |

|      | 7.2.1 dbC Overview, 80<br>7.2.2 dbC Example, 81                                                                                                                                                                |         |

|      | Compiling from dbC to Splash 2 82                                                                                                                                                                              | 7.3     |

|      | <ul> <li>7.3.1 Creating a Specialized SIMD Engine, 83</li> <li>7.3.2 Generic SIMD Code, 84</li> <li>7.3.3 Generating VHDL, 84</li> </ul>                                                                       |         |

|      | Global Operations 88                                                                                                                                                                                           | 7.4     |

|      | 7.4.1 Nearest-Neighbor Communication, 88                                                                                                                                                                       |         |

|    |      | 7.4.2 Reduction Operations, 89 7.4.3 Host/Processor Communication, 91                                                                                                        |     |

|----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | 7.5  | Optimization: Macro Instructions 92                                                                                                                                          |     |

|    |      | <ul><li>7.5.1 Creating a Macro Instruction, 93</li><li>7.5.2 Discussion, 94</li></ul>                                                                                        |     |

|    | 7.6  | Evaluation: Genetic Database Search 94                                                                                                                                       |     |

|    | 7.7  | Conclusions and Future Work 95                                                                                                                                               |     |

| 8  | SEA  | RCHING GENETIC DATABASES ON SPLASH 2                                                                                                                                         | 97  |

|    | 8.1  | Introduction 97                                                                                                                                                              |     |

|    |      | <ul><li>8.1.1 Edit Distance, 98</li><li>8.1.2 Dynamic Programming Algorithm, 98</li></ul>                                                                                    |     |

|    | 8.2  | Systolic Sequence Comparison 100                                                                                                                                             |     |

|    |      | 8.2.1 Bidirectional Array, 100<br>8.2.2 Unidirectional Array, 103                                                                                                            |     |

|    | 8.3  | Implementation 104                                                                                                                                                           |     |

|    |      | <ul> <li>8.3.1 Modular Encoding, 105</li> <li>8.3.2 Configurable Parameters, 106</li> <li>8.3.3 Bidirectional Array, 107</li> <li>8.3.4 Unidirectional Array, 107</li> </ul> |     |

|    | 8.4  | Benchmarks 107                                                                                                                                                               |     |

|    | 8.5  | Discussion 108                                                                                                                                                               |     |

|    | 8.6  | Conclusions 108                                                                                                                                                              |     |

| 9  | TEXT | SEARCHING ON SPLASH 2                                                                                                                                                        | 110 |

|    | 9.1  | Introduction 110                                                                                                                                                             |     |

|    | 9.2  | The Text Searching Algorithm 111                                                                                                                                             |     |

|    | 9.3  | Description of the Single-Byte Splash Program 113                                                                                                                            |     |

|    | 9.4  | Timings, Discussion 114                                                                                                                                                      |     |

| 9  | 9.5  | Outline of the 16-bit Approach 115                                                                                                                                           |     |

|    | 9.6  | Conclusions 116                                                                                                                                                              |     |

| 10 | FING | ERPRINT MATCHING ON SPLASH 2                                                                                                                                                 |     |

|    | 10.1 | Introduction 117                                                                                                                                                             | 117 |

|    | 10.2 | Background 120                                                                                                                                                               |     |

|    |      | g.odite 120                                                                                                                                                                  |     |

|    |      |                                                                                                                                                                              |     |

|    |      |                                                                                                                                                                              |     |

|    |       | 10.2.1 Pattern Recognition Systems, 121<br>10.2.2 Terminology, 122<br>10.2.3 Stages in AFIS, 123                                                                                                                                                                                                                   |     |

|----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | 10.3  | Splash 2 Architecture and Programming Models 125                                                                                                                                                                                                                                                                   |     |

|    | 10.4  | Fingerprint Matching Algorithm 125                                                                                                                                                                                                                                                                                 |     |

|    |       | 10.4.1 Minutia Matching, 126<br>10.4.2 Matching Algorithm, 127                                                                                                                                                                                                                                                     |     |

|    | 10.5  | Parallel Matching Algorithm 128                                                                                                                                                                                                                                                                                    |     |

|    |       | <ul><li>10.5.1 Preprocessing on the Host, 131</li><li>10.5.2 Computations on Splash, 132</li><li>10.5.3 VHDL Specification for X0, 133</li></ul>                                                                                                                                                                   |     |

|    | 10.6  | Simulation and Synthesis Results 134                                                                                                                                                                                                                                                                               |     |

|    | 10.7  | Execution on Splash 2 137                                                                                                                                                                                                                                                                                          |     |

|    |       | 10.7.1 User Interface, 137<br>10.7.2 Performance Analysis, 137                                                                                                                                                                                                                                                     |     |

|    | 10.8  | Conclusions 139                                                                                                                                                                                                                                                                                                    |     |

| 1  |       | H-SPEED IMAGE PROCESSING WITH SPLASH 2                                                                                                                                                                                                                                                                             | 141 |

|    | 11.1  | Introduction 141                                                                                                                                                                                                                                                                                                   |     |

|    | 11.2  | The VTSplash System 142                                                                                                                                                                                                                                                                                            |     |

|    | 11.3  | Image Processing Terminology and Architectural Issues 143                                                                                                                                                                                                                                                          |     |

|    | 11.4  | Case Study: Median Filtering 150                                                                                                                                                                                                                                                                                   |     |

|    | 11.5  | Case Study: Image Pyramid Generation 153                                                                                                                                                                                                                                                                           |     |

|    |       | <ul> <li>11.5.1 Gaussian Pyramid, 154</li> <li>11.5.2 Two Implementations for Gaussian Pyramid on Splash 2, 155</li> <li>11.5.3 The Hybrid Pipeline Gaussian Pyramid Structure, 157</li> <li>11.5.4 The Laplacian Pyramid, 157</li> <li>11.5.5 Implementation of the Laplacian Pyramid on Splash 2, 159</li> </ul> |     |

|    | 11.6  | Performance 159                                                                                                                                                                                                                                                                                                    |     |

|    | 11.7  | Summary 163                                                                                                                                                                                                                                                                                                        |     |

| 12 | THE I | PROMISE AND THE PROBLEMS                                                                                                                                                                                                                                                                                           | 166 |

|    | 12.1  | Some Bottom-Line Conclusions 166                                                                                                                                                                                                                                                                                   |     |

|    |       | 12.1.1 High Bandwidth I/O Is a Must, 166 12.1.2 Memory Is a Must, 167 12.1.3 Programming Is Possible, and Becoming More So, 168 12.1.4 The Programming Environment Is Crucial, 168                                                                                                                                 |     |

|    | 122   | To Where from Here? 160                                                                                                                                                                                                                                                                                            |     |

# Splash 2

# FPGAs in a Custom Computing Machine

edited by Duncan A. Buell, Jeffrey M. Arnold, and Walter J. Kleinfelder

Details the complete Splash 2 project—the hardware and software systems, their architecture and implementation, and the design process by which the architecture evolved from an earlier version machine. In addition to the description of the machine, this book explains why Splash 2 was engineered. It illustrates several applications in detail, allowing you to gain an understanding of the capabilities and the limitations of this kind of computing device.

The Splash 2 program is significant for two reasons. First, it is part of a complete computer system that achieves supercomputer like performance on a number of different applications. The second significant aspect is that this large system is capable of performing real computations on real problems. In order to understand what happens when the application programmer designs the processor architecture of the machine that executes his programs, it is necessary to see the system as a whole. This book looks in-depth at one of the handful of data points in the design space of this new kind of machine.

## Contents:

- Custom Computing Machines: An Introduction

- The Architecture of Splash 2

- Hardware Implementation

- Splash 2: The Evolution of a New Architecture

- Software Architecture

- Software Implementation

- A Data Parallel Programming Model

- Searching Genetic Databases on Splash 2

- Text Searching on Splash 2

- Fingerprint Matching on Splash 2

- High-Speed Image Processing with Splash 2

- The Promise and the Problems

- An Example Application

Published by the IEEE Computer Society Press 10662 Los Vaqueros Circle P.O. Box 3014 Los Alamitos, CA 90720-1314

IEEE Computer Society Press Order Number BP07413 Library of Congress Number 95-47397 ISBN 0-8186-7413-X X-E142-9818-0 NBZI

# Attachment 5B

QA 76 .8 .S68 S68 1996

# Splash 2

# FPGAs in a Custom Computing Machine

LANDOVER GenColl

Duncan A. Buell Jeffrey M. Arnold Walter J. Kleinfelder

# Splash 2 FPGAs in a Custom Computing Machine

Xilinx, the Xilinx logo, XC3090, XC4010, XBLOX, XACT, LCA, and Configurable Logic Cell are trademarks of Xilinx, Inc.

CM-2 and Paris are trademarks of Thinking Machines Corporation.

VMEbus is a trademark of Motorola Corporation.

SPARC and SPARCstation are trademarks of SPARC International, Inc. Products bearing a SPARC trademark are based on an architecture developed by Sun Microsystems, Inc. SPARCstation is licensed exclusively to Sun Microsystems, Inc.

UNIX is a trademark of UNIX System Laboratories.

Sun, Sun Workstation, SunOS, and SBus are trademarks of Sun Microsystems, Inc.

Design Compiler and FPGA Compiler are trademarks of Synopsys, Inc.

DEC is a trademark of Digital Equipment Corporation.

Verilog is a trademark of Cadence Design Systems, Inc.

# Splash 2 FPGAs in a Custom Computing Machine

Duncan A. Buell Jeffrey M. Arnold Walter J. Kleinfelder Editors Center for Computing Sciences Bowie, Maryland

# IEEE Computer Society Press Los Alamitos, California

Washington

Brussels

Tokyo

## Library of Congress Cataloging-in-Publication Data

Buell, Duncan A.

Splash 2: FPGAs in a custom computing machine / Duncan A. Buell, Jeffrey M. Arnold, Walter J. Kleinfelder.

p. cm.

Includes bibliographical references and index.

ISBN 0-8186-7413-X

Spash 2 (Computer)

Electronic digital computers—Design and construction.

Arnold, Jeffrey M. II. Kleinfelder, Walter J. III. Title.

QA76.8.S65B84 1996

004.2 ' 2-dc20

95-47397 CIP

IEEE Computer Society Press 10662 Los Vaqueros Circle P.O. Box 3014 Los Alamitos, CA 90720-1264

Copyright © 1996 by The Institute of Electrical and Electronics Engineers, Inc. All rights reserved.

Copyright and Reprint Permissions: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy isolated pages beyond the limits of US copyright law, for private use of their patrons. Other copying, reprint, or republication requests should be addressed to: IEEE Copyrights Manager, IEEE Service Center, 445 Hoes Lane, P.O. Box 1331, Piscataway, NJ 08855-1331.

# IEEE Computer Society Press Order Number BP07413 Library of Congress Number 95-47397 ISBN 0-8186-7413-X

Additional copies may be ordered from:

IEEE Computer Society Press Customer Service Center 10602 Los Vaqueros Circle P.O. Box 3014 Los Alamitos, CA 90720-1264

Tel: +1-7/4-821-8380 Fax: +1-7/14-821-4641

Email: cs.books@computer.org

445 Hoes Lane

P.O. Box 1331

Piscataway, NJ 08855-1331

Tel: +1-908-981-1393

Fax: +1-908-981-9667

mis.custsery@computer.org

IEEE Service Center

IEEE Computer Society

13, Avenue de l'Aquilon

B-1200 Brussels

BELGIUM

Tel: +32-2-770-2198

Tel: +32-2-770-2198 Fax: +32-2-770-8505 euro.ofc@computer.org IEEE Computer Society Ooshima Building 2-19-1 Minami-Aoyama Minato-ku, Tokyo 107

JAPAN Tel: +81-3-3408-3118

Fax: +81-3-3408-3553 tokyo.ofc@computer.org

Assistant Publisher: Matt Loeb Technical Editor: Dharma P. Agrawal Acquisitions Assistant: Cheryl Smith Advertising/Promotions: Tom Fink Production Editor: Lisa O'Conner

Cover Image: Dan Kopetzky, Center for Computing Sciences

Printed in the United States of America

The Institute of Electrical and Electronics Engineers, Inc

# QA76 .8 .S68 S68 1996 **Contents**

|   | PREFA                                      | CE                                                                                                                                           | xi |  |  |  |  |

|---|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

| 1 | CUSTOM COMPUTING MACHINES: AN INTRODUCTION |                                                                                                                                              |    |  |  |  |  |

|   | 1.1 Introduction 1                         |                                                                                                                                              |    |  |  |  |  |

|   | 1.2                                        | The Context for Splash 2 4                                                                                                                   |    |  |  |  |  |

|   |                                            | 1.2.1 FPGAs, 4 1.2.2 Architecture, 5 1.2.3 Programming, 6                                                                                    |    |  |  |  |  |

| 2 | THE ARCHITECTURE OF SPLASH 2               |                                                                                                                                              |    |  |  |  |  |

|   | 2.1                                        | Introduction 10                                                                                                                              |    |  |  |  |  |

|   | 2.2                                        | The Building Blocks 11                                                                                                                       |    |  |  |  |  |

|   | 2.3 The System Architecture 12             |                                                                                                                                              |    |  |  |  |  |

|   | 2.4                                        | Data Paths 13                                                                                                                                |    |  |  |  |  |

|   | 2.5                                        | The Splash 2 Array Board 16                                                                                                                  |    |  |  |  |  |

|   |                                            | <ul> <li>2.5.1 The Linear Array, 16</li> <li>2.5.2 The Splash 2 Crossbar, 16</li> <li>2.5.3 Xilinx Chip X0 and Broadcast Mode, 17</li> </ul> |    |  |  |  |  |

|   | 2.6                                        | The Interface Board and Control Features 17                                                                                                  |    |  |  |  |  |

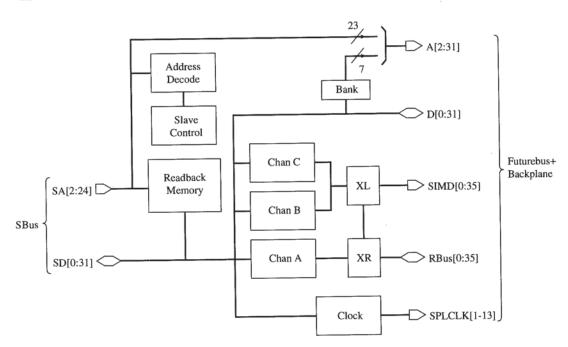

|   | 3.3   | Interface Board Design 21                                                                                                                                                                                                                        |    |

|---|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |       | 3.3.1 DMA Channel, 23 3.3.2 XL and XR, 23 3.3.3 Interrupts, 24 3.3.4 Clock, 24 3.3.5 Programming and Readback, 24 3.3.6 Miscellaneous Registers, 25                                                                                              |    |

|   | 3.4   | Array Board Design 25                                                                                                                                                                                                                            |    |

|   |       | <ul> <li>3.4.1 Processing Element, 26</li> <li>3.4.2 Control Element, 28</li> <li>3.4.3 External Memory Access, 28</li> <li>3.4.4 Crossbar, 28</li> <li>3.4.5 Programming and Readback, 29</li> <li>3.4.6 Miscellaneous Registers, 29</li> </ul> |    |

| 4 | SPLAS | SH 2: THE EVOLUTION OF A NEW ARCHITECTURE                                                                                                                                                                                                        | 31 |

|   | 4.1   | Splash 1 31                                                                                                                                                                                                                                      |    |

|   | 4.2   | Splash 2: Thoughts on a Redesign 34                                                                                                                                                                                                              |    |

|   | 4.3   | Programming Language 36                                                                                                                                                                                                                          |    |

|   | 4.4   | Choice of FPGAs 37                                                                                                                                                                                                                               |    |